UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

LAÉRCIO LIMA PILLA

Topology-Aware Load Balancing for Performance Portability over Parallel High Performance Systems

> Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Philippe Olivier Alexandre Navaux Advisor

Prof. Jean-François Méhaut Advisor

#### **CIP – CATALOGING-IN-PUBLICATION**

Laércio Lima Pilla,

Topology-Aware Load Balancing for Performance Portability over Parallel High Performance Systems /

Laércio Lima Pilla. – Porto Alegre: Programa de Pós-Graduação em Computação da UFRGS, 2014.

125 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2014. Advisor: Philippe Olivier Alexandre Navaux; Advisor: Jean-François Méhaut.

1. Computer architecture, Parallel programming, Profiling, Scheduling. I. Navaux, Philippe Olivier Alexandre. II. Méhaut, Jean-François. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. José Carlos Alexandre Netto Pró-Reitor de Coordenação Acadêmica: Prof. Rui Vicente Oppermann Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb Coordenador do PPGC: Prof. Luigi Carro Bibliotecário-chefe do Instituto de Informática: Alexsander Borges Ribeiro

To the set of my family, the set of my friends, the set of my colleagues, the set of my collaborators, and specially for all their intersections.

## CONTENTS

| LIST OF ABBREVIATIONS AND ACRONYMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                           |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                           |

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                           |

| RESUMO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                           |

| 1INTRODUCTION1.1Problem statement1.2Objectives and thesis contributions1.3Research context1.4Document organization                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19<br>20<br>20<br>21<br>21                                                                   |

| 2BACKGROUND2.1Components of high performance computing platforms2.1.1Composition2.1.2Asymmetry and nonuniformity at topology levels2.1.2Asymmetry and nonuniformity at topology levels2.2Characterization of scientific applications2.2.1Tasks: load and communication2.2.2Application irregularity and dynamicity2.2.3Examples of scientific applications2.3.4Task mapping2.3.1Load imbalance and costly communications2.3.2Performance portability2.3.3Information required for mapping tasks2.4.4Machine topology identification2.4.5Discussion | 23<br>23<br>24<br>27<br>28<br>28<br>29<br>31<br>32<br>32<br>33<br>34<br>35<br>35<br>36<br>37 |

| 3 MODELING THE TOPOLOGIES OF HPC PLATFORMS         3.1 Topology representation         3.1.1 Topology tree         3.1.2 Communication costs         3.2 Topology modeling         3.2.1 Memory hierarchy of multicore platforms                                                                                                                                                                                                                                                                                                                   | <ol> <li>39</li> <li>39</li> <li>39</li> <li>40</li> <li>41</li> <li>41</li> </ol>           |

| 3.2.2         | HPC network topology                                   | 43  |

|---------------|--------------------------------------------------------|-----|

| 3.3           | Topology model evaluation                              | 44  |

| 3.3.1         | Latency and bandwidth measurements                     | 45  |

| 3.3.2         | Use of midpoints                                       | 47  |

| 3.3.3         | Nonuniformity measurement at memory level              | 48  |

| 3.4           | Machine topology library                               | 51  |

| 3.4.1         | Tools                                                  | 51  |

| 3.4.2         | Data storage                                           | 51  |

| 3.4.3         | Library interface                                      | 52  |

| 4 0           |                                                        | 50  |

|               |                                                        | 53  |

| 4.1           | Centralized algorithms                                 | 53  |

| 4.1.1         | NUCOLB: Nonuniform communication costs load balancer   | 54  |

| 4.1.2         | HwTOPOLB: Hardware topology load balancer              | 57  |

| 4.1.3         | Comparison between proposed centralized algorithms     | 62  |

| 4.2           | Hierarchical algorithms                                | 62  |

| 4.2.1         | HIERARCHICALLB: Hierarchical load balancer composition | 62  |

| 4.3           | Implementation details                                 | 65  |

| 4.4           | Conclusion                                             | 68  |

| 5 R           | ELATED WORK ON TASK MAPPING                            | 69  |

| 5.1           | Load balancing algorithms                              | 69  |

| 5.1.1         | Graph partitioning                                     | 70  |

| 5.1.2         | Runtime level load balancers                           | 71  |

| 5.1.3         | Application-focused load balancers                     | 74  |

| <b>5.1</b> .5 | Work stealing                                          | 75  |

| 5.3           | Process mapping                                        | 78  |

| 5.4           | Discussion                                             | 79  |

|               |                                                        | 17  |

|               |                                                        | 85  |

| 6.1           | Evaluation methodology                                 |     |

| 6.1.1         | Experimental platforms                                 | 85  |

| 6.1.2         | Benchmarks and applications                            | 86  |

| 6.1.3         | Load balancers                                         | 88  |

| 6.1.4         | Experimental setup                                     | 88  |

| 6.2           | Load balancing on multicore machines                   | 89  |

| 6.2.1         | NUCOLB                                                 | 90  |

| 6.2.2         | HwTopoLB                                               | 95  |

| 6.2.3         | NUCOLB and HwTOPOLB                                    | 98  |

| 6.3           | Load balancing on clusters                             | 100 |

| 6.3.1         | NucolB                                                 | 101 |

| 6.3.2         | HwTopolb                                               | 102 |

| 6.3.3         |                                                        | 105 |

| 6.4           |                                                        | 108 |

|               |                                                        | 111 |

|               |                                                        | 111 |

| 7.1           |                                                        | 111 |

| 7.2           | Perspectives                                           | 113 |

| Α | RESUMO EXPANDIDO EM PORTUGUÊS | 115 |

|---|-------------------------------|-----|

|   | Contextualização              |     |

|   | FERENCES                      |     |

## LIST OF ABBREVIATIONS AND ACRONYMS

| AMPI       | Adaptive MPI                                                                       |

|------------|------------------------------------------------------------------------------------|

| ASIC       | Application-Specific Integrated Circuit                                            |

| BC         | Betweenness Centrality                                                             |

| BRAMS      | Brazilian developments on the Regional Atmospheric Modeling System                 |

| BSP        | Bulk Synchronous Parallel                                                          |

| CN         | Compute Node                                                                       |

| coNCePTuaL | Network Correctness and Performance Testing Language                               |

| C-PML      | Convolutional Perfectly Matched Layer                                              |

| CPU        | Central Processing Unit                                                            |

| GPU        | Graphics Processing Unit                                                           |

| GPPD       | Parallel and Distributed Processing Group                                          |

| HPC        | High Performance Computing                                                         |

| HWLOC      | Portable Hardware Locality                                                         |

| JLPC       | Joint Laboratory for Petascale Computing                                           |

| LB         | Load Balancing                                                                     |

| LICIA      | International Laboratory in High Performance and Ambient Informatics               |

| LIG        | Grenoble Informatics Laboratory                                                    |

| LLC        | Last Level Cache                                                                   |

| MPI        | Message Passing Interface                                                          |

| MPIPP      | MPI Process Placement                                                              |

| MSTII      | Mathematics, Information Sciences and Technologies, and Computer Science           |

| MTS        | Multithreaded Shepherds                                                            |

| NAMD       | NAnoscale Molecular Dynamics                                                       |

| Nanosim    | Nanosimulations and Embedded Applications for Hybrid Multi-core Ar-<br>chitectures |

| NL 6       | NUMAlink 6                                                                         |

| Nonuniform Cache Access                 |

|-----------------------------------------|

| Nonuniform Memory Access                |

| ·                                       |

| Parallel Programming Laboratory         |

| Process Mapping                         |

| Processing Unit                         |

| QuickPath Interconnect                  |

| Random Access Memory                    |

| Regional Atmospheric Modeling System    |

| Runtime System                          |

| Round-Trip Time                         |

| Symmetric Multiprocessor                |

| Simultaneous Multithreading             |

| Single Program, Multiple Data           |

| Transmission Control Protocol           |

| Translation Lookaside Buffer            |

| User Datagram Protocol                  |

| Federal University of Rio Grande do Sul |

| Uniform Memory Access                   |

| Extensible Markup Language              |

| Work Stealing                           |

|                                         |

## **LIST OF FIGURES**

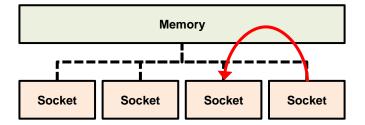

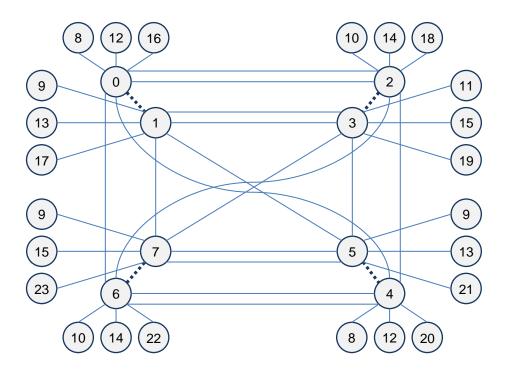

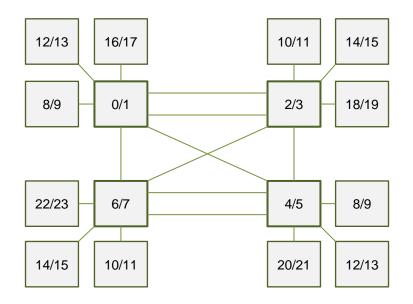

| Figure 2.1:   | Example of machine topology of a UMA machine with 24 PUs dis-<br>tributed in 4 sockets.                                                     | 24       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2.2:   | Example of communication through memory on a UMA machine                                                                                    | 25       |

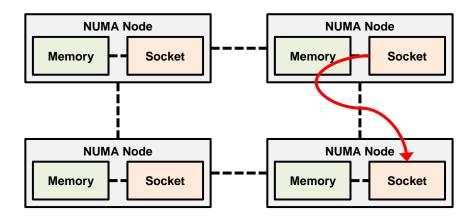

| Figure 2.3:   | Example of a machine topology of a NUMA machine with 24 PUs                                                                                 | ~ ~      |

|               | distributed in 4 NUMA nodes.                                                                                                                | 25       |

| Figure 2.4:   | Example of communication through memory on a NUMA machine.                                                                                  | 26       |

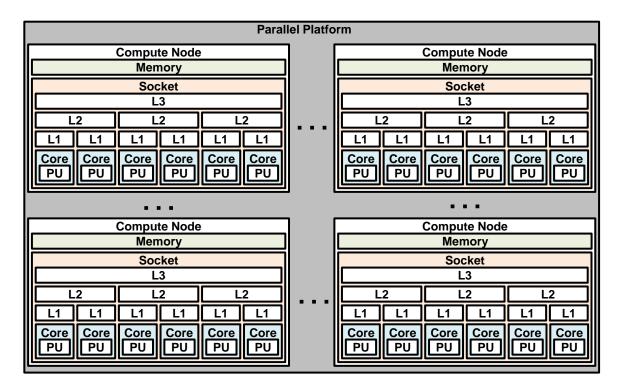

| Figure 2.5:   | Example of a machine topology with multiple compute nodes.                                                                                  | •        |

| <b>D' O</b> ( | 4 UMA compute nodes are illustrated.                                                                                                        | 26       |

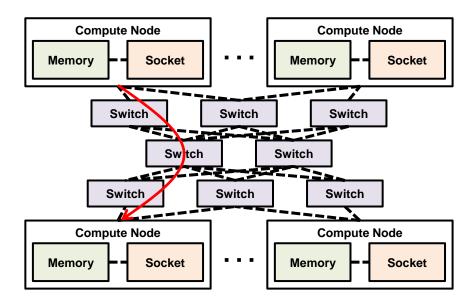

| Figure 2.6:   | Example of communication through network organized as a fat tree.                                                                           | 27       |

| Figure 2.7:   | Different levels of load irregularity and dynamicity.                                                                                       | 30       |

| Figure 2.8:   | Different levels of communication irregularity and dynamicity                                                                               | 30<br>34 |

| Figure 2.9:   | Challenges for performance portability                                                                                                      | 54       |

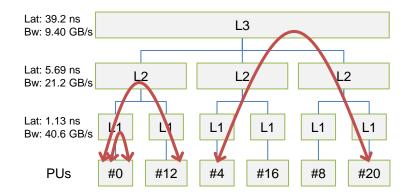

| Figure 3.1:   | Machine topology representation of one socket of machine Xeon24.<br>Different levels of the cache hierarchy present different latencies and | 41       |

| Figure 3.2:   | bandwidths                                                                                                                                  | 41       |

| Figure 3.3:   | scale between the sizes of two levels                                                                                                       | 42       |

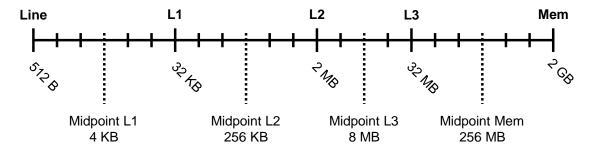

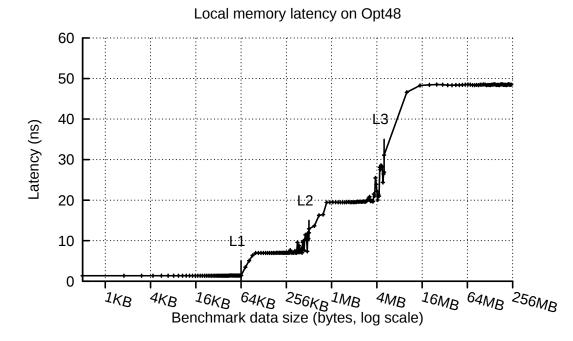

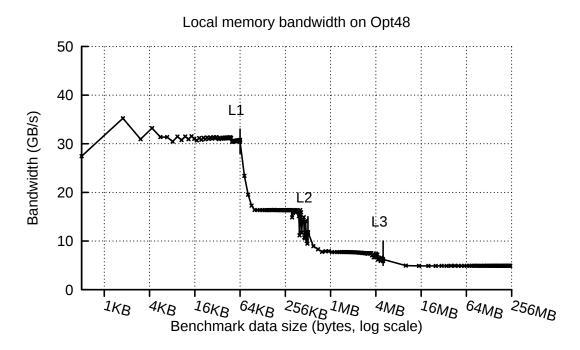

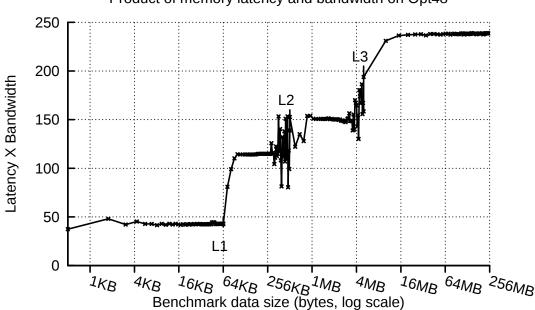

| Figure 5.5.   | sizes on Opt48.                                                                                                                             | 45       |

| Figure 3.4:   | Memory bandwidth measured with bw_mem for different data sizes<br>on Opt48.                                                                 | 46       |

| Figure 3.5:   | Product between memory latency and bandwidth for machine Opt48.                                                                             | 40       |

| Figure 3.6:   | Interconnections of the first eight NUMA nodes of machine Xeon192<br>based on topology file.                                                | 49       |

| Figure 3.7:   | Interconnections of the first eight NUMA nodes of machine Xeon192                                                                           | 49       |

| 1 iguie 5.7.  | based on the machine specification of processor nodes                                                                                       | 49       |

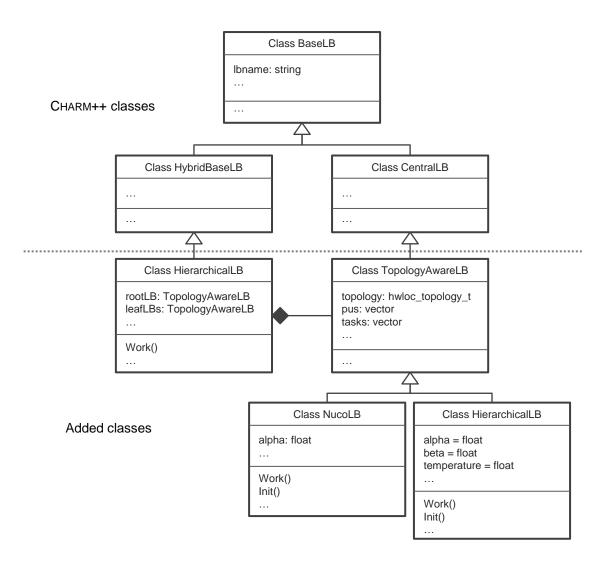

| Figure 4.1:   | Load balancers simplified class diagram.                                                                                                    | 67       |

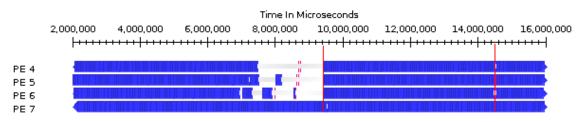

| Figure 6.1:   | Execution of <i>lb_test</i> on PUs 4 to 7 of Xeon32, as captured by Projections.                                                            | 90       |

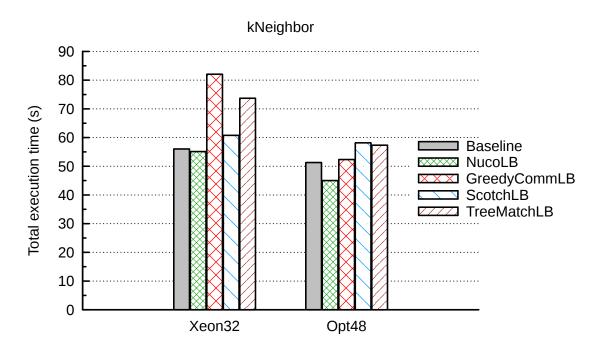

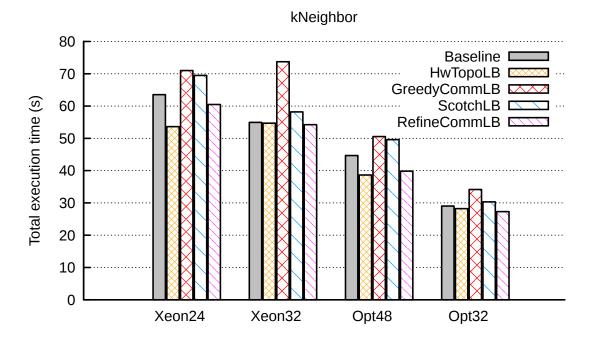

| Figure 6.2:   | Total execution time of <i>kNeighbor</i> with NUCOLB and other load balancers.                                                              | 92       |

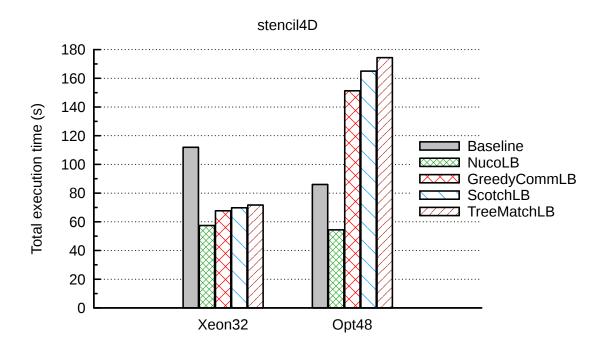

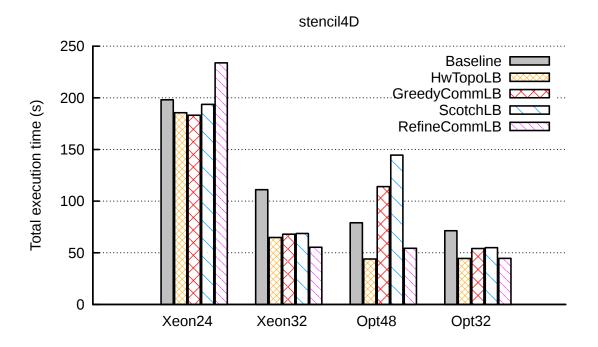

| Figure 6.3:   | Total execution time of <i>stencil4D</i> with NUCOLB and other load balancers.                                                              | 92       |

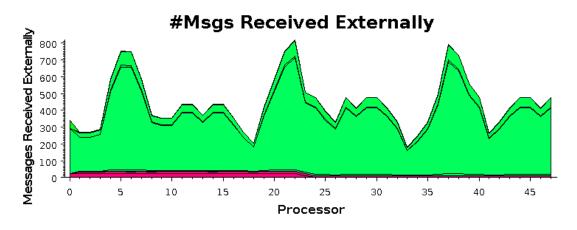

| Figure 6.4:   | Messages received per PU before load balancing (first 10 timesteps)                                                                         | 93       |

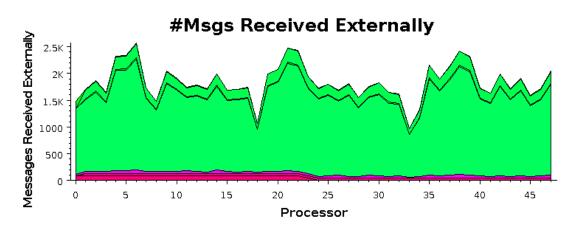

| Figure 6.5:                 | Messages received per PU after load balancing with NUCOLB (re-<br>maining 40 timesteps).                                                                                                           | 94  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

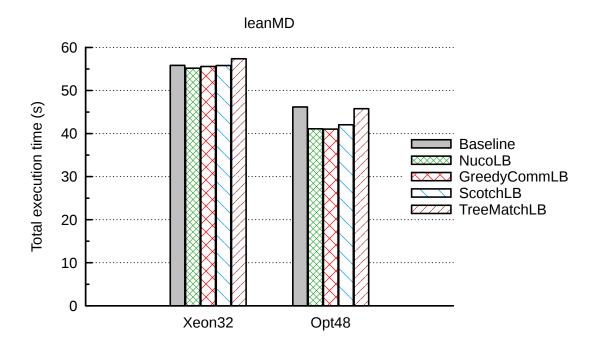

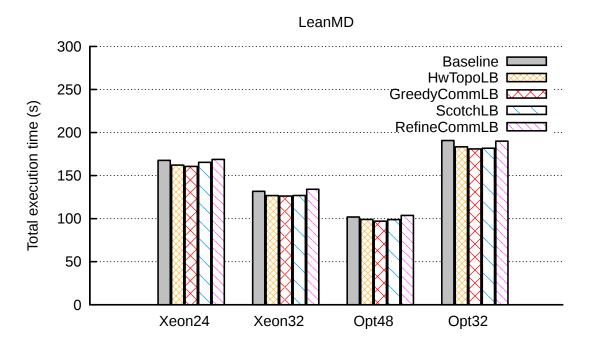

| Figure 6.6:                 | Total execution time of <i>LeanMD</i> with NUCOLB and other load balancers.                                                                                                                        | 94  |

| Figure 6.7:                 | Total execution time of <i>kNeighbor</i> with HwTOPOLB and other load balancers.                                                                                                                   | 95  |

| Figure 6.8:                 | Total execution time of <i>stencil4D</i> with HwTOPOLB and other load balancers.                                                                                                                   | 96  |

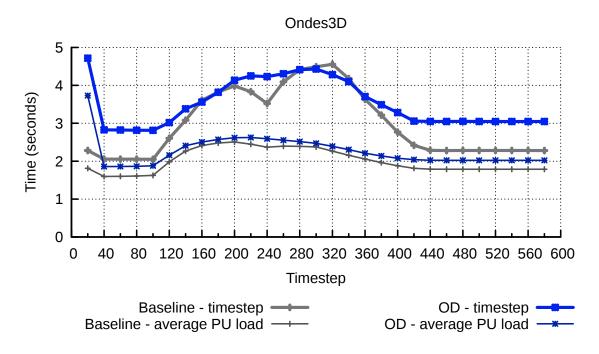

| Figure 6.9:<br>Figure 6.10: | Total execution time of <i>LeanMD</i> with different load balancers Average timestep and average PU load for <i>Ondes3D</i> on Xeon32. Val-                                                        | 98  |

| -                           | ues averaged at each 20 timesteps                                                                                                                                                                  | 99  |

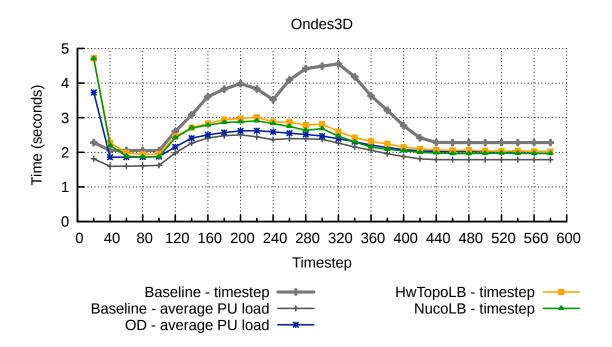

| Figure 6.11:                | Average timestep duration for <i>Ondes3D</i> on Xeon32 with HWTOPOLB and NUCOLB. Values averaged at each 20 timesteps.                                                                             | 100 |

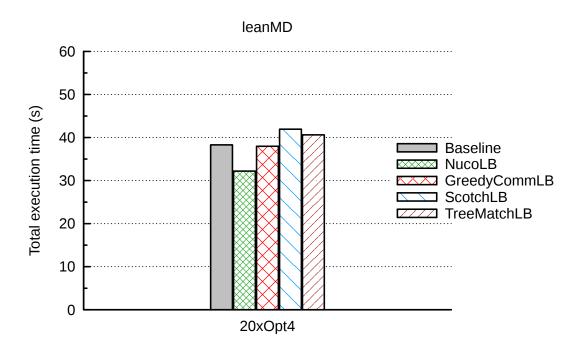

| Figure 6.12:                | Total execution time of <i>LeanMD</i> on 20xOpt4                                                                                                                                                   | 101 |

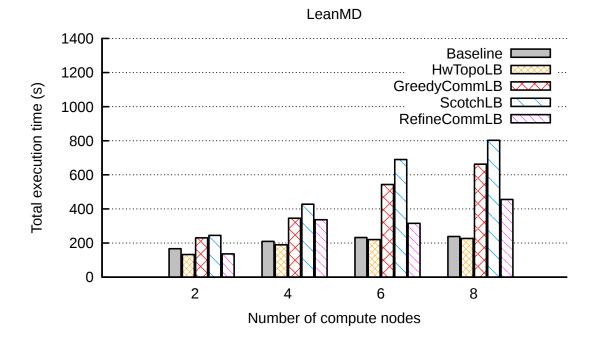

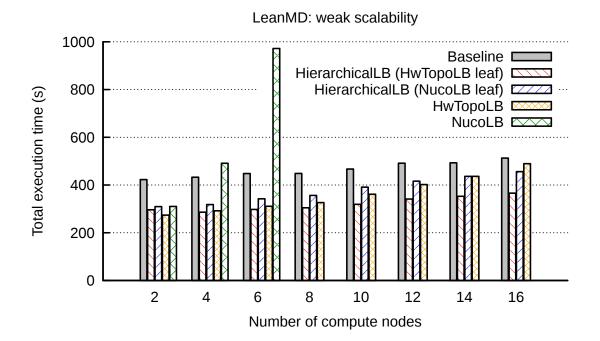

| Figure 6.13:                | Total execution time of <i>LeanMD</i> with HwTOPOLB and other load balancers on a varying number of Opt32 compute nodes. The prob-                                                                 |     |

| Figure 6.14:                | lem size is increased with the number of compute nodes Total execution time of <i>LeanMD</i> with different load balancers on up to 16 Opt32 CNs. The problem size is increased with the number of |     |

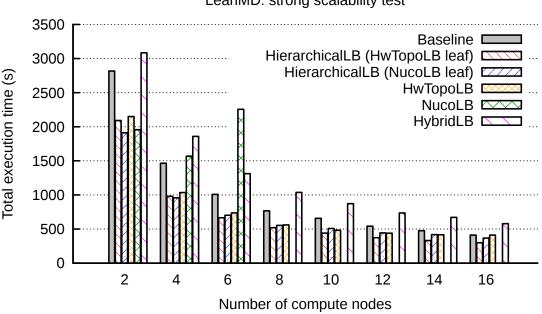

| Figure 6.15:                | compute nodes                                                                                                                                                                                      | 105 |

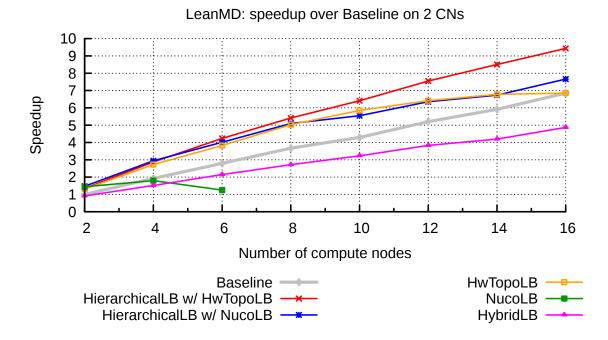

| Figure 6.16:                | compute nodes                                                                                                                                                                                      | 107 |

| 8                           | baseline on 2 compute nodes.                                                                                                                                                                       | 107 |

# LIST OF TABLES

| Table 2.1:  | Characterization of the example platforms in regards to machine topology symmetry and uniformity.                                 | 28  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2:  | Characterization of the example applications in regards to application dynamicity and irregularity.                               | 32  |

| Table 2.3:  | Characterization of the example applications in regards to sources of load imbalance and costly communications.                   | 33  |

| Table 3.1:  | Memory latency (ns) as measured by lat_mem_rd on different ma-<br>chines                                                          | 47  |

| Table 3.2:  | Comparison of the different representations of communication dis-<br>tance from NUMA node 0 on Xeon192                            | 50  |

| Table 5.1:  | Task mapping algorithms comparison in terms of application modeling.                                                              | 80  |

| Table 5.2:  | Task mapping algorithms comparison in terms of machine topologymodeling.                                                          | 82  |

| Table 5.3:  | Task mapping algorithms comparison in terms of techniques em-<br>ployed and objectives.                                           | 84  |

| Table 6.1:  | Overview of the platforms' hardware characteristics.                                                                              | 86  |

| Table 6.2:  | Overview of the platforms' software components                                                                                    | 86  |

| Table 6.3:  | Benchmarks and application characteristics.                                                                                       | 87  |

| Table 6.4:  | Load balancers comparison in terms of machine topology modeling.                                                                  | 88  |

| Table 6.5:  | Load balancers comparison in terms of application modeling and techniques employed.                                               | 89  |

| Table 6.6:  | Total execution time in seconds of <i>lb_test</i> and speedups for NUCOLB and other load balancers.                               | 91  |

| Table 6.7:  | Load balancing times in seconds for <i>stencil4D</i> for different NUMA machines.                                                 | 93  |

| Table 6.8:  | Average number of LLC misses (in millions) for <i>stencil4D</i> with HWTOPOLB and other load balancers on Opt32.                  | 97  |

| Table 6.9:  | Total execution time in seconds of <i>Ondes3D</i> and speedups for NUCOLB, HWTOPOLB and other load balancers.                     | 99  |

| Table 6.10: | Average timestep duration and load balancing time (ms) for <i>LeanMD</i> with NUCOLB and other load balancers on 20xOpt4          | 102 |

| Table 6.11: | Average timestep duration of <i>LeanMD</i> with HwTOPOLB and other load balancing algorithms on a varying number of Opt32 compute |     |

|             | nodes                                                                                                                             | 104 |

| Table 6.12: | Average load balancing time of HwTOPOLB and other load balanc-        |     |  |  |  |  |

|-------------|-----------------------------------------------------------------------|-----|--|--|--|--|

|             | ing algorithms for <i>LeanMD</i> on a varying number of Opt32 compute |     |  |  |  |  |

|             | nodes                                                                 | 104 |  |  |  |  |

### ABSTRACT

This thesis presents our research to provide performance portability and scalability to complex scientific applications running over hierarchical multicore parallel platforms. Performance portability is said to be attained when a low core idleness is achieved while mapping a given application to different platforms, and can be affected by performance problems such as load imbalance and costly communications, and overheads coming from the task mapping algorithm. Load imbalance is a result of irregular and dynamic load behaviors, where the amount of work to be processed varies depending on the task and the step of the simulation. Meanwhile, costly communications are caused by a task distribution that does not take into account the different communication times present in a hierarchical platform. This includes nonuniform and asymmetric communication costs at memory and network levels. Lastly, task mapping overheads come from the execution time of the task mapping algorithm trying to mitigate load imbalance and costly communications, and from the migration of tasks.

Our approach to achieve the goal of performance portability is based on the hypothesis that precise machine topology information can help task mapping algorithms in their decisions. In this context, we proposed a generic machine topology model of parallel platforms composed of one or more multicore compute nodes. It includes profiled latencies and bandwidths at memory and network levels, and highlights asymmetries and nonuniformity at both levels. This information is employed by our three proposed topology-aware load balancing algorithms, named NUCOLB, HWTOPOLB, and HIER-ARCHICALLB. Besides topology information, these algorithms also employ application information gathered during runtime. NUCOLB focuses on the nonuniform aspects of parallel platforms, while HWTOPOLB considers the whole hierarchy in its decisions, and HIERARCHICALLB combines these algorithms hierarchically to reduce its task mapping overhead. These algorithms seek to mitigate load imbalance and costly communications while averting task migration overheads.

Experimental results with the proposed load balancers over different platform composed of one or more multicore compute nodes showed performance improvements over state of the art load balancing algorithms: NUCOLB presented improvements of up to 19% on one compute node; HwTOPOLB experienced performance improvements of 19% on average; and HIERARCHICALLB outperformed HwTOPOLB by 22% on average on parallel platforms with ten or more compute nodes. These results were achieved by equalizing work among the available resources, reducing the communication costs experienced by applications, and by keeping load balancing overheads low. In this sense, our load balancing algorithms provide performance portability to scientific applications while being independent from application and system architecture.

Keywords: Computer architecture, Parallel programming, Profiling, Scheduling.

#### Balanceamento de Carga Ciente da Topologia de Máquina para a Portabilidade de Desempenho em Plataformas de Alto Desempenho Paralelas

### RESUMO

Esta tese apresenta nossa pesquisa para prover portabilidade de desempenho e escalabilidade para aplicações científicas complexas executadas em plataformas multicore paralelas e hierárquicas. A portabilidade de desempenho é dita como alcançada quando uma pequena ociosidade nas unidades de processamento é obtida para o mapeamento de uma aplicação em diferentes plataformas. A portabilidade de desempenho pode ser afetada por problemas como o desbalanceamento de carga, comunicações custosas e sobrecustos vindos do algoritmo de mapeamento de tarefas. O desbalanceamento de carga é um resultado de comportamentos de cargas de tarefas irregulares e dinâmicas, onde a quantidade de trabalho a ser processado varia dependendo da tarefa e da etapa da simulação. Enquanto isso, comunicações custosas são causadas por uma distribuição de tarefas que não leva em conta os diferentes tempos de comunicações presentes em uma plataforma hierárquica. Isto inclui custos de comunicações não uniformes e assimétricos em níveis de memória e rede. Por fim, os sobrecustos de mapeamento de tarefas vêm do tempo de execução do algoritmo de mapeamento de tarefas tentando mitigar o desbalanceamento de carga e comunicações custosas, além do tempo ligado à migração de tarefas.

Nossa abordagem para atingir o objetivo de portabilidade de desempenho é baseada na hipótese de que informações precisas da topologia de máquina podem auxiliar algoritmos de mapeamento em suas decisões. Neste contexto, nós propomos um modelo de topologia de máquina genérico para plataformas paralelas compostas de um ou mais nós de processamento multicore. Ele inclui latências e larguras de banda perfiladas nos níveis de memória e rede, além de salientar assimetrias e não uniformidade em ambos níveis. Estas informações são empregadas pelos nossos três algoritmos de balanceamento de carga cientes da topologia de máquina propostos, chamados NUCOLB, HWTOPOLB e HIE-RARCHICALLB. Além das informações da topologia, estes algoritmos também utilizam informações da aplicação capturadas durante o tempo de execução. NUCOLB foca nos aspectos não uniformes de plataformas paralelas, enquanto HWTOPOLB considera toda a hierarquia da máquina em suas decisões. HIERARCHICALLB combina estes algoritmos buscam mitigar o desbalanceamento de carga e comunicações custosas enquanto evitam sobrecustos de migração de tarefas.

Resultados experimentais com os balanceadores de carga propostos em diferentes plataformas compostas de um ou mais nós de processamento multicore apresentaram desempenhos superiores a outros algoritmos de balanceamento de carga do estado da arte: NUCOLB apresentou melhorias de até 19% em média; HWTOPOLB demonstrou melhorias de desempenho de 19% em média; e HIERARCHICALLB superou HWTOPOLB em 22% em média em plataformas paralelas com dez ou mais nós de processamento. Estes resultados foram obtidos através da equalização da carga de trabalho entre os recursos disponíveis, redução dos custos de comunicação sentidos pelas aplicações e manutenção de sobrecustos de balanceamento de carga pequenos. Dessa forma, nossos algoritmos de balanceamento de carga proveem portabilidade de desempenho para aplicações científicas enquanto se mantendo independentes de uma aplicação ou arquitetura de sistema específica.

**Palavras-chave:** Arquitetura de computadores, Programação Paralela, Perfilamento, Escalonamento.

## **1 INTRODUCTION**

For years now, science has advanced thanks to the insights brought by numerical simulations. These scientific applications are used to reproduce and predict complex phenomena, with scales varying from the way a protein behaves to the effects caused by an earthquake. These applications have ever increasing demands in performance and resources. For instance, the higher the resolution of a weather forecasting model, the more precise and accurate would be its predictions, as local phenomena would be better represented in the system. In order to take profit from the multiple resources available in high performance computing (HPC) platforms, scientific applications are developed using parallel languages and runtimes.

Parallel applications are decomposed into smaller parts, which can be implemented as processes, threads, objects, etc. We refer to them as tasks. Each task participates in the simulation by processing a part of the total workload. Before starting an application, it may not be possible to predict the amount of work, or load, each task will receive or produce. Load irregularity may come from tasks playing different roles in the application, or simulating different aspects or materials in the system. The load of a task can also change dynamically through time, as it achieves a different state in the simulation, or receives feedback from other tasks. When tasks are distributed over a parallel platform without taking such behaviors into account, load imbalance occurs.

In addition to the effects that tasks' loads have over the execution of a scientific application, there is also the affinity of tasks that affect it. A task's affinity group refers to the other tasks that it shares data or communicates with. It is in the best of interests to have communicating tasks mapped in the parallel platform in a way that reduces their communication times. However, communication times are not only affected by the communication behavior of a task, which can be irregular and dynamic as can happen to its load, but also by the organization of the HPC platform where the application is executing.

Typical HPC platforms are composed of multiple processing units, varying in scale from a multicore machine to a cluster composed of many multicore compute nodes. Their topologies include different cache, memory, and network levels organized hierarchically. As a consequence, the communication time between a pair of processing units or compute nodes will also depend on their distance in the whole topology.

Besides the effects caused by a hierarchical organization, communication times may not be uniform in some of the topology levels. At an interconnection network level, this happens because having a direct and dedicated interconnection between every pair of compute nodes is unfeasible in scale. Meanwhile, in order to mitigate the effects of the "memory wall problem" (WULF; MCKEE, 1995), not only is memory organized in a hierarchical fashion, but the main memory is also being assembled from different memory banks in a nonuniform memory access (NUMA) design. Besides nonuniformity, symmetry may not be held, as the communication time between two components can depend on which direction it is happening, and the routing algorithms involved. If not taken into account when mapping tasks to the available resources, these characteristics of HPC platforms (namely nonuniform and asymmetric communication times, and hierarchical organization), together with an application's irregular and dynamic communication behaviors, can result in costly communications to said application.

Mitigating costly communications and balancing load are two different ways to improve application performance. Nevertheless, they can be orthogonal: an optimal task distribution for balancing load can negatively affect performance by increasing communication costs, as can the opposite happen. In this context, an equilibrium has to be found when focusing in both objectives for performance.

#### **1.1 Problem statement**

A challenge lies on managing the execution of a scientific application in order to explore the resources of a parallel platform to their fullest and, consequently, achieve high performance and scalability. This requires identifying characteristics of the application and platform, and managing which processing and communication resources get to be shared among tasks based on their loads and affinity. This problem is also aggravated by the fact that platforms and applications evolve independently from one another.

Finding the best task distribution to balance load and/or communication costs is a NP-Hard problem (LEUNG, 2004), thus requiring impracticable amounts of time for any application or platform of interest. To mitigate this problem, heuristics are employed to schedule tasks in feasible time. Although different algorithms exist, they may not provide performance portability.

A task mapping algorithm is said to attain performance portability when it is able to map a given application to different platforms and still achieve high efficiencies, which comes from a low core idleness. Although an algorithm can be tuned to a specific application and platform, this sacrifices portability in the process, as extensive work has to be done to provide scalable performance when running the same application in another platform, or another application in the same platform.

Performance portability also requires the task mapping algorithm to be performant, as its execution time will influence the application's performance. In this sense, a challenge lies in displaying performance portability with task mapping algorithms, as one needs to equilibrate balancing load, reducing communication costs, and keeping the algorithm's execution time small.

#### **1.2** Objectives and thesis contributions

The main objective of our research is to provide performance portability and scalability to complex scientific applications running over hierarchical multicore parallel platforms. We follow the hypothesis that precise machine topology information can help load balancing algorithms in their decisions. Considering this objective and hypothesis, our contributions are the following:

• We develop a generic machine topology model of parallel platforms composed of one or more multicore compute nodes. It includes profiled information at memory and network levels. This model is used to provide detailed information to task

mapping algorithms. Our model is able to automatically measure, store, and make available the machine topology at a user level. It is also kept generic by using tools and benchmarks independent of application and system architecture.

- We propose load balancing algorithms that work at runtime level, which keeps them independent of a specific platform or application. They combine application information gathered during execution to our proposed machine topology model that considers real communication costs over the platform. They improve the distribution of tasks over a parallel platform in order to mitigate load imbalance and costly communications. They are able to handle applications with irregular and dynamic behaviors, and machine topologies with nonuniform and asymmetric communications costs (PILLA et al., 2012, 2014).

- We experimentally evaluate our approach with real benchmarks and applications over multiple parallel platforms. We implement our load balancing algorithms with a parallel language and compare their performance to other state of the art algorithms.

#### **1.3 Research context**

This research is conducted under the context of a joint doctorate between the *Institute* of *Informatics* of the Federal University of Rio Grande do Sul (UFRGS); and the *Mathematics, Information Sciences and Technologies, and Computer Science* (MSTII) Doctoral School, part of the University of Grenoble (UdG). This cooperation is held within the *International Laboratory in High Performance and Ambient Informatics* (LICIA).

At UFRGS, research is developed in the *Parallel and Distributed Processing Group* (GPPD). This research group possesses a vast experience with task mapping algorithms and scientific applications, which include load balancing algorithms for Bulk Synchronous Parallel applications (RIGHI et al., 2010) and weather forecasting models (RO-DRIGUES et al., 2010).

At UdG, this research is conducted in the *Nanosimulations and Embedded Applications for Hybrid Multi-core Architectures* (Nanosim) team, which is part of the *Grenoble Informatics Laboratory* (LIG). This team counts with an extensive background in multicore architecture modeling and memory management (RIBEIRO, 2011; CASTRO, 2012).

This research also profits from a collaboration with the *Parallel Programming Laboratory* (PPL) of the University of Illinois at Urbana-Champaign through the *Joint Laboratory for Petascale Computing* (JLPC). They are the developers of a parallel language and runtime system named CHARM++, which was used as a test bed for the implementation of our proposed load balancing algorithms.

#### **1.4 Document organization**

The remaining chapters of this thesis are organized as follows:

- A review of the main characteristics of parallel platforms and applications is presented in Chapter 2. It also discusses the basics of task mapping algorithms and machine topology probing.

- Our machine topology model is presented in Chapter 3. Its rationals, advantages,

and limitations are explored in this chapter. An evaluation of the parameters measured in the topology is also detailed.

- Two centralized load balancing algorithms are proposed in Chapter 4. They are: NUCOLB, a load balancer that focuses on the nonuniform aspects of parallel platforms; and HWTOPOLB, a load balancer that considers the whole machine topology hierarchy in its decisions. This chapter also presents HIERARCHICALLB, a hierarchical topology-aware load balancer based on the composition of centralized algorithms.

- The experiments conducted to evaluate our load balancers are shown in Chapter 6. This chapter includes information about the parallel platforms, benchmarks, applications, and other load balancers used to measure the performance and scalability of our algorithms.

- Concluding remarks and research perspectives are discussed in Chapter 7.

## 2 BACKGROUND

The performance of scientific applications can be affected by many different variables related to attributes intrinsic to the application itself and to the platform. For instance, at platform level, the communication time between two tasks will depend on the time that it takes for data to travel from one core to another through the machine topology. Mean-while, when focusing in the application, the execution time of a task at a certain timestep will depend on the phenomena being simulated and the input data. These problems are accentuated as applications become more complex, and parallel platforms are designed with more hierarchical characteristics. In this context, task mapping algorithms are employed to reduce the impact of such attributes. They ease the process of distributing work over a parallel machine.

A task mapping algorithm provides performance portability by achieving a low core idleness when mapping an application to different platforms. This not only demands the algorithm to handle load imbalance and communication performance problems, but also to be performant by keeping its time overhead to a minimum. For an algorithm to decide which of these problems is the most relevant in a given situation, knowledge about the parallel platform and application of interest is required.

In this chapter, we discuss the core concepts of parallel platforms and applications, as well as their characteristics that affect performance. First, we introduce the features of parallel system architectures, how they are assembled, and how they can influence the communication time of applications. After that, we describe how parallel applications are composed, and exemplify how they behave using three different scientific applications. The performance challenges faced by task mapping algorithms and their basic concepts are explained next. We follow with a presentation of tools to control and probe the machine characteristics, which serve to provide detailed information to task mapping algorithms. We conclude this chapter with a discussion on the aforementioned topics.

#### 2.1 Components of high performance computing platforms

High performance computing (HPC) platforms are parallel machines designed to run applications with high demands of computing power and other resources. The main approach to increase their computing power is to increase their parallelism. The amount of processing units per chip has been growing in the last decade, as has been the number of compute nodes used to compose a parallel system. For instance, the most performing parallel platform in the world as evaluated by the TOP500 list in November 2013 (DONGARRA; MEUER; STROHMAIER, 2013), known as Tianhe-2, is composed of 16,000 compute nodes, and includes a total of 3, 120,000 processing units. Such platform design leads to highly hierarchical architectures, with complex memory subsys-

tems and network topologies. This makes achieving scalable performance with different applications a challenge.

#### 2.1.1 Composition

When considering a bottom-up approach, the basic component of this system architecture is the **processing unit** (**PU**). A processing unit is the place where a task is executed. In this scenario, one core in a simple multicore processor would represent one PU, while a simultaneous multithreading (SMT) core would have two or more PUs. This is the same definition used by HWLOC (BROQUEDIS et al., 2010; HWLOC, 2013), as will be discussed later in Section 2.4.1.

When one or more PUs are grouped in a single shared memory space, we have a **compute node** (**CN**). Besides PUs and main memory, a compute node includes many levels of cache memory to accelerate memory access. These components are hierarchically organized, as illustrated in Figure 2.1. It shows the machine topology of one compute node composed of 24 PUs (6 PUs per socket). In this example, the memory hierarchy is organized as follows: each PU has its own L1 cache; pairs of PUs share a L2 cache; L3 cache is shared among all PUs inside the same socket; and the main memory is shared among all PUs.

| Compute Node |                          |                    |                    |                    |  |

|--------------|--------------------------|--------------------|--------------------|--------------------|--|

| Memory       |                          |                    |                    |                    |  |

| Socke        |                          |                    | Socket             |                    |  |

| L3           |                          |                    | L3                 |                    |  |

| L2 L2        | L2                       | L2                 | L2                 | L2                 |  |

|              | 1 L1 L1                  | L1 L1              | L1 L1              | L1 L1              |  |

|              | vre Core Core<br>U PU PU | Core Core<br>PU PU | Core Core<br>PU PU | Core Core<br>PU PU |  |

| Socke        |                          |                    | Socket             |                    |  |

| L3           |                          |                    | L3                 |                    |  |

| L2 L2        | L2                       | L2                 | L2                 | L2                 |  |

|              | 1 L1 L1                  | L1 L1              | L1 L1              | L1 L1              |  |

|              | vre Core Core<br>U PU PU | Core Core<br>PU PU | Core Core<br>PU PU | Core Core<br>PU PU |  |

Figure 2.1: Example of machine topology of a UMA machine with 24 PUs distributed in 4 sockets.

Inside a compute node, tasks are considered to communicate through shared memory. It is also considered that they are able to benefit from the memory hierarchy when communicating. Data sent from one task to another is regarded as stored in the first level of the topology that is shared among the involved PUs. If the involved PUs do not share any cache level, then data can be found in the main memory. In the case of a uniform memory access (UMA) machine, all tasks accessing the main memory will take similar times. This happens because all use the same interface (for instance, a bus) to read data, as illustrated in Figure 2.2. However, the same does not happen with nonuniform memory access (NUMA) architectures.

NUMA architectures are a current trend in the design of parallel compute nodes. As the number of PUs inside a CN increases, so does increase the stress to the shared memory controller hub in a UMA CN. Meanwhile, on NUMA architectures, the main memory

Figure 2.2: Example of communication through memory on a UMA machine.

is partitioned in multiple memory banks that are physically distributed, but the memory space is still shared among all PUs in the same compute node. This design has the advantage of spreading the memory accesses over these different banks. Each group of PUs sharing one memory bank is called a **NUMA node**. Figure 2.3 shows a compute node similar to the one seen in Figure 2.1, but partitioned into 4 NUMA nodes.

| Compute Node                    |                    |            |            |            |            |            |            |

|---------------------------------|--------------------|------------|------------|------------|------------|------------|------------|

| NUMA Node                       |                    |            | NUMA Node  |            |            |            |            |

| Memory                          |                    |            | Memory     |            |            |            |            |

| Socket                          |                    |            | Socket     |            |            |            |            |

| L3                              |                    |            |            | L3         |            |            |            |

| L2 L2                           | L2                 |            | L2         | L2         |            |            | 2          |

| L1 L1 L1 L1                     | L1 L1              | L1         | L1         | L1         | L1         | L1         | L1         |

| Core Core Core Core PU PU PU PU | Core Core<br>PU PU | Core<br>PU | Core<br>PU | Core<br>PU | Core<br>PU | Core<br>PU | Core<br>PU |

| NUMA Node                       | NUMA Node          |            |            |            |            |            |            |

| Momory                          |                    |            |            | Mom        | orv        |            |            |

| Memory                          |                    |            |            | Mem        |            |            |            |

| Socket                          |                    |            |            | Sock       | ket        |            |            |

| Socket<br>L3                    |                    |            |            | Sock<br>L3 | (et        |            |            |

| Socket                          |                    |            | L2         | Sock       | (et        |            | 2          |

| Socket<br>L3                    | L2<br>L1 L1        |            | L2         | Sock<br>L3 | (et        |            | 2<br>L1    |

Figure 2.3: Example of a machine topology of a NUMA machine with 24 PUs distributed in 4 NUMA nodes.

When tasks residing in PUs from different NUMA nodes communicate, data is usually considered to be stored in the sender's memory bank due to a *first-touch* memory policy, as it stores data in the NUMA node of the first thread to access it (LOF; HOLMGREN, 2005). In this scenario, the receiver will have to make a remote memory access to read data. This is depicted in Figure 2.4. The arrow represents the path that data travels to get from sender to receiver. One of the main characteristics of NUMA machines is that accessing data in a remote memory bank takes longer than accessing it in local memory.

Besides the memory hierarchy of a compute node, a network hierarchy is present when clustering more than one CN. When using the same representation illustrated in Figures 2.1 and 2.3, an additional level is added to the machine topology to include the network interconnection. This is depicted in Figure 2.5. Tasks communicating in this platform use the same mechanisms discussed before if both tasks happen to be in the

Figure 2.4: Example of communication through memory on a NUMA machine.

same CN. If that is not the case, then data will be sent to the receiver's CN. This communication organization is displayed in Figure 2.6. The time that it takes for two tasks to communicate through network is usually considered to be greater than the time it takes for them to communicate through memory.

Figure 2.5: Example of a machine topology with multiple compute nodes. 4 UMA compute nodes are illustrated.

The communication time between two PUs is strongly influenced by the machine topology level where it happens. The closer the topology level is to the PUs, the smaller this time is. In this sense, communication at a cache level is faster than at a memory or network level. Still, other factors can influence communication performance. For instance, contention happens when there is conflict for a shared resource (e.g., a network link), which decreases the performance of tasks using it. Besides that, differences inside a topology level can affect performance, as discussed next.

Figure 2.6: Example of communication through network organized as a fat tree.

#### 2.1.2 Asymmetry and nonuniformity at topology levels

When studying the communication time among PUs in the machine topology, two important properties emerge: symmetry and uniformity. They are explained below:

- Symmetry: a level in the machine topology is said to be symmetric if the communication time of a first task sending data to a second one is the same than the communication time of the second task sending data to the first one. When this does not happen, a topology level is said to be **asymmetric**.

- Uniformity: a level in the machine topology is said to be uniform if all tasks communicating through that level have the same communication time. When this does not happen, a topology level is said to be **nonuniform**.

For a more formal definition, a machine topology can be denoted as a quadruple  $\mathcal{O} = (\mathcal{P}, \mathcal{L}, S, C)$ , with  $\mathcal{P}$  the set of PUs,  $\mathcal{L}$  the set of levels of the topology, the first topology level shared by two PUs as a function  $S : \mathcal{P} \times \mathcal{P} \to \mathcal{L}$ , and the communication time of one PU to another as a function  $C : \mathcal{P} \times \mathcal{P} \to \mathbb{R}_{>0}$ . S is symmetric and transitive. A topology level  $l \in \mathcal{L}$  is considered to be symmetric if

$$\forall a, b \in \mathcal{P} \land S(a, b) = l \Rightarrow C(a, b) = C(b, a).$$

(2.1)

Additionally, a topology is said to be symmetric if Equation 2.1 holds for all  $l \in \mathcal{L}$ . A topology level  $l \in \mathcal{L}$  is considered to be uniform if

$$\forall a, b, c \in \mathcal{P} \land S(a, b) = S(a, c) \Rightarrow C(a, b) = C(a, c).$$

(2.2)

Likewise, a topology is said to be uniform if Equation 2.2 holds for all  $l \in \mathcal{L}$ . It is important to notice that a topology level cannot be asymmetric and uniform at the same time due to S being a symmetric function. All other combinations are valid.

Table 2.1 relates symmetry and uniformity to the machine topologies illustrated in Figures 2.1, 2.3, and 2.5. Other combinations can happen in real platforms, such as a cluster of NUMA CNs. Cache levels are usually, but not exclusively, symmetric and uniform.

| Platform          | Cache levels | Memory level | Network level |

|-------------------|--------------|--------------|---------------|

| UMA CN            | Symmetric    | Symmetric    |               |

|                   | Uniform      | Uniform      |               |

| NUMA CN           | Symmetric    | Asymmetric   |               |

| NUMA CIN          | Uniform      | Nonuniform   |               |

| Clustered UMA CNs | Symmetric    | Symmetric    | Symmetric     |

|                   | Uniform      | Uniform      | Nonuniform    |

Table 2.1: Characterization of the example platforms in regards to machine topology symmetry and uniformity.

Nonuniformity can be seen in non-uniform cache access (NUCA) architectures (KIM; BURGER; KECKLER, 2002). The **memory level** is uniform for UMA compute nodes, and nonuniform for NUMA CNs. NUMA compute nodes may also present asymmetry (RIBEIRO, 2011). The **network level** strongly depends on the network topology. In Figure 2.6, all compute nodes are interconnected through a tree of switchs. This results in a symmetric but nonuniform network level. Asymmetry may come in the network level as a result of routing (HOEFLER; SCHNEIDER, 2012).

The hierarchical design of a system architecture, combined with asymmetric and nonuniform topology levels, impacts the communication time of an application. If the different communication times between pairs of processing units are not taken into account, then communication can hinder application performance. Still, the machine topology is not the only factor affecting the total execution time of a parallel application, as characteristics of the application itself play a role too. These characteristics are discussed in the next section.

### 2.2 Characterization of scientific applications

Scientific applications are used to simulate phenomena through time at different scales (e.g., from the way molecules interact in nanoseconds, to the climate in years). Simulations involve large datasets and/or much processing. These parallel applications have their work and data split into **tasks** which populate the resources available in parallel platforms. The actual implementation of these tasks depends on the programming language. For instance, tasks may be implemented as threads in OPENMP (DAGUM; MENON, 2002), processes in MPI (GROPP; LUSK; SKJELLUM, 1999), and active objects in CHARM++ (KALE; KRISHNAN, 1993). The number of tasks in an application can be much larger than the number of PUs available in the parallel platform.

#### 2.2.1 Tasks: load and communication

Each task has an amount of processing to do. This is going to be referred as **load** in this thesis. A task's load is measured as the time it takes running on a processing unit in a machine. The bigger the load, the longer the execution time. Although load could be decomposed into two parameters, amount of work of a task and PU performance, we keep it as single entity for simplicity. All platforms considered in this research are homogeneous, which means that their processing units have the same performance. This is the same approach seen in related works (CHEN et al., 2006; HOFMEYR et al., 2011; JEANNOT;

MERCIER, 2010; LIFFLANDER; KRISHNAMOORTHY; KALE, 2012; TCHIBOUKD-JIAN et al., 2010; OLIVIER et al., 2011). This is discussed in more details in Chapter 5.

As tasks compute, the simulation iteratively evolves, and tasks start to communicate. Even though simulations commonly evolve in timesteps, they are not required to follow a Bulk Synchronous Parallel (BSP) (VALIANT, 1990) approach.

Task communication may happen through memory or network, depending on where the involved tasks are mapped, as previously discussed in Section 2.1. For the sake of simplicity, we are going to refer to data exchanges as **messages**. All messages sent and received during the execution of an application (or a part of it) can be seen as its **communication graph**, where vertices represent tasks and edges represent communication. Communication is measured by the number of messages sent from a task to another and the amount of bytes communicated. The time that it takes for a task to receive a message depends on both factors, and is also strongly affected by the distance between the processing units where tasks are mapped.

Considering these characteristics, an instance of an application execution (or part of it) can be defined as a quintuple  $\mathcal{A} = (\mathcal{T}, Load, Size, Msgs, Bytes)$ , with  $\mathcal{T}$  the set of tasks, their loads as a function  $Load : \mathcal{T} \to \mathbb{R}_{>0}$ , their sizes in bytes as a function  $Size : \mathcal{T} \to \mathbb{R}_{>0}$ , the number of messages sent from one task to another as a function  $Msgs : \mathcal{T} \times \mathcal{T} \to \mathbb{N}$ , and the number of bytes sent from one task to another as a function  $Bytes : \mathcal{T} \times \mathcal{T} \to \mathbb{N}$ . This organization is used to explain how application behavior interacts with its performance.

#### 2.2.2 Application irregularity and dynamicity

The way an application and its tasks behave can affect performance in different ways, e.g., tasks may have different loads; their loads may change through time; and communication may follow different patterns in different phases of the application. In the context of this thesis, we focus on two task characteristics: (i) how their load behaves; and (ii) how their communication behaves. This does not take into account other characteristics that may influence the final performance of an application, such as the way tasks interact with the file system. Communication and load vary from one application to another in two axes: **regularity** and **dynamicity**. They are explained in more details below:

- **Regularity** refers to how the load or communication of a task differs from another task. An application with **regular load** has tasks that compute for approximately the same time. When this is not the case, an application is said to have **irregular load**. **Regular communication** is present in applications with well-defined communication graphs, where the number of messages and amount of bytes exchanged is the same among different tasks. Meanwhile, an application with **irregular communication** has a complex communication graph, or the amount of bytes or messages communicated varies between pairs of tasks.

- **Dynamicity** refers to how the load or communication of a task varies through time. An application with **dynamic load** has tasks that compute for different amounts of time at different timesteps. If loads are constant through time, an application is said to have **static load**. An application with **static communication** has a communication graph that does not change. If that is not the case for an application, it is said to exhibit **dynamic communication**.

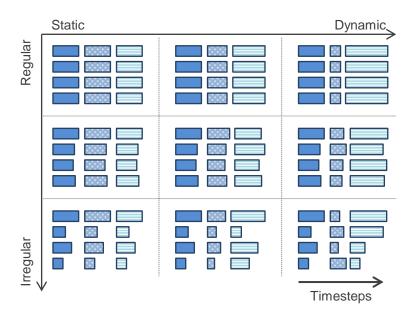

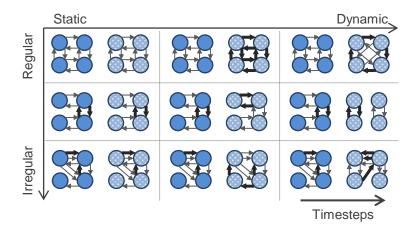

Figures 2.7 and 2.8 illustrate how regularity and dynamicity affect the load and communication graph of an application, respectively. The vertical axis represents changes in regularity, while the horizontal axis represents a variation in dynamicity through timesteps. The horizontal bars in Figure 2.7 represent the load of four different tasks during three timesteps. The circles in Figure 2.8 represent four tasks in two different timesteps, while the arrows represent messages, and their thickness imply the volume of data exchanged. As these figures illustrate, regularity and dynamicity are not absolute characteristics, as they vary in levels.

Figure 2.7: Different levels of load irregularity and dynamicity.

Figure 2.8: Different levels of communication irregularity and dynamicity.

Irregularity and dynamicity affect application performance at both load and communication sides. If the total load of tasks mapped to one PU is greater than in others, then PUs will be idle while waiting for the slowest (most loaded) PU. This scenario can easily happen in an application with a large load irregularity. Additionally, load dynamicity can generate this scenario during execution time, making it hard to predict and avoid. Meanwhile, communication time will reduce if tasks that communicate more than others are mapped closer in the machine topology, and it will suffer if the opposite happens. Communication dynamicity can change which tasks have their performance affected by the communication time. All these characteristics can be present in different levels in a scientific application. We exemplify this next.

#### 2.2.3 Examples of scientific applications

To better understand how dynamicity and irregularity present themselves in real scenarios, we analyze three scientific applications from different areas: seismology, weather forecasting, and molecular dynamics.

Seismic wave propagation models are mainly employed to estimate the damage in future earthquake scenarios. Simulations are applied in a regional scale, where the domain is divided into a three-dimensional grid. Each sub-domain can be seen as a task. In addition to the simulated region, the domain also includes artificial borders used to process and absorb the outgoing energy of the seismic waves. In these models, task communication is regular and static, as tasks only communicate with their neighbors. Their load is mostly static, but wave propagation can spread dynamism in nonlinear simulations (DUPROS et al., 2010). These applications can also present load irregularity. This happens because the physical domain simulation has a different load than the artificial absorbing borders; and because different geological layers may have different constitutive laws, which results in different computational costs (DUPROS et al., 2008, 2010; TESSER et al., 2014).

Weather forecasting models are used to predict the state of the atmosphere at given place and time. This prediction can vary from tomorrow's weather to how the climate is going to be in the following years. Models such as the Regional Atmospheric Modeling System (RAMS) (WALKO et al., 2000), and its Brazilian variant, BRAMS (BRAMS, 2013), split part of the globe and the atmosphere in a three-dimensional mesh. Each of these parts can be seen as a task. Their communication follows a regular and static behavior as seismology models do. Weather forecasting models can present load irregularity, as tasks may have different workloads depending on input data. Load dynamicity can also happen due to phenomena moving through the simulated area (e.g., thunderstorms) (RO-DRIGUES et al., 2010)(XUE; DROEGEMEIER; WEBER, 2007). This dynamism happens in a scale smaller than the one seen in seismic wave propagation.

**Molecular dynamics** simulations are employed to study the dynamics and properties of biomolecular systems. Typical experiments with applications such as Nanoscale Molecular Dynamics (NAMD) (NELSON et al., 1996) simulate the behavior of the molecular system for hundreds of nanoseconds. This takes millions of femtoseconds steps to simulate (BHATELE et al., 2009). NAMD uses a hybrid of spatial and force decomposition methods, where the simulation space is divided into cubical regions called *cells*, and the forces between two cells are the responsibility of *computes*. These two kinds of tasks, cells and computes, bring load irregularity to the application. Load dynamicity happens as simulated atoms can move from one cell to another. Communication is also irregular, as it involves different communication patterns at the same time, such as pair to pair and multicasts.

Table 2.2 summarizes the irregular and dynamic behaviors of the three applications. Although these applications have similarities, as being iterative and involving a threedimensional space, the differences in the simulated phenomena results in various combinations of performance challenges to be handled when executing them in parallel platforms. In the next section, we discuss the potential performance problems that should be considered when mapping tasks to physical resources.

| Application              | Irregularity                                | Dynamicity |

|--------------------------|---------------------------------------------|------------|

| Seismic wave propagation | Load (two kinds of tasks)                   | Load       |

| Weather forecasting      | Load (physical regions)                     | Load       |

| Molecular dynamics       | Load (two kinds of tasks) and communication | Load       |

Table 2.2: Characterization of the example applications in regards to application dynamicity and irregularity.

### 2.3 Task mapping

Task mapping algorithms serve to, as their name says, guide the way tasks are mapped to physical resources (mainly the processing units). More formally, we define a task mapping as a function  $\mathcal{M} : \mathcal{T} \to \mathcal{P}$ , where  $\mathcal{T}$  represents the set of tasks of an application, and  $\mathcal{P}$  is the set of PUs of a platform.

Some variations of task mapping algorithms can be called load balancers, schedulers, process mapping algorithms, and others. They play a central role in achieving performance portability with scientific applications running on parallel HPC platforms, as properties of both can affect application performance. For instance, a naïve task mapping involving an equal number of tasks per PU can perform well with a regular, static application over a symmetric and uniform platform. However, any irregular or dynamic behaviors can result in an increase of core idleness and loss of scalability. We discuss the main performance problems considered in this thesis below.

#### 2.3.1 Load imbalance and costly communications

The aforementioned behaviors can negatively affect performance in two ways: (i) through **load imbalance**; and (ii) through **costly communication**. An application is said to be load imbalanced when its current task mapping presents processing units with significant load differences. The load of a processing unit is considered to be the sum of the load of the tasks mapped to it. These load differences result in processing units being idle while waiting its tasks to synchronize with others. Such idleness affects the parallel efficiency and scalability of an application. Regular applications are the easiest to reduce load imbalance, as an even task distribution results at most in an *off-by-one* imbalance, where the number of tasks on each processing unit is within one of each other. Meanwhile, dynamic applications are harder to keep balanced, as changes in behavior during execution time are more difficult to predict and mitigate.

Load imbalance is mostly independent of the machine topology. However, the opposite happens for costly communications. The time that it takes for two tasks to communicate depends on how many messages are exchanged, the data volume, and where these tasks are mapped. For instance, communication through network is usually considered to take longer than through shared memory. If we consider that the communication time of an application is the sum of the time that all its messages take, then an application is considered to have costly communications if its current communication time is much greater than its optimal communication time. In other words, an application is said to have costly communications if its current task mapping does not benefit from the machine topology. Applications with regular communication are easier to map to the machine topology in a way that reduces communication costs.

| Application                                     | Load imbalance                                               | Costly communication                 |

|-------------------------------------------------|--------------------------------------------------------------|--------------------------------------|

| Seismic wave propagation<br>Weather forecasting | Load irregularity and dynamicity<br>Load irregularity mainly | Bad task mapping<br>Bad task mapping |

| Molecular dynamics                              | Load irregularity and dynamicity                             | Irregular communication              |

Table 2.3: Characterization of the example applications in regards to sources of load imbalance and costly communications.

The impact of load imbalance and costly communications will depend on the application and platform of interest. For instance, considering the three applications discussed in Section 2.2.3, Table 2.3 summarizes possible sources of load imbalance and costly communications. Seismic and weather simulations are less likely to suffer from costly communications, as their communication behavior is strongly static and regular. Still, a task mapping that leaves communicating tasks far from each other could generate a performance problem. Meanwhile, load irregularity and dynamicity pose challenges to a load balanced task distribution for the three applications. All these factors and some more have to be taken into consideration to provide performance portability to parallel applications, as is discussed next.

#### 2.3.2 Performance portability

Performance portability is achieved when an application can be mapped to different platforms and still achieve low core idleness. This requires a task mapping that mitigates the effects of load imbalance and costly communications. Besides these two challenges, the task mapping algorithm itself must not be a liability to performance.

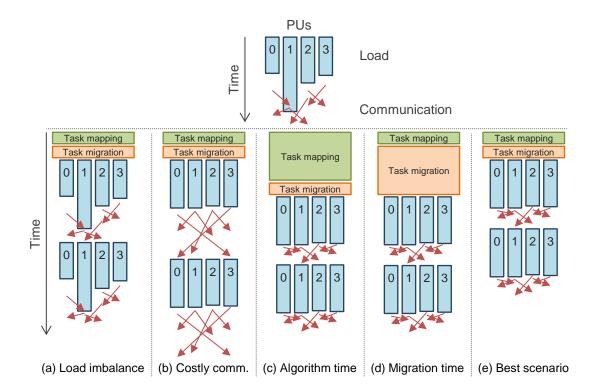

To better illustrate these concepts, Figure 2.9 depicts a scenario at its top where an application running on four PUs is imbalanced and suffering from costly communications. The vertical bars represent the load on each PU, and the arrows represent the communication time among PUs. Communication is illustrated after the computation phase of the application only to evidence it, as communication can happen at the same time tasks are computing.

Below the initial task mapping in Figure 2.9, five different task mappings are presented. Mapping (a) improves communication, but does not solve the load imbalance problem. Mapping (b) fixes the load imbalance, but increases the communication costs of the application. This could be a result of the task mapping algorithm not taking into account the communication behavior of the application or the machine topology. Mapping (c) solves both problems, but application performance is affected by the execution time of the task mapping algorithm. While this algorithm is running, the application is stalled. A similar problem happens with mapping (d), where the task migration overhead increases the total execution time of the application. The ideal case in Figure 2.9 is illustrated by mapping (e), where both performance problems are handled by a task mapping algorithm with a low overhead.

For performance portability to be achieved, a task mapping algorithm must take informed decisions regarding where to map tasks. In the next section, we discuss the main sources of application and platform knowledge used by task mapping algorithms.

Figure 2.9: Challenges for performance portability.

#### 2.3.3 Information required for mapping tasks

As previously discussed in Sections 2.2.1 and 2.1.2, we can see an application execution as the quintuple  $\mathcal{A} = (\mathcal{T}, Load, Size, Msgs, Bytes)$ , and the machine topology of the parallel platform where it is executing as a quadruple  $\mathcal{O} = (\mathcal{P}, \mathcal{L}, S, C)$ . Nonetheless, different task mapping algorithms may only consider part of this representation for its decisions, as they focus on different objectives or scenarios where part of this information is not available.

Task mapping algorithms that focus on mitigating load imbalance usually require some knowledge of the execution time of the tasks or the current utilization of the processing units. Tasks' loads, or *Load*, can be obtained by timing the execution of each task (for instance, at a runtime (KALE; KRISHNAN, 1993) or operating system (HOFMEYR et al., 2011) level), or by predicting their processing time based on some previous knowledge of the application. However, this second approach can only be applied to applications with static loads mostly. By using *Load*, an algorithm will seek to distribute tasks in a way that the sum of their loads in each PU is similar.

The total time spent of migrating tasks, or the migration overhead, can be estimated using the amount of bytes private to each task, or their Size. The current task mapping M is also important in this situation, as it enables the task mapping algorithm to keep some tasks where they currently are, avoiding unnecessary task migrations.