## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

### JERSON PAULO GUEX

# Utilizando Folding no Projeto de Portas Lógicas Robustas à Variabilidade de Processo

Dissertação apresentada como requisito parcial para obtenção do grau de Mestre em Microeletrônica

Prof. Dr. Ricardo Reis Orientador

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Guex, Jerson Paulo

Utilizando Folding no Projeto de Portas Lógicas Robustas à Variabilidade de Processo / Jerson Paulo Guex. – Porto Alegre: PGMICRO da UFRGS, 2013.

90 f.: il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2013. Orientador: Ricardo Reis.

Leiaute de células.

Variabilidade de processo.

DFM.

Folding de transistores.

Microeletrônica.

Reis, Ricardo.

Título.

#### Banca Examinadora:

Dra. Cecília Mezzomo, ST Microelectronics, Grenoble, França.

Prof. Dr. Marcelo de Oliveira Johann, PGMICRO, UFRGS, Porto Alegre, Brasil.

Prof. Dr. Tiago Roberto Balen, PGMICRO, UFRGS, Porto Alegre, Brasil.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Pró-Reitor de Coordenação Acadêmica: Prof. Rui Vicente Oppermann

Pró-Reitora de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do PGMICRO: Prof. Gilson Inácio Wirth

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **AGRADECIMENTOS**

Agradeço primeiramente a Deus por ter me acompanhado durante todos os dias de minha vida. Agradeço aos meus pais pelo total e incondicional apoio mesmo à distância, principalmente nos momentos de tristeza e apatia pela saudade de casa. Agradeço a todos os meus familiares pelo incentivo a seguir adiante, mas sem esquecer das origens e dos valores em que fui criado.

Agradeço aos meus colegas de jornada. Colegas que tive o prazer de conviver durante dois anos. Colegas que demonstraram amizade e acolhida. Agradeço profundamente o apoio que todos vocês me propiciaram, nas horas de alegria e de dificuldades, sua companhia e amizade sincera. Muito obrigado colegas dos Laboratórios 67-217, 67-219, 67-232. Um agradecimento especial para os mestrandos, mas mais do que isso, amigos Carolina Metzler, Fabio Walter, Walter C. Bartra pela companhia, apoio e incentivo durante esta jornada. Agradeço também aos bolsistas Davi Fagundes e Luigi Ferreira pela amizade e apoio.

Agradeço a minha grande amiga Cristina Meinhardt pela contínua ajuda e suporte ao trabalho que desenvolvi, pelas críticas, por me mostrar o que estava certo e o que estava errado, mas principalmente pelo seu comprometimento em me ajudar na medida do possível a concluir este mestrado com exito.

Agradeço ao programa PGMICRO pela oportunidade da realização deste mestrado. Agradeço a CAPES pelo financiamento de bolsa de estudo.

Agradeço ao meu orientador Prof. DR. Ricardo Reis pela dedicação, pelas dicas e críticas no decorrer destes dois anos, que mesmo de longe conseguia nos atender.

Um agradecimento mais do que especial a aquela que infelizmente não esta mais entre nós, mas seu amor por mim sempre me fez seguir em frente. Obrigado vó por toda a atenção que me dedicou durante todos esses anos.

Meus sinceros agradecimentos a todos. MUITO ABRIGADO!

# SUMÁRIO

| LISTA DE ABREVIATURAS E SIGLAS                                                                                                                                                                                                                                                                                                                                                                                             | 7                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| LISTA DE FIGURAS                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                            |

| LISTA DE TABELAS                                                                                                                                                                                                                                                                                                                                                                                                           | 10                                           |

| RESUMO                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                           |

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                   | 12                                           |

| 1.1       Motivação       1         1.2       Objetivo do Trabalho       1                                                                                                                                                                                                                                                                                                                                                 | 13<br>14<br>15                               |

| 2.1       Classificação da Variabilidade de Processo       1         2.2       Efeitos sobre os Parâmetros do Modelo       2         2.2.1       Dopagem Aleatória Discreta (RDD)       2         2.2.2       Line-Edge Roughness (LER)       2         2.2.3       Rugosidade de Interface e Variação de Espessura de Óxido       2                                                                                       | 17<br>17<br>20<br>21<br>22<br>23             |

| 3.1       Off Axis Ilumination (OAI)       2         3.2       Optical Proximity Correction (OPC)       2         3.3       Intensidade de Iluminação       3         3.4       Sub-Resolution Assist Feature (SRAF)       3         3.5       Phase Shift Mask (PSM)       3         3.6       Leiautes Regulares       3         3.6.1       Trade-Off       3         3.6.2       Classificação da Regularidade       3 | 25<br>29<br>29<br>31<br>31<br>33<br>34<br>34 |

| 4 CARACTERIZAÇÃO DA VARIABILIDADE DE PROCESSO                                                                                                                                                                                                                                                                                                                                                                              | 37<br>37<br>39                               |

| 4.4                 | Modelamento por Variação de Corrente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.4.                | randon resident and resident an | 43         |

| 4.4.2<br><b>4.5</b> | Fontes de Corrente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44<br>45   |

| <b>4.5 4.6</b>      | Variação da Tensão de Limiar devido a Flutuação da Espessura do Óxido                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45         |

| 4.0<br>4.7          | Variabilidade Considerando Contexto de Projeto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47         |

| 4.8                 | Modelamento Utilizando Distribuição Multivariada Normal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48         |

| 4.9                 | Caracterização Baseada em Forma de Onda Independente para Mode-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>-</b> 0 |

|                     | lamento de Porta (WiM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49         |

| 4.10                | Substituição de Transistores por Estruturas Paralelas, Seriais ou Mistas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50         |

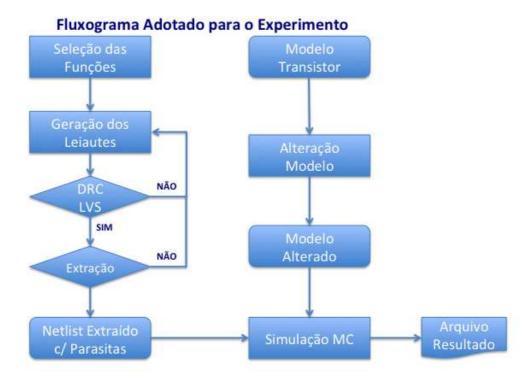

| 5                   | PROPOSTA E METODOLOGIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52         |

| <b>5.1</b>          | Proposta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52         |

| 5.2                 | Metodologia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53         |

| 5.2.3               | 1 Escolha das Funções                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53         |

| 5.2.2               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53         |

| 5.2.3               | Alteração do Modelo e Simulação                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55         |

| 6                   | RESULTADOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59         |

| 6.1                 | Comparando a Técnica de Folding Sobre os Experimentos Envolvendo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|                     | Portas Complexas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59         |

| <b>6.2</b>          | Folding sobre Células Básicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61         |

| 6.3                 | Comparação entre Circuitos com Células Complexas e Células Básicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|                     | (NAND, NOR, INVERSOR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63         |

| 6.4                 | Desvantagens da Utilização de Folding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 64         |

| 7                   | CONCLUSÃO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69         |

| REF                 | ERÊNCIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70         |

| 8                   | APÊNDICE A LEIAUTES DE PORTAS COMPLEXAS SEM FOLDING CRI-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|                     | ADAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75         |

|                     | APÊNDICE B LEIAUTES DE PORTAS COMPLEXAS COM FOLDING CRI-<br>ADAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79         |

|                     | APÊNDICE C NETLIST EXTRAÍDO COM O PADRÃO DSPF DE UMA<br>PORTA XOR DE 2 ENTRADAS UTILIZANDO FOLDING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83         |

## LISTA DE ABREVIATURAS E SIGLAS

ASIC Circuito integrado de aplicação específica

BEOL Back end of Line

CD Dimensões Críticas (menor dimensão da tecnologia)

CMOS Metal Óxido Semicondutor Complementar

CMP Polimento Químico Mecânico

DSPF Detailed Standard Parasitic Format

EUVL Luz Ultravioleta Extrema

FEOL Front End of Line

FPGA Field Programable Gate Array

IC Circuito Integrado

MOSFET Transistor de Efeito de Campo Metal Óxido Semicondutor

NBTI Negative Bias Temperature Instability

$T_{ox}$  Espessura do Óxido de porta

V<sub>th</sub> Tensão de Limiar

VLSI Very Large Scale Integration

# LISTA DE FIGURAS

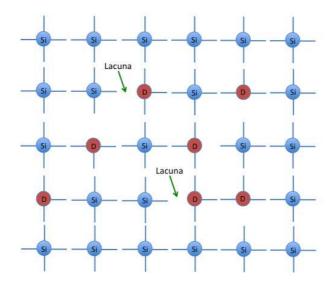

| Figura 2.1:  | Rede cristalina de silício com dopagem após processo de annealing .                                                                           | 19 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

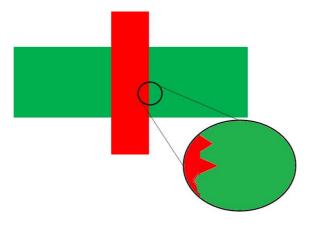

| Figura 2.2:  | Exemplo de rugosidade entre a interface difusão/canal                                                                                         | 22 |

| Figura 2.3:  | Processo de CMP. Fonte (HANYANG, 2011)                                                                                                        | 24 |

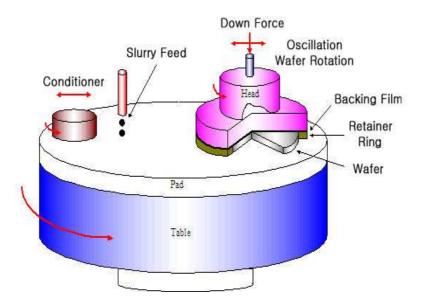

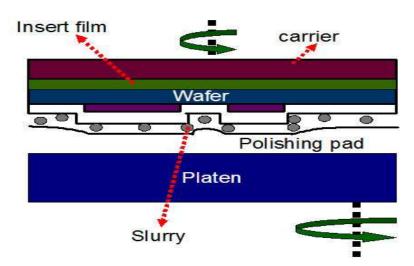

| Figura 2.4:  | Processo de CMP. Fonte (HANYANG, 2011)                                                                                                        | 24 |

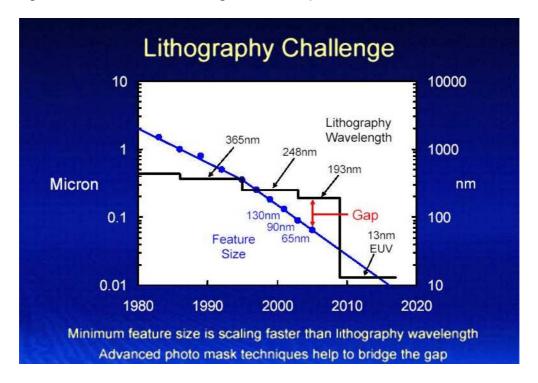

| Figura 3.1:  | Comprimento de onda utilizado no processo de Litografia (INTEL,                                                                               |    |

|              | 2011)                                                                                                                                         | 26 |

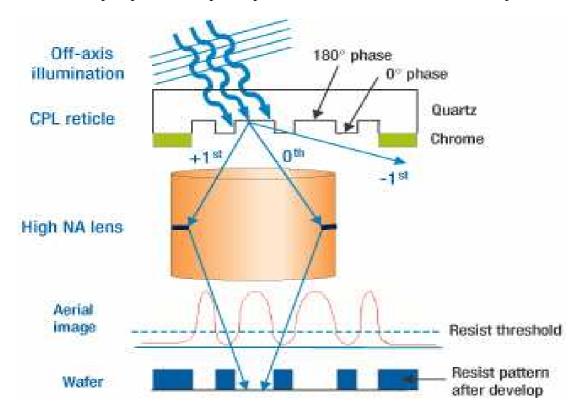

| Figura 3.2:  | Processo do Off Axis Ilumination. Fonte (ASML, 2011a)                                                                                         | 29 |

| Figura 3.3:  | Fluxo hipotético desde o projeto até o processo envolvendo OPC                                                                                | 30 |

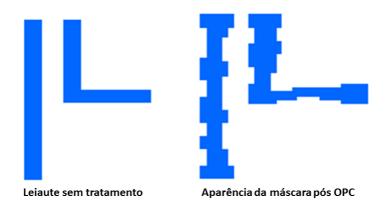

| Figura 3.4:  | Aplicação da técnica de OPC sobre a estrutura                                                                                                 | 30 |

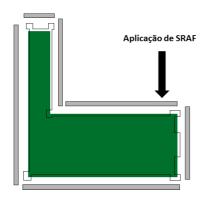

| Figura 3.5:  | Técnica SRAF aplicada sobre uma estrutura                                                                                                     | 32 |

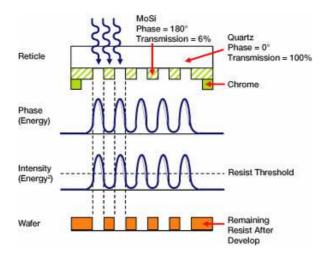

| Figura 3.6:  | Phase Shift Mask (PSM). Fonte (ASML, 2011b)                                                                                                   | 32 |

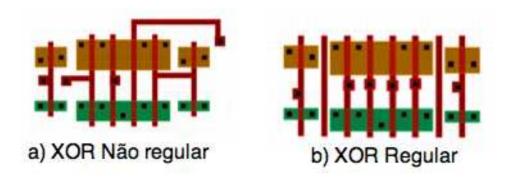

| Figura 3.7:  | a)Leiaute sem regularidade, b) Leiaute apresentando regularidade e com a adição de linhas <i>dummy</i> de polisilício, ambos leiautes despre- |    |

|              | zando roteamento em metal (SUBRAMANIAM et al., 2008)                                                                                          | 33 |

| Figura 3.8:  | Granularidade fina de um bloco regular                                                                                                        | 35 |

| Figura 3.9:  | Granularidade pequena de um bloco regular                                                                                                     | 35 |

| Figura 3.10: | Granularidade média de um bloco regular                                                                                                       | 36 |

| Figura 3.11: |                                                                                                                                               |    |

|              | hipotético                                                                                                                                    | 36 |

| Figura 4.1:  | Discriminação da distância entre duas áreas distintas                                                                                         | 38 |

| Figura 4.2:  | Relação entre parâmetros físicos e elétricos                                                                                                  | 39 |

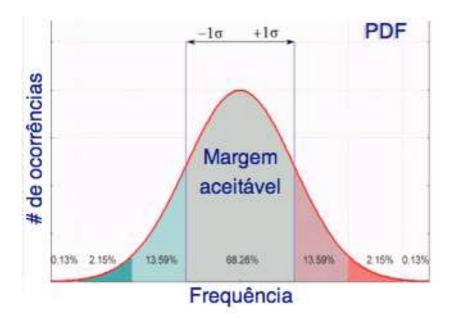

| Figura 4.3:  | Níveis hipotéticos de aceitação de variação de um circuito a partir de                                                                        |    |

|              | uma PDF qualquer                                                                                                                              | 42 |

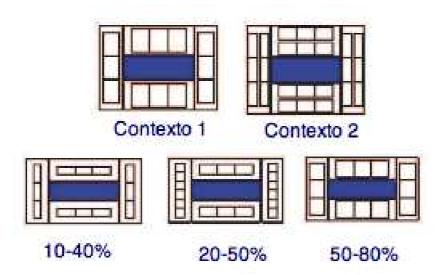

| Figura 4.4:  | Contexto utilizado para simulação da variabilidade sobre uma célula .                                                                         | 48 |

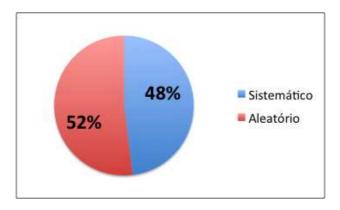

| Figura 4.5:  | Contribuição da Variabilidade Sistemática e Aleatória                                                                                         | 49 |

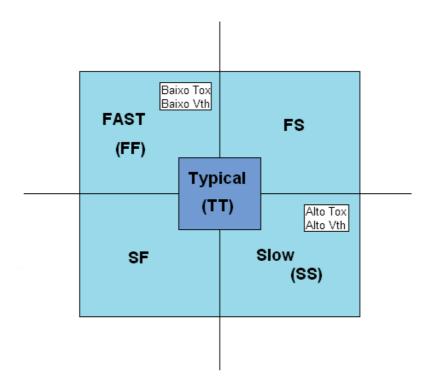

| Figura 5.1:  | Diagrama dos Cornes de Desempenho de um Circuito                                                                                              | 53 |

| Figura 5.2:  | Fluxograma das Etapas Executadas Durante o Experimento                                                                                        | 54 |

| Figura 5.3:  | Funções Lógicas Implementadas em Leiaute                                                                                                      | 55 |

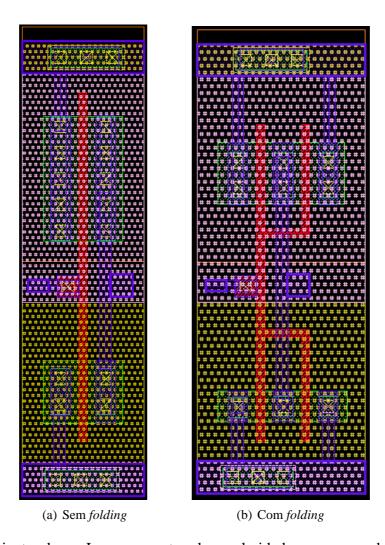

| Figura 5.4:  | Leiautes de um Inversor mostrando regularidade para a camada de                                                                               |    |

|              | polisilício                                                                                                                                   | 56 |

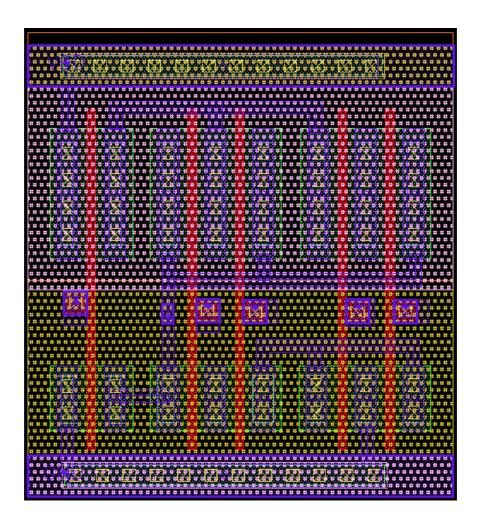

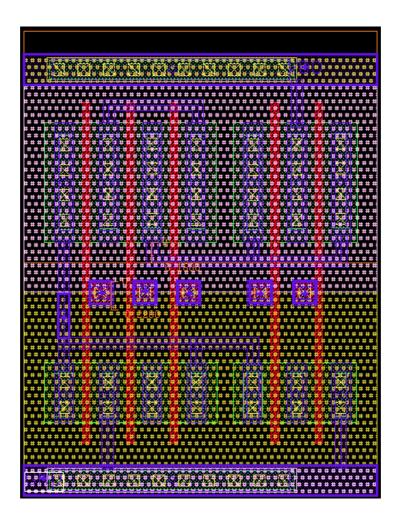

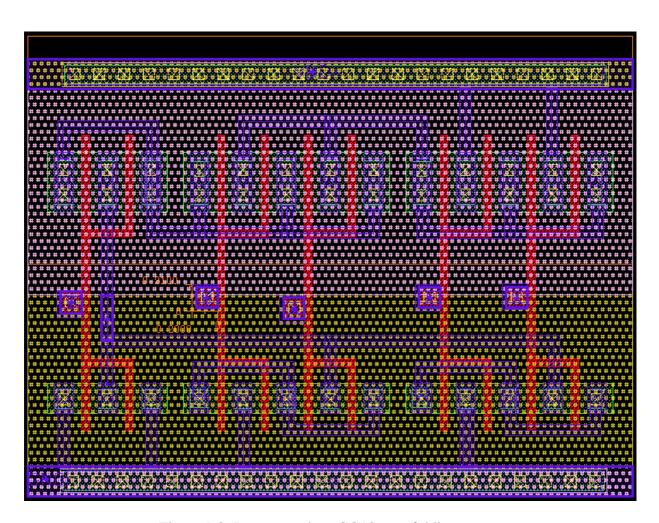

| Figura 8.1:  | Porta complexa CG2 sem folding                                                                                                                | 75 |

| Figura 8.2:  | Porta complexa CG3 sem folding                                                                                                                | 76 |

| Figura 8.3:  | Porta complexa CG10 sem folding                                                                                                               | 77 |

| Figura 8.4:  | Porta complexa CG11 sem folding                                                                                                               | 78 |

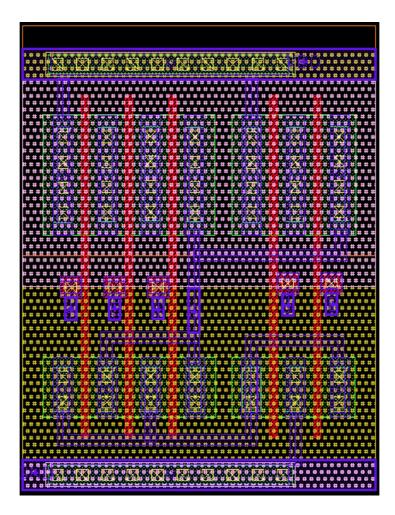

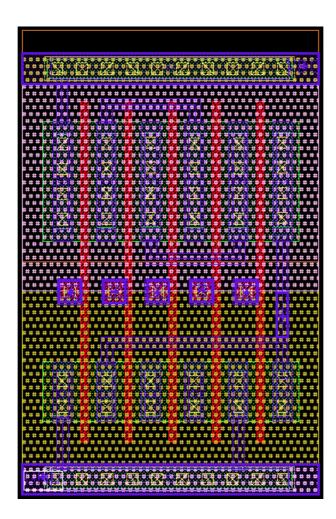

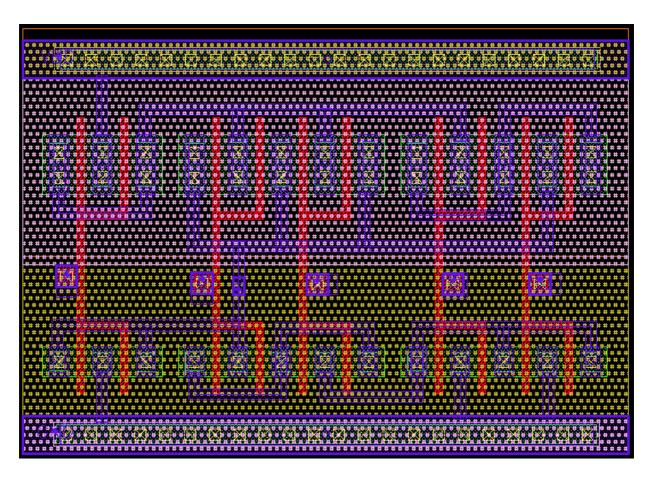

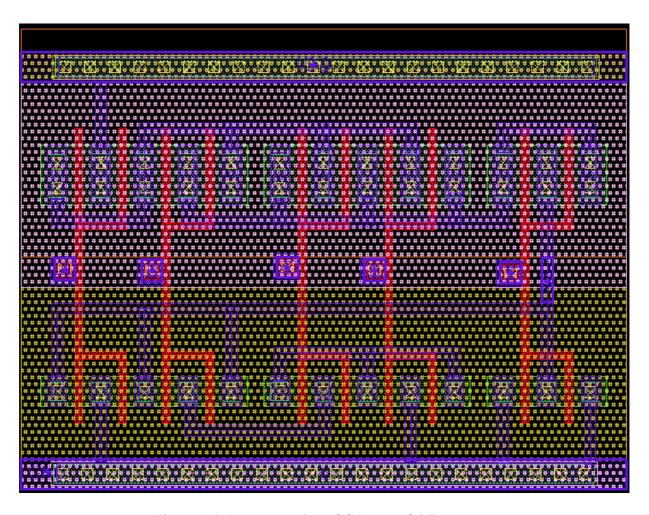

| Figura 9.1: | Porta complexa CG2 com folding  | 79 |

|-------------|---------------------------------|----|

| Figura 9.2: | Porta complexa CG3 com folding  | 80 |

| Figura 9.3: | Porta complexa CG10 com folding | 81 |

| Figura 9.4: | Porta complexa CG11 com folding | 82 |

# LISTA DE TABELAS

| Tabela 2.1:  | Variabilidade Espacial Aproximada                                             | 20         |

|--------------|-------------------------------------------------------------------------------|------------|

| Tabela 6.1:  | Resultados obtidos comparando o pior atraso encontrado usando corne           |            |

|              | de simulação TT                                                               | 60         |

| Tabela 6.2:  | Resultados obtidos comparando o pior atraso encontrado usando corne           |            |

|              | de simulação SS                                                               | 60         |

| Tabela 6.3:  | Resultados obtidos comparando o pior atraso encontrado usando corne           |            |

|              | de simulação FF                                                               | 61         |

| Tabela 6.4:  | Resultados obtidos para variação de potência RMS para o corne de              |            |

| T 1 1 6 5    | simulação TT                                                                  | 61         |

| Tabela 6.5:  | Resultados obtidos para variação de potência RMS para o corne de              | <b>6</b> 2 |

| Tabala 6.6.  | simulação SS                                                                  | 62         |

| Tabela 6.6:  | Resultados obtidos para variação de potência RMS para o corne de simulação FF | 62         |

| Tabela 6.7:  | Comparação dos piores atrasos normalizados sobre portas básicas               | 02         |

| idocia o.7.  | com e sem Folding                                                             | 63         |

| Tabela 6.8:  | Variação de potência RMS normalizada para células básicas com e               |            |

|              | sem Folding.                                                                  | 64         |

| Tabela 6.9:  | Comparação entre o pior atraso de versões com e sem folding em                |            |

|              | relação versão constituída de portas básicas                                  | 65         |

| Tabela 6.10: | Comparação da variação de potência RMS de versões com e sem fol-              |            |

|              | ding em relação a versão constituída de portas básicas                        | 66         |

| Tabela 6.11: | Comparação sobre a área total das células com e sem <i>folding</i>            | 67         |

| Tabela 6.12: | Comparação sobre a potência RMS consumida pelas células com e                 |            |

|              | sem <i>folding</i>                                                            | 68         |

### **RESUMO**

Este trabalho visa explorar técnicas de projeto de células que possibilitem a minimização dos efeitos da variabilidade de processo sobre o comportamento elétrico dos circuitos integrados. Para este trabalho foram abordados aspectos de regularidade, principalmente na camada de polisilício. A técnica de folding foi explorada em conjunto com a regularidade como possível metodologia de projeto voltada para a minimização dos efeitos da variabilidade de processo. Leiautes de portas lógicas complexas e básicas foram criadas utilizando tecnologia em 65nm. Os netlists dos leiautes extraídos foram simulados utilizando modelos que refletiam os efeitos da variabilidade sobre os parâmetros tecnológicos mais afetados pela variabilidade de processo. Os parâmetros selecionados para este experimento foram a largura (W) e comprimento (L) do canal do transistor, espessura do óxido de porta  $(T_{ox})$  e a mobilidade  $(\mu_0)$  das cargas. Os dados referentes ao pior caso envolvendo atraso e potência consumida de cada porta foram utilizados como métricas de comparação. Os resultados encontrados demonstram que a utilização da técnica de folding juntamente com aspectos de regularidade tornaram os experimentos menos sensíveis às variações do processos de manufatura de circuitos integrados. Essas reduções de sensibilidade chegaram em algumas situações à 33.22% para as portas básicas e de 28.96% para as portas complexas. A adição de folding e regularidade da camada de polisilício, trazem desvantagens significativas em área e potência consumida de cada porta. Pelos experimentos realizados é possível verificar aumento superior a 100% em área de algumas portas e de até 20.54% de aumento em potência. A união destas duas técnicas pode ser utilizada para tornar, por exemplo, o caminho crítico de um circuito integrado mais robusto quanto as variações de temporização e de potência.

**Palavras-chave:** Leiaute de células, variabilidade de processo, DFM, folding de transistores, microeletrônica.

#### Using Folding to Design Logic Gates Robust to Process Variability

### **ABSTRACT**

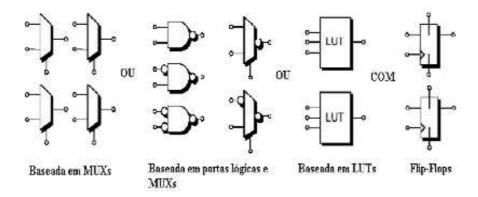

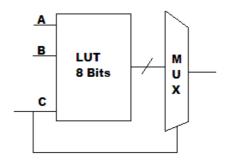

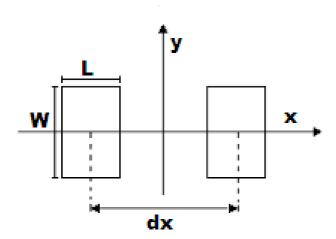

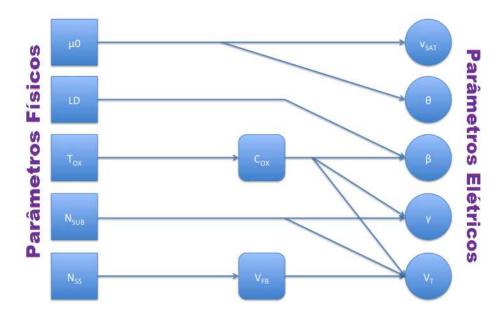

This paper aims to explore for design techniques that allow the minimization of the effects of process variability on the electrical behavior of integrated circuits. To this work were discussed aspects of regularity, especially in poly-silicon layer. The technique of it folding was explored in conjunction with the regularity as possible design methodology aimed to minimizing the effects of process variability. Complex and basic layouts logic gates were built using 65nm technology. The it netlists extracted from layouts of the gates were simulated using models that reflected the effects of variability on the main technological parameters such as W, L,  $T_x$ ,  $mu_0$  of the charges. The worst delay of each port and power consumption parameters were used for comparison in this work. The results show that using the it folding with regularity aspects of the experiments turns the layout gates less sensitive to process variations. These sensitivity reductions reached in some situations to 33.22 % for the basic gates and 28.96 % for the complex gates created. This techniques brings significant disadvantages in size and power consumption. For the experiments you can check increase of over 100% in area and up than 20,54% increase in power. These techniques should be used with discretion, especially on projects where there are area or consumption restrictions.