### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

CRISTIANO LAZZARI

## Automatic Layout Generation of Static CMOS Circuits Targeting Delay and Power Reduction

Dissertation presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Ricardo Augusto da Luz Reis Advisor

Prof. Dr. José Luís Almada Güntzel Coadvisor Lazzari, Cristiano

Automatic Layout Generation of Static CMOS Circuits Targeting Delay and Power Reduction / Cristiano Lazzari. – Porto Alegre: PPGC da UFRGS, 2003.

113 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2003. Advisor: Ricardo Augusto da Luz Reis; Coadvisor: José Luís Almada Güntzel.

Automatic layout generation.

Static CMOS logic gates.

Power and timing optimization.

Reis, Ricardo Augusto da Luz. II. Güntzel, José Luís Almada. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitora: Prof<sup>a</sup>. Wrana Maria Panizzi Pró-Reitor de Ensino: Prof. José Carlos Ferraz Hennemann Pró-Reitora Adjunta de Pós-Graduação: Prof<sup>a</sup>. Jocélia Grazia Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux Coordenador do PPGC: Prof. Carlos Alberto Heuser Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

The most dangerous moment comes with victory. NAPOLEON BONAPARTE

## AGRADECIMENTOS

Gostaria de agradecer primeiramente a meus pais Eloi e Lurdes pelo apoio dado durante minha vida e, principalmente, a educação que sempre me ofereceram, servindo de exemplo para minhas atitudes.

Agradeço a minha amada esposa Patrícia pelo apoio que me tem dado nos momentos difíceis. Ela que sempre me motivou a batalhar por meus objetivos e soube me incentivar nos momentos mais difíceis.

Sou grato aos meus orientadores Ricardo Reis e José Guntzel. Sem seus conselhos, suporte e encorajamento, este trabalho não teria sido possível. Agradeço pela confiança que depositaram em em mim e pela amizade que surgiu a partir deste trabalho.

Agradeço a meus professores Altamiro Amadeu Suzim, Luigi Carro, Marcelo Johann, Marcelo Lubaszewski e Sergio Bampi por me mostrar o valor da pesquisa e me auxiliar no meio acadêmico.

Gostaria de agradecer as pessoas que trabalharam diretamente comigo, Fabrício Bastian, Cristiano Domingues, Cristiano dos Santos, Daniel Ferrão, Gustavo Wilke, Renato Hentschke, Cláudio Menezes, Reginaldo Tavares e aos colegas do grupo de microeletrônica, especialmente a Alessandro Girardi, Fernando Paixão Cortes, Alexandre Morais Amory, Érika Fernandes Cota, Lucas Brusamarello, Fernanda Lima, Felipe Marques, Lisane Brisolara e Gustavo Neuberger.

# TABLE OF CONTENTS

| LIST OF ABBREVIATIONS AND ACRONYMS                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| LIST                                                                                                                                                                                               | OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                | 13                                                                         |  |

| LIST                                                                                                                                                                                               | OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                                         |  |

| ABS                                                                                                                                                                                                | TRACT                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                         |  |

| RES                                                                                                                                                                                                | JMO                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                         |  |

| 1 IN<br>1.1                                                                                                                                                                                        | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                               | 21<br>23                                                                   |  |

| 2 L<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                                                                                                                             | AYOUT GENERATION OF INTEGRATED CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                   | 25<br>25<br>25<br>30<br>34<br>36                                           |  |

|                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |  |

|                                                                                                                                                                                                    | PTIMIZATION TECHNIQUES USED IN ASSOCIATION WITH LAY-                                                                                                                                                                                                                                                                                                                                                                      | 37                                                                         |  |

|                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                           | 37<br>37                                                                   |  |

| 0                                                                                                                                                                                                  | UT GENERATION                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |  |

| 0<br>3.1                                                                                                                                                                                           | UT GENERATION       Introduction         Introduction       Introduction         Logic Optimization and Power Consumption Reduction       Introduction         Timing Verification       Introduction                                                                                                                                                                                                                     | 37                                                                         |  |

| 0<br>3.1<br>3.2                                                                                                                                                                                    | UT GENERATION                                                                                                                                                                                                                                                                                                                                                                                                             | 37<br>37<br>40<br>40                                                       |  |

| 0<br>3.1<br>3.2<br>3.3                                                                                                                                                                             | UT GENERATION       Introduction         Introduction       Introduction         Logic Optimization and Power Consumption Reduction       Introduction         Timing Verification       Introduction                                                                                                                                                                                                                     | 37<br>37<br>40<br>40<br>42                                                 |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br>3.3.1<br>3.3.2<br><b>3.4</b>                                                                                                                             | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization                                                                                                                                                                                           | 37<br>37<br>40<br>40<br>42<br>46                                           |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br>3.3.1<br>3.3.2<br><b>3.4</b><br>3.4.1                                                                                                                    | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models                                                                                                                                                                       | 37<br>37<br>40<br>40<br>42<br>46<br>46                                     |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br>3.3.1<br>3.3.2<br><b>3.4</b><br>3.4.1<br>3.4.2                                                                                                           | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing                                                                                                                                                   | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55                               |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br>3.3.1<br>3.3.2<br><b>3.4</b><br>3.4.1<br>3.4.2<br>3.4.3                                                                                                  | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing         Buffer Insertion                                                                                                                          | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55<br>56                         |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br>3.3.1<br>3.3.2<br><b>3.4</b><br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                         | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing         Buffer Insertion         Cloning                                                                                                          | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55<br>56<br>58                   |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br><b>3.3.1</b><br><b>3.3.2</b><br><b>3.4</b><br><b>3.4.1</b><br><b>3.4.2</b><br><b>3.4.3</b><br><b>3.4.4</b><br><b>3.4.4</b><br><b>3.4.5</b>               | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing         Buffer Insertion         Cloning         Related Works                                                                                    | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55<br>56                         |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br>3.3.1<br>3.3.2<br><b>3.4</b><br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                         | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing         Buffer Insertion         Cloning         Related Works         A Gate Sizing Method Applied to an Automatic Custom Layout Gener-          | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55<br>56<br>58<br>59             |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br><b>3.3.1</b><br><b>3.3.2</b><br><b>3.4</b><br><b>3.4.1</b><br><b>3.4.2</b><br><b>3.4.3</b><br><b>3.4.4</b><br><b>3.4.4</b><br><b>3.4.5</b><br><b>3.5</b> | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing         Buffer Insertion         Cloning         Related Works         A Gate Sizing Method Applied to an Automatic Custom Layout Generation Tool | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55<br>56<br>58                   |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br><b>3.3.1</b><br><b>3.3.2</b><br><b>3.4</b><br><b>3.4.1</b><br><b>3.4.2</b><br><b>3.4.3</b><br><b>3.4.4</b><br><b>3.4.4</b><br><b>3.4.5</b>               | UT GENERATION         Introduction         Logic Optimization and Power Consumption Reduction         Timing Verification         Critical Delay of Combinational Blocks         Clock Distribution         Timing Optimization         Cost models         Gate Sizing         Buffer Insertion         Cloning         Related Works         A Gate Sizing Method Applied to an Automatic Custom Layout Gener-          | 37<br>37<br>40<br>40<br>42<br>46<br>46<br>55<br>56<br>58<br>59<br>62<br>62 |  |

| 3.6   | Conclusion                                                      | 64  |

|-------|-----------------------------------------------------------------|-----|

| 4 M   | IAIN ASPECTS ON LAYOUT SYNTHESIS                                | 65  |

| 4.1   | Introduction                                                    | 65  |

| 4.2   | Full Automatic Layout Generation                                | 65  |

| 4.2.1 | Transistor Placement                                            | 65  |

| 4.2.2 | Effects of Diffusion Area Optimization on the Delay of Circuits | 66  |

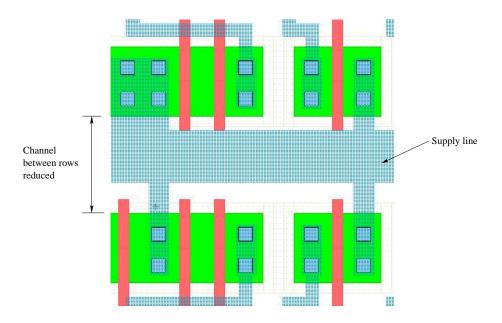

| 4.2.3 | Power Supply Lines Distribution                                 | 66  |

| 4.3   | The Placement Problem                                           | 70  |

| 4.4   | The Routing Problem                                             | 71  |

| 4.5   | Experiences on Layout Generation                                | 72  |

| 4.5.1 | First Experience                                                | 72  |

| 4.5.2 | Second Experience                                               | 74  |

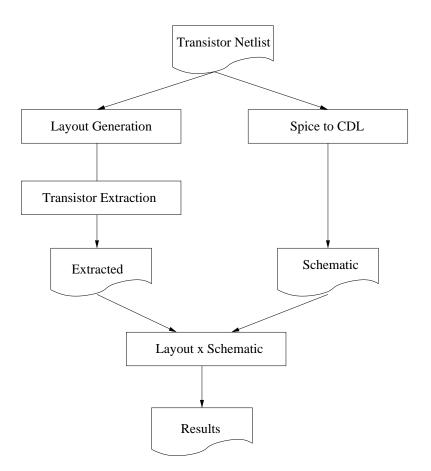

| 4.6   | Layout Validation                                               | 76  |

| 4.7   | Conclusion                                                      | 78  |

|       |                                                                 |     |

|       | NEW STRATEGY TO LAYOUT GENERATION                               | 79  |

| 5.1   | Introduction                                                    | 79  |

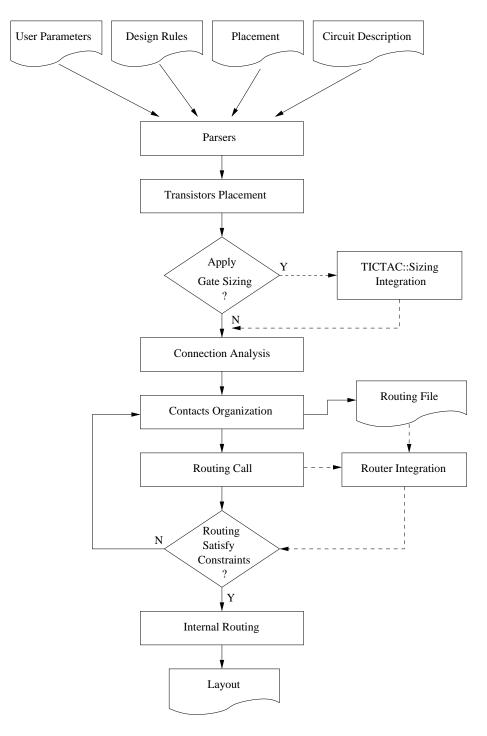

| 5.2   | Layout Generation Strategy                                      | 79  |

| 5.2.1 | Input Files and Parsers                                         | 79  |

| 5.2.2 | Transistors placement                                           | 80  |

| 5.2.3 | The Gate Sizing Tool Integration                                | 82  |

| 5.2.4 | Connection Analysis                                             | 82  |

| 5.2.5 | Contacts Organization                                           | 83  |

| 5.2.6 | The Routing Integration                                         | 83  |

| 5.2.7 | Row Internal Routing                                            | 84  |

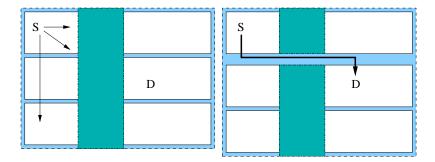

| 5.3   | Transistor Folding                                              | 85  |

| 5.4   | The Worm Grid Router                                            | 87  |

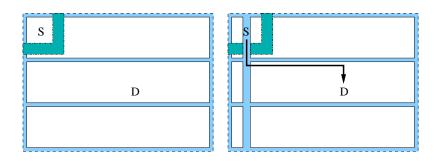

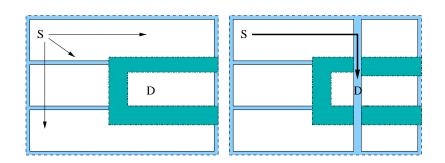

| 5.4.1 | First Situation: Blocking on the Source Point                   | 88  |

| 5.4.2 | Second Situation: Blocking on the Destination Point             | 88  |

| 5.4.3 | Third Situation: No path between Source and Destination         | 89  |

| 5.5   | Conclusion                                                      | 89  |

|       |                                                                 |     |

|       |                                                                 | 91  |

| 6.1   | Introduction                                                    | 91  |

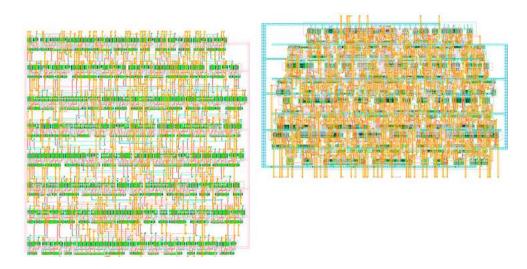

| 6.2   | Comparison with the automatic custom generator TROPIC3          | 91  |

| 6.3   | A Comparison with the Standard Cell Approach                    | 93  |

| 6.4   | Layout Optimization                                             | 94  |

| 6.5   | Conclusion                                                      | 96  |

| 7 C   | ONCLUSION                                                       | 97  |

| 7.1   |                                                                 | 99  |

| /•1   |                                                                 | 77  |

| REFE  | ERENCES                                                         | 101 |

| APPE  | ENDIX A AUTOMATIC LAYOUT GENERATION DESIGN RULES                | 109 |

| APPENDIX B | GERAÇÃO AUTOMÁTICA DE LEIAUTES DE CIRCUITOS<br>CMOS ESTÁTICOS VISANDO DIMINUIÇÃO DE ATRASO |

|------------|--------------------------------------------------------------------------------------------|

|            | <b>E CONSUMO</b>                                                                           |

# LIST OF ABBREVIATIONS AND ACRONYMS

ATPG Automatic Test Pattern Generation

| CAD    | Computer-Aided Design                                                   |

|--------|-------------------------------------------------------------------------|

| CDL    | Circuit Description Language                                            |

| $C_L$  | Load Capacitance                                                        |

| CMOS   | Complementary Metal-Oxide-Silicon                                       |

| DAG    | Direct Acyclic Graph                                                    |

| DFF    | D Flip-Flop                                                             |

| DSP    | Digital Signal Processing                                               |

| EDA    | Electronic Design Automation                                            |

| FOTC   | Full Over-the-cell                                                      |

| FSM    | Finite State Machine                                                    |

| GME    | Microelectronics Group                                                  |

| LVS    | Layout versus Schematic                                                 |

| IC     | Integrated Circuit                                                      |

| PI     | Primary Input                                                           |

| РО     | Primary Output                                                          |

| RMS    | Root Mean Square                                                        |

| RTL    | Register-Transfer Language                                              |

| SCCG   | Static CMOS Complex Gates                                               |

| TROPIC | Transparent Reconfigurable Optimized Parameterizable Integrated Circuit |

| VHDL   | Very high speed integrated circuits High Description Level              |

| VLSI   | Very Large Scale Integration                                            |

# LIST OF FIGURES

| Figure 1.1:  | Increase of the Number of Transistors in Microprocessors 21   |

|--------------|---------------------------------------------------------------|

| Figure 2.1:  | Different Levels in a Project Design                          |

| Figure 2.2:  | VHDL Behavior Description                                     |

| Figure 2.3:  | VHDL RTL Description                                          |

| Figure 2.4:  | Weinberger matrix                                             |

| Figure 2.5:  | Left edge algorithm applied to an Weinberger matrix           |

| Figure 2.6:  | An example of gate matrix                                     |

| Figure 2.7:  | the CLIP layout style                                         |

| Figure 2.8:  | Possible placeable devices within a datapath tile             |

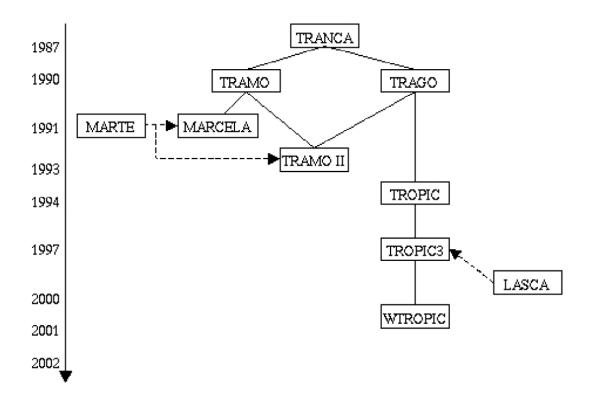

| Figure 2.9:  | Time line of physical synthesis at GME                        |

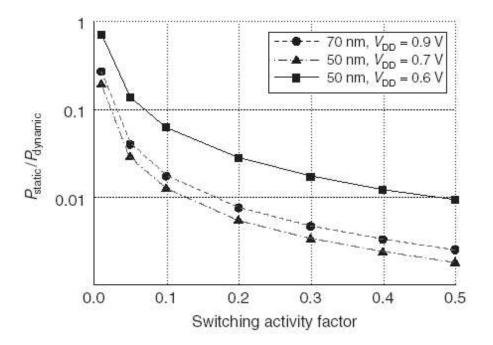

| Figure 3.1:  | Ratio of static to dynamic power consumption                  |

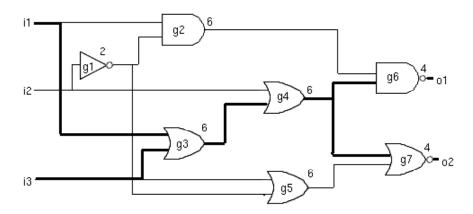

| Figure 3.2:  | A simple critical path example                                |

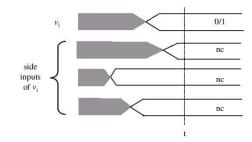

| Figure 3.3:  | Path Sensitization Criteria                                   |

| Figure 3.4:  | A TIC TAC example                                             |

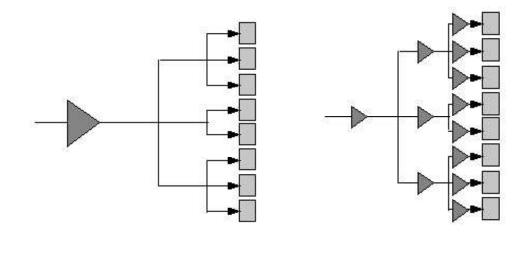

| Figure 3.5:  | Techniques to clock distribution                              |

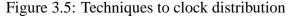

| Figure 3.6:  | Typical synchronous circuit                                   |

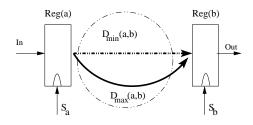

| Figure 3.7:  | Technology rules used to estimate the area                    |

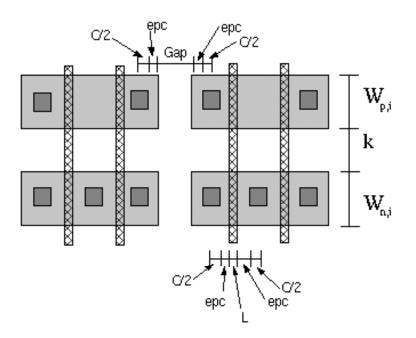

| Figure 3.8:  | Propagation delays of an inverter                             |

| Figure 3.9:  | Logical effort g to INV, NAND and NOR CMOS gates              |

| Figure 3.10: | Direct Acyclic Graph (DAG) for CMOS gates                     |

| Figure 3.11: | The DAG corresponding to a circuit of two 3-input static CMOS |

|              | NAND gates in series                                          |

| Figure 3.12: | Estimating $\tau$                                             |

|              | Area/delay curve for transistor sizing                        |

| Figure 3.14: | Example of transistor folding                                 |

|              | Row-based style gate sizing                                   |

| Figure 3.16: | Buffer insertion strategies                                   |

|              | Gate cloning as alternative to buffer insertion               |

| Figure 3.18: | Area increase under timing constraints                        |

| Figure 4.1:  | Effects of Diffusion Area Optimization                        |

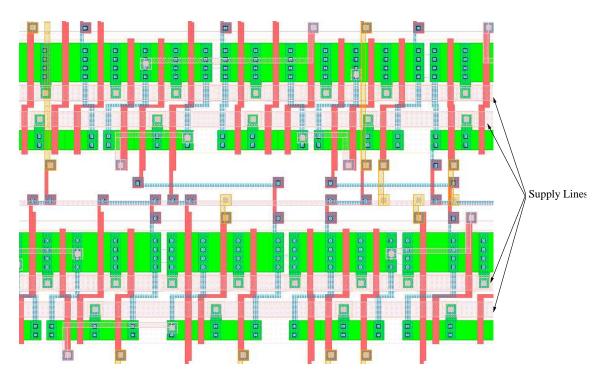

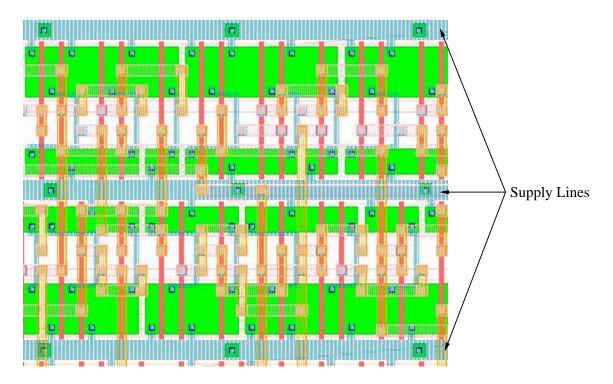

| Figure 4.2:  | Supply lines between PMOS and NMOS diffusion 68               |

| Figure 4.3:  | Supply lines on PMOS and NMOS diffusion                       |

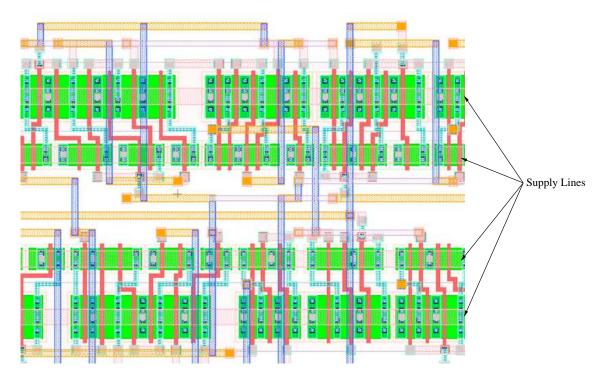

| Figure 4.4:  | Supply lines between rows                                     |

| Figure 4.5:  | Comparison in area between channel routing and full over-the-cell routing | 7      |

|--------------|---------------------------------------------------------------------------|--------|

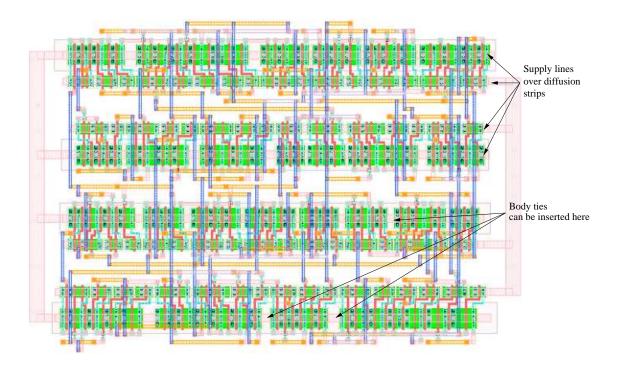

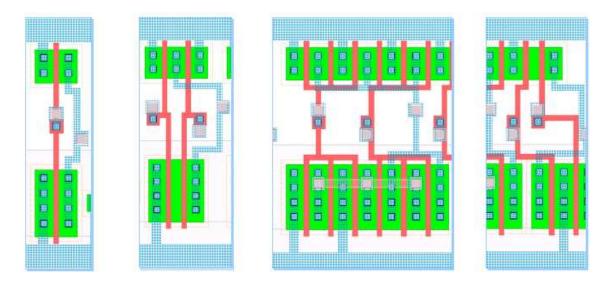

| Figure 4.6:  | An Example Resulting of the First Layout Generation Experience            | 7      |

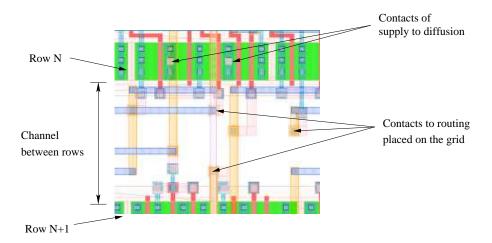

| Figure 4.7:  | Other Characteristics about the Layout Shown in Figure 4.6                | 7      |

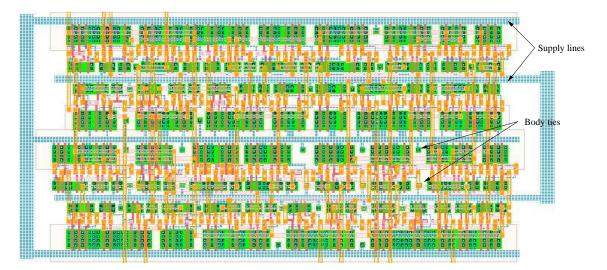

| Figure 4.8:  | An Example Resulting of the Second Layout Generation Experience .         | 7      |

| Figure 4.9:  | Supply line and Channel between rows about the Layout Shown in            | /      |

| 1 igule 4.9. | Figure 4.8                                                                | 7      |

| Figure 4.10: | -                                                                         | ,<br>7 |

| 0            | Examples of Complex Gates Automatically Generated                         | 7<br>7 |

| 0            | · · ·                                                                     |        |

| Figure 4.12: | A Layout versus Schematic Flow                                            | 7      |

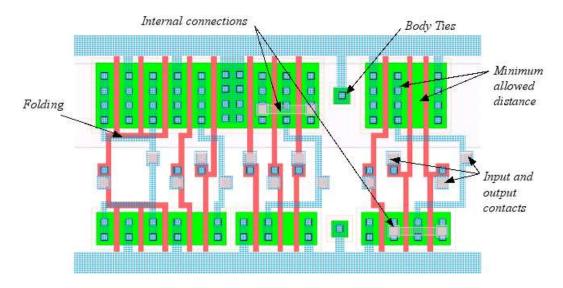

| Figure 5.1:  | An example of Layout generated by Parrot Punch                            | 8      |

| Figure 5.2:  | Automatic Layout Generation Strategy                                      | 8      |

| Figure 5.3:  | Algorithm for transistor placement                                        | 8      |

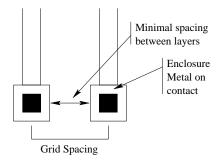

| Figure 5.4:  | Grid router spacing                                                       | 8      |

| Figure 5.5:  | Candidate positions to gates input and output terminals                   | 8      |

| Figure 5.6:  | Four situations on the poly routing algorithm                             | 8      |

| Figure 5.7:  | Schematic and Graph of a logic gate                                       | 8      |

| Figure 5.8:  | An Example of the Folding technique                                       | 8      |

| Figure 5.9:  | First Situation: Blocking on the Source Point                             | 8      |

| Figure 5.10: | Second Situation: Blocking on the Destination Point                       | 8      |

| Figure 5.11: |                                                                           | 8      |

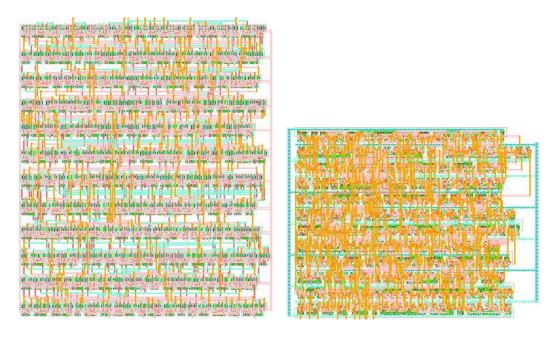

| Figure 6.1:  | TROPIC3 (left) and Parrot Punch (right) layouts of the C432 circuit .     | 9      |

| Figure 6.2:  | TROPIC3 (left) and Parrot Punch (right) layouts of the C499 circuit .     | 9      |

| Figure 6.3:  | TROPIC3 (left) and Parrot Punch (right) layouts of the C880 circuit .     | 9      |

| Figure 6.4:  | Comparison between Standard Cell layouts and Parrot Punch Layouts         | 9      |

# LIST OF TABLES

| Table 3.1: | Error amount in the estimated area.                               | 48 |

|------------|-------------------------------------------------------------------|----|

| Table 3.2: | Logical effort of common gates                                    | 51 |

| Table 3.3: | Experimental results                                              | 63 |

| Table 6.1: | Area Occupation in TROPIC3 and Parrot Punch layouts ( $\mu m^2$ ) | 92 |

| Table 6.2: | Delay $(ns)$ and Power Consumption $(mW)$ in TROPIC3 and Parrot   |    |

|            | Punch Layouts                                                     | 93 |

| Table 6.3: | Comparison between STD CELL and Parrot Punch layouts              | 94 |

| Table 6.4: | Layout optimization in the circuit csa8                           | 95 |

| Table 6.5: | Layout optimization in the circuit bw                             | 96 |

| Table 6.6: | Layout optimization in the circuit alu2                           | 96 |

## ABSTRACT

The evolution of integrated circuits technologies demands the development of new CAD tools. The traditional development of digital circuits at physical level is based in library of cells. These libraries of cells offer certain predictability of the electrical behavior of the design due to the previous characterization of the cells. Besides, different versions of each cell are required in such a way that delay and power consumption characteristics are taken into account, increasing the number of cells in a library.

The automatic full custom layout generation is an alternative each time more important to cell based generation approaches. This strategy implements transistors and connections according patterns defined by algorithms. So, it is possible to implement any logic function avoiding the limitations of the library of cells. Tools of analysis and estimate must offer the predictability in automatic full custom layouts. These tools must be able to work with layout estimates and to generate information related to delay, power consumption and area occupation.

This work includes the research of new methods of physical synthesis and the implementation of an automatic layout generation in which the cells are generated at the moment of the layout synthesis. The research investigates different strategies of elements disposition (transistors, contacts and connections) in a layout and their effects in the area occupation and circuit delay. The presented layout strategy applies delay optimization by the integration with a gate sizing technique. This is performed in such a way the folding method allows individual discrete sizing to transistors.

The main characteristics of the proposed strategy are: power supply lines between rows, over the layout routing (channel routing is not used), circuit routing performed before layout generation and layout generation targeting delay reduction by the application of the sizing technique. The possibility to implement any logic function, without restrictions imposed by a library of cells, allows the circuit synthesis with optimization in the number of the transistors. This reduction in the number of transistors decreases the delay and power consumption, mainly the static power consumption in submicrometer circuits.

Comparisons between the proposed strategy and other well-known methods are presented in such a way the proposed method is validated.

**Keywords:** Automatic layout generation, static CMOS logic gates, power and timing optimization.

#### Geração Automática de Leiautes de Circuitos CMOS Estáticos Visando Diminuição de Atraso e Consumo

### RESUMO

A crescente evolução das tecnologias de fabricação de circuitos integrados demanda o desenvolvimento de novas ferramentas de CAD. O desenvolvimento tradicional de circuitos digitais a nível físico baseia-se em bibliotecas de células. Estas bibliotecas de células oferecem certa previsibilidade do comportamento elétrico do projeto devido à caracterização prévia das células. Além disto, diferentes versões para cada célula são requeridas de forma que características como atraso e consumo sejam atendidos, aumentando o número de células necessárias em uma bilioteca.

A geração automática de leiautes é uma alternativa cada vez mais importante para a geração baseada em células. Este método implementa transistores e conexões de acordo com padrões que são definidos em algoritmos sem as limitações impostas pelo uso de uma biblioteca de células. A previsibilidade em leiautes gerado automaticamente é oferecida por ferramentas de análise e estimativa. Estas ferramentas devem ser aptas a trabalhar com estimativas do leiaute e gerar informações relativas a atraso, potência e área.

Este trabalho inclui a pesquisa de novos métodos de síntese física e a implementação de um gerador automático de leiautes cujas células são geradas no momento da síntese do leiaute. A pesquisa investiga diferentes estratégias de disposição dos componentes (transistores, contatos e conexões) em um leiaute e seus efeitos na ocupação de área e no atraso e de um circuito. A estratégia de leiaute utilizada aplica técnicas de otimização de atraso pela integração com uma técnicas de dimensionamento de transistores. Isto é feito de forma que o método de folding permita diferentes dimensionamentos para os transistores.

As principais características da estratégia proposta neste trabalho são: linhas de alimentação entre bandas, roteamento sobre o leiaute (não são utilizados canais de roteamento) e geração de leiautes visando a redução do atraso do circuito pela aplicação da técnica de dimensionamento ao leiaute e redução do comprimento médio das conexões. O fato de permitir a implementação de qualquer combinação de equações lógicas, sem as restrições impostas pelo uso de uma biblioteca de células, permite a síntese de circuitos com uma otimização do número de transistores utilizados. Isto contribui para a diminuição de atrasos e do consumo, especialmente do consumo estático em circuitos submicrônicos.

Comparações entre a estratégia proposta e outros métodos conhecidos são apresentadas de forma a validar a proposta apresentada.

**Palavras-chave:** Geração Automática de Leiautes, Portas Lógicas Estáticas CMOS, Otimização em Atraso e Consumo.

## **1** INTRODUCTION

CAD (Computer-Aided Design) tools are used since of the beginning of the microelectronics. They have great importance because of the need for obtaining products that lies on time-to-market. As new technologies are available each time more frequently, it is fundamental the use of CAD tools to design circuits.

Another point of influence in the use of CAD tools is the complexity of VLSI systems. Small commercial circuits may contain hundred or thousand of transistors, becoming hard the manual development.

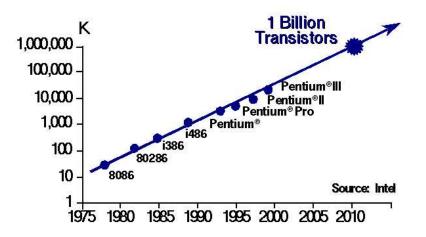

Figure 1.1: Increase of the Number of Transistors in Microprocessors

Figure 1.1 shows the increase of the number of transistors in a microprocessor family. It is possible to verify that the increase of the number of transistors grows linearly and it is estimated to manufacture processors with one billion of transistors by 2010.

In state-of-the-art and next generation VLSI circuits, geometries get smaller, clock frequencies keeps increasing and on-chip interconnect gains increased importance (CONG; SARRAFZADEH, 2000). In addition, problems in physical design are getting more complex and EDA (Electronic Design Automation) tools are essential to solve current design problems (SARRAFZADEH et al., 2001).

From  $0.13\mu m$  and smaller, ICs are more susceptible to breakdown during fabrication (antenna effect) or to wear-out over time (electro-migration). Dealing with these issues requires careful planning (OTTEN; CAMPOSANO; GROENEVELD, 2002). This emphasizes the need for EDA tools able to automatically implement and validate integrated

circuits.

Traditional physical level design relies on standard cell libraries. Standard cell methodology can be used for ASIC design because the layout process is partially automated. In addition, cell libraries offer some predictability to design because cells are characterized before synthesis.

However, standard cell libraries have limited number of cells. This imposes some restrictions in the layout synthesis. Also, different versions of each cell are required in order to drive different strengths, thus, increasing the number of elements in libraries to some hundreds of cells.

An alternative to the standard cell based layout generation is the automatic custom layout generation approach. In this approach it is not used cells from a library. Instead, it generates each element (transistors, contacts and connections) according to a layout pattern that is intrinsically programmed within its algorithms. In addition, automatic custom generation can be flexible to create optimized layouts to each location where they are inserted. Thus, it is a library free approach.

The automatic layout generation appeared with the Weinberger matrix (WEINBERGER, 1967). Other works on automatic cell generation were those of Lopez and Law (LOPEZ; LAW, 1980) and Uehara and Cleemput (UEHARA; CLEEMPUT, 1981). The formers introduce a layout style known as gate matrix, while the latters present the so-called linear matrix layout style. Both works were originally developed having in mind the automatic generation of cell libraries. Current layout generators are mainly based on the linear matrix style and they are able to generate modules with thousands of transistors.

In automatic custom layout generation, analysis and estimation tools must offer the predictability. An analysis tool can work well with layout estimates and generate accurate information about the layout.

In (GÜNTZEL, 2000) it is presented important concepts about timing analysis in VLSI circuits. Guntzel reports that timing verification targets at determining whether the timing constraints imposed to the design may be satisfied or not. More strictly, timing verification is concerned with estimating the critical delay of circuits and the maximal operating frequency, in case of clocked circuits.

The accuracy of timing verification is completely dependent on the accuracy of the used circuit models. By circuit models it is meant not only the physical delay model used to quantify the delay of each component, but also the models for computing circuit component delay and the circuit delay itself.

Timing analysis associated to layout generation can improve accurate timing optimization characteristics to the circuit design. Besides, timing analysis can be used to improve layout optimization by gate sizing and buffer insertion techniques.

Gate sizing is a technique to optimize each individual gate of the circuit, given certain characteristics. Characteristics refer to widths of the transistors, relations between gates and their implication in the timing.

Buffer insertion consists on the insertion of buffers in the circuit in order to distribute the capacitance of the original gate over the buffers reducing the delay of the path.

Santos et al. present in (SANTOS et al., 2003) a gate sizing tool able to perform timing optimization. The technique uses a timing analysis tool in order to estimate long paths and apply gate sizing in the critical path.

The number of transistors in a circuit is directly related to the power consumption.

Thus, logic optimization targeting reduction on the number of transistors associated to a layout generation able to implement a large set of logic functions can reduce the total power consumption of a circuit.

Layout optimization is very important in the development of integrated circuits (IC). No chip is designed without analyzing the environment where it is used. According the project application, characteristics as area, speed and power dissipation are studied to generate best results.

In this work it is presented a research about physical synthesis and the implementation of an automatic custom layout generator. The research is related to layout strategies and its effects on area occupation and on the delay of the circuit. As result it is presented a new strategy to automatic custom layout generation in which small area occupation and delay reduction are aimed.

The layout generation strategy applies techniques to timing optimization by the integration with a gate sizing technique. This is performed with the application of a folding technique that resize the transistors.

A tool called Parrot Punch was developed in order to validate the proposed strategy and it is presented in this work.

#### **1.1 Organization of This Work**

The work is organized as follows. Chapter 2 presents some basic concepts about layout generation available in the literature and the time line of techniques and tools developed at the UFRGS microelectronics group. Besides, it is shown an overview on the design flow, starting from the high level design until the physical level.

Chapter 3 presents different techniques often used in layout optimization, its characteristics and its effects in circuits. Works related to layout optimization are reported and the method proposed in (SANTOS et al., 2003) is highlighted.

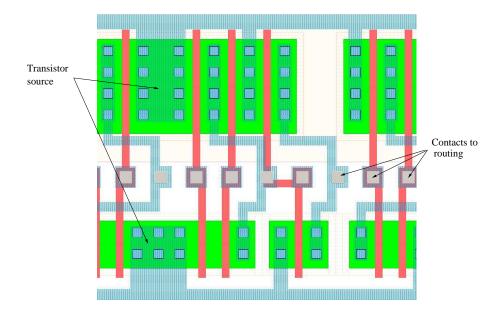

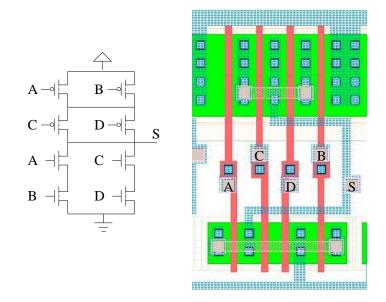

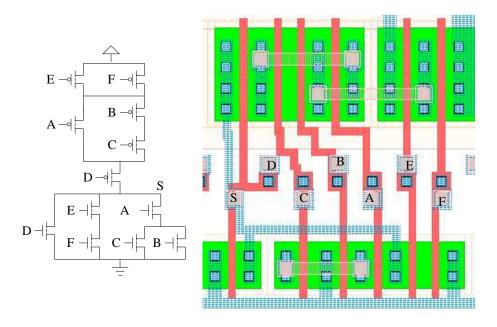

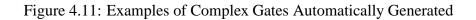

Main aspects on layout synthesis are presented in chapter 4. It is shown important aspects about layout generation, effects on layout optimization and the power supply distribution. The placement and routing problem is also reported. To finish this chapter, some experiences on automatic layout generation is emphasized as consequence to the proposed layout generation strategy.

Chapter 5 presents a new strategy to the automatic generation problem. It is proposed a new method to layout generation without the use of library cells and the used algorithms are reported.

Experimental results are reported in chapter 6. Results obtained from the comparison between the strategy described in chapter 5 and other well known methods to layout generation are shown and layout optimization results are discussed.

Finally, some concluding remarks and suggestions to future works are offered.

## 2 LAYOUT GENERATION OF INTEGRATED CIRCUITS

### 2.1 Introduction

The complexity of the systems increase and also the need for design automation on more abstract levels where functionality and tradeoffs are easier to understand (GAJSKI et al., 1992). Thus, techniques on different abstraction levels can be used in order to generate accurate integrated circuits given the circuit specification.

When ASIC is aimed, the design of circuits may starts in higher abstraction level than the transistor level. In section 2.2 it is given some basic concepts about abstraction levels and characteristics that implies on the layout generation.

Researches on automatic layout generation have been done since the 60's. Nowadays, academic and commercial tool are able to generate layouts with thousands of transistors. In section 2.3 it is shown some layout techniques found in the literature. Section 2.4 presents a brief description of the physical synthesis at the UFRGS microelectronics group.

### 2.2 A High Level to Layout Level Flow Overview

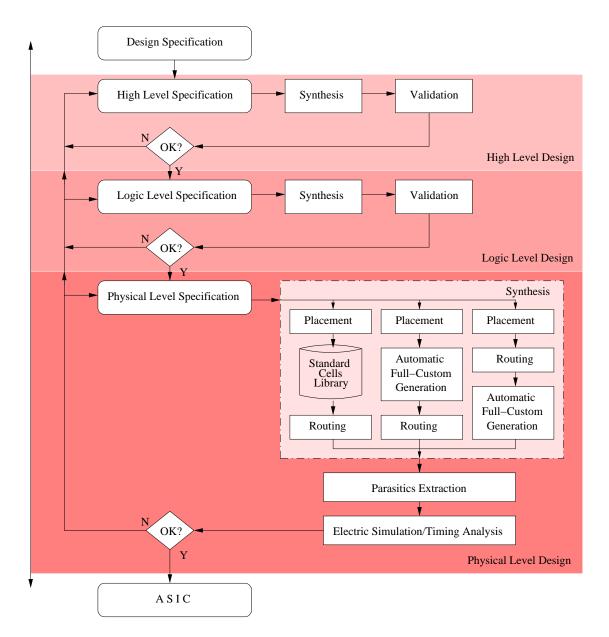

Figure 2.1 shows a flow in which a system design is separated in tree levels of abstraction. When the goal is develop an ASIC, the design may starts in any level in function of circuit complexity. In each design level, tools are used to optimize and to validate automatically the design according to the designer requirements.

Following is reported some characteristics of the related flow and it is given a brief description about *high level design*, *logic level design* and *physical level design*. As the focus of this work is the automatic custom layout generation, the discussion is detailed on the physical level design.

Nowadays, design flows may starts from a higher abstraction level than the high level design. System C and System Verilog are examples of description languages in system level. They have been used as a solution to describe and validate systems.

#### **High Level Design**

System designers think in terms of states and actions triggered by external and internal events, and in terms of computations and communications (CAMPOSANO; WOLF, 1991). This emphasizes the use of high-level descriptions on the development of integrated circuits.

Figure 2.1: Different Levels in a Project Design

High-level synthesis takes a specification of the behavior of a digital system with a set of constraints and goals on the resulting hardware to be satisfied, and finds a structure that realizes the given behavior while satisfying the given goals and constraints (KU; MICHELI, 1992).

The behavior is described as an algorithm in which the implementation is separated in *data-path* and *control* parts. The data-path contains functional units, register and their interconnection. The control is responsible to activate the behavior of the data-path.

A high level coding can be developed in behavior level or RTL (Register-Transfer Language). In a behavior description, the coding is based on the behavior of each component used in the HDL code while a RTL description presents structural elements close to the logic of the hardware. Figures 2.2 and 2.3 illustrates VHDL behavior description and VHDL RTL description, respectively.

```

library IEEE;

use IEEE.std_logic_1164.all;

entity ripple_carry is

generic( N : natural := 4 ;

port( a :in std_logic_vector(N-1 downto 0);

b :in std_logic_vector(N-1 downto 0);

s :out std logic vector(N-1 downto 0);

cin : in std logic;

cout :out std_logic );

end entity;

architecture estrut of ripple_carry is

signal carry : std_logic_vector(N downto 0);

begin

carry(0) <= cin;</pre>

cout <= carry(N);</pre>

add:for i in 0 to N-1 generate

begin

s(i) <= carry(i) xor a(i) xor b(i);</pre>

carry(i+1) <= (carry(i) and a(i)) or

(carry(i) and b(i)) or (a(i) and b(i));

end generate;

end architecture;

```

Figure 2.2: VHDL Behavior Description

The most known and used high level description languages are VHDL and Verilog. Usually VHDL is more frequently found in academic projects and Verilog is widely used in the industry.

```

entity fulladder is

port (V1,

V2,

Carry_in : IN bit;

Carry_out,

S : OUT bit );

end entity;

architecture str of fulladder is

signal t1, t2 : bit;

begin

t1 <= V1 xor V2;

t2 <= V1 and V2;

S <= Carry_in xor t1;

Carry_out <= t2 or ( Carry_in and t1 );

end architecture str;

```

Figure 2.3: VHDL RTL Description

#### Logic Level Design

The benefits of automating the logic design process are lost if the result does not meet area, speed and power constraints, while optimizing the design tradeoffs as well as an expert designer could (HACHTEL; SOMENZI, 1996). This highlights the importance of the quality of the tools used in synthesis not only in the logic level but also in whole design flow.

Hachtel and Somenzi also report accepted optimization criteria for logic synthesis. Logic tools must be able to workout minimize on:

- 1. Area occupied by logic gates and interconnects;

- 2. The delay of the critical path through the logic;

- 3. The degree of testability of the circuit (fault coverage);

- 4. Power consumed by the logic gates.

Algorithms for logic optimization must be able to satisfy these quantities based on designer requirements. The area of logic gates and their interconnect is directly related to the area occupied by the circuit while the delay of the circuit is given by its critical path. The minimization of power consumption is very important nowadays because of the increasing use of mobile technologies.

Manufacturing for testing is another important aspect in integrated circuits design that determines when a fabricated chip works as expected.

#### **Physical Level Design**

At the physical level, the layout generation of ICs is done based on technology process and design specifications. The result of the physical design is a layout and a set of estimates (i.e. circuit delay, area and power) to guarantee that the circuit can be manufactured in accordance to its specifications.

Usually, this level can start from a transistor schematic or a description containing a transistors and connections lists(i.e. SPICE netlist). In both cases it is presented full information needed for generating the IC. In addition, other specifications circuit delay and power consumption demanded by the designer can be constrained to the physical design.

Synthesis based on a transistor netlist can be separated in two branches. First, the standard cell approach is important because it is the most used in academic and industry environment. The other method is related to the automatic custom generation. The custom generation can be separated into other two parts which is explained below.

Traditional physical level design relies on standard cells libraries. These cell libraries can be generated automatically or manually based on some constraints defined by the designer.

However, standard cell libraries have a limited number of cells that imposes restrictions to layout synthesis because it is not possible to implement any logic function but only the ones that are available in the library. Also, different versions of each cell are required in order to drive different strengths increasing the number of cells in libraries to some hundreds.

Automatic full-custom layout of circuits is an alternative to the standard cell approach. This method consists on generating a block or a complete circuit in a fully automatic way without using any cell library. This means that the circuit is generated based only on a transistor netlist and the cells are generated on the fly.

It is clear that the standard cell approach is faster to generate solutions because of the possibility to search a cell in a library and to place it into the layout. This search, targeting a specified logic gate, can find a set of cells with the same logic function in which they are distinguished in delay, area and power optimization. The synthesis tool must be able to choose a cell with the best as possible solution given the demand for a logic function.

Automatic full-custom layout generation differs from the standard cell approach by the methodology flow where it is generated layout on demand. Thus, all transistors are placed into the layout and their connections are performed on-the-fly.

In order to produce automatic custom synthesis able to generate layouts that relies with the circuit specifications, other tools for area, delay and power estimation must be associated to the synthesis flow.

As reported above, automatic custom generation can be separated into two synthesis flows. The difference lies on the integration between automatic layout generation and the routing step. The two methods are similar but different results can be obtained from each other.

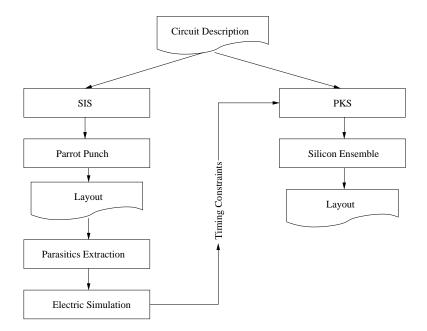

The first physical synthesis flow is the traditional one in which the placement of the logic gates are done based on area estimates. After, the synthesis of the transistors is performed and the layout is generated. As last step, the routing is done to implement gates connections.

Tavares (TAVARES, 2003) proposes another method for automatic layout generation. This method is very interesting due to the possibility to perform the routing before the layout generation. The placement is done exactly as the traditional method but the circuit layout is generated only when the routing is completed.

This idea is more interesting when the routing algorithm has, not fixed points in a net, but a range of possible positions in each logic gate. Thus, the routing can be easily performed and the result given by the routing algorithm is better than the method with fixed point to connections.

After synthesis, tools for parasitics extraction and simulation are used to validate the generated layout. Related to parasitics are capacitances and resistances present in the layout. These parasitics are responsible by the delay and power consumption of a circuit.

Cadence  $Diva^{TM}$ , Mentor  $ICExtract^{TM}$  and LASCA are examples of parasitics extraction tools. Diva and ICExtract are commercial tool widely used in the industry and LASCA is an academic tool presented in (FERREIRA; MORAES; REIS, 2000). These tools are able to extract capacitances and resistances of transistors and connections.

There are two main ways to validate the layout after synthesis and extraction. First, an electric simulation based in an electric model may be used to generate a waveform in the PO (primary outputs) based on sources applied to the PIs (primary inputs). Thus, it is possible to calculate the delay of the circuit based on the waveform differences.

A timing analysis tool is a faster way to estimate the delay of a circuit. In this type of delay estimation, the analysis tool extracts the critical path of the circuit and it is able to present the delay and the patterns that applied to the PIs are responsible by this delay.

### 2.3 Layout Generation Strategies

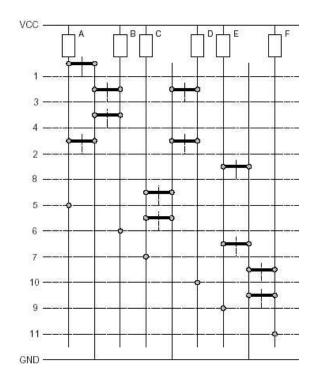

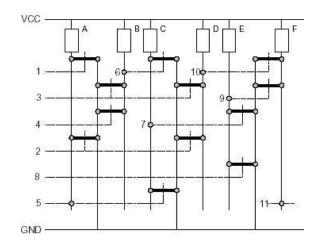

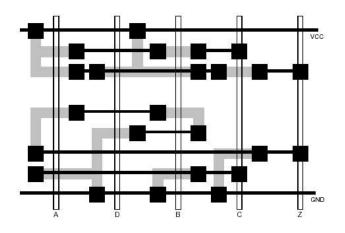

The *Weinberger matrix* (WEINBERGER, 1967) is the first method to synthesize boolean functions. In this method, a circuit containing only NOR logic are implemented in a NMOS matrix. In figure 2.4 it is possible to verify that this approach is very simple.

Figure 2.4: Weinberger matrix

Note in this example (figure 2.4) that the lines does not use all the space. The algorithm *left edge* is presented in (HASHIMOTO; STEVENS, 1971) in which the area of the circuit is reduced with a better utilization of the lines. Figure 2.5 shows the *left edge* algorithm applied to the example in figure 2.4.

Figure 2.5: Left edge algorithm applied to an Weinberger matrix

The *gate array* consists on using a set of prediffused cells in a matrix. Metal layers inserted in the layout define the logic function. In order to support different circumstances, the cells present transistors with width greater than the necessary. Thus, power consumption and timing performance problems can be found in this approach.

In the *standard cell* approach, cells stored in a library are used to generate the layout. Each cell is defined by a logic function and presents specific characteristics related to power consumption and timing.

The layout generation based on the standard cell approach is basically divided into two steps. First, the *placement* is performed in which the position of each cell is found in the layout surface. Once the placement is done, the routing of the cells can be performed. The main goal of the placement step is to reduce the congestion in order to guarantee the complete routing of the circuit.

The *gate matrix* (LOPEZ; LAW, 1980) is introduced as an approach to VLSI systems. In this method, complex gates are placed in vertical polysilicon lines with spaces used to connect the gate of transistors. Usually, the number of inputs of a gate defines the number of polysilicon columns. Figure 2.6 illustrates the gate matrix approach.

In (UEHARA; CLEEMPUT, 1981) it is proposed a technique called *linear matrix*. In this layout style, only 2 diffusion strips, one PMOS and one NMOS, are placed horizon-tally and the polysilicon lines are placed vertically over the diffusions in order to generate the transistors. The ordering of the transistors in the diffusion strips is also defined in (UE-HARA; CLEEMPUT, 1981) by the search of the *Euler Path* algorithm.

The main characteristics of the linear matrix style are:

- Used in static CMOS layouts;

- Implement series/parallel transistors;

- Dual P/N planes;

Figure 2.6: An example of gate matrix

- 2 diffusion strips to implement transistors;

- Transistors with the same gate signal are aligned.

Many algorithms are presented to increase the efficiency of this layout style. New algorithms for ordering transistors in the linear matrix are presented in (MAZIASZ; HAYES, 1987; WIMMER; PINTER; FELDMAN, 1987; WANG, 1989, 1990). These algorithms show techniques to improve better results with the relative position of the transistor inside the cells, decreasing the occupied area.

Algorithms for reduction of the rows height is presented in (ONG; LI; LO, 1989; MAZIASZ; HAYES, 1991; NAKAGAKI; YAMADA; FUKUNAGA, 1992). These algorithms try to optimize the area occupied by connections in the channel routing in order to reduce the area of the cells.

In (WANG, 1993) it is presented an alternative to the previous algorithms in which the power supply lines are placed between P and N diffusion strips. In this method, the routing is performed outside the row and connections between P and N nodes are implemented in metal 2.

Kaneko and Jialin present in (KANEKO; JIALIN, 1997) a concurrent cell generation and mapping for CMOS circuits. This approach includes the following problems:

- Generation of the transistor topology for a cell, which is done concurrently with cell assignment;

- Determination of each transistor size;

- Generation of physical layout of each cell.

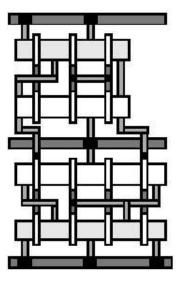

In (GUPTA; HAYES, 2000), it is presented a technique for the automatic generation of layouts of CMOS cells in the two-dimensional (2D) style. The technique, CLIP (Cell Layout via Integer Programming) is based on integer-linear programming and solves both width and height minimization problems for 2D cell.

Width minimization is formulated in form that combines factors influencing the 2D cell width in a common problem space: transistor placement, diffusion sharing and verti-

cal inter-row connections. This space is searched in a systematic manner by the branchand-bound algorithms used in ILP solvers. For height minimization, cell height is modeled based on the horizontal wire density.

The CLIP run time for width minimization is in seconds for circuits with 30 or more transistors. For both height and width optimization, the CLIP is practical for circuits with up to 20 transistors. To extend the algorithms to larger circuits, hierarchical methods are necessary.

(a) One-dimension layout

(b) Two-dimension layout

Figure 2.7: the CLIP layout style

Figure 2.7 shows an one-dimension layout in figure 2.7(a) and the same two-dimension layout in figure 2.7(b). It is important to note that the three routing horizontal tracks in the two-dimension layout are distributed in the two-dimensional layout.

A transistor level placement tool is presented in (DASH et al., 2000). The used technique divides large circuits into groups of strongly connected transistors. In the proposed algorithm, series connected transistors having the same substrate potential can be placed together to form chains of transistors called stacks and adjacent transistors in a stack share a common source/drain diffusion area.

Each stack represents a locally optimal placement of transistors. The width of each stack can also be controlled using transistors folding. The entire circuit can be broken up into stacks. In this work, the simulated annealing algorithm is used to place these stacks.

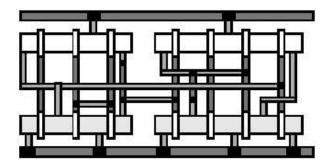

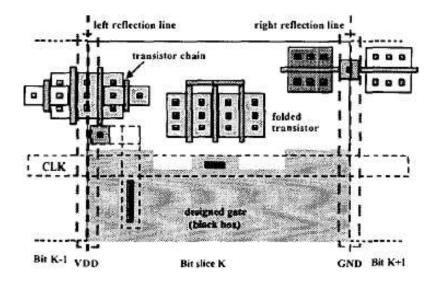

A datapath tile placement and routing at transistor level is presented in (SERDAR; SECHEN, 2001). In this work, there are two signal flows in the layouts. One is the data flow, which runs vertically along the power rails. The other is the control flow, which goes horizontally. Since a tile is replicated across an entire row, it is sufficient to optimize the area of a single tile at a time.

Figure 2.8: Possible placeable devices within a datapath tile

The placement process is divides into two steps: a global placement step using simulated annealing, and a detailed placement step based on extensive modifications using the O-tree algorithm. The proposed algorithm places the tiles mirrored. Thus, devices can be placed such that geometry sharing is possible between adjacent tiles in the datapath array. In figure 2.8 the transistor chain shares the diffusion contact in the left side and the single transistor shares the poly/metal1 contact in the right side.

As obtained results, it is presented four small circuits (10 to 70 transistors) generated by the proposed algorithm. It is important to note that these small circuits are used in big ones in order to generate real datapath circuits.

#### 2.4 Layout Generation at UFRGS Microelectronics Group

Many tools have been developed at the UFRGS microelectronics group (GME) for researching and developing new techniques related to the physical synthesis. Figure 2.9 shows the time line of tools developed at GME.

In (REIS, 1983) it is presented a research about control parts of microprocessors designed in the 70's. A new set of concepts is presented in (REIS, 1987) called TRANCA (TRANsparent-Cell Approach) methodology. The main goal of this methodology was

Figure 2.9: Time line of physical synthesis at GME

to use the knowledge acquired in the research of commercial layouts and to apply the techniques in automatic tools.

TRAMO (TRAnca MOdule) generator (LUBASZEWSKI, 1990) was the first developed system based on the TRANCA methodology. In this work, layouts were generated based on a library of cells.

In TRAGO (TRanca Automatic GeneratOr) (MORAES, 1990), synthesis was performed in such a way, layouts were automatically generated without cells library. The system used a description similar to a netlist spice to generate the layout.

Gate-array and sea-of-gates are examples of circuits generated by Marcela (GÜNTZEL; RIBAS; REIS, 1991; GÜNTZEL, 1993; GÜNTZEL et al., 1995) approach. In this approach, over-the-cell routing and track allocation is used to avoid routing congestion.

MARLA (GÜNTZEL et al., 1993) and MARTE (JOHANN; REIS, 1993) are tools to generate layouts based on the MARCELA approach. MARLA was responsible to generate the layout under a matrix and, MARTE was used to route the cells. The main characteristics of the circuits were the full over-the-cell (FOTC) routing.

The main goal of TRAMOII (REIS; REIS, 1991; REIS, 1993) was the layout generation of ICs in which cells are transparent to metal 1 and metal 2 connections. In TRAMO, only one metal layers was used.

In (MORAES, 1994) it is presented a tool called TROPIC (Transparent Reconfigurable Optimized Parametrizable Integrated Circuit generator) based on the concept of layout generation based on a transistors netlist. In this work, layouts can be generated onthe-fly based on design rules. Layouts generated by TROPIC were limited to technologies

35

with 2 metal layers.

TROPIC3 is presented in (MORAES; REIS; LIMA, 1997). In this work, 3 metal layers were used in the routing. This modification decreased up to 50% in the area between rows.

A tool for electric extraction of circuits generated by TROPIC was presented in (FER-REIRA; MORAES; REIS, 2000). It is possible to extract resistances, coupling capacitances and intrinsic capacitances by layouts of ICs.

WTROPIC (FRAGOSO, 2001) is presented as a tool to layout generation to be used via Internet. Besides, some optimizations are presented (in comparison of TROPIC3) in which the transistor density increase up to 4%.

#### 2.5 Conclusion

The complexity of the systems demand higher abstraction levels than a transistor description. Thus, the design of circuits can be developed in a high level description and optimized in the high, logic and physical level in order to meet the designer specifications.

At the physical level, three main options are available to designers according the synthesis strategy. The classic standard cell approach can be used in such a way elements stored in a library are placed and routed.

The layout can be generated fully automatic without using any library of cells in which the placement, the layout generation and the routing are performed in this sequence. As last option to layout generation, the full custom automatic layout generation can be done in which the layout generation is performed only when the routing is performed. This strategy offers to the layout generation some freedom concerning the routing process.

Tools have been used to automate the layout generation process since the 60's. Many strategies are proposed in the literature starting from the Weinberger matrix until the standard cell generation. At UFRGS microelectronics group, researches on full custom automatic layout generation have been developed in order to generate layouts similar to done manually.

# **3 OPTIMIZATION TECHNIQUES USED IN ASSOCIATION WITH LAYOUT GENERATION**

## 3.1 Introduction

The association with analysis techniques improves the efficiency of the layout generation. Logic optimization, timing analysis and power consumption estimate are examples of techniques essential for generating layouts able to be manufactured.

Logic optimization and its effects are reported in section 3.2. It is shown some techniques for logic optimization targeting reduction of power consumption and the importance of the technology to the layout generation.

In section 3.3 it is reported important aspects about critical paths in combinational and sequential circuits, path sensitization criteria and clock distribution techniques. Besides, clock tree synthesis and the concept of clock skew is also reported.

Techniques for timing optimization are presented in section 3.4. Cost models for area occupation and timing analysis are reported and techniques for gate sizing and buffer insertion are shown. In section 3.5 it is reported details about a gate sizing tool developed with the goal of resize circuits generated by automatic full custom generators.

## **3.2** Logic Optimization and Power Consumption Reduction

With the increased popularity of portable devices, battery size and lifetime are becoming important factors in the design time. At the same time, the amount of data to be processed is increasing at a rapid pace (IMAN; PEDRAN, 1996). These considerations have resulted in a growing need for minimizing power consumption in digital systems.

There are three main components of power consumption in digital CMOS VLSI circuit (SHAMS; BAYOUMI, 2000).

- 1. *Switching Power:* consumed in charging and discharging of the circuit capacitances during transistor switching;

- 2. *Short-Circuit Power:* consumed due to short-circuit current flowing from the power supply to ground during transistor switching;

- 3. *Static Power:* consume due to static and leakage currents flowing while the circuit is in a stable state.

In non-deep-submicrometer technologies, dynamic power consumption is the dominant source of power consumption. Moreover, the dominant source of power dissipation is due to capacitive currents because of the charging and discharging of the capacitances. Many works (ALIDINA et al., 1994; PRADHAN et al., 1996; IMAN; PEDRAN, 1996; WANG; VRUDHULA, 1996) related to power estimation and optimization use the following equation to approximate the average power dissipated by a gate:

$$P_{avg} = \frac{1}{2} \times v_{DD}^2 \times C_{load} \times f \times E(transitions)$$

(3.1)

where  $v_{DD}$  is the supply voltage,  $C_{load}$  is the load capacitance, f if the clock frequency and E(transitions) is the number of gate output transitions per global clock cycle.

However, high leakage current in deep-submicrometer regimes is becoming a significant contributor to power consumption of CMOS circuits when threshold voltage, channel length and gate oxide thickness are reduced (ROY; MUKHOPADHYAY; MEIMAND, 2003). Thus, the dynamic (switching) power can be estimated by the equation 3.1, but when the transistors are not switching, the power consumption is approximated by

$$P_{LEAK} = I_{LEAK} \times V_{DD}. \tag{3.2}$$

Figure 3.1: Ratio of static to dynamic power consumption

Figure 3.1 is presented in (SYLVESTER; KAUL, 2001). The figure illustrates the relative importance of static and dynamic power for an inverter driving a fan-out of four gates identical to the inverter. It is shown that for logic with switching activities on the order to 0.01 to 0.1, static power can approach and exceed 10% of dynamic power.

In (NGUYEN et al., 2003) it is emphasize that at a 90nm technology, leakage power may make up 42% of total power. The primary reason for this increase in leakage power is the reduction of threshold voltage of devices, and an exponential increase in leakage current that it causes.

Based on equations 3.1 and 3.2, it is possible to conclude that, at a circuit level, low power application can be obtained from two ways. Reducing the switching activity it is possible to reduce the dynamic power and modifying the logic of the circuit and, consequently, reducing the number of transistors to decrease the static power.

Many authors show that including additional logic in the circuit can reduce the switching activity. Logic optimization techniques are presented in (ALIDINA et al., 1994; MONTEIRO et al., 1995) which precomputation is used to selectively disable the inputs of a sequential logic circuit, thereby reducing switching activity and power dissipation.

In (WANG; VRUDHULA, 1996), it is presented a technique to reduce the switching activity based on local logic transformations. These transformations consist on adding redundant connections or gates to reduce the power consumption. The obtained results show an average decrease in the switching activity of 13% and the increase in delay up to 29%.

These techniques increase circuit area and can adversely impact circuit performance. It is clear that the additional logic inserted in the circuit reduces the switching activity but the static power is not reduced. On the contrary, the consumed power is increased by the additional logic.

Iman and Pedran present in (IMAN; PEDRAN, 1996) a framework for specifying and maintaining power relevant circuit information of low power circuits. This methodology uses simplification techniques to optimize the logic and uses a technology mapping to make area-power trade-off during logic optimization.

In all techniques targeting low power by logic optimization presented in this section, any of them explore the possibility to reduce the number of transistors by the utilization of logic function of complex gates. The reason is related to the library cell mapping in which a limited number of defined logic functions available to the logic synthesis.

Reis presents in (REIS et al., 1997) a method for mapping a set of boolean equations into a set of static CMOS complex gates (SCCG) under a constraint in the number of serial transistors. In this work, a tool called TABA is used to generate a virtual library of complex gates. The tool is able to optimize a circuit to a set of complex gates in which the number of transistors is reduced.

In a free library mapping as used in a full automatic layout generator it is possible to generate an optimized set of cells with reduced number of transistor in comparison of a standard cell mapping.

A given limitation in the number of serial transistors induces the number of complex functions available in the virtual library. In a logic mapping where the number of serial transistors is constrained to 4, the number of possible logic functions is 396 (DETJENS et al., 1987).

The library free mapping is very important because of the reduction of the number of transistors in a circuit in comparison with a library with restricted number of logic functions. Thus, the dynamic and static power consumption is reduced due to the utilization of a bigger set of complex gates.

## **3.3** Timing Verification

## 3.3.1 Critical Delay of Combinational Blocks

Many logic paths in combinational blocks do not require any conscious effort when it comes to speed. However, usually there are a number of paths that require attention to timing details (WESTE; ESRAGHIAN, 1993). These paths are called the *critical paths*.

There are many paths to a signal that cross a circuit according the gates and the connections among them. The critical path is the slowest path to a signal cross a circuit, starting at the terminal inputs (PIs) and arriving at one of the outputs (POs).

Figure 3.2: A simple critical path example

In figure 3.2 it is shown a simple example of the critical path. Consider the value at the output of each gate the delay of the gate. The critical path may starts in the inputs  $i_1$  or  $i_3$  and finishes in any output. The gates in the critical path may be  $g_3, g_4$  and  $g_6$  or  $g_3, g_4$  and  $g_7$ .

In a circuit, critical paths require attention to timing details. These may be recognized by experience or timing simulation, but most designer use a timing analyzer, which is a design tool that automatically finds the slowest paths in a logic design (WESTE; ES-RAGHIAN, 1993).

The critical path can be affected at four main levels:

- The architectural level

- The RTL/logic gate level

- The circuit level

- The layout level

In a high level implementation (architecture level), the knowledge of the algorithms that implement the function and chip parameter is required. Functions refer to how many gate delays fit in a clock cycle, how fast operation occurs or how fast memories access.

Timing optimization can be done in the RTL/logical level. In this level, pipelining, gate types (inverter, nand, etc), fan-in and fan-out are taken into account.

In the circuit level, sizing transistors or other technique to optimize the circuit can improve the critical speed path.

The speed of a circuit can be affected by rearranging the physical layout. At the layout level, placement and routing algorithms can modify the critical path in order to organize the layout in such a way that critical nets are routed with the minimum interconnect length between them.

Furthermore, only sensitizable paths contribute to the delay of a circuit. Thus, false paths must be excluded in optimizing the delay of the circuit. A sensitizable path is a path that can be activated by at least one input vector (LIN; HWANG, 1994).

## 3.3.1.1 Path Sensitization Criteria

Most of sensitization criteria are defined by topological parameters. Güntzel classifies the sentization criteria either as delay-dependent or delay-independent (GÜNTZEL, 2000). In delay-independent criteria, only logic values are considered while in a delaydependent, the time such signals become stables are also considered.

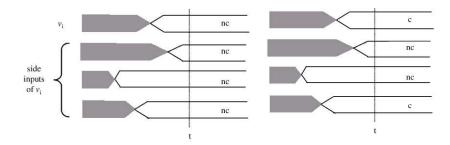

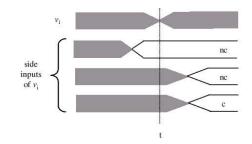

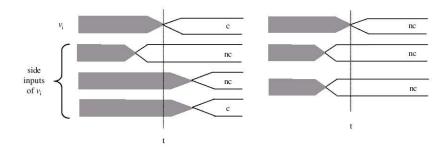

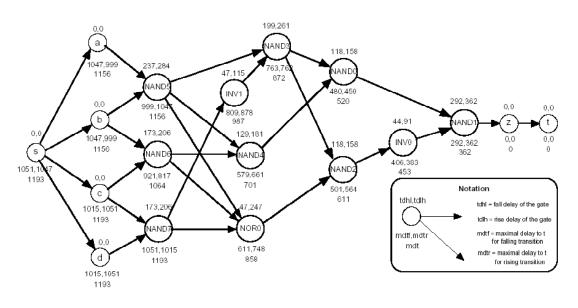

In addition, Güntzel presents four sensitization criteria in the context of the floating mode. Figure 3.3 shows the reported criteria.

## Static Sensitization

Static sensitization is a delay-independent criterion. It was one of the first sets of sensitization conditions used in timing analysis. When pairs of vectors assume the delay (i.e. transition mode), it corresponds as the concept of sensitization in the propagation of error signals in stuck fault test generation. Static sensitization is defined by:

**Definition 3.1** A path P is said to **statically sensitizable** if and only if there is at least one input vector w such as for each  $v_i$ ,  $1 \le i \le n$ , each side-input of  $v_i$  settles to  $nc(v_i)$  under w.

Figure 3.3(a) shows the condition for static sensitization.

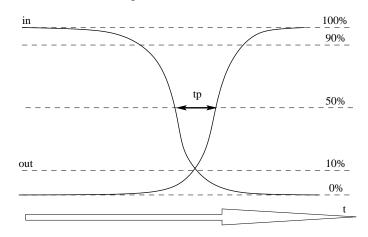

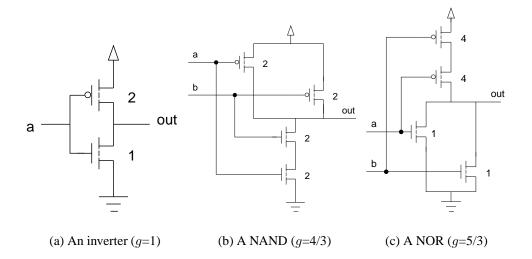

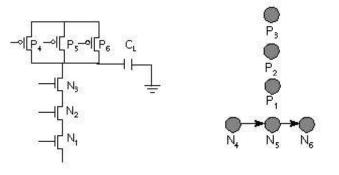

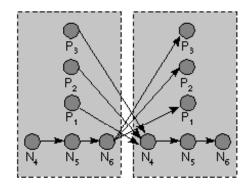

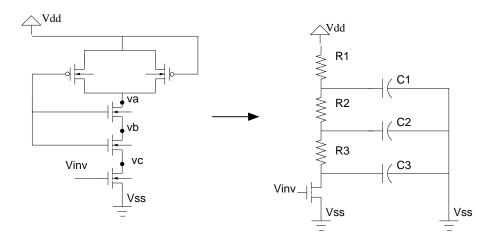

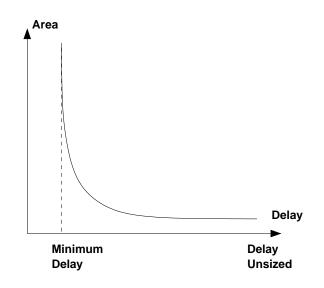

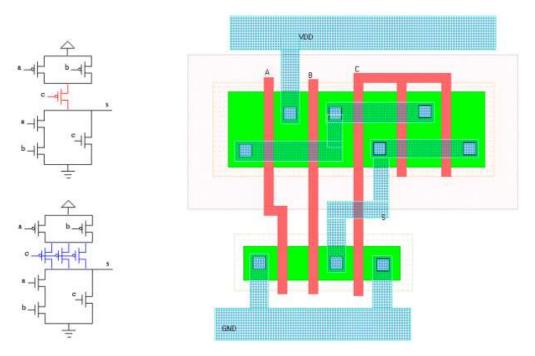

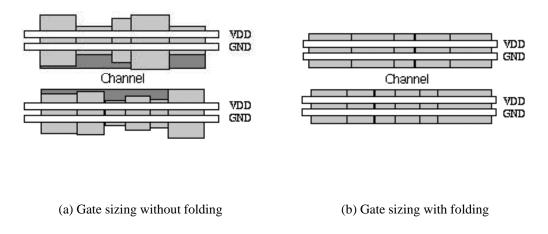

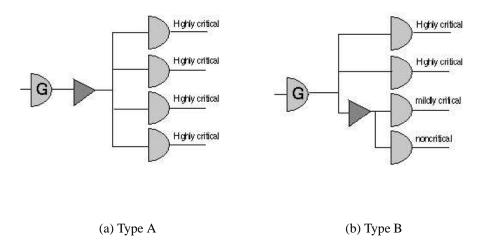

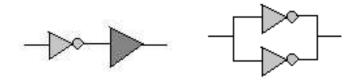

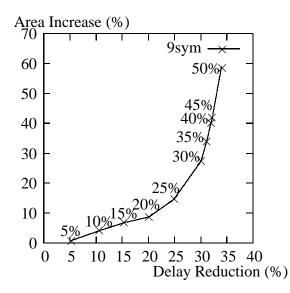

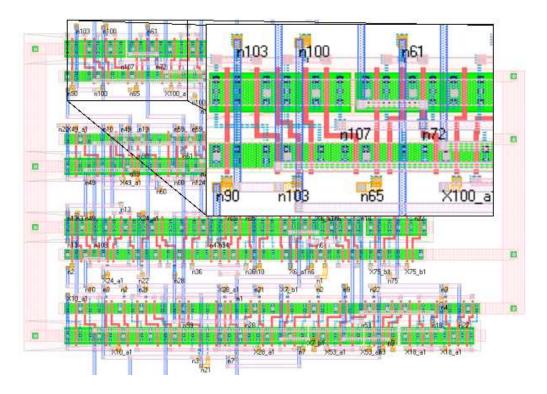

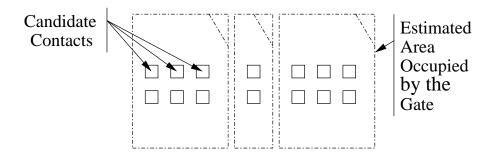

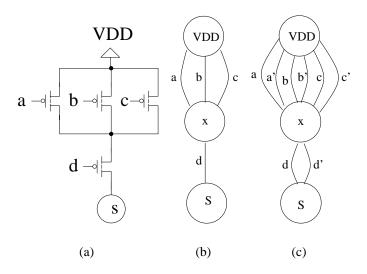

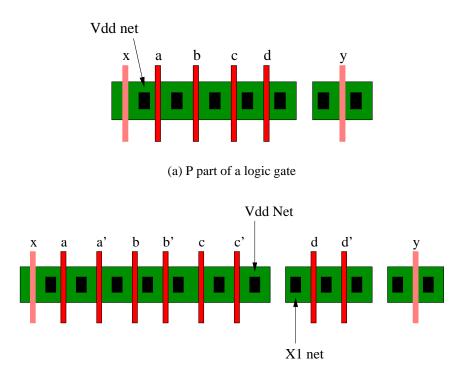

#### Static Cosensitization