### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMATICA PROGRAMA DE POS GRADUACAO EM COMPUTACAO

#### FERNANDA GUSMÃO DE LIMA KASTENSMIDT

Designing Single Event Upset Mitigation Techniques for Large SRAM-Based FPGA Components

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Computer Science

Prof. Dr. Ricardo Augusto da Luz Reis Advisor

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Kastensmidt, Fernanda Gusmão de Lima

Designing Single Event Upset Mitigation Techniques for Large SRAM-Based FPGA Components / Fernanda Gusmão de Lima Kastensmidt. – Porto Alegre: PPGC da UFRGS, 2003.

157 f.: il.

Thesis (Ph.D) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2003. Advisor: Ricardo Reis

1. Técnicas de tolerância a falhas. 2. Circuitos programáveis customizado por SRAM. 3. Falhas transientes e permanentes. 4. Injeção de falhas. 5. Efeitos da radiação em FPGA. 6. SEU mitigation techniques. 7. FPGA. I. Reis, Ricardo. II. Título.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitora: Prof<sup>a</sup>. Wrana Maria Panizzi

Pró-Reitor de Ensino: Prof. José Carlos Ferraz Hennemann Pró-Reitora Adjunta de Pós-Graduação: Profa. Jocélia Grazia

Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux

Coordenador do PPGC: Prof. Carlos Alberto Heuser

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **ACKNOWLEDGMENT**

I am very grateful to all of you that have been with me all my life: my family, my friends and my colleagues. Every person that I know is important to me and each one has shared something that has made a difference. Everyday when I make decisions, I know that each one has contributed in some way to these choices and I am sure that my life is so wonderful because of that.

First I would like to thank God for the wonderful life that I have. Thank you God for keeping up my courage and enthusiasm every day. I would like to thank my family that always looks after me. I want especially to thank you mom, Ana Maria, and dad, Luiz Fernando, for supporting me and for giving me all the best of your heart. For all that I have conquered in my life so far, I need to thank you both. I would like to thank you, my lovely husband Christopher, for supporting me in my last year of the thesis, encouraging me every day. My friends were all present in my life as well, giving me assistance to get through the difficulties. I want to thank you, all of you, for making my life so happy and full of emotion.

I am very grateful to my first professor that has shown to me how to work in a computer and to write my first lines in code when I was still a little child, Professor Magda Bercht. Thank you very much; you have raised on me the interest on working in computers. I want to thank you all my professors that have helped me since I started in the GME in 1994. I learned a lot with all of you in all stages of the research. I am sure that my work today has something from all the work that we have done together since the beginning. You are more than my instructors, you are my friends. Some of them I want to thank more explicitly for the constant support in this thesis in the past few years. I want to thank Professor Ricardo Reis, who has been my advisor since I started in the GME in 1994 for the constant and infinite support in my studies. Thank you very much, Professor Reis, for always trusting me and encouraging me every moment, in every new challenge. Thank you for always show to me new opportunities and help me to get them. I want also to thank Professor Luigi Carro for inviting me to work on the 8051 micro-controller again. Many years after we first worked together on the 8051 architecture, I had the chance to perform this investigation on the 8051 architecture, protecting against radiation. This work has opened new doors for me for which I am very grateful. Thank you, Luigi, for supporting me and for encouraging me every moment in the studies too. You are always present to help me in my work, to discuss new ideas and to guide me into new investigations. I want to thank Professor Marcelo Lubaszewski that has also support me in my work, since the first project in the electric engineer using the micro-controller 8051 to automatic recognize the position of an object in the tray. Thank you for all the discussions in fault tolerance. I want to thank all undergraduate students that worked with me in some moments of thesis, in particular, Gustavo Neuberger, who has done an outstanding research and helped me a lot in the last two year of work.

I also want to thank the researcher Raoul Velazco from the laboratory TIMA in Grenoble for the constant support. The internship that I did in his lab for 6 months was very important for my studies and for my personal life too. I was very pleased for that opportunity. During that period I had the chance to work in state of the art research related to radiation effects, SEU mitigation techniques and fault injection in digital circuits. There I also had a chance to meet great colleagues and friends. I also want to thank all my colleagues from Xilinx in the USA, where I also had the opportunity to be an intern for 11 months. There I had the chance to work with state of the art products and developments related to FPGAs and to meet wonderful friends. I want to give special thanks to Joe Fabula, Rick Padovani and Carl Carmichael for helping me during all those months and for always giving me confidence at work. This internship was fundamental for my thesis work and it was an immense experience for my personal life too.

Finally, I want to thank the wonderful institution Universidade Federal do Rio Grande do Sul, Escola de Engenharia and Instituto de Informática for provide me the opportunity to study since the electrical engineer course, the master degree in computer science and now the Ph.D. I am also very grateful to the Brazilian research agency CNPq that has helped me with a grant for all these past years and supporting me to attend and to present papers at conferences, which were very important to increase my knowledge and to help the state-of-the-art research.

# **CONTENTS**

| LIS            | T OF ABBREVIATIONS                                                                                    | 7        |

|----------------|-------------------------------------------------------------------------------------------------------|----------|

| LIS            | T OF FIGURES                                                                                          | 8        |

| LIS            | T OF TABLESERROR! BOOKMARK NOT DEFIN                                                                  | ED.      |

| AB             | STRACT                                                                                                | 13       |

| RES            | SUMO                                                                                                  | 14       |

| 1              | INTRODUCTION                                                                                          | 15       |

| 2              | SPACE ENVIRONMENT AND RADIATION EFFECTS                                                               |          |

| 2.1 E<br>2.2 P | Effect of SET and SEU in Integrated CircuitsPeculiar Effect of SET and SEU in SRAM-based FPGA Devices | 26<br>29 |

| 3              | STATE-OF-THE-ART OF SET AND SEU MITIGATION TECHNIQUES                                                 |          |

|                | Design-based Techniques to Detect and Mitigate SET and SEU                                            |          |

|                | Mitigation Techniques                                                                                 |          |

|                | Examples of SET and SEU Mitigation Techniques in ASICs                                                |          |

| 3.3 E          | Examples of SEU Mitigation and Recovery Techniques in FPGAs                                           | 59       |

|                | Anti-fuse based FPGAs                                                                                 |          |

| 3.3.2          | 2 SRAM-based FPGAs                                                                                    | 62       |

| 4              | ARCHITECTURAL SET AND SEU MITIGATION TECHNIQUES FOR SRAM-BASED FPGAS                                  | 69       |

|                | Proposing a SET and SEU Tolerant SRAM-based FPGA                                                      | 70       |

|                | Technique based on Hardened Memory Cells to replace the SRAM cells in the Routing,                    |          |

|                | tomization and Lookup tables                                                                          |          |

|                | Fechnique based on Error Correction and Detection Codes (EDAC) for the Embedded Men                   |          |

|                | Fechnique based on Logic Redundancy for the CLBs flip-flops                                           |          |

| 5              | HIGH-LEVEL SEU MITIGATION TECHNIQUES FOR SRAM-BASED                                                   |          |

|                | FPGAS                                                                                                 | 78       |

|                | Friple Modular Redundancy Technique for FPGA                                                          |          |

|                |                                                                                                       |          |

| 6 EVALUATING THE ROBUSTNESS OF THE TMR TECHNIQUE INT                                                                                                 |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1 Test Design Methodology                                                                                                                          | 87  |

| 6.2 Fault Injection in the FPGA Bitstream                                                                                                            | 88  |

| 6.3 Locating the upset in the design floorplanning                                                                                                   |     |

| 6.3.1 Bit column location in the matrix                                                                                                              |     |

| 6.3.2 Bit row location in the matrix                                                                                                                 |     |

| 6.3.3 Bit location in the CLB                                                                                                                        |     |

| 6.3.4 Bit Classification                                                                                                                             |     |

| 6.4 Fault Injection Results                                                                                                                          |     |

| 6.5 The "Golden" Chip Approach                                                                                                                       | 97  |

| 7 DESIGNING AND TESTING A TMR MICRO-CONTROLLER INTO VIRTEX® FPGA                                                                                     | 98  |

| 7.1 Area and Performance Results                                                                                                                     |     |

| 7.2 TMR 8051 Micro-controller Radiation Ground Test Results                                                                                          |     |

| 7.3 Final Remarks                                                                                                                                    |     |

| 8 REDUCING TMR OVERHEADS BY COMBINING HARDWARE AN                                                                                                    |     |

| TIME REDUNDANCY                                                                                                                                      |     |

| 8.1 Duplication with comparison combined with time redundancy                                                                                        |     |

| 8.2 Fault Injection in the VHDL Description                                                                                                          |     |

| 8.3 Final Remarks                                                                                                                                    |     |

| 9 IMPROVING DUPLICATION WITH COMPARISON BY USING                                                                                                     | 110 |

| CONCURRENT ERROR DETECTION TECHNIQUE (DWC-CED)                                                                                                       |     |

| 9.1 Designing DWC-CED Technique in Arithmetic-based Circuits                                                                                         |     |

| 9.1.1 Using CED based on hardware redundancy                                                                                                         |     |

| 9.1.2 Using CED based on time redundancy                                                                                                             |     |

| 9.2 Choosing the appropriated CED block for Arithmetic-based Circuits                                                                                |     |

| 9.2.1 Multipliers                                                                                                                                    |     |

| 9.2.2 Arithmetic and Logic Unit (ALU)                                                                                                                |     |

| 9.2.3 Digital FIR Filter                                                                                                                             |     |

| 9.3 Fault Coverage Results of the DWC-CED in Arithmetic-based Circuits                                                                               |     |

| 9.4 Area and Performance Results of the DWC-CED Technique in Arithmetic-based Circu 9.5 Designing DWC-CED Technique in Non-Arithmetic-based Circuits |     |

| 9.5 Designing DWC-CED Technique in Non-Arithmetic-based Circuits                                                                                     | 138 |

| 10 CONCLUSIONS                                                                                                                                       | 141 |

| REFERENCES                                                                                                                                           | 145 |

# LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuits

BRAM Embedded Memory

CED Concurrent Error Detection

CLB Complex Logic Block

CMOS Complementary Metal-Oxide Silicon

COTS Commercial-Off-The-Shelf DMR Dual Modular Redundancy DSP Digital Signal Processing

EDAC Error Correction and Detection Codes FPGA Field Programmable Gate Array

IC Integrated Circuits

LET Linear Energy Transfer

LUT Lookup Table

MBU Multiple Bit Upset

NRE Non-Recurring Engineer Cost

RS Code

SEE

Single Event Effect

SET

Single Event Transient

SEU

Single Event Upset

SOC

System on a Chip

SOI

Silicon on Insulator

SRAM Static Random Access Memory

TMR Triple Modular Redundancy

VDSM Very Deep Submicron

# **LIST OF FIGURES**

| Figure 1.1:  | Design evolution using FPGA                                            | .17 |

|--------------|------------------------------------------------------------------------|-----|

| Figure 1.2:  | Actual architecture generation of commercial field programmable gate   |     |

|              | arrays                                                                 |     |

| Figure 1.3:  | Design flow of how to protect a digital circuit implemented in a Sram- |     |

|              | based FPGA                                                             | .19 |

| Figure 2.1:  | Charged particle striking the silicon surface                          | .23 |

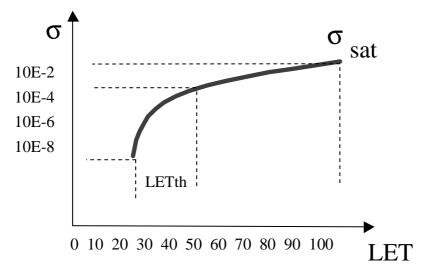

| Figure 2.2:  | An example of cross-section per LET curve                              |     |

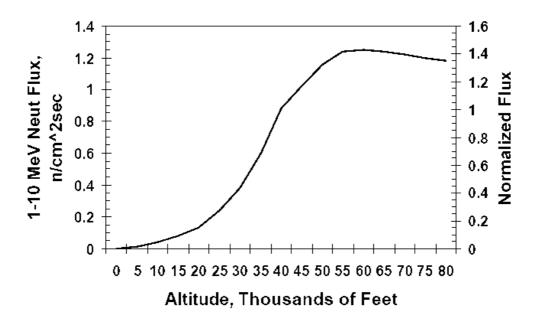

| Figure 2.3:  | 1-10 Mev atmospheric neutron flux vs. altitude, simplified boeing      |     |

| C            | model                                                                  |     |

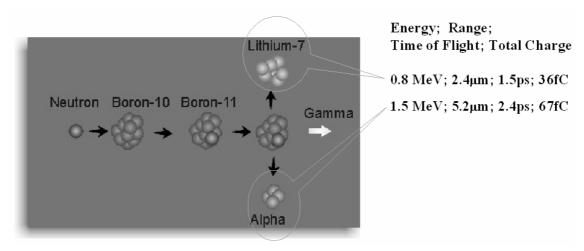

| Figure 2.4:  | Neutron reaction                                                       |     |

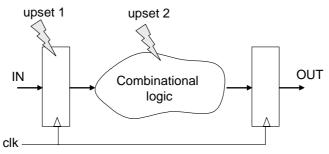

| Figure 2.5:  | Upsets Hitting combination and sequential logic                        | .26 |

| Figure 2.6:  | Single Event Upset (SEU) effect in a SRAM memory cell                  |     |

| Figure 2.7:  | Single Event Transient (SET) effect in combinational logic             |     |

| Figure 2.8:  | MBU provoked by a single particle                                      |     |

| Figure 2.9:  | • • • •                                                                |     |

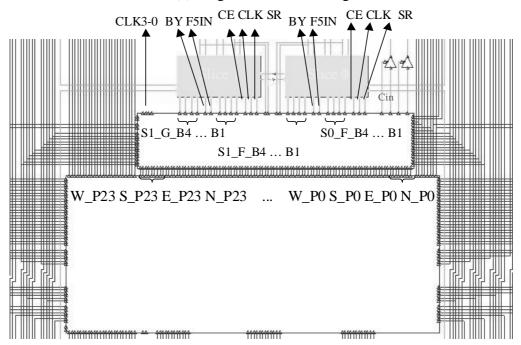

| _            | Virtex CLB tile schematic                                              |     |

| Figure 2.11: | Slice overview in the virtex CLB                                       | .31 |

| -            | 4-Input LUT schematic                                                  |     |

| _            | LUT configuration examples                                             |     |

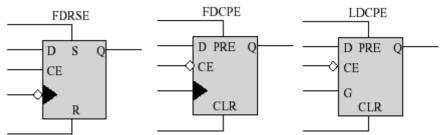

|              | Examples of CLB flip-flop configuration                                |     |

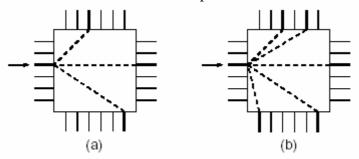

|              | Two examples of switch matrices with a different flexibility (a) fs=3  |     |

| C            | (b) fs=5                                                               |     |

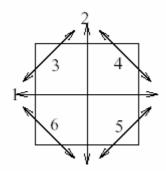

| Figure 2.16: | Direction of the connections in a switch matrix (W=6)                  | .34 |

| _            | Routing Switch connections                                             |     |

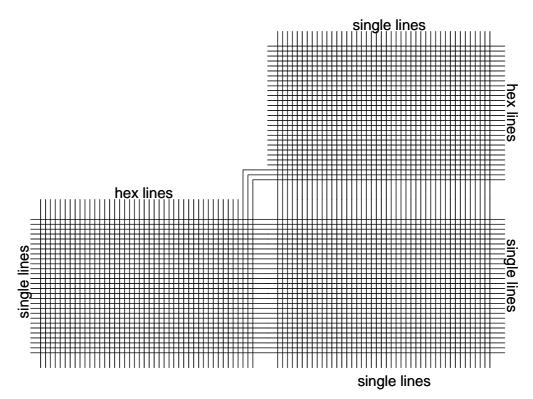

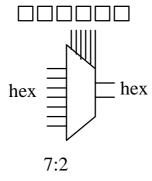

|              | Switch matrix connects the single and hex segments                     |     |

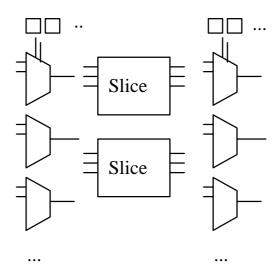

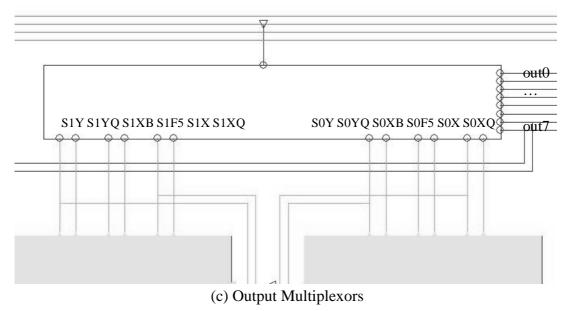

|              | Input And output multiplexors in the routing                           |     |

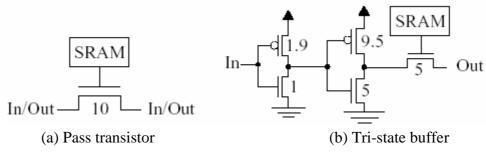

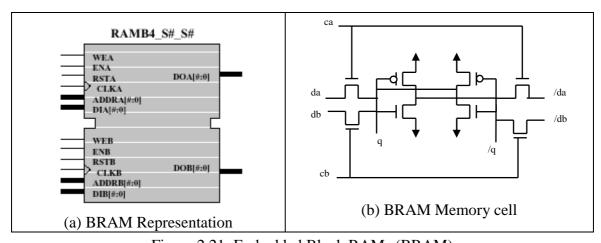

|              | Embedded block RAMs (BRAM)                                             |     |

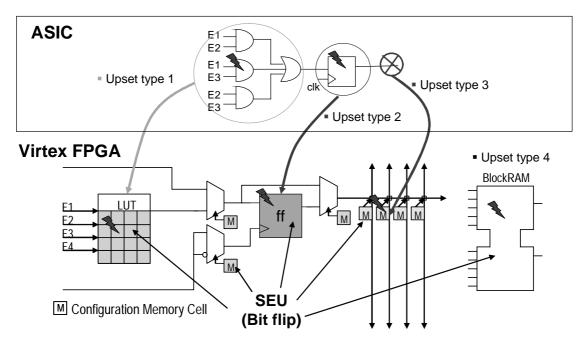

| _            | The comparison of the effects of a SEU in ASIC and FPGA                |     |

| C            | architecture                                                           |     |

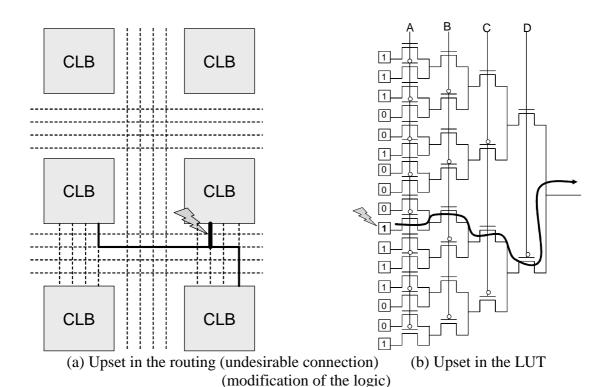

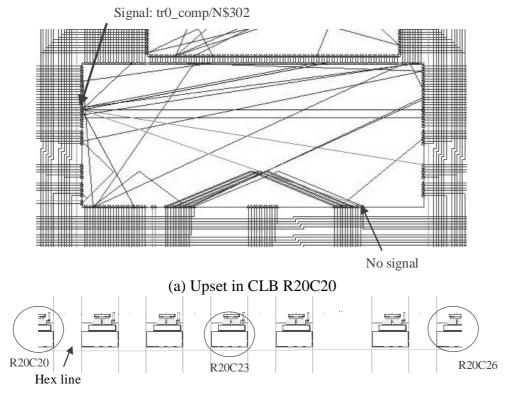

| Figure 2.23: | Examples of upsets in the SRAM-based FPGA architecture                 |     |

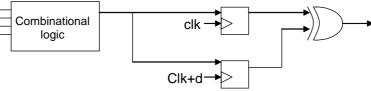

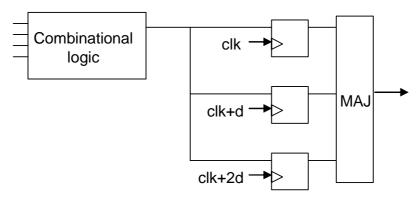

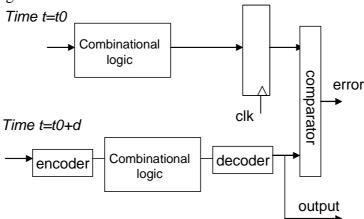

| Figure 3.1:  | Time redundancy duplication scheme to detect set in combinational      |     |

| C            | logic                                                                  |     |

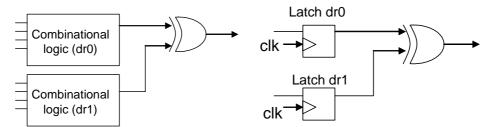

| Figure 3.2:  | Hardware redundancy duplication scheme to detect set in                |     |

| C            | combinational logic and seu in sequential logic                        |     |

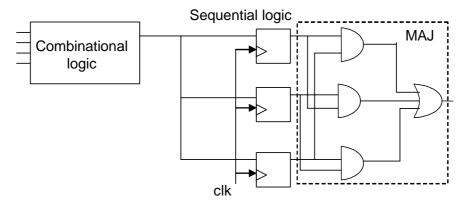

| Figure 3.3:  | Full time redundancy scheme to correct set in combinational logic      |     |

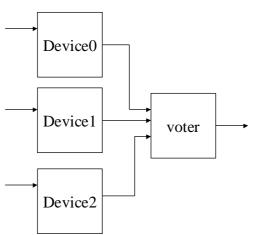

| Figure 3.4:  | TMR implemented in the entire device                                   |     |

| Figure 3.5:  | TMR memory cell with single voter                                      |     |

| Figure 3.6:  | TMR memory cell with three voters and refreshing                       |     |

| Figure 3.7:    | Full time redundancy scheme for combinational logic combined to full    |     |

|----------------|-------------------------------------------------------------------------|-----|

|                | hardware redundancy in the sequential logic                             | 44  |

| Figure 3.8:    | Full Hardware redundancy (TMR) scheme for combinational and             |     |

|                | sequential logic                                                        | 44  |

| Figure 3.9:    | Duplication and time redundancy to mitigate set in combinational        |     |

|                | logic                                                                   | 45  |

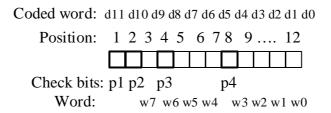

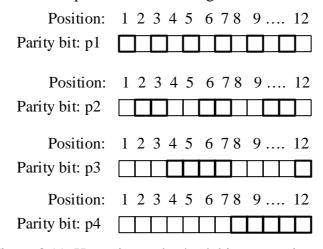

| Figure 3.10:   | Hamming code 12-bit word and the check bits                             | 46  |

| Figure 3.11:   | Hamming code check bits generation                                      | 46  |

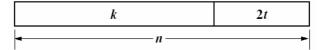

| Figure 3.12:   | Reed-Solomon coded word                                                 | 48  |

| Figure 3.13:   | Examples of double bit flips in a memory where each row is protected    |     |

| _              | by RS code                                                              | 48  |

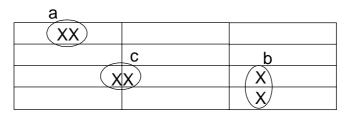

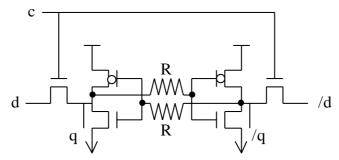

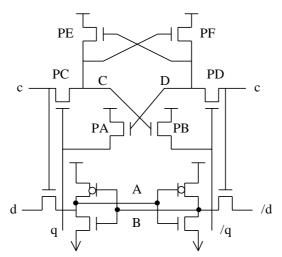

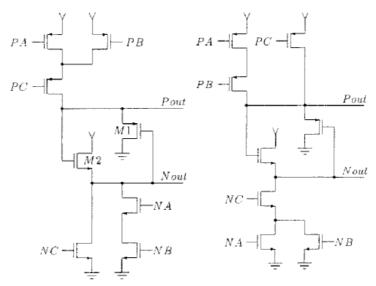

| Figure 3.15:   | Resistor hardened memory cell                                           | 49  |

|                | IBM hardened memory cell                                                |     |

| •              | HIT hardened memory cell                                                |     |

| -              | Canaris hardened memory cell                                            |     |

| •              | DICE hardened memory cell                                               |     |

| •              | NASA I hardened memory cell                                             |     |

| •              | NASA II hardened memory cell                                            |     |

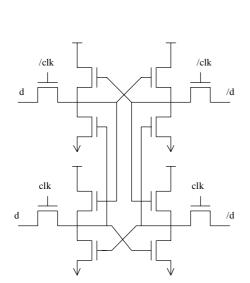

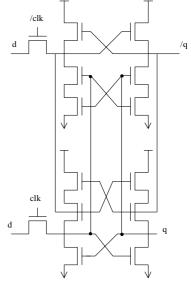

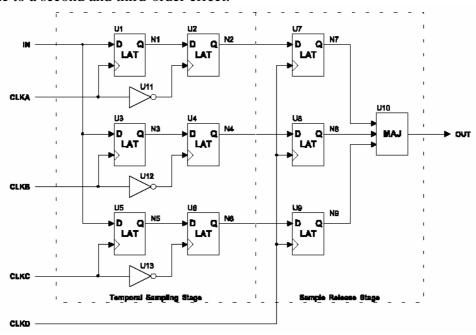

| _              | Temporal sampling latch with sample and release stages                  |     |

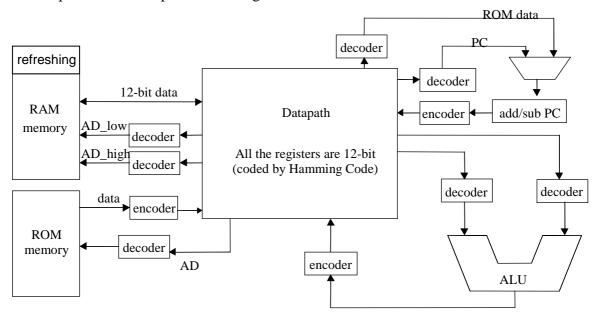

|                | General scheme of the SEU hardened 8051                                 |     |

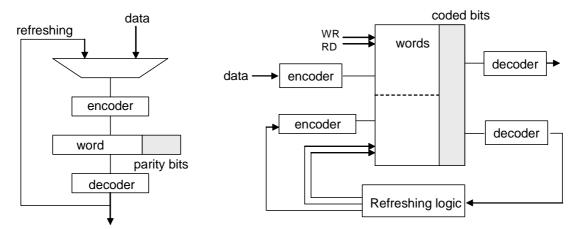

| •              | Scheme of the hamming code implemented in the memory and                |     |

| 1 15010 3.2 1. | registers of the 8051-like micro-controller                             |     |

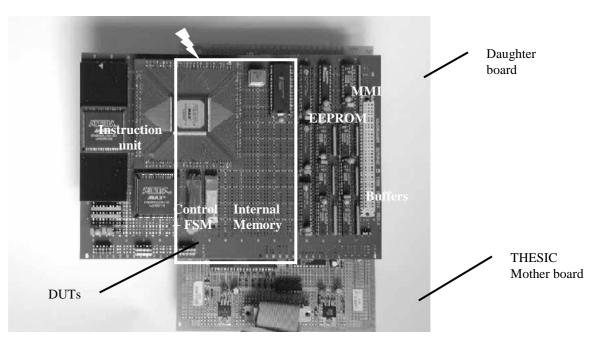

| Figure 3.25.   | SEU Hardened 8051 daughter board and thesic mother board                |     |

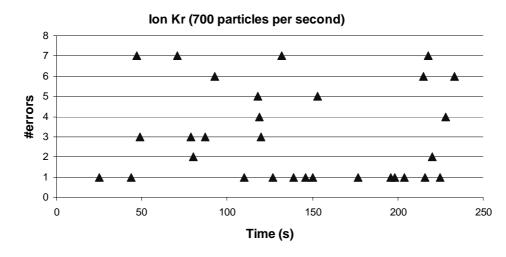

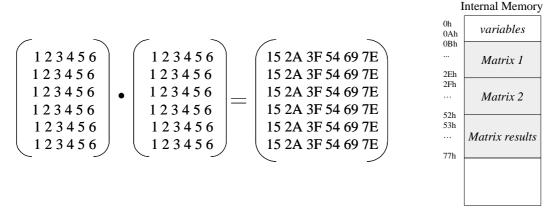

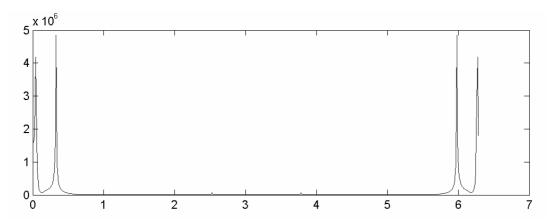

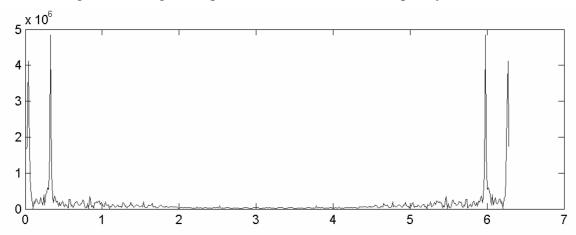

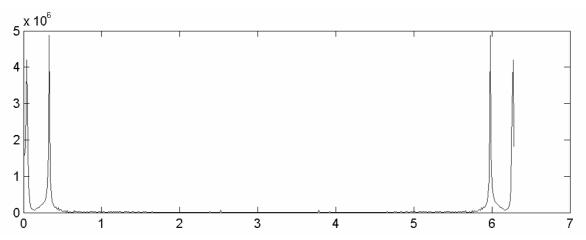

|                | Radiation test result i of the "not protected" 8051 in the matrix       |     |

| 1 1guic 5.20.  | multiplication test                                                     |     |

| Figure 3.27:   | Architecture of Actel FPGAs                                             |     |

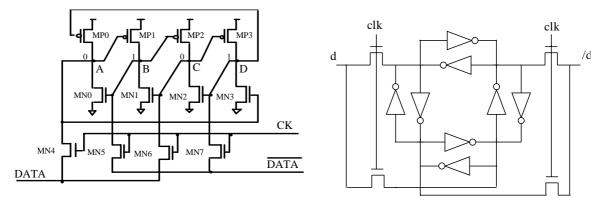

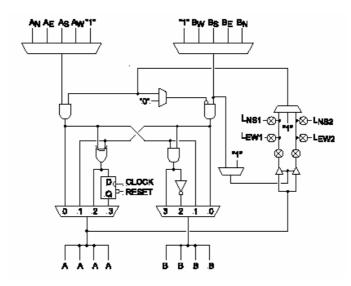

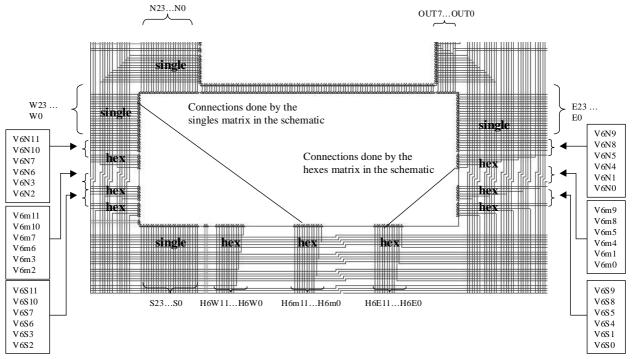

| Figure 3.28:   | Multistage interconnection network (min) in a Xilinx FPGA               | 63  |

| Figure 3.29:   | Atmel FPGA logic block                                                  | 65  |

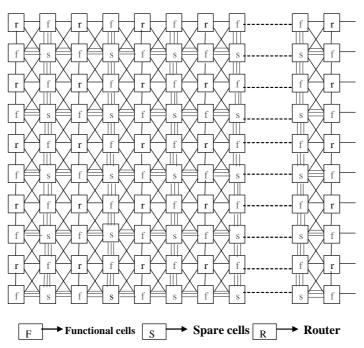

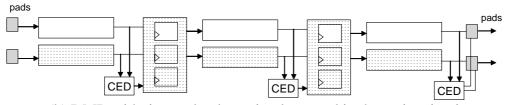

| Figure 3.30:   | Example of SRAM-based FPGA matrix                                       | 65  |

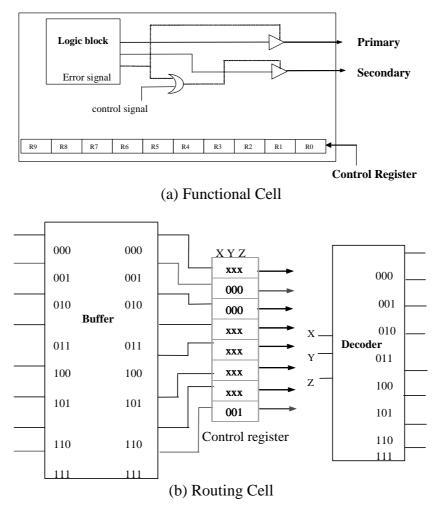

| Figure 3.31:   | Example of functional cell and routing cell                             | 66  |

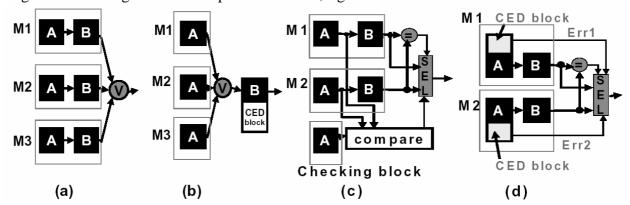

| Figure 3.32:   | Design candidates modified from tmr. (a) the original tmr design. (b) a |     |

| C              | hybrid tmr-simplex-ced design. (c) a duplex system with a checking      |     |

|                | block. (d) a duplex system with two ced blocks (yu; mccluskey, 2001)    | 67  |

| Figure 4.1:    | A Case of Study: hypothetical FPGA architecture                         | 69  |

| Figure 4.2:    | Special features elements in the SRAM-based FPGA matrix                 |     |

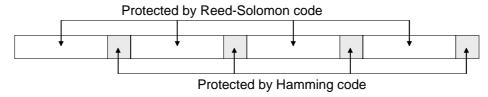

| Figure 4.3:    | Schematic of a memory row protected by Reed-Solomon and                 |     |

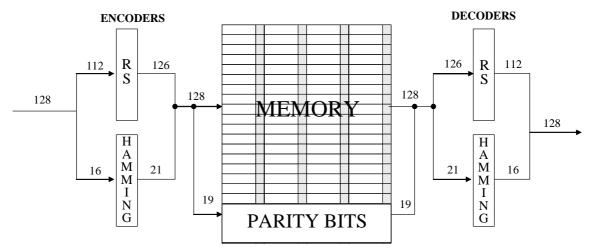

| C              | hamming code                                                            | 75  |

| Figure 4.4:    | Schematic of a memory row protected by Reed-Solomon and                 |     |

| C              | hamming code                                                            | 75  |

| Figure 4.5:    | Hamming and RS code in memory architecture                              |     |

| Figure 4.6:    | Proposed SEU and SET hardened flip-flop with refreshing                 |     |

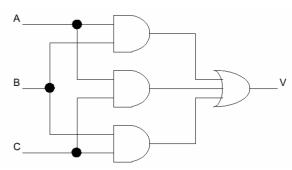

| Figure 5.1:    | TMR logic with voter                                                    |     |

| Figure 5.2:    | Majority voters                                                         |     |

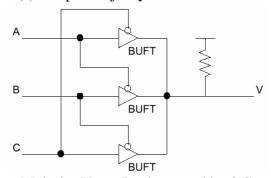

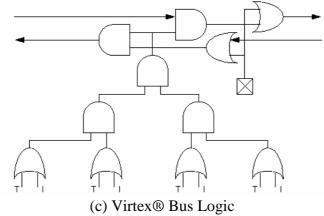

| Figure 5.3:    | Majority voter in the virtex <sup>®</sup> output logic                  | 81  |

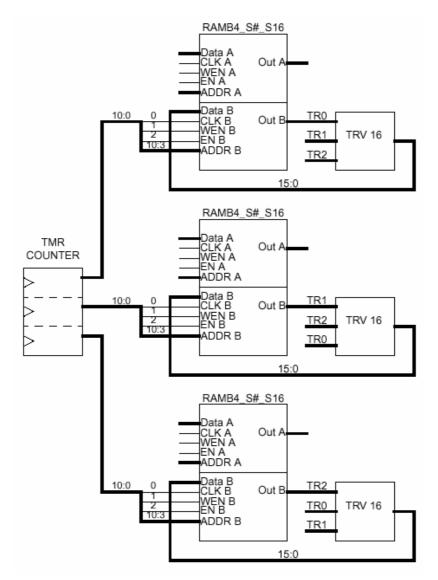

| Figure 5.4:    | BRAM TMR with refreshing.                                               |     |

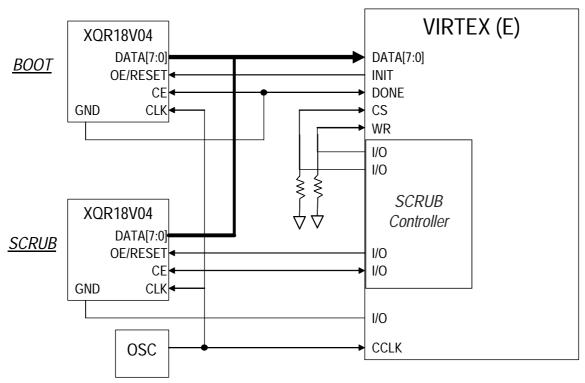

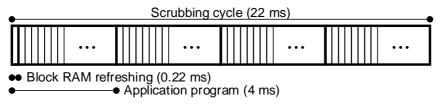

| Figure 5.5:    | Scrubbing configuration scheme                                          |     |

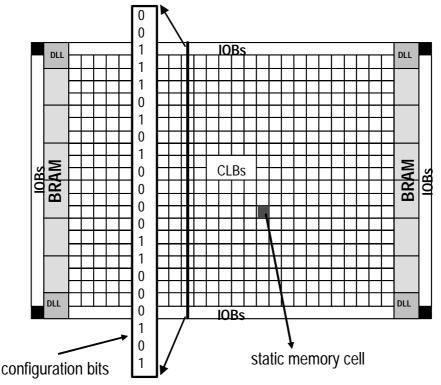

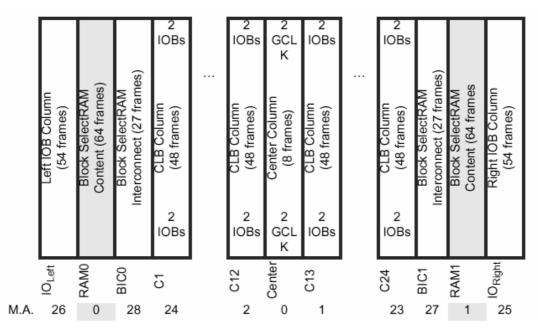

| Figure 6.1:    | Virtex® architecture overview                                           |     |

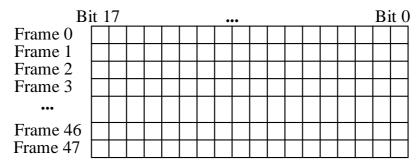

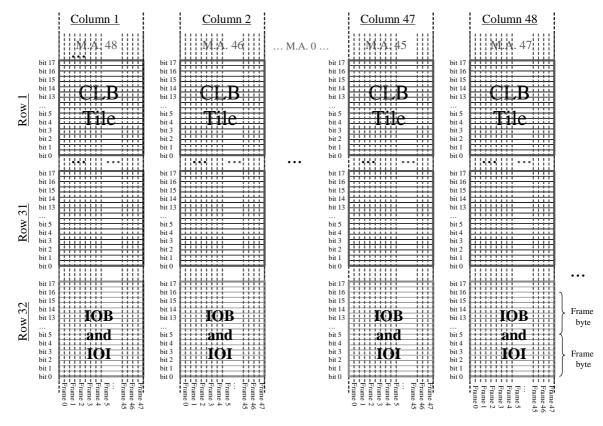

| Figure 6.2:    | CLB tile map                                                            |     |

| Figure 6.3:    | Matrix frame organization map                                           |     |

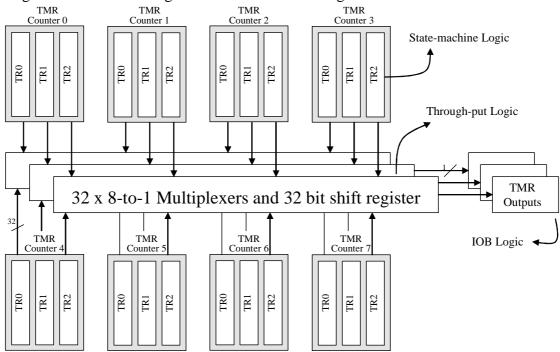

| Figure 6.4:    | TMR design of a 32-bit pipelined counter                                | 87  |

| -0             |                                                                         | - ' |

| Figure 6.5:  | TMR design methodology                                                  | 88    |

|--------------|-------------------------------------------------------------------------|-------|

| Figure 6.6:  | SEU test platform                                                       |       |

| Figure 6.7:  | Example of frame organization in Virtex® Family                         | 90    |

| Figure 6.8:  | Example of design connection file (.ncd)                                | 92    |

| Figure 6.9:  | CLB tile representation in the ISE floorplanning tool from Xilinx       | 94    |

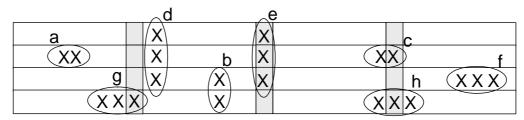

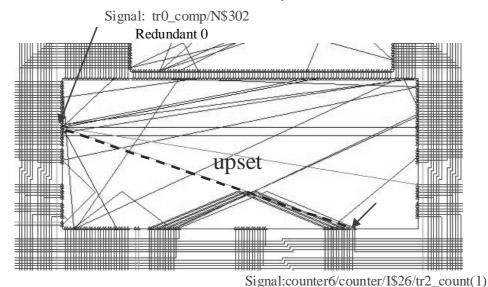

| Figure 6.10: | SEU example in the GRM user's design floorplanning                      | 95    |

| Figure 6.11: | Example of effect of a SEU in the FPGA routing                          | 96    |

| Figure 6.12: | "Golden" chip method                                                    | 97    |

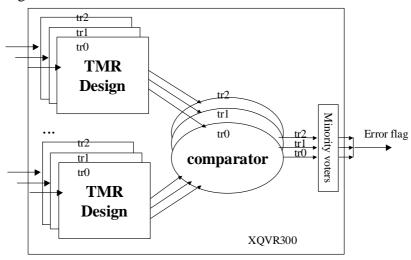

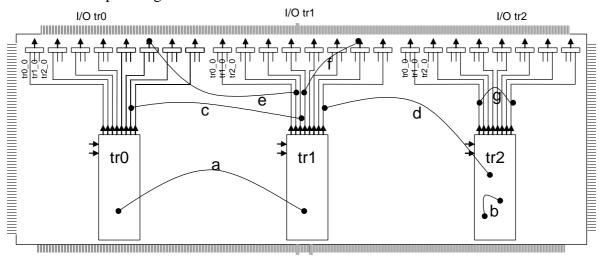

| Figure 7.1:  | TMR 8051 design methodology                                             | 99    |

| Figure 7.2:  | Example of TMR vhdl code                                                |       |

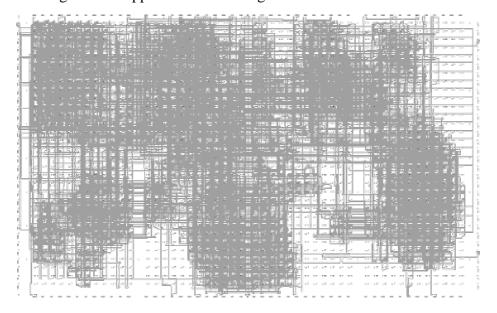

| Figure 7.4:  | TMR 8051 Micro-controller routing floorplanning                         | 101   |

| Figure 7.5:  | Testing platform                                                        |       |

| Figure 7.6:  | Scrubbing and refreshing times                                          | 103   |

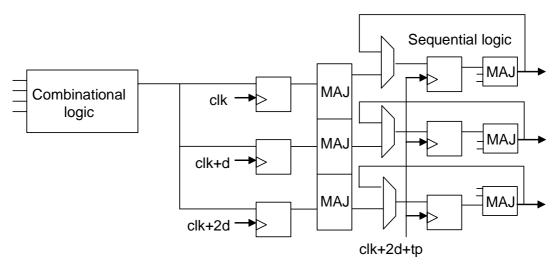

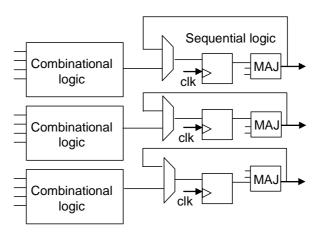

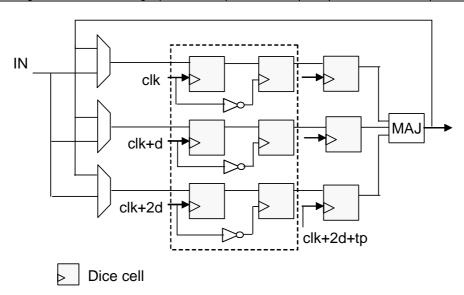

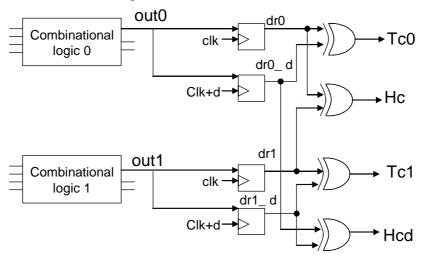

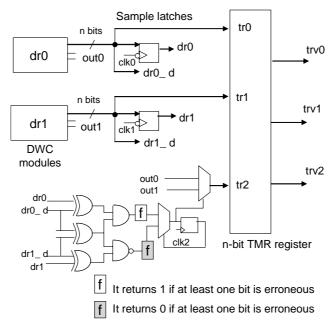

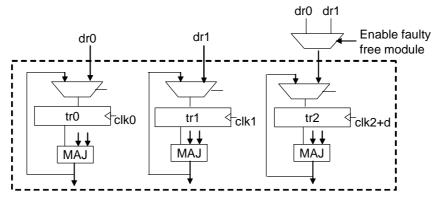

| Figure 8.1:  | Time and hardware redundancy schematic for upset detection              | 106   |

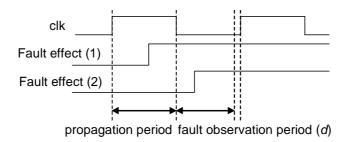

| Figure 8.3:  | Fault effect in the clock period                                        | 108   |

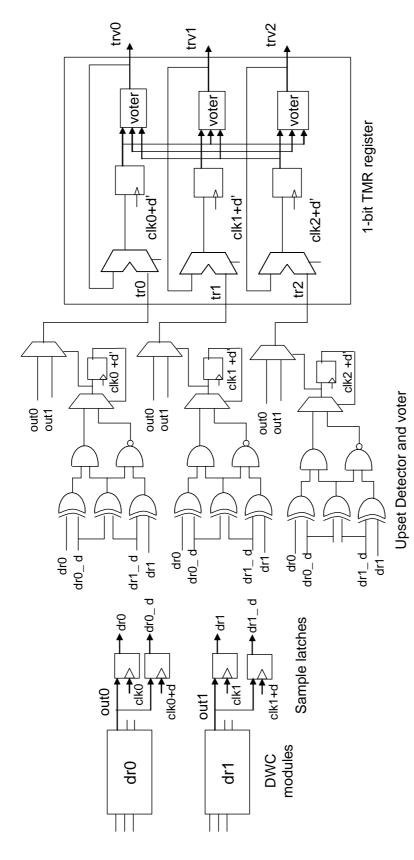

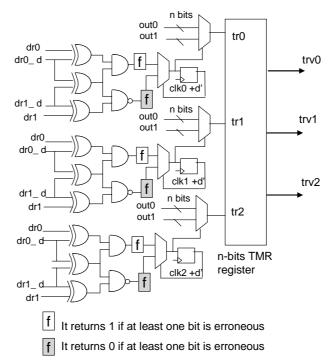

| Figure 8.2:  | DWC with time redundancy proposed technique scheme for one be           | it    |

|              | output                                                                  | 109   |

| Figure 8.4:  | Upset detector and voter circuit area optimization using group of       | n     |

|              | bits                                                                    |       |

| Figure 8.5:  | Upset detector and voter circuit area optimization using a single stat  | e     |

|              | machine for a group of n bits                                           | 111   |

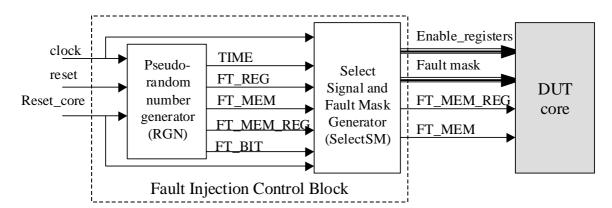

| Figure 8.6:  | Schematic of the fault injection generator block                        | 112   |

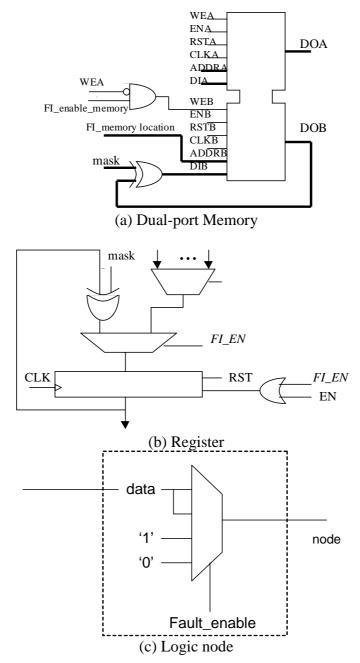

| Figure 8.7:  | Example of the mechanisms used to inject faults in the design           | 113   |

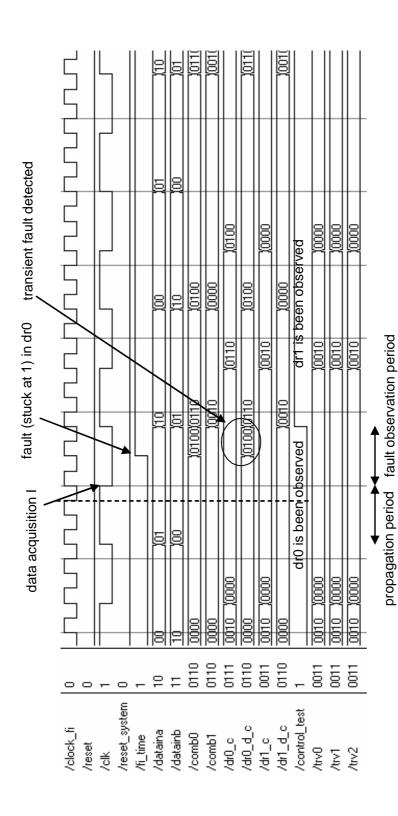

| Figure 8.8:  | Simulation analysis of a fault injection in the DMR with tim            | e     |

|              | redundancy scheme implemented in a 2x2 bits multiplier                  | 115   |

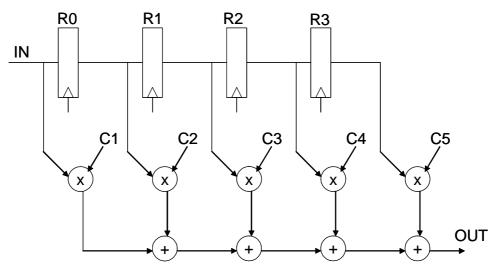

| Figure 8.9:  | Example of FIR canonical filter of 5 taps scheme                        | 116   |

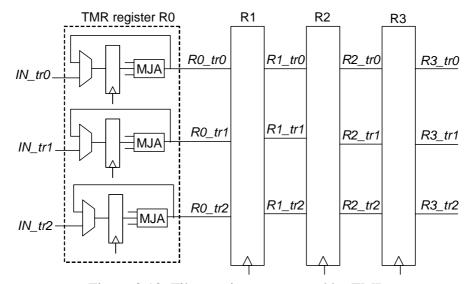

| Figure 8.10: | Filter registers protected by TMR                                       | 117   |

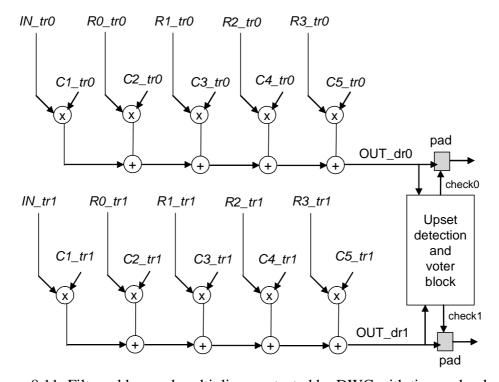

| Figure 8.11: | Filter adders and multipliers protected by DWC with time redundancy     | y 117 |

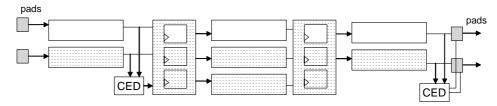

| Figure 8.12: | Evaluation schemes of the TMR and the DWC with time redundanc           | y     |

|              | approach                                                                |       |

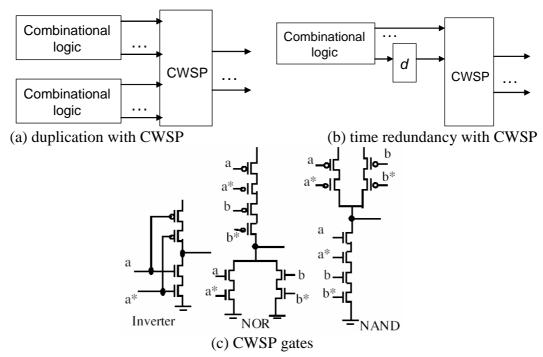

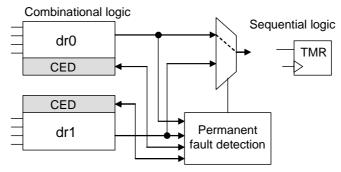

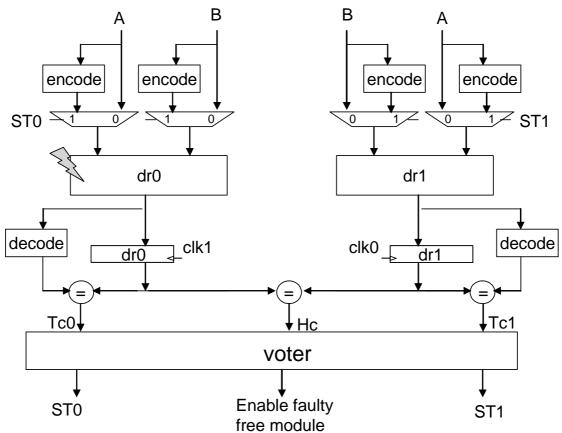

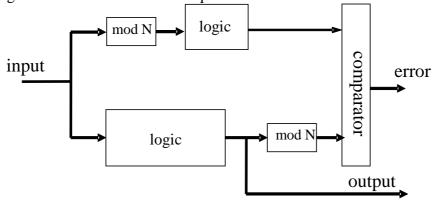

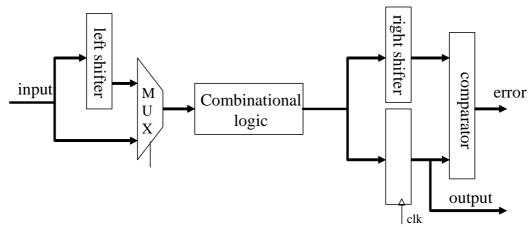

| Figure 9.1:  | DWC combined with CED scheme                                            |       |

| Figure 9.2:  | Time redundancy for permanent fault detection                           |       |

| Figure 9.4:  | Examples of implementations with the combinational output               | ıt    |

|              | registered and in the pads                                              |       |

| Figure 9.5:  | Residue code technique implementation                                   |       |

| Figure 9.6:  | Residue code technique implementation in vhdl                           |       |

| Figure 9.7:  | Reso technique implementation.                                          |       |

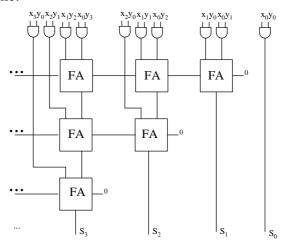

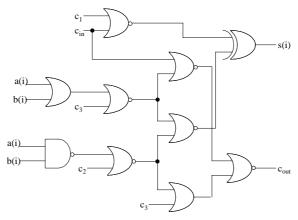

| Figure 9.8:  | Multiplier using cascaded full adders                                   |       |

| Figure 9.9:  | ALU bit slice                                                           |       |

| Figure 9.10: | Upsets emulation in the Chipscope analyzer using the Virtex FPGA        |       |

|              | prototype board                                                         |       |

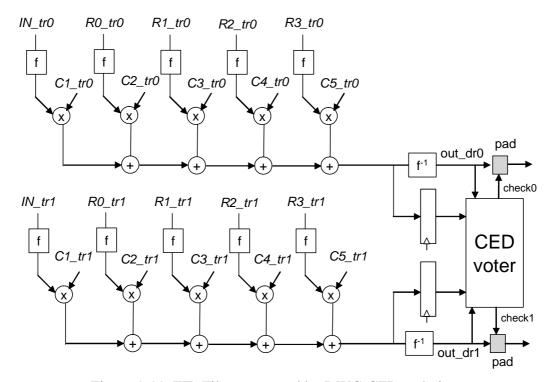

| •            | FIR filter protected by DWC-CED technique                               |       |

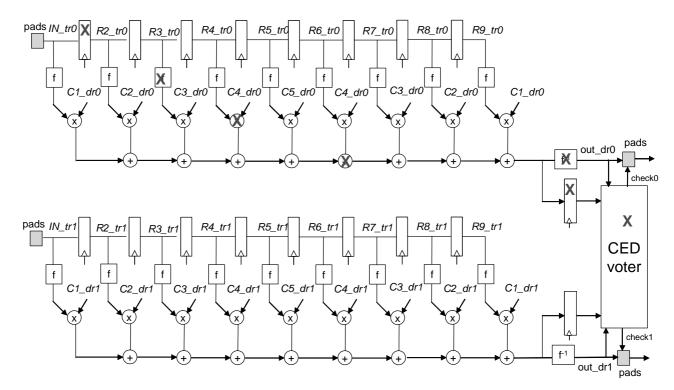

| Figure 9.12: | FIR filter protected by DWC-CED technique in the combinational an       |       |

|              | sequential logic                                                        |       |

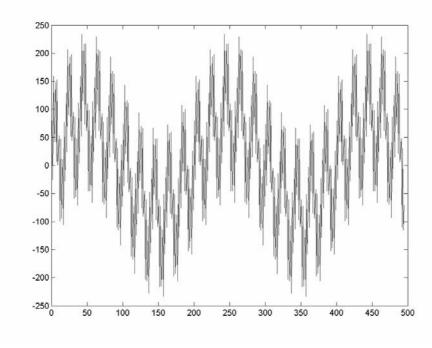

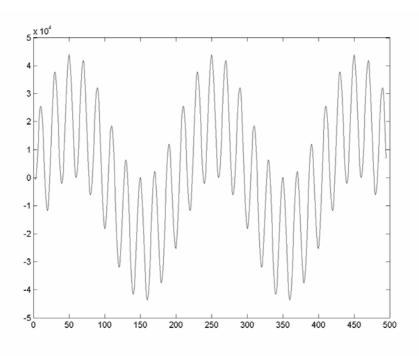

| •            | Amplitude signal input in the FIR filter                                |       |

|              | Amplitude signal output in the FIR filter                               |       |

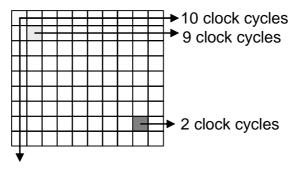

|              | Map of the memory cells in the filter (9 bits x 10 registers)           |       |

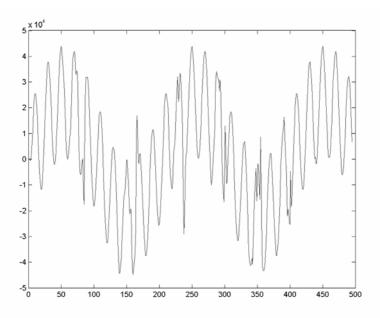

|              | Amplitude signal output in the faulty FIR filter                        |       |

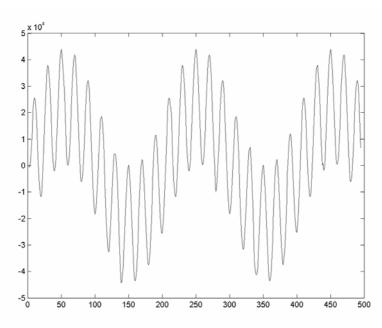

| Figure 9.17: | Amplitude signal output in the faulty FIR filter with 3-bit protected i |       |

|              | the first 7 registers taps                                              | 137   |

| Figure 9.18: | Signal output in the FIR filter in the frequency domain            | 138     |

|--------------|--------------------------------------------------------------------|---------|

| Figure 9.19: | Signal output in the faulty FIR filter in the frequency domain     | 138     |

| Figure 9.20: | Signal output in the faulty FIR filter with 3-bit protected in the | first 7 |

|              | registers taps in the frequency domain                             | 138     |

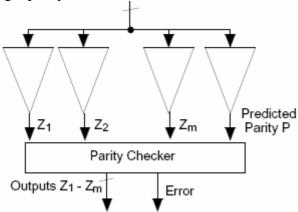

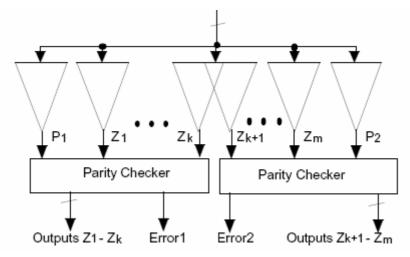

| Figure 9.21: | Parity prediction using single parity bit                          | 139     |

| Figure 9.22: | Multiple parity bits for concurrent error detection                | 139     |

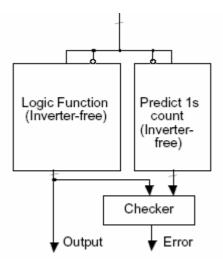

| Figure 9.23: | Unidirectional error detecting codes                               | 140     |

# **LIST OF TABLES**

| Table 3.1: | Hamming code and TMR comparison summary                                    | 47  |

|------------|----------------------------------------------------------------------------|-----|

| Table 3.2: | SEU mitigation techniques summary                                          | 54  |

| Table 3.3: | Results of robust 8051-like micro-controller implemented in PLDs           | 57  |

| Table 4.1: | Evaluation of the sensitive cells in the Virtex® CLB                       | 72  |

| Table 4.2: | Summary of hardened memory cells: main advantages and drawbacks            | 73  |

| Table 4.3: | Area and delay of reed-solomon and hamming codes used to protect a         |     |

|            | memory                                                                     |     |

| Table 4.4: | Summary of tmr approaches: main advantages and drawbacks                   | 77  |

| Table 6.1: | Virtex® configuration column type                                          | 85  |

|            | Frame organization                                                         |     |

|            | Virtex® configuration column type                                          |     |

| Table 6.4: | Bit classification in the CLB                                              | 91  |

| Table 7.1: | TMR logic overhead in the 8051 (XQVR300)                                   | 101 |

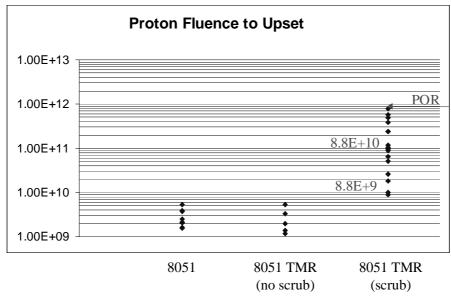

| Table 7.2: | Virtex® dynamic cross-section of TMR 8051                                  | 103 |

| Table 8.1: | Syndrome analysis in the double modular redundancy approach                | 107 |

| Table 8.2: | Example of combinational circuit: multiplier implemented in XCV300-        |     |

|            | pq240 FPGA                                                                 | 116 |

| Table 8.3: | Example of sequential circuit: FIR canonical filter of 9 taps              |     |

|            | implemented in XCV300-pq240 FPGA                                           | 118 |

| Table 9.1: | Fault coverage, area and performance evaluation of CED techniques in       |     |

|            | sram-based FPGAs                                                           |     |

|            | Comparison of multiplier implementations (XCV300-pq240)                    |     |

|            | Filter implementations XCV300-pq240                                        |     |

|            | The influence of the upsets injected in the registers in the filter output |     |

| Table 9.5: | Filter implementation using dwc-ced in the combinational and sequential    |     |

|            | logic (XCV300-pq240)                                                       | 136 |

## **ABSTRACT**

This thesis presents the study and development of fault-tolerant techniques for programmable architectures, the well-known Field Programmable Gate Arrays (FPGAs), customizable by SRAM. FPGAs are becoming more valuable for space applications because of the high density, high performance, reduced development cost and re-programmability. In particular, SRAM-based FPGAs are very valuable for remote missions because of the possibility of being reprogrammed by the user as many times as necessary in a very short period. SRAM-based FPGA and micro-controllers represent a wide range of components in space applications, and as a result will be the focus of this work, more specifically the Virtex<sup>®</sup> family from Xilinx and the architecture of the 8051 micro-controller from Intel.

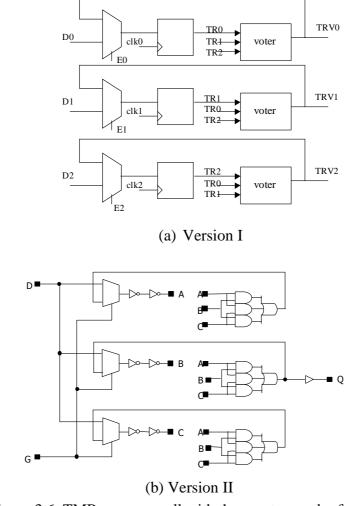

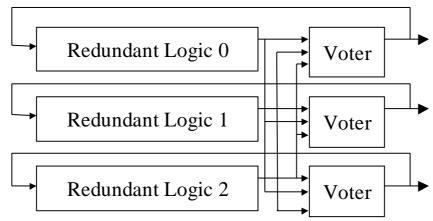

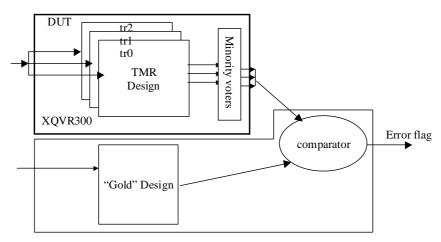

The Triple Modular Redundancy (TMR) with voters is a common high-level technique to protect ASICs against single event upset (SEU) and it can also be applied to FPGAs. The TMR technique was first tested in the Virtex<sup>®</sup> FPGA architecture by using a small design based on counters. Faults were injected in all sensitive parts of the FPGA and a detailed analysis of the effect of a fault in a TMR design synthesized in the Virtex<sup>®</sup> platform was performed. Results from fault injection and from a radiation ground test facility showed the efficiency of the TMR for the related case study circuit. Although TMR has showed a high reliability, this technique presents some limitations, such as area overhead, three times more input and output pins and, consequently, a significant increase in power dissipation.

Aiming to reduce TMR costs and improve reliability, an innovative high-level technique for designing fault-tolerant systems in SRAM-based FPGAs was developed, without modification in the FPGA architecture. This technique combines time and hardware redundancy to reduce overhead and to ensure reliability. It is based on duplication with comparison and concurrent error detection. The new technique proposed in this work was specifically developed for FPGAs to cope with transient faults in the user combinational and sequential logic, while also reducing pin count, area and power dissipation. The methodology was validated by fault injection experiments in an emulation board. The thesis presents comparison results in fault coverage, area and performance between the discussed techniques.

**Keywords:** fault tolerance, FPGA, single event upset, fault injection, time and hardware redundancy

# Desenvolvimento de Técnicas de Tolerância a Falhas Transientes em Componentes Programáveis por SRAM

#### **RESUMO**

Esse trabalho consiste no estudo e desenvolvimento de técnicas de proteção a falhas transientes, também chamadas single event upset (SEU), em circuitos programáveis customizáveis por células SRAM. Os projetistas de circuitos eletrônicos estão cada vez mais predispostos a utilizar circuitos programáveis, conhecidos como Field Programmable Gate Array (FPGA), para aplicações espaciais devido a sua alta flexibilidade lógica, alto desempenho, baixo custo no desenvolvimento, rapidez na prototipação e principalmente pela reconfigurabilidade. Em particular, FPGAs customizados por SRAM são muito importantes para missões espaciais pois podem ser rapidamente reprogramados à distância quantas vezes for necessário.

A técnica de proteção baseada em redundância tripla, conhecida como TMR, é comumente utilizada em circuitos integrados de aplicações específicas e pode também ser aplicada em circuitos programáveis como FPGAs. A técnica TMR foi testada no FPGA Virtex<sup>®</sup> da Xilinx em aplicações como contadores e micro-controladores. Falhas foram injetadas em todos as partes sensíveis da arquitetura e seus efeitos foram detalhadamente analisados. Os resultados de injeção de falhas e dos experimentos sob radiação em laboratório comprovaram a eficácia do TMR em proteger circuitos sintetizados em FPGAs customizados por SRAM. Todavia, essa técnica possui algumas limitações como aumento em área, uso de três vezes mais pinos de entrada e saída (E/S) e conseqüentemente, aumento na dissipação de potência.

Com o objetivo de reduzir custos no TMR e melhorar a confiabilidade, uma técnica inovadora de tolerância a falhas para FPGAs customizados por SRAM foi desenvolvida para ser implementada em alto nível, sem modificações na arquitetura do componente. Essa técnica combina redundância espacial e temporal para reduzir custos e assegurar confiabilidade. Ela é baseada em duplicação com um circuito comparador e um bloco de detecção concorrente de falhas. Esta nova técnica proposta neste trabalho foi especificamente projetada para tratar o efeito de falhas transientes em blocos combinacionais e seqüenciais na arquitetura reconfigurável, reduzir o uso de pinos de E/S, área e dissipação de potência. A metodologia foi validada por injeção de falhas emuladas em uma placa de prototipação. O trabalho mostra uma comparação nos resultados de cobertura de falhas, área e desempenho entre as técnicas apresentadas.

**Palavras-Chaves**: tolerância a falhas, circuitos programáveis, falhas transientes, injeção de falhas, redundância espacial e temporal

### 1 INTRODUCTION

Fault-tolerance on semiconductor devices has been a meaningful matter since upsets were first experienced in space applications several years ago. Since then, the interest in studying fault-tolerant techniques in order to keep integrated circuits (ICs) operational in such hostile environment has increased, driven by all possible applications of radiation tolerant circuits, such as space missions, satellites, high-energy physics experiments and others (NASA, 2003). Spacecraft systems include a large variety of analog and digital components that are potentially sensitive to radiation and must be protected or at least qualified for space operation. Designers for space applications currently use radiation-hardened devices to cope with radiation effects. However, there is a strong drive to utilize standard commercial-off-the-shelf (COTS) and military devices in spaceflight systems to minimize cost and development time as compared to radiation-hardened devices (KATZ et al., 1997; OBRYAN; LABEL, 2001).

The space radiation environment can have serious effects on spacecraft electronics. Single Event Effect (SEE) is the main concern in space (BARTH, 1997), with potentially serious consequences for the application, including loss of information and functional failure. SEE occurs when charged particles hit the silicon transferring enough energy in order to provoke a fault in the system. SEE can have a destructive or transient effect, according to the amount of energy deposited by the charged particles and the location of the strike in the device. The main consequences of the transient effect, also called Single Event Upset (SEU), are bit flips in the memory elements. SEU has been constantly magnified in the past years, caused by the continuous technology evolution that has led more and more complex architectures, with a large amount of embedded memories, followed by an amazing scaling down process of transistor dimensions (Moore's Law) (MOORE, 1975).

The fabrication technology process of semiconductor components is in continuous evolution in terms of transistor geometry shrinking, power supply, speed, and logic density (SIA SEMICONDUCTOR, 1994). As stated in (JOHNSTON, 2000; OBRYAN; LABEL, 2001; OBRYAN et al., 2002; DUPONT; NICOLAIDIS; ROHR, 2002), drastic device shrinking, power supply reduction, and increasing operating speeds reduce significantly the noise margins and thus the reliability that very deep submicron (VDSM) ICs face from the various internal sources of noise. This process is now approaching a point where it will be unfeasible to produce ICs that are free from these effects. A more significant problem is related to SEU. It is predicted that neutrons produced by sun activity will affect dramatically the operation of future ICs. At the sea level, the energy of these particles is not strong enough to drastically affect the operation of current ICs. But as we approach 0.1um, or very low supply voltage, the rates of random errors induced by cosmic neutrons will be unacceptable. The situation is worse at flight altitudes. Alpha particles produced by packaging material are becoming another cause of increasing soft error rates in these technologies.

The necessity to protect integrated circuits against upsets has become more and more eminent (JOHNSTON, 2000; LABEL et al., 2000). Experiments presented in (NORMAND; BAKER, 1993; NORMAND, 1996; NORMAND, 2001) indicate that neutron particles present in the atmosphere are capable of producing SEE in avionics. Recent studies also show that memory cells composed of transistors with length smaller than 0.25 µm and combinational logic composed of transistors with length smaller than 0.13 µm may be subject to upsets while operating in the space environment or inside the atmosphere (BAUMANN, 2001, BOREL; GAUTIER; GASIOT, 2001). Terrestrial applications that are determined as critical such as bank servers, telecommunication servers and avionics are more and more considering the use of fault-tolerant techniques to ensure reliability.

Both discussed factors, the space market interest of using COTS/military devices in space applications and the constant increase in the radiation sensitivity of integrated circuits driven by the process scaling, have brought the necessity of researching fault-tolerant techniques for ICs able to cope with the radiation effects at sea level and also qualifying the design for space applications. Although many techniques have been developed in the last few years attempting to avoid SEU, efficient fault-tolerant solutions are still a challenge for the next generation semiconductor industry, especially because of the complexity of the new architectures.

The development of fault-tolerant techniques is strongly associated with the target device and it requires a detailed analysis of the effects of an upset on the related architecture. For each type of circuit, there is a set of most suitable solutions to be applied. In the past years, the integrated circuit industry has designed more and more complex architectures in order to improve performance, to increase logic density and to reduce cost. Examples of this development include Application Specific Integrated Circuits (ASICs), microprocessors composed of millions of transistors, high-density Field Programmable Gate Array (FPGA) components and more recently System-on-a-Chip (SOC) composed of embedded microprocessors, memories and analog logic blocks. These architectures have made a dramatic impact on the way systems are designed, providing a large amount of information processing on a single chip. They cover a wide range of applications, from portable systems to dedicated embedded control units and computers. In particular, FPGAs have made a major improvement in system designs by adding the reconfigurability feature, which reduces the time to market and increases the flexibility in the design.

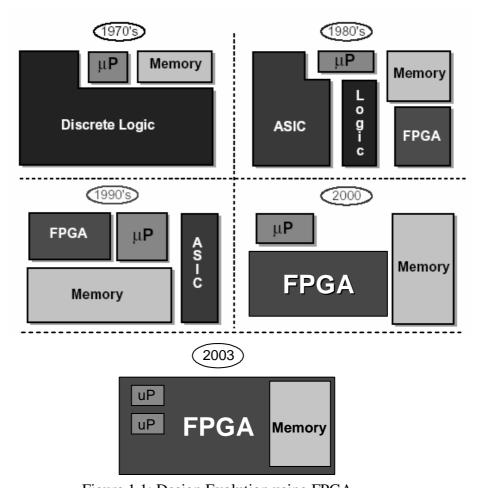

Due to the constant advances in technology over the last few years, Moore's law again, the gap between FPGAs and ASICs in terms of performance has been reduced to a negligible level for the majority of applications, which has increased the market for FPGAs (figure 1.1). In the 70s, a system was basically composed of a microprocessor component, a memory chip and discrete logic. In the 80s, a large part of the discrete logic was replaced by ASICs and some part by programmable logic components (FPGA). In the 90s, the discrete logic completely disappeared and the system was composed of microprocessors, memory, ASICs and FPGA components. ASICs are progressively being replaced by FPGAs in many systems as illustrated in the illustration. In addition, more complex structures are constantly being added to FPGA architectures, supported by substantial increases in logic density and performance in the last few years. Nowadays, FPGAs are also replacing microprocessors and memories as these parts are being added to the FPGA matrix.

Consequently, next generation of FPGA architectures do not claim to reduce that gap between ASIC and programmable logic anymore, but to merge microprocessors and reconfigurability features in the same component in order to improve performance and

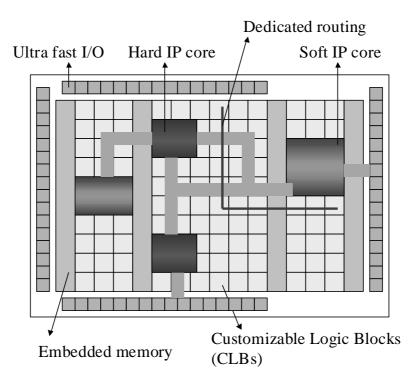

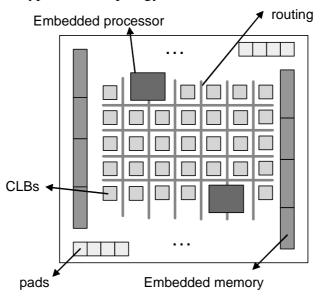

flexibility (DAC, 2001). FPGAs already provide reconfigurability and high performance for many applications, but the necessity of adding either more performance for applications such as Digital Signal Processing (DSP), using high-bandwidth and reducing the board space, power and cost, has increased the interest of embedding microprocessors in the programmable matrix, as illustrated in more detail in figure 1.2. This experience had started with the soft cores synthesized in the FPGA architecture in order to get the highest performance and density tradeoff (XILINX, 2000; ALTERA, 2001). And it has arrived at the next level of performance and complexity with the Virtex<sup>®</sup> II –Pro generation, which has up to four hard PowerPC core microprocessors from IBM embedded in the matrix (XILINX, 2001a).

Figure 1.1: Design Evolution using FPGA

As a consequence, FPGAs are increasingly demanded by spacecraft electronic designers because of their high flexibility in achieving multiple requirements such as high performance, low NRE (Non-Recurring Engineering) cost and fast turnaround time. There are many types of customization in the FPGAs. One of the most popular ones uses SRAM memory cells to customize the FPGA, which makes possible in-the-field customization as many times as necessary in a very short period of time. Examples are the families Virtex<sup>®</sup>, Virtex<sup>®</sup>-E and Virtex<sup>®</sup>-II fabricated by Xilinx. As a result, SRAM-based FPGAs are even more valuable for remote missions by offering the additional benefits of allowing in-orbit design changes, with the aim of reducing the mission cost by correcting errors or improving system performance after launch.

Figure 1.2: Actual architecture generation of commercial Field Programmable Gate Arrays

The advantages of using SRAM-based FPGAs for space applications and the increase of logic complexity of the programmable logic with more and more embedded memories and specific architectures such as microprocessors brings us the necessity of researching new SEU mitigation techniques specific for programmable architecture. This thesis presents the study and development of SEU mitigation techniques for programmable logic architectures, more specifically for SRAM-based FPGAs. The consideration of using FPGA for space applications is fairly recent and there is a lot of work to be done in this area. Presently, there is no efficient solution for SRAM based FPGAs that can ensure 100% reliability in all conditions for SEU.

Several fault-tolerant techniques have been studied in the past years to protect ASICs against transient faults, and because FPGAs are composed of combinational and sequential logic and more recently embedded processors, previous work dealing with standard integrated circuits can be adapted to the programmable logic architecture by finding the best tradeoff among area overhead, performance penalties, single and multiple upset correction, process technology and implementation cost. However, the SEU mitigation techniques previously used for ASICs cannot simply be applied to programmable circuits because of the distinct effect of a SEU in the FPGA architecture compared to an ASIC, as will be further discussed in the next chapter. Consequently, the effect of SEUs in the SRAM-based FPGA architecture must be investigated to identify the limitations of the already used fault-tolerant techniques and to guide the investigation to new solutions.

The goal of this work is to investigate the techniques used nowadays and to develop new SEU mitigation techniques for SRAM-based FPGAs that are cost efficient in terms of:

- time to market,

- low development cost,

- high performance,

- low area cost.

- low power dissipation,

- high reliability.

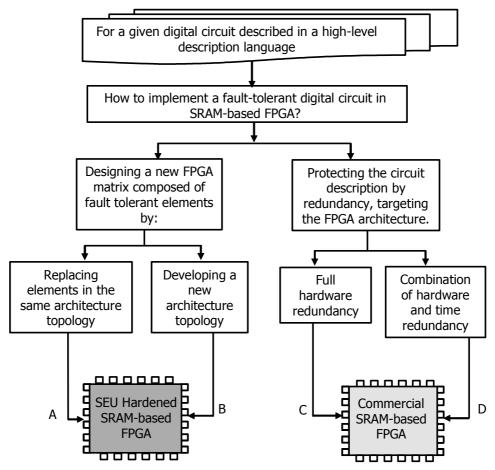

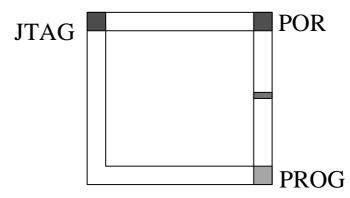

There are two ways to implement fault-tolerant circuits in SRAM-based FPGAs, as exemplified in the flowchart in figure 1.3. The first possibility is to design a new FPGA matrix composed of fault-tolerant elements. These new elements can replace the old ones in the same architecture topology or a new architecture can be developed in order to improve robustness. The cost of these two approaches is high and it can differ according to the development time, number of engineers required to perform the task and the foundry technology used. Another possibility is to protect the high-level description by using some sort of redundancy, targeting the FPGA architecture. In this way, it is possible to use a commercial FPGA part to implement the design and the SEU mitigation technique is applied to the design description before being synthesized in the FPGA. The cost of this approach is inferior to the previous one because in this case the user is responsible for protecting the own design and it does not require new chip development and fabrication. In this way, the user has the flexibility of choosing the fault-tolerant technique and consequently the overheads in terms of area, performance and power dissipation.

Figure 1.3: Design flow of how to protect a digital circuit implemented in a SRAM-based FPGA

In summary, the four different implementations of a fault-tolerant FPGA: A, B, C and D have different costs that are approximately organized as: cost B > cost A >>>> cost C > cost D. All of them have their own space in the market, as each application requires different constraints. But because the semiconductor industry trends to emphasize time-to-market and low-cost production, the implementations C and D look

more interesting. In this work, both architectural and the high-level methods are presented and discussed, but because of the high cost of the implementations A and B, only implementations C and D are designed and tested in details.

This thesis work can be divided into three main phases, ranging from the study of state-of-the-art of SEU mitigation techniques for ASIC and FPGA components, to the implementation and test of new fault-tolerant techniques for SRAM-based FPGA components. Some of the research phases are also related to the two internships concluded during the thesis work, one at Tima laboratory (Grenoble, France) for 6 months under the supervision of researcher Raoul Velazco and other one at Xilinx (San Jose, USA) for 11 months under the supervision of engineer Joe Fabula in the high reliability team.

In the first phase of the research, available techniques to protect integrated circuits against radiation were studied. The radiation fault-tolerant techniques can be classified as: the ones that change the technology used in the fabrication process such as Silicon on Insulator (SOI), and the ones that change the hardware design of a system such as SEU hardened memory cells, error detection and correction codes (EDAC) and logic redundancy. There is a trade-off with each mitigation technique for each type of architecture system, and there is no best unique solution so far. Some of the considered techniques were evaluated in terms of area, cost and performance. The first case study circuit was the 8051 micro-controller from Intel (INTEL, 1994). The microprocessor architecture was chosen for its representation of the majority of system requirements in space applications nowadays, presenting all types of logic to be protected and being part of the new generation architectures based on FPGA with an embedded hard microprocessor core.

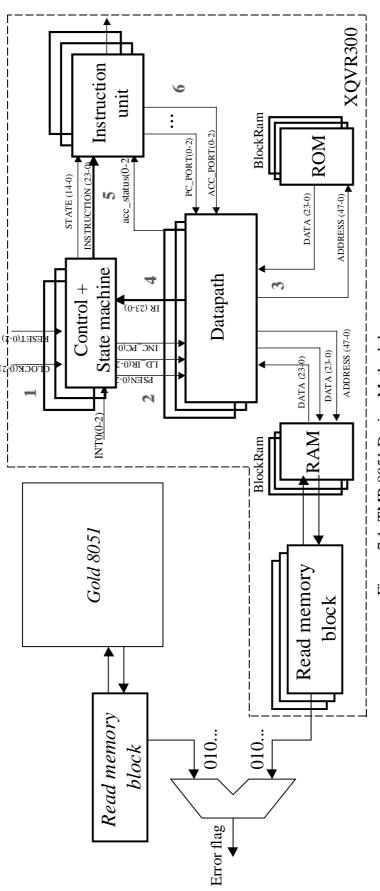

The description of the 8051 micro-controller used in the experiment was developed at UFRGS (CARRO; PEREIRA; SUZIM, 1996). It is composed of a datapath unit, control unit, state machine, instruction decoding unit and embedded memory. Although the 8051 micro-controller has a simplified architecture compared to the latest microprocessors, the assumptions made in its architecture can be adapted to any other processor-like circuit. Techniques such as hamming code and radiation tolerant flip-flops were implemented in the 8051 micro-controller (LIMA et al., 2000a; LIMA et al., 2000b). Fault injection (LIMA et al., 2001a; LIMA et al., 2002a; LIMA et al., 2002b) and simulation were used to analyze the efficiency of the techniques. Area and performance were taken into consideration with the results.

The second phase of the work resumes the analysis of an SRAM-based FPGA and the SEU effects in this architecture. The Virtex® family FPGA from Xilinx is the most popular high density and high performance FPGA used in the market nowadays and it was chosen to be the object of study in this work. There are two ways to mitigate SEU in FPGA designs, as mentioned previously. One is based in changing the FPGA architecture and the other one is based on modifying the high-level design description before the FPGA synthesis. First, implementations of some SEU mitigation techniques in the architectural level of the FPGA matrix were proposed. The SRAM-based architecture was divided in main blocks classified by functionality (such as LUT), flip-flops, customization routing, embedded memory, PLL, etc. SEU mitigation techniques for many of the blocks are discussed. The objective is to show the trade-off of each technique in the Virtex® FPGA and the complexity of developing a new architecture with changes at the mask level. This investigation was based on the experience collected in first phase.

Because of the limitations in developing and testing a new fault-tolerant FPGA architecture such as cost and time-to-market/ techniques at the high-level description

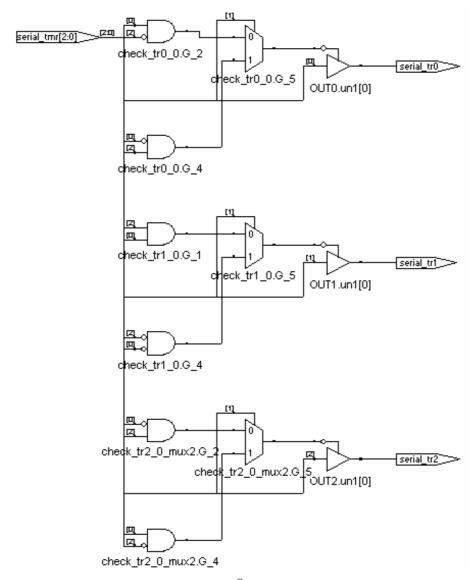

must also be investigated. The Triple Modular Redundancy (TMR) with voters is a common technique to protect against SEU in ASICs and it can be also applied to protect FPGAs against SEU, as shown in (CARMICHAEL, 2001). In this case, the mitigation can be applied to the high-level design description language and synthesized in the device without any changes in the mask process. The TMR technique was first tested in the Virtex architecture by using a small design based on counters. Faults were injected in all sensitive parts of the FPGA and a detailed analysis of the effect of a fault in a TMR design synthesized in the Virtex platform was performed. Results were published in (LIMA et al., 2001b).

In order to test a more complex design protected by TMR in the Virtex® platform that would also include embedded memories, the same 8051 like micro-controller description was protected by TMR and tested under the FPGA platform. There are many advantages of using the same design as the 8051 micro-controller, such as good description knowledge, importance of micro-controllers IP in FPGA and the possibility of comparison with the previous techniques (hamming code and SEU hardened memory cells) applied in the same description. The TMR 8051 micro-controller was tested by fault injection and under proton radiation in a ground facility (LIMA et al., 2001b). At the end of these practical experiments (LIMA et al., 2001b; CARMICHAEL; FULLER; FABULA; LIMA, 2001), the use of TMR in Virtex FPGAs has confirmed the efficacy of the TMR structure to recover upsets in the FPGA architecture. However, the TMR technique presents some limitations, such as area overhead, three times more input and output pins and, consequently, a significant increase in power dissipation and also some robustness issues. The result has brought about the necessity of improving this technique in order to reduce the overheads and to try to improve robustness as well.

In the third phase of the work, additional SEU mitigation techniques for the Virtex® FPGA architecture were investigated. A new high-level fault-tolerant technique for SRAM-based FPGA was developed (LIMA, CARRO, REIS, 2003a; LIMA, CARRO, REIS, 2003b). This technique combines time and hardware redundancy with some extra features able to cope with the effects of SEU in FPGAs and at the same time it is able to reduce the number of input and output pads and area overhead compared to the traditional TMR approach. The methodology was validated in combinational and sequential circuits by using fault injection experiments emulated in a prototype board. Results have confirmed that this new technique can reduce not only pin count but also area as well without compromising performance and reliability.

This thesis report is organized as follows. Chapter 2 describes the radiation effects on integrated circuits manufactured using CMOS process and it explains in detail the difference between the effects of a SEU in ASIC and in SRAM-based FPGA architectures. This chapter shows the architecture analysis of the Virtex® FPGA and all its radiation sensitive area. Chapter 3 presents the main techniques available in the literature, either being commercialized by companies or being studied by researchers, to mitigate the effects of radiation in ASICs, such as microprocessors and memories, and in programmable architectures, such as FPGAs programmed by SRAM and by anti-fuse technology.

Chapter 4 discusses some SEU mitigation techniques that can be applied at the FPGA architectural level. The FPGA was divided by functionality in main logic blocks. Each block has different characteristics, and the fault-tolerant technique must take into account the peculiarities of each. In the end, a SEU tolerant FPGA is proposed based on the presented SEU mitigation techniques.

Chapter 5 defines the problem of protecting SRAM-based FPGAs against radiation in the high level description. The Triple Modular Redundancy (TMR) technique in the

high level description for FPGAs is addressed in this chapter. Chapter 6 evaluates the robustness of the TMR technique by using fault injection in the bitstream of the FPGA and also in a radiation ground test facility. In this chapter, a methodology is presented to relate the upset bit in the bitstream to the SRAM cell location in the user's design floorplanning. The obtained results represent an important base for this work, because it shows the limitations of the TMR method on the SRAM-based FPGA, justifying the research of new design techniques for SEU mitigation in SRAM based FPGAs.

Chapter 7 shows the implementation and results of the 8051 description protected by TMR in the Virtex FPGA. All implementation details of the TMR technique were carefully applied to the VHDL description of the 8051 to test this technique in a more complex design. The final protected design was tested by fault injection in the FPGA bitstream and also in a radiation ground test facility. Results and final remarks are placed at the end of that chapter.

Chapter 8 introduces a new high-level technique for designing fault tolerant systems for SRAM-based FPGAs, without modifications in the FPGA architecture, able to cope with transient faults in the user combinational and sequential logic, while also reducing pin count, area and power dissipation compared to the traditional TMR. The methodology was validated by fault injection experiments in VHDL description emulated in a prototyped board. Results in terms of fault coverage and area and performance comparison with the TMR approach are presented.

The technique presented in chapter 8 presents some limitations in fault coverage because it uses the standard time redundancy approach to detect the effect of a SEU in the FPGA matrix. In chapter 9, an improvement to the high-level technique presented in chapter 8 is proposed. This technique combines duplication with comparison and concurrent error detection technique in order to cope with the permanent effects of a SEU in FPGAs and at the same time to reduce TMR overheads. In addition, this proposed method is also able to detect physical faults, which are permanent faults that are not corrected by reconfiguration. The methodology was also validated by fault injection experiments in an emulation board. Some fault coverage results and a comparison with the TMR approach are evaluated.

The conclusion is placed in chapter 10, followed by the references, and it analyzes the architectural and high-level methods of fault-tolerant techniques for SRAM-based FPGAs studied and developed in this thesis. Because the technology is constantly in evolution, there are always improvements to be made in the projection of integrated circuits, and consequently, in the way designs are protected against faults. This work has contributed to some solutions for the SRAM-based FPGAs that are being projected to work in commercial applications but are manufactured by nanotechnologies and need to work properly in the presence of upsets. However, there is much more research to be done as each step of investigation brings more questions and possibilities of solutions. As a result, future works are proposed at the end of this report.

## 2 SPACE ENVIRONMENT AND RADIATION EFFECTS

Signal integrity is becoming much more critical in integrated circuits (ICs) designed in very deep sub-micron technologies (VDSM), as device dimensions continue to shrink. Some of the causes are cross coupling and ground bounce, which are increasing the sensitivity of VDSM designs to transient errors (IROM ET AL, 2002). In addition, ICs operating in space environment and more recently at sea level can be upset by charged particles that also generate transient errors in the system. Transient errors provoked by radiation effects are a major concern and they must be tolerated in order to ensure reliability.

The radiation environment is composed of various particles generated by sun activity (STASSINOPOULOS; RAYMOND, 1988; BARTH, 1997; BAUMANN, 2001; LERAY, 2001). The particles can be classified as two major types: (1) charged particles such as electrons, protons and heavy ions, and (2) electromagnetic radiation (photons), which can be x-ray, gamma ray, or ultraviolet light. The main sources of charged particles that contribute to radiation effects are protons and electrons trapped in the Van Allen belts, heavy ions trapped in the magnetosphere, galactic cosmic rays and solar flares. The charged particles interact with the silicon atoms causing excitation and ionization of atomic electrons.

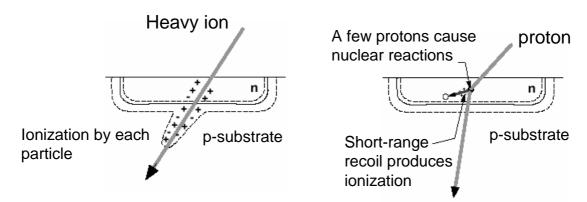

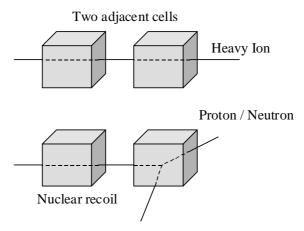

When a single heavy ion strikes the silicon, it loses its energy via the production of free electron hole pairs resulting in a dense ionized track in the local region, as illustrated in figure 2.1 (a). Protons and neutrons can cause nuclear reaction when passing through the material, as illustrated in figure 2.1 (b). The recoil also produces ionization. The ionization generates a transient current pulse that can be interpreted as a signal in the circuit causing an upset.

Figure 2.1: Charged particle striking the silicon surface (OBRYAN et al., 1998)

The influence of radiation in the material is measured by the energy and the flux of particles. The flux is the number of particles passing during one second through one cm<sup>2</sup> of area [1/s.cm<sup>2</sup>]. Integrating the flux over time one gets the fluence, which is [1/cm<sup>2</sup>].

The flux of these sources is affected by the activity of the sun. The energy deposited by the charged particle is measured in rad (1 rad =  $10^{-2}$  Js<sup>-1</sup>), which corresponds roughly to the generation of  $4x10^{13}$  electron-hole pairs in one cm<sup>3</sup> of silicon. The rate at which the particle loses energy is called stopping power (dE/dx). The incremental energy dE is usually measured in units of MeV while the material thickness is usually measured as a mass thickness in units of mg/cm<sup>2</sup>. The energy transferred to the device is called Linear Energy Transfer (LET) and it is measured by the incremental energy per unit length (MeV/(mg/cm<sup>2</sup>)). The minimum LET that can cause an SEU is called the LET threshold (LET<sub>th</sub>) (DENTAN, 2000). There are many levels of robustness, according to the amount of flux and energy transferred to the silicon that can keep the circuit operating properly. On average, space applications operating in low orbit and military applications need to be robust to LETs higher than  $40 \text{ MeV/(mg/cm}^2)$ .

In other words, there is a minimum charge that must be deposited in the node in order to cause an upset. This minimum charge is called critical charge ( $Q_{crit}$ ) and it is defined by  $Q_{crit} = C_{node}.V_{node}+I_{restore}.T_{flip}$ . The critical charge must be bigger than the node collector charge ( $Q_{col}$ ), which is based on node parameters such as capacitance and voltage. The critical charge has been reduced in the new process technologies because of the scaling. For constant field scaling, for example, as all physical device dimensions such as gate length L, gate width W, and gate oxide thickness Tox, are reduced, the supply voltage  $V_{DD}$  and the threshold voltage  $V_{TH}$  are also reduced proportionately. This fact results in proportionately lower drain current (I), proportionately lower load capacitance (C), and proportionately lower circuit gate delay ( $C^*V_{DD}/I$ ). This means that less charge or current is required to store information. Consequently, devices are becoming more vulnerable to radiation and this means that particles with small charge, which were once negligible, are now much more likely to produce upset.

By counting the number of upsets and knowing how many particles passed through the part, we can calculate the probability of a particular particle causing an upset. This resultant number, which is the number of upsets divided by the number of particles per cm<sup>2</sup> causing the upsets, is called the cross-section of the part and is measured in units of cm<sup>2</sup> / device. Consequently, the sensitivity of a device to an upset is measured by a function of the cross-section ( $\sigma$ ) in terms of the LET (Linear Energy Transfer). Figure 2.2 shows an example of cross-section per LET curve.

Figure 2.2: An example of cross-section per LET curve

Analyzing this curve, one can say that no error occurs in the presence of particles with LET (linear energy transfer) lower than 25 MeV. For particles with 25 MeV, more than 100.000.000 particles must travel through the circuit sensitive area to trigger one upset. For particles with 50 MeV, 10.000 particles per second are needed to trigger one upset. And a flux of 100 particles per second with a LET of 100 MeV is needed to trigger one upset.

At the ground level, the neutrons are the most frequent cause of upset (NORMAND, 1996; OBRYAN et al, 1998; BAUMANN; SMITH, 2000). Neutrons are created by cosmic ion interactions with the oxygen and nitrogen in the upper atmosphere. The neutron flux is strongly dependent on key parameters such as altitude, latitude and longitude. Its peak is around 60,000 ft (~20,000 m). At 30,000 ft (~10,000 m) the neutrons are about 1/3 of the peak flux, and on the ground, it is about ~1/400 of the peak flux. At airplane altitudes, the neutron flux is 7,200 neutrons/cm²/hour. The peak at ground level is around 4 neutrons/cm²/sec, but the average at sea level is around 20 neutrons/cm²/hour. Figure 2.3 shows a graphic of the variation of the neutron flux according to the altitude.

Figure 2.3: 1-10 MeV Atmospheric Neutron Flux vs. Altitude, Simplified Boeing Model (NORMAND, 1996)

There are high-energy neutrons that interact with the material generating free electron hole pairs and low energy neutrons. These neutrons interact with a certain type of Boron present in semiconductor material creating others particles as represented in figure 2.4. The energized alpha particles are the greatest concern in this case and they are addressable through processing and packaging material. In principle, a very careful selection of materials can minimize alpha particles. However, this solution is very expensive and never eliminates the problem completely (DUPONT; NICOLAIDIS; ROHR, 2002).

Figure 2.4: Neutron reaction (OBRYAN et al, 1998)

The detailed analysis of the effects of radiation particles in the bulk of a semiconductor is still a challenge. One of the difficulties is in predicting just what percentage of electron hole pairs is actually collected in the area around the stored data. It is this percentage that determines the critical point at which the radiation induced charge provokes an error in the stored data. Solutions to help the analysis can be the use of complex 3D simulations to help find an accurate shape for the pulse generated by the strike and the exploration of how the electron-hole-pair cloud can neutralize the stored data.

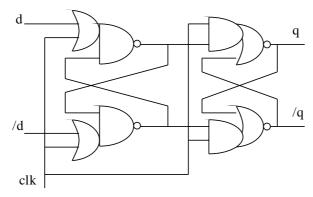

### 2.1 Effect of SET and SEU in Integrated Circuits

A single particle can hit either the combinational logic or the sequential logic in the silicon (CRAIN et al., 2001; ALEXANDRESCU; ANGHEL; NICOLAIDIS, 2002). Figure 2.5 illustrates a typical circuit topology found in nearly all sequential circuits. The data from the first latch is typically released to the combinatorial logic on a falling or rising clock edge, at which time logic operations are performed. The output of the combinatorial logic reaches the second latch sometime before the next falling or rising clock edge. At this clock edge, whatever data happens to be present at its input (and meeting the setup and hold times) is stored within the latch.

Figure 2.5: Upsets hitting combination and sequential logic

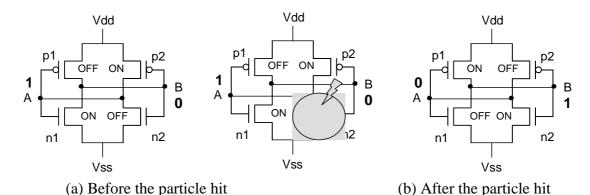

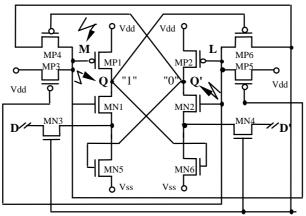

When a charged particle strikes one of the sensitive nodes of a memory cell, such as a drain in an off state transistor, it generates a transient current pulse that can turn on the gate of the opposite transistor. The effect can produce an inversion in the stored value, in other words, a bit flip in the memory cell. Memory cells have two stable states, one that represents a stored '0' and one that represents a stored '1.' In each state, two transistors are turned on and two are turned off (SEU target drains). A bit-flip in the memory element occurs when an energetic particle causes the state of the transistors in

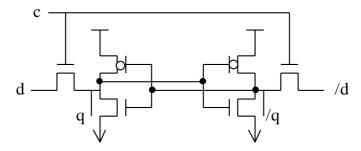

the circuit to reverse, as illustrated in figure 2.6. This effect is called Single Event Upset (SEU) and it is one the major concerns in digital circuits.

Figure 2.6: Single Event Upset (SEU) effect in a SRAM Memory cell

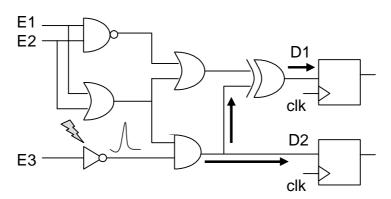

When a charged particle hits the combinational logic block, it also generates a transient current pulse. This phenomenon is called single transient effect (SET) (LEAVY et al., 1991). If the logic is fast enough to propagate the induced transient pulse, then the SET will eventually appear at the input of the second latch in figure 2.5, where it may be interpreted as a valid signal. Whether or not the SET gets stored as real data depends on the temporal relationship between its arrival time and the falling or rising edge of the clock. Figure 2.7 exemplifies the signal paths in a combinational logic. In (HASS et al., 1998; HASS, 1999) the probability of a SET becoming a SEU is discussed. The analysis of SET is very complex in large circuits composed of many paths. Techniques such as timing analysis (GUNTZEL; REIS, 2000) could be applied to analyze the probability of a SEU in the combinational logic being stored by a memory cell or resulting in an error in the design operation. Additional invalid transients can occur at the combinatorial logic outputs as a result of SETs generated within global signal lines that control the function of the logic. An example of this would be SETs generated in the instruction lines to an ALU (Arithmetic Logic Unit). In (NICOLAIDIS; PEREZ, 2003), the widths of some induced transient pulses are measured to obtain more precise models for fault-tolerant analysis.

Figure 2.7: Single Event Transient (SET) Effect in Combinational Logic (ANGHEL; ALEXANDRESCU; NICOLAIDIS, 2000)

SEUs can be classified in first, second and third order effects, according to the number of upsets that occur at the same time in the circuit. A single bit upset (SEU) is classified as a first order effect, while multiple bit upsets (MBU) are classified as second or third order effects. MBU can occur when a single charged particle traveling

through the IC at a shallow angle, nearly parallel the surface of the die, simultaneously strikes two sensitive junctions (ZOUTENDYK; EDMONDS; SMITH, 1989). Just as SEU, direct ionization or nuclear recoil can induce MBUs, as is presented in figure 2.8 (VARGAS; AMORY, 2001).

Figure 2.8: MBU provoked by a single particle

In (REED et al., 1997), experiments in memories under proton and heavy ions fluxes have shown multiple upsets provoked by a single ion. MBUs were observed for all angles of incidence for LET greater than 25 MeV/(mg/cm<sup>2</sup>). There are three types of MBU. The first one occurs when a single particle hits two adjacent nodes, located in two distinct memory cells. This event is classified as a second-order effect. This type of MBU can be avoided by specific placement.

The second type of MBU occurs when a single particle strikes two adjacent nodes located in the same memory cell. This event is classified as a third-order effect. It can be avoided by layout constraints. In this case, two or more charged particles are necessary to generate multiple upsets. The probability of this occurrence is related to the placement of the memory cells. The cross section is proportional to the sensitive areas of the junctions that are normal to the incident cosmic ray and to the solid angle subtended between these sensitive areas. The probability of such a multiple node strike can be minimized in a circuit design by taking care in the physical layout to separate critical node junctions by large distances and to align such junctions so that the area of each, as viewed from the other, is minimized.

The third type of MBU occurs when multiple bits strike that silicon provoking upsets in multiple nodes. This event can be analyzed like a group of SEU and it will represent the same (this should be "immunity characteristics" or "characteristic immunity"). Based on (REED et al., 1997), the majority of multiple upsets located in adjacent cells are provoked by a single particle. There is a very low probability of more than one charged particle interacting in adjacent cells, provoking upsets in a period smaller than 1 s. in (VELAZCO; CHEYNET, ECOFFET, 1999), it is shown some SEU flight results of two SRAM memories (Hitachi and MHS). A total of 691 upsets were detected for the analyzed period of time, 333 of them arising on the Hitachi SRAM and 358 occurring in the MHS SRAM memory. The distribution of bit flips within the memory word's bits was uniform. Some double bit upsets were also detected, 8 double upsets in the Hitachi and 3 in the MHS memory. Transitions 1 to 0 seem to be slightly more frequent than 0 to 1 for all the tested memories too.

#### 2.2 Peculiar Effect of SET and SEU in SRAM-based FPGA Devices

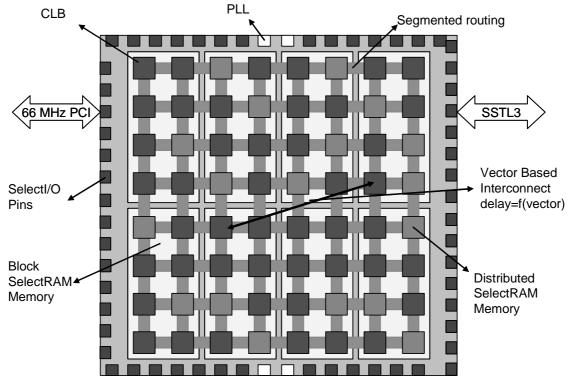

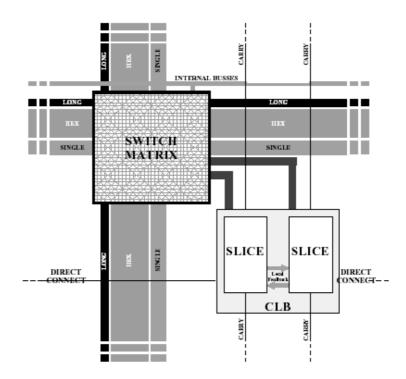

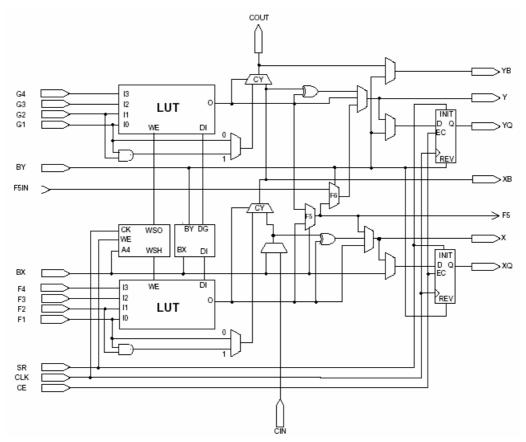

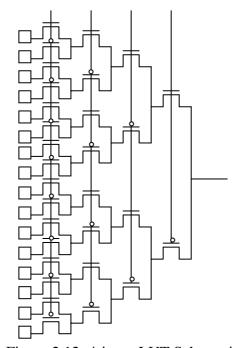

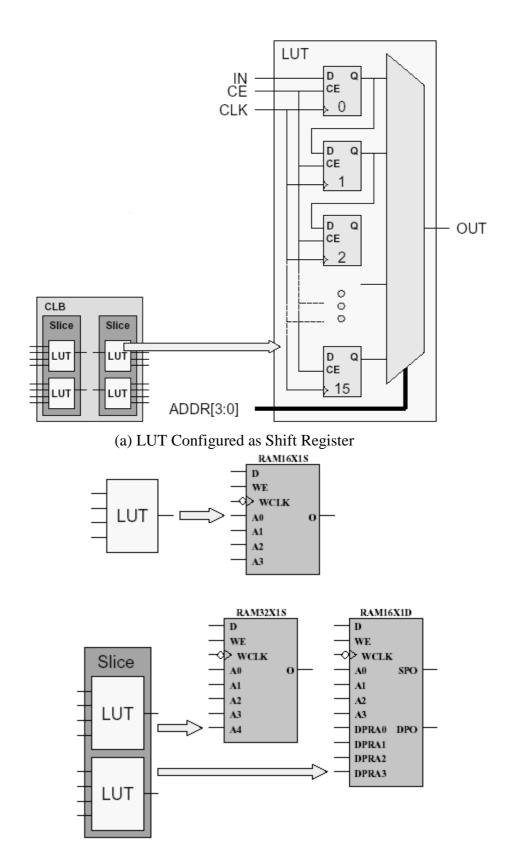

The Virtex<sup>®</sup> family from Xilinx (XILINX, 2000) is one of the most popular SRAM-based programmable devices used in the market nowadays because of its high density and high-performance. It supports a wide range of configurable gates, from 50k to more than 1M system gates. It is fabricated on thin-epitaxial silicon wafers using the commercial mask set and the Xilinx 0.22µ CMOS process with 5 metal layers. The Virtex<sup>®</sup> family is valuable for space applications because of the reduced cost, high-density and reconfigurability, which can considerably reduce the mission cost. Because it is a VDSM design, it is highly sensitive to radiation effects and its architecture must be studied in order to be protected against upsets.