### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

ALEXANDRE BERGMANN YPIRANGA BENEVIDES

## PROJETO DE DIPLOMAÇÃO

## ANÁLISE DOS EFEITOS DA RADIAÇÃO IONIZANTE EM MEMÓRIAS FLASH E SRAM

Porto Alegre

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

## ANÁLISE DOS EFEITOS DA RADIAÇÃO IONIZANTE EM MEMÓRIAS FLASH E SRAM

Projeto de Diplomação apresentado ao Departamento de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul, como parte dos requisitos para Graduação em Engenharia Elétrica.

ORIENTADOR: Prof. Dr. Gilson Inácio Wirth

Porto Alegre

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

#### ALEXANDRE BERGMANN YPIRANGA BENEVIDES

## ANÁLISE DOS EFEITOS DA RADIAÇÃO IONIZANTE EM MEMÓRIAS FLASH E SRAM

Este projeto foi julgado adequado para fazer jus aos créditos da Disciplina de "Projeto de Diplomação", do Departamento de Engenharia Elétrica e aprovado em sua forma final pelo Orientador e pela Banca Examinadora.

| Orientador:                                           |

|-------------------------------------------------------|

| Prof. Dr. Gilson Inácio Wirth, UFRGS                  |

| Doutor pela Universität Dortmund – Dortmund, Alemanha |

#### Banca Examinadora:

Prof. Dr. Gilson Inácio Wirth, UFRGS

Doutor pela Universität Dortmund – Dortmund, Alemanha

Prof<sup>a</sup>. Dr<sup>a</sup>. Fernanda Gusmão de Lima Kastensmidt, UFRGS

Doutora pela Universidade Federal do Rio Grande do Sul – Porto Alegre, Brasil

Prof. Dr. Marcelo Götz, UFRGS

Doutor pela Universität Paderborn – Paderborn, Alemanha

Porto Alegre, Julho de 2011.

## **DEDICATÓRIA**

Dedico este trabalho à minha esposa Márcia, à minha mãe Regina, ao meu irmão Alessandro e a toda minha família, por todo apoio concedido durante toda a minha vida, e por terem sido os principais fatores que me ajudaram a alcançar tudo que conquistei.

#### **AGRADECIMENTOS**

Agradeço primeiramente à minha esposa Márcia, por ser minha companheira e ter me dado todo o apoio durante a graduação, me auxiliando sempre que necessitei.

À toda a minha família, em especial à minha mãe Regina, por toda a dedicação e apoio concedidos durante toda a minha vida, e por terem sempre me incentivado a estudar, superando todas as dificuldades da vida.

Ao meu professor orientador, Professor Doutor Gilson Inácio Wirth, por todo o tempo dedicado a este projeto e por ter me ajudado sempre que o procurei.

A todos os professores do Departamento de Engenharia Elétrica desta Universidade, além dos professores de outros departamentos com os quais convivi em aula ou em outras atividades, pelas aulas que jamais esquecerei e por todo o crescimento pessoal e profissional que me ajudaram a construir.

Agradeço também a todos meus amigos e colegas de curso, pessoas que sempre me ajudaram a superar as dificuldades da vida universitária e que souberam entender os momentos em que não havia tempo disponível para diversão, apenas para estudo.

#### **RESUMO**

Este relatório apresenta o trabalho desenvolvido durante a disciplina Projeto de Diplomação do Curso de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul. O projeto desenvolvido consiste no estudo dos efeitos da radiação ionizante sobre dispositivos semicondutores, especialmente em memórias flash e SRAM, e os tipos de falha que podem vir a ocorrer nestes tipos de memória. Além disso, consiste na seleção de testes que podem ser aplicados às memórias de forma a verificar as falhas provocadas pela radiação, e o projeto de uma plataforma para testar algumas memórias, que foi desenvolvida baseada em FPGA.

Palavras-chaves: Radiação ionizante, memória flash, SRAM, testes march, FPGA, VHDL.

#### **ABSTRACT**

This document presents the work developed in the final project of the graduation in Electrical Engineering at Universidade Federal do Rio Grande do Sul (UFRGS). The project consists in the study of the effects of ionizing radiation on flash memories and SRAMs, and the fault types that may occur in these memories. Also, this work includes the selection of tests that can be applied to the memories in order to verify their comportment in a radiation environment, and the design of a test platform to analyze the faults in the memories, which was developed based on a FPGA platform.

Keywords: Ionizing radiation, flash memory, SRAM, march tests, FPGA, VHDL.

## **SUMÁRIO**

| 1      | INTRODUÇÃO                                                 | 15        |

|--------|------------------------------------------------------------|-----------|

| 1.1    | Motivação                                                  | 15        |

| 1.2    | Objetivos                                                  |           |

| 2      | EFEITOS DA RADIAÇÃO IONIZANTE EM SEMICONDUTORES            | 19        |

| 2.1    | Efeitos da Radiação Ionizante em Transistores MOS          | 19        |

| 2.2    | Efeitos da Radiação Ionizante em Memórias SRAM             | 23        |

| 2.3    | Efeitos da Radiação Ionizante em Memórias Flash            | 25        |

| 3      | FALHAS EM MEMÓRIAS                                         | 29        |

| 3.1    | Notação das Falhas                                         | 31        |

| 3.2    | Falhas de Valor Fixo                                       | <b>32</b> |

| 3.3    | Falhas de Transição                                        | 34        |

| 3.4    | Falhas por Acoplamento                                     | 35        |

| 3.4.1. | Falhas de Inversão por Acoplamento                         | 36        |

|        | Falhas de Valor Armazenado por Acoplamento                 |           |

|        | Falhas por Acoplamento Dinâmicas                           |           |

|        | Falhas de Ligação                                          |           |

|        | Falhas de Estado por Acoplamento                           |           |

| 3.5    | Falhas por Acoplamento Sensíveis aos Padrões da Vizinhança |           |

| 3.6    | Falhas no Decodificador de Endereço                        |           |

| 3.7    | Falhas de Retenção de Dados                                |           |

| 4      | TESTES DE MEMÓRIAS                                         |           |

| 4.1    | Notação dos Testes March                                   |           |

| 4.2    | Testes March para Detecção de Falhas                       |           |

| 4.3    | Testes March para Identificação de Falhas                  |           |

| 5      | ANÁLISE DE ALTERNATIVAS                                    |           |

| 5.1    | Seleção das Memórias                                       |           |

| 5.2    | Definição da Tecnologia da Plataforma de Testes            |           |

| 5.3    | Seleção dos Testes Desenvolvidos Durante o Projeto         |           |

| 6      | HARDWARE DESENVOLVIDO                                      |           |

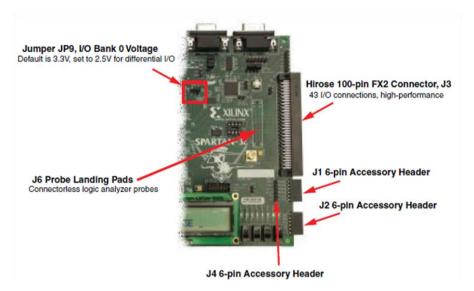

| 6.1    | Kit de Desenvolvimento Spartan-3e                          | <b>59</b> |

| 6.1.1. | FPGA Xilinx Spartan-3e XC3S500E                            |           |

|        | Oscilador de 50MHz                                         |           |

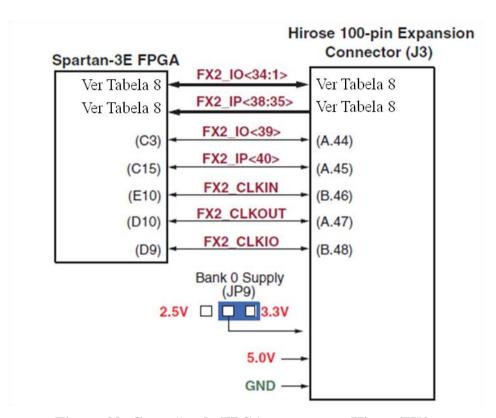

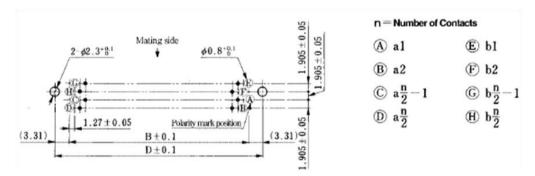

| 6.1.3. | Conector de Expansão Hirose FX2                            | 63        |

|        | Placa de Expansão                                          |           |

| 6.2.1. | Conector de Expansão Hirose FX2                            | 66        |

|        | Memória SRAM IS66WV25616BLL-55TLI                          |           |

| 6.2.3. | Memória Flash AM29LV040B-90JD                              | 69        |

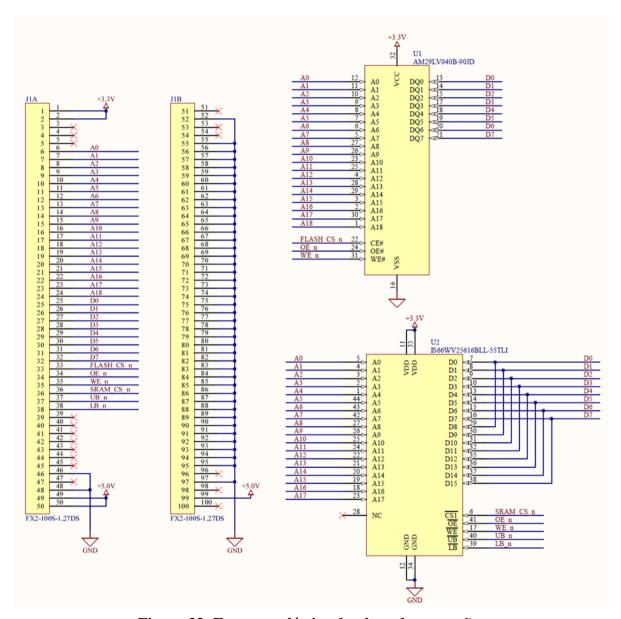

| 6.2.4. | Esquema Elétrico                                           | <b>70</b> |

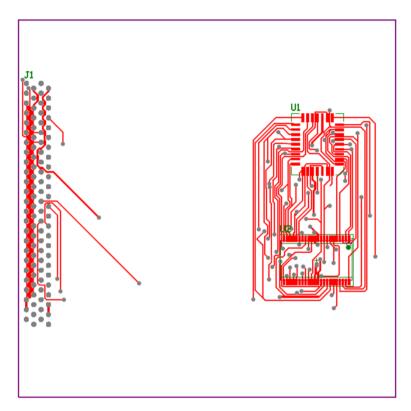

| 6.2.5. | Leiaute da Placa                                           | <b>73</b> |

| 7      | TESTES IMPLEMENTADOS                                       |           |

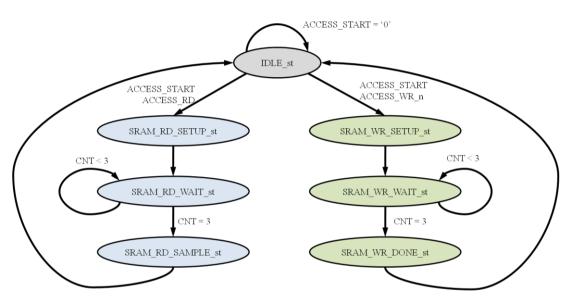

| 7.1    | Bloco de Acesso às Memórias (memory_access.vhd)            | <b>75</b> |

| 7.1.1. | Requisitos                                                 | <b>75</b> |

| 7.1.2. | Implementação                                              | <b>79</b> |

|        |                                                            |           |

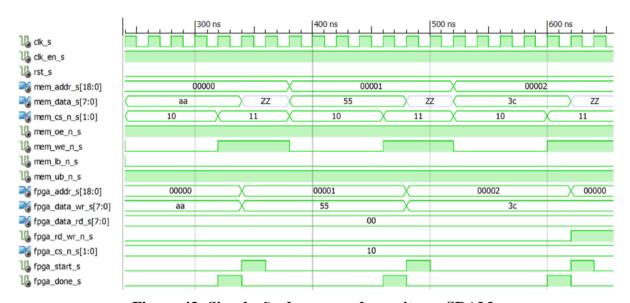

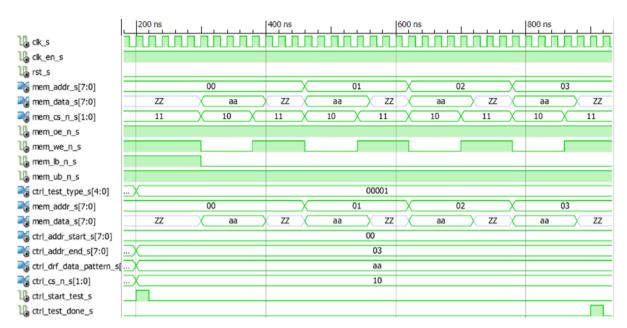

| 7.1.3. | Simulações                                   | 82 |

|--------|----------------------------------------------|----|

|        | Bloco de Teste de Memórias (memory_test.vhd) |    |

| 7.2.1. | Requisitos                                   | 84 |

| 7.2.2. | Implementação                                | 85 |

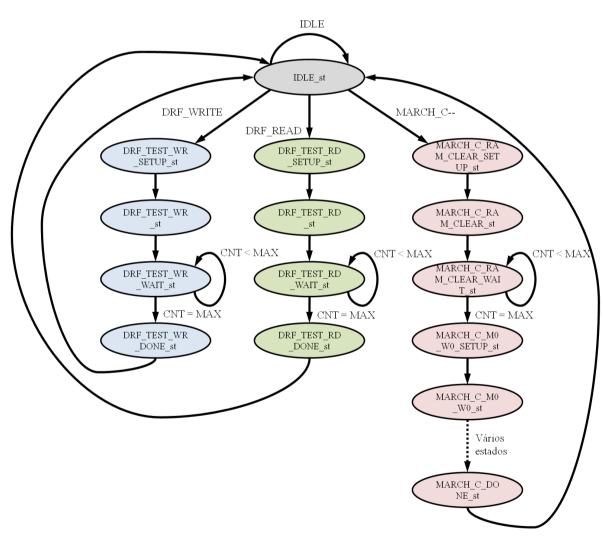

|        | Simulações                                   |    |

| 8      | RESULTADOS ALCANÇADOS                        | 92 |

| 9      | CONCLUSÃO                                    | 94 |

| REFE   | ERÊNCIAS                                     | 96 |

## LISTA DE ILUSTRAÇÕES

| Figura 1: Irradiador de raios gama a partir de Cobalto-60                             | 17   |

|---------------------------------------------------------------------------------------|------|

| Figura 2: Estrutura para realização dos testes nas memórias                           | 18   |

| Figura 3: Transistor MOS canal-n (NMOS)                                               | 19   |

| Figura 4: Efeitos da radiação ionizante no dióxido de silício                         | 21   |

| Figura 5: Criação de pares elétron-lacuna no óxido, recombinação dos mesmos, e poster |      |

| deslocamento e aprisionamento de lacunas na interface Si/SiO <sub>2</sub>             | 21   |

| Figura 6: Formação de canal em um transistor NMOS devida à presença de cargas positi  | ivas |

| aprisionadas no óxido junto à porta                                                   |      |

| Figura 7: Formação de canais parasitas devido a cargas aprisionadas no óxido de campo | , e  |

| consequente corrente de fuga.                                                         |      |

| Figura 8: Célula de memória SRAM                                                      | 24   |

| Figura 9: Célula de memória flash.                                                    | 25   |

| Figura 10: Processo de gravação de uma célula de memória flash                        | 26   |

| Figura 11: Processo de apagamento de uma célula de memória flash                      | 27   |

| Figura 12: Perda de carga negativa armazenada em células de memória flash causadas pe | or   |

| recombinação com lacunas liberadas pela radiação ionizante                            | 28   |

| Figura 13: Modelo funcional de uma memória.                                           | 29   |

| Figura 14: Modelo funcional simplificado de uma memória.                              | 30   |

| Figura 15: Diagrama de estados de uma célula sem falhas.                              |      |

| Figura 16: Diagrama de estados de uma célula que apresenta falha stuck-at 0           | 33   |

| Figura 17: Diagrama de estados de uma célula que apresenta falha stuck-at 1           | 33   |

| Figura 18: Diagrama de estados de uma falha na transição de subida <↑/0 >             | 34   |

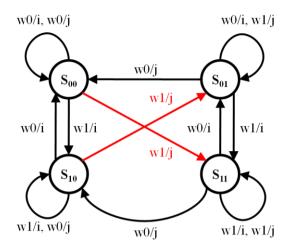

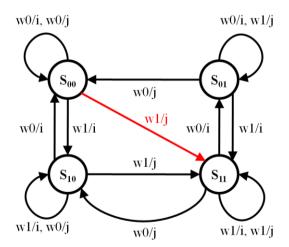

| Figura 19: Diagrama de estados de duas células que não apresentam falhas              | 36   |

| Figura 20: Diagrama de estados de uma falha CFin do tipo <1; \$\( \)>                 | 37   |

| Figura 21: Diagrama de estados de uma falha CFid do tipo <1; 1 >                      | 37   |

| Figura 22: Falhas no decodificador de endereços.                                      | 39   |

| Figura 23: Combinações de falhas no decodificador de endereços                        | 40   |

| Figura 24: Detecção de uma falha SA0 na célula (2,1) através de teste MATS+           | 47   |

| Figura 25: Kit de Desenvolvimento Xilinx Spartan-3e.                                  |      |

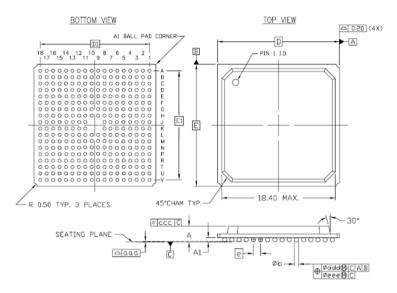

| Figura 26: FPGA Xilinx Spartan-3e XC3S500E FG320                                      |      |

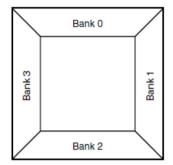

| Figura 27: Bancos de pinos de entrada/saída do XC3S500E FG320                         | 62   |

| Figura 28: Chave de seleção (JP9) da tensão do banco 0 (e da placa de expansão)       | 63   |

| Figura 29: Conexões do FPGA ao conector Hirose FX2.                                   |      |

| Figura 30: Leiaute para o conector Hirose FX2-100S-1.27DS.                            |      |

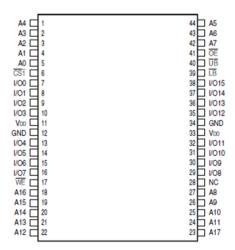

| Figura 31: Memória SRAM IS66WV25616BLL-55TLI.                                         |      |

| Figura 32: Memória Flash AM29LV040B-90JD.                                             |      |

| Figura 33: Esquema elétrico da placa de expansão.                                     |      |

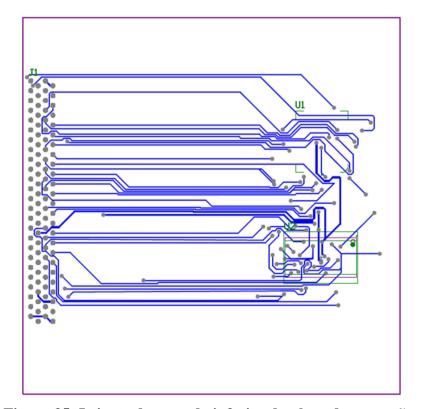

| Figura 34: Leiaute da camada superior da placa de expansão                            |      |

| Figura 35: Leiaute da camada inferior da placa de expansão.                           |      |

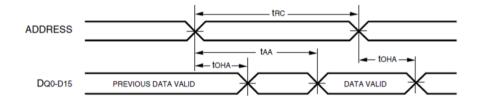

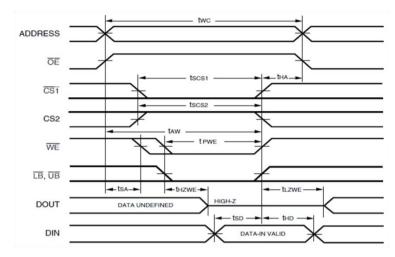

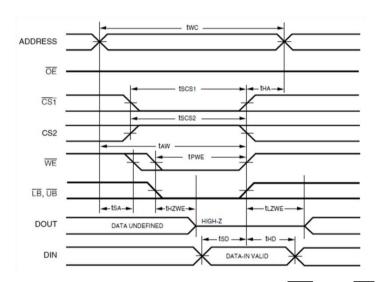

| Figura 36: Ciclo de leitura 1 para SRAM (controlado pelo endereço)                    |      |

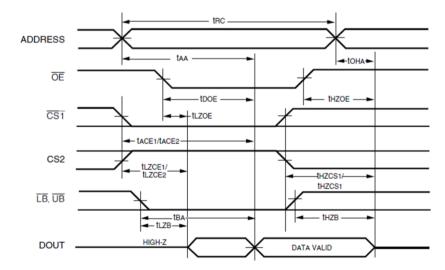

| Figura 37: Ciclo de leitura 2 para SRAM (controlado por CS1, CS2, OE, UB e LB)        |      |

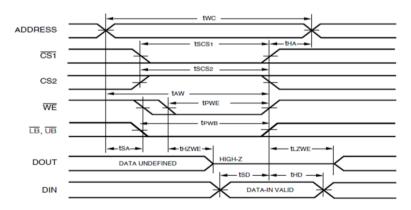

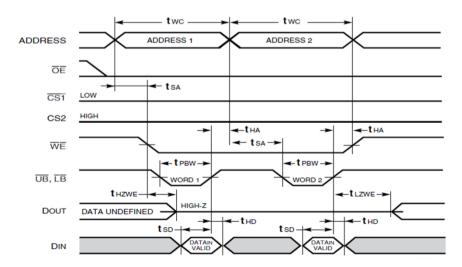

| Figura 38: Ciclo de escrita 1 para SRAM (controlado por CS1)                          | 77   |

| Figura 39: Ciclo de escrita 2 para SRAM (controlado por WE, com OE em nível alto)  | 78 |

|------------------------------------------------------------------------------------|----|

| Figura 40: Ciclo de escrita 3 para SRAM (controlado por WE, com OE em nível baixo) | 78 |

| Figura 41: Ciclo de escrita 4 para SRAM (controlado por UB e LB)                   | 78 |

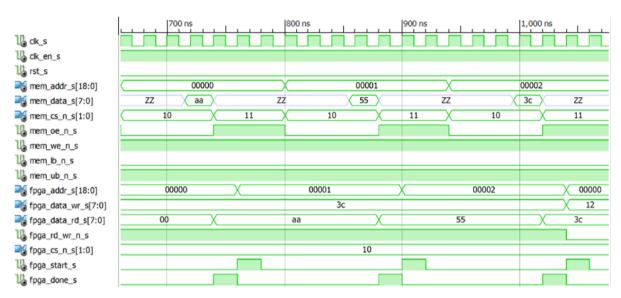

| Figura 42: Máquina de estados implementada no bloco de acesso às memórias          |    |

| (memory_access.vhd)                                                                | 81 |

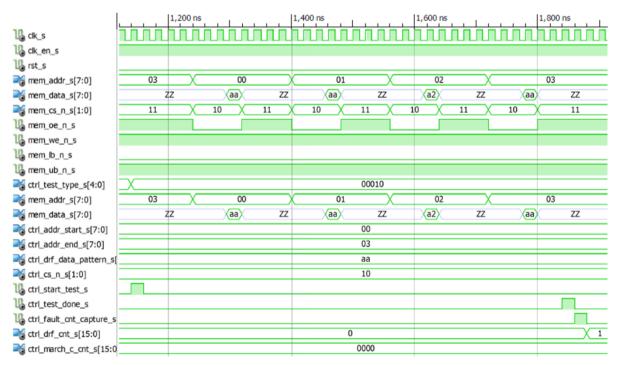

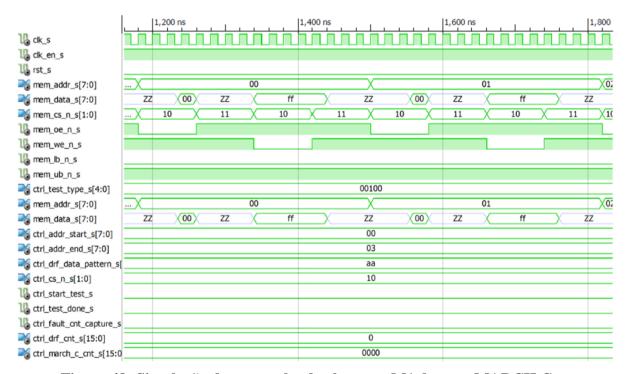

| Figura 43: Simulação de acessos de escrita na SRAM                                 | 83 |

| Figura 44: Simulação de acessos de leitura na SRAM                                 | 84 |

| Figura 45: Máquina de estados implementada no bloco de teste de memórias           |    |

| (memory_test.vhd)                                                                  | 87 |

| Figura 46: Simulação da etapa de escrita do teste de retenção de dados             | 89 |

| Figura 47: Simulação da etapa de leitura do teste de retenção de dados             | 89 |

| Figura 48: Simulação de um trecho do elemento M1 do teste MARCH C                  | 90 |

|                                                                                    |    |

## LISTA DE TABELAS

| Tabela 1: Falhas funcionais que podem ocorrer em memórias                              | 30 |

|----------------------------------------------------------------------------------------|----|

| Tabela 2: Conjunto reduzido de falhas funcionais de memórias                           | 31 |

| Tabela 3: Mapeamento de falhas funcionais no conjunto reduzido de falhas funcionais de |    |

| memórias                                                                               | 31 |

| Tabela 4: Algoritmos de alguns testes march.                                           | 45 |

| Tabela 5: Cobertura de falhas de alguns testes march                                   |    |

| Tabela 6: Duração total de alguns testes march executados em memórias de tamanhos e    |    |

| tempos de acesso diferentes                                                            | 46 |

| Tabela 7: Duração total de alguns testes march executados em memórias de tamanhos e    |    |

| tempos de acesso diferentes                                                            | 46 |

| Tabela 8: Conjunto mínimo de sinais necessários para atendimento às memórias           | 51 |

| Tabela 9: Níveis de tensão requeridos pela SRAM (V <sub>CC</sub> = 3.3V)               | 52 |

| Tabela 10: Níveis de tensão requeridos pela memória flash ( $V_{CC} = 3.3V$ )          | 52 |

| Tabela 11: Características do kit do Spartan-3e em relação aos requisitos do projeto   | 53 |

| Tabela 12: Conexões do FPGA ao conector Hirose FX2.                                    | 65 |

| Tabela 13: Sinais entre o FPGA e a placa de expansão                                   | 67 |

| Tabela 14: Função dos pinos da memória SRAM IS66WV25616BLL-55TLI                       | 69 |

| Tabela 15: Função dos pinos da memória Flash AM29LV040B-90JD.                          | 70 |

| Tabela 16: Conexões necessárias entre as memórias SRAM e Flash                         | 70 |

| Tabela 17: Conexões das memórias SRAM e Flash ao conector Hirose FX2                   | 71 |

| Tabela 18: Características temporais da SRAM em ciclos de leitura.                     | 77 |

| Tabela 19: Características temporais da SRAM em ciclos de escrita.                     | 79 |

| Tabela 20: Configurações (generics) do bloco de acesso às memórias                     | 80 |

| Tabela 21: Interface do bloco de acesso às memórias                                    | 80 |

| Tabela 22: Configurações (generics) do bloco de teste de memórias                      | 85 |

| Tabela 23: Interface do bloco de teste de memórias.                                    | 86 |

| Tabela 24: Resultados da síntese dos testes desenvolvidos                              | 93 |

#### LISTA DE ABREVIATURAS

AF: Address Decoder Fault

BF: Bridging Fault

CF: Coupling Fault

CFdyn: Dynamic Coupling Fault

CFid: Idempotent Coupling Fault

CFin: Inversion Coupling Fault

CLB: Configurable Logic Block

CPLD: Complex Programmable Logic Device

DCM: Digital Clock Manager

DCTA: Departamento de Ciência e Tecnologia Aeroespacial

DDR: Double Data Rate

DRAM: Dynamic Random Access Memory

**DRF**: Data Retention Fault

EEPROM: Electrically-Erasable Programmable Read-Only Memory

EPROM: Erasable Programmable Read-Only Memory

FBGA: Fine-Pitch Ball Grid Array

FPGA: Field Programmable Gate Array

IEAv: Instituto de Estudos Avançados

LED: Light-Emitting Diode

LUT: Look-Up Table

MOS: Metal Oxide Semiconductor

NMOS: Transistor MOS Canal N

NPSF: Neighborhood Pattern Sensitive Coupling Fault

PCI: Placa de Circuito Impresso

PLCC: Plastic Leaded Chip Carrier

PMOS: Transistor MOS Canal P

PROM: Programmable Read-Only Memory

**RAM: Random Access Memory**

**ROM: Read-Only Memory**

SAF: Stuck-At Fault

SCF: State Coupling Fault

SDRAM: Synchronous Dynamic Random Access Memory

SPI: Serial Peripheral Interface Bus

SRAM: Static Random Access Memory

TF: Transition Fault

TID: Total Ionizing Dose

TSOP: Thin Small-Outline Package

UFRGS: Universidade Federal do Rio Grande do Sul

USB: Universal Serial Bus

VGA: Video Graphics Array

VHDL: VHSIC Hardware Description Language

VHSIC: Very-High-Speed Integrated Circuit

#### 1 INTRODUÇÃO

#### 1.1 MOTIVAÇÃO

Nos dias atuais, a utilização de sistemas eletrônicos é cada vez mais massiva, a expansão da eletrônica de consumo faz com que a cada dia surjam diversos novos dispositivos, cada vez mais densos e integrados, para satisfazer os desejos da população. Com o aumento da utilização de circuitos eletrônicos, a sua utilização consequentemente se dá em ambientes cada vez mais variados. Estes ambientes vão desde residências, nas quais as condições ambientais são relativamente estáveis e controladas, a locais com condições não tão adequadas à operação normal de dispositivos semicondutores. Estes locais podem contar com temperaturas extremas, como automóveis ou indústrias, com pressões de valores distantes dos encontrados ao nível do mar ou até com presença de radiação ionizante em níveis críticos. Enfim, as condições podem ser adversas em vários sentidos.

Um dos mercados que opera em condições extremamente adversas é o de sistemas embarcados aeroespaciais, que podem ser dispositivos eletrônicos para aviões, satélites, naves e sondas espaciais. Nos ambientes frequentados por estes dispositivos as condições ambientais são extremamente diferentes das encontradas na superfície da Terra, em termos de temperatura, pressão, composição da atmosfera e, é claro, presença de radiação ionizante.

Os dispositivos eletrônicos em geral, por sua vez, cada vez mais empregam memórias em suas estruturas, sendo que elas podem ser utilizadas como componentes eletrônicos dedicados ou até mesmo blocos de um circuito integrado. Sistemas embarcados também necessitam de volumes cada vez maiores de memórias, tanto voláteis quanto não-voláteis, e SRAM e Flash são opções largamente empregadas. Sistemas embarcados aeroespaciais não são exceção à essa necessidade de armazenamento de dados, e também requerem cada vez mais espaço para isto.

Como no ambiente aeroespacial há a presença de níveis elevados de radiação ionizante, é imprescindível a análise do comportamento elétrico dos sistemas eletrônicos que são projetados para operar em tais condições, de forma que a radiação não venha a causar falhas nos circuitos. Um tipo de dispositivo eletrônico de grande importância para a operação de sistemas embarcados é a memória, volátil ou não-volátil, visto que as memórias são responsáveis por armazenar desde programas controladores de dispositivos críticos dos veículos aeroespaciais até dados e estatísticas das missões. Para garantir que o comportamento das memórias utilizadas neste tipo de aplicação será adequado é necessário efetuar testes para avaliação dos efeitos da radiação, através da aplicação de radiação ionizante e monitoramento do comportamento do componente eletrônico.

#### 1.2 OBJETIVOS

O objetivo deste projeto é de desenvolver uma plataforma para a realização de testes em alguns modelos de memórias submetidos a radiação ionizante, de forma a avaliar os efeitos de dose total ionizante (TID) nas memórias estudadas. Estas memórias foram selecionadas através de informações obtidas em contatos com Odair Lelis Gonçalez, pesquisador do Departamento de Ciência e Tecnologia Aeroespacial – DCTA, Instituto de Estudos Avançados – IEAv, localizado em São José dos Campos/SP, que informou alguns modelos que são comumente empregados em aplicações aeroespaciais. As informações a respeito dos componentes utilizados em satélites e outras aplicações aeroespaciais geralmente não são públicas, sendo desta forma importante obtê-las diretamente com pesquisadores do setor. Desta forma foram selecionadas duas memórias que devem ser previstas na plataforma de testes, sendo uma memória Flash (Spansion AM29LV040B-90JD) e uma SRAM (ISSI IS66WV25616BLL-55TLI).

Para alcançar este objetivo é imprescindível estudar os efeitos da radiação ionizante em transistores e células de memória, além dos tipos de teste empregados nas memórias que são objeto deste estudo. Após esta etapa de estudos é necessário realizar o levantamento e a seleção de alguns testes para aplicação nas memórias, que devem ser executados pela plataforma de teste. A plataforma a ser desenvolvida deve ser composta por um hardware que acomode as duas memórias que se deseja testar e que deve executar os testes selecionados para a avaliação das memórias.

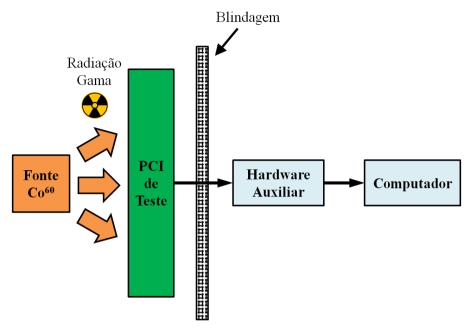

A plataforma de testes desenvolvida nesta etapa será utilizada para a realização de testes nas memórias sob o efeito de radiação ionizante, para verificar as consequências da dose total ionizante no comportamento das memórias. Com isso será possível avaliar a relação entre a dose de radiação aplicada e o número e os tipos de falhas que passam a ocorrer nos dispositivos. Para a geração da radiação ionizante será utilizada uma fonte de raios gama através de Cobalto-60, que consiste de um aparelho de radioterapia modificado para melhor atender aos requisitos dos testes, ilustrado na figura 1. Este equipamento produz um feixe de radiação altamente direcional, que será aplicado diretamente às memórias, conforme ilustrado na figura 2, que apresenta a estrutura necessária para a realização dos testes.

Figura 1: Irradiador de raios gama a partir de Cobalto-60.

Figura 2: Estrutura para realização dos testes nas memórias.

Assim sendo, a sequência de trabalho neste projeto, e que está retratada neste relatório inicia-se com o estudo dos efeitos da radiação ionizante em transistores MOS, passando para seus efeitos em memórias flash e SRAM. A etapa seguinte é o estudo dos tipos de falhas funcionais que podem vir a ocorrer em memórias, e a partir daí avaliar quais tipos de falhas podem vir a ocorrer provocadas por radiação. A seguir vem a etapa de estudo dos tipos de testes empregados em memórias, de forma a buscar tipos de testes que sejam adequados aos objetivos deste trabalho, ou seja, que não sejam de muito longa duração e que não sejam de implementação muito complexa e que exija muitos recursos.

A partir da definição dos testes a etapa seguinte é a de definição das memórias flash e SRAM que terão utilização prevista na plataforma de testes, e a partir da definição das mesmas pode-se selecionar a tecnologia empregada na plataforma e realizar as definições finais das especificações de hardware, procedendo com seu desenvolvimento. A última etapa é selecionar os testes a serem implementados, cuja complexidade deve estar de acordo com o tempo disponível para o desenvolvimento dos mesmos.

#### 2 EFEITOS DA RADIAÇÃO IONIZANTE EM SEMICONDUTORES

#### 2.1 EFEITOS DA RADIAÇÃO IONIZANTE EM TRANSISTORES MOS

Existem diversas formas de radiação ionizante, e cada uma delas produz determinados efeitos em dispositivos semicondutores. A radiação ionizante pode ser formada por raios gama, raios-x, partículas alfa e outros tipos de partículas pesadas. As partículas pesadas, como íons e prótons, produzem efeitos nos semicondutores que são detectados logo após o mesmo ser submetido à radiação. Estes efeitos podem ser destrutivos ou não, e não serão estudados neste trabalho.

Outro tipo de efeito que pode vir a ocorrer em dispositivos semicondutores é o efeito de dose total ionizante, causado geralmente por raios gama ou raios-x. Este efeito caracteriza-se por não causar falhas imediatamente após o início da exposição do dispositivo à radiação. Seus efeitos são, como seu próprio nome indica, causados pela dose total de radiação acumulada no semicondutor, ou seja, apenas após um certo tempo de irradiação o semicondutor começa a apresentar falhas.

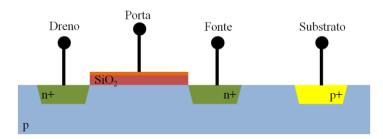

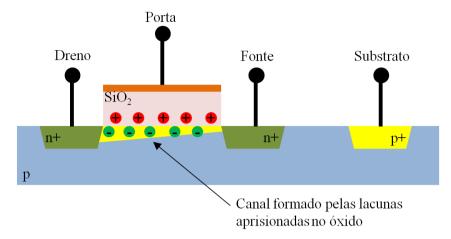

Nos transistores MOS (Metal-Oxide Semiconductor) a dose total ionizante tem como efeito principal e característico a ionização das camadas de óxido que são utilizadas como camadas isolantes na construção destes componentes, geralmente constituídas por dióxido de silício (SiO<sub>2</sub>). A figura 3 apresenta a vista em corte de um transistor MOS canal-n (NMOS), no qual pode ser visto o óxido que separa a porta do transistor da região do canal.

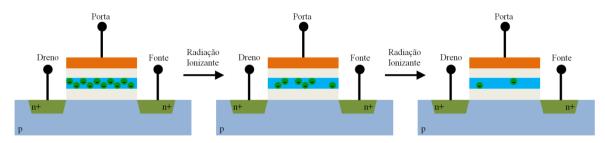

Figura 3: Transistor MOS canal-n (NMOS).

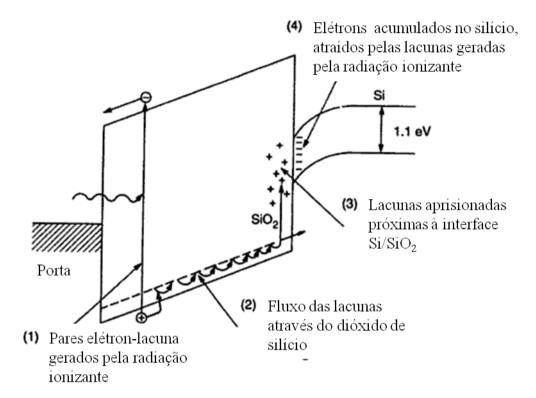

Quando um transistor MOS é submetido a um ambiente com radiação ionizante de alta energia, esta radiação acaba por retirar elétrons da camada de valência do óxido isolante, levando-os à banda de condução. Com isso, é gerado um par elétron-lacuna na região do dióxido de silício. Grande parte dos elétrons gerados, visto que possuem grande mobilidade (comparados às lacunas), acaba por ser drenada pela porta do transistor em um intervalo de tempo muito pequeno. Uma outra parte destes elétrons por sua vez acaba sofrendo recombinação com as lacunas geradas, de forma que resta no óxido um número menor de lacunas do que foi gerado inicialmente. Estas lacunas restantes, por sua vez, acabam por se locomover até a região próxima à interface com o silício que compõe o canal do transistor, de forma a formar uma camada de cargas positivas junto ao canal. Esta camada de cargas positivas, por sua vez, age com as cargas presentes no silício, de forma que ela acaba por alterar a tensão de limiar do transistor que está no ambiente de radiação. Mesmo que o número de cargas positivas seja pequeno, se o tempo de exposição à radiação for suficientemente grande haverá influência significativa na tensão de limiar, o que causará problemas ao funcionamento do circuito eletrônico no qual o transistor está inserido. Caso a dose de radiação acumulada seja ainda maior, este transistor pode ter tanta carga acumulada em seu óxido que nem as tensões limite do circuito eletrônico podem ser capazes de formar ou extinguir o canal, de forma que o transistor ficará travado em um estado, que pode ser ativo ou inativo. A figura 4 mostra o efeito da radiação no dióxido de silício, com a geração de pares elétron-lacuna e a acumulação de cargas positivas junto à interface do óxido com o canal do transistor. A figura 5, por sua vez, apresenta o processo que ocorre no óxido por etapas, mostrando a geração dos pares elétron-lacuna, a recombinação e a presença de cargas acumuladas no óxido. Já a figura 6 é responsável por ilustrar a presença de cargas positivas aprisionadas no óxido isolante de um transistor NMOS, e seu efeito na formação de canal do referido transistor. Neste caso a presença de cargas é tamanha que já é capaz de formar o canal de condução entre dreno e fonte mesmo sem a presença de tensão na porta.

Figura 4: Efeitos da radiação ionizante no dióxido de silício.

Figura 5: Criação de pares elétron-lacuna no óxido, recombinação dos mesmos, e posterior deslocamento e aprisionamento de lacunas na interface Si/SiO<sub>2</sub>.

Figura 6: Formação de canal em um transistor NMOS devida à presença de cargas positivas aprisionadas no óxido junto à porta.

Em transistores NMOS a alteração na tensão de limiar se dá de forma que é necessária uma tensão menos positiva no gate, devido à presença de cargas aprisionadas no óxido, para a formação do canal. Em casos extremos o travamento do transistor se dá com o canal formado, ou seja, o transistor sempre estará ligado, visto que haverá tantas cargas positivas no dióxido de silício que o canal sempre estará formado. Em transistores PMOS o efeito é inverso, visto que para a formação do canal são necessárias tensões de porta negativas, de forma a atrair os portadores minoritários negativos para formarem o canal. Como haverá cargas positivas aprisionadas junto à interface Si/SiO<sub>2</sub>, será necessária uma tensão ainda mais negativa para formar o canal, de forma que em casos extremos torna-se impossível formar o canal, ou seja, o transistor estará sempre desligado.

Além do efeito da alteração na tensão de limiar e possível travamento dos transistores expostos à radiação, são observados outros efeitos no funcionamento destes dispositivos. O principal deles é o aumento da corrente de fuga, especialmente entre dreno e fonte. Como pode haver formação de canal apenas pelo efeito das cargas aprisionadas no óxido, podem surgir correntes de fuga no dispositivo mesmo que não esteja sendo aplicada na porta uma tensão para provocar a formação do canal. Este efeito é verificado em transistores NMOS, visto que em transistores PMOS a presença de cargas positivas aprisionadas no óxido não irá

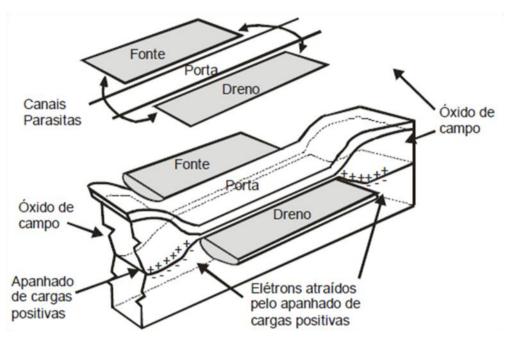

produzir efeitos de formação de canal. Além disso, a corrente de fuga pode surgir devido ao surgimento de canais parasitas no óxido de campo que tem como função isolar transistores adjacentes, o que é mostrado na figura 7. Como há a presença de óxido nesta região, nela também pode ocorrer o aprisionamento de cargas positivas, que acabam por atrair portadores minoritários do substrato e formando caminhos para a corrente de fuga. Da mesma forma, este efeito também é característico de transistores NMOS.

Figura 7: Formação de canais parasitas devido a cargas aprisionadas no óxido de campo, e consequente corrente de fuga.

#### 2.2 EFEITOS DA RADIAÇÃO IONIZANTE EM MEMÓRIAS SRAM

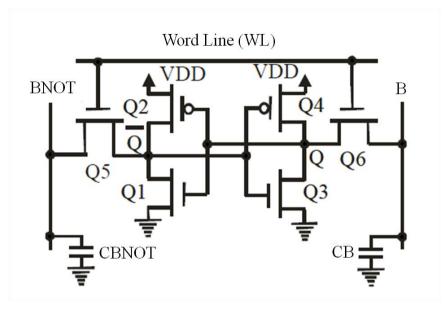

A célula de memória SRAM, ilustrada na figura 8, é constituída por seis transistores MOS, sendo formada por dois inversores lógicos realimentados, cada um formado por dois transistores, um NMOS e um PMOS, e dois transistores responsáveis por ligar a célula de memória às linhas de dados, chamadas de *bit lines* (BL e  $\overline{BL}$ ). Estes dois transistores são acionados pela *word line* (WL), que é a linha de endereçamento.

Figura 8: Célula de memória SRAM.

Uma memória SRAM é composta por uma matriz de células de memória que compõem sua capacidade de armazenamento e por diversos circuitos auxiliares, responsáveis pela interface entre a matriz de células e os pinos de acesso do circuito integrado. Estes circuitos são decodificadores de endereço, que controlam o acesso às *word lines*, circuitos detectores do sinal armazenado nos inversores (células de memória) e multiplexadores de linhas de dados, além de máquinas de controle responsáveis por realizar a interface dos dispositivos externos com a célula de memória. Desta forma, há diversos circuitos eletrônicos e uma grande quantidade de transistores utilizados em diversas aplicações que podem vir a ser afetados pelos efeitos de dose total ionizante caso a memória venha a ser utilizada em ambientes com radiação ionizante.

Cada um dos circuitos periféricos pode vir a falhar, o que pode causar erros no endereçamento da célula de memória que se deseja ler, ou fazer com que duas linhas de dados sejam acessadas simultaneamente, caso os transistores dos multiplexadores das linhas de dado entrem em condução conjuntamente. Desta forma, podem ocorrer falhas de diversos tipos, que serão descritas no capítulo 3 deste trabalho. Além disso, a própria célula de memória

pode vir a apresentar falhas, visto que seus transistores também podem vir a ter suas tensões de limiar alteradas devido ao efeito de dose total ionizante. Desta forma pode ocorrer a perda do dado armazenado naquela célula.

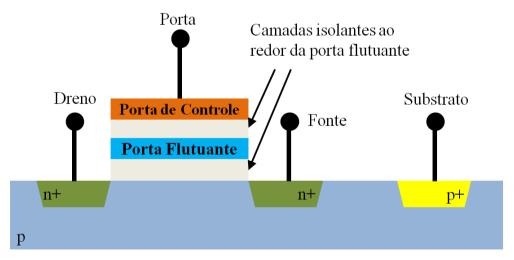

#### 2.3 EFEITOS DA RADIAÇÃO IONIZANTE EM MEMÓRIAS FLASH

Células de memória flash são transistores MOS de porta flutuante. Este tipo de transistor possui uma característica construtiva diferente dos transistores tradicionais, visto que possuem entre a porta do transistor e a região do canal uma outra região semicondutora, chamada de porta flutuante, envolta por material isolante (dióxido de silício). Esta porta flutuante é responsável pelo armazenamento de dados na célula de memória, visto que ela pode estar sem nenhum tipo de carga elétrica armazenada ou com elétrons, que ficam aprisionados nela devido à presença de camadas isolantes ao redor da porta flutuante. Desta forma a célula de memória é composta por apenas um transistor, ilustrado na figura 9.

Figura 9: Célula de memória flash.

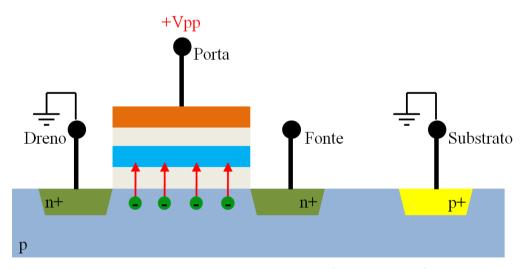

Para efetuar a gravação (inserção de cargas na porta flutuante) ou o apagamento (retirada de cargas da porta flutuante) de uma célula de memória são necessárias tensões mais elevadas que as tensões normais de leitura da memória, visto que é necessário fazer com que

os elétrons atravessem as camadas isolantes ao redor da porta flutuante, ou seja, é necessária uma maior quantidade de energia para causar o tunelamento dos mesmos. Desta forma, além dos circuitos periféricos existentes nas memórias SRAM há também a necessidade de circuitos elevadores de tensão, chamados de *charge pumps*, para efetuar a gravação ou apagamento das células de memória. Por este motivo as memórias flash requerem um protocolo para gravação, que faz com que a máquina de controle ative estes circuitos para efetuar a gravação ou apagamento. Isto faz com que os procedimentos de gravação e apagamento demandem um tempo elevado em comparação ao procedimento de leitura, especialmente se a gravação ou apagamento for feita em blocos pequenos de endereços. Na figura 10 está ilustrada uma célula de memória flash em um tipo de processo de gravação (inserção de cargas negativas na porta flutuante), e na figura 11 é mostrado um tipo de processo de apagamento (retirada dos elétrons aprisionados na célula de memória).

Figura 10: Processo de gravação de uma célula de memória flash.

As memórias flash estão sujeitas aos mesmos tipos de falhas que os já citados para as memórias SRAM, como falhas no decodificador de endereços e nos multiplexadores de

dados. Além disso, os *charge pumps* são dispositivos bastante sujeitos a falhas devido à presença de radiação ionizante, conforme descrito por (NGUYEM, 1998).

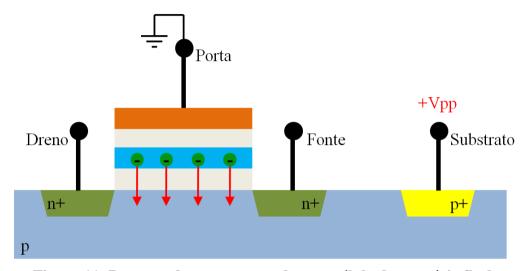

Figura 11: Processo de apagamento de uma célula de memória flash.

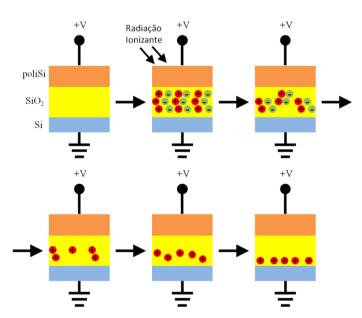

Como as memórias flash armazenam dados na forma de elétrons (ou falta deles) aprisionados em uma região condutora isolada da porta e do canal, há uma outra possibilidade de falha que surge da possibilidade desta carga armazenada ser retirada da porta flutuante. Isto pode ocorrer devido ao efeito de dose total ionizante, visto que ele é responsável pela geração de cargas positivas nas regiões isolantes do transistor (dióxido de silício). Como estas cargas positivas ficam aprisionadas no óxido elas podem ser atraídas pelas cargas negativas armazenadas na porta flutuante, e assim pode ocorrer a recombinação entre os elétrons armazenados e as lacunas geradas pela radiação ionizante. Desta maneira pode ocorrer a perda dos dados armazenados nas células de memória flash. Na figura 12 é ilustrado este efeito de geração de cargas positivas no óxido e recombinação das mesmas com as cargas negativas (elétrons) armazenadas na porta flutuante da célula de memória.

Figura 12: Perda de carga negativa armazenada em células de memória flash causadas por recombinação com lacunas liberadas pela radiação ionizante.

#### 3 FALHAS EM MEMÓRIAS

Como a única forma disponível de testar os componentes eletrônicos é através da excitação e leitura de seus terminais externos, não sendo possível examinar o silício do componente, qualquer teste será realizado de forma a comparar o comportamento da memória em teste com seu comportamento ideal. Logo, qualquer tipo de falha que venha a ser detectado será de nível funcional, e não de nível físico.

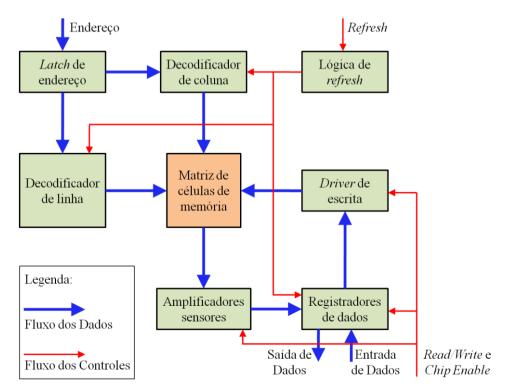

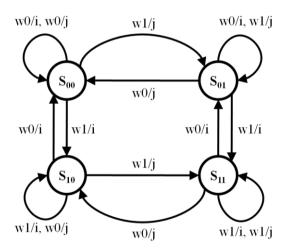

Neste trabalho será utilizado o modelo funcional de falhas, também conhecido como modelo *gray-box*, apresentado em (BUSHNELL, 2000). A figura 13 ilustra o modelo funcional de uma memória dinâmica, e a figura 14 ilustra o mesmo modelo de forma simplificada. O modelo da figura 13 ilustra uma DRAM, mas ele pode ser utilizado para memórias do tipo ROM, EPROM e EEPROM retirando alguns blocos do modelo, além de poder ser utilizado para memórias do tipo SRAM através da retirada do bloco da lógica de regravação (*refresh logic*).

Figura 13: Modelo funcional de uma memória.

Figura 14: Modelo funcional simplificado de uma memória.

Existem diversos tipos de falhas funcionais que podem ocorrer em uma memória. Os principais deles estão listados na tabela 1. Uma célula pode ser tanto uma célula de memória quanto um registrador, enquanto uma linha é uma conexão física na memória. Estas falhas podem ser sintetizadas em um conjunto reduzido de falhas funcionais, que está de acordo com o modelo da figura 14 e listado na tabela 2. Estes dois conjuntos de falhas funcionais podem ser relacionados, visto que cada item do conjunto reduzido de falhas funcionais engloba um ou mais tipos de falhas, e este mapeamento de falhas está listado na tabela 3.

Tabela 1: Falhas funcionais que podem ocorrer em memórias.

|   | Falha funcional                      |  |   | Falha funcional                                                 |

|---|--------------------------------------|--|---|-----------------------------------------------------------------|

| a | Travamento da célula                 |  | i | Travamento da linha de endereço                                 |

| b | Travamento do <i>driver</i>          |  | j | Circuito aberto na linha de endereço                            |

| c | Travamento da linha read/write       |  | k | Curto-circuito entre linhas de endereço                         |

| d | Travamento da linha chip-select      |  | 1 | Circuito aberto no decodificador                                |

| e | Travamento da linha de dados         |  | m | Acesso a endereço incorreto                                     |

| f | Circuito aberto na linha de dados    |  | n | Acesso a múltiplos endereços simultaneamente                    |

| g | Curto-circuito entre linhas de dados |  | O | A célula pode ser colocada em 0 mas<br>não em 1 (ou vice-versa) |

| h | Crosstalk entre linhas de dados      |  | p | Interação sensível a padrões entre células                      |

Tabela 2: Conjunto reduzido de falhas funcionais de memórias.

| Notação | Falha                                                     |

|---------|-----------------------------------------------------------|

| SAF     | Falha de travamento                                       |

| TF      | Falha de transição                                        |

| CF      | Falha por acoplamento                                     |

| NPSF    | Falha por acomplamento sensível aos padrões da vizinhança |

Tabela 3: Mapeamento de falhas funcionais no conjunto reduzido de falhas funcionais de memórias.

| Falha funcional do conjunto reduzido |   | Falha funcional                                        |

|--------------------------------------|---|--------------------------------------------------------|

| SAF                                  | a | Travamento da célula                                   |

| SAF                                  | b | Travamento do driver                                   |

| SAF                                  | c | Travamento da linha read/write                         |

| SAF                                  | d | Travamento da linha chip-select                        |

| SAF                                  | e | Travamento da linha de dados                           |

| SAF                                  | f | Circuito aberto na linha de dados                      |

| CF                                   | g | Curto-circuito entre linhas de dados                   |

| CF                                   | h | Crosstalk entre linhas de dados                        |

| AF                                   | i | Travamento da linha de endereço                        |

| AF                                   | j | Circuito aberto na linha de endereço                   |

| AF                                   | k | Curto-circuito entre linhas de endereço                |

| AF                                   | 1 | Circuito aberto no decodificador                       |

| AF                                   | m | Acesso a endereço incorreto                            |

| AF                                   | n | Acesso a múltiplos endereços simultaneamente           |

| TF                                   |   | A célula pode ser colocada em 0 mas não em 1 (ou vice- |

| 11                                   | 0 | versa)                                                 |

| NPSF                                 | p | Interação sensível a padrões entre células             |

#### 3.1 NOTAÇÃO DAS FALHAS

Para descrever as falhas que podem ocorrer em uma memória, utilizaremos a seguinte notação:

- r0 Operação de leitura em um endereço de memória, esperando o valor 0;

- r1 Operação de leitura em um endereço de memória, esperando o valor 1;

- w0 Operação de escrita do valor 0 em um endereço de memória;

- w1 Operação de escrita do valor 1 em um endereço de memória;

- 1 Transição de 0 para 1 no valor armazenado em uma célula;

- 1 Transição de 1 para 0 no valor armazenado em uma célula;

- \$\frac{1}{2}\$ O valor armazenado em uma célula passa a ser seu complemento;

- 1 O endereçamento da memória deve ser incrementado a cada operação;

- ↓ O endereçamento da memória deve ser decrementado a cada operação;

- • O endereçamento da memória pode ser incrementado ou decrementado a

cada operação.

→ Escrita de um valor 0 em uma célula que já o contém;

- $\forall$  Indica qualquer operação de escrita na memória:  $\forall \in \{\uparrow, \downarrow, \uparrow, \rightarrow, \rightarrow, \Rightarrow\}$ ;

- < ··· > Representa uma falha qualquer, que deve ser descrita no lugar do símbolo (...);

- < I/F > Representa uma falha, conforme notação acima, sendo que I é a condição para que a falha se manifeste, e F é o valor da célula durante a ocorrência da falha. I ∈ {↑, ↓, ↑, →, →, ⇒} e F ∈ {0,1,↑,↓,↑};

- < I1, ..., In 1; In/F > Representa uma falha, conforme notação acima, envolvendo n células de memória. I1, ..., In 1 são as condições para que a falha na célula n se manifeste, enquanto que In é a condição que deve ocorrer na própria célula para potencializar a ocorrência da falha. Caso a própria célula não tenha influência nas falhas, então o campo In/F passa a ser escrito apenas como F.

- n Número de endereços de memória de um determinado componente. No caso de memórias orientadas a bit é o próprio número de células de memória.

#### 3.2 FALHAS DE VALOR FIXO

As falhas de valor fixo (*Stuck-At Faults* – SAF) são aquelas nas quais o valor de uma célula ou de uma linha é sempre lido como 0 (falha chamada de *stuck-at 0* - SA0) ou 1 (chamada de *stuck-at 1* - SA1), independente de qualquer escrita que seja realizada no

referido endereço. Enfim, a célula (ou linha) está permanentemente no estado de falha, que não pode ser modificado.

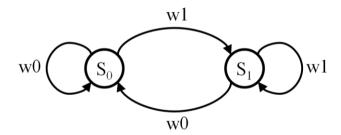

As falhas SA0 são descritas pela notação  $< \forall /0 >$ , e as falhas SA1 são descritas pela notação  $< \forall /1 >$ , que afirmam que para qualquer ação tomada sobre aquele referido endereço sua resposta sempre será 0 (para SA0) ou 1 (para SA1). Na figura 15 temos o diagrama de estados de uma célula com comportamento adequado, para comparação com os as células que apresentam falhas. Na figura 16 pode ser observado o diagrama de estados de uma célula com falha do tipo SA0, e na figura 17 temos o diagrama de uma célula com falha SA1.

Figura 15: Diagrama de estados de uma célula sem falhas.

Figura 16: Diagrama de estados de uma célula que apresenta falha stuck-at 0.

Figura 17: Diagrama de estados de uma célula que apresenta falha stuck-at 1.

Para que um teste seja capaz de detectar e localizar qualquer tipo de *stuck-at faults* a condição é que, para cada célula de memória, um valor lógico 0 e um valor lógico 1 devem ser lidos.

Este tipo de falha pode ocorrer devido a problemas de fabricação, mas também pode ser causado pelos efeitos da radiação ionizante, visto que os circuitos de decodificação e multiplexação dos barramentos de dados podem ter seus transistores afetados pelos efeitos da radiação. Além disso, os transistores das células de memória SRAM podem ter seu comportamento afetado pelos efeitos da TID, de forma a apresentarem este tipo de falha. Também podemos citar o fato de que o transistor de porta flutuante das memórias flash pode ter sua tensão de limiar alterada devido aos efeitos da TID, ou até ficar travado em casos extremos, portanto este tipo de falha pode ser provocado por radiação tanto em memórias flash quanto em SRAMs.

#### 3.3 FALHAS DE TRANSIÇÃO

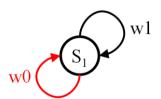

A falha de transição (transition fault - TF) é um caso especial das falhas SAF. Ela ocorre quando uma célula de memória não consegue efetuar uma transição de subida ou de descida ao ser escrita. A notação para uma falha na transição de subida, cujo diagrama de estados é mostrado na figura 18, é  $<\uparrow/0>$ , e a para uma falha na transição de descida a notação é  $<\downarrow/0>$ .

Figura 18: Diagrama de estados de uma falha na transição de subida  $<\uparrow/0>$ .

Para que um teste seja capaz de detectar e localizar todos os tipos de falha de transição ele deve realizar, em cada célula, uma transição de subida (↑) e uma transição de descida (↓), e ler a célula imediatamente após efetuar a transição, antes de efetuar qualquer outra escrita, para evitar que outros tipos de falha possam mascarar a ocorrência da falha de transição.

Este tipo de falha pode ocorrer devido a problemas de fabricação, mas também pode ser causado pelos efeitos da radiação ionizante, visto que os circuitos de decodificação e multiplexação dos barramentos de dados podem ter seus transistores afetados pelos efeitos da radiação. Além disso, os transistores das células de memória SRAM podem ter seu comportamento afetado pelos efeitos da TID, de forma a apresentarem este tipo de falha.

#### 3.4 FALHAS POR ACOPLAMENTO

As falhas por acoplamento (*Coupling Faults* – CF) ocorrem quando a transição em um bit de memória, ocorrida durante um processo de escrita neste bit, causa uma transição indesejada em outro(s) bit(s) da memória. Existem diversos tipos de falhas por acoplamento, alguns envolvendo apenas duas células (uma agressora e uma vítima) e outros envolvendo diversas células.

Analisando o conceito de falhas por acoplamento pode-se concluir que é possível que elas sejam causadas pelos efeitos da radiação ionizante. Sua principal causa é a existência de curtos-circuitos ou capacitâncias parasitas entre células e/ou linhas de dados ou endereçamento próximas. Como a radiação ionizante tem efeitos na presença de cargas elétricas armazenadas nos óxidos que são utilizados como isolantes entre transistores ou ligações elétricas adjacentes nos dispositivos semicondutores, pode ser considerado que a alteração da presença de cargas elétricas nestes isolantes pode potencializar uma falha do tipo. A seguir serão analisados e descritos os diversos tipos de falhas por acoplamento.

#### 3.4.1. Falhas de Inversão por Acoplamento

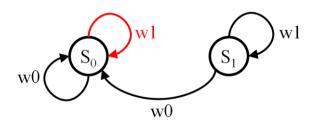

As falhas de inversão por acoplamento (*inversion coupling faults – CFin*) são provocadas por uma transição de subida ou de descida na célula agressora j, que causa a inversão do conteúdo da célula vítima i. Existem dois tipos de falhas CFin, o causado por uma transição de subida, que possui a notação  $<\uparrow; \updownarrow>$ , e o causado por uma transição de descida, descrito pela notação  $<\downarrow; \updownarrow>$ . O símbolo ( $\updownarrow$ ) indica que o conteúdo da célula vítima i é invertido, independente do seu valor anterior à falha. A figura 19 mostra o diagrama de estados de um par de células que não apresentam nenhum tipo de falha, para comparação com os diagramas das células com falhas. A figura 20 tem por objetivo ilustrar a ocorrência de uma falha CFin causada por transição de subida na célula agressora, ou seja, uma falha  $<\uparrow; \updownarrow>$ .

Figura 19: Diagrama de estados de duas células que não apresentam falhas.

Para que um teste detecte todas as ocorrências de falhas CFin, ele deve efetuar a leitura de todas as células que estão potencialmente acopladas entre si após a ocorrência de uma possível CFin devido à escrita nas céluas agressoras, e o número de transições nas células acopladas deve ser ímpar, de forma a prevenir que as falhas mascarem umas às outras.

Figura 20: Diagrama de estados de uma falha CFin do tipo <↑; ↓>.

### 3.4.2. Falhas de Valor Armazenado por Acoplamento

Falhas de valor armazenado por acoplamento (*idempotent coupling faults* – CFid) ocorrem quando uma transição de subida ou de descida na célula agressora j faz com que o valor armazenado célula vítima i passe para 0 ( $<\uparrow$ ; 0 > ou  $<\downarrow$ ; 0 >) ou 1 ( $<\uparrow$ ; 1 >).

Figura 21: Diagrama de estados de uma falha CFid do tipo < $\uparrow$ ; 1 >.

Um teste que seja capaz de detectar todas as ocorrências possíveis de CFid deve ler cada célula acoplada após escritas nas células agressoras que podem causar a ocorrêcia de

uma série de falhas CFid, evitando que haja múltiplas falhas que podem mascarar umas às outras.

### 3.4.3. Falhas por Acoplamento Dinâmicas

As falhas por acoplamento dinâmicas (*dynamic coupling faults* – CFdyn) ocorrem entre células que estão em diferentes palavras da memória, e são causadas quando uma operação qualquer, de escrita ou de leitura, efetuada na célula agressora faz com que o conteúdo da célula vítima seja passado para 0 ou para 1. Este tipo de falha é um caso mais geral de falhas CFid, sendo causado tanto por operações de leitura quanto de escrita, enquanto as falhas CFid são causadas apenas por operações de escrita.

# 3.4.4. Falhas de Ligação

As falhas de ligação (*Bridging Faults* – BF) são curto-circuitos entre duas ou mais células de memória ou linhas de endereçamento ou de dados. Estas falhas são caracterizadas pelo fato de que qualquer ação tomada em uma das células será efetuada em todas as outras, seja esta operação de escrita ou de leitura.

### 3.4.5. Falhas de Estado por Acoplamento

As falhas de estado por acoplamento (*state coupling faults* – SCF) ocorrem quando uma célula agressora j que está com um determinado nível lógico faz com que a célula vítima i fique com um determinado nível lógico, 0 ou 1. Há quatro tipos de SCFs, descritos por <0;0>,<0;1>,<1;0>e<1;1>.

#### 3.5 FALHAS POR ACOPLAMENTO SENSÍVEIS AOS PADRÕES DA VIZINHANCA

Este tipo de falha, cuja sigla é NSPF (Neighborhood Pattern Sensitive Coupling Fault), caracteriza-se pelo fato de que o conteúdo da célula vítima i é influenciado pelo

conteúdo de todas as outras células de memória, que podem possuir o valor 0, o valor 1 ou estar transicionando. Este tipo de falha é de detecção bastante difícil, devido à necessidade de gerar todos os padrões de vizinhança possíveis para todas as células do componente. Devido a este fato, este tipo de falha não será considerado no desenvolvimento da plataforma de testes.

### 3.6 FALHAS NO DECODIFICADOR DE ENDEREÇO

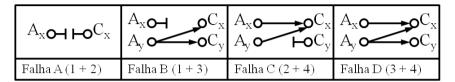

Estas falhas, conhecidas por AF (*address decoder faults*), ocorrem quando há um erro na decodificação do endereço que se deseja acessar. Para uma abordagem em termos de falhas funcionais é necessário assumir que elas se dêem tanto nas operações de escrita quanto nas de leitura. Existem basicamente quatro casos de falhas deste tipo, ilustradas na figura 22:

- Falha 1: Nenhuma célula de memória é acessada por um determinado endereço;

- Falha 2: Nenhum endereço é capaz de acessar uma determinada célula;

- Falha 3: Um endereço acessa mais de uma célula simultaneamente;

- Falha 4: Uma célula pode ser acessada a partir de diversos endereços.

| A <sub>x</sub> <b>0</b> —                       | ├ <b>~</b> C <sub>x</sub>                                 | $A_y$ $C_x$ $C_y$                   | $A_x$ $A_y$ $C_x$                 |

|-------------------------------------------------|-----------------------------------------------------------|-------------------------------------|-----------------------------------|

| Falha 1                                         | Falha 2                                                   | Falha 3                             | Falha 4                           |

| Nenhuma célula é<br>acessada por A <sub>x</sub> | Nenhum endereço acessa a célula $\mathrm{C}_{\mathrm{x}}$ | $A_{ m x}$ acessa várias<br>células | $V$ ários endereços acessam $C_x$ |

Figura 22: Falhas no decodificador de endereços.

Para cobrir todos os tipos de falhas possíveis, basta que sejam verificadas as seguintes combinações de falhas, que estão ilustradas na figura 23:

- Falha A: Falha 1 + Falha 2;

- Falha B: Falha 1 + Falha 3;

- Falha C: Falha 2 + Falha 4;

- Falha D: Falha 3 + Falha 4.

Figura 23: Combinações de falhas no decodificador de endereços.

Para que sejam testadas todas as possibilidades de falhas no decodificador de endereços, é necessária a execução de um teste march que possua os seguintes elementos march:

- $\uparrow (rx, ..., w\overline{x});$

- $\psi$   $(r\overline{x}, ..., wx).$

Os testes march, suas etapas e seus elementos serão explicados no capítulo 4 deste relatório, e a prova de que um teste que possua os elementos descritos acima é capaz de detectar todas as ocorrências de falhas no decodificador de endereços está em (BUSHNELL, 2000).

Como os efeitos da radiação ionizante atuam também nos transistores dos circuitos decodificadores de endereço podemos facilmente concluir que este é um tipo de falha que pode ser causado pelos efeitos da radiação.

### 3.7 FALHAS DE RETENÇÃO DE DADOS

As falhas de retenção de dados (*data retention faults* – DRF) são caracterizadas pela perda do dado armazenado em uma determinada célula de memória, ou seja, algum tempo após uma escrita que ocorreu com sucesso o dado armazenado muda de valor.

Em memórias flash um dos efeitos da radiação ionizante é a geração de cargas positivas no óxido que existe entre o canal e a porta flutuante, e entre a porta flutuante e o terminal de porta em si. Desta forma, estas cargas acabam alterando a tensão de limiar do transistor, e acabam anulando o efeito causado pelas cargas negativas armazenadas na porta flutuante. Com a ação destes efeitos em um determinado momento a tensão de limiar de transistores com e sem carga acumulada em sua porta flutuante acaba por induzir a uma leitura que indica a perda dos dados gravados. Enfim, este tipo de falha é causado por radiação ionizante.

Em SRAMs as falhas de retenção de dados ocorrem devido a danos nos transistores que compõem as células de memória. Como já foi visto, a radiação ionizante altera o comportamento elétrico dos transistores MOS, modificando sua tensão de limiar, entre outros efeitos. Esta alteração da tensão de limiar dos transistores da célula de memória pode vir a interferir na capacidade de armazenamento de dados da célula, pois pode impedir o correto funcionamento dos dois inversores lógicos que compõem cada célula de memória. Portanto, em SRAMs este tipo de falha também pode ser causado pelos efeitos da radiação ionizante.

# 4 TESTES DE MEMÓRIAS

Existem diversos tipos de testes para aplicação em memórias, desenvolvidos para diferentes fins. Uma família de testes, que é chamada de testes march, apresenta características que fazem com que ela seja largamente empregada para a realização de testes em memórias.

Os testes march consistem de uma sequência de operações, um algoritmo, que deve ser aplicado em todos os endereços de memória do dispositivo que se deseja testar. Existem testes march com o objetivo de somente detectar falhas, além de testes march cujo objetivo é identificar o tipo de falha ocorrido.

Uma das vantagens da utilização de testes march é o pequeno tempo necessário para sua execução. O número de operações de um teste march é um múltiplo do número de endereços da memória, enquanto outros testes têm um tempo de duração bem mais elevado, chegando ao número de endereços de memória elevado ao quadrado para testes do tipo 1's caminhantes. Desta forma, este trabalho consistirá apenas na análise dos testes march, devido à sua velocidade e simplicidade de execução.

### 4.1 NOTAÇÃO DOS TESTES MARCH

Antes de iniciar a descrição dos testes march é necessário definir a notação que será utilizada. Os símbolos e notações utilizados são os descritos no capítulo 3.1. Cada teste march é constituído de uma sequência de elementos march, que por sua vez são compostos por uma sequência de uma ou mais operações. Estas operações podem ser de quatro tipos:

- Escrita de um valor 0 na célula, descrita por w0;

- Escrita de um valor 1 na célula, descrita por w1;

- Leitura de uma célula cujo valor esperado é 0, descrita por r0;

- Leitura de uma célula cujo valor esperado é 1, descrita por r1.

Após a execução de todas as operações de um elemento march em uma determinada célula, elas devem ser aplicadas à célula seguinte, e assim sucessivamente. O endereço da célula seguinte pode seguir três tipos de ordenação, uma delas denotada pelo símbolo (1), outra denotada pela operação (1) e uma terceira na qual a ordem dos endereços é irrelevante, representada pelo símbolo (1). Deve ser observado que as ordens representadas pelos símbolos (1) e (1) não necessariamente representam um incremento ou decremento do valor do endereçamento da célula de memória, mas sim que as duas ordens são exatamente o inverso uma da outra. O teste só pode passar para o elemento march seguinte após efetuar todas as operações do elemento march anterior em todas as células de memória.

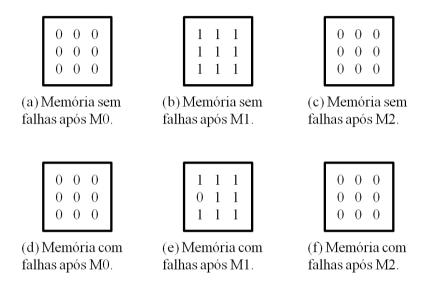

Analisando o teste MATS+ podemos identificar os seus elementos march e as operações de cada elemento, de forma a esclarecer a notação dos testes march. A notação completa do teste MATS+ é a seguinte:  $\{ (w0); (r0,w1); (r1,w0) \}$ . Entre chaves está a notação completa do teste, e seus elementos march estão separados por ponto e vírgula. Desta forma, temos os seguintes elementos march:

- Elemento march  $M_0$ : (w0). Este elemento é composto por apenas uma operação, w0, que indica que devemos escrever o valor 0 em todos os endereços de memória. A sequência de endereçamento que deve ser seguida é irrelevante, conforme o operador (1) indica.

- Elemento march M₁: ↑ (r0, w1). Este elemento possui duas operações que devem ser executadas em sequência para cada célula de memória. A primeira é a operação r0, que indica que deve ser feita a leitura na célula, e que o valor esperado é 0. Caso seja lido um valor 1, a célula apresenta falha. A segunda operação é w1, ou seja, deve ser escrito o valor 1 na célula de memória. Após a realização destas duas operações, passa-se para o endereço seguinte. Como o

- operador utilizado para representar a sequência de endereços que deve ser seguida é o (1), o endereço deve ser incrementado.

- Elemento march M₂: ↓ (r1, w0). Este elemento também é constituído por duas operações. A sua diferença para o M₁ é que as operações são de leitura com valor esperado 1 e de escrita de valor 0 na célula de memória. Além disso, a ordem de endereçamento é inversa, ou seja, o endereço deve ser decrementado após a realização de todas as operações em cada célula de memória.

Cabe a observação de que neste capítulo e no restante deste trabalho os testes march que serão abordados são voltados a memórias com palavras de 1 bit. Assim, segundo (VAN DE GOOR, 1998) os testes serão capazes apenas de verificar falhas que envolvam mais de uma célula entre duas *words* diferentes, ficando as falhas entre células de uma mesma palavra fora da cobertura dos testes. Para que o teste abordasse falhas entre palavras e entre células de uma mesma palavra uma abordagem, descrita em (VAN DE GOOR, 1998) é a de realizar um teste orientado a bit na memória para verificar as falhas entre as diferentes *words* e na sequência um teste dentro de cada palavra, que pode ser, por exemplo, um teste de 1's caminhantes (no qual se faz um valor 1 passar por cada bit da palavra, sendo que os outros bits têm valor 0 gravado), para verificação de falhas entre células de uma mesma palavra. Esta alternativa de testar apenas falhas entre *words* foi escolhida devido ao tempo disponível para o desenvolvimento do trabalho, visto que abordar falhas dentro da *word* demandaria testes mais complexos e extensos. Esta escolha será retratada com maiores detalhes no capítulo 5.

### 4.2 TESTES MARCH PARA DETECÇÃO DE FALHAS

Existem diversos testes march já desenvolvidos, cada um deles com um propósito específico. Na tabela 4 estão descritos os algoritmos e o número de operações total para diversos tipos de testes march.

Estes testes são capazes de detectar diversos tipos de falhas em cada operação, porém para que um teste seja capaz de detectar todas as ocorrências de um determinado tipo de falha ele deve cumprir alguns requisitos, comentados no capítulo 3. A cobertura de falhas dos testes march citados na tabela 4 pode ser vista na tabela 5.

Tabela 4: Algoritmos de alguns testes march.

| Algoritmo | Descrição                                                                                                                       | Número de operações |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|

| MATS      | $\{ \updownarrow (w0); \updownarrow (r0, w1); \updownarrow (r1) \}$                                                             | $4 \cdot n$         |

| MATS+     | $\{\updownarrow (w0); \uparrow (r0,w1); \downarrow (r1,w0)\}$                                                                   | $5 \cdot n$         |

| MATS++    | $\{ (w0); \ (r0, w1); \ \forall \ (r1, w0, r0) \}$                                                                              | 6 · n               |

| MARCH X   | $\{ \updownarrow (w0); \uparrow (r0,w1); \downarrow (r1,w0); \uparrow (r0) \}$                                                  | 6 · n               |

| MARCH C—  | $\{\updownarrow\ (w0);\ \uparrow\ (r0,w1);\ \uparrow\ (r1,w0);\ \downarrow\ (r0,w1);\ \downarrow\ (r1,w0);\ \downarrow\ (r0)\}$ | $10 \cdot n$        |

| MARCH A   | $\{ (w0); \ (r0, w1, w0, w1); \ (r1, w0, w1); \ (r1, w0, w1, w0); \ (r0, w1, w0) \}$                                            | 15 · n              |

| MARCH Y   | $\{ \updownarrow (w0); \uparrow (r0, w1, r1); \downarrow (r1, w0, r0); \uparrow (r0) \}$                                        | $8 \cdot n$         |

| MARCH B   | $\{ (w0); \ (r0,w1,r1,w0,r0,w1); \ (r1,w0,w1); \ (r1,w0,w1,w0); \ (r0,w1,w0) \}$                                                | 17 · n              |

Tabela 5: Cobertura de falhas de alguns testes march.

|           |       |         | Cobe  | rtura de f | alhas |       |       | Número          |

|-----------|-------|---------|-------|------------|-------|-------|-------|-----------------|

| Algoritmo | SAF   | AF      | TF    | CFin       | CFid  | CFdyn | SCF   | de<br>operações |

| MATS      | Todas | Algumas |       |            |       |       |       | $4 \cdot n$     |

| MATS+     | Todas | Todas   |       |            |       |       |       | $5 \cdot n$     |

| MATS++    | Todas | Todas   | Todas |            |       |       |       | $6 \cdot n$     |

| MARCH X   | Todas | Todas   | Todas | Todas      |       |       |       | 6 · n           |

| MARCH C   | Todas | Todas   | Todas | Todas      | Todas | Todas | Todas | $10 \cdot n$    |

| MARCH A   | Todas | Todas   | Todas | Todas      |       |       |       | $15 \cdot n$    |

| MARCH Y   | Todas | Todas   | Todas | Todas      |       |       |       | $8 \cdot n$     |

| MARCH B   | Todas | Todas   | Todas | Todas      |       |       |       | 17 · n          |

Observa-se que os testes march citados proporcionam uma grande cobertura de falhas com um número total de operações bastante baixo, o que faz com que o tempo total de execução dos testes seja reduzido também. Nas tabelas 6 e 7 podem ser vistos os tempo necessários para executar as operações em memórias de diversos tamanhos e diversos tempos

mínimos de acesso. Estes baixos tempos necessários para a execução dos testes os torna viáveis para as aplicações deste trabalho. Nas tabelas 6 e 7 a memória número 1 é uma SRAM da fabricante ISSI, modelo IS66WV25616BLL-55TLI, com seu barramento de dados orientado a uma palavra de 16 bits, a memória 2 é a mesma SRAM com seu barramento de dados orientado a uma palavra de 8 bits, e a memória número 3 é uma memória flash, fabricada pela Spansion, modelo AM29LV040B-90JD. Estas memórias foram as selecionadas para o desenvolvimento da plataforma de testes deste projeto.

Tabela 6: Duração total de alguns testes march executados em memórias de tamanhos e tempos de acesso diferentes.

| Memória | Número de<br>Endereços | Tempo Mínimo<br>de Acesso | MATS<br>4n | MATS+  | MATS++<br>6n | MARCH X<br>6n |

|---------|------------------------|---------------------------|------------|--------|--------------|---------------|

| 1       | 256k                   | 55ns                      | 0,058s     | 0,072s | 0,087s       | 0,087s        |

| 2       | 512k                   | 55ns                      | 0,115s     | 0,144s | 0,173s       | 0,173s        |

| 3       | 512k                   | 90ns                      | 0,189s     | 0,236s | 0,283s       | 0,283s        |

Tabela 7: Duração total de alguns testes march executados em memórias de tamanhos e tempos de acesso diferentes.

| Memória | Número de<br>Endereços | Tempo Mínimo<br>de Acesso | MARCH C-<br>10n | MARCH B<br>17n | 1's Caminhantes<br>n^2 |

|---------|------------------------|---------------------------|-----------------|----------------|------------------------|

| 1       | 256k                   | 55ns                      | 0,144s          | 0,245s         | 1,05h                  |

| 2       | 512k                   | 55ns                      | 0,288s          | 0,490s         | 4,20h                  |

| 3       | 512k                   | 90ns                      | 0,472s          | 0,802s         | 6,87h                  |

O processo de teste é bastante simples, especialmente para testes mais curtos. O teste MATS+ possui apenas três operações de leitura, ou seja, exige poucos recursos para a

avaliação de falhas em uma memória. Na figura 24 observa-se a detecção de uma falha do tipo SA0 com a utilização de um teste march MATS+.

Figura 24: Detecção de uma falha SA0 na célula (2,1) através de teste MATS+.

#### 4.3 TESTES MARCH PARA IDENTIFICAÇÃO DE FALHAS

Além dos testes focados apenas em detectar as falhas, que não possuem a capacidade de identificar qual foi o tipo de falha ocorrido em determinada célula de memória, há testes que, através da execução de certas etapas de teste, são capazes de identificar alguns tipos de falha que podem vir a ter ocorrido na memória. Estes testes, além de identificar o tipo de falha ocorrido podem identificar também a célula agressora e a célula vítima do processo de falha, o que permite que seja feita uma análise mais profunda das falhas ocorridas na memória, e seus potenciais motivos.

Testes que são capazes de fazer a identificação de falhas necessitam mais operações que um teste desenvolvido apenas para detectar falhas. Para realizar a identificação da falha ocorrida é utilizada a assinatura ou síndrome do teste, que é formada pela existência ou não de falhas em cada operação de leitura efetuada durante o teste. Um valor 1 na assinatura do teste

significa que uma operação de leitura naquela célula detectou falha, ou seja, foi lido um valor diferente do esperado. Um valor 0 na assinatura representa que não foi detectado nenhum tipo de falha naquela operação de leitura. Se a célula de memória que está sendo testada não possuir falha alguma ou poossuir falhas que não podem ser detectadas pelo teste a assinatura para esta célula irá ser formada apenas por zeros.

Um teste march capaz de identificar a falha ocorrida deve garantir que cada falha que deve ser identificada possua uma assinatura diferente. Mesmo que o teste seja bastante completo e extenso ele pode não ser capaz de identificar todas as falhas possíveis, visto que algumas falhas apresentam o mesmo comportamento durante um teste march.

O teste march DSS, descrito em (AL-HARBI, 2007), é um teste march para identificação de falhas. Este é um teste bastante extenso comparado àqueles descritos anteriormente, sendo constituído por 46 operações, ou seja, requer a execução de 46\*n operações para sua conclusão, sendo *n* o número de endereços da memória a ser testada. A notação do teste march DSS é dada por

$$\{ \Uparrow (w0); \Uparrow (r0,r0,w0,r0,w1); \Uparrow (r1,w1,r1,w0);$$

$$\Downarrow (r0,w0,r0,w1); \Downarrow (r1,w1,r1,w0,w0,r0);$$

$$\Downarrow (r0,w0,r0); \Downarrow (r0,w1,r1); \Downarrow (r1,w1);$$

$$\Uparrow (r1,w0,r0); \Uparrow (r0,w1,r1); \Uparrow (r1,w0);$$

$$\Downarrow (r0,w0); \Uparrow (r0,w1); \Downarrow (r1,w1,r1);$$

$$\Downarrow (r1,w0); \Downarrow (r0) \}$$

$$(1)$$

Algumas falhas não são identificáveis entre si. São os casos do grupo formado pelas falhas SA0 e falhas de transição de subida e do grupo oposto, formado por falhas SA1 e falhas de transição de descida. Uma ampla gama de falhas pode ser identificada, incluindo

diversos tipos de *coupling faults*. Isto permite que se saiba exatamente o tipo de problema que se está detectando, e assim pode-se analisar as causas destas falhas, levando a um maior entendimento dos efeitos das condições ambientais no funcionamento das memórias.

Observa-se portanto que o teste march DSS é um teste muito interessante para a utilização na plataforma de testes, visto que através dele é possível ter uma ideia bastante aprofundada dos fatos que estão ocorrendo na memória, enquanto outros testes apenas permitem que sejam detectadas as falhas, e desta forma pode ser feita uma avaliação dos pontos fortes e fracos dos componentes testados.

# 5 ANÁLISE DE ALTERNATIVAS

A partir dos estudos retratados nos capítulos 2, 3 e 4, pode-se iniciar a especificação dos requisitos da plataforma de testes de memória a ser desenvolvida como objetivo deste projeto.

### 5.1 SELEÇÃO DAS MEMÓRIAS

Na introdução deste trabalho já foram citadas duas memórias de interesse para este projeto, selecionadas através de informações obtidas em contatos com Odair Lelis Gonçalez, pesquisador do Departamento de Ciência e Tecnologia Aeroespacial – DCTA, Instituto de Estudos Avançados – IEAv, localizado em São José dos Campos/SP, que informou alguns modelos que são comumente empregados em aplicações aeroespaciais. Cabe ressaltar que as informações a respeito dos componentes utilizados em satélites e em outras aplicações aeroespaciais geralmente não são públicas, sendo desta forma importante obtê-las diretamente com pesquisadores do setor.

As memórias indicadas foram duas ao todo, sendo uma memória Flash (Spansion AM29LV040B-90JD) e uma SRAM (ISSI IS66WV25616BLL-55TLI). A decisão foi a de prever a utilização das duas memórias na plataforma de testes, de forma que a placa de circuito impresso a ser projetada deve acomodar estes dois componentes. Como são apenas dois componentes com interfaces bastante semelhantes entre si não haverá problema em compartilhar a plataforma entre as duas memórias.

#### 5.2 DEFINIÇÃO DA TECNOLOGIA DA PLATAFORMA DE TESTES

Para que sejam realizados os testes é necessária a construção de uma plataforma de hardware capaz de acomodar em uma placa de circuito impresso as duas memórias que se deseja testar. Esta placa de circuito impresso deve se comunicar com um dispositivo capaz de

se comunicar com as duas memórias, realizando os acessos de leitura e escrita necessários à execução de qualquer tipo de teste que venha a ser executado.

A definição inicial do projeto neste sentido é de que este dispositivo responsável pela execução dos testes deve ser uma plataforma de desenvolvimento baseada em microcontrolador ou FPGA, cuja placa deve estar disponível na Universidade ou seja de fácil aquisição, ou seja, tenha baixo custo e disponibilidade em distribuidores autorizados pelos fabricantes.

Outro critério bastante importante na seleção da plataforma de desenvolvimento é o número de pinos de entrada / saída disponíveis para uso geral, que devido ao tamanho dos barramentos das memórias utilizadas não deve ser inferior a 33 pinos, conforme tabela 8.

Tabela 8: Conjunto mínimo de sinais necessários para atendimento às memórias.

| Sinal       | Número de sinais | Função                                  |

|-------------|------------------|-----------------------------------------|

| MEM_ADDR_o  | 19               | Endereçamento (SRAM e flash)            |

| MEM_DATA_io | 8                | Dados (SRAM e flash)                    |

| MEM_CS_n_o  | 2                | Chip Select (um para cada memória)      |

| MEM_OE_n_o  | 1                | Output Enable (SRAM e flash)            |

| MEM_WE_n_o  | 1                | Write Enable (SRAM e flash)             |

| MEM_LB_n_o  | 1                | Ativa o byte menos significativo (SRAM) |

| MEM_UB_n_o  | 1                | Ativa o byte mais significativo (SRAM)  |

| TOTAL       | 33               | -                                       |

Também é necessária a presença de uma porta de comunicação serial RS-232, para permitir comunicação com um microcomputador que fará o controle da realização dos testes, e que será a plataforma na qual serão visualizados os resultados das operações.

Outro requisito fundamental é que os sinais de entrada / saída configuráveis sejam compatíveis com os níveis de tensão das portas das memórias, conforme tabelas 9 e 10, e que esteja disponível no conector que faz a ligação com a placa de expansão que acomoda as memórias uma tensão de 3.3V para alimentar estes componentes.

Tabela 9: Níveis de tensão requeridos pela SRAM ( $V_{CC} = 3.3V$ ).

| Símbolo           | Parâmetro                        | Valor mínimo (V) | Valor máximo (V) |

|-------------------|----------------------------------|------------------|------------------|

| $V_{OH}$          | Tensão de saída em nível alto    | 2.2              | -                |

| $V_{\mathrm{OL}}$ | Tensão de saída em nível baixo   | -                | 0.4              |

| $ m V_{IH}$       | Tensão de entrada em nível alto  | 2.2              | 3.6              |

| $ m V_{IL}$       | Tensão de entrada em nível baixo | -0.2             | 0.6              |

Tabela 10: Níveis de tensão requeridos pela memória flash ( $V_{CC} = 3.3V$ ).

| Símbolo           | Parâmetro                        | Valor mínimo (V) | Valor máximo (V) |

|-------------------|----------------------------------|------------------|------------------|

| $V_{OH}$          | Tensão de saída em nível alto    | 2.805            | -                |

| $V_{\mathrm{OL}}$ | Tensão de saída em nível baixo   | -                | 0.45             |

| $ m V_{IH}$       | Tensão de entrada em nível alto  | 2.31             | 3.6              |

| $V_{ m IL}$       | Tensão de entrada em nível baixo | -0.5             | 0.8              |