## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### THIAGO ROCHA DE ASSIS

**Analysis of Transistor Sizing and Folding Effectiveness to Mitigate Soft Errors.**

Thesis presented in partial fulfillment of the requirements for the degree of Master in Computer Science

Prof. Dr. Ricardo Augusto da Luz Reis Advisor

Prof. Dr. Fernanda Gusmão de Lima Kastensmidt Co-advisor

Porto Alegre, March 2009.

## CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Assis, Thiago Rocha de

Analysis of Transistor Sizing and Folding Effectiveness to Mitigate Soft Errors / Thiago Rocha de Assis — Porto Alegre: Programa de Pós-Graduação em Computação, UFRGS 2009.

102 f.:il.

Thesis (Master) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2008. Advisor: Ricardo Augusto da Luz Reis; Co-Advisor: Fernanda Gusmão de Lima Kastensmidt.

1.Fault Tolerance. 2.Radiation Effects 3.Single Event Transient.

4. Single Event Effect. 5. Soft Errors. 6. Transistor Sizing. 7. Folding. I. Ricardo Augusto da Luz Reis, II. Fernanda Gusmão de Lima Kastensmidt.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-reitor: Prof. Rui Vicente Oppermann

Pró-Reitora Adjunta de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PPGC: Prof Álvaro Freitas Moreira

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **ACKNOWLEDGMENT**

I would like to thank my father (Ailton Assis) and my mother (Telma Assis) for all support that they gave me during undergrad and graduate courses. Without their help this journey would certainly had become much harder. I also thank my brother (Ailton Junior) and sister (Milla Assis) for their patience during the last years. I also thank my girlfriend (Reginara Souza) for her understanding and supporting during the last years.

I'm very grateful to advisor Prof. Dr. Ricardo Reis for this great opportunity to prepare a master at UFRGS. I wish to thank Prof. Dr. Fernanda Kastensmidt and Prof. Dr. Gilson Wirth for their outstanding contribution to the developing of this work. Without their help this research would never be possible.

I wish to thank all my teachers and friends from the Universidade Federal do Rio Grande do Sul that somehow had contribute to the development of this work. I also wish to thank the great teachers that I had at the Universidade Salvador were I did my undergrad course.

Thanks!

# **TABLE OF CONTENTS**

| LIST OF ABBREVIATIONS                                                                                | 6  |

|------------------------------------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                                                      | 8  |

| LIST OF TABLES                                                                                       | 11 |

| ABSTRACT                                                                                             | 12 |

| 1 INTRODUCTION                                                                                       | 14 |

| 1.1 Methodology                                                                                      | 17 |

| 1.2 Dissertation Organization                                                                        |    |

| 2 RADIATION OVERVIEW                                                                                 | 20 |

| 2.1 Radiation Sources and Earth Environment                                                          | 20 |

| 2.2 Radiation Effects                                                                                |    |

| <ul><li>2.3 Techniques to Mitigate Radiation Effects</li><li>2.4 Main Equations and Models</li></ul> |    |

| 3 DEVICE MODELING                                                                                    |    |

|                                                                                                      |    |

| <ul><li>3.1 Modeled Device – 3D NMOSFET</li><li>3.2 NMOSFET Device Simulations</li></ul>             |    |

| 4 SOFT ERRORS MODELLING                                                                              |    |

| 4.1 Ion Profiles                                                                                     | 51 |

| 4.2 Physical Models Used in Davinci Simulations                                                      |    |

| 4.3 Pulse Measurements                                                                               |    |

| 5 TRANSISTOR SIZING TECHNIQUE                                                                        | 64 |

| 5.1 Devices and Simulations                                                                          |    |

| 5.2 Transistor Sizing Results                                                                        |    |

| 5.3 Related Work                                                                                     |    |

| 6 TRANSISTOR FOLDING                                                                                 |    |

| 6.1 Transistor Folding Device Simulations                                                            | 81 |

| 6.2 Transistor Folding Results                                                                       | 82 |

| 6.3 Transistor Folding Conclusion                                                                    | 89 |

| 7 CONCLUSIONS                                                                                        | 90 |

| REFERENCES                                                                                           | 92 |

| APPENDIX RADIAL DISTRIBUTION OF CARRIERS                                                             | 98 |

| AF | PPENDIX 2 - | RESUMO. | <br> | <br>1 | 04 |

|----|-------------|---------|------|-------|----|

| Al | PENDIX 2 -  | RESUMO. | <br> | <br>  | 04 |

## LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuit

ASU Arizona State University

AUGER Auger Recombination Model

BGN Band Gap Narrowing

CCSMOB Carrier-Carrier Scattering Mobility Model

CME Coronal Mass Ejection

CMOS Complementary Metal Oxide Silicon

DD Displacement Damage

DMR Double Modular Redundancy

ELG Enclosed Layout Geometry

ELT Enclosed Layout Transistor

EPI Epitaxial Substrate

FPGA Field Programmable Gate Array

GND Ground

IC Integrated Circuit

LDD Light Doped Drain

LET Linear Energy Transfer

MBU Multiple Bit Upset

MIT Massachusetts Institute of Technology

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NIEL Non-Ionizing Loss Energy

OS Operating System

PTM Predictive Technology Model

RPP Rectangular Parallelepiped

SAA South Atlantic Anomaly

SBU Single Bit Upset

SEE Single Event Effect

SEFI Single Event Functional Interruption

SEGR Single Event Gate Rupture

SEL Single Event Latchup

SET Single Event Transient

SER Soft Error Rate

SEU Single Event Upset

SRAM Static Random Access Memory

SRH Schockley-Read-Hall Model

SSR Super Step Retrograde

TID Total Ionizing Dose

TMR Triple Modular Redundancy

UFRGS Universidade Federal do Rio Grande do Sul

# LIST OF FIGURES

| Figure 1.1: SRAM Integration vs. Soft Error Rate                              | 15 |

|-------------------------------------------------------------------------------|----|

| Figure 1.2: PMOS Diode SER vs. Supply voltage                                 | 16 |

| Figure 1.3: Methodology of simulations                                        | 18 |

| Figure 2.1: Cosmic radiation and Solar Events                                 | 21 |

| Figure 2.2: Sunspot Cycle                                                     | 21 |

| Figure 2.3: Van Allen Belts                                                   |    |

| Figure 2.4: South Atlantic anomaly                                            | 23 |

| Figure 2.5: Soft Error Rate at Earth                                          | 23 |

| Figure 2.6: Radiation interaction with atmosphere                             | 24 |

| Figure 2.7: Altitude vs. Neutron Flux                                         | 25 |

| Figure 2.8: Neutron flux vs. latitude.                                        | 25 |

| Figure 2.9: Total Ionizing Dose mechanism                                     | 27 |

| Figure 2.10: Threshold shift during radiation                                 | 27 |

| Figure 2.11: Displacement Dose mechanism                                      | 28 |

| Figure 2.12: DD effect on lifetime.                                           | 28 |

| Figure 2.13: Soft error mechanism                                             | 29 |

| Figure 2.14: SET and SEU at logic                                             | 30 |

| Figure 2.15: Logical Masking factor                                           | 30 |

| Figure 2.16: Path of a particle inside the silicon                            | 31 |

| Figure 2.17: Multiple interaction of the particle                             | 32 |

| Figure 2.18: Abstraction Levels                                               | 33 |

| Figure 2.19: Enclosed Layout Transistor Design                                | 34 |

| Figure 2.20: Guard Ring layout structure                                      | 34 |

| Figure 2.21: Inverter using ELT and Guard Rings                               |    |

| Figure 2.22: DMR                                                              | 36 |

| Figure 2.23: Triple Modular Redundancy technique                              | 36 |

| Figure 2.24: Time Redundancy Technique                                        | 36 |

| Figure 2.25: Full Time Redundancy                                             | 37 |

| Figure 2.26: Current for different charges.                                   | 40 |

| Figure 2.27: Cross Section of a circuit.                                      | 40 |

| Figure 2.28: Transient propagation over logic                                 | 42 |

| Figure 3.1: NMOS transistor symbol                                            |    |

| Figure 3.2: NMOSFET device                                                    | 45 |

| Figure 3.3: Developed NMOS 90nm device                                        |    |

| Figure 3.4: I <sub>DS</sub> vs V <sub>GS</sub> for PTM and the device modeled |    |

| Figure 3.5: $I_{DS}$ vs $V_{DS}$ for PTM and the device modeled               | 48 |

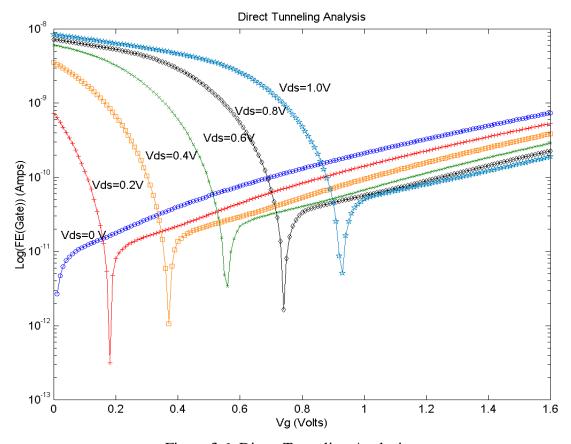

| Figure 3.6: Direct Tunneling Analysis                                                    | . 49 |

|------------------------------------------------------------------------------------------|------|

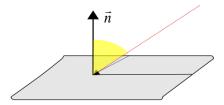

| Figure 4.1: Surface Impact Angle Dependence                                              | . 50 |

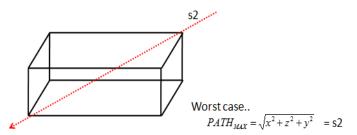

| Figure 4.2: Worst case impact.                                                           | . 50 |

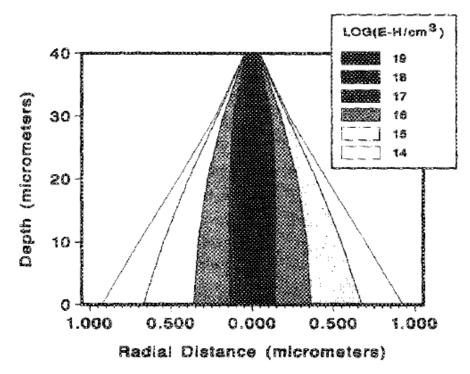

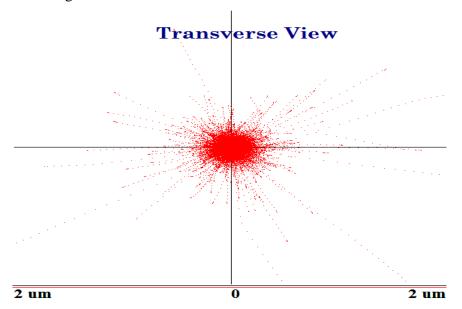

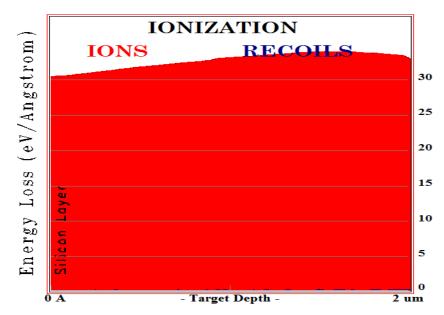

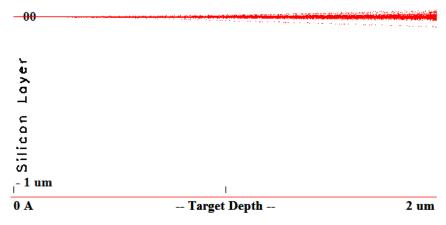

| Figure 4.3: Radial distribution of an Ar ion of 180 MeV in Si.                           | . 51 |

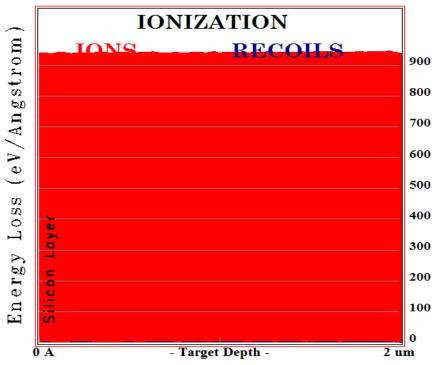

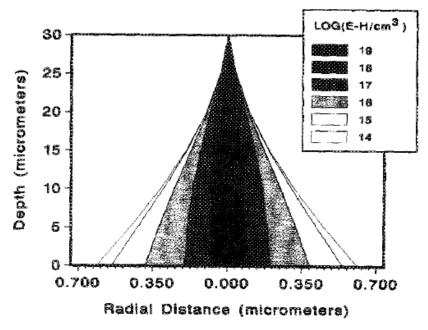

| Figure 4.4: Hydrogen hitting silicon layer                                               | . 52 |

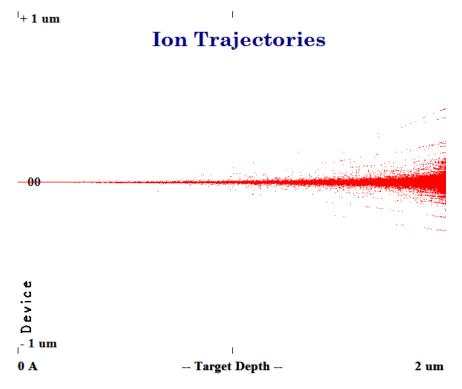

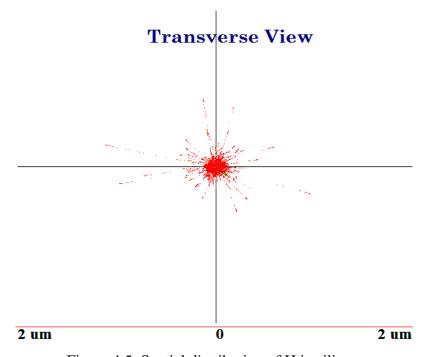

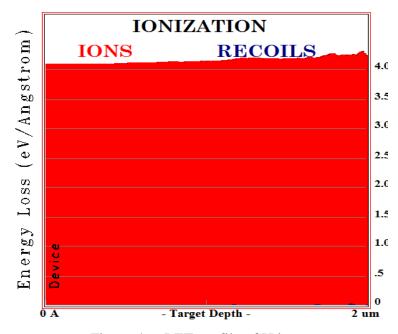

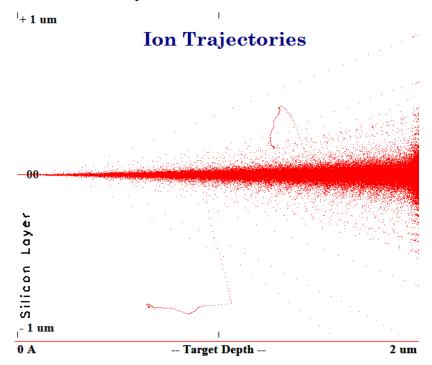

| Figure 4.5: Spatial distribution of H in silicon                                         | . 52 |

| Figure 4.6: LET profile of H ion.                                                        |      |

| Figure 4.7: He Range of the particle inside the device                                   | . 55 |

| Figure 4.8: He Spatial profile inside the device.                                        | . 55 |

| Figure 4.9: He Ionization profile inside the device.                                     | . 56 |

| Figure 4.10: Copper trajectory                                                           | . 56 |

| Figure 4.11: Copper spatial distribution.                                                | . 57 |

| Figure 4.12: Copper ionization.                                                          | . 57 |

| Figure 4.13: Krypton trajectory                                                          | . 58 |

| Figure 4.14: Krypton spatial range                                                       |      |

| Figure 4.15: Krypton ionization profile                                                  | . 59 |

| Figure 4.16: Kr radial distribution of e-h pairs                                         | . 59 |

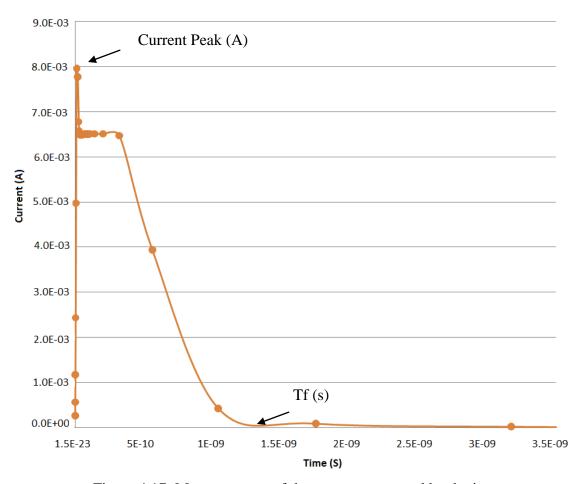

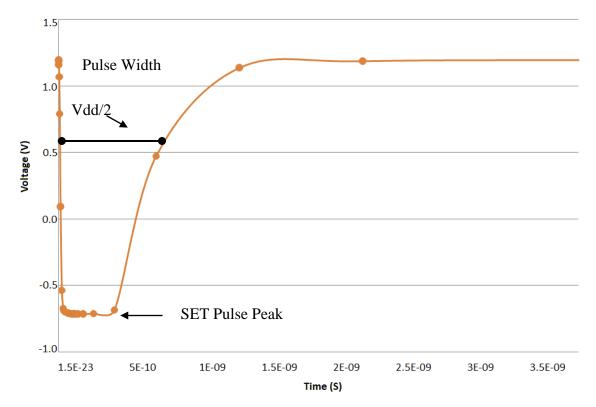

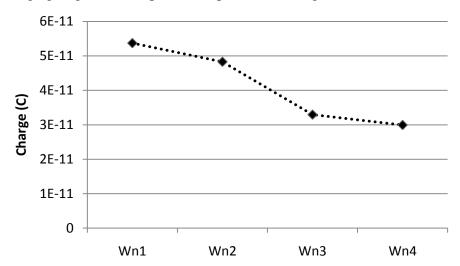

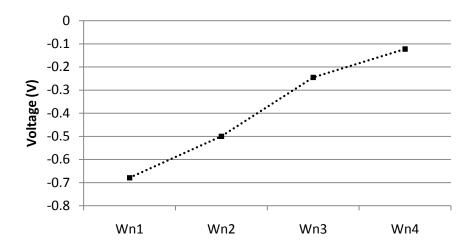

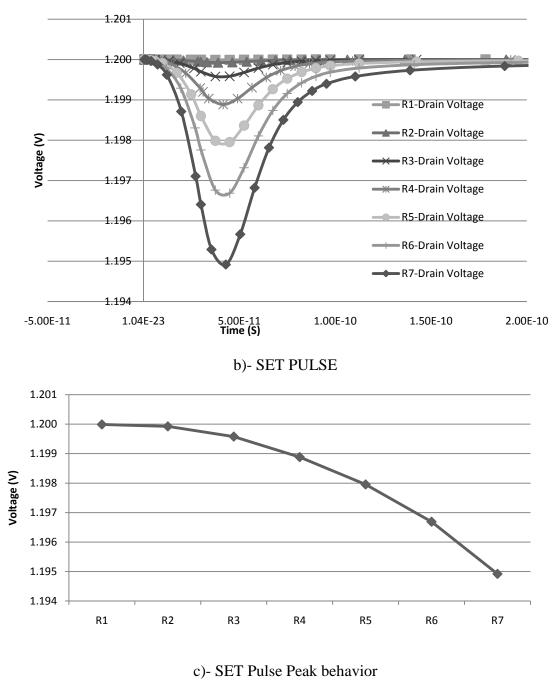

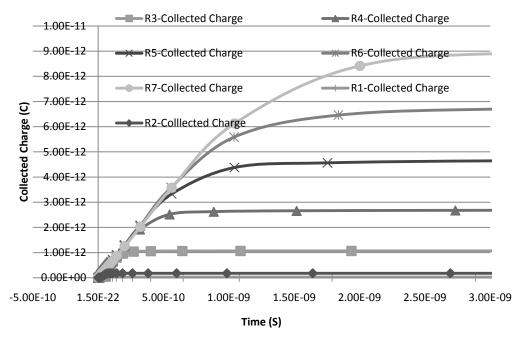

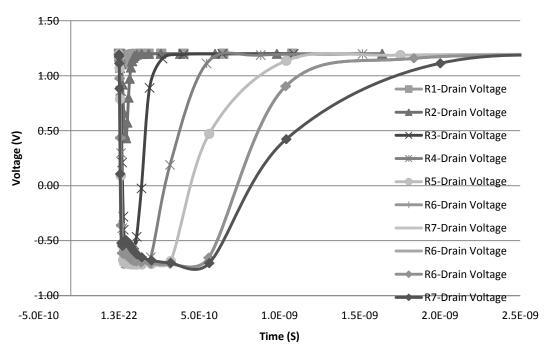

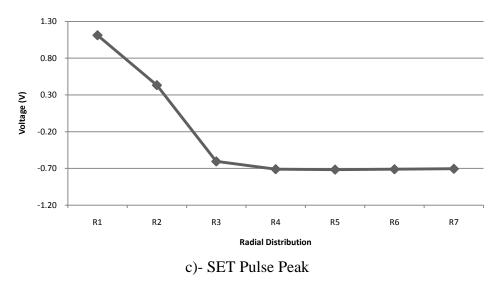

| Figure 4.17: Measurements of the current generated by the ion                            | . 62 |

| Figure 4.18: SET pulse width and peak                                                    | . 63 |

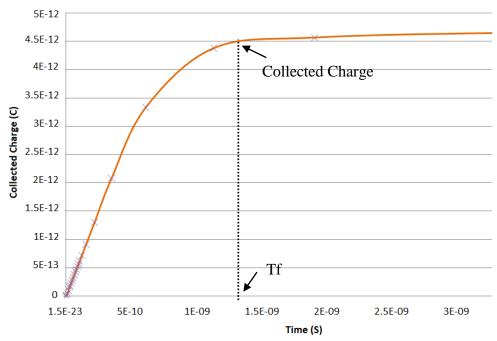

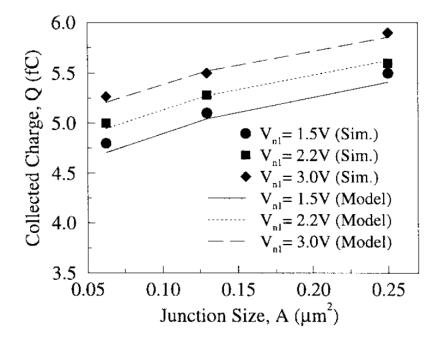

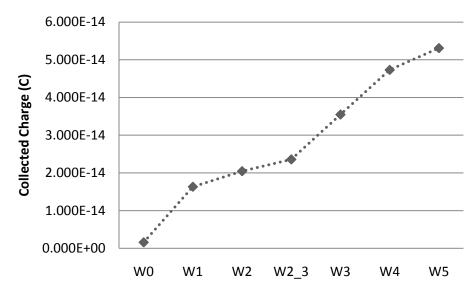

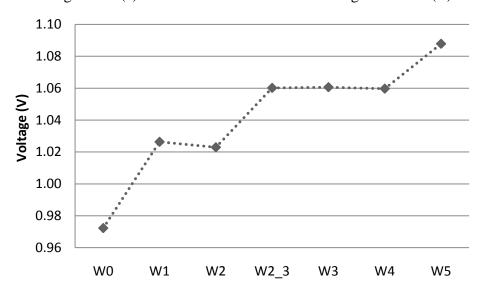

| Figure 4.19: Collected Charge                                                            | . 63 |

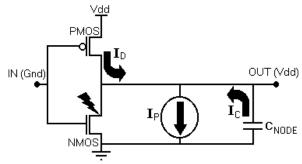

| Figure 5.1: Circuit level representation of the charge deposition                        | . 64 |

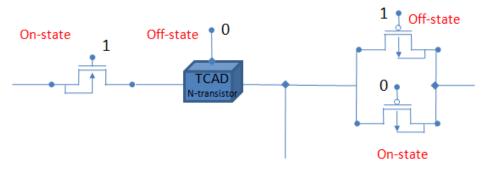

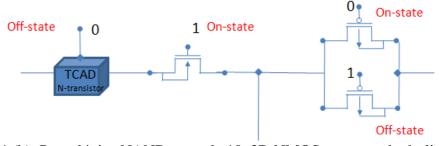

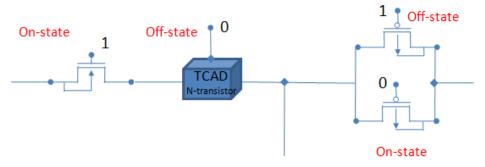

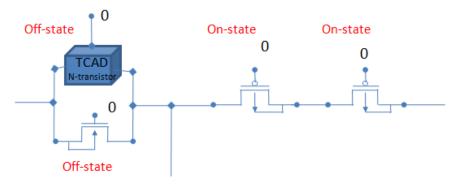

| Figure 5.2 (a): NOT gate, input:0, 3D NMOS at off-state.                                 | . 65 |

| Figure 5.2 (b): NAND gate, input:10, 3D NMOS at off-state connected to gnd               | . 65 |

| Figure 5.2 (c): NAND gate, input:01, 3D NMOS at off-state at the output                  | . 66 |

| Figure 5.2 (d): NOR gate, input:00, 3D NMOS at off-state                                 |      |

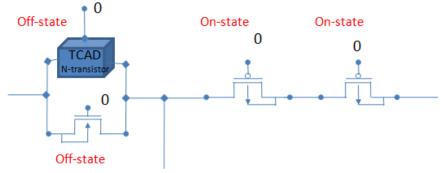

| Figure 5.3: 3D NMOS transistor during ionization                                         |      |

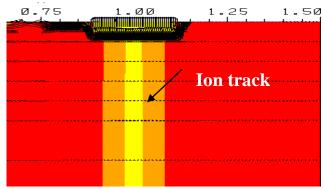

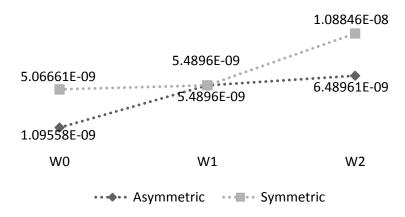

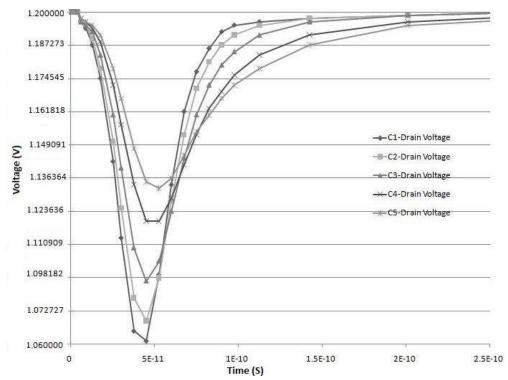

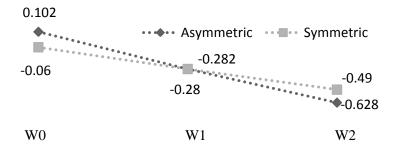

| Figure 5.4 (a): Alpha Particle, NOT, Collected Charge (C)                                | . 68 |

| Figure 5.4 (b): Alpha Particle, NOT, SET Pulse Peak (V)                                  |      |

| Figure 5.5 (b): Alpha Particle, NOR, SET Pulse Peak(V)                                   | . 69 |

| Figure 5.6 (a): Alpha Particle, NAND 01, Collected Charge (C)                            | . 70 |

| Figure 5.6 (b): Alpha Particle, NAND 01, SET Pulse Peak (V)                              | . 70 |

| Figure 5.7 (b): Alpha particle- NOT- SET Pulse Peak (V)                                  |      |

| Figure 5.8: Alpha particle - Transient voltage pulse to different capacitances           | . 72 |

| Figure 5.9 (a): Cu ion, NOT, SET Pulse Peak (V)                                          | . 72 |

| Figure 5.9 (b): Kr ion, NOT, SET Pulse Peak (V)                                          | . 73 |

| Figure 5.10 (a): Cu ion, NOT, Collected Charge (C)                                       |      |

| Figure 5.10 (b): Kr ion, NOT, Collected Charge (C)                                       |      |

| Figure 5.11 (a): Cu ion, NOT, Pulse Width (s)                                            | . 74 |

| Figure 5.11 (b): Kr ion, NOT, Pulse Width                                                | . 74 |

| Figure 5.12 (a): Cu ion, NOR, SET Pulse Peak (V)                                         | . 74 |

| Figure 5.12 (b): Kr ion, NOR, SET Pulse Peak (V)                                         | . 75 |

| Figure 5.13 (a): Cu ion, NOR, Pulse Width (s)                                            | . 75 |

| Figure 5.13 (b): Kr ion, NOR, Pulse Width (s)                                            | . 76 |

| Figure 5.14: 26.5MeV/(mg/cm <sup>2</sup> ) - Transient voltage pulse to different output |      |

| capacitances                                                                             |      |

| Figure 5.15- Collected charge vs. junction size                                          |      |

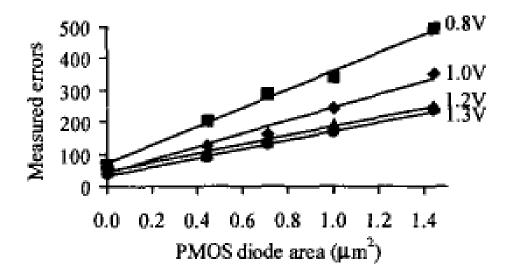

| Figure 5.16 (a): PMOS Diode area vs. Errors                                              |      |

| Figure 5.16 (b): NMOS Diode area vs. Errors                                              |      |

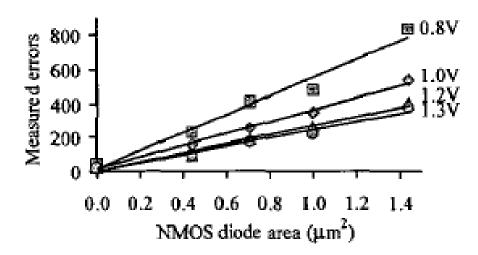

| Figure 6.1: Layout not folded and folded.                                                | . 80 |

|                                                                                          |      |

| Figure 6.2: NMOS with folding                                                     | 81 |

|-----------------------------------------------------------------------------------|----|

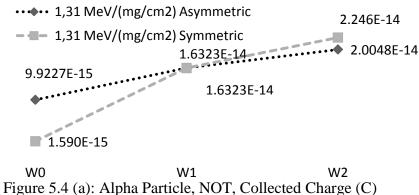

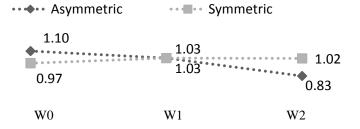

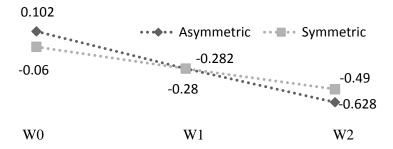

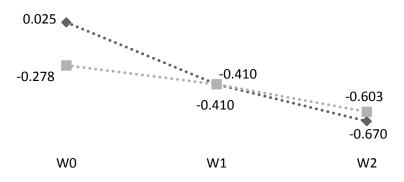

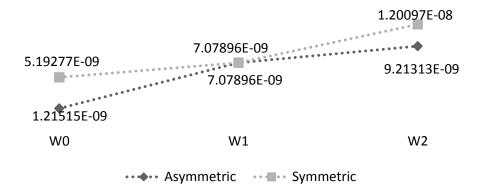

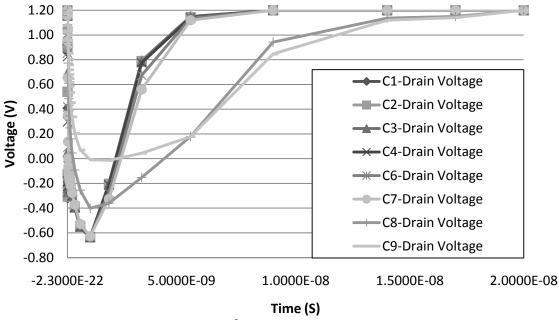

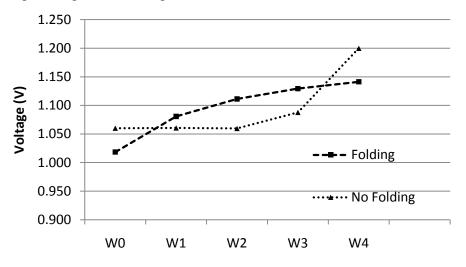

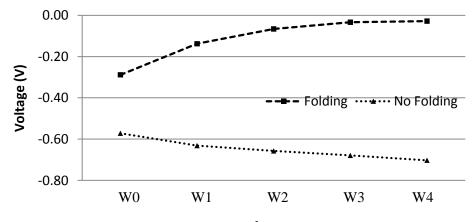

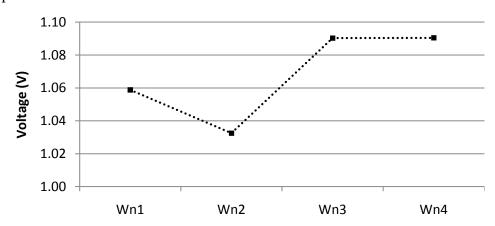

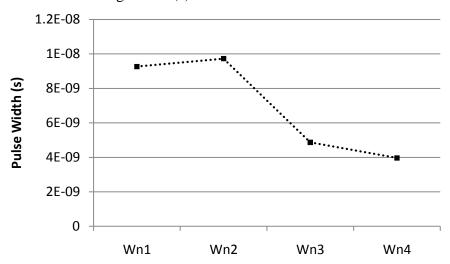

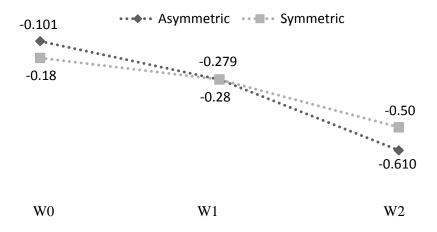

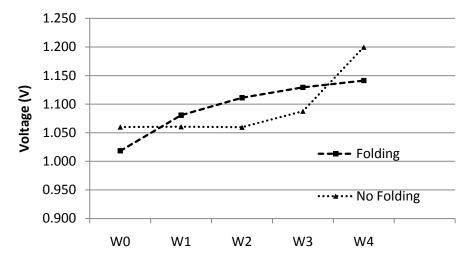

| Figure 6.3 (a): Alpha Particle, SET Pulse Peak (V)                                | 82 |

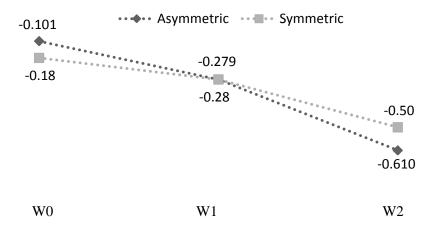

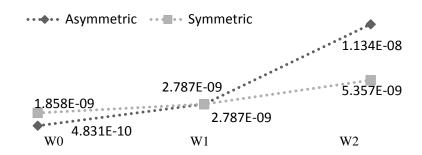

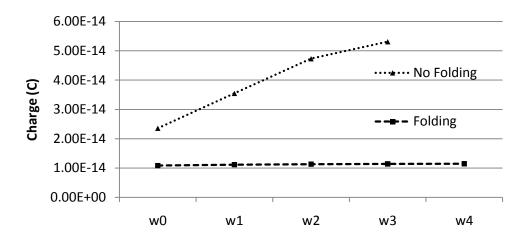

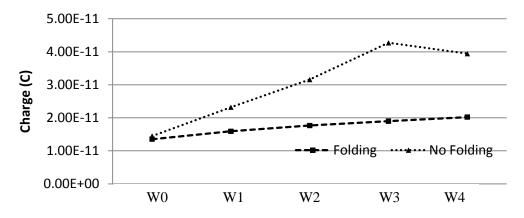

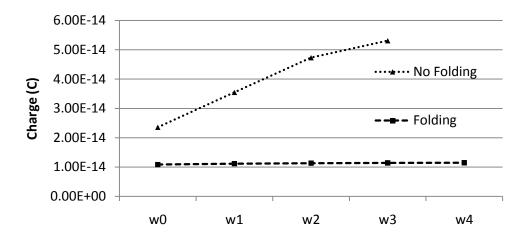

| Figure 6.3 (b): Alpha particle, Collected Charge (C)                              | 83 |

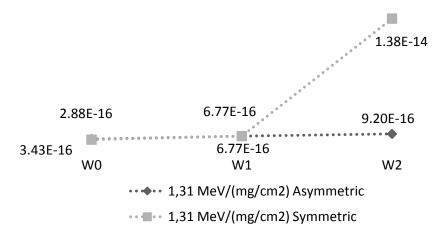

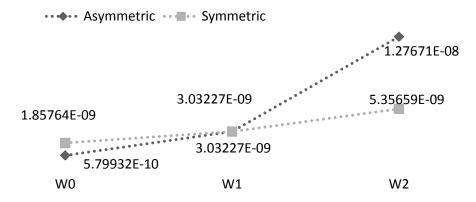

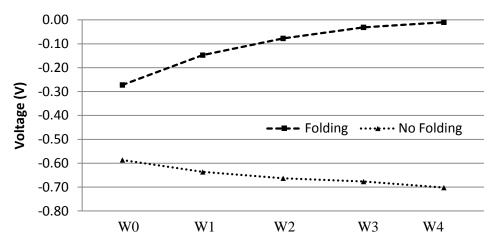

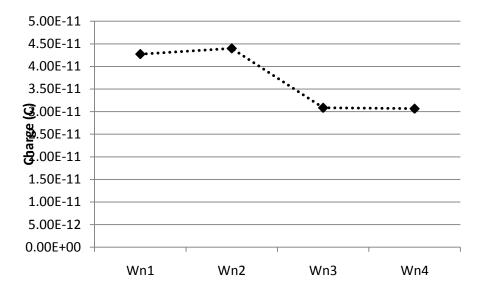

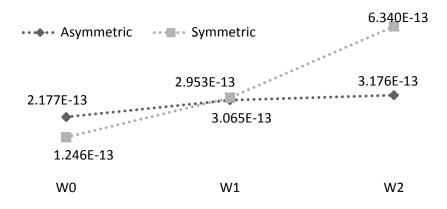

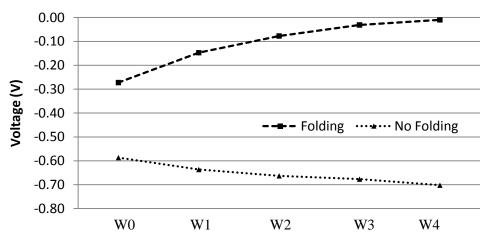

| Figure 6.4 (a): 26.5 MeV/(mg/cm <sup>2</sup> ) ion – SET Pulse Peak (V)           | 83 |

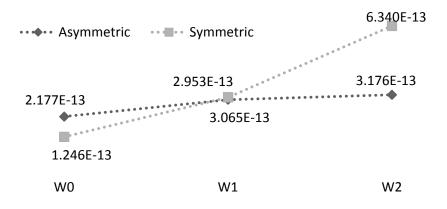

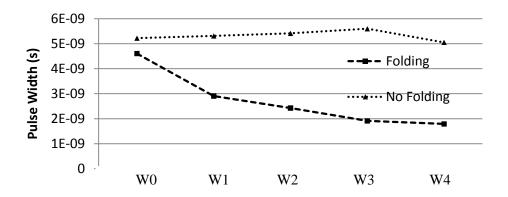

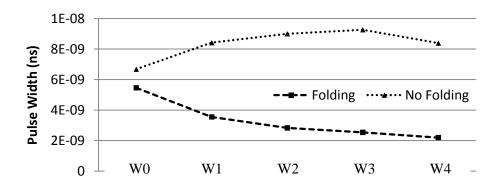

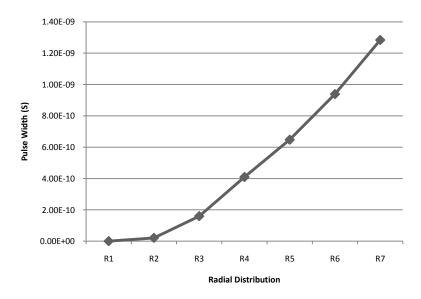

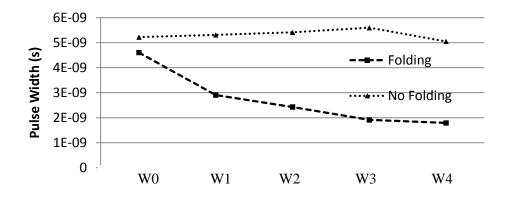

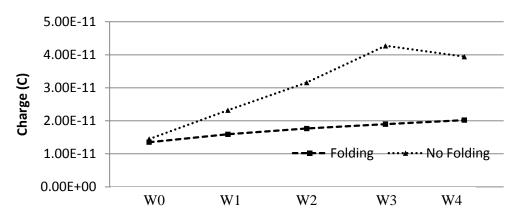

| Figure 6.4 (b): 26.5 MeV/(mg/cm <sup>2</sup> ) ion - Pulse Width (s)              | 84 |

| Figure 6.4 (c): 26.5 MeV/(mg/cm <sup>2</sup> ) ion – Collected Charge             | 84 |

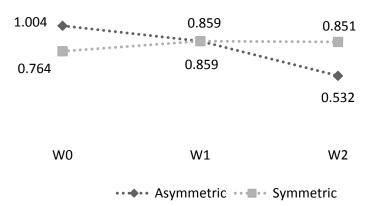

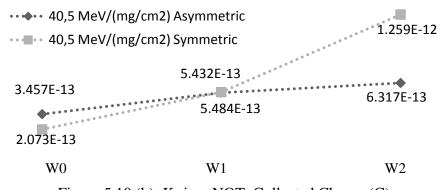

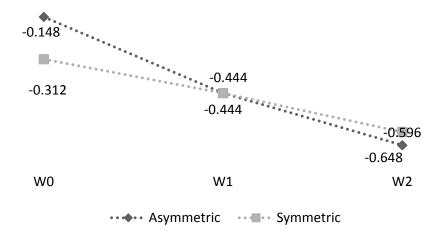

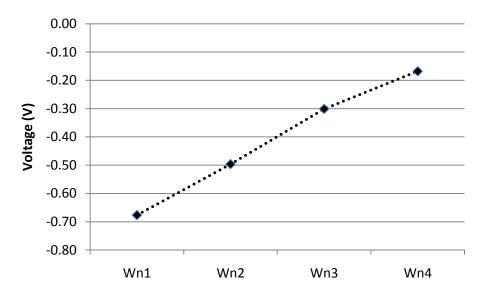

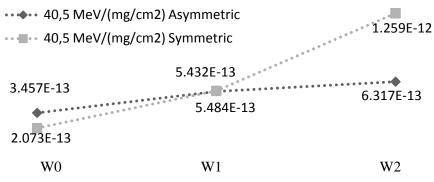

| Figure 6.5 (a): 40.5 MeV/(mg/cm <sup>2</sup> ) ion – SET Pulse Peak (V)           | 84 |

| Figure 6.5 (b): 40.5 MeV/(mg/cm <sup>2</sup> ) ion - Pulse Width (s)              | 85 |

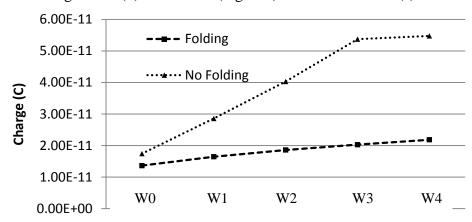

| Figure 6.5 (c): 40.5 MeV/(mg/cm <sup>2</sup> ) Ion – Collected Charge (C)         | 85 |

| Figure 6.6: Alpha Particle – SET Pulse Peak (V) for 1.31 MeV(mg/cm <sup>2</sup> ) | 85 |

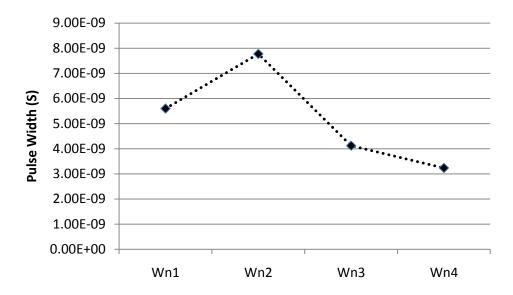

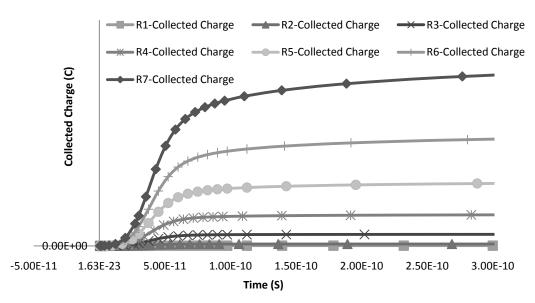

| Figure 6.7 (a): 26.5MeV/(mg/cm <sup>2</sup> ) ion- Collected Charge (C)           | 86 |

| Figure 6.7 (b): 26.5MeV/(mg/cm <sup>2</sup> ) ion- SET Pulse Peak (V)             | 86 |

| Figure 6.7 (c): 26.5MeV/(mg/cm <sup>2</sup> ) ion- Pulse Width (s)                | 87 |

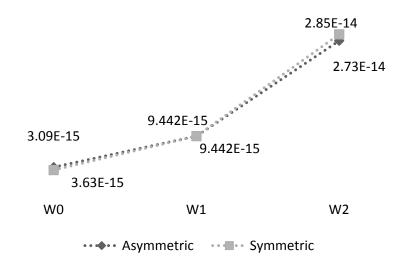

| Figure 6.8 (a): 40.5MeV/(mg/cm <sup>2</sup> ) ion- Collected Charge (C)           | 87 |

| Figure 6.8 (b): 40.5 MeV/(mg/cm <sup>2</sup> ) ion -SET Pulse Peak (V)            | 88 |

| Figure 6.8 (c): 40.5 MeV/(mg/cm <sup>2</sup> ) ion – Pulse Width (s)              |    |

|                                                                                   |    |

# LIST OF TABLES

| Table 3.1: Dimensions and doping profiles                       | 46 |

|-----------------------------------------------------------------|----|

| Table 4.1: LET table for H ion.                                 |    |

| Table 4.2: LET table of He ion                                  | 54 |

| Table 4.3: Ion Profiles                                         | 60 |

| Table 5.1: 3D NMOS Asymmetric Sizing                            | 66 |

| Table 5.2: 3D NMOS Symmetric Sizing                             | 66 |

| Table 5.3: Output Capacitances placed at the target gate output | 67 |

| Table 5.4: Ion profiles used at simulations                     | 67 |

| Table 5.5: Pull-up transistor is sized                          | 76 |

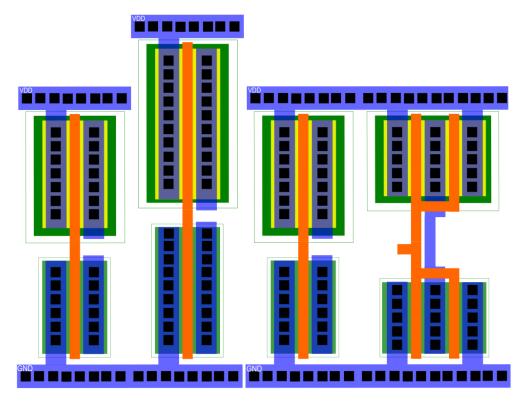

| Table 6.1: 3D NMOS Symmetric Sizing                             | 81 |

| Table 6.2: 3D NMOS varying number of parallel devices           | 82 |

### **ABSTRACT**

In this work the transistor sizing and folding techniques were evaluated for SET robustness in a 90nm MOSFET technology using a 3D device model. A n-type MOSFET transistor using a 90nm technology predictive profile was modeled and functional behavior compared with PTM level 54 model showing a fit of the device with the PTM. During simulations the modeled device was irradiated in a simulation environment using particles with the profile of sea and space level ions. The radiation effects simulation had indicated that the transistor sizing can be more or less efficient to reduce SET according to the collected charge. It was found that for environments with high energy particle, transistor sizing was not able to reduce soft errors intensity. The use of folding has shown significant reduction of the amplitude and duration of the transient pulse, making this technique very useful to reduce soft errors. For alpha particles and heavy ions the combination of transistor folding and sizing had shown to be an effective combination to enhance the reliability of the circuits. A 6T SRAM cell was modeled to evaluate transistor sizing and folding techniques and the results confirmed the efficiency of folding plus sizing to reduce the effects of radiation.

**Keywords:** Radiation effects, Single Event Effect, Transistor Sizing, Folding, Microelectronics, Fault Tolerance, Soft Errors.

# Análise da influência do dimensionamento e partição de transistores e na proteção de circuitos contra efeitos de radiação.

## **RESUMO**

Este trabalho apresenta uma avaliação da eficiência do dimensionamento e particionamento (folding) de transistores para a eliminação ou redução de efeitos de radiação. Durante o trabalho foi construído um modelo de transistor tipo-n MOSFET para a tecnologia 90nm, utilizando modelos preditivos. O transistor 3D modelado foi comparado com o modelo de transistor elétrico PTM level 54 da Arizona State University e os resultados mostraram uma coerência entre os dispositivos. Este transistor modelado foi irradiado por uma série de partículas que caracterizam ambientes terrestres e espaciais. Foi descoberto que a técnica de redimensionamento de transistores tem sua eficiência relacionada ao tipo de partícula do ambiente e não é aplicável em ambientes com partículas com alta energia. Descobriu-se também que aplicando o particionamento de transistores é possível reduzir a amplitude e a duração de erros transientes. A combinação do dimensionamento e o particionamento de transistores pode ser utilizada para a redução de efeitos de radiação incluindo partículas leves e pesadas. Por fim um estudo de caso foi realizado com uma célula de memória estática de 6 transistores utilizando as técnicas mencionadas anteriormente. Os resultados da célula de memória indicaram que a combinação das duas técnicas pode de fato reduzir e até impedir a mudança do estado lógico armazenado na célula.

**Palavras-chaves:** Efeito de radiação, Evento de efeito único, Dimensionamento de transistores, Microeletrônica, Tolerância a falhas, Erros transientes.

## 1 INTRODUCTION

Integrated Circuit (IC) is a semiconductor device consisting of electrical components such as transistors, diodes and capacitances (REIS, 2002). The main component of an IC is the transistor, an electric device made by the overlaying of semiconductor materials with doses of positive and negative ions. These ICs are used to build devices that will be used at televisions, cellular phones, computers, medical equipments, avionic instruments and military instruments (RABAEY, 2003).

The use of an IC is transparent to users, but it is becoming even more present to their lives. One of the factors that had contributed to the success of ICs is the scaling of the technology to nanometer scale which had allowed to build ICs with higher computational power, lower area occupation and smaller energy consumption. The usage of IC's in more applications had also allowed a reduction in their price, since a larger production reduce the unit price.

The constant increases of the use of electronic devices with their constant scale to nanometer range made a common phenomenon dangerous to IC functionality. The Earth is constantly bombarded by radiation particles from sources of radiation like cosmic rays and the sun. Most part of this radiation is turned away by Earth Magnetic Field or filtrated by Earth Atmosphere, and what can pass has too lower energy and generally can't harm humans and animals. But unfortunately the radiation that is able to pass through earth atmosphere is able to harm electrical devices such as the IC, making rise pulses of energy that can provoke transient effects or even permanent problems (BOUDENOT, 2007).

The same technology scale that had contributed to the diffusion of ICs in many applications had also contributed to the reduction of the tolerance of these devices to radiation effects. The correlation of technology scale and radiation tolerance has been the focus of many works that will be briefly approached at the following.

Johnston (2000) makes a review over the increase of error rate for alpha particles and heavy ions in memory cells. Technology issues about supply voltage, lithography resolution, channel length, and density of devices are discussed and correlated to the soft error rate. Basically, increasing the frequency imposes that transient pulses of small duration are able to disturb the device and small supply voltages indicates that smaller amplitude changes of transient pulses are able to disturb the device which also make it more susceptible to soft error. The reduction of the device thickness contributes to the reduction of the soft error. The work also makes a briefly discussion about the behavior of neutrons at Silicon-on-Insulator devices.

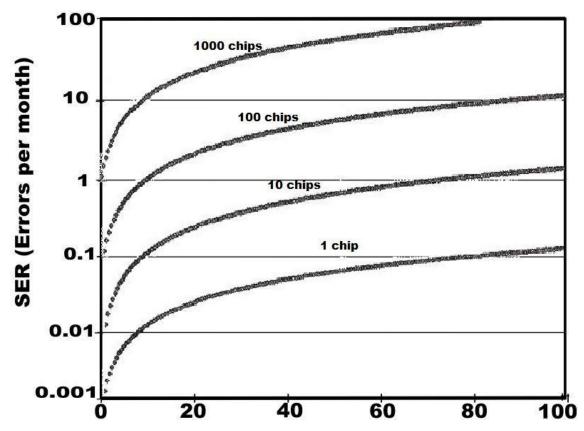

Another work done by Baumann, (2005) does an extensive evaluation of radiation effects and the increase of soft errors in advanced semiconductor technologies focus in memory cells. In figure 1.1 the author analyses the number of embedded SRAM cells

per chip correlated with the soft error rate. The author concludes that SER in single chips system is not a main reliability problem instead of chips with multiples SRAM cells. The author also analyses the reaction of heavy ions inside the silicon evaluating the energy generated by these events correlating the results with the critical charge of the device.

Figure 1.1: SRAM Integration vs. Soft Error Rate (BAUMANN, 2005)

Another important issue about the usage of ICs is that they are fabricated to operate at different environments that also result in different doses of radiation. This is an important point because the common radiation at zero altitude is different from those founded at higher altitudes. Issues about environment conditions will be discussed at chapter 2.

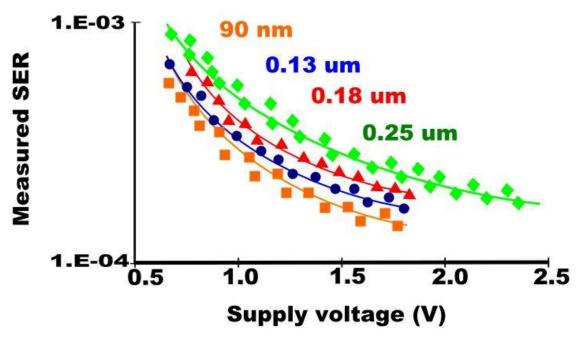

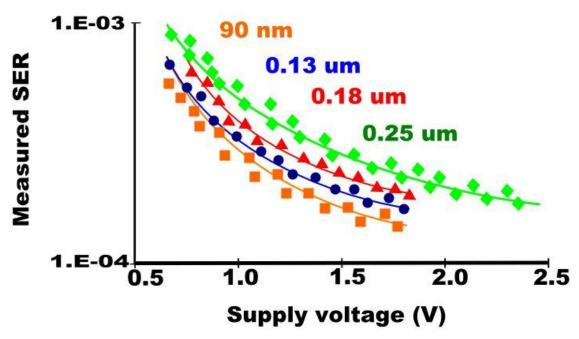

The work done by Hazucha, (2003) evaluates supply voltage scale correlated with the SER generated by neutrons. In figure 1.2 the author presents results for test chips using 90nm, 0.13um, 0.18um and 0.25um technologies. It is clear that for all technologies the supply voltage scaling for smaller values imposes increases at the soft error rate, as also mentioned by (BAUMANN, 2005). The author had analyzed this behavior for PMOS and NMOS diode and has found similar results for the devices.

Figure 1.2: PMOS Diode SER vs. Supply voltage (HAZUCHA, 2003)

The industry and academic institutions have been studying the problems caused by radiation in ICs and some approaches are already know to reduce the problem and make the components less vulnerable to some doses of radiation. The space and avionics industry have a particular interest in research about radiation effects because of the higher doses of radiation that are founded in higher altitudes and space.

The necessity of allowing circuits to tolerate radiation effect, has promoted researches about fault tolerance of radiation effects field at many abstraction levels. Techniques to enhance circuits tolerance to these effects may be applied at all levels of the development of a circuit going from early project decisions and specifications, to techniques applied at fabrication level. One important issue about radiation effects is that they can be permanent or transient and each of them requires different approaches to reduce their effects on devices.

The main motivation of this work is the necessity to evaluate transient radiation effects at nanometer technologies. The analyses of the effectiveness of mitigation techniques like transistor sizing using an accurate simulation tool is required since geometry properties of regions that are impacted by the ion are changed. The transistor folding technique was also evaluated since it is a common layout decision applied by designers to allow the regularity of layout cells with the same width. One important point of this work is that this research field is considered a key area of investigation to all countries that expect to develop a space industry or even avionics instruments which must be also hardened against radiation.

The transistor sizing technique which will be discussed in Chapter 3 is a technique applied at electrical level. The use of the technique to mitigate SET was first proposed by (ZHOU, 2006) and consists of an increase in the transistor width to allow an increase of the total capacitance of the node which contributes to the reduction of the injected pulse. Since this technique is applied and tested at electrical level, no information's about the ion that impact the device and none of geometry and doping characteristics of the device are evaluated. This dissertation is the first work that evaluates the technique at device level.

Other technique that was also evaluated for SET robustness for the first time is the Transistor Folding. The technique is not applied with the purpose of mitigating radiation effects and is used by layout designers to allow the regularity of cells using a same width having a directly impact during the floor planning and placement of the cell. This dissertation is also the first work to evaluate transistor folding impact for transient radiation effects.

## 1.1 Methodology

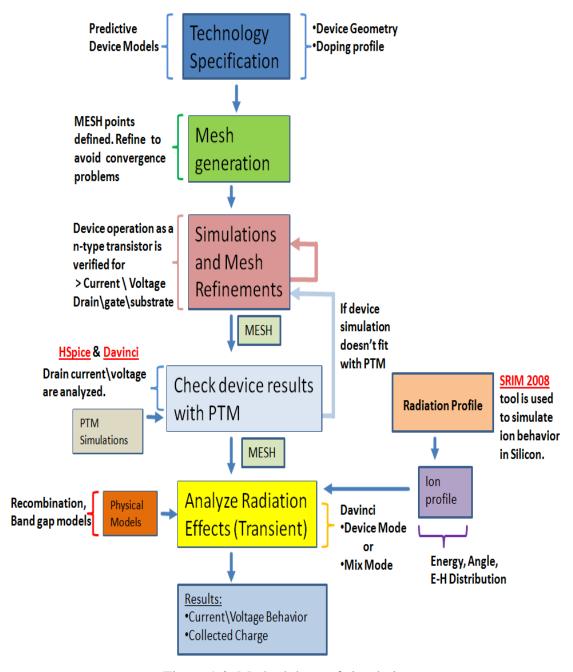

In figure 1.3 the complete methodology used in this work is shown. The first step was the research of technology specifications to build a model of the device that would be used during simulations. At this step the main issues were to obtain device and geometry profiles of the transistors to be used in simulations.

The second and third step consist in the generation of the MESH and simulations to evaluate if the device has the desired behavior. The following step is done simulating predictive models at spice level and comparing the behavior of the modeled device. If the device doesn't have the desired behavior it must return to possible refinements.

After the device is validated, analyses of radiation simulations are done. The tool Stopping and Range of Ions in Matter - 2008 (ZIEGLER, 2008) is used to obtain ion profiles and those are injected at the device by Davinci (SYNOPSYS, 2006). Once these simulations are done the results can be evaluated.

Figure 1.3: Methodology of simulations

Notice that for standalone electrical simulations the HSpice tool from Synopsys is used to evaluate transistors behavior. For device simulations and mix-mode simulations the tool Davinci also from Synopsys is used. For radiation profile and the evaluation of the linear energy transfer of ions the tool SRIM 2008 is used. At next section the thesis organization is detailed.

## 1.2 Dissertation Organization

This dissertation is organized as follows. In chapter 2 the main radiation sources and Earth environment is discussed. Radiation effects and main mechanisms to the generation of transient effects are approached in section 2.2, and in section 2.3 techniques used to detect and mitigate transient and permanent effects are briefly discussed. In section 2.4 the main radiation equations and models are briefly presented.

In Chapter 3 predictive models used to build the test device is presented. In Chapter 4 issues about ion profiles are discussed. In section 3.4 ion profiles used to irradiate the devices are presented with the tool used to evaluate the interaction of each ion with silicon.

In chapter 5 the transistor sizing technique is presented and the devices used during irradiation are showed. In section 4.2 and 4.3 results and main conclusions are approached.

In chapter 6 the folding technique is discussed and the devices modeled to simulations are presented. Section 5.2 and 5.3 include results and main conclusions. In chapter 7 main conclusions of the dissertation are discussed.

## **2 RADIATION OVERVIEW**

Radiation is defined as energy in transit as high-speed particles or electromagnetic waves (YAVORSKY, 1972). Its classified as ionizing and non ionizing radiation. Ionizing radiation has sufficient energy to create charged particles (ions) from atoms by removing electrons. Non ionizing radiation has low energy and cant strip electrons from the orbit of other atoms, so it's not able to create ions, besides that non ionizing radiation is only able to disturb others atoms when collide with another atom. The ionizing radiation is able to interact with other particles by Coulomb interaction which allows this kind of particle to disturb a higher number of atoms of the lattice structure of the device (TEODORESCU, 2005).

When analyzing radiation effects, the kind of ion that is most common at the environment will have strong impact on simulations. For example, simulations with neutrons deal with a non ionizing radiation that creates energy by the impact of the neutron with ions used at the doping of the device as shown in equation 2.1. This reaction may also create an ionizing radiation which makes this simulation more complex to simulate and requires specific tools.

$$^{10}B + n \rightarrow Li^{7}(0.84~MeV) + He^{4}(1.47MeV) + Gamma(0.48MeV)~(2.1)$$

(ZIEGLER, 2004)

At the following section the main radiation sources are presented and Earth environment is briefly approached. Understand these environments are a key factor to allow a proper evaluation of radiation effects at Earth and surround space.

### 2.1 Radiation Sources and Earth Environment

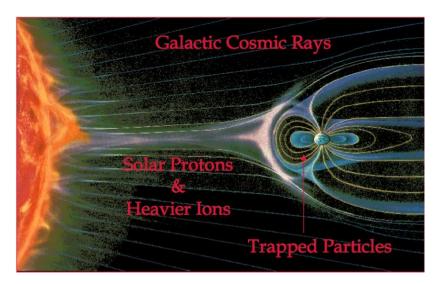

Earth receives constantly radiation from different sources from space. The three major sources of radiation are: Sun, Cosmic Rays and Radiation Belts (on earth referred as *Van Allen Belts*). Each of these sources has their own characteristics that will be briefly discussed on the following paragraphs. Figure 2.1 shows the main sources of radiation in Earth surround space.

Figure 2.1: Cosmic radiation and Solar Events (BOUDENOT, 2006)

The Sun is a star at solar system with a mass of about 1.989e30 kg with a temperature of about 5800 K that is in constantly on activity (SEDS, 2007). The activity in the Sun generates solar winds and coronal mass ejections that continue emit particles into space. Solar Wind is a stream of particles generated by the sun and is mainly composed of protons and electrons of about 1 keV. A coronal mass ejection (CMEs) is a sudden energy release from the Sun, generating a cloud of charged particles and is preceded by a shock wave. These particles are ejected from the atmosphere of the sun with a very high velocity.

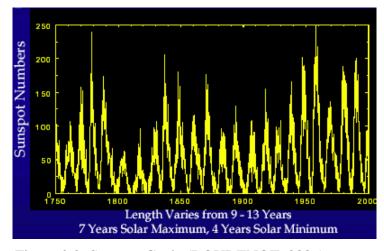

Another important factor that contributes to the rate of upsets caused by radiation is the Sunspot Cycle as shown in figure 2.2. The Sun has a cycle of about 9 to 13 years in which the solar activity varies through a high and low period of emission of particles on the space.

Figure 2.2: Sunspot Cycle (BOUDENOT, 2006)

The information provided by the Sunspot Cycle is used to control missions schedule and the necessary hardening to be used by satellites and space missions. The higher number of Sunspot indicates a higher number of activities and implies on higher doses of radiation that will affect electronics.

Cosmic radiation can also provoke failure in a circuit. It is composed of a mixture of interstellar material from stars, supernovae and *Wolf-Rayet Stars*. *Wolf-Rayet Stars* are massive stars that are losing mass rapidly in the form of stellar wind (BOUDENOT, 2007). *Supernovae* is a stellar explosion that creates plasma (ionized matter) and spread most part of the material of the star through the galaxy (TEODORESCU, 2005). The composition of cosmic ray is about 90% of *protons*, 9% of *alpha particles* (*He nuclei*) and about 1% of *electrons* (TEODORESCU, 2005).

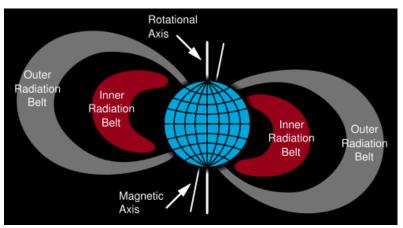

Figure 2.3: Van Allen Belts (BOUDENOT, 2006).

Particles generated from outer space and solar winds when near earth are influenced by earth magnetic field. This influence captures some of these materials and creates belts called *Van Allen Belts* (TEODORESCU, 2005). Earth *Van Allen Belts* are composed of two belts each one with their own characteristic. In figure 2.3 the Van Allen Belt. The outer belt is at about 13.000 km and 65.000 km of altitude and is mainly composed of *electrons* and some *ions*. The major range of energy of these particles is between 0.1-10.0 MeV. The inner belt extends from 700 km and 10.000 km of altitude and the major composition is of *protons* and some *electrons*. The *protons* from inner belt can reach 100 MeV and the *electrons* about 100 keV (TEODORESCU, 2005).

Understanding of the *Van Allen Belts* is critical to space programs of space industry. Commercial and Military satellites must avoid areas of high radiation to make possible the property work of their system, and to increase their lifetime. In space travels the *Van Allen Belts* are also critical. Besides the problems that high doses of radiation can cause on electrical devices, astronauts also suffer effects and must be preserved of this kind of exposure.

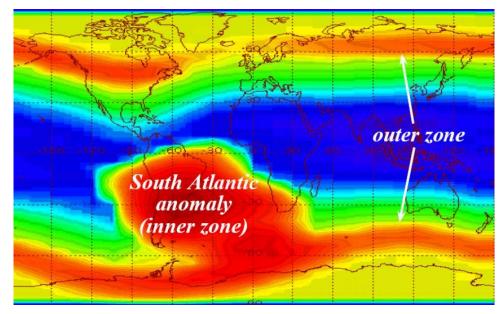

The interaction of particles from the sources discussed before with Earth magnetic field has not the same influence for all regions of the planet. In figure 2.4 it is showed what is called *South Atlantic Anomaly* (SAA), a region of high incidence of radiation particles from the space. The red zone indicates a high number of incident particles and blue zones a low number of particles. This anomaly is justified due to the asymmetry of Earth magnetic field which drives a large number of particles for the red zones. This asymmetric behavior is not constant and the anomaly moves with changes in the magnetic field.

Figure 2.4: South Atlantic anomaly (BOUDENOT, 2006)

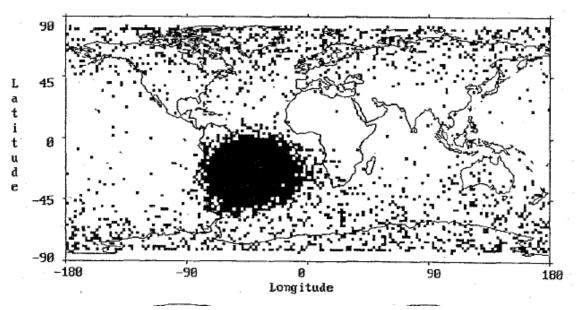

The confirmation of the effect of the SAA in electronics came with the analysis of the number of measured soft errors at experimental tests over the environment using memory cells. At (DYER, 96) the author brings the measurements of SEE at different environments including SAA region. In figure 2.5 the SAA and measured soft error rate.

Figure 2.5: Soft Error Rate at Earth (BOUDENOT, 2006)

Besides these primary sources of radiation there are also secondary radiation sources that are the result of radiation interaction (of primary sources) with earth environment. This interaction generates other range of particles kind and energy making this study more important to understand the radiation environment at Earth atmosphere. In figure 2.6 it is showed the interaction of particles from the space with earth atmosphere.

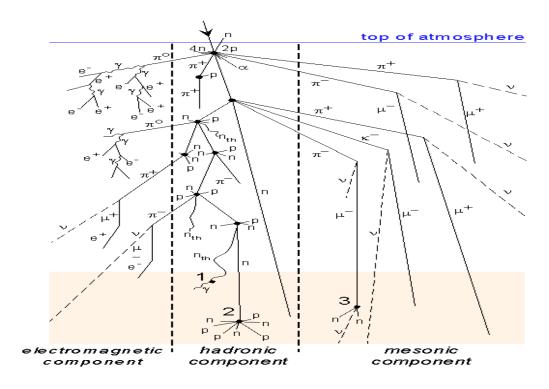

When interacting with the atmosphere the radiation particle suffers collisions with atoms, liberating *electrons*, *protons*, *neutrons* and streams of *alpha*, *beta and gamma* decay. But the main component generated by these collisions is the *neutron*, which is

the main cause of upsets in ICs at sea level. In the Figure 2.6 electromagnetic component are the *electrons* and *gamma decay*. *Hadronic* components are *hadrons*, a subatomic particle composed by *quarks* and *antiquarks*. *Measonic* component are *measons* a kind of *hardron* with high force of interaction. *Hardrons* and *measons* are all subatomic particles generated by nuclear reactions. For currently technology hardrons and measons does not have significant effect in ICs, as they have a too low energy, to interact with MOS transistors elements.

Figure 2.6: Radiation interaction with atmosphere (DALHOUSIE, 2008)

As mentioned before, neutrons are the main concern type of radiation at Earth atmosphere therefore studies are done to model these environments. At (BAKER, 1993) the author creates Neutron Flux model to evaluate the rate of neutrons at different altitudes and latitudes. At (LERAY, 2004) the effects of Neutron on IC are approached.

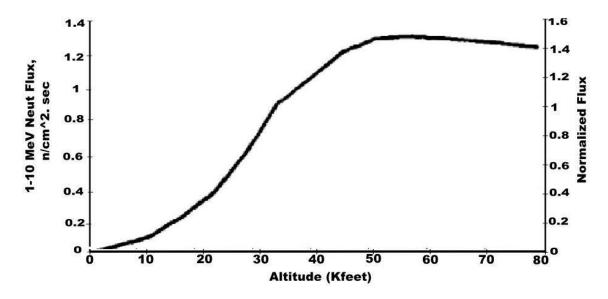

The *Neutron Flux* is studied to create a profile of regions with lower and higher doses of neutrons. These data are important to detect the places on Earth with higher probability to suffer effects of radiation. The atmospheric neutron model (equation 2.2) proposed by BAKER using altitude and latitude informations is presented at the following. In figure 2.7 is presented the relation between altitude and neutron flux.

The rate of neutrons increases with the altitude indicating the necessity of a higher protection to electronics operating in these environments. This increase has directly impact in soft error rate since with more particles the probability of errors increases, besides the fact that increasing the altitude the range of the energy of the particles at these environments also increases. The following equation is proposed by BAKER to obtain the neutron flux using altitude informations.

Figure 2.7: Altitude vs. Neutron Flux (BAKER, 1993)

$$x = 1033 exp \left[ \begin{cases} -0.04534 - (1.17E - 9)x \\ |(A - 1.05E5)/1E3|^{3.58} \end{cases} (A/1000) \right] (2.2)$$

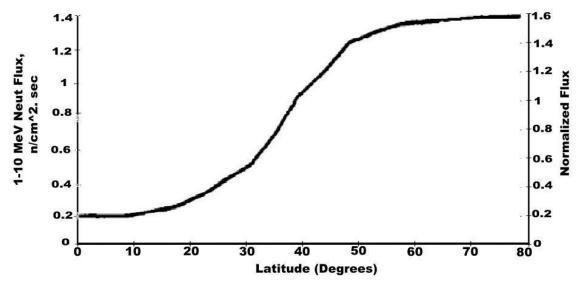

The neutron flux and its relation with the latitude is also modeled by BAKER. The Neutron flux also increases with higher altitudes. This difference can be understood by the studied of the asymmetric magnetic field of Earth which concentrates the radiation particle at higher latitudes (BAKER, 1993). In figure 2.8 it is shown the relation between the latitude and the flux of neutrons. The equation 2.3 represents the model proposed by BAKER to latitude.

Figure 2.8: Neutron flux vs. latitude. (BAKER, 1993)

$$\emptyset_{1-10}(Lat) = 0.6252exp \begin{cases} -0.461[\cos(2xLat)]^2 \\ -0.94\cos(xLat) + 0.252 \end{cases}$$

(2.3)

Using models of the radiation environment like the presented BAKER it is possible to predict the radiation level and the expected upset rate for electronic devices. These informations are useful to understand the ion profile in the environment on which the electrical device will be exposed.

There are other resources that models space environment. For space weather information and detailed flux of electrons, protons and heavy ion flux consult NASA space weather site at (NASA, 2008b). For specific information about environments and measurements of radiation in Earth consult the Cosmic Ray Energetic and Mass (CREAM) project of NASA and University of Maryland at (NASA, 2008a). In next section the main radiation effects in circuits are discussed.

### 2.2 Radiation Effects

Radiation effects can be classified as transient or permanent effects. Transients effects are those that have a specific duration of time and will eventually disappear. Permanent effects are not related with the time and will not disappear with the time. Some of the main radiation effects in integrated circuits are classified as follows (Kastensmidt, 2003):

- a) Permanent effects

- a. *Total Ionizing Dose* (TID)

- b. Displacement Damage (DD).

- b) Transient effects

- a. Single Event Transient (SET)

- b. Single Event Upset (SEU)

- c. Single Bit Upset (SBU) and Multiple Bit Upset (MBU).

There are other effects that will not be approached in this work like: *Single Event Functional Interruption* (SEFI), *Single Event Gate Rupture* (SEGR) and *Single Event Latchup* (SEL). In the following paragraphs it is presented a briefly discussion about each permanent and transient effect listed before.

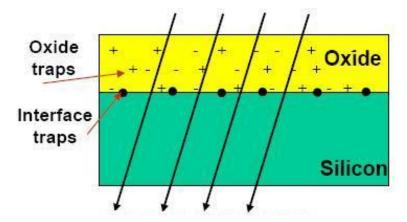

A Total Ionizing Dose occurs in a semiconductor or insulating material during the creation of electron-hole pairs. In the gate and in the substrate the electron-hole pairs quickly disappear since these are conductive materials with low resistance, but in the oxide which is an insulator (high resistance) only a fraction of electron-hole pairs recombine immediately after creation allowing the appearance of void regions that will degrade the device. When a positive bias is applied to the gate, the electrons are attracted to the gate and holes are moved towards the dioxide of silicon interface creating trap regions (LIU, 2007). This continuo ionization makes the threshold-voltage of the device shift and provokes also the mobility degradation of the gate (DUSSEAU, 2007). In figure 2.9 the TID mechanism is shown.

Figure 2.9: Total Ionizing Dose mechanism (ECOFFET, 2007)

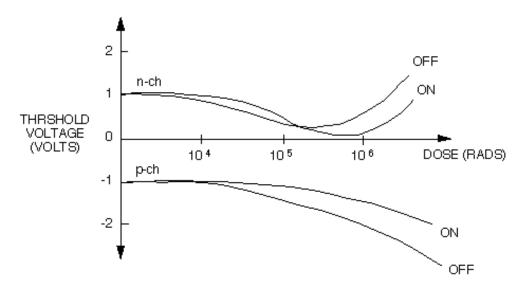

It is important to notice that the main effect of TID is over the oxide and interface. In figure 2.9 the recombination of electron-hole pairs is low and so the electrons and holes are free to move when a bias is applied at the gate. In figure 2.10 it is shown the increase of the radiation dose and the effect of TID in device threshold.

Figure 2.10: Threshold shift during radiation (NASA, 1993)

In the test done by (NASA, 1993) the n/p-channel are irradiated and the threshold is evaluated during the test. Since this is a cumulative event, it is expected that the shift of threshold increase over the time. The leakage current will also increase due TID effect. The TID must be mitigated to ensure the lifetime of electronics in space environment. To ensure that an electrical device is able to be used in a space project, the device pass through a qualification test in which each device is irradiated with incremental doses of radiation (COCHRAN, 2005).

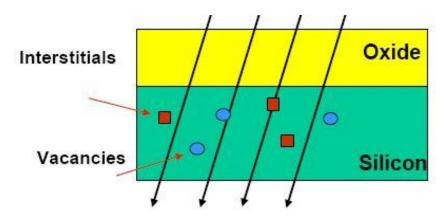

Another permanent effect is the Displacement Damage, which is the result of nuclear interaction of the incident particle, causing the displacement of atoms of the device to other regions. This kind of interaction can be done by the primary particle or other secondary particles that were generated through the interaction of the primary

particle with the device material (SROUR 2003). At DD most of energy is transferred when an atom is knocked (DUSSEAU, 2007). The DD mechanism is shown in figure 2.11.

Figure 2.11: Displacement Dose mechanism (ECOFFET, 2007)

In figure 2.11 interstitials are atoms dislocated by the radiation particle to regions between atoms of the lattice structure of silicon. Vacancies are unoccupied regions of the lattice structure of silicon (ECOFFET, 2007). The DD cause permanent defects over the device and it main effects are the degradation of gain and leakage current in bipolar transistors. In figure 2.12 the Non-Ionizing Energy Loss (NIEL) is shown. NIEL is the rate in which a non-ionizing energy is lost at the device. The picture shows the decreasing of device lifetime during the radiation of Protons.

Figure 2.12: DD effect on lifetime. (DYER, 2006)

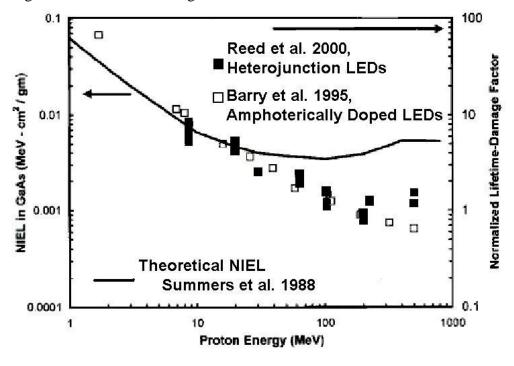

Besides permanent effects, there are also transient phenomena. In figure 2.13 the mechanism of soft error generation is shown. In the picture it is seen a cross-section of the Drain of a transistor. A p-type substrate with an active region of n-type is showed, as a part of a n-type transistor. In the figure it is considered an abrupt-junction to simplify the mechanism. The mechanism of generation of a single event effect occurs during the passage of the ion over the drain (*pn junction*). During this event the ion generates a burst of electron-hole pairs that will be distributed over the device. This passage makes the funneling of the electric field of the charged region. This funneling will be able to collect e-h pairs that will be generated out of the drain volume (HU, 1982). Basically carriers will move to the charge region by drift due to electric field and diffusion due to the large concentration of carriers during the ionization. The distribution of carriers will have a directly impact over the collected charge since carriers concentration will have impact on carrier recombination that will also have an effect over the collected charge.

Figure 2.13: Soft error mechanism

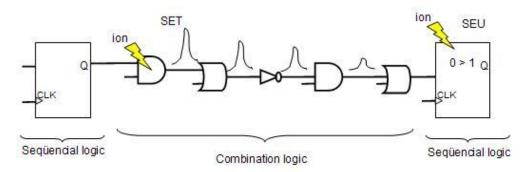

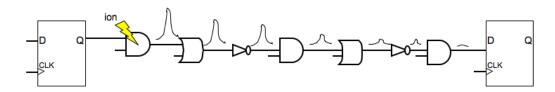

The mechanism described before can generate an effect that is called single event effect (since generally occur in just one device) or even referred as a soft error. When this event occurs in a sequential circuit it is called Single Event Upset (SEU) and when it happens in a combinational circuit and is able to turn into a pulse similar to the logical "0" or logical "1" it is called Single Event Transient (SET). A SEU is an upset caused on a memory cell and when this value become permanent (until it is written again) it is called Single Bit Upset (SBU). A MBU is an occurrence of multiples SBU by different particles or even by the interaction of one single event with multiple devices. SEU and SET events are showed in figure 2.14. In figure 2.14 it is shown a SEE generated at the combinational logic provoking a SET, and a SEE generated at the memory element provoking a SEU.

Figure 2.14: SET and SEU at logic

These events (SET and SEU) can be mitigated by different approaches at high abstraction levels. A SET depends on factors like electrical/logic/window masking factors to cause an upset in the flip-flop. An electrical masking occurs when the transient pulse is degraded by electrical characteristics of the circuits and is not able to reach a storage device. A logical masking is when the transient pulse is masked by the logic of the cell, this is shown in figure 2.15. A window masking is when the transient pulse generated in the combinational logic reaches a sequential logic element which is using a clock and at that time the clock signal was not indicating to the sequential element to store the input value.

Figure 2.15: Logical Masking factor

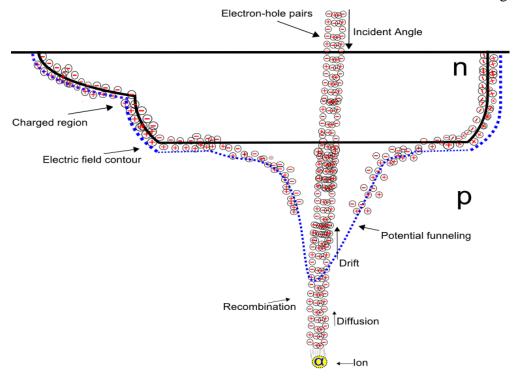

The view of transient effects generated by a single burst of one interaction is a typical modeling for single event effects that is widely used by research community and most supported by TCAD tools. However researches have been conducted to show that more phenomena occurs inside the device having strong difference with the simplify model. It has been showed that a particle passing through the integrated circuit can provoke a chain reaction generating different kinds of events with different magnitudes. In (SCHRIMPF, 2007) the author show experimental works in which the reaction of the particle inside the silicon generates secondary reactions that will affect the device. In figure 2.16 and 2.17 it is showed two different analysis of the path of the same particle.

Figure 2.16: Path of a particle inside the silicon (SCHRIMPF, 2006)

The picture shows an incident particle with the generation of electron-hole pairs almost uniformly over the path without considering the possibility of second interactions. The calculation of electron-hole pair generation in this kind of situation is trivial and is the most used approach. For the event with this path and reaction interpretation the equation (2.4) of the *LET* has a great agreement with the model.

In figure 2.17 the path of the particle inside the silicon is considered using a model to analyze the secondary reactions of the primary particle.

Figure 2.17: Multiple interaction of the particle (SCHRIMPF, 2006)

This picture show how complex the system can behave with a single particle. The electron-hole generation is increased with the reaction of secondary particles and with multiple paths that occur when a secondary particle moves inside the silicon generating more electron-hole pairs and maybe other nuclear reactions with more interactions.

For this kind of event the model using the basic LET equation doesn't fit anymore and it is necessary to expand the interpretation of the event to have a better agreement of the event with the basic equations. The industry is starting to know more about this kind of event and there is no much information about the calculation of the energy transference and prediction of it.

Unfortunately simulating these multiples interactions imposes the necessity of using specific tools that are very rare and most of them closed for internal use of specific research groups. In this work multiple interactions were not considered and simulations are done using the model of one single interaction. In the next section the main techniques to mitigate radiation effects will be briefly discussed.

## 2.3 Techniques to Mitigate Radiation Effects

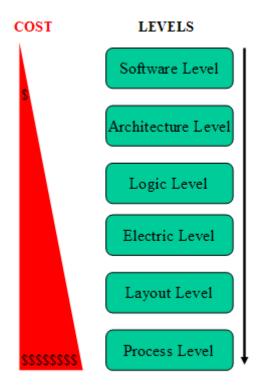

Techniques to mitigate radiation effects on IC and specially ASICS can be applied in the following levels of abstraction: process, layout, electric, logic, architecture and software. In figure 2.18 a brief diagram of the abstractions levels is shown.

Figure 2.18: Abstraction Levels

Notice that techniques applied at higher levels generally have a lower cost of time and money when compared with lower level techniques. This occurs because higher abstraction level techniques take advantage on the simplification of the problem which they propose to solve. At higher abstraction levels the radiation effect can be seen as a simple change in a variable of a program making the resolution of the problem less complex than in lower levels. Be aware that this doesn't necessary means that higher level techniques are easier to implement since there are other considerations of the problem like the size of the system to be harden and its complexity. At the following paragraphs a brief review about each level of abstraction and the major techniques used by each one.

For process level some techniques are buried-layer implant and EPI substrate. At (ZIEGLER, 2004) these techniques are discussed and at this work they will be briefly explained. The buried-layer implant consist in a highly defect or doped layer below the device. The idea is to reduce the mobile electrons or holes concentration at this layer. As mentioned in chapter 3 the high doped area will suffer more electron-hole recombination, this will leave the other layer suffering less effects from the particle interaction.

The *Epitaxial Substrate* (EPI) is similar to the buried-layer presented before. The technique is based on using a highly doped substrate which will allow a quickly recombination of radiation particles when interacting with the layer. Consult (ZIEGLER, 2004) to an extensive discussion about these techniques.

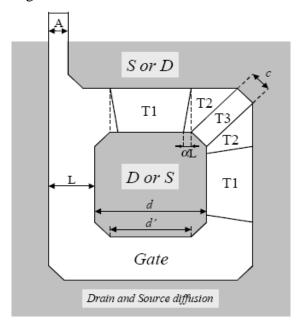

At layout level the major techniques are: guard rings and enclosed geometries. In (CHEN, 2005) the efficiency of Enclosed Layout Transistor (ELT) to mitigate TID and

SEL is studied with n-type transistors in 0.18 um technology. As showed in the latter section one of the main effects of the Total Ionizing Dose is the shift of the threshold of the device which is a permanent effect. The ELT technique changes the design of the basic transistor layout reducing the effect of radiation to change the threshold of the device. With this new configuration showed in figure 2.19 it is required a larger number of collisions to make a significant shift in the threshold of the device.

Figure 2.19: Enclosed Layout Transistor Design

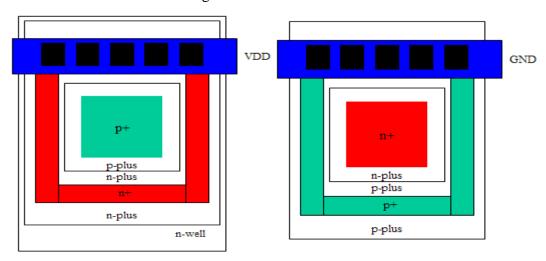

The other common technique used at layout level is the guard ring. The guard ring technique (figure 2.20) consists in making a ring over the transistor and biasing this ring with the supply voltage (for p-type) and ground (for n-type). This polarization will create a dummy collector that will capture (electrons or holes) depending on the polarization. This technique will reduce the collected charge of the device and also reduce the current in the substrate. In (CLARK, 2007) the technique Guard Rings and ELT are used to reduce the leakage current of irradiated devices.

Figure 2.20: Guard Ring layout structure (RABAEY, 2003)

The techniques presented before (ELT and Guard rings) are used by (ANELLI, 2000) to mitigate TID and reduce the collected charge. This work evaluates both techniques and its efficiency to reduce errors. Note that in the layout of the figure 2.21 the ELT is not made with the same geometry showed in figure 2.19. Designers don not need to follow that geometry because the main idea of the technique is to enclose the drain/source regions inside a gate "ring" allowing the existence of an inversion channel at all the ring.

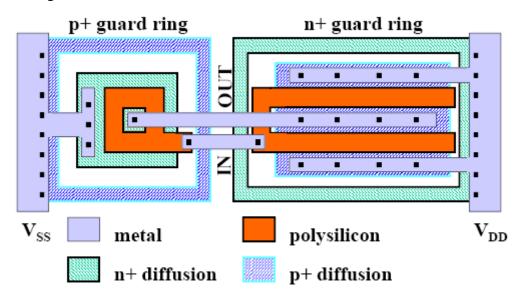

Figure 2.21: Inverter using ELT and Guard Rings (ANELLI, 2000)

At electric level many organizations of transistors are studied to avoid the propagation of the transient. In (ROCHE, 96) it is presented a not gate tolerant to total ionizing dose using a set of auxiliary transistors to control the threshold of the transistors that are damaged during the ionization.

In (ZHOU, 2006) the transistors are resized to avoid the appearance of transients, this is done increasing the width of the transistor which contributes to the increase of the critical charge of the node. In (LAZZARI, 2007) a method to use synchronous and asynchronous resizing is presented and a tool to automatic evaluate circuits is developed.

Logic level techniques can be based on space or temporal redundancy. Space redundancy techniques also called hardware redundancy are based on making copies of the protected hardware and use a voter to select the output that appears more times.

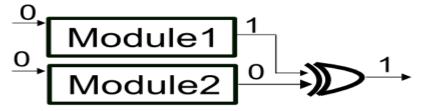

The Double Modular Redundancy technique is a detection technique since it is not able to identify the correct value. The technique proposes that two modules of the circuit should be replicated and a cell is used to compare their results. If the results are not the same, a signal must be sent to the control block to notify that an error had occurred as shown in figure 2.22. The main overhead of DMR technique is in the area of the circuit.

Figure 2.22: DMR (Kastensmidt, 2003)

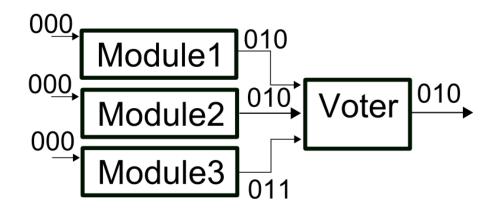

Other hardware redundancy technique is the Triple Modular Redundancy (TMR) described at (RUI, 2006) and (CHEN, 2006) shown in figure 2.23. The technique is similar to the DMR but includes other module and a voter. The technique is able to detect the correct value since it votes for the dominant result. The technique will not vote correctly if there are more than one error of if the error occurs at the voter. There are specific techniques to protect the voter, these will not be approached at this work.

Figure 2.23: Triple Modular Redundancy technique

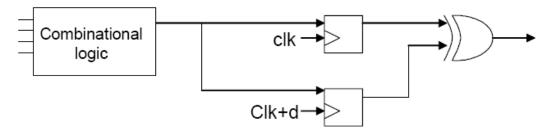

Another commonly used technique at logic level is the Temporal Redundancy (TR) which is based on the use of a delay inside the circuit to compare samples of the signal that is being transmitted with the possibility to filter the transient. Using the architecture showed in figure 2.24 the technique is able to detect the error, but not to correct it.

Figure 2.24: Time Redundancy Technique (KASTENSMIDT, 2003)

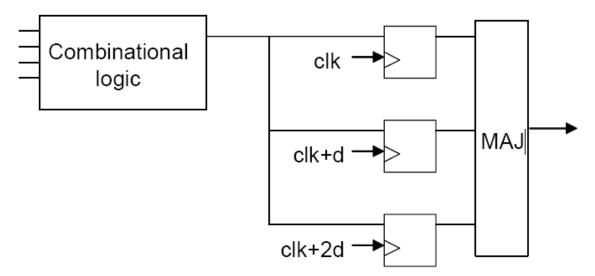

The TR technique can be extended to compare more than one sample of the signal. Using another module to have one more sample of the signal allows TR detects the correct value. This will decrease the performance of the circuit but will allow the mitigation of the soft error, as seen in figure 2.25.

Figure 2.25: Full Time Redundancy (KASTENSMIDT, 2003)

At architecture level the techniques are closed related with the system architecture and can combine a mixture of hardware, software and temporal redundancy. In (FRIEND, 92) the author approaches the design of critical real time applications tolerant to soft errors. In the work of FRIEND the processor of the architecture was designed to verify the integrity of the data using triggers to detect possible faults. The author had also used a software layer to verify the correct operation of the application.

At software level the techniques take the concepts of space and temporal redundancy and apply the techniques at the software level. The techniques can be directly applied at the code that must be protected or can be used an Operating System (OS) to protect the application. In (ANDERSON, 85) the author analyses different software level approaches like redundancy use of variables and recomputation to mitigate transient effects.

Other approaches protect devices without direct contact with the integrated circuit. In (TRIPATHI, 2006) the author describes techniques that use electric-static fields to protect the integrated circuit against ionizing radiation. Other techniques related to the detection and mitigation of soft errors in FPGAs were not approached in this section since this is not the focus of this work. For FPGA mitigation and detection techniques consult (KASTENSMIDT, 2006; KASTENSMIDT, 2007).

# 2.4 Main Equations and Models

The main value used to refer to ion profile during radiation simulations is the Linear Energy Transfer (LET). The LET is the measurement of energy transferred from the ion to the material per unit distance (FACCIO, 2007) and is given by equation (2.4).

$$LET = \frac{dE}{dX} (2.4)$$

where dE is the average energy locally transmitted to the medium by a charged particle in traversing a distance of dx and its unit is given by keV/um. The impact angle

of the ion also contributes to characterization of the energy transfer. The Effective LET is the effective energy that is transferred to the material and is given by (2.5).

$$LET_{effect} = \frac{LET}{Cos\theta}$$

(2.5)

Where LET is the Linear Energy Transfer calculated by (2.4) and  $Cos\theta$  is given by the angle between the vector of the ion, and an orthogonal line to the plane of the device. In radiation effects works the LET is generally expressed in MeV/(mg/cm<sup>2</sup>), this value is obtained by equation (2.6) given by

$$\left[\frac{MeVcm^2}{ma}\right] = \left[\frac{MeV}{cm}\right] \div \left[\frac{mg}{cm^3}\right] (2.6)(SCHIRMP, 2006)$$

where [MeV/cm] is the LET of the ion and [mg/cm<sup>3</sup>] is the mass density of the device. The reader must understand that when using this kind of unit the LET is now dependent of the target material. The number of electron-hole pairs generated by the ion inside the silicon can be obtained by equation (2.7) given by

$$\left[\frac{\#EHPs}{cm}\right] = \left[\frac{MeVcm^2}{mg}\right] \times \left[\frac{mg}{cm^3}\right] \div \left[\frac{3.6eV}{EHP}\right] (2.7)(SCHIRMP, 2006)$$

where the

$$\left[\frac{MeVcm^2}{mg}\right]$$

is the LET of the ion,  $\left[\frac{mg}{cm^3}\right]$  is the mass density of the

material and  $[3.6eV/_{EHP}]$  is the quantity of energy that is required to create an electron-hole pair in the silicon.

In electric abstraction level other approach is generally used to refer to ions. The energy of the ion is commonly expressed in the form of deposited charge which can be calculated by (2.8) and is expressed in Coulombs. To convert typical LET units to Coulombs for Silicon (Si) devices use (2.9)

$$[pC] = \left[\frac{pC}{um}\right] * [d] \quad (2.8)$$

$$\left[\frac{pC}{um}\right] = 0.0446 * \left[\frac{MeV}{um}\right] (2.9)$$

In equation (2.8) the deposited charge is given in [pC], the [pC/um] is the LET of the ion that can be obtained in this unit using (2.9) and [d] is the ion range at the device and is given in [um].

Another parameter that is generally evaluated is the Critical Charge. The Critical Charge is defined as the minimum quantity of energy that is needed to disturb a transistor or a cell and is calculated by measuring the capacitances of the device which is been evaluated. The critical charge can be calculated by equations 2.10a and 2.10b (ZIEGLER, 2004):

$$Q_{crit} = \int_0^{V_{TRIP}} (C_{TOTAL} + 2C_{COUPLE}) dV + n \times I_{N,P} \times T_{PULSE}$$

(2.10a)

$$C_{TOTAL} = C_{GON} \times A_N + C_{GOP} \times A_P + (C_{GDON} + C_{GDLN}) \times w_N + (C_{GDOP} + C_{GDLP}) \times w_p + (C_{JAN} \times A_{DN} + C_{JSWN} \times w_N) + (C_{JAP} \times A_{DP} + C_{JSWP} \times w_p) (2.10b)$$

Where  $V_{TRIP}$  is the standard voltage of technology,  $C_{TOTAL}$  is the total front-end capacitor,  $C_{GON}$  and  $C_{GOP}$  are gate capacitances of N/P transistors,  $A_N$  and  $A_P$  are gate area of N/P transistors respectively,  $C_{GDON}$  and  $C_{GDP}$  are bias-independent part of the overlap capacitance, and  $C_{GDLN}$  and  $C_{GDLP}$  are bias-dependent overlap capacitance. Source and drain junction capacitance are  $C_{JAN}$  and  $C_{JAP}$ , and sidewall capacitances are  $C_{JSWN}$  and  $C_{JSWP}$  respectively (ZIEGLER, 2004).

The relation between Threshold Effective LET and critical charge (Q<sub>critic</sub>) can be obtained by equation (2.11).

$$Q_c = \frac{(L_{Th} * T * d * e)}{x}$$

(2.11)

where  $L_{th}$  is the Threshold Effective LET, T is the device thickness (2.32 g/cm<sup>3</sup> for Si), d the material density and e the electronic charge ( $e = 1.602 \cdot 10^{-7} pC$ ), and x is the energy needed to create an electron-hole par, x = 3.6 eV in Si.

To simulate the current generated by the particle strike the double exponential equation of (MESSENGER, 1982) is used. The equation is given by equation (2.12)

$$I_{in}(t) = I_0 \left( e^{\frac{-t}{\tau_\alpha}} - e^{\frac{-t}{\tau_\beta}} \right)$$

(2.12)

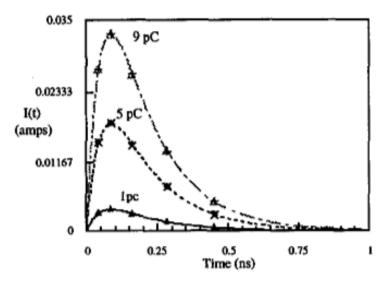

where  $I_0$  is the maximum current, t is the simulation time,  $\tau_{\alpha}$  is the collection time constant of the junction and  $\tau_{\beta}$  is the ion-track establishment time constant. The last two parameters are process dependent. In (NASEER, 2007) authors analyze different equations to model the soft error and compare their results with physical simulations. The results of NASEER have shown that the equation (2.12) fits with device simulation behavior for low energy particles. In Figure 2.26 the equation  $I_{in}$  is used to plot the behavior of the ion for different charges (Q) over the time.

Figure 2.26: Current for different charges. (DHARCHOUDHURY, 1994)

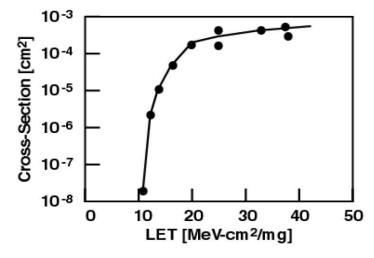

To estimate the vulnerability of a given circuit at circuit level the error-cross section is calculated using equation 2.13. This information is used to estimate the vulnerability of circuits to different LETs. This is generally a form to evaluate the effectiveness of techniques to mitigate errors at different environments (KARNIK, 2004).

$$\sigma_{SEE} = \left[ \#events \right] \div \left[ \frac{\#particles}{cm^2} \right]_{(2.13)}$$

The error cross-section is the ratio of upsets with the number of incident particles by the area. It is calculated by (2.13) in which #events is the number of measured upsets in the circuit and #particles is the number of particles that had been irradiated. In figure 2.27 the error cross section of a circuit is shown, indicating that a LET of more than  $10 \text{MeV/(mg/cm}^2)$  is required to upset the circuit . It is noticed that with the increase of the LET the number of errors increase from many orders of magnitude. The error cross-section is a common method used to analyze the effect of hardening technique.

Figure 2.27: Cross Section of a circuit (SCHRIMPF, 2006).

Besides modeling the ion profile there is the necessity of modeling the transient pulse shape generated by the radiation. In (WIRTH, 2007a) the author developed a model to analyze the transient pulse duration (2.14) the time on which the transient pulse reaches its peak (2.15) and the transient pulse peak (2.16) over the node. These equations take into account the resistance and capacitance of the node and the current obtained from the equation (2.12).

$$T_{D} = t_{peak} - RC \ln \left( \frac{V_{DD} / 2}{V_{peak}} \right) - \tau_{\alpha} \ln \left( \frac{V_{DD} / 2}{V_{peak}} \right) (2.14)$$

$$t_{peak} = \frac{\ln(\frac{\tau_{\alpha}}{RC})\tau_{\alpha}RC}{\tau_{\alpha} - RC}$$

(2.15)

$$V_{peak} = \frac{I_0 \tau_{\alpha} R}{\tau_{\alpha} + RC} \tag{2.16}$$

where R and C are the effective resistance and capacitance of the node. The  $\tau_{\alpha}$  is the collection time constant of the junction. With these information, in (WIRTH, 2007b) the author presents a model to analyze the propagation of transients. The model is used to analyze the behavior of the transient signals through the combinational logic. The model is able to determinate if the transient pulse will be electrically masked by the circuit. The model can be briefly understood by the following equations that models different situations for the pulse and the stage of the logic. The equation (2.17) defines the case in which the transient pulse is not propagated. Equation (2.18) the pulse is propagated and degraded in amplitude and duration. Equation (2.19) the transient is propagated and degraded in duration. Equation (2.20) pulse is propagated but not degraded.

$$if (\tau_n < k \cdot tp)$$

$$\tau_{n+1} = 0 \tag{2.17}$$

$$if (k \cdot tp < \tau_n < (k+1) \cdot tp)$$

$$\tau_{n+1} = (k+1) \cdot tp (1 - e^{2.5 - (\tau_n/tp)})^{(2.18)}$$

$$if((k+1) \cdot tp < \tau_n < (k+3) \cdot tp)$$

$\tau_{n+1} = (\tau_n^2 - tp^2) / \tau_n$

(2.19)

$$if (\tau_n > (k+3) \cdot tp),$$

$$\tau_{n+1} = \tau_n$$

(2.20)

where tp is the propagation delay of the gate,  $\tau_n$  the transient duration at stage n and  $\tau_{n+1}$  the transient duration at stage n+1. K is a fitting parameter that is equal to the minimum ratio of  $\tau_n/tp$  needed by a transient to be propagated into the next stage of a combinational logic. The K is obtained through a stage of characterization of the technology process that will be used. This model is important because it can provide valuable information about the behavior of the transient pulse inside the circuit. In figure 2.28 the electrical masking of the transient pulse that is propagated over the combinational logic is shown. The model proposed before has as target model this behavior.

Figure 2.28: Transient propagation over logic (LAZZARI, 2007)

The information provided by equation (10-12) can be used to analyze the propagation of the ion showed in figure 2.28. With gate delays and information about resistance and capacitance of the nodes it is possible to verify if the transient will reach the sequential element. These equations where used by (LAZZARI, 2007) to analyze the propagation of a transient in a combinational logic to define the necessity to size the transistors to increase the critical charge.

### 3 DEVICE MODELING

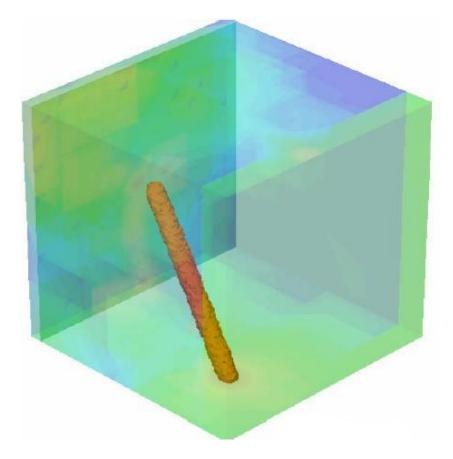

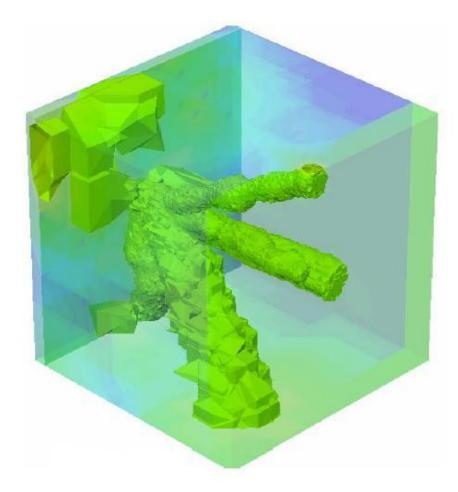

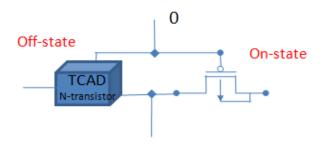

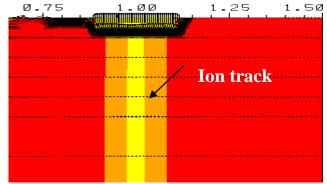

As mentioned in the previous chapter, the simulation of transient radiation effects inside semiconductors devices can be done considering a single or multiple interaction event. Due to software technology limitations this work will be done using a traditional approach used to simulate soft errors considering a single interaction event. This work will be conducted using the TCAD tool Davinci from Synopsys. The tool Davinci allows the creation of semiconductors devices and the simulation of soft errors using a function of generation of electron-hole pairs. This has been the approach to simulate soft errors at researches group that don't have specific tools (generally created by the own group) to simulate soft errors. One example of a specific tool to evaluate transient radiation effects is the Soft-Error Monte Carlo Model 2 (SEMM-2) from IBM, to obtain more information about the tool consult (TANG, 2008).

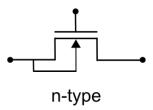

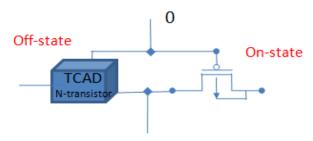

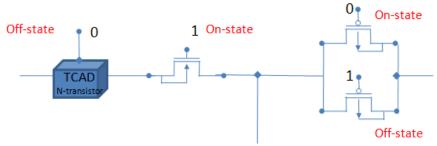

In this work the semiconductor device used during radiation tests was a n-type MOSFET transistor with a 90nm channel length. It was not necessary to build a p-type transistor because the effect that was analyzed in this work has the same behavior for both devices. When simulations required a p-type transistor at the pull-up logic of the gate, a Predictive Technology Model - PTM from ASU electrical model was used. The tool Davinci allows the execution of both device and electrical transistor running in a mode called mix-mode simulation. It must be noticed that to evaluate the soft errors in transistors some works like (HAZUCHA, 2003) do not build the entire transistor, instead they build, just the diode of the device to represent the drain of the transistor. This approach simplifies the simulation but can't be used to evaluate different impact angle of the ion, since other parts of the device (transistor) can influence the behavior the collected charge. In figure 3.1 the electrical symbol of a n-type MOSFET transistor.

Figure 3.1: NMOS transistor symbol

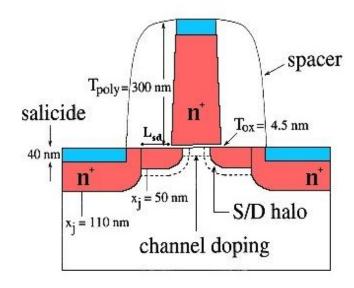

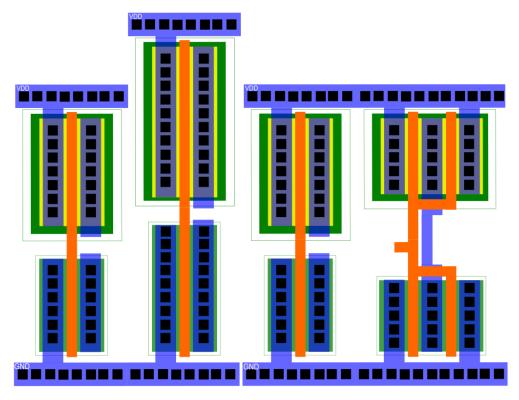

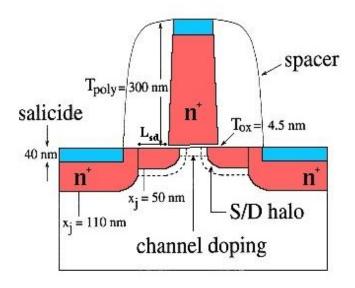

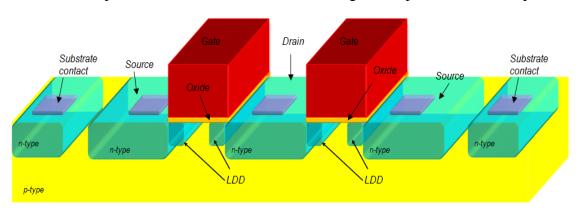

The device modeled in this work was based on data extracted from the models of the Microsystems Technology Laboratory of MIT (DIMITRI, 2008) that has also used information of doping profile of (HU, 1995) suggesting the topology showed in figure 3.2. The model presents a NMOSFET using a Super Steep Retrograde (SSR) channel doping, source/drain halo and a Light Doped Drain (LDD) structure. The SSR technique described at (SRINIVASAN, 2005) and (TIAN, 1994) consists of a channel engineering technique used to prevent short channel effects on nanometer MOS devices. The technique proposes to increase the doping of the substrate (prevent short channel effects) and to create a thin layer with a lower doping near the surface of oxide and silicon to control the threshold of the device.

Figure 3.2: NMOSFET device (DIMITRI, 2008)

Another technique applied at the model showed in figure 3.2 is the use of halos. The halo implant is also a channel engineering technique used to control short channel effects. The halo is able to reduce the effect of the high doping profile of the device that is able to increase hot carriers effects, which consist of the high acceleration of the carrier due to the high electric field produce at the junction. This structure will not be used in this work, for more details about halo implants consult (SRINIVASAN, 2005). Other structure used is the LDD. The LDD structure consists of creasing a small active region that will be overlapped by the channel using a thickness smaller than the active region (Source\Drain) and with a smaller doping concentration (TSIVIDIS, 1999). The technique (LDD) is used to reduce the electrical field strength near the gate channel, making a reduction in hot carrier effect.

Another work presented by (DASGUPTA, 2007) also gives valuable information about a 90 nm NMOS model. Information about n-type and p-type transistors for high performance and low power are presented by the author. There are differences with the model presented before by the MIT. These differences are more aggressive to the substrate doping profile and oxide thickness. For MIT model it is presented a generic transistor with an oxide of 4.5 nm instead of (DASGUPTA, 2007) high performance transistor with an oxide of 1.4nm and low power model with 2.8nm. The substrate doping for both devices is uniform presenting for MIT model about 7e19atm/cm<sup>-3</sup> and for (DASGUPTA, 2007) about 1e16atm/cm<sup>-3</sup>. Both models present similar geometry profiles for the other regions of the device. In next section the modeled device used in this work is presented.

### 3.1 Modeled Device – 3D NMOSFET

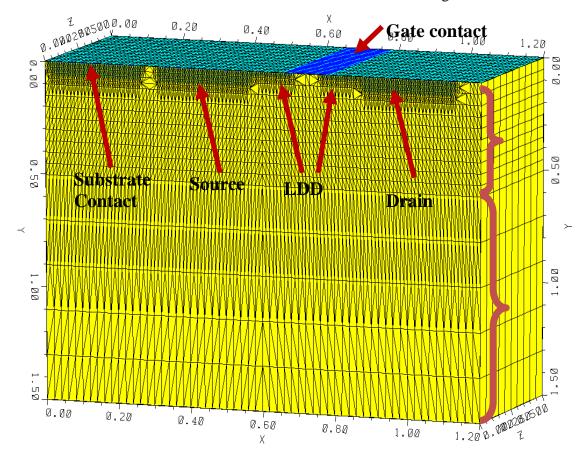

The device the design of the 3D MESH used to model the transistor in Davinci will be briefly described. The 3D MESH is a structure where the device regions are created with the MESH points indicating where physic calculations are done to evaluate the simulations. If the MESH is defined with too much simulation points it will lead to many hours of simulation even if the device is small, but if the number of simulation points is small the results will loose accuracy. This balance between simulation time and accuracy should be adjusted interactively.

An strategy to define the MESH is presented at (DASGUPTA, 2007) where the author suggests the creation of a MESH divided in regions with higher and lower concentration of simulation points and with the refinement of the points in areas where a simulation is more important. Dasgupta (2007) also suggests the creation of the 3D MESH from the top to the bottom. These indications were followed as it will be described.

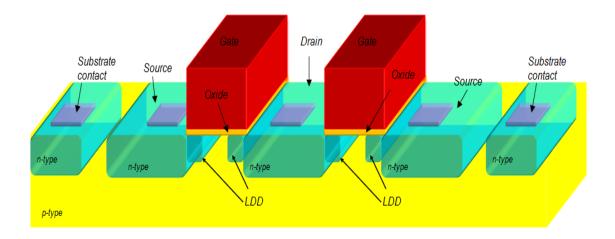

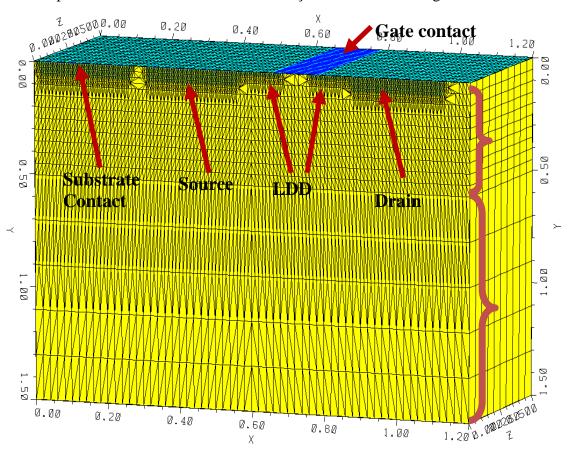

The Y axis was defined with two regions, the first from 0.0 to 0.5um with the spacing from mesh points of about 50 nm. The second region was defined from 0.5 to 1.5 um with an increase in the spacing between mesh points to 2um. Over active regions MESH is refined to receive more simulation points allowing a more accurate simulation. The refinement of the active region was used to reduce the spacing for 10nm. This kind of refinement can be done at any time during simulations. In figure 3.3 the cross-sectional view of the NMOSFET 3D MESH that was designed.

Figure 3.3: Developed NMOS 90nm device

Detailed information about doping and geometry profiles of the device is shown in table 3.1. Notice that these dimensions are based on (DASGUPTA, 2007) and (DIMITRI, 2008).

Table 3.1: Dimensions and doping profiles

| Region           | Width (x) | Width(y) | Width (z) | Doping             |

|------------------|-----------|----------|-----------|--------------------|

| LDD              | 115 nm    | 30 nm    | 240 nm    | n-type. Peak: 1e19 |

| Source\Drai<br>n | 240 nm    | 60 nm    | 240 nm    | n-type. Peak:1e20  |

| SSR       | 90 nm  | 5 nm   | 240 nm | n-type. Peak:1.5e18 |

|-----------|--------|--------|--------|---------------------|

| Gate      | 136 nm | 300 nm | 240 nm | n-type. Peak:2e20   |

| Oxide     | 136 nm | 1.4 nm | 240 nm | None                |

| Substrate | 0.9    | 1.5    | 0.3 um | p-type. Peak:5.5e18 |

The doping of both active regions and SSR has Gaussian distribution. The doping of the substrate is uniform. To control the threshold of the device the SSR was used. The oxide was not adjusted to control the threshold voltage and this value is the same that (DASGUPTA, 2007) had used to 90 nm high performance devices.

### 3.2 NMOSFET Device Simulations

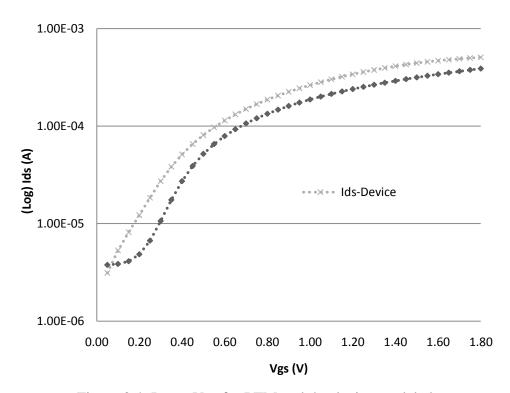

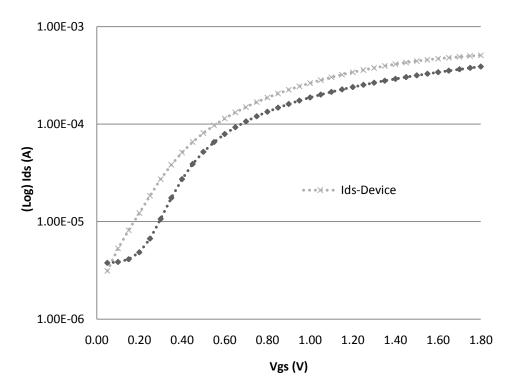

To validate the NMOS transistor modeled in Davinci, device mode simulations were conducted to analyze the behavior of the device when a bias is applied over the terminals (substrate\source\gate\drain). These simulations were done to compare the device behavior with a 90nm Predictive Technology Model (PTM) from (ZHAO, 2007) Arizona State University (ASU, 2008). The threshold voltage of the device was also compared with ST 90nm transistor model. For the simulations results presented in figure 3.4 and 3.5 the numerical method of Newton was used as recommended by Davinci Manual. For all simulations a standard temperature of T=300K was used.

In figure 3.4 and 3.5 the substrate and source are grounded ( $V_S=V_B=0V$ ). Notice that simulations of the device are done in Davinci and the spice models (PTM) are simulated in HSpice. In figure 3.4 the  $V_{GS}$  vs.  $I_{DS}$  behavior is evaluated for both devices. It is possible to verify that the PTM model and the device have similar results. The threshold of the device modeled was extracted using the "MOS PARAMETER EXTRACTION" command of Davinci and was found to be  $V_T=0.31V$ . The threshold voltage of the PTM level 54 device, is about  $V_T=0.29V$ . The documentation of the design rule kit from ST 90nm (ST, 2002) indicates a  $V_T=0.32V$ . These data confirms that the modeled device fits with the results of PTM.

Figure 3.4:  $I_{DS}$  vs  $V_{GS}$  for PTM and the device modeled

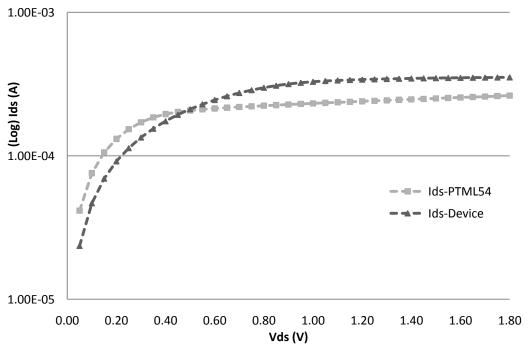

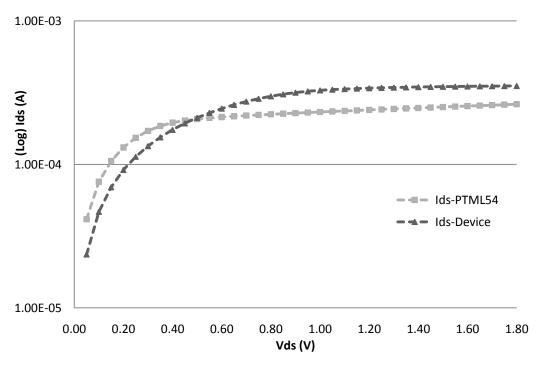

In figure 3.5 the  $I_{DS}$  vs  $V_{DS}$  behavior of both devices are evaluated. The  $V_{GS}$  is fixed on 1.2 V and the drain bias is varied. The result also shows similar results for both devices, indicating a fit for the device with the PTM.

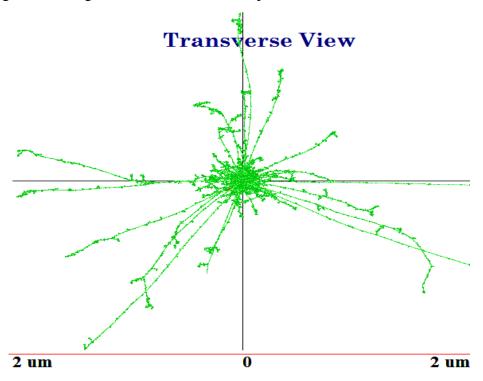

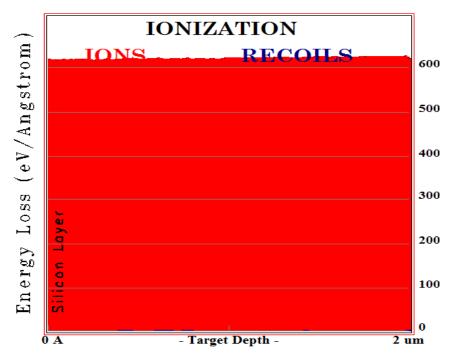

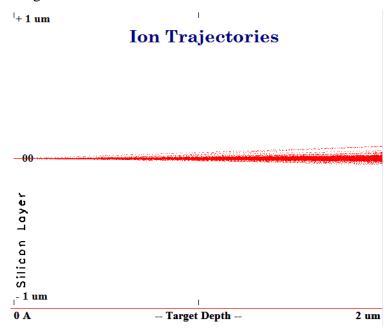

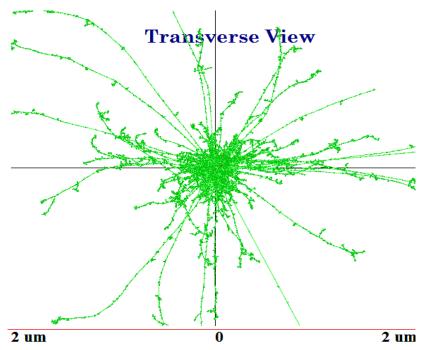

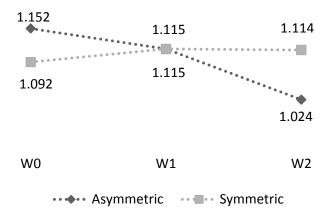

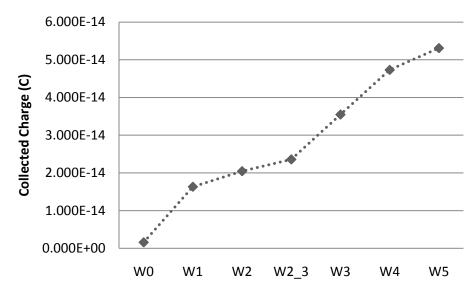

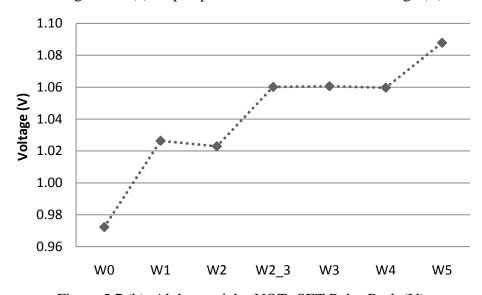

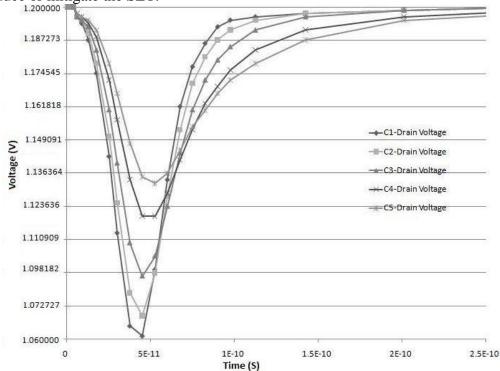

Figure 3.5:  $I_{DS}$  vs  $V_{DS}$  for PTM and the device modeled