## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

Murilo Eduardo Reinicke

# Ensaio sobre os Efeitos de Envelhecimento Acelerado Decorrentes de BTI em Circuitos Digitais

Porto Alegre 2024

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

#### Murilo Eduardo Reinicke

# Ensaio sobre os Efeitos de Envelhecimento Acelerado Decorrentes de BTI em Circuitos Digitais

Projeto de Diplomação, apresentado ao Departamento de Engenharia Elétrica da Escola de Engenharia da Universidade Federal do Rio Grande do Sul, como requisito para a obtenção do grau de Engenheiro Eletricista

#### **UFRGS**

Orientador: Prof. Dr. Tiago Roberto Balen

Coorientador: Prof. Dr. Paulo Francisco Butzen

Porto Alegre 2024

#### Murilo Eduardo Renicke

## Ensaio sobre os Efeitos de Envelhecimento Acelerado Decorrentes de BTI em Circuitos Digitais

Projeto de Diplomação, apresentado ao Departamento de Engenharia Elétrica da Escola de Engenharia da Universidade Federal do Rio Grande do Sul, como requisito para a obtenção do grau de Engenheiro Eletricista

Prof. Dr. Alexandre Balbinot

Chefe do Departamento de Engenharia Elétrica (DELET) - UFRGS

**BANCA EXAMINADORA**

**Prof. Dr. Hamilton Klimach** UFRGS

**Prof. Dr. Raphael Martins Brum** UFRGS

**Prof. Dr. Tiago Roberto Balen**Orientador - UFRGS

Aprovado em 21 de Fevereiro de 2024.

# Agradecimentos

Gostaria de agradecer ao professor Tiago Balen por me apoiar desde o início no trabalho, sempre acreditando na minha capacidade, ao professor Paulo Butzen por estar sempre de bom humor e pela motivação no momentos difíceis, conhecer vocês durante ocurso foi uma satisfação tremenda.

Agradeço à minha mãe, por sempre poder contar com seu carinho e sua ajuda (até na hora de soldar componentes). Ao meu pai por em momento algum duvidar da minha capacidade. Á minha irmã Luana pelos momentos de descontração e por lembrar que não é necessário ser sério o tempo inteiro.

Por fim, agradeço à Duda por tudo que a gente passou junto desde o início, te conhecer foi a melhor coisa que aconteceu comigo. Obrigado por me suportar nos momentos em que fui insuportável. Sempre quando estou contigo me sinto em casa e inteiro de novo, não importa o que aconteça, eu vou sempre te amar.

## Resumo

O presente trabalho teve como objetivo estudar o comportamento de FPGAs afetados por envelhecimento acelerado, mais especificamente através do fenômeno de BTI, ou Bias-Temperature Instability, que ocorre em decorrência da operação do dispositivo em ambientes de alta temperatura e com campos elétricos elevados atravessando o óxido dos transistores. Consequentemente uma variação na tensão de threshold ocorre nos transistores que compõe o componente. Foram ensaiados dois FPGAs: o Cyclone II da Altera (em uma placa de desenvolvimento DE2) e o Artix 7 da Xilinx (em uma placa de desenvolvimento ZedBoard), ambos de tecnologia CMOS, com nó tecnológico de, respectivamente, 90nm e 28nm. Os ensaios consistiram em sintetizar circuitos osciladores em anel nos dispositivos e submetê-los a uma temperatura de 135 °C em uma câmara térmica enquanto operavam, além de deixar duas placas dos mesmos modelos das ensaiadas operando em temperatura ambiente para fins de comparação. Após 150h de exposição as frequências de oscilação foram medidas e verificou-se que houve uma maior degradação na frequência do FPGA da placa ZedBoard (aproximadamente 2%) em relação a placa DE2 (aproximadamente 1%). A DE2 não apresentou muita diferença entre a placa estressada e a não estressada, já a ZedBoard sim. Também foi verificado a evolução dos dispositivos sendo deixados em relaxamento, para verificar se a degradação era recuperável. Nessas medidas foi visto que A ZedBoard recuperou aproximadamente 10% do que foi degradado, já a DE2 recuperou aproximadamente 80%.

**Palavras-chave**: Envelhecimento Acelerado, Bias-Temperature Instability, Osciladores em Anel, FPGA.

# Sumário

| 1       | INTRODUÇÃO                                     | g  |

|---------|------------------------------------------------|----|

| 2       | FUNDAMENTAÇÃO TEÓRICA E REVISÃO BIBLIOGRÁFICA  | 11 |

| 2.1     | FPGAs                                          | 11 |

| 2.2     | Oscilador em Anel                              | 13 |

| 2.3     | Efeitos de Envelhecimento                      | 14 |

| 2.3.1   | Bias-Temperature Instability                   | 15 |

| 2.3.1.1 | Mecanismos do NBTI                             | 15 |

| 2.3.1.2 | Gerando e Medindo NBTI                         | 18 |

| 3       | METODOLOGIA                                    | 21 |

| 3.1     | Dispositivos Ensaiados                         | 21 |

| 3.2     | Desenvolvimento dos Osciladores em Anel        | 22 |

| 3.2.1   | Desenvolvimento do Código para os Osciladores  | 23 |

| 3.3     | Ensaios de Envelhecimento                      | 26 |

| 4       | RESULTADOS                                     | 30 |

| 4.1     | Medidas Iniciais                               | 30 |

| 4.2     | Medidas à temperatura ambiente                 | 30 |

| 4.3     | Medidas a 135ºC                                | 33 |

| 4.4     | Comparação das Curvas Frequência X Temperatura | 35 |

| 4.5     | Medidas de relaxamento                         | 36 |

| 4.6     | Discussão                                      | 39 |

| 5       | CONCLUSÃO                                      | 40 |

|         | REFERÊNCIAS BIBLIOGRÁFICAS                     | 41 |

# Lista de Figuras

| Figura 1 – Estrutura de um FPGA. Fonte: (SATO et al., 2014)                      | 12 |

|----------------------------------------------------------------------------------|----|

| Figura 2 - Integração de linguagens que constituem o VHDL. Fonte: (WUN-          |    |

| NAVA; MONTENEGRO, 2004)                                                          | 12 |

| Figura 3 - Oscilador em Anel. Fonte: (SPARKFUN, 2023), modificado pelo autor     | 13 |

| Figura 4 – Seção da interface gate-substrato de um transistor PMOS. Fonte:       |    |

| (LORENZ, 2012)                                                                   | 16 |

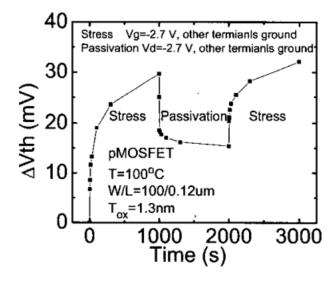

| Figura 5 – Estresse e relaxamento de um transistor. Fonte: (CHEN et al., 2003)   | 18 |

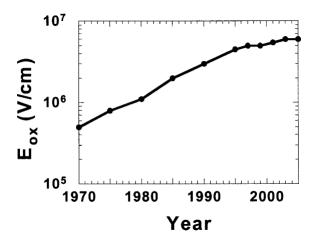

| Figura 6 - Campo elétrico no óxido em dispositivos CMOS ao longo dos anos.       |    |

| Fonte: (SCHRODER; BABCOCK, 2003)                                                 | 19 |

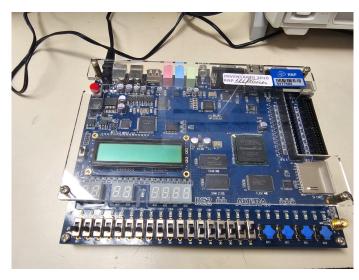

| Figura 7 - Placa DE2. Fonte: O Autor                                             | 22 |

| Figura 8 - Placa ZedBoard. Fonte: O Autor                                        | 22 |

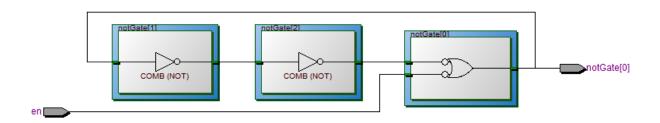

| Figura 9 - Síntese de um oscilador com três inversores no Quartus II. Fonte: O   |    |

| Autor                                                                            | 24 |

| Figura 10 – Síntese de um oscilador com três inversores gerado no Vivado. Fonte: |    |

| O Autor                                                                          | 24 |

| Figura 11 – Síntese do módulo de alto nível gerado no Quartus II. Fonte: O Autor | 25 |

| Figura 12 – Síntese do módulo de alto nível gerado no Vivado. Fonte: O Autor .   | 25 |

| Figura 13 – Câmara térmica utilizada para os ensaios. Fonte: O Autor             | 26 |

| Figura 14 – FPGAs dentro da Câmara térmica. Fonte: O Autor                       | 28 |

| Figura 15 – Osciloscópio utilizado para as medidas. Fonte: O Autor               | 28 |

| Figura 16 – Comparação das duas placas à temperatura ambiente. Fonte: O Autor    | 31 |

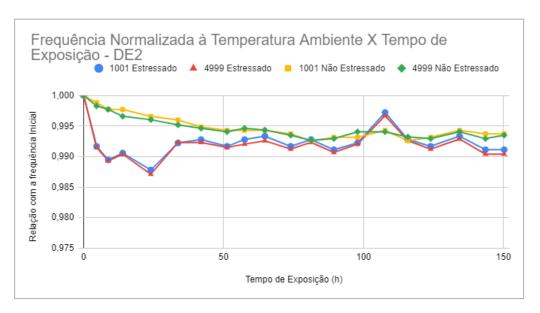

| Figura 17 – Curva das placas DE2 à temperatura ambiente. Fonte: O Autor          | 31 |

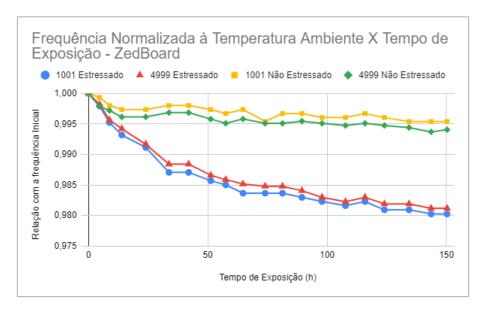

| Figura 18 – Curva das placas ZedBoard a temperatura ambiente. Fonte: O Autor     | 32 |

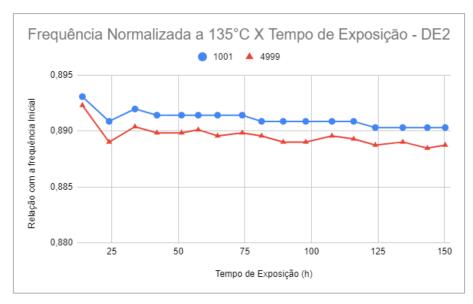

| Figura 19 – Curva da DE2 a 135ºC. Fonte: O Autor                                 | 33 |

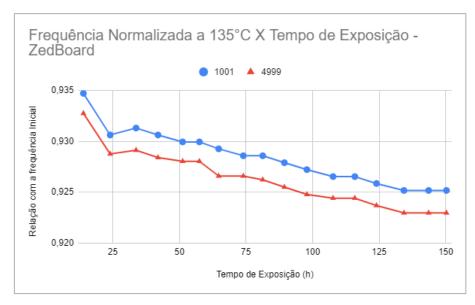

| Figura 20 – Curva da ZedBoard a 135ºC. Fonte: O Autor                            | 34 |

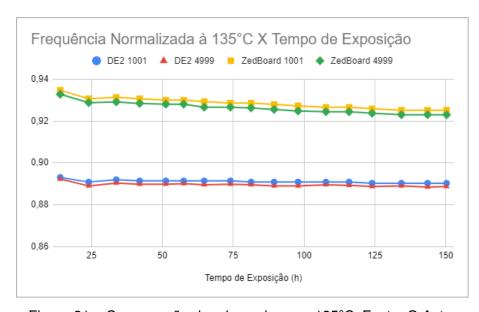

| Figura 21 – Comparação das duas placas a 135ºC. Fonte: O Autor                   | 34 |

| Figura 22 – Curva Frequência por Temperatura do oscilador com 1001 inversores    |    |

| da placa DE2. Fonte: O Autor                                                     | 35 |

| Figura 23 – Curva Frequência por Temperatura do oscilador com 1001 inversores    |    |

| da placa ZedBoard. Fonte: O Autor                                                | 36 |

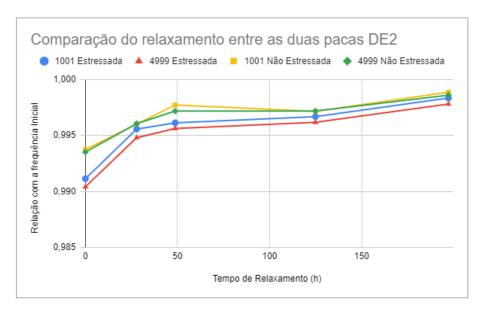

| Figura 24 – Comparação do relaxamento das duas placas. Fonte: O Autor            | 37 |

| Figura 25 – Curva de relaxamento das placas DE2. Fonte: O Autor                  | 37 |

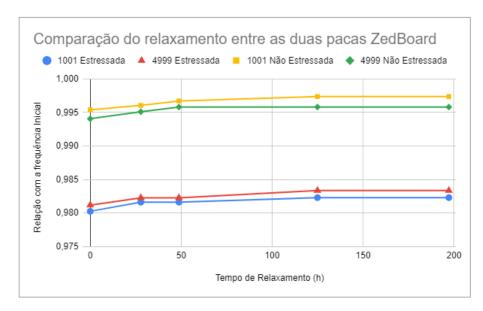

| Figura 26 – Curva de relaxamento das placas ZedBoard. Fonte: O Autor             | 38 |

# Lista de Tabelas

| Tabela 1 – Tempo de exposição por dia                                       | 27 |

|-----------------------------------------------------------------------------|----|

| Tabela 2 – Frequências iniciais dos osciladores                             | 30 |

| Tabela 3 - Frequências finais dos osciladores à temperatura ambiente        | 32 |

| Tabela 4 – Degradação na frequência dos osciladores à temperatura ambiente. | 32 |

| Tabela 5 - Frequências iniciais e finais dos osciladores a 135℃             | 34 |

| Tabela 6 – Frequência recuperada                                            | 38 |

| Tabela 7 – Porcentagem da degradação que foi recuperada                     | 38 |

## Lista de abreviaturas

BTI Bias Temperature Instability

CMOS Complementary Metal Oxide Semiconductor

EM Electromigration

FPGA Field-Programmable Gate Array

HCI Hot Carrier Injection

IDE Integrated Development Environment

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NBTI Negative Bias Temperature Instability

NMOS N-Type Metal Oxide Semiconductor

PBTI Positive Bias Temperature Instability

PMOS P-type Metal Oxide Semiconductor

RD Reaction Diffusion

TDDB Time-Dependent Dielectric Breakdown

TSP Transistor Stress Probability

# 1 Introdução

Os sistemas embarcados cumprem um papel fundamental na nossa sociedade, desempenhando funções que vão de aplicações rotineiras como computadores e aparelhos celulares a aplicações críticas como tecnologia aeroespacial e médica, os sistemas estão cada vez mais complexos.

Em aplicações críticas, a confiabilidade é essencial para garantir a segurança e a saúde das pessoas. Por exemplo, em equipamentos médicos, como monitores de sinais vitais ou respiradores mecânicos, falhas podem levar a resultados graves, e até mesmo fatais (KOÇAK *et al.*, 2021). Da mesma forma, em sistemas aeronáuticos, falhas podem resultar em acidentes com consequências desastrosas (GALLER; SLENSKI, 1991).

Com o avanço tecnológico os componentes eletrônicos estão cada vez menores, tendo sido cada vez de mais fácil acesso dispositivos cujos transistores possuem nó tecnológico na casa dos nanômetros. Esse processo é denominado miniaturização (RADAMSON *et al.*, 2019), e ele permite a criação de circuitos mais rápidos, compactos e com menor consumo energético. Porém dispositivos menores estão mais propensos a efeitos de envelhecimento que degradam parâmetros dos transistores e diminuem sua confiabilidade em sistemas críticos (LORENZ, 2012).

Entre os diversos efeitos de envelhecimento que podem afetar um transistor, um dos que tem se tornado mais crítico e alvo de extensas pesquisas é o BTI (*biastemperature instability*) (FERNÁNDEZ-GARCÍA *et al.*, 2009). Ele tem como consequência um aumento no valor absoluto da tensão de *threshold* ( $\Delta$ Vth) dos transistores do tipo p e transistores do tipo n que constituem o dispositivo (PAUL *et al.*, 2006), o que acarreta em uma menor velocidade de transição de aberto para fechado (ou de fechado para aberto) podendo depreciar a performance do sistema como um todo.

É de grande importância entender a mudança de comportamento desses sistemas para ser possível realizar projetos com maior previsibilidade e robustez, consequentemente tornando viáveis produtos mais duráveis e seguros. Existem muitos trabalhos que realizaram estudos sobre o BTI, porém não muitos utilizando dispositivos comerciais.

Um dos dispositivos comerciais mais utilizados são os FPGAs, que podem ser utilizados para os mais diversos fins pela sua natureza reconfigurável. Eles são muito afetados pelos efeitos de envelhecimento devido a serem lançados no mercado, constantemente, modelos novos e de nós tecnológicos menores (DEGALAHAL *et al.*, 2007).

Com isso, o presente trabalho tem como objetivo estudar os efeitos do envelhecimento em sistemas em chip de dois diferentes nós tecnológicos de CMOS planar, 90nm e 28nm, utilizando, respectivamente a placa DE2 da altera, que possui um FPGA da família Cyclone 2, e a placa ZedBoard da Xilinx, que possui um FPGA da família Artix 7.

Para isso foram definidos os seguintes objetivos específicos:

- Desenvolver osciladores em anel sintetizados utilizando linguagem de descrição de hardware;

- Expor os componentes a envelhecimento acelerado através de uma câmera térmica;

- Verificar a degradação da performance;

- Verificar a recuperação após o estresse térmico.

# 2 Fundamentação Teórica e Revisão Bibliográfica

Este capítulo trata das bases teóricas necessárias para este trabalho. Ele é dividido em três seções, cada um abordando um assunto considerado essencial para o entendimento do leitor.

A primeira sessão apresenta conceitos básicos sobre FPGAs, o que são, para que servem e como programá-los, com uma pequena explicação sobre as principais linguagens de descrição de hardware.

A segunda fala sobre osciladores em anel, explica seu funcionamento e mostra, com exemplos práticos, porque é uma topologia muito utilizada em ensaios de circuitos CMOS.

Já a terceira apresentar os efeitos de envelhecimento que afetam circuitos, focando no NBTI, que vem se tornando o principal componente na degradação da vida útil dos dispositivos.

#### 2.1 FPGAs

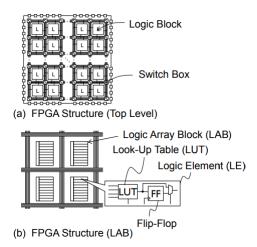

FPGA, ou *Field Programmable Gate Arrays*, são dispositivos eletrônicos que são baseados em matrizes de blocos lógicos configuráveis que são conectados via interconexões programáveis (XILINX, 2023a). Eles podem ser programados e reprogramados para as funcionalidades desejadas.

Sua utilização é necessária em aplicações onde uma implementação em *soft-ware* utilizando um microcontrolador não é capaz de cumprir os requisitos de frequência de operação (SULAIMAN *et al.*, 2009).

O que cada bloco lógico possui internamente depende da fabricante e modelo do dispositivo, mas de forma geral possuem pelo menos *Look-Up Tables* (LUTs), que são implementações em hardware de tabelas verdade e elementos de memória, como Flip-Flops (SATO *et al.*, 2014).

A Figura 1 ilustra a estrutura básica de um FPGA mostrando os blocos lógicos configuráveis, as conexões programáveis.

Figura 1 – Estrutura de um FPGA. Fonte: (SATO et al., 2014)

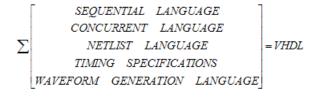

Os FPGAs são, de forma geral, programados utilizando linguagens de descrição de *hardware* (HDL), sendo VHDL e Verilog as mais utilizadas (AIN; NAGHMASH; CHYE, 2010). Essas linguagens, diferentemente de linguagens de programação convencionais onde se escreve uma série de comandos que serão executados de maneira sequencial, descrevem um circuito elétrico que será sintetizado no dispositivo.

A linguagem VHDL é pode ser utilizada para modelar sistemas digitais em diversos níveis de abstração indo do nível de algoritmo ao nível de portas lógicas. A complexidade pode variar do mais simples ao mais complexo (WUNNAVA; MONTENEGRO, 2004). A Figura 2 mostra que a linguagem VHDL também pode ser definida como uma combinação de linguagens quando consideramos o nível de abstração.

Figura 2 – Integração de linguagens que constituem o VHDL. Fonte: (WUNNAVA; MONTENE-GRO, 2004)

A linguagem Verilog permite descrever sistemas digitais desde o nível de portas lógicas ao nível de algoritmo. Também descreve um design do ponto de vista comportamental, de fluxo de dados, estrutural e de atrasos (BHASKER, 1999). Além disso, define sintaxe, semântica e estrutura para realizar simulações, facilitando os testes, em nível de simulação, antes da prototipação e possui simbologia e estrutura parecida com a linguagem C, tornando-se mais familiar para quem for utilizá-la (WUNNAVA; MONTENEGRO, 2004).

#### 2.2 Oscilador em Anel

O oscilador em anel é uma topologia de circuito muito utilizada para a caracterização de parâmetros de circuito de diversos tipos. Um dos principais motivos para isso é a capacidade de representar uma aplicação operando em alta velocidade. Segundo (BHUSHAN *et al.*, 2006) medidas feitas sob estas condições são mais próximas das aplicações reais da tecnologia do que parametrização de convencionais, o que é verdade principalmente para dispositivos CMOS de alta performance.

Eles também são utilizados como sensores de alta precisão que aumentam a confiabilidade de um chip, podendo ser usados para monitorar diversos parâmetros como variações de processo, temperatura e efeitos de envelhecimento (SATO *et al.*, 2014). Podem ser facilmente implementados e possuem um consumo de energia pequeno.

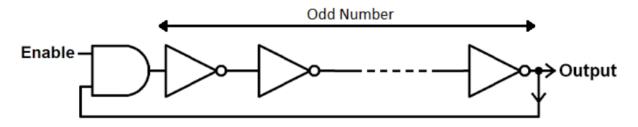

O circuito do oscilador em anel consiste em portas lógicas inversoras ligadas em sequência com uma realimentação entre a saída da última e a entrada da primeiro. É necessário que haja um número ímpar de inversores, para assim haver uma inversão periódica da entrada e da saída. O atraso de propagação de cada inversor e a realimentação gera uma onda quadrada na saída.

O período da oscilação é duas vezes o somatório do atraso de cada inversor. A Equação 1 mostra frequência de oscilação, considerando que todos os inversores têm o mesmo atraso, onde N representa o número de inversores e Ta representa o tempo de atraso de um inversor.

$$F = \frac{1}{2NTa} \tag{1}$$

A Figura 3 mostra o diagrama do oscilador em anel. O circuito em questão também possui um sinal de *enable*, que, além de servir para controlar o funcionamento do oscilador, também evita que o circuito entre em um estado de metaestabilidade e não oscile.

Figura 3 – Oscilador em Anel. Fonte: (SPARKFUN, 2023), modificado pelo autor

A frequência de um oscilador em anel pode ser utilizada pra medir indiretamente a variação na tensão de *threshold* causada pelo NBTI (as causas do NBTI serão

explicadas com maior profundidade na Seção 2.3.1). Um aumento no valor absoluto da tensão de *treshold* implica em um maior atraso para o transistor ser chaveado, já que suas capacitâncias precisam ser carregadas até um valor maior de tensão.

A Equação 2 relaciona a tensão de *threshold* com o atraso gerado em um transistor MOS (RJOUB; SHATNAWI, 2003). Onde  $V_{DD}$  é a tensão de alimentação do circuito,  $V_{th}$  é a tensão de *threshold*,  $C_L$  é a capacitância de carga e k é uma constante que depende de parâmetros construtivos.

$$Td = \frac{C_L V_{DD}}{k(V_{DD} - V_{th})^2} \tag{2}$$

O Td da Equação 2 não é equivalente ao Ta da Equação 1, pois o atraso de cada inversor dependerá de como ele é constituído. Porém se considerarmos eles proporcionais é possível unir as Equações 1 e 2 obtendo a Equação 3, onde k' é a constante proporcional entre os tempos de atraso. A Equação 3 demonstra que com um aumento do  $V_{th}$  há uma diminuição da frequência.

$$F = \frac{kk'(V_{DD} - V_{th})^2}{2NC_L V_{DD}} \tag{3}$$

Uma quantidade na casa das centenas de inversores no circuito reduzirá as variações aleatórias intrínsecas de cada MOSFET que poderiam aparecer caso fossem medidos individualmente, permitindo uma caracterização mais confiável e robusta.

O trabalho de (BHUSHAN *et al.*, 2006) descreve estratégias de design para estruturas de osciladores em anel e também apresenta o uso dessas estruturas para mensurar consumo de energia e outros parâmetros de MOSFETs.

Um outro trabalho, (MICHAL, 2012) realizou estudos para reduzir o consumo de energia de osciladores em anel, conseguindo isso reduzindo o número de inversores, mas acoplando capacitores a cada um deles para aumentar o atraso.

### 2.3 Efeitos de Envelhecimento

Os efeitos que causam envelhecimentos em circuitos podem ser divididos em dois grupos, os que causam falhas abruptas e os que causam deriva de parâmetros ao longo do tempo. Os principais exemplos do primeiro grupo são os TDDB (*time-dependent dielectric breakdown*) e EM (*electromigration*) (LORENZ, 2012). Já, para o segundo grupo, se tem o NBTI (*negative bias temperature instability*) e o HCI (*hot carrier injection*) (LORENZ, 2012).

Os efeitos do primeiro grupo devem ser tratados estocasticamente, já os do segundo grupo podem ser tratados deterministicamente (LORENZ, 2012).

Este trabalho tem como foco os efeitos de envelhecimento de longo prazo, portanto não será tratado sobre os efeitos que causam falhas abruptas.

#### 2.3.1 Bias-Temperature Instability

A variação da tensão de *threshold* ( $\Delta V$ th) dos transistores tipo p e tipo n é a principal característica a ser levada em conta ao analisar o envelhecimento acelerado de tecnologias CMOS. Essa variação acarreta em uma menor velocidade de chaveamento dos transistores.

Uma das principais causas da variação da tensão de *threshold* é o fenômeno Bias-Temperature Instability (BTI), mais especificamente o Negative BTI (NBTI) afetando os transistores do tipo p e o Positive BTI (PBTI) afetando os transistores do tipo n.

O NBTI vem sendo estudado desde a década de 60 (ALAM *et al.*, 2007), mas com dispositivos CMOS de nós tecnológicos cada vez menores, esse fenômeno se torna um dos principais fatores que determinam a longevidade de transistores PMOS, diferentemente de transistores NMOS, que o principal fator é o HCI (BHARDWAJ *et al.*, 2016).

A miniaturização dos transistores aumenta o impacto desse efeito (SILVA, 2012), devido a campos elétricos maiores devido a óxidos mais finos, temperaturas maiores causadas pelo aumento na densidade de transistores e o uso de dielétricos *high-k*, que estão mais propensos a apresentar falhas.

Transistores PMOS possuem uma tensão de *threshold* negativa. O NBTI diminui a tensão de *threshold* dos transistores PMOS, portanto, aumenta o valor absoluto dela, tornando-o ainda mais negativo.

#### 2.3.1.1 Mecanismos do NBTI

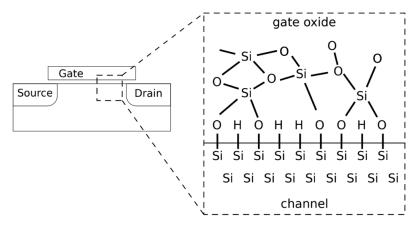

O NBTI não pode ser explicado por um único mecanismo físico, mas por uma superposição de diversos processos (BUTZEN, 2012). Dois desses fenômenos são os mais aceitos, sendo eles: a geração de armadilhas na interface, o aprisionamento de lacunas.

O primeiro pode ser explicado pelo modelo de Reação-Difusão (RD), que diz que o NBTI é causado por ligações Si-H quebradas na interface entre o substrato e o óxido do gate. Essas ligações Si-H são formadas na fabricação dos dispositivos para impedir que os átomos de silício fiquem com a valência incompleta após a colocação da camada de óxido de silício (SiO2) sobre o substrato. As ligações pendentes são denominadas estados de interface e podem voltar a ocorrer devido a campos elétricos elevados e alta temperatura (SILVA, 2012).

A Figura 4 mostra as ligações Si-H na interface entre o gate e o substrato de um transistor PMOS.

Figura 4 – Seção da interface gate-substrato de um transistor PMOS. Fonte: (LORENZ, 2012)

Os estados de interface resultante deterioram parâmetros do transistor. Isso pode ser modelado pelo sistema RD, composto de dois processos: uma reação local e uma difusão dos produtos da reação.

A taxa de geração dessas interfaces é dada pela Equação 4 (LORENZ, 2012).

$$\frac{\mathrm{d}N_{\mathsf{i}}t}{\mathrm{d}t} = KF(N_0 - N_{it}) - K_R N_H(0) N_{it} \tag{4}$$

O primeiro termo do lado direito da equação mostra a componente de geração dos estados de interface, já o segundo termo descreve a regeneração das ligações, também denominada *annealing* reverso, uma característica especial do NBTI.

$N_0$  representa a quantidade inicial de ligações Si-H,  $N_{it}$  representa o número de estados de interface e  $K_R$  é a taxa constante de criação de ligações quebradas. No termo de recuperação  $N_{H(0)}$  representa o número de átomos de hidrogênio na interface do silício com o óxido,  $K_R$  é a taxa constante de *annealing* reverso das ligações incompletas e átomos de hidrogênio em ligações Si-H.

O lado direito da equação mostra que os estados de interface voltam a diminuir quando a condição de estresse, causada pela alta temperatura e o campo elétrico, é removida.

A criação de estados de interface é limitado pela difusão dos átomos de hidrogênio, como mostrado na Equação 5.

$$\frac{\mathrm{d}N_{it}}{\mathrm{d}t} = -DH\frac{\mathrm{d}N_H}{\mathrm{d}x} + N_{H\mu H}E_{ox} \tag{5}$$

Onde  $D_H$  representa o coeficiente de difusão,  $\mu_H$  representa a mobilidade dos átomos de hidrogênio e  $E_{ox}$  representa o campo elétrico que atravessa o óxido.

O segundo termo pode ser negligenciado para átomos ou moléculas eletricamente neutros (LORENZ, 2012).  $K_F$ ,  $K_R$  e  $D_H$  dependem da temperatura.  $K_F$  também depende do

campo elétrico aplicado. Isso demonstra que as interfaces só são geradas quando um campo elétrico é aplicado, o que não é necessário para o *annealing* e para a difusão.

As Equações 4 e 5 formam um sistema que pode ser resolvido caso seja considerado que  $N_{it}$  é muito menor que  $N_0$ . A Equação 6 mostra a solução desse sistema e a dependência da quantidade de interfaces com relação o tempo.

$$N_{it} = \sqrt{\frac{K_F N_0}{2K_R}} (D_H t)^n \tag{6}$$

Onde n representa a constante exponencial de difusão e é sempre menor que 1, de forma que a geração das interfaces irá desacelerar com o tempo.

A variação Vth será proporcional ao  $N_{\rm it}$ , de forma que poderá ser escrito como mostrado na Equação 7, onde  $\Phi s$  é o potencial de superfície e Cox é a capacitância do óxido.

$$V_{th} \propto -\frac{qN_{it}(\Phi S)}{C_{ox}} \tag{7}$$

Porém, esse fenômeno não explica completamente o fenômeno, não descrevendo corretamente a recuperação rápida que ocorre quando as condições de estresse não estão mais presentes (WIRTH; SILVA; KACZER, 2011).

Um segundo mecanismo relacionado, denominado *Trapping/Detrapping*, é baseado no aprisionamento de lacunas em defeitos no óxido preexistentes ou provenientes de estresse elétrico (BUTZEN, 2012). O campo elétrico que é gerado no gate quando o PMOS está negativamente polarizado causa o tunelamento de portadores do canal, levando-as diretamente até nas falhas no óxido. Esse fenômeno vem sendo cada vez mais relevante na degradação por NBTI, considerando que falhas no óxido são mais comuns em transistores *high-k*.

Cada armadilha apresenta como característica a probabilidade de capturar e liberar um portador e o valor do impacto na tensão de *threshold* será gerado em caso de captura. As probabilidades tem relação com os tempos médios entre as capturas e emissões, já o impacto na tensão de *threshold* tem relação com a localização em que a armadilha está localizada, podendo ser muito relevante caso obstrua o caminho de percolação do canal.

Caminhos de percolação são os caminhos de condução que se formam em transistores nanométricos nos lugares onde há a falta de átomos dopantes, pois estes formam barreiras onde a energia de condução é maior, bloqueando os portadores (ASHRAF *et al.*, 2011).

Esses dois mecanismos podem ser considerados simultaneamente, sendo o primeiro responsável por uma componente permanente da degradação e o segundo responsável por uma componente recuperável da degradação (SILVA, 2012).

Cada um desses fenômenos contribui para a variação da tensão de threshold resultando na Equação 8. Onde  $\Delta V_{IT}$  é a contribuição das armadilhas na interface (primeiro mecanismo),  $\Delta V_{HT}$  é a contribuição do aprisionamento em defeitos pré existentes e  $\Delta V_{OT}$  é a contribuição do aprisionamento em defeitos gerados eletricamente (segundo mecanismo).

$$\Delta V_{th} = \Delta V_{IT} + \Delta V_{HT} + \Delta V_{OT} \tag{8}$$

A Equação 9 mostra uma aproximação da variação da tensão de threshold ao longo do tempo considerando um nó tecnológico específico e um certo conjunto de condições ambientais (BUTZEN, 2012).

$$\Delta Vth = A(TSP.t)^n \tag{9}$$

Onde A é uma constante que depende da tecnologia, t é o tempo, n é a constante exponencial do NBTI e TSP é a probabilidade do transistor estar negativamente polarizado.

O *TSP* de um transistor pode depender não só de seu duty cicle, mas também de sua posição na topologia do circuito. Por exemplo, no caso de dois transistores que compõe a malha de pull-up de uma porta NOR, o TSP do transistor superior depende apenas de seu sinal de entrada, já o TSP do inferior depende da combinação de seu sinal de entrada e do sinal de entrada do transistor superior, de forma que o transistor superior terá uma tendência maior a sofrer envelhecimento.

Quando não há campo elétrico atravessando o óxido do transistor, o que no caso dos PMOS ocorre quando a tensão de gate é positiva, há a recuperação das armadilhas de interface (CHEN *et al.*, 2003). Ou seja, em um circuito em que um transistor alterna entre fechado e aberto, haverá uma certa recuperação da degradação quando o transistor estiver fechado. A Figura 5 exemplifica esse comportamento de estresse e relaxamento em um transistor.

Figura 5 – Estresse e relaxamento de um transistor. Fonte: (CHEN et al., 2003)

#### 2.3.1.2 Gerando e Medindo NBTI

Muitos estudos já foram realizados para determinar em que condições o NBTI ocorre com mais facilidade em circuitos CMOS.

O fenômeno NBTI normalmente ocorre em transistores do tipo p operando com tensão de gate negativa em temperaturas variando de 100°C a 250°C (DAVIDOVIĆ *et al.*, 2021). Os campos elétricos devem ser na faixa dos 6MV/cm, valores encontrados durante o *burn-in* do componente, porém com transistores cada vez menores, esses campos podem ocorrer durante a operação normal de dispositivos de alta performance (SCHRODER; BABCOCK, 2003). A Figura 6 mostra o aumento do campo elétrico que atravessa o óxido em transistores CMOS ao longo dos anos.

Figura 6 – Campo elétrico no óxido em dispositivos CMOS ao longo dos anos. Fonte: (SCHRO-DER; BABCOCK, 2003)

Para aplicar o efeito de NBTI no dispositivo ensaiado no trabalho (DAVIDOVIĆ *et al.*, 2021), os pesquisadores o estressaram por 2000 horas, aplicando tensões negativas de 30 a 45V no gate (com fonte e dreno aterrados) em uma temperatura de variando de 125 a 175ºC.

O trabalho de (BHARDWAJ *et al.*, 2016) desenvolveu um modelo preditivo para NBTI em dispositivos CMOS de nó tecnológico de 45nm, que alcançou estimativas precisas da degradação em longo prazo da tensão de *threshold* de transistores PMOS devido ao fenômeno.

Um outro trabalho (GROSSI; OMAÑA, 2021), realizou simulações para analisar os efeitos do BTI em amplificadores operacionais, e viu que o ganho DC, a frequência de corte e o *slew rate* são significativamente degradados em AMPOPs operando em malha aberta. Já para Ampops operando com realimentação negativa apenas a frequência de corte mostrou uma degradação significativa.

Alguns trabalhos, inclusive, realizaram estudos dos efeitos de NBTI em osciladores em anel. Um deles (LORENZ, 2012) mostra uma degradação de 5% com 144 horas de exposição à 125 °C. Já outro (SATO *et al.*, 2014), que estudou métodos para diminuir o efeito de NBTI em osciladores em anel, resultou uma degradação de 0,25%, com 42 horas de exposição, porém à apenas 85 °C. Um terceiro trabalho (LINDER *et al.*, 2011) propõe topologias de osciladores em anel que permitem estudar em separado os efeitos do PBTI, nele foi medida um degradação de 1,8% considerando apenas o PBTI, 2,2% considerando apenas o NBTI e 3,9% considerando apenas os dois efeitos combinados tendo sido realizado um estresse de 2 horas e 47 minutos (10000 segundos) segundos à 125 °C.

Esses três trabalhos avaliaram a degradação causada pelo NBTI através da diminuição da frequência de osciladores em anel. Isso é viável, pois a variação da tensão de *threshold* causada pelo NBTI aumentará o tempo de propagação dos transistores dos circuitos, aumentando o período de oscilação.

# 3 Metodologia

Neste capítulo são descritos os procedimentos utilizados para verificar os efeitos de envelhecimento acelerado nos FPGAs de interesse. Ele será composto por três seções.

A primeira apresenta os FPGAs escolhidos para serem estudados, além dos motivos para essa escolha e de características desses dispositivos.

A segunda descreve como os osciladores em anel foram projetados, programados e sintetizados nos FPGAs, além de detalhar sobre as decisões tomadas com relação a topologia e número de inversores dos osciladores.

Por fim, a terceira detalha os ensaios realizados utilizando a câmara térmica para estressar os dispositivos e envelhecê-los, bem como as análises e comparações realizadas para alcançar os resultados.

### 3.1 Dispositivos Ensaiados

Foram utilizadas as placas de desenvolvimento DE2 e ZedBoard. Elas foram escolhidas considerando suas disponibilidades no laboratório e por serem de fabricantes diferentes e possuírem nós tecnológicos diferentes.

A DE2 possui o FPGA EP2C35F672C6N da família o Cyclone II da fabricante Altera, pertencente a Intel, que possui um nó tecnológico de 90nm. A ZedBoard possui o SoC Zynq-7000, da Xilinx, agora pertencente a AMD, que contém um processardor ARM Cortex-A9 de dois núcleos e um FPGA Artix 7 de nó tecnológico de 28nm (XILINX, 2023b).

Ambas as placas possuem, além dos FPGAs, componentes e periféricos necessários para testes e prototipação de sistemas, como: botões, chaves, LEDs, display, memória flash e diversas entradas e saídas.

As Figuras 7 e 8 mostram, respectivamente, a placa de desenvolvimento DE2 e ZedBoard utilizadas.

Figura 7 - Placa DE2. Fonte: O Autor

Figura 8 – Placa ZedBoard. Fonte: O Autor

#### 3.2 Desenvolvimento dos Osciladores em Anel

A topologia de oscilador em anel foi escolhida para os testes por sua disseminada utilização na caracterização de dispositivos MOSFET. Seu uso é amplo, pois medidas utilizando esse circuito se aproximam muito mais de aplicações reais do que medições paramétricas DC padrões.

Foram realizados testes preliminares com diferentes quantidades de inversores para encontrar uma quantidade apropriada, pois, com poucos osciladores a capacitância de saída afeta demais o sinal, o que faz com que ele não seja mais uma onda quadrada e com muitos osciladores o limite de iterações em um bloco 'for' que as IDEs permitem era atingido.

Considerando isso, foi decidido que em cada um dos dispositivos seria sintetizado dois osciladores, um com 1001 inversores, pois foi o valor em que se considerou que a onda poderia ser considerada quadrada, e outro com 4999, por ser o maior valor ímpar permitido pela IDE

Quartus II. A escolha de utilizar dois osciladores em cada FPGA foi tomada por dois motivos: para se ter certeza que as IDEs não estavam simplificando os estágios inversores do circuito sintetizado e para verificar que o envelhecimento afeta igualmente diferentes partes do FPGA.

A grande quantidade de inversores é relevante, pois assim as pequenas variações aleatórias nas características de cada transistor que compõe os dispositivos tenderão a se diluir.

#### 3.2.1 Desenvolvimento do Código para os Osciladores

Para desenvolver e sintetizar os osciladores em anel foi utilizada a linguagem de descrição Verilog. Para o Cyclone II foi utilizada a IDE Quartus II versão 12.1, já para o ZedBoard foi utilizada a IDE Vivado versão 2023.1.

O Quadro 3.1 mostra o código desenvolvido em Verilog para o módulo que implementa o oscilador em anel com N inversores, sendo N igual a 5 caso nenhum valor seja definido durante a instanciação do módulo. O mesmo código foi utilizado para os dois FPGAs nas duas IDEs diferentes.

```

1 module RingOscillator

\#(parameter N = 5)

3

4

input en,

5

/*synthesis keep*/

output reg and_1

6

7

reg [N - 1:0] notGate /*synthesis keep*/;

8

integer i;

9

generate

always @ (*) begin

10

and_1 <= en & notGate[N - 1];

11

12

notGate[0] <= ~and_1;</pre>

for (i = 1; i < N; i = i + 1) begin: inverter_chain</pre>

13

notGate[i] <= ~notGate[i - 1];</pre>

14

15

end

16

end

17

endgenerate

18 endmodule

```

Quadro 3.1 – Módulo do Oscilador em Anel. Fonte: O Autor

O módulo possui uma entrada en, responsável por habilitar o circuito, uma saída and\_1 que é a saída da porta and do circuito, de onde o sinal do oscilador é obtido. O valor N é parametrizável, o que permite a reutilização do mesmo código para osciladores com diferentes números de inversores.

São então instanciadas N variáveis, que serão utilizados para criar os inversores. A variável and\_1 recebe o resultado da operação E lógica do sinal de *enable* e a saída do último inversor. O primeiro inversor é definido como a variável and\_1 invertido.

Um bloco 'for' é utilizado para automatizar as atribuições dos inversores seguintes, sendo a cada um atribuído o valor inversor anterior negado.

Um ponto importante de destacar é a necessidade de utilizar diretivas de compilação para impedir que os inversores sejam simplificados na síntese. Essas diretivas são diferentes em cada uma das IDEs, na Quartus II é utilizado a diretiva /\* synthesis keep \*/ e na Vivado é utilizado a diretiva /\* synthesis syn\_keep=1 \*/.

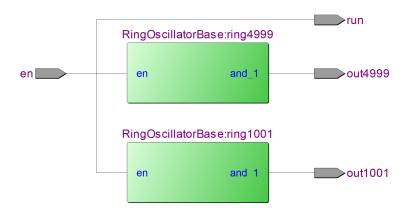

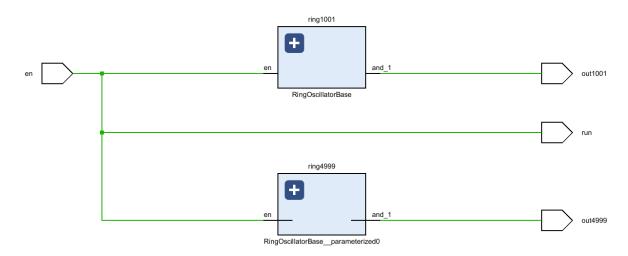

Nas Figuras 9 e 10 pode ser visto como, respectivamente, o Quartus II e o Vivado implementam em hardware o código do quadro 3.1 para um N igual a 3. É importante destacar que, por mais que para o Quartus II sejam utilizados portas lógicas para ilustrar o circuito, essas portas lógicas são construídas, na verdade, com LUTs que implementam o seu comportamento.

Figura 9 – Síntese de um oscilador com três inversores no Quartus II. Fonte: O Autor

Figura 10 – Síntese de um oscilador com três inversores gerado no Vivado. Fonte: O Autor

O Quadro 3.2 mostra o módulo de alto nível em que é instanciado dois osciladores em anel, um com 1001 e outro de 4999 inversores.

```

1 module TopLevel

2

3

input en,

4

output run,

5

output out1001, out4999

6

7

8

assign run = en;

9

RingOscillator #(.N(1001)) ring1001(en, out1001);

10

11

RingOscillator #(.N(4999)) ring4999(en, out4999);

12 endmodule

```

Quadro 3.2 – Instanciação dos Módulos. Fonte: O Autor

O módulo possui uma entrada 'en', responsável por habilitar o circuito, uma saída 'run', usada para indicar que o circuito está em funcionamento e as saídas dos dois osciladores

'out1001', 'out4999'. Também são declaradas duas instâncias do módulo desenvolvido no Quadro 3.1.

As Figuras 11 e 12 mostram, respectivamente, o circuito implementado pelo software Quartus II e Vivado para o módulo de alto nível que serão utilizado nos FPGAs.

Figura 11 – Síntese do módulo de alto nível gerado no Quartus II. Fonte: O Autor

Figura 12 – Síntese do módulo de alto nível gerado no Vivado. Fonte: O Autor

Nas duas placas a entrada 'en' foi atribuída a um pino do FPGA ligado a uma chave, a saída 'run' foi atribuída a um pino do FPGA ligado a um LED e as saídas 'out1001' e out4999 foram atribuídas a pinos do FPGA ligados a conectores de entrada e saída de uso geral.

Em ambas as sínteses foram utilizadas 6000 elementos lógicos, quantidade condizente com inversores presentes em cada um dos dois osciladores. Isso mostra que a única simplificação que ocorreu foi a operação lógica E ter sido integrada ao primeiro inversor da corrente.

Após o desenvolvimento, o circuito sintetizado foi simulado utilizando a ferramenta apropriada para cada um dos componentes. Constatada a validade da solução ela foi transferida

para os FPGAs reais e será medida, através de um osciloscópio, a frequência de oscilação das saídas do circuitos.

#### 3.3 Ensaios de Envelhecimento

Para induzir o fenômeno de BTI nos dispositivos foi utilizada uma câmara térmica para ensaios com componenentes eletrônicos. Inicialmente a temperatura de exposição foi de 100 ℃, temperatura que é inferior a faixa de ocorrência do BTI, mas que foi utilizada para verificar se os componentes não iriam ser danificados com a temperatura.

A Figura 14 mostra a câmera térmica utilizada para os ensaios. Ele foi fabricado pela SPX *Thermal Product Solutions* sendo capaz de alcançar temperaturas de -75°C a 200°C.

Figura 13 – Câmara térmica utilizada para os ensaios. Fonte: O Autor

Constatando que não houve problema à 100°C, a temperatura foi aumentada para 125 °C. Como também não houve danos, a temperatura foi, então, elevada para 135 °C.

Nessa temperatura foi observado que o conector de alimentação da placa DE2 apresentava sinais de derretimento, por isso, a temperatura dos ensaios foi definida em 135 °C.

Temperatura que está dentro da faixa de 125 e 175ºC que a bibliografia indica como sendo a faixa em que o BTI ocorre mais facilmente.

O tempo total de estresse térmico foi de 150h, tempo definido levando-se em conta o que foi estudado na seção 2.3.1.2. A contagem do tempo era iniciada quando a câmara térmica era ligada e paralisada quando desligada.

O tempo que os dispositivos foram expostas ao calor não foi contínua, devido a impossibilidade de ficar durante a noite no laboratório e, por motivos de segurança, de deixar a câmara térmica ligada sem supervisão. Portanto os dispositivos, de forma geral, foram expostos à câmara térmica durante o dia e retirados dela durante a noite, ficando ligados o tempo todo, de forma que não houvesse relaxamento.

As 150h de exposição foram divididas ao longo de 19 dias, não sendo necessariamente dias seguidos. A Tabela 1 mostra quanto tempo as placas foram expostas em cada dia em que foi realizado ensaio.

| Dia        | Tempo de Exposição (h) | Tempo Total Acumulado (h) |

|------------|------------------------|---------------------------|

| 18/10/23   | 4,63                   | 0,00                      |

| 19/10/23   | 4,17                   | 4,63                      |

| 20/10/2023 | 5,17                   | 8,80                      |

| 23/10/2023 | 10,05                  | 13,97                     |

| 24/10/2023 | 9,72                   | 24,02                     |

| 25/10/2023 | 8,25                   | 33,73                     |

| 30/10/2023 | 9,25                   | 41,98                     |

| 01/11/2023 | 6,28                   | 51,23                     |

| 03/11/2023 | 7,25                   | 57,52                     |

| 08/11/2023 | 9,25                   | 64,77                     |

| 10/11/2023 | 7,28                   | 74,02                     |

| 16/11/2023 | 8,13                   | 81,30                     |

| 17/11/2023 | 8,45                   | 89,43                     |

| 22/10/2023 | 9,83                   | 97,88                     |

| 23/11/2023 | 8,17                   | 107,72                    |

| 29/11/2023 | 8,13                   | 115,88                    |

| 30/11/2023 | 10,32                  | 124,02                    |

| 11/12/2023 | 9,25                   | 134,33                    |

| 12/12/2023 | 6,70                   | 143,58                    |

| 13/12/2023 | 1,73                   | 150,28                    |

Tabela 1 – Tempo de exposição por dia

Outras duas placas, dos mesmo modelos das ensaiadas, foram deixadas fora da câmara térmica pelo mesmo tempo, sempre ligadas e com os mesmos osciladores em anel sintetizados. Comparar as medidas entre as placas que foram aquecidas com as que não foram é importante para verificar que se a degradação na frequência é proveniente do estresse térmico ou se é apenas resultado do funcionamento prolongado.

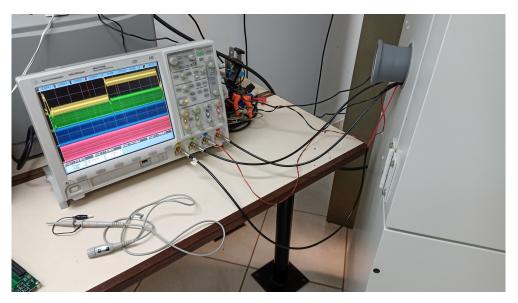

A câmara térmica permite realizar medidas nos dispositivos ensaiados enquanto eles estão dentro dela. Portanto foi possível medir a frequência dos osciladores em anel durante o processo de estresse térmico. As Figuras 14 e 15 mostram o *setup* experimental construído, com os FPGAs ensaiados dentro da câmera térmica com os cabos de medição saindo da câmera e ligadas ao osciloscópio.

Figura 14 – FPGAs dentro da Câmara térmica. Fonte: O Autor

Figura 15 – Osciloscópio utilizado para as medidas. Fonte: O Autor

Enquanto a câmara aquecia da temperatura ambiente para a temperatura alvo, as medições foram mais frequentes, mantendo-se, no máximo um período de cinco minutos entre as medidas. Quando a temperatura alvo é atingida as medidas ficam mais esparsas, considerando que há menos variação na frequência medida.

É importante separar os efeitos instantâneos da temperatura na frequência dos osciladores do efeito a longo prazo do BTI. Por isso é necessário comparar as medidas feitas em

uma mesma temperatura. O momento que a temperatura é a mais estável é quando a câmara já chegou aos 135 ℃.

Com as medidas ao longo do aquecimento da câmara é possível construir curvas de frequência por temperatura e compará-las para diferentes ciclos. Como em cada ciclo os dispositivos estão há um determinado tempo sofrendo estresse, será possível analisar o deslocamento dessa curva, se houver, com o passar do tempo.

Comparando essas medidas em relação ao tempo total estressado será possível constatar se houve ou não uma degradação na frequência de funcionamento dos dispositivos, e se houve uma diferença significativa na degradação entre as duas placas.

Após os ensaios de envelhecimento foi realizado um ensaio para medir a recuperação dos circuitos, para verificar quanto da degradação sofrida é reversível. Para isso as quatro placas foram desligadas (exceto quando as medidas eram realizadas) e deixadas em temperatura ambiente. Medidas ao longo do tempo foram realizadas até o tempo de relaxamento totalizar o tempo total que as placas foram estressadas.

### 4 Resultados

Este capítulo mostra os resultados obtidos através dos dados colhidos durante os ensaios de envelhecimento detalhados na seção 3.3. São apresentados os valores iniciais e finais das frequências dos osciladores, as curvas de como as frequências variaram com o tempo de exposição ao calor, as curvas frequência por temperatura para diferentes tempos de exposição e as curvas das medidas durante o relaxamento dos dispositivos.

#### 4.1 Medidas Iniciais

As primeiras medidas foram realizadas em temperatura ambiente antes dos ensaios iniciarem, para se ter as frequências iniciais dos osciladores. A Tabela 2 mostra esses valores os dois osciladores de cada placa. Esses valores serão utilizados como valor unitário quando os valores das frequências medidas estiverem normalizado.

Tabela 2 – Frequências iniciais dos osciladores.

|                 | Frequência (kHz) |       |      |       |

|-----------------|------------------|-------|------|-------|

|                 | Altera DE2 Z     |       | ZedE | Board |

|                 | 1001 4999 1001 4 |       | 4999 |       |

| Estressados     | 1805             | 364,9 | 1470 | 276,5 |

| Não Estressados | 1756             | 354,5 | 1520 | 286   |

A frequência dos osciladores da placa ZedBoard foram menores que os da placa DE2, mesmo o nó tecnológico dela sendo menor. Isso pode ser devido ao fato das LUTs que constituem o circuito sintetizado na ZedBoard serem mais complexos que os presentes na DE2.

### 4.2 Medidas à temperatura ambiente

As medidas em temperatura ambiente foram realizadas no início de cada um dos ciclos de estresse (como indicado na Tabela 1) antes de ligar a câmara térmica. As medidas apresentam uma certa oscilação devido a variabilidade da temperatura ambiente.

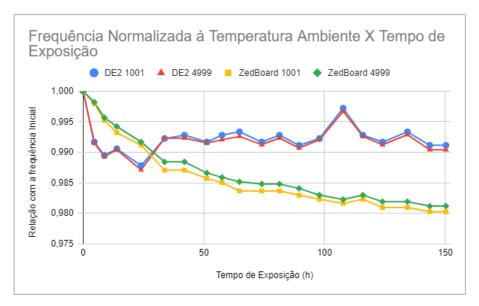

As curvas da Figura 16 mostram as frequências normalizadas dos osciladores das placas que foram estressadas em relação ao tempo de exposição. Nas curvas da placa DE2 é possível ver uma diminuição da frequência no início dos ensaios seguido de uma estabilidade. Já as curvas da placa ZedBoard apresentam uma degradação maior e ao longo de todas as medidas. O formato das curvas é o esperado segundo a Equação 9 que indica uma degradação que desacelera com o tempo devido a uma saturação do efeito do NBTI.

Figura 16 – Comparação das duas placas à temperatura ambiente. Fonte: O Autor

A Figura 17 mostra as curvas das frequências normalizadas dos osciladores das placas DE2, tanto a que foi estressada termicamente quanto a que não foi estressada, em relação ao tempo de exposição.

É possível observar que a placa que não foi estressada apresenta uma curva semelhante à que foi estressada, o que pode indicar que o FPGA da DE2 não sofreu do NBTI e que a degradação é apenas decorrente do uso prolongado da placa ou que a temperatura não foi um fator tão relevante para o fenômeno, tendo sido, ambas as placas, afetados por ele da mesma forma.

Figura 17 – Curva das placas DE2 à temperatura ambiente. Fonte: O Autor

As mesmas curvas são mostradas na Figura 18, porém para as placas ZedBoard. Diferentemente da DE2, para a ZedBoard o comportamento entre a placa que foi estressada e

a que não foi apresentaram uma diferença considerável, ambas possuem o mesmo formato porém a estressada demonstra uma queda maior na frequência.

Figura 18 – Curva das placas ZedBoard a temperatura ambiente. Fonte: O Autor

A Tabela 3 mostra os valores finais das frequências de cada um dos osciladores. Já a Tabela 4 mostra a porcentagem da degradação das frequências em relação às frequências iniciais, valor encontrado através da Equação 10 onde D é a degradação,  $F_i$  é a frequência inicial e  $F_f$  é a frequência final.

Tabela 3 – Frequências finais dos osciladores à temperatura ambiente.

|                 | Frequência (kHz)   |       |      |       |

|-----------------|--------------------|-------|------|-------|

|                 | Altera DE2         |       | ZedE | Board |

|                 | 1001   4999   1001 |       | 4999 |       |

| Estressados     | 1789               | 361,4 | 1441 | 271,3 |

| Não Estressados | 1745               | 352,2 | 1513 | 284,3 |

Tabela 4 – Degradação na frequência dos osciladores à temperatura ambiente.

|                 | Degradação (%)           |      |      |       |

|-----------------|--------------------------|------|------|-------|

|                 | Altera DE2 ZedBoard      |      |      | Board |

|                 | 1001   4999   1001   499 |      |      | 4999  |

| Estressados     | 0,89                     | 0,96 | 1,97 | 1,88  |

| Não Estressados | 0,63                     | 0,65 | 0,46 | 0,59  |

$$D = \frac{F_i - F_f}{F_i} X 100\% \tag{10}$$

Na Tabela 4 é confirmado o que foi visto na Figura 16 de que a ZedBoard apresentou uma degradação maior que a DE2. Além disso, nela também é visível que a diferença entre o

dispositivo estressado e o não estressado é consideravelmente maior no caso da ZedBoard do que no caso da DE2, corroborando com o mostrado nas Figuras 17 e 18.

Um fato que ficou evidente aqui e se repetirá nas seções seguintes é que o comportamento dos osciladores de uma mesma placa, de 1001 e de 4999 inversores, foi semelhante.

Um problema encontrado nestas medidas foi, justamente, a variabilidade da temperatura ambiente, que, por ter influência no valor da frequência, causou um certo ruído nas medidas, principalmente nas da DE2 que foi estressada.

#### 4.3 Medidas a 135°C

Considerando o problema com a variabilidade da temperatura ambiente também foram realizadas medidas na temperatura de 135 °C, por ser a temperatura que a câmara térmica estabilizava. As medidas eram feitas pelo menos 30 minutos após a temperatura alvo ter sido atingida para se obter um valor mais consolidado.

As medidas nessa temperatura só começaram a ser feitas a partir de 14 horas de exposição, pelo fato de nos primeiros ciclos ter sido usado temperaturas mais baixas para verificar se haveriam danos críticos aos dispositivos, como descrito na Seção 3.3.

A Figura 19 mostra as curvas das frequências normalizadas dos osciladores das placas DE2 que foi estressada termicamente em relação ao tempo de exposição. Nela é visto que a degradação continuou, mesmo que pequena, até o fim dos ensaios, o que não podia ser observado na Figura 17 devido a variação da temperatura ambiente.

Figura 19 – Curva da DE2 a 135ºC. Fonte: O Autor

A Figura 20 mostra as curvas para a ZedBoard, possuindo um comportamento semelhante ao discutido sobre a Figura 18.

Figura 20 - Curva da ZedBoard a 135ºC. Fonte: O Autor

Figura 21 – Comparação das duas placas a 135ºC. Fonte: O Autor

A Tabela 5 mostra as frequências iniciais e finais dos osciladores das duas placas que foram estressadas.

Tabela 5 – Frequências iniciais e finais dos osciladores a 135 ℃.

|         | Frequência (kHz)    |       |      |       |  |  |

|---------|---------------------|-------|------|-------|--|--|

|         | Altera DE2 ZedBoard |       |      |       |  |  |

|         | 1001                | 4999  | 1001 | 4999  |  |  |

| Inicial | 1612 325,6          |       | 1374 | 257,9 |  |  |

| Final   | 1607                | 324,3 | 1360 | 255,2 |  |  |

As curvas das Figuras 19 e 20 apresentam um comportamento semelhante às curvas da Seção 4.2, mostrando que a tendência do FPGA da placa ZedBoard degradar mais que o da DE2 continua independente da temperatura. Porém, essas medidas não podem ser comparadas de nenhuma forma com as medidas das placas de controle, já que elas sempre operaram na temperatura ambiente.

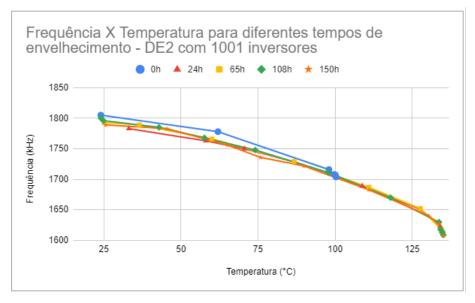

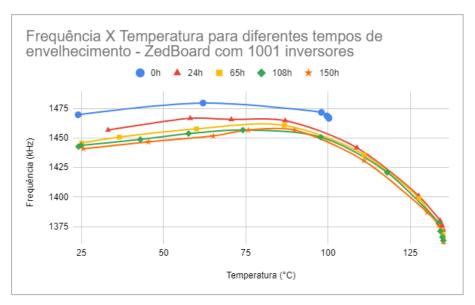

### 4.4 Comparação das Curvas Frequência X Temperatura

Com as medidas de frequência durante o aquecimento da câmera térmica da temperatura ambiente até a temperatura alvo foi possível construir as curvas apresentadas nas Figuras 22 e 23. Cada uma das curvas é construída com os dados de um ciclo de estresse e está relacionada a um tempo de envelhecimento acumulado. Na Tabela 1 da Seção 3.3 consta que dia corresponde ao ciclo de cada uma das curvas.

Na Figura 22 se vê que as curvas estão próximas e que não há uma sequência entre elas com relação ao tempo de envelhecimento, visto que a curva de 24 horas (vermelha) é a posicionada mais abaixo.

Figura 22 – Curva Frequência por Temperatura do oscilador com 1001 inversores da placa DE2. Fonte: O Autor

No entanto, na Figura 23 é observado que as curvas estão ordenadas em relação ao tempo de envelhecimento, sendo deslocadas para baixo a cada sido. Ou seja, é possível verificar que, de forma geral, a frequência em qualquer temperatura foi diminuindo com o estresse térmico.

Figura 23 – Curva Frequência por Temperatura do oscilador com 1001 inversores da placa ZedBoard. Fonte: O Autor

Essas duas figuras corroboram com o discutido na Seção 4.2 de que os osciladores da ZedBoard apresentaram uma degradação consideravelmente maior que os osciladores da DE2.

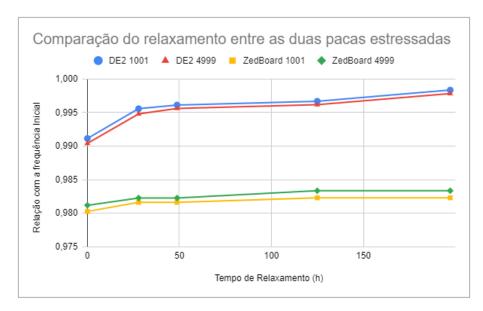

#### 4.5 Medidas de relaxamento

Após os ensaios de envelhecimento foram realizadas medidas nos dispositivos para verificar a recuperação da degradação infligida a eles. Todos os FPGAs foram deixados desligados e em temperatura ambiente, sendo ligados apenas para realizar as medições.

A Figura 24 mostra as curvas das frequências normalizadas ao longo do tempo de relaxamento das placas que foram estressadas termicamente. Nela se vê que os FPGAs da altera recuperaram mais que os da ZedBoard, e que ele apresenta uma tendência de continuar recuperando após o fim dos ensaios, enquanto a ZedBoard apresentou uma estabilização na frequência.

Figura 24 – Comparação do relaxamento das duas placas. Fonte: O Autor

É demonstrado na Figura 25 como as duas placas DE2 se comportaram ao longo do tempo de relaxamento. É visível que as duas apresentaram semelhança no formato da curva, inclusive alcançando um valor próximo na última medida.

Figura 25 – Curva de relaxamento das placas DE2. Fonte: O Autor

Uma comparação da recuperação das duas ZedBoards é ilustrada na Figura 26 onde é possível observar que o formato da curva é semelhante, porém, devido ao valor diferente de degradação que tiveram, a placa estressada recuperou menos proporcionalmente.

Figura 26 - Curva de relaxamento das placas ZedBoard. Fonte: O Autor

A Tabela 6 mostra o percentual da frequência inicial que foi recuperado durante o período de relaxamento. A proporção da frequência inicial que foi recuperada foi semelhante para todos os osciladores de ambas as Zedboards, já para os osciladores da DE2 houve uma diferença considerável.

Tabela 6 – Frequência recuperada.

|                 | Recuperação (%)         |      |      |       |

|-----------------|-------------------------|------|------|-------|

|                 | Altera DE2 ZedBoard     |      |      | Board |

|                 | 1001   4999   1001   49 |      |      | 4999  |

| Estressados     | 0,72                    | 0,74 | 0,20 | 0,22  |

| Não Estressados | 0,51                    | 0,51 | 0,20 | 0,17  |

Esses valores não refletem exatamente a realidade sobre a recuperação, pois a porcentagem de degradação foi diferente entre as placas. Uma análise mais condizente seria ver a proporção entre a porcentagem da recuperação e a porcentagem da degradação, de forma que se tem a um proporção de quanto da degradação foi recuperada. A Tabela 7 mostra esses valores.

Tabela 7 – Porcentagem da degradação que foi recuperada.

|                 | Proporção Recuperada (%) |       |           |       |

|-----------------|--------------------------|-------|-----------|-------|

|                 | Altera DE2 ZedBoard      |       |           | Board |

|                 | 1001                     | 4999  | 1001 4999 |       |

| Estressados     | 81,25                    | 77,14 | 10,34     | 11,54 |

| Não Estressados | 81,82                    | 78,26 | 42,86     | 29,41 |

Na Tabela 7 se observa que as DE2 tiveram valores de recuperação semelhantes e que ambas recuperaram uma porção considerável, de em torno de 80%, do que foi degradado.

Já as ZedBoards que foram estressadas recuperaram apenas 10% do que foi degradado e, diferente do outro modelo de FPGA, não teve semelhança com sua contraparte não estressada, que tiveram entre 29% e 43% de recuperação.

#### 4.6 Discussão

De forma geral, o que foi visto nesta seção foi que o FPGA da placa ZedBoard foi mais afetado pelo estresse térmico e, consequentemente, pelo fenômeno do NBTI que o FPGA da placa DE2. Isso está dentro do estabelecido na literatura de que transistores de nós tecnológicos menores são mais propensos a sofrer do fenômeno, como visto em diversos outros trabalhos (CHEN *et al.*, 2003), (PAUL *et al.*, 2006) e (ZENG *et al.*, 2017).

A ZedBoard também teve uma recuperação menor da frequência degradada, mostrando que, além dos efeitos terem sidos mais severos, foram mais duradouros, o que indica que a componente permanente do NBTI (SILVA, 2012) domina o fenômeno. De forma diferente, para a DE2 pode-se supor que existe um domínio maior da componente recuperável.

Isso pode demonstrar que, por mais que a ZedBoard seja um dispositivo mais poderoso, ela pode não ser o mais indicado para aplicações críticas que precisam operar em alta temperatura e manter uma frequência de operação constante devido a estar mais propenso aos fenômenos de envelhecimento.

# 5 Conclusão

Neste trabalho foi proposta a realização de ensaios de estresse térmico para gerar NBTI nos transistores de diferentes FPGAs e avaliar a degradação na frequência de osciladores em anel sintetizados neles, para assim comparar a susceptibilidade dos dispositivos ao fenômeno estudado. Os dispositivos ensaiados foram uma placa DE2, que possui um FPGA da família Cyclone II, fabricado pela Altera, de nó tecnológico de 90nm, e uma placa ZedBoard, com um FPGA da família Artix 7, da Xilinx, de nó tecnológico de 28nm.

Além de comparar a degradação entre as duas placas de fabricantes diferentes, ela foi comparada com a degradação de placas dos mesmos modelos mas que não foram estressadas termicamente. Finalmente, foram realizadas medidas para avaliar a recuperação que os dispositivos tiveram ante a degradação.

Após as 150h de estresse foi observado uma maior degradação na frequência do FPGA da placa ZedBoard (aproximadamente 2%) em relação a placa DE2 (aproximadamente 1%). As comparações com entre as placas de mesmo modelo mostrou que a DE2 não apresentou muita diferença entre a placa estressada e a não estressada, já a ZedBoard sim. Nas medidas de relaxamento foi visto que A ZedBoard recuperou pouco (aproximadamente 10%), já a DE2 recuperou quase completamente (aproximadamente 80%).

Isso corrobora a hipótese de que as duas placas não envelhecem com a mesma intensidade, o que pode ser devido ao fato que o nó tecnológico da ZedBoard ser menor que o da DE2, o que está de acordo com a literatura, que diz que o fenômeno do NBTI é mais crítico quanto menor for o nó tecnológico.

Essas medidas trazem mais informações sobre como o NBTI afeta os dispositivos comerciais em questão, possibilitando uma escolha mais assertiva na hora de um projeto. O trabalho também contribuiu apresentando uma forma simples de analisar os efeitos de envelhecimento acelerado em dispositivos comerciais.

Um possível trabalho poderia ser realizar ensaios semelhantes utilizando um FPGA de tecnologia FinFET, pois os FPGAs estudados nesse são de tecnologia CMOS planar. Outra sugestão de trabalho seria a análise de diferentes topologias de oscilador em anel, como os propostos no trabalho de (SATO *et al.*, 2014), em FPGAs de nós tecnológicos diferentes, para verificar como essas diferentes topologias se comportam em dispositivos diferentes.

# Referências Bibliográficas

AIN, M. F.; NAGHMASH, M. S.; CHYE, Y. H. Synthesis of HDL code for FPGA design using system generator. *European Journal of Scientific Research*, v. 45, n. 1, p. 111–121, 2010. Disponível em: <a href="https://www.researchgate.net/publication/292566560\_Synthesis\_of\_HDL\_code\_for\_FPGA\_design\_using\_system\_generator">https://www.researchgate.net/publication/292566560\_Synthesis\_of\_HDL\_code\_for\_FPGA\_design\_using\_system\_generator</a>.

ALAM, M. *et al.* A comprehensive model for PMOS NBTI degradation: Recent progress. *Microelectronics Reliability*, v. 47, n. 6, p. 853–862, 2007.

ASHRAF, N. S. *et al.* Accurate model for the threshold voltage fluctuation estimation in 45-nm channel length MOSFET devices in the presence of random traps and random dopants. *IEEE Electron Device Letters*, v. 32, n. 8, p. 1044–1046, 2011.

BHARDWAJ, S. *et al.* Predictive modeling of the NBTI effect for reliable design. *IEEE Custom Integrated Circuits Conference*, p. 189–192, 2016.

BHASKER, J. A Verilog HDL Primer 2nd edition. [S.I.]: Star Galaxy Publishing, USA, 1999.

BHUSHAN, M. *et al.* Ring oscillators for CMOS process tuning and variability control. *IEEE Transactions on Semiconductor Manufacturing*, v. 19, n. 1, p. 10–18, 2006.

BUTZEN, P. F. Aging aware design techniques and CMOS gate degradation estimative. *Tese - Escola de Engenharia*, *Universidade Federal do Rio Grande do Sul*, 2012. Disponível em: <a href="https://lume.ufrgs.br/bitstream/handle/10183/61868/000866378.pdf">https://lume.ufrgs.br/bitstream/handle/10183/61868/000866378.pdf</a>?sequence=1&isAllowed=y>.

CHEN, G. *et al.* Dynamic NBTI of PMOS transistors and its impact on device lifetime. *IEEE International Reliability Physics Symposium Proceedings*, v. 41, p. 196–202, 2003.

DAVIDOVIĆ *et al.* Nbt stress and radiation related degradation and underlying mechanisms in power VDMOSFETS. *FACTA UNIVERSITATIS Series: Electronics and Energetics*, v. 31, n. 3, p. 367–388, 2021. Disponível em: <a href="https://doi.org/10.2298/FUEE1803367D">https://doi.org/10.2298/FUEE1803367D</a>.

DEGALAHAL, V. et al. Impact of NBTI on FPGAs. 20th International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems (VLSID'07), p. 717–722, 2007.

FERNÁNDEZ-GARCÍA, R. et al. A CMOS circuit for evaluating the NBTI over a wide frequency range. *Microelectronics Reliability*, v. 49, n. 8, p. 885–891, 2009.

GALLER, D.; SLENSKI, G. Causes of aircraft electrical failures. *IEEE Aerospace and Electronic Systems Magazine*, v. 6, n. 8, p. 3–8, 1991.

GROSSI, M.; OMAÑA, M. Investigation of the impact of BTI aging phenomenon on analog amplifiers. *IEJ Electron Test*, v. 37, p. 533–544, 2021. Disponível em: <a href="https://doi.org/10.1007/s10836-021-05967-9">https://doi.org/10.1007/s10836-021-05967-9</a>.

KOÇAK, H. M. *et al.* Detecting transistor defects in medical systems using a multi model ensemble of convolutional neural networks. *2021 IEEE International Conference on Big Data* (*Big Data*), p. 4731–4737, 2021.

LINDER, B. P. et al. Separating NBTI and PBTI effects on the degradation of ring oscillator frequency. 2011 IEEE International Integrated Reliability Workshop Final Report, p. 1–6, 2011.

LORENZ, D. Aging analysis of digital integrated circuits. *TECHNISCHE UNIVERSITÄT MÜNCHEN*, 2012.

MICHAL, V. On the low-power design, stability improvement and frequency estimation of the CMOS ring oscillator. *Proceedings of 22nd International Conference Radioelektronika*, p. 1–4, 2012.

PAUL, B. C. *et al.* Temporal performance degradation under NBTI: Estimation and design for improved reliability of nanoscale circuits. *Proceedings of the Design Automation Test in Europe Conference*, v. 1, p. 1–6, 2006.

RADAMSON, H. H. et al. Miniaturization of CMOS. Micromachines, v. 10, n. 5, p. 293, 2019.

RJOUB, A.; SHATNAWI, A. M. High speed low power multi–threshold voltage flip flops. *Journal of ELECTRICAL ENGINEERING*, v. 54, n. 5-6, p. 123–127, 2003.

SATO *et al.* Reduction of NBTI-induced degradation on ringoscillators in FPGA. *Pacific Rim International Symposium on Dependable Computing*, v. 20, n. 10, p. 59–67, 2014. Disponível em: <a href="http://hdl.handle.net/10228/00006261">http://hdl.handle.net/10228/00006261</a>.

SCHRODER, D. K.; BABCOCK, J. A. Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing. *Journal of Applied Physics*, v. 94, n. 1, 2003.

SILVA, M. B. da. Circuito on-chip para a caracterização em alta escala do efeito de bias temperature instability. *Dissertação - Escola de Engenharia, Universidade Federal do Rio Grande do Sul*, 2012. Disponível em: <a href="https://www.lume.ufrgs.br/bitstream/handle/10183/147989/001001128.pdf?sequence=1">https://www.lume.ufrgs.br/bitstream/handle/10183/147989/001001128.pdf?sequence=1</a>.

SPARKFUN. *LogicBlocks Experiment Guide*. 2023. Disponível em: <a href="https://learn.sparkfun.com/tutorials/logicblocks-experiment-guide/5-ring-oscillator">https://learn.sparkfun.com/tutorials/logicblocks-experiment-guide/5-ring-oscillator</a>.

SULAIMAN, N. *et al.* Design and implementation of FPGA-based systems - a review. *Australian Journal of Basic and Applied Sciences*, 2009. Disponível em: <a href="https://www.researchgate.net/publication/268424617\_Design\_and\_Implementation\_of\_FPGA-Based\_Systems\_-A\_Review">https://www.researchgate.net/publication/268424617\_Design\_and\_Implementation\_of\_FPGA-Based\_Systems\_-A\_Review</a>.

WIRTH, G. I.; SILVA, R. da; KACZER, B. Statistical model for MOSFET bias temperature instability component due to charge trapping. *IEEE Transactions on Electron Devices*, v. 58, n. 8, p. 2743–2751, 2011. Disponível em: <a href="https://ieeexplore.ieee.org/document/5910375">https://ieeexplore.ieee.org/document/5910375</a>.

WUNNAVA, S.; MONTENEGRO, J. M. Tutorial on VHDL and verilog applications. Second LACCEI International Latin American and Caribbean Conference for Engineering and Technology, 2004. Disponível em: <a href="https://studylib.net/doc/7714871/tutorial-on-vhdl-and-verilog-applications">https://studylib.net/doc/7714871/tutorial-on-vhdl-and-verilog-applications</a>.

XILINX. *Field Programmable Gate Array (FPGA)*. 2023. Disponível em: <a href="https://www.xilinx.com/products/silicon-devices/fpga/what-is-an-fpga.html">https://www.xilinx.com/products/silicon-devices/fpga/what-is-an-fpga.html</a>.

XILINX. *Zynq 7000 Product Brief.* 2023. Disponível em: <a href="https://www.xilinx.com/content/dam/xilinx/support/documents/product-briefs/zynq-7000-product-brief.pdf">https://www.xilinx.com/content/dam/xilinx/support/documents/product-briefs/zynq-7000-product-brief.pdf</a>.

ZENG et al. Detailed study of NBTI characterization in 40-nm CMOS process using comprehensive models. Chinese Phys. B, v. 26, n. 10, 2017.