# Evaluation of Single Event Upset Susceptibility of FinFET-based SRAMs with Weak Resistive Defects

Thiago Copetti<sup>1,2</sup> • Guilherme Cardoso Medeiros<sup>3</sup> • Mottaqiallah Taouil<sup>3</sup> • Said Hamdioui<sup>3</sup> • Letícia Bolzani Poehls<sup>2,4</sup> • Tiago Balen<sup>1</sup>

Received: 15 December 2020 / Accepted: 19 May 2021 / Published online: 1 June 2021 © The Author(s) 2021

#### **Abstract**

Fin Field-Effect Transistor (FinFET) technology enables the continuous downscaling of Integrated Circuits (ICs), using the Complementary Metal-Oxide Semiconductor (CMOS) technology in accordance with the More Moore domain. Despite demonstrating improvements on short channel effect and overcoming the growing leakage problem of planar CMOS technology, the continuity of feature size miniaturization tends to increase sensitivity to Single Event Upsets (SEUs) caused by ionizing particles, especially in blocks with higher transistor densities such as Static Random-Access Memories (SRAMs). Variation during the manufacturing process has introduced different types of defects that directly affect the SRAM's reliability, such as weak resistive defects. As some of these defects may cause dynamic faults, which require more than one consecutive operation to sensitize the fault at the logic level, traditional test approaches may fail to detect them, and test escapes may occur. These undetected faults, associated with weak resistive defects, may affect the FinFET-based SRAM reliability during its lifetime. In this context, this paper proposes to investigate the impact of ionizing particles on the reliability of FinFET-based SRAMs in the presence of weak resistive defects. Firstly, a TCAD model of a FinFET-based SRAM cell is proposed allowing the evaluation of the ionizing particle's impact. Then, SPICE simulations are performed considering the current pulse parameters obtained with TCAD. In this step, weak resistive defects are injected into the FinFET-based SRAM cell. Results show that weak defects can positively or negatively influence the cell reliability against SEUs caused by ionizing particles.

Keywords SRAMs · FinFET · Resistive defects · TCAD · SEU · Reliability · Single event transient modeling

#### 1 Introduction

Fin Field-Effect Transistor (FinFET)-based Static Random-Access Memories (SRAMs) represent one of the current state-of-the-art technologies for integrated systems as they

Communicated by S. N. Demidenko.

☐ Thiago Copetti copetti@ids.rwth-aachen.de

Guilherme Cardoso Medeiros G.CardosoMedeiros@tudelft.nl

Mottaqiallah Taouil M.Taouil@tudelft.nl

Said Hamdioui

S.Hamdioui@tudelft.nl

Letícia Bolzani Poehls leticia@poehls.com; poehls@ids.rwth-aachen.de

Tiago Balen tiago.balen@ufrgs.br are designed with high density and produced at the limit of the fabrication process. Furthermore, as FinFET is a recent technology, there is a need to evaluate and model its behavior concerning defects and failures [1].

One major reliability issue in nanometer technologies is radiation-induced Single Event Effects (SEE), i.e., soft

- Graduate Program on Microelectronics PGMICRO, Federal University of Rio Grande Do Sul, Porto Alegre, Brazil

- IDS, RWTH Aachen University, Aachen, Germany

- Computer Engineering Laboratory, Delft University of Technology, Delft, The Netherlands

- School of Engineering, Pontifical Catholic University of Rio Grande Do Sul, Porto Alegre, Brazil

errors caused by ionizing particles [2]. In SRAM cells, a soft error may generate a bit-flip, called Single Event Upset (SEU). This faulty behavior occurs when an ionizing particle strikes a reverse-biased PN junction (usually an off-state transistor's drain) initially generating a transient current pulse in a given circuit node. If the affected transistor belongs to a cell's storage node, this transient current pulse may propagate through the feedback of the cross-coupled inverter, generating a bit-flip [3].

Another essential reliability issue in FinFET memory technology is related to weak resistive defects [1] caused by variability in the manufacturing process. These defects can be classified either as resistive-opens or resistive-bridge defects [4]. They can be classified as "weak" [5] if they are hard to detect, especially using traditional memory tests such as March tests [5]. Therefore, they may lead to test escapes, which might affect the FinFET device's susceptibility to single events due to ionizing particle strikes in the field, as discussed in this paper.

It is known from the literature that radiation can lead to soft errors in FinFETs even at ground level [2, 6]. Several works performed a comparative analysis regarding SEEs between FinFET and other technologies (conventional bulk CMOS and SOI) [2]. Also, in [2], an analysis of FinFETbased SRAMs at different altitude levels was performed. Analysis of weak resistive defects has already been carried out for both planar SRAM cells [4] and FinFET-based SRAM cells [7]. Further, an analysis of the radiation susceptibility of conventional CMOS SRAM cells in the presence of weak resistive defects is presented in [8]. Considering the previsously published work, we propose to analyze the influence of weak resistive defects on the FinFET-based SRAM robustness under single event effects. Because the FinFET structure is physically more complex than the planar CMOS, a more precise and realistic simulation tool is necessary. Thus, a FinFET-based SRAM cell was modeled using a Technology Computer-Aided Design (TCAD) tool, and simulations of ionizing particle impacts were performed at the physical level. Further, the transient current generated by such an event was modeled at the electrical level.

Hence, the main contributions of this paper are: 1) obtain, by physical simulation, the minimum value of Linear Energy Transfer (LET) of an incident particle that results in a bit-flip (LET<sub>th</sub>, or threshold LET) for FinFET SRAM cells designed in a technology equivalent to a 14 nm node; 2) propose a SPICE model for the obtained current curves; 3) investigate the impact of SEUs on the reliability of FinFET-based SRAMs with weak resistive defects. Note that the first step towards these goals was presented in [9]. Thus, this publication extends the explanations regarding the proposed simulation flow during experiments, improves the development of the transistor's electrical characteristics, and enhances the SRAM cell's analysis with respect to regions far from the

critical node. The results obtained in this work may help researchers working on SRAM reliability by providing a feasible simulation flow and important insights of the possible impacts of test escapes, considering non-critical resistive defects, in SRAM field applications susceptible to ion strikes.

# 2 Background

FinFETs are composed of thin vertical slices of silicon (known as fins) that are wrapped by the gate structure and built on top of a silicon substrate [1]. These fins comprise the channel region of the transistor. Note that this work considers the bulk FinFET model, in which the fins are directly connected to the substrate, and the oxide is used to isolate each fin from the others.

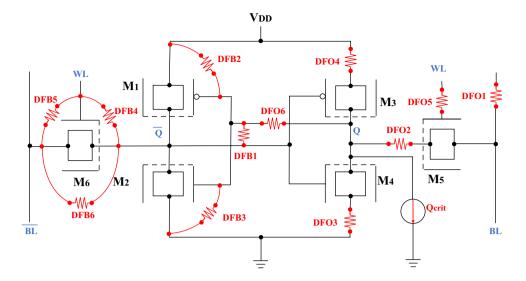

A schematic view of a standard 6 T-SRAM cell is illustrated in Fig. 1. For sake of conciseness, this figure also shows the equivalent resistive defects and the transient current model ( $Q_{crit}$ ) that will be described in Section III. This cell is composed of six transistors: two cross-coupled inverters ( $M_1 \& M_2$  and  $M_3 \& M_4$ ) that store the digital information in nodes Q and its counterpart  $\overline{Q}$ , and the other two nFET transistors acting as Pass Gates (PG) ( $M_5$  and  $M_6$ ), responsible for isolating the cell during hold phase, and open the cell during read and write operations. The Word Line (WL) signal controls the two PGs that are connected to the bit lines (BL and  $\overline{BL}$ ) [4].

One of the main causes of test escapes in new technologies based on FinFETs is related to the presence of weak defects, which make the cell more prone to dynamic faults than conventional planar CMOS-based SRAM [1]. Weak resistive defects are defects with resistive characteristics that cause small device's electrical parameter deviations [10]. In SRAM cells, such defects can generate dynamic faults, which require more than one consecutive read operations to propagate a fault at logic level [10–12]. A resistive-open is modeled as a resistor between two nodes that share a connection, and a resistive-bridge is modeled as a resistor between two nodes that not should be connected [4], as illustrated in Fig. 1.

The memory testing methodology for the detection of dynamic faults, used for FinFET and CMOS, caused by resistive defects can be done by performing n consecutive read operations (stress condition) [13]. The number of consecutive operations is related to the defect size, which means that weak defects could require a prohibitive number of consecutive read operations during manufacturing testing. Thus, when considering FinFET technology, the presence of weak defects and the fact that they did not necessarily propagate any fault at the logic level, causing an electrical deviation only, is considered a great source

Fig. 1 FinFET-based SRAM cell with injected defects and transient current

of test scape [1]. In this context, a memory including cells with very weak defects can be classified as fault-free. However, the presence of these very weak defects can exacerbate the memory susceptibility to SEUs, justifying the proposed methodology and analysis.

In [14], a comparison of SEEs between a 16 nm bulk FinFET and a 28 nm bulk planar technology was carried out. This study shows that low-LET particles may cause transients in FinFETs when hitting the fin region. Therefore, FinFET technology has a very strong dependence on the ion strike location, unlike planar CMOS, which demonstrates less dependence on the position of impact. The same study reported that a strike between two fins produces a very small transient voltage. This effect happens in FinFETs due to their low charge collection efficiency, which means that a small fraction of the generated electron—hole pairs is collected at the FinFET drain during the silicon ionization, resulting in lower current pulses [2].

However, with the proximity of connections and the reduced supply voltage, FinFET-based SRAMs are becoming more susceptible to SEUs, even at ground level [6]. Traditionally, the major sources of radiation-induced soft errors at ground level or flight altitudes are: (1) alpha particles originated by the radioactive contamination existing in the packaging [15, 16]; (2) the high-energy neutrons from cosmic radiation (generating secondary reactions); and (3) the interaction of cosmic ray thermal neutrons with devices containing borophosphosilicate glass [16]. The work presented in [2] has shown that for SRAMs, protons, and muons are also among the particles able to generate SEUs at ground level in bulk FinFET technologies.

The work presented in [17] describes an empiric experiment of two 128 Mb FinFET-based SRAMs using two different configurations: High-Density (HD), and High Performance (HP), both being exposed to alpha particles, thermal

neutrons, and high energy neutrons. The experiments show that the HP cell is more sensitive than the HD cell due to its advanced geometric isolation from the substrate. It is interesting to note, that the method used for computing the critical charge differs from the method used in this work. In [17] the critical charge is obtained from the equation given in [18], resulting in a higher critical charge for HP when compared to HD cells. However, as is described throughout this paper, it has to be assumed that the critical charge's definition is not so trivial.

# 3 Methodology

In order to evaluate the transient effects caused by ion strikes, a layout of a 14 nm FinFET-based SRAM cell was designed and modeled in Sentaurus<sup>TM</sup> TCAD tool. This technology node was chosen due to its current use by memory manufacturing companies. This section also describes the methodology carried out to simulate ionizing particle strikes at the physical level as well as the SPICE modeling of resistive defects.

# 3.1 Modeling a FinFET-SRAM Cell in TCAD

To study the effects of SEUs, an initial FinFET SRAM 3D model was developed using Sentaurus<sup>TM</sup> TCAD. In comparison to SPICE simulations, this tool allows larger flexibility while controlling the device physics aspects, including the impact location of ionizing particles and its associated LET. This study considers three models of FinFET-based SRAM cells: High-Density (HD), High Performance (HP), and Low Voltage (LV). Because of the discrete nature of fins, it is not possible to tune the transistor parameters to obtain an ideal robustness/area ratio as it would be feasible in planar

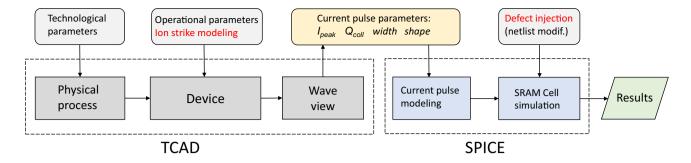

Fig. 2 Adopted simulation flow

CMOS. Therefore, each model has its configuration with a different distribution of fins in the cell's transistors. The SRAM cell structure is divided into three parts with their proper notation (PU:PG:PD), meaning respectively: Pull Up, Pass Gate and Pull Down [18]. As an example, the HD configuration adopts a (1:1:1) configuration, meaning that all the cell transistors are composed of a single fin.

Figure 2 shows the simulation flow adopted in the Synopsys Sentaurus<sup>TM</sup> environment [20]. Firstly, the physical process of cells was developed, using the Sentaurus<sup>TM</sup> Process (S\_Process) tool. The transistors designed with the Sentaurus<sup>TM</sup> tool were calibrated using the physical characteristics described by the 2015 International Technology Roadmap for Semiconductors (ITRS) [21], summarized in Table 1. The mesh grid configured in these simulations was generated given special attention to the active zones such as channel, source, and drain.

Using the Sentaurus Device (S\_Device), the operational parameters of the circuit are implemented, allowing its validation. The curve of Static Noise Margin (SNM) was also collected at this stage in order to properly evaluate the reliability of the circuit with respect to noise fluctuations. After these steps, the injected ionizing particle is modeled, using the same tool. The tool Sentaurus Visual (S\_Visual) was used to analyze the electrical behavior, by wave verification. Finally, the Inspect tool was used to verify the transient operations while simulating the ion impact.

Table 1

Adopted Physical Parameters for FinFETs

| Physical Parameters  | Values [nm] |

|----------------------|-------------|

| Physical Gate Length | 26          |

| Fin Width            | 8           |

| Fin Height           | 42          |

| Fin Pitch            | 42          |

| Poly Pitch           | 90          |

| Effective Width      | 92          |

| Metal Pitch          | 56          |

The heavy-ion injection in TCAD simulation follows the methodology presented in [14], considering a Gaussian charge distribution with a track radius of 10 nm. To model the worst-case scenario of such particle strike, the charge track length should be longer than the fin height, with normal incidence over the drain of the sensitive transistor (off-state transistor). The sensitive transistor is the pull-down transistor when the node (inverter output) is charged with a logic '1', or the pull-up transistor when the node is '0'.

In the simulation setup, the input parameters for heavy ions are given in charge per track length (pC/μm). To convert this value into the LET parameter the relation of 1 pC/ um is equivalent to a 97 MeV-cm<sup>2</sup>/mg LET in silicon [15]. For example, the alpha particles due to radioactive contamination in the packaging material can result in 0.015 pC/µm, which approximates 1.5 MeV-cm<sup>2</sup>/mg [15]. This analysis aims to find the threshold LET that causes a bitflip in the cell. Considering this LET, the drain current in the affected transistor is evaluated, obtaining important parameters, such as the collected charge  $(Q_{coll})$ , current peak  $(I_{neak})$ , pulse width, and general shape, which is then compared with the traditional double exponential. The obtained current shape is modeled in SPICE to allow transient injections and resistive defect modeling at the same time. This analysis is carried out in SPICE since TCAD simulations would demand a huge computational effort. The overall simulation flow, including the resistive defects modeling in SPICE, is depicted in Fig. 2.

# 3.3 Injecting Resistive Defects

The electrical simulations to evaluate the robustness of a FinFET-based SRAM cell in the presence of weak defects are performed using Hspice<sup>TM</sup> from Synopsys. The Fin-FET-based SRAM was designed using the Arizona State University's 14 nm FinFET Predictive Technology Model

Table 2 Number of fins and area considering different SRAM cells

| (PU:PG:PD) | Area (um²)         |

|------------|--------------------|

| (1:1:1)    | 0.0558             |

| (1:1:2)    | 0.07092            |

| (1:2:2)    | 0.07092            |

|            | (1:1:1)<br>(1:1:2) |

(PTM) [22]. For this purpose, the injected charge to simulate single events in SPICE is set with a value lower than the excess charge observed when simulating a particle strike with LET = LET<sub>th</sub>, while simultaneously injecting resistive defects. In this case, the defect resistance values are varied using an automated tool that interacts with the SPICE simulator. Note that the critical resistance (R<sub>crit</sub>) is the defect resistance threshold that results in a bit-flip when injecting the ionizing particle. The methodology for resistive defects injection, according to the model shown in Fig. 1, is the same used in [7] and [22]. This effort is necessary to observe if resistive defects may change the cell's robustness to SEUs. The opposite situation was also verified, simulating an event depositing the critical charge (Q<sub>crit</sub>) at the same time that resistive defects are injected, in order to determine if SEEs are attenuated due to the presence of a given defect.

#### 4 Results and Discussion

This section presents the results divided into three subsections: A) the FinFET-based SRAM cell model and validate using TCAD; B) TCAD-based SEE injection results and comparison with SPICE injections; C) the influence of resistive defects on cell reliability when considering single events.

#### 4.1 SRAM Cell Modeling and Validation

As previously mentioned, a FinFET-based SRAM cell was implemented based on the physical parameters described on

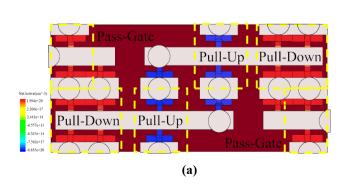

the 2015 ITRS [21], and as presented in [19]. Three different models were adopted, whose configurations (number of fins of the transistors), along with the corresponding area, are shown in Table 2. As an example, Fig. 3 shows an LV SRAM cell modeled in 3D-TCAD. Different from this exemplary cell, the HD configuration, the most compact, would not possess a fin column on each side of the cell, and the HP configuration would show two fins in the PG. To reproduce industrial devices, only HD and LV cells use source and drain regions with a polyhedron of silicon over the fin [19]. Note that these structures do not cause a considerable current variation in the transistor when compared with the HP cell. Electrically, the LV model has a more robust SNM for a read operation, and the HP model is faster during reading and writing operations [19].

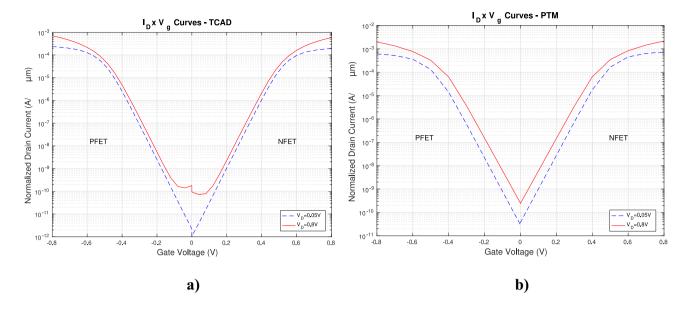

To validate the device's electrical operation is compatible with the 14 nm node used as target technology, the electrical behavior was compared to the drain current/gate voltage data from the Arizona State University's Predictive Technology Model (PTM) [22]. To observe the Id x Vg behavior, Fig. 4 presents the drain current (Id) comparison, for both p and n Fin-FETs considering two drain voltages, 0.05 V and 0.8 V. Table 3 shows the off and saturation currents ( $I_{off}$  and  $I_{sat}$ ), as well as the percentage difference between the PTM model and the TCAD modeled device for each reported parameter. The  $I_{off}$  is obtained with 0.8 V as drain voltage and the  $I_{sat}$  with the highest possible voltage value. The normalized currents are the currents divided by the fin pitch in µm, thereby 0.042 for the developed transistor and 0.023 for PTM. Note that the difference between them is calculated using normalized values. Despite observing a significant difference between the saturation currents, the PTM model was used as a behavioral reference model only. The physical parameters of the PTM model are different from the parameters used in the TCAD model, consequently, the behavior is not expected to be exactly the same.

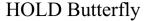

Table 4 summarizes the hold, read and write SNM values for the three different FinFET-SRAM cells developed using TCAD as well as for the circuit modeled according to PTM parameters in SPICE. Comparing the data, it is verified that

Fig. 3 FinFET LV SRAM cell implemented in this work: (a) top view; (b) 3D view without gate and metals

Fig. 4 Drain Current vs Gate Voltage for the transistors modeled in: a) TCAD, with physical parameter x b) SPICE, with PTM

the behavior of the circuit modeled in the TCAD simulator is correct, being even more robust than the PTM version. Finally, Fig. 5 shows the hold SNM butterfly curve of the FinFET-SRAM cell modeled using TCAD.

# 4.2 Simulating Single Event Transient using TCAD

The heavy-ion simulation considers the particle strike in the corresponding time of 10 ps and the ion track according to the parameters presented in Section III. Considering that the

Table 3

Electrical Characteristics—comparative between the Fin-FETs modeled in TCAD and SPICE (PTM)

| Electrica | al Character- | TCAD        | PTM         | Δ       |

|-----------|---------------|-------------|-------------|---------|

| NFET      | Ioff          | 3.920 pA    | 5.589 pA    | -29,86% |

|           | Ioff_norm     | 93.33 pA/μm | 243.0 pA/µm | -61.59% |

|           | Isat          | 24.69 μΑ    | 50.00 uA    | -50.62% |

|           | Isat_norm     | 587.9 μA/μm | 2174 uA/µm  | -72.96% |

| PFET      | Ioff          | 7.505 pA    | 5.732 pA    | 30.93%  |

|           | Ioff_norm     | 178.7 pA/μm | 249.2 pA/µm | -28.29% |

|           | Isat          | 29.63 μΑ    | 45.91 uA    | -35.46% |

|           | Isat_norm     | 705.6 μA/μm | 1996 uA/μm  | -64.65% |

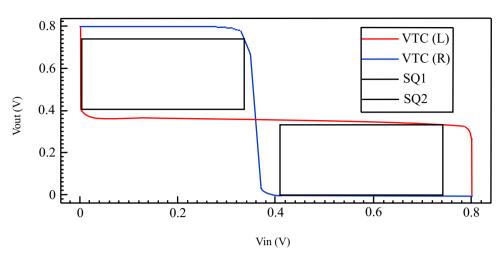

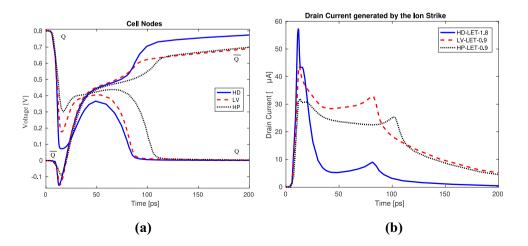

cells were designed with a depth of 1 µm, the deep length for the ion track was set as 0.9 µm. Figure 6 depicts the cells' behavior when an SEU is observed. In more detail, Fig. 6(a) presents the bit-flip caused by ionizing particles with the lower LETs (threshold LET, or LET<sub>th</sub>) in the different designed cells, or, in other words, when  $Q_{crit}$  is achieved. However, according to [3], the definition of  $Q_{crit}$  in SRAMs is not as intuitive as for logic circuits, where it is associated exclusively with the charge stored in the node and the drive strength of the restoration transistors. In SRAMs, the feedback plays an important role, collaborating with the behavior of the transient current pulse. Two ways of defining  $Q_{crit}$  can be found in the literature. The first one considers the value of deposited or collected charge able to start bit-flips. The second definition considers the value of the charge flowing in excess during the transient current in the affected node, which considers also the charge flow due to the circuit dynamics (hence not merely the collected charge) [3]. Moreover, Fig. 6(b) shows the drain current observed for particles (with LET=LET<sub>th</sub>) injected at one of the inverters' nFET. One can notice a plateau region on the current pulses, corresponding to the occurrence of the feedback action. The feedback action tends to activate the nFET, which is nominally off before the transient. As can

Table 4 Comparison of the SNM values considering the FinFET-SRAM cell modeled in TCAD and in SPICE (PTM)

| Cell | Hold_SNM |      | Read_SNM |      | Write_SNM |      |

|------|----------|------|----------|------|-----------|------|

|      | TCAD     | PTM  | TCAD     | PTM  | TCAD      | PTM  |

| HD   | 0.33     | 0.30 | 0.15     | 0.13 | 0.39      | 0.30 |

| LV   | 0.34     | 0.30 | 0.18     | 0.16 | 0.38      | 0.30 |

| HP   | 0.33     | 0.30 | 0.15     | 0.13 | 0.39      | 0.30 |

Fig. 5 Hold SNM butterfly curve

be observed from Fig. 6(a), the plateau happens while both transistors are simultaneously in a conduction state (near the inverter trip point). Since the n devices of LV and HP cells are built with two fins, the current on this plateau is higher, which facilitates the inversion of the bit stored in the cell. Thus, it can be expected that the LET<sub>th</sub> for these two models is similar.

The data presented in Table 5 demonstrates that the HD cell is the most robust when considering transients injected in pull-down transistors; the LET<sub>th</sub> obtained with TCAD simulations is higher. The table's remaining columns show the charge that is injected to simulate the heavy-ion ( $Q_{dep}$ ) and the excess charge ( $Q_{exc}$ ), which is the charge disturbance on the affected node (integral of the transient current). Despite the lower LET<sub>th</sub>, one may notice that  $Q_{exc}$  is higher for LV and HP cells due to circuit dynamics. Another point that deserves attention is that not all the deposited charge is collected, as already discussed by [3]. Indeed, related works often consider the quantity denominated  $Q_{exc}$  as the  $Q_{crit}$

in SPICE-based injection campaigns. However, it is clear that this may lead to an erroneous evaluation regarding the circuit reliability, especially for SRAMs, as can be observed in Table 5. According to [24],  $Q_{crit}$  values computed from currents of 3D device simulation are approximately 3 times smaller than those found using current models. Therefore, this paper uses the value of LET<sub>th</sub>, based on the values obtained with TCAD, for reliability comparison purposes. Additionally, for SPICE simulations, we adopted the quantity  $Q_{exc}$ , which is the charge disturbance on the circuit due to the impact of a particle with LET = LET<sub>th</sub> on the drain of the sensitive transistor. From here on, this work avoids using the term critical charge during its analysis, since smaller LET values and deposited charges may result in a higher amount of excess charge, as observed during TCAD simulations, and in Table 5.

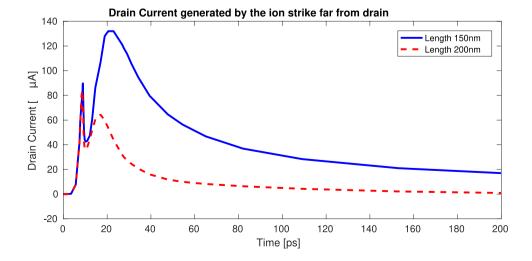

The distance of the ion impact from the transistor drain and the track length also plays an important role. Figure 7 shows the drain current that results from the impact of a

**Fig. 6** (a) Bit-flip in the cell; (b) Current generated by the ion strike

Table 5 Threshold LET and Deposited Charges (TCAD)

| Cell | LET <sub>th</sub> (MeV-cm <sup>2</sup> /mg) | $Q_{dep}$ (fC) | $Q_{exc}$ (fC) |

|------|---------------------------------------------|----------------|----------------|

| HD   | 1.8                                         | 16.7           | 1.24           |

| LV   | 0.9                                         | 8.34           | 3.79           |

| HP   | 0.9                                         | 8.34           | 3.55           |

particle with LET = 80 MeV-cm<sup>2</sup> /mg occurring 112 nm from the drain region's center of the pFET in the HD cell. The current difference observed in this figure is only caused by the variation of the charge track length from 150 to 200 nm. Integrating the results, one obtains a charge of 9.0 fC and 11 fC, respectively. It is possible to see that a much higher LET is needed to produce a similar amount of charge collection, able to generate a bit-flip if the impact occurs far from the drain.

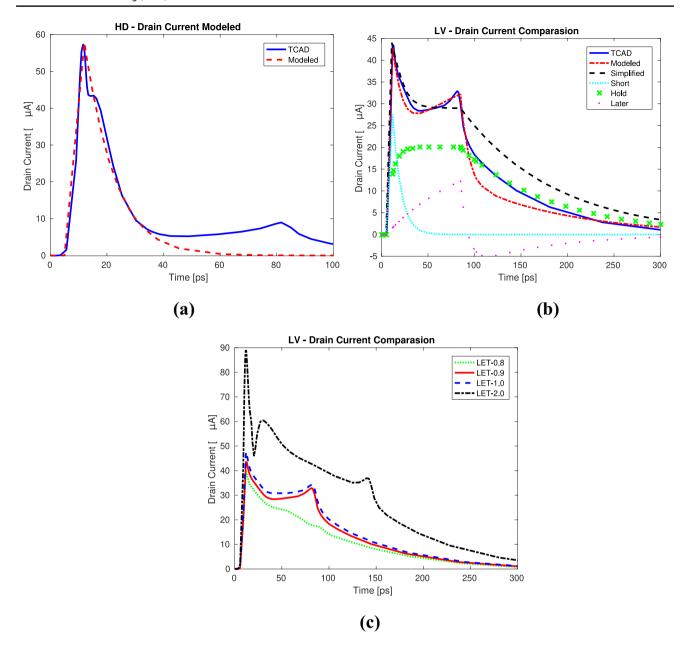

The observed current curves in TCAD simulations were then modeled as current sources in SPICE. The well-established Messenger's double exponential model [25] is still being applied in related works to simulate SEEs due to its simplicity, even for recent FinFET technologies [6]. However, in some cases, this model may not accurately represent the current behavior. For instance, in this work, the double exponential is suitable to model a particle with LET = LET<sub>th</sub> striking the pull-down transistor of the HD cell because the current from the plateau has a low effect in the bit-flip, while the same is not true to the LV and HP cell (Fig. 6(b)). A previous work that investigated single events in FinFETs [6] considered the following values using the double exponential time constants for the execution of SPICE simulations:  $\tau_1 = 2$  ps and  $\tau_2 = 20$  ps (time constants of rising and falling exponentials, respectively). However, TCAD simulations in the present work showed that, for strikes on nFET of the HD configuration, the rising and fall times are similar, resulting

in  $\tau_1 = 6$  ps,  $\tau_2 = 9$  ps, and  $(t_{d2} - t_{d1}) = 7$  ps  $(t_{d1})$  and  $t_{d2}$  are the initial times of both exponentials). Therefore, the double exponential curve is shown in Fig. 8(a) was used to perform transient injections on HD cells in SPICE, though varying the current peak according to the desired injected charge. Both curves (TCAD and SPICE modeled double exponential) are shown in Fig. 8(a).

However, the pulse shapes observed for the LV and HP configurations are significantly different from the double exponential. Hence, following the methodology proposed by [26], a combination of three exponential sources in SPICE is proposed to represent the behavior. The first is the double exponential with  $\tau_1 = 6$  ps,  $\tau_2 = 8$  ps, and  $(t_{d2} - t_{d1}) = 7$  ps with a short peak, the second source is a long double exponential with  $\tau_1 = 6$  ps,  $\tau_2 = 100$  ps, and  $(t_{d2} - t_{d1}) = 80$  ps. Finally, an exponential curve with a slow rising time constant completes the modeling, whit  $\tau_1 = 85$  ps,  $\tau_2 = 8$  ps, and  $(t_{d2} - t_{d1}) = 80$  ps. Figure 8(b) depicts these curves.

Although these three source models fit the observed transients very well, a further simplification may be executed. Figure 8(c) shows a comparison of curves with different particle LETs for LV cells, including a simulation in which no bit-flip has occurred. Based on these and other performed simulations, it was verified that besides the current's peak value, the plateau amplitude and duration are the main parameters of the curve related to bit-flips. Therefore, the component of the later peak from the proposed curve can be removed to simplify the model, though keeping the plateau as shown in Fig. 8(b).

# 4.3 Influence of Resistive Defects on SEU Reliability

In order to evaluate the impact of SEUs on the reliability of the FinFET-SRAMs in the presence of resistive defects, simulations using Hspice<sup>TM</sup> were performed. A FinFET-SRAM cell adopting a 14 nm PTM technology was designed

Fig. 7 Drain current with different charge track lengths implemented with ion far from the drain

Fig. 8 Transient current modeled in spice for (a) HD cell and (b) LV cell and (c) comparison of curves with different particle LETs for LV cell (TCAD)

for simulating the ionizing particle as a current source in the pull-down transistor according to the models presented in the previous Section. The values of  $Q_{exc}$  corresponding to the transient effects ( $Q_{exc\_nom}$ ), the peak current ( $I_{peak}$ ), and the plateau current ( $I_{plateau}$ ) are summarized in Table 6. Note that the values of  $Q_{exc\_nom}$  were obtained by integrating the current pulse, considering the lower values of  $I_{peak}$  that resulted in bit-flips in the SPICE model, and modeling the same value of plateaus observed in TCAD. This way, some variations in  $Q_{exc\_nom}$  were observed when compared to the TCAD model. This difference is observed due to the fact that

different technological parameters for the TCAD model and the SPICE PTM model are applied.

Table 7 shows the observed values of  $R_{crit}$ , along with the values of simulated  $Q_{exc}$  and the correspondent  $I_{peak}$  and  $I_{plateau}$ . The value of  $Q_{exc\_alt}$  was reduced from  $Q_{exc\_nom}$  by 10% to verify if weak defects can reduce the amount of charge needed to cause a bit-flip. For resistive open defects, the critical resistance is the lowest value that results in a bit-flip, considering the reduced value of  $Q_{exc\_nom}$ . For resistive bridges, the  $R_{crit}$  are the highest values that render the cell susceptible to SEUs. The defects marked with '\*' indicate

Table 6 Excess Charge Configuration

| Cell | $Q_{exc\_nom}$ (fC) | I <sub>peak</sub> (μA) | I <sub>plateau</sub> (µA) |

|------|---------------------|------------------------|---------------------------|

| HD   | 1.01                | 63.5                   | -                         |

| LV   | 5.28                | 47.0                   | 31.0                      |

| HP   | 5.46                | 47.9                   | 32.1                      |

that this defect was injected into a different cell's inverter than the transient was injected into.

Looking at Table 8, it is possible to observe that weak resistive defects may indeed modify the cell robustness. DFO2 and DFO4, which are low resistance open defects, as well as DFB2 and DFB6, which represent high resistances for bridge defects, represent this situation where the cell robustness is reduced. Note that the defect sizes adopted represent weak defects, which means that may not be detectable by manufacturing tests, even those able to detect dynamic faults, according to the results in [23].

This paper also investigated what is the nominal value of excess charge necessary for causing a bit-flip in a healthy cell. It was possible to observe that some defects may turn the cell more robust to the SEUs, as shown in Table 8. It is interesting to notice that some defects may have distinct impacts when occurring in the inverter that is affected by the SEU or during their occurrence in the opposite inverter. For example, if DFO2 occurs in the inverter hit by the ion, the bit-flip occurrence is facilitated, while, if it occurs in the opposite inverter, a higher collected charge is needed to turn the event into an SEU.

$\begin{tabular}{ll} \textbf{Table 7} & Weak \ resistive \ defects \ that \ increase \ the \ SEU \ sensitivity \ of \ the studied SRAM \ cells \end{tabular}$

(0)

| $Q_{exc\_alt}$ (fC) | $I_{peak}$ ( $\mu$ A) | $I_{plateau}$ ( $\mu$ A) | $R_{crit}\left(\Omega\right)$  |

|---------------------|-----------------------|--------------------------|--------------------------------|

| 0.909               | 56.0                  | -                        | DFO2=2839                      |

|                     |                       |                          | DFO4*=509                      |

|                     |                       |                          | DFB1 = $1.524 \text{ M}$       |

|                     |                       |                          | DFB2*= $1.680 M$               |

|                     |                       |                          | DFB3&4=710.6 k                 |

|                     |                       |                          | DFB6 = $1.680 \text{ M}$       |

| 4.77                | 41.6                  | 28.0                     | DFO2 = 4351                    |

|                     |                       |                          | DFO4*=920                      |

|                     |                       |                          | DFB1 = $209.5 \text{ k}$       |

|                     |                       |                          | DFB2*= $1.145 \text{ M}$       |

|                     |                       |                          | DFB3&4=106.8 k                 |

|                     |                       |                          | DFB6 = $145.0 \text{ k}$       |

| 4.94                | 43.6                  | 29.1                     | DFO2 = 3480                    |

|                     |                       |                          | DFO4* = 708                    |

|                     |                       |                          | DFB1 = $638.7 \text{ k}$       |

|                     |                       |                          | DFB2*=348.3 k                  |

|                     |                       |                          | DFB3&4=163.1 k                 |

|                     |                       |                          | DFB6 = 348.4  k                |

|                     | 0.909<br>4.77         | 4.77 41.6                | 0.909 56.0 -<br>4.77 41.6 28.0 |

**Table 8** Weak resistive defects that prevent bit-flips, considering the critical excess charge (spice)

| Cell | $Q_{exc\_nom}$ (fC) | $R_{crit}\left(\Omega\right)$ |

|------|---------------------|-------------------------------|

| HD   | 1.01                | DFO2*=2429                    |

|      |                     | DFO3 = 5623                   |

|      |                     | DFO4 = 1603                   |

|      |                     | DFO6 = 2715                   |

|      |                     | DFB2 = 645.1  k               |

|      |                     | DFB3& $4* = 11.30 \text{ k}$  |

|      |                     | DFB6*=645.1 k                 |

| LV   | 5.28                | DFO2* = 7052                  |

|      |                     | DFO3 = 2044                   |

|      |                     | DFO4=4128                     |

|      |                     | DFO6* = 664                   |

|      |                     | DFB2 = 1.322 M                |

|      |                     | DFB3& $4* = 168.3 \text{ k}$  |

|      |                     | DFB6* = $1.322 \text{ M}$     |

| HP   | 5.46                | DFO2* = 310                   |

|      |                     | DFO3 = 132                    |

|      |                     | DFO4 = 4803                   |

|      |                     | DFO5 = 157                    |

|      |                     | DFO6=351                      |

|      |                     | DFB2 = $5.122 \text{ M}$      |

|      |                     | DFB3*& $4$ *=5.036 M          |

|      |                     | DFB6*=5.122 M                 |

#### 5 Final Considerations

This work analyzed the impact of SEUs on the reliability of defective FinFET-based SRAM cells. To accomplish this, three variants of 14 nm FinFET SRAM cells were modeled using TCAD. In a subsequent step, ion strikes were simulated and injected into the modeled cells. As a contribution, the obtained current shapes and the corresponding excess charges for the different design variants (HD, LV, and HP) were modeled.

This work also remarks that physical simulations (TCAD) should be performed if the goal is to evaluate, by simulation, the design sensitivity to a given energy spectrum of incident particles. This phenomenon happens due to a specific SRAM circuit dynamic: a particle with lower LET can result in a higher value of excess charge depending on the layout configuration, as demonstrated in this work. Therefore, SPICE simulations that consider this value as a comparison parameter or as a critical charge (classic simulation method) do not accurately represent the actual memory reliability concerning single events in real radiation environments.

In this work, considering the TCAD simulation data, the HD cell demonstrated to be more robust than HP and LV cells since a higher LET was necessary to trigger a

C-11

(60)

bit-flip. After discussing the suitability of applying the double exponential model to simulate SEE in this technology, the obtained current shapes observed in TCAD were modeled in SPICE. For specific cell configurations and particle energy conditions, the double exponential is still a satisfyingly accurate model, while for other cases, different current models had to be proposed.

Finally, this paper showed that weak resistive defects might indeed affect the behavior of the cell under single events. In fact, some weak defects may turn the cell more prone to SEUs. However, some defects may prevent bit-flips from occurring, considering the LET<sub>th</sub> observed for a defect-free cell, making a higher particle LET necessary to generate an SEU. This ambiguous behavior is explained by the fact that the amount of excess charge due to a single event in SRAMs is highly dependent on the circuit's dynamic response, which indeed may be significantly modified by the occurrence of resistive defects. As future work, we identify that it would be interesting to calibrate the proposed models with empiric experimental data.

**Funding** Open Access funding enabled and organized by Projekt DEAL. This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior – Brasil (CAPES)—Finance Code 001, the Programa de Doutorado Sanduíche no Exterior (PDSE) 2017/2018, process nº 88881.188720/2018-01, and European Union's Horizon 2020 under grant 722325.

**Data Availability** The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

# References

- Harutyunyan G, Tshagharyan G, Zorian Y (2015) Test and repair methodology for FinFET-based memories. IEEE Trans Device Mater Reliab 15(1):3–9

- Hubert G, Artola L, Regis D (2015) Impact of scaling on the soft error sensitivity of bulk, FDSOI and FinFET technologies due to atmospheric radiation. Integr VLSI J 50:39–47

- 3. Baumann R (2005) Soft errors in advanced computer systems. IEEE Des Test Comput 22(3):258–266

- Hamdioui S, Van De Goor AJ (2000) An Experimental Analysis of Spot Defects in SRAMs: Realistic Fault Models and Tests, in Proc. Ninth Asian Test Symp pp. 131–138

- Cardoso Medeiros G, Taouil M, Fieback M, Bolzani Poehls L, Hamdioui S (2019) DFT Scheme for Hard-to-Detect Faults in FinFET SRAMs, in Proc. Eur Test Workshop pp. 1–2

- Royer P, Garcia-Redondo F, Lopez-Vallejo M (2015) Evolution of radiation-induced soft errors in FinFET SRAMs under process variations beyond 22nm, in Proc. of the 2015 IEEE/ACM Int Symp Nanoscale Archit, NANOARCH 2015 pp. 112–117

- Copetti TS, Medeiros GC, Poehls LMB, Balen TR (2017) Analyzing the Behavior of FinFET SRAMs with Resistive Defects, in Proc. IFIP/IEEE Int Conf Very Large Scale Integr (VLSI-SoC) pp. 1–6

- Medeiros GC, Poehls LB, Vargas FF (2016) Analyzing the Impact of SEUs on SRAMs with Resistive-Bridge Defects, in Proc. 29th Int Conf VLSI Des and 15th Int Conf Embed Syst (VLSID) pp. 487–492

- Copetti C, Medeiros GC, Taouil M, Hamdioui S, Poehls LB, Balen T (2020) Evaluating the Impact of Ionizing Particles on FinFETbased SRAMs with Weak Resistive Defects, in Proc. 2020 IEEE Lat Am Test Symp (LATS) pp. 1–6

- van de Goor AJ, Al-Ars Z (2020) Functional memory faults: a formal notation and a taxonomy, in Proc. 18th IEEE VLSI Test Symp pp. 281–289

- Hamdioui S, Van De Goor AJ, Delos Reyes J, Rodgers M (2006) Memory test experiment: Industrial results and data, in IEE Proc. Comput Digit Tech 153(1):1–8

- Hamdioui S, Wadsworth R, Delos Reyes J, Van De Goor AJ (2004) Memory fault modeling trends: A case study, J Electronic Test: Theory Appl (JETTA) 20(3):245–255

- Vatajelu EI, Bosio A, Dilillo L, Girard P, Todri A, Virazel A, Badereddine N (2013) Analyzing resistive-open defects in SRAM core-cell under the effect of process variability, in Proc. 18th IEEE Eur Test Symp (ETS) pp. 1–6

- Nsengiyumva P et al (2017) Analysis of Bulk FinFET Structural Effects on Single-Event Cross Sections. IEEE Trans Nucl Sci 64(1):441–448

- Kim J, Lee JS, Han JW, Meyyappan M (2018) Single-event transient in FinFETs and nanosheet FETs. IEEE Electron Device Lett 39(12):1840–1843

- Baumann RC (2001) Soft errors in advanced semiconductor devices-part i: the three radiation sources. IEEE Trans Device Mater Reliab 1(1):17–22

- Lee S, Kim I, Ha S, Yu CS, Noh J, Pae S, Park J (2015) Radiation-induced soft error rate analyses for 14 nm FinFET SRAM devices, in Proc. 2015 IEEE Int Reliab Phys Symp pp. 4B.1.1–4B.1.4

- Roche P, Palau JM, Bruguier G, Tavernier C, Ecoffet R, Gasiot J (1999) Determination of key parameters for SEU occurrence using 3-D full cell SRAM simulations. IEEE Trans Nucl Sci 46(6):1354–1362

- Burnett D, Parihar S, Ramamurthy H, Balasubramanian S (2014) FinFET SRAM design challenges, in Proc. IEEE Int Conf IC Des Technol no. 512, pp. 6–9

- Guide SDU (2016) Version M-2016.12, Synopsys, Incorporated, Mountain View, CA, vol. 49

- Neisser M, Wurm S (2015) ITRS lithography roadmap: 2015 challenges. Advanced Optical Technologies 4(4):235–240

- ASU "Predictive Technology Model (PTM)." [Online]. Available: http://ptm.asu.edu/

- Copetti TS, Medeiros GC, Poehls LMB, Balen TR (2019) Evaluating the Impact of Resistive Defects on FinFET-Based SRAMs.

IFIP Advances in Information and Communication Technology 500:22–45

- Naseer R, Boulghassoul Y, Draper J, Del Rey M (2007) Critical Charge Characterization for Soft Error Rate Modeling in 90nm SRAM, in Proc. IEEE Int Symp Circuits Syst pp. 1879–1882

- Messenger GC (1982) Collection of charge on junction nodes from ion tracks. IEEE Trans Nucl Sci 29(6):2024–2031

- Black DA, Robinson WH, Wilcox IZ, Limbrick DB, Black JD (2015) Modeling of Single Event Transients with Dual Double-Exponential Current Sources: Implications for Logic Cell Characterization. IEEE Trans Nucl Sci 62(4):1540–1549

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Thiago Santos Copetti graduated in 2012 and received his Master of Science Degree in 2015, both in Electrical Engineering at Pontifical Catholic University of Rio Grande do Sul (PUCRS), Brazil. Recently, in 2020 he did his thesis defense at the Federal University of Rio Grande do Sul (UFRGS). At the moment he starts as a Postdoc at the Chair of Integrated Digital Systems and Circuit Design (IDS) at RWTH University, Germany. His fields of interest include Fault Tolerant Integrated Circuits, Memory Testing, Single Event Upset (SEU) and Negative Bias Temperature Instability (NBTI) Aware, Design of Integrated Circuits and Memories, and emerging technologies, such as memristors.

Guilherme Cardoso Medeiros received his B.Sc. degree from the Pontifical Catholic University of Rio Grande do Sul (PUCRS), Porto Alegre, Brazil, in 2015. He received his M.Sc. degree from the same university in 2017. He is currently a Ph.D. candidate at Delft University of Technology, the Netherlands. His main areas of interest are test strategies for SRAMs, defect and fault modelling for FinFET devices, and emerging memory technologies.

**Mottaqiallah Taouil** received his M.Sc. and Ph.D. degrees in computer engineering from the Delft University of Technology, Delft, the Netherlands. He is currently an assistant professor in the Dependable Nano-Computing Group at the same university. His current research interests include design for test, reliability and security. He published more than 100 papers in these topics.

Said Hamdioui is currently a chair professor and the head of the Quantum & Computer Engineering Department at TU Delft. He received the MSEE and PhD degrees (both with honors) from TU Delft. Prior to joining TU Delft as a professor, Hamdioui spent about seven years in the industry including Intel Corporation (California, USA), Philips Semiconductors R&D (Crolles, France), Philips/NXP Semiconductors (Nijmegen, The Netherlands). His research focuses on two domains:

Dependable CMOS nano-computing (including Reliability, Testability, Hardware Security) and emerging technologies and computing paradigms (including 3D stacked ICs, in-memory-computing).

L. M. Bolzani Poehls graduated in Computer Science at the Federal University of Pelotas (Brazil) in 2001 and received the best thesis award for her work. In the year 2004 she received her Master of Science Degree in Electrical Engineering at Pontifical Catholic University of Rio Grande do Sul (Brazil). During Ph.D. her work was focused on the development of New Techniques for Highly Reliable Systems-on-Chip. In 2008 she received her Ph.D. in Computer Engineering from the Politecnico di Torino (Italy). She holds three postdoctoral titles, the first one accomplished in 2008 in the field of Low Power Design of Integrated Circuits (ICs) at the Politecnico di Torino, the second one in 2010 with focus on Electromagnetic Interference-Aware Systemson-Chip Design at the Pontifical Catholic University of Rio Grande do Sul (Brazil), and the third form the Politecnico di Torino (Italy) achieved in 2013 in the area of emerging technologies. She is Professor of the School of Technology of the Pontifical Catholic University of Rio Grande do Sul (Brazil) and part of the EASE research laboratory, leading the OASiS research group. At the moment she is a senior researcher at RWTH Aachen University working on test and reliability of memristive devices, more specifically she is working identifying new fault models and developing manufacturing testing strategies for Resistive RAMs as well as investigating reliability issues regarding memristive devices. Her fields of interest basically include: Fault Tolerance and Testing of Integrated Systems, Power-, Aging- and Temperature-Aware Integrated Circuits Design and Development of Electronic Design Automation (EDA) tools for optimization of Integrated Circuits, and ultimately testing and reliability of emerging technologies. Among other activities, she continues to serve as technical committee member in many IEEE-sponsored conferences. She is member of the IEEE Latin American Test Symposium Steering Committee and Coordinating Editor of Journal of Electronic Testing: Theory and Application.

Tiago Roberto Balen received his Electrical Engineering degree, MSc and PhD degrees from Federal University of Rio Grande do Sul (UFRGS), Porto Alegre, Brazil, in 2004, 2006, and 2010, respectively. In 2012, he received an important award from FAPERGS (Rio Grande do Sul State Research Fomentation Agency) for the innovative contributions of his PhD thesis. His research interests include analog and mixed-signal test, built-in-self test, programmable analog devices, fault tolerant circuits and radiation effects on electronic systems. He has published more than 50 papers on these topics in important conferences and journals, receiving two "Best Paper Awards" for his contributions. Currently, he is associate professor at the Electrical Engineering department and head of the graduate program on Microelectronics (PGMICRO) of the Federal University of Rio Grande do Sul (UFRGS).