# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

BRENO FANCHIOTTI ZANCHETTA

# Deep Learning in Edge: Evaluation of Models and Frameworks in ARM Architecture

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Advisor: Prof. Dr. Claudio R. Geyer

Porto Alegre February 2022 Zanchetta, Breno Fanchiotti

Deep Learning in Edge: Evaluation of Models and Frameworks in ARM Architecture / Breno Fanchiotti Zanchetta. – Porto Alegre: PPGC da UFRGS, 2022.

122 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2022. Advisor: Claudio R. Geyer.

I. Geyer, Claudio R.. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. João Luiz Dihl Comba Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"If I have seen farther than others, it is because I stood on the shoulders of giants." — SIR ISAAC NEWTON

#### AGRADECIMENTOS

Agradeço a Deus por mais um dia de vida.

Agradeço à minha família, pelo amparo à todas as minhas necessidades materiais, principalmente minha Mãe Jucilene, que nunca desistiu e nem duvidou de mim.

Agradeço aos colegas do Grupo de Processamento Paralelo e Distribuído (GPPD): Prof. Dr. Claudio R. Geyer por sua orientação. Dr. Julio dos Anjos Santos, por sua coorientação, paciência e votos de confiança nos momentos de turbulência. MsC. Kassiano Matteussi, pelas inúmeras lições profissionais, técnicas e acadêmicas. Também por sua dedicação, paciência e amizade, que ajudaram muito a persistir nessa pós-graduação.

Extendo meus agradecimentos à Universidade Federal do Rio Grande do Sul (UFRGS), pela hegemônica conduta em pesquisas científicas, que é exemplo primordial da importância da educação no Rio Grande do Sul, no Brasil e no mundo.

Saúdo o Intituto de Informática da UFRGS (INF) pela organização, determinação, e primosia com que tem auxiliado os estudantes de pós-graduação. Sem vocês o caminho da pós-graduação se tornaria muito maior.

Agradeço aos funcionários de segurança, limpeza, recepção e a todos que eu não conseguir lembrar agora, mas que foram fundamentais para o exercício de minha pesquisa no dia-a-dia. Agradeço também aos professores, pesquisadores, técnicos, servidores, alunos, médicos e psicológos que participaram de minha caminhada, ajudando-me desde assuntos pequenos até às resoluções de situações complexas.

Agradeço ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) por me agraciar com uma bolsa de mestrado com dedicação exclusiva pelo período de 24 meses. Compreendo que, em momentos de tensão política e regressão de valores, estudar tem se tornado um previlégio -infelizmente-. Por isso, extendo meus agradecimentos aos milhões de cidadãos que permitiram esta bolsa por meio de suas contribuições.

Agradeço também ao programa da NVIDIA Grant pela doação de duas unidades de NVIDIA Jetson TX2, permitindo assim a existência de meus experimentos.

Agradeço à minha amiga de graduação Stéphanie Ames por me auxiliar com a escrita final deste trabalho.

Agradeço à minha grande amiga Mariana de Nunes Flores e Silva pelo companherismo, por ter passado as dificuldades comigo sempre acreditando na minha vitória.

Agradeço à União do Vegetal, por me devolver à vontade e à fé que me permitiram estar vivo até hoje.

### ABSTRACT

The boom and popularization of edge devices have molded its market due to stiff competition that provides better functionalities at low energy costs. The ARM architecture has been unanimously unopposed in the huge market segment of smartphones and still makes a presence beyond that: in drones, surveillance systems, cars, and robots. Also, it has been used successfully for the development of solutions for chains that supply food, fuel, and other services. Up until recently, ARM did not show much promise for high-level computation, i.e., thanks to its limited RISC instruction set, it was considered power efficient but weak in performance compared to x86 architecture. However, most recent advancements in ARM architecture pivoted that inflection point up thanks to the introduction of embedded GPUs with DMA into LPDDR memory boards. Since this development in boards such as NVIDIA TK1, NVIDIA Jetson TX1, and NVIDIA TX2, perhaps it finally became feasible to study and perform more challenging parallel and distributed workloads directly on a RISC-based architecture. On the other hand, the novelty of this technology poses a fundamental question of whether these boards are gaining a meaningful ratio between processing power and power consumption over conventional architectures or if they are bound to have reached their limitations. This work explores the Parallel Processing of Deep Learning on embedded GPUs of NVIDIA Jetson TX2 to evaluate the question above comprehensively. Thus, it uses 4 ARM boards, with 2 Deep Learning frameworks, 7 CNN models, and one medium-sized dataset combined into six board settings to conduct experiments. The experiments were conducted under similar environments, all built from the source. Altogether, the experiments ran for a total of 4,804 hours and revealed a slight advantage for MxNet on GPU-reliant training and a PyTorch overall advantage in total execution time and power, but especially for CPU-only executions. The experiments also showed that the NVIDIA Jetson TX2 already makes feasible some complex workloads directly on its SoC.

Keywords: Deep Learning. Embedded-GPU Devices. ARM Evaluation.

# LIST OF ABBREVIATIONS AND ACRONYMS

| AE     | Auto Encoders                                      |

|--------|----------------------------------------------------|

| AI     | Artificial Intelligence                            |

| AM     | Application Metric                                 |

| ARM    | Advanced RISC Machine                              |

| CPU    | Central Processing Unit                            |

| CNN    | Convolutional Neural Networks                      |

| DMA    | Direct Memory Access                               |

| DS     | Data set                                           |

| DL     | Deep Learning                                      |

| EIE    | Efficient Inference Engine                         |

| FFT    | Fast Fourier Transform                             |

| FGPA   | Field-Programmable Gate Array                      |

| FNN    | Feed-forward Neural Networks                       |

| FP     | Footprint                                          |

| GAN    | Generative Adversarial Networks                    |

| GPU    | Graphical Processing Unit                          |

| HM     | Hardware Metric                                    |

| ILSVRC | CImageNet Large-Scale Visual Recognition Challenge |

| LSTM   | Long-Short Term Memory                             |

| ML     | Machine Learning                                   |

| MLP    | Multilayer Perceptron                              |

| MPI    | Message Passing Interface                          |

| RNN    | Recurrent Neural Networks                          |

| SoC    | Service-on-Chip                                    |

# LIST OF FIGURES

| -          | Perceptron Model Architecture (left), Activation Function (right) and  |       |

|------------|------------------------------------------------------------------------|-------|

| 1          | ut (bottom)                                                            |       |

|            | Multi-layer Perceptron (MLP) Architecture                              |       |

| •          | AI Hierarchical Vision                                                 |       |

| -          | Illustrated Example of Convolution                                     |       |

| Figure 2.5 | Graphical Representation of the Models                                 | .25   |

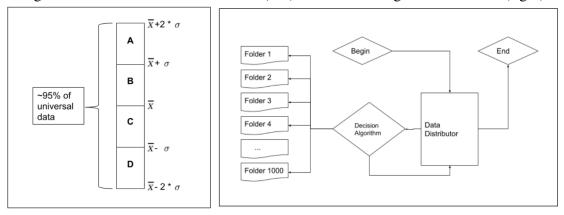

| 0          | Normal Data Distribution (left) and Dataset Algorithm's Model (right)  |       |

| •          | ImageNet Subset Selection Algorithm for Specific Purposes: Pseudocode. |       |

| Figure 4.3 | ImageNet Subset Statistical Analysis: Pseudocode                       | .49   |

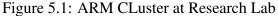

| Figure 5.1 | ARM CLuster at Research Lab                                            | .56   |

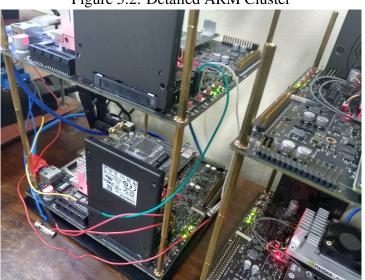

| Figure 5.2 | Detailed ARM Cluster                                                   | .56   |

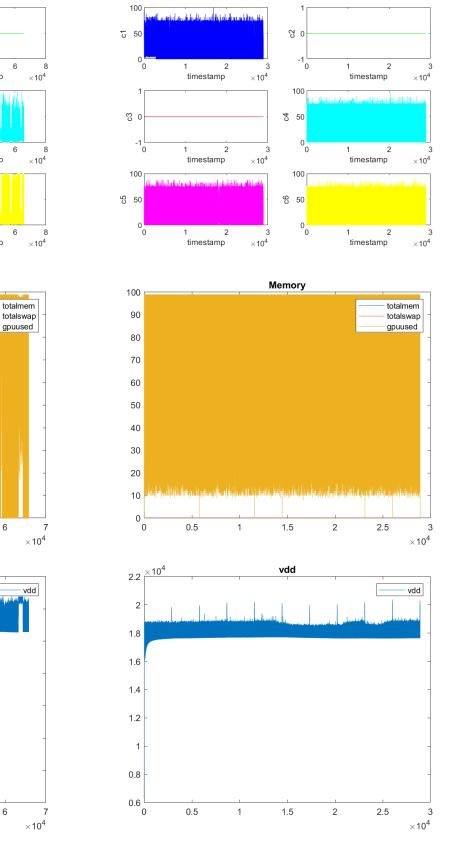

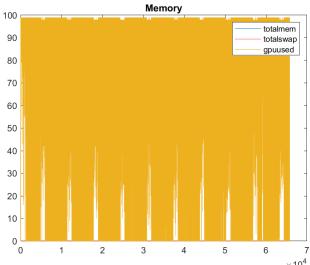

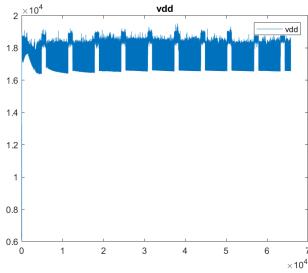

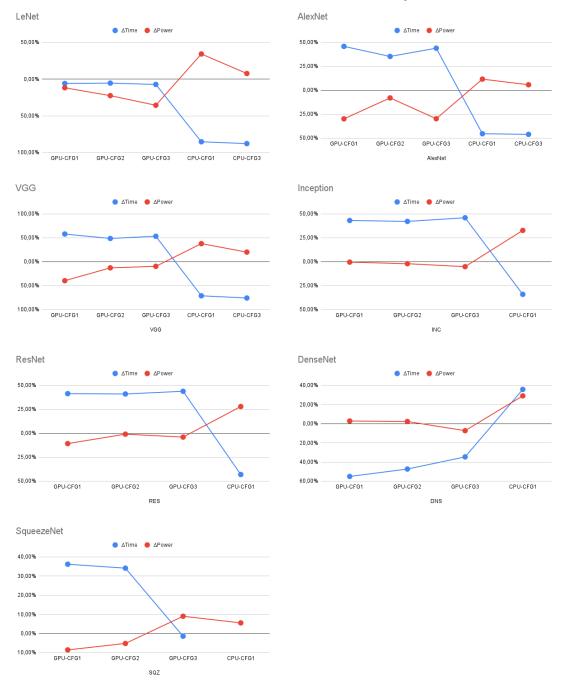

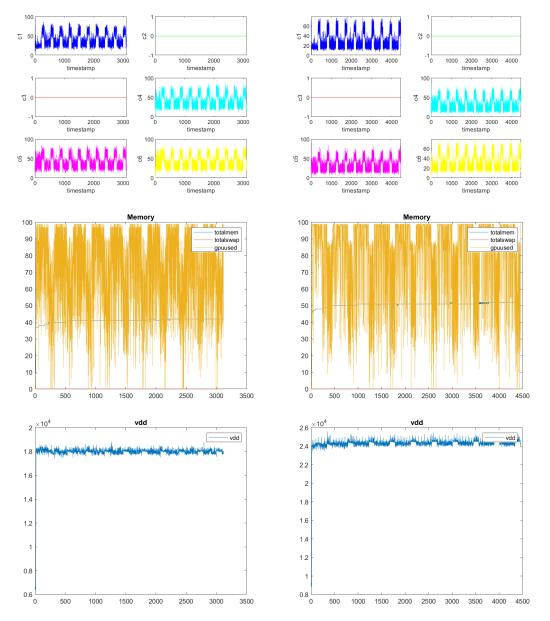

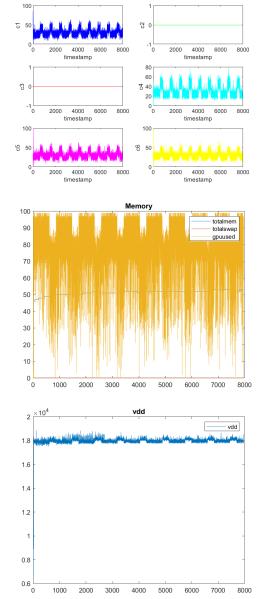

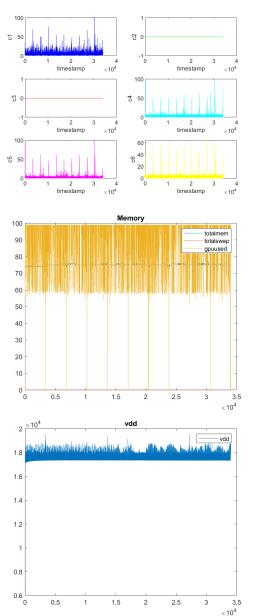

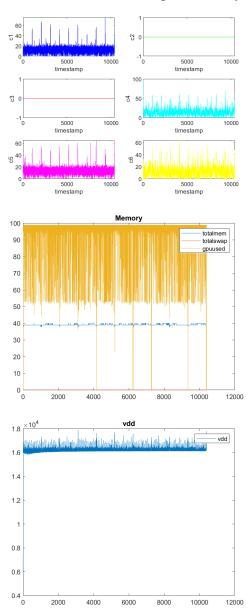

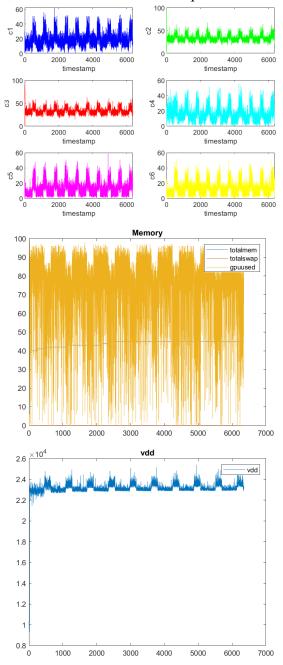

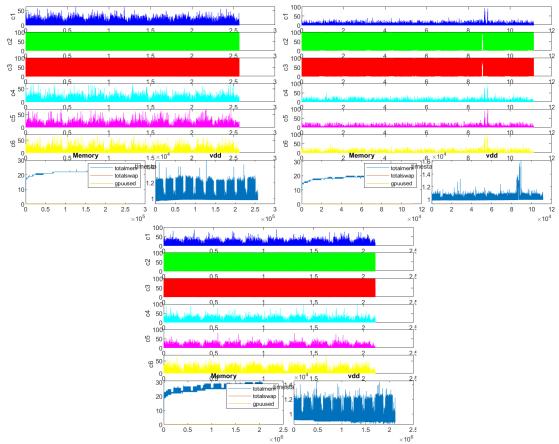

| -          | CPU, MEM and VDD uses for LeNet and AlexNet on MxNet at GPU-           | 0.4   |

|            | 1                                                                      | .94   |

| •          | CPU, MEM and VDD uses for VGG and Inception on MxNet at GPU-<br>1      | 05    |

| Figure 8.3 | CPU, MEM and VDD uses for ResNet and DenseNet on MxNet at -CFG1        |       |

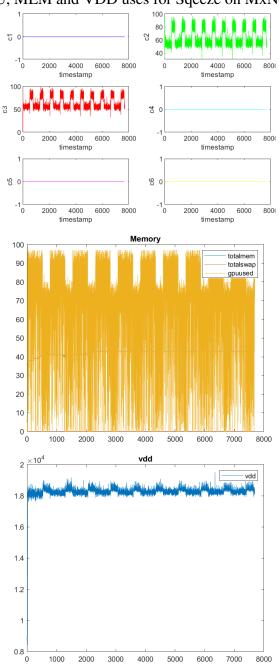

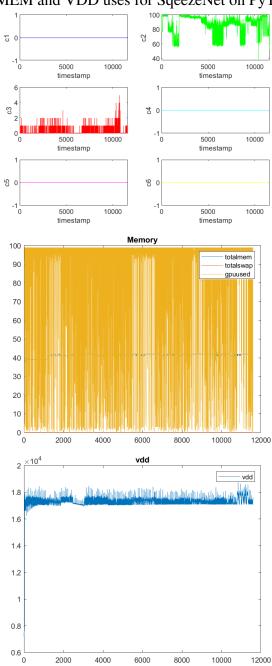

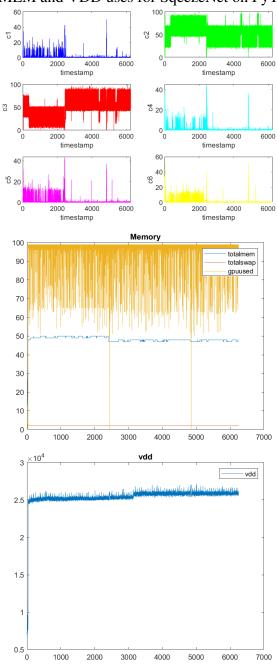

|            | CPU, MEM and VDD uses for SqueezeNet on MxNet at GPU-CFG1              |       |

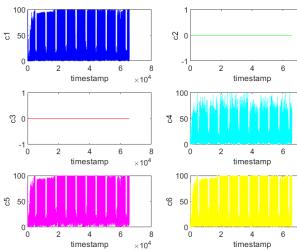

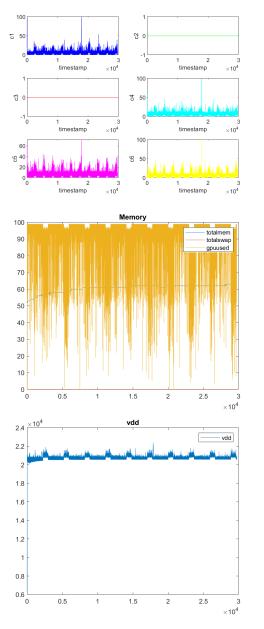

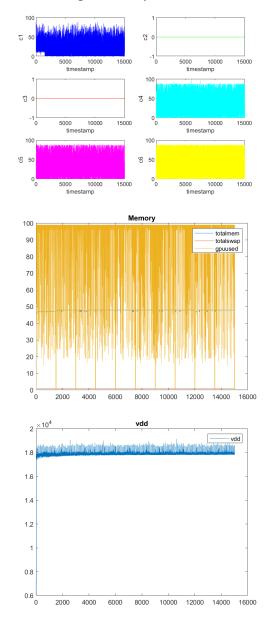

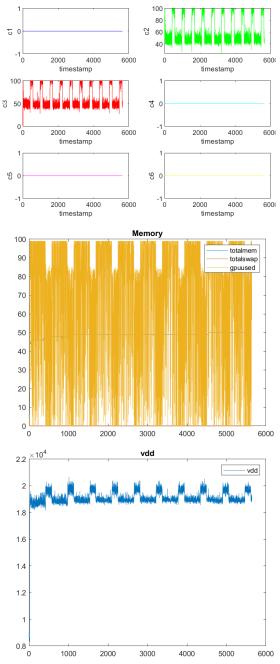

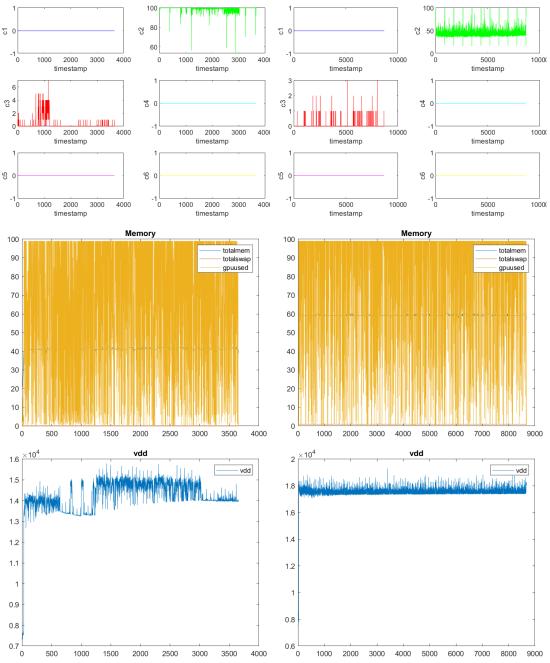

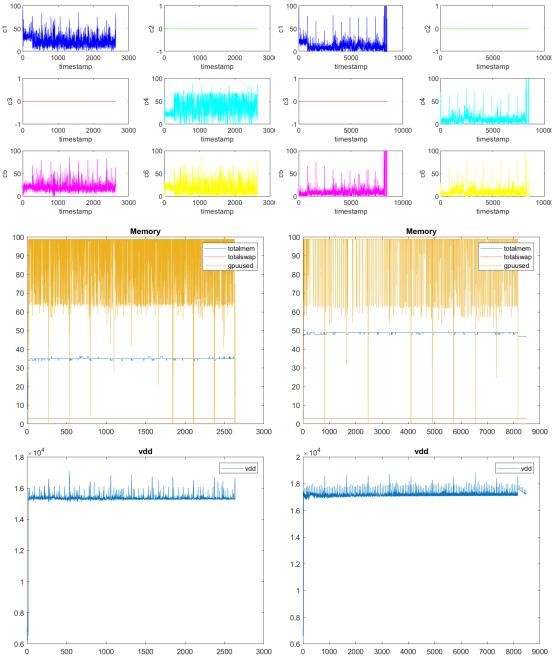

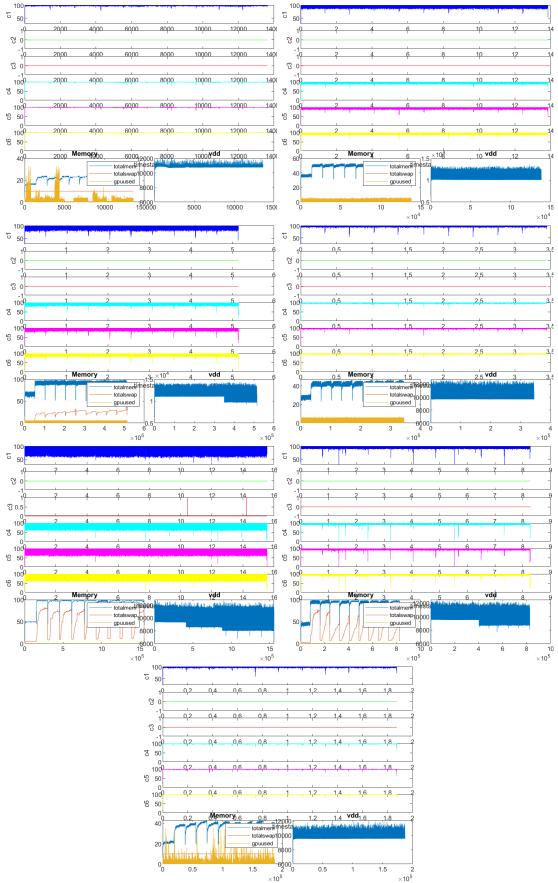

| •          | CPU, MEM and VDD uses for LeNet and AlexNet on PyTorch at GPU-         | . , , |

| U          |                                                                        | .98   |

|            | CPU, MEM and VDD uses for VGG and Inception on PyTorch at GPU-<br>1    |       |

|            | CPU, MEM and VDD uses for ResNet and DenseNet on PyTorch at            |       |

| GPU        | -CFG11                                                                 | 00    |

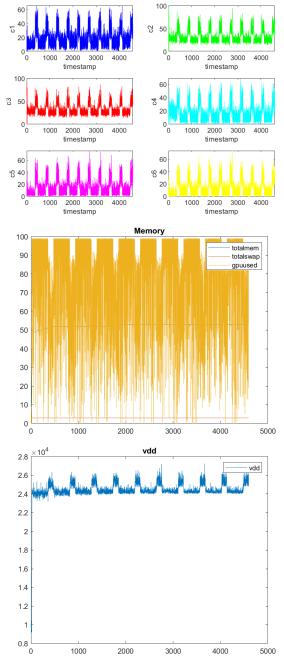

| Figure 8.8 | CPU, MEM and VDD uses for Squeeze on PyTorch at GPU-CFG1               | 01    |

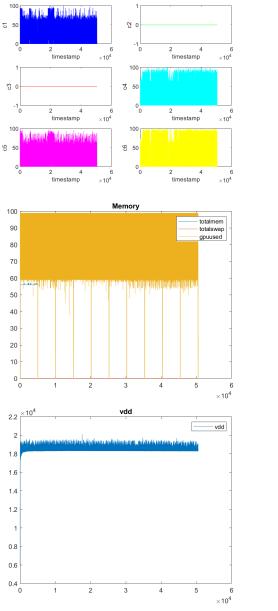

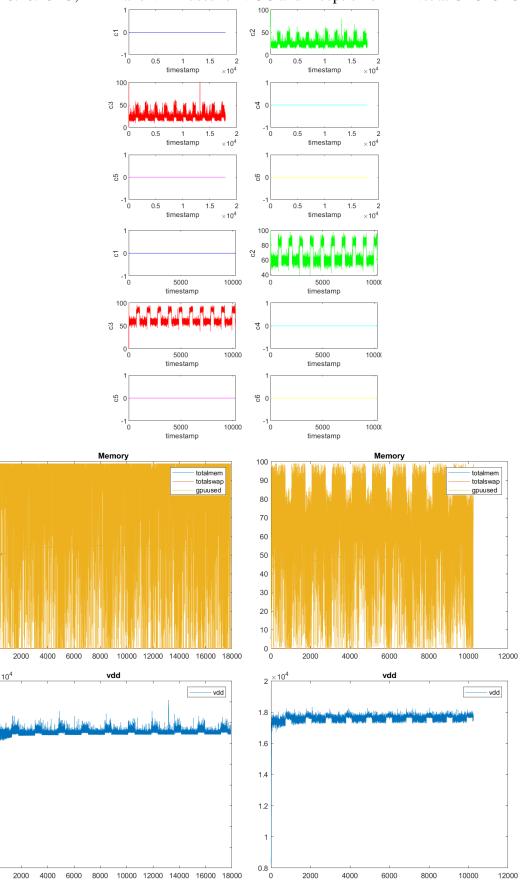

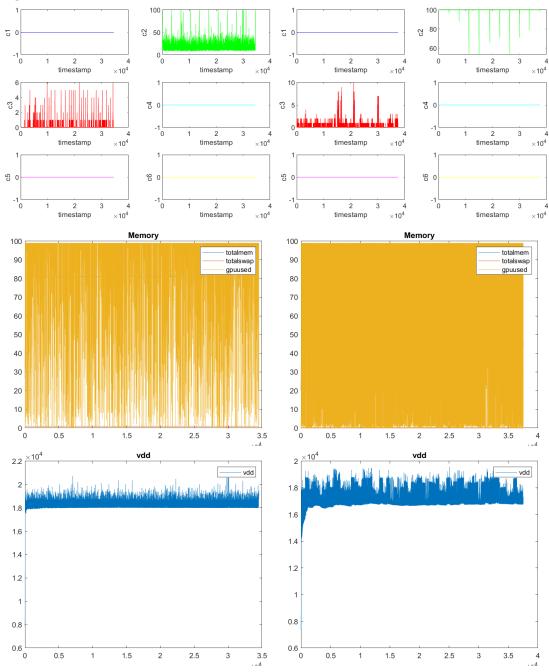

|            | CPU, MEM and VDD uses for LeNet and AlexNet on MxNet at GPU-           |       |

|            | 21                                                                     | 102   |

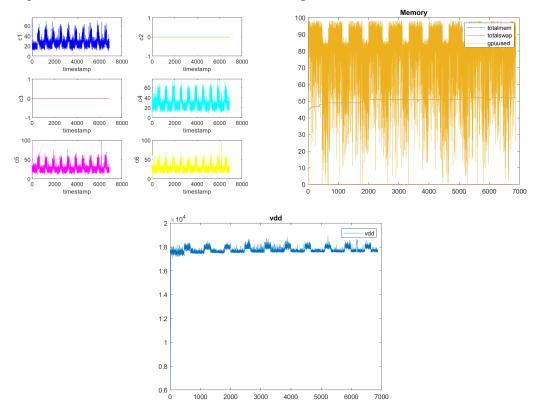

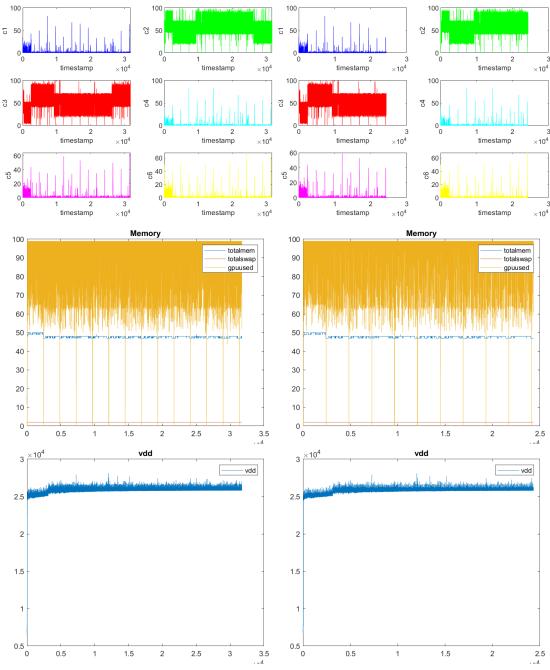

|            | 0 CPU, MEM and VDD uses for VGG and Inception on MxNet at GPU-         |       |

|            | 2                                                                      | 103   |

| U          | 1 CPU, MEM and VDD uses for ResNet and DenseNet on MxNet at            |       |

|            | -CFG2                                                                  |       |

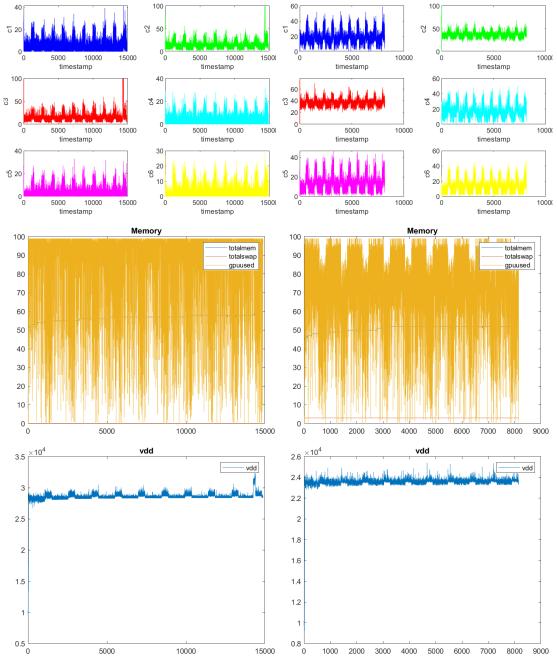

| -          | 2 CPU, MEM and VDD uses for Sqeeze on MxNet at GPU-CFG2                | 105   |

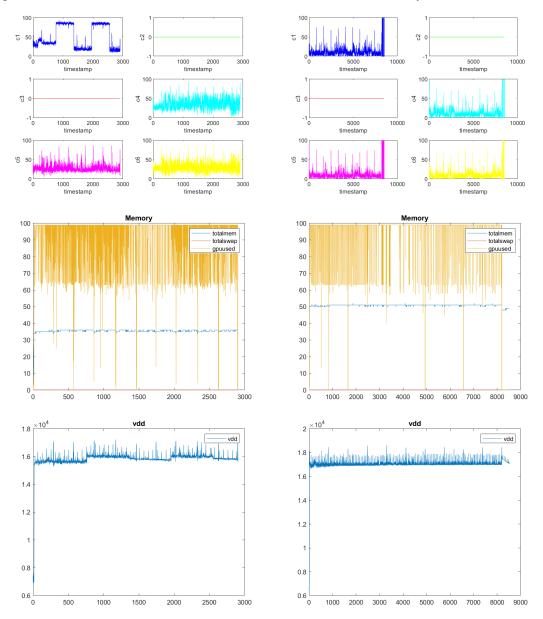

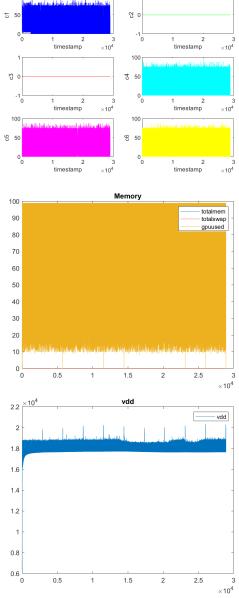

|            | 3 CPU, MEM and VDD uses for LeNet and AlexNet on PyTorch at -CFG2      | 06    |

|            | 4 CPU, MEM and VDD uses for VGG and Inception on PyTorch at            | 100   |

|            | -CFG2                                                                  | 07    |

|            | 5 CPU, MEM and VDD uses for ResNet and DenseNet on PyTorch at          | 107   |

| -          | -CFG2                                                                  | 08    |

|            | 6 CPU, MEM and VDD uses for SqeezeNet on PyTorch at GPU-CFG21          |       |

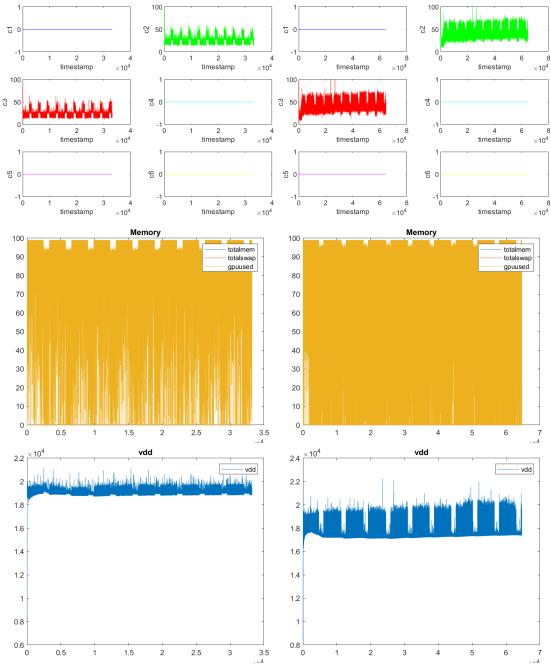

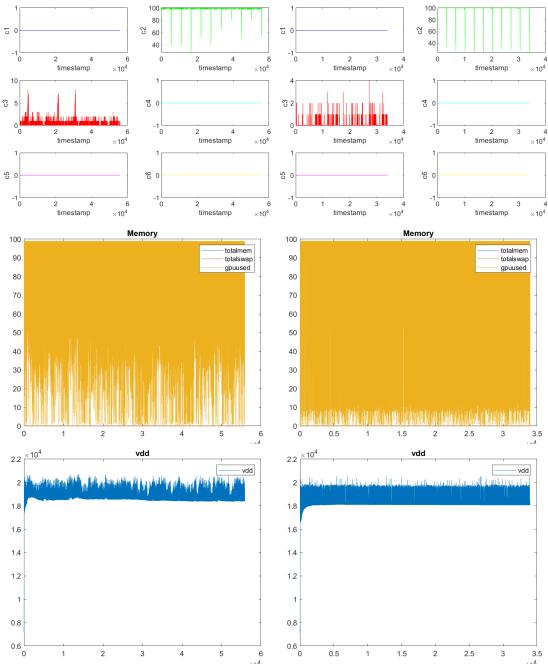

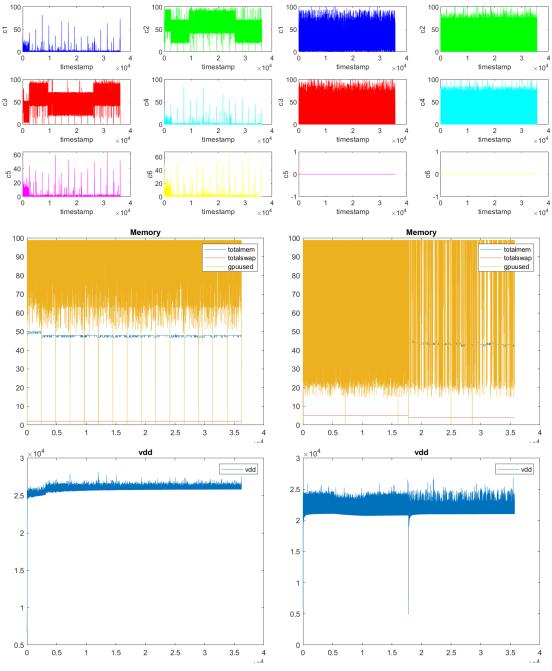

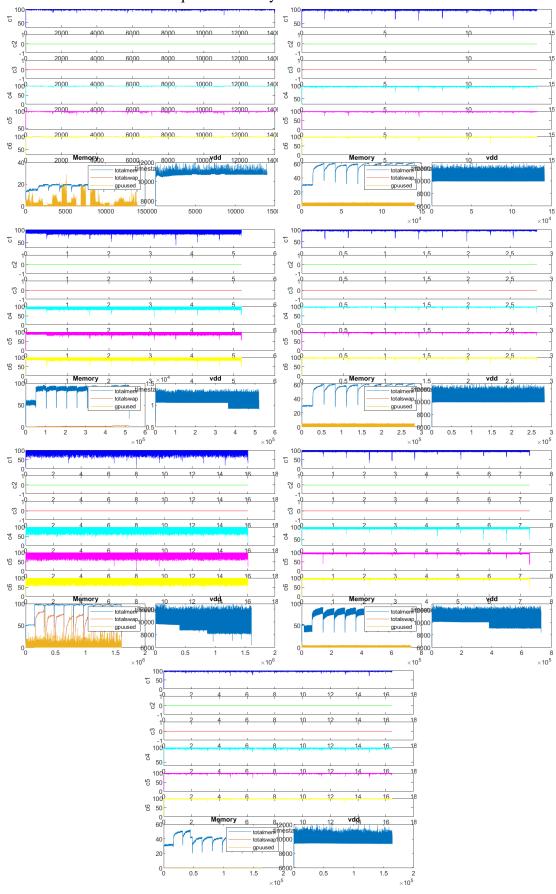

| -          | 7 CPU, MEM and VDD uses for LeNet and AlexNet on MxNet at GPU-         |       |

| 0          | 31                                                                     | 10    |

|            | 8 CPU, MEM and VDD uses for VGG and Inception on MxNet at GPU-         |       |

|            | 31                                                                     | 11    |

|            | 9 CPU, MEM and VDD uses for ResNet and DenseNet on MxNet at            |       |

| -          | -CFG31                                                                 | 12    |

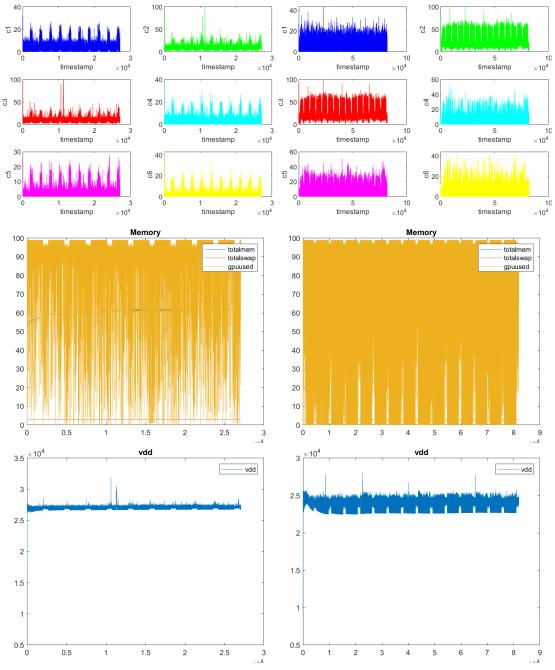

| Figure 8.20 CPU, MEM and VDD uses for Sqeeze on MxNet at GPU-CFG3            | .113 |

|------------------------------------------------------------------------------|------|

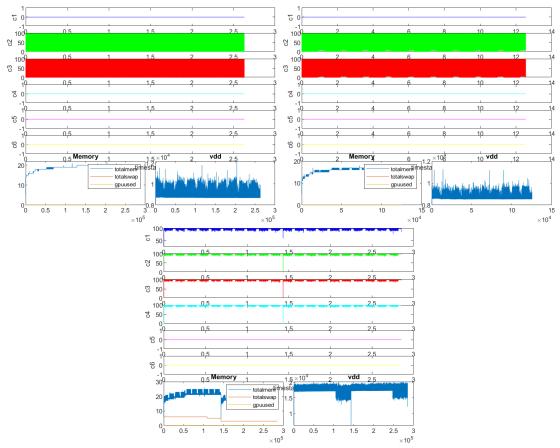

| Figure 8.21 CPU, MEM and VDD uses for LeNet and AlexNet on PyTorch at        |      |

| GPU-CFG3                                                                     | .114 |

| Figure 8.22 CPU, MEM and VDD uses for VGG and Inception on PyTorch at        |      |

| GPU-CFG3                                                                     | .115 |

| Figure 8.23 CPU, MEM and VDD uses for ResNet and DenseNet on PyTorch at      |      |

| GPU-CFG3                                                                     | .116 |

| Figure 8.24 CPU, MEM and VDD uses for SqeezeNet on PyTorch at GPU-CFG3       | .117 |

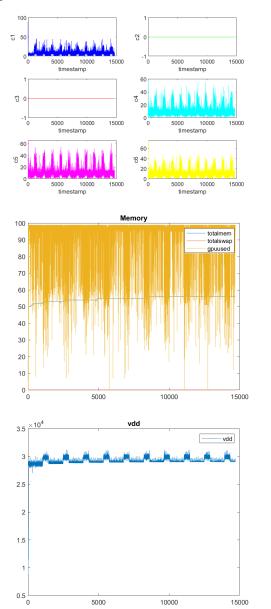

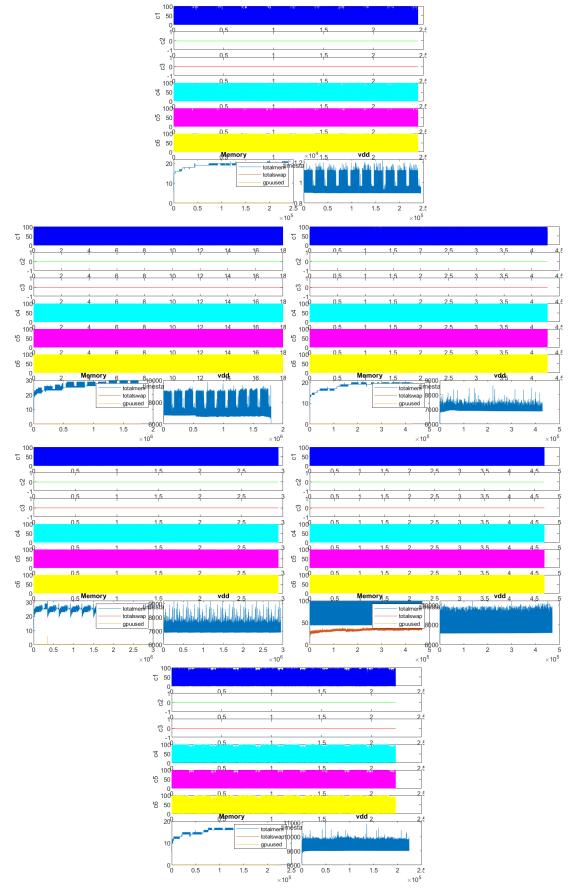

| Figure 8.25 CPU, MEM and VDD uses for LeNet, AlexNet, VGG and Inception,     |      |

| ResNet, DenseNet and SqeezeNet on MxNet at CPU-CFG1                          | .118 |

| Figure 8.26 CPU, MEM and VDD uses for LeNet and AlexNet, VGG and Incep-      |      |

| tion, ResNet and DenseNet and SqeezeNet on PyTorch at CPU-CFG1               | .119 |

| Figure 8.27 CPU, MEM and VDD uses for LeNet and AlexNet, CNN e VGG on        |      |

|                                                                              | 120  |

| Figure 8.28 CPU, MEM and VDD uses for LeNet and AlexNet, CNN e VGG on        |      |

| MxNet at CPU-CFG1                                                            | 121  |

| Figure 8.29 CPU, MEM and VDD uses for LeNet, AlexNet, VGG, Inception, ResNet |      |

| and SqeezeNet on MxNet at CPU-CFG1                                           | 122  |

|                                                                              |      |

# LIST OF TABLES

| Table 2.1    Details of the most used DL frameworks                                | 22 |

|------------------------------------------------------------------------------------|----|

| Table 3.1 Works with DL on SoCs and their Metrics                                  | 40 |

| Table 3.2 Hardware and Datasets of the State-of-the-art                            |    |

| Table 4.1 ARM in Comparison with x86                                               | 45 |

| Table 4.2 Comparison of CNN models - The table presents the most famous CNN        |    |

| models in literature sorted by appearance                                          | 47 |

| Table 4.3 Experiment Metrics, Units, Origins and Types                             | 53 |

| Table 5.1 Hardware Specifications                                                  |    |

| Table 5.2 Model Mapping for Experiments                                            |    |

| Table 5.3 Dataset Size Specification                                               |    |

| Table 5.4 Possible Hardware Configurations                                         |    |

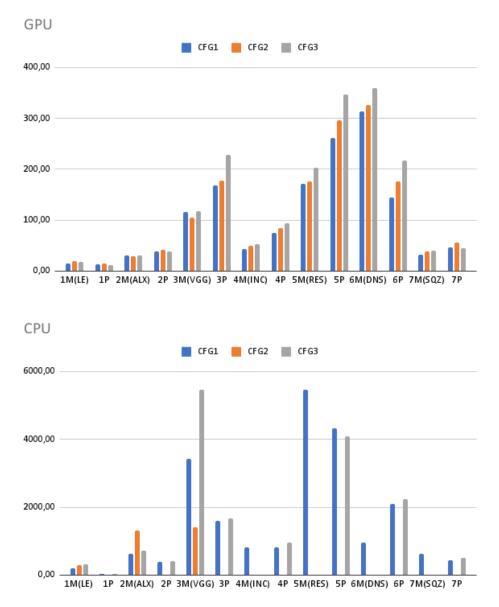

| Table 5.5 Table of Complete List of Experiments in mImageNet10 dataset with Result |    |

| Table 5.6 CNN Models on mImgNet10 - Results at GPU-CFG1                            |    |

| Table 5.7 Ranking and Evaluation for CNN Models on mImgNet10 at GPU-CFG1           | 63 |

| Table 5.8 Hardware Metrics Comparison of CPU (top), Memory (middle) and En-        |    |

| ergy (bottom) for DenseNet in GPU-CFG1 for mImgNet dataset in MxNet                |    |

| (left) and PyTorch (right), respectively                                           |    |

| Table 5.9 CNN Models on mImgNet10 - Results at GPU-CFG2                            | 66 |

| Table 5.10 Ranking and Evaluation for CNN Models on mImgNet10 at GPU-CFG2          |    |

| Table 5.11 CNN Models on mImgNet10 - Results at GPU-CFG3                           |    |

| Table 5.12 Ranking and Evaluation for CNN Models on mImgNet10 at GPU-CFG3          |    |

| Table 5.13 CNN Models on mImgNet10 - Results at CPU-CFG1                           |    |

| Table 5.14 Ranking and Evaluation for CNN Models on mImgNet10 at CPU-CFG1          |    |

| Table 5.15 CNN Models on mImgNet10 - Results at CPU-CFG2                           |    |

| Table 5.16 CNN Models on mImgNet10 - Results at CPU-CFG3                           | 76 |

| Table 5.17 Ranking and Evaluation for CNN Models on mImgNet10 at CPU-CFG3          |    |

| Table 5.18 Compilation of Best Total Time and Average Power Results                | 78 |

| Table 5.19 Best Results Comparison for all Configurations by Model: Above Hor-     |    |

| izontal Line Means Favorable to MxNet and Below Means Better for PyTorch           |    |

| Table 5.20    Total Power Consumption Results                                      |    |

| Table 5.21   Summary of Power Consumption Table                                    | 84 |

|                                                                                    |    |

# CONTENTS

| 1 INTRODUCTION                                           | .11 |

|----------------------------------------------------------|-----|

| 1.1 Problem statement                                    | .12 |

| 1.2 Motivation                                           | .12 |

| 1.3 Objectives                                           | .12 |

| 1.4 Contributions                                        |     |

| 1.5 Work Organization                                    |     |

| 2 BACKGROUND                                             | .15 |

| 2.1 General View                                         | .15 |

| 2.2 Frameworks                                           |     |

| 2.3 Network Types                                        |     |

| 2.4 Models                                               | .25 |

| 2.4.1 CNN                                                |     |

| 2.4.2 Datasets                                           |     |

| 2.5 Background Final Remarks                             |     |

| 3 RELATED WORK                                           |     |

| 3.1 Deep Learning on Desktops and GPU-based SoC          |     |

| 3.2 Deep Learning on Cloud                               | .34 |

| 3.3 Deep Learning Performance Evaluation Towards SoC     | .35 |

| 3.4 Very Similar Related Works                           |     |

| 4 METHODOLOGY                                            |     |

| 4.1 Methodological Approach                              |     |

| 4.2 Research Classification                              |     |

| 5 EXPERIMENTS AND RESULTS                                |     |

| 5.1 Hardware Setup                                       |     |

| 5.2 Software Stack                                       |     |

| 5.3 Workloads                                            |     |

| 5.4 Experimentation                                      |     |

| 5.4.1 Comparison 1: GPU-CFG1 trained and validated at D3 | .61 |

| 5.4.2 Comparison 2: GPU-CFG2 trained and validated in D3 | .66 |

| 5.4.3 Comparison 3: GPU-CFG3 trained and validated in D3 |     |

| 5.4.4 Comparison 4: CPU-CFG1 trained and validated at D3 | .12 |

| 5.4.5 Comparison 5: CPU-CFG2 trained and validated at D3 |     |

| 5.4.6 Comparison 6: CPU-CFG3 trained and validated at D3 |     |

| 5.5 Summary of Comparison Best Results                   |     |

| 6 CLOSING REMARKS AND FUTURE WORKS                       |     |

| 6.1 Closing Remarks                                      |     |

| 6.2 Future Works                                         |     |

| 6.3 Tips of Choice                                       |     |

| 6.4 Acknowledgments                                      |     |

| REFERENCES<br>7 ANNEX 1: RESUMO EM PORTUGUÊS             | .88 |

|                                                          |     |

| 8 ANNEX 2: EXPERIMENTAL HARDWARE PLOTS                   | .94 |

## **1 INTRODUCTION**

The rise in worldwide internet access has led to high web access and content production rates. According to (WEBSITE, ), it is predicted that 3.5 billion people (nearly half the world's population) accessed the internet in 2016. Also, according to the company Internet of Things Analytics <sup>1</sup>, as of this 2019, we already had about 8 billion gadgets connected to the internet, which also reveal the vast potential sources of data creation.

The reasons for this significant number may be linked to the popularization of smartphones and tablet devices. This increase in technology consumption implies market sales competition, which dramatically reduces the cost of purchasing sensor-based technology. These appliances and their sensors may generate spatial position, velocity, acceleration, pictures, videos, and audio. These data are generated in huge volumes at unpredictable rates, which must be dealt with accordingly.

This vast number of sensor-based technologies differ from the traditional x86 architecture in such a way that a new paradigm called Edge Computing emerged. Thus, this paradigm is based on in-situ processing to provide analytics at the data source (FRANKLIN, 2017). Exploring the Locality Principle, this paradigm allows gadgets to relieve some or all of the workload from the cloud, thus alleviating the performance fluctuations that it suffers on high demands.

Also, the study of Edge Computing has been highlighting the increase of gadgets' overall performance and autonomy. Aligned with that, recent strands of cost-effective Graphical Processing Unit (GPU) embedded edge devices have elaborated fertile ground for many complex applications, such as in the field of Artificial Intelligence (AI). It is noteworthy to mention that Deep Learning (DL), a sub-field of AI (GOODFELLOW et al., 2016), adapted well to these Edge devices in tasks such as facial recognition, speech detection, and image processing.

These System-on-Chip (SoC) have been the focus of many recent works, which attest to their advantages in terms of low purchase cost, portability, and high energy efficiency with good performance. However, these SoC evolve rapidly with noteworthy gains but lack experimentation regarding the new boundaries of its evolution.

For instance, the NVIDIA Jetson TX1 and TX2 were released in November 2015 and March 2017 and counted with 4 GB and 8 GB of RAM, respectively. For instance, NVIDIA Jetson Xavier was released in December 2018 with 16 GB of RAM.

<sup>&</sup>lt;sup>1</sup>https://iot-analytics.com/

However, even though these boards evolve at such high speed, there still is a lack of studies that attest to the full potential of these boards on Deep Learning, especially regarding the training of DL models directly on the board.

#### **1.1 Problem statement**

Regarding deep learning execution in embedded systems, it is customary to perform training steps of a deep neural network offline and only deploy it on an embedded architecture. However, there has been an increase in frameworks and applications production in the past few years. This work intends to tackle the following question:

Is it possible to train and deploy deep learning applications at the edge?

There are a few questions that need to be answered in order to respond to this question, such as:

- 1. What are the limits while training DL on embedded platforms?

- 2. What frameworks and models perform the best training and deployment on Advanced RISC Machine (ARM) architecture?

#### **1.2 Motivation**

Since many DL frameworks and models have been created for regular x86 architectures, they face compatibility issues with arm64 and face differences in implementations and optimizations. Thus, it is essential to measure and compare the performance of these frameworks and models under a proper methodological experimental setup.

This work's motivation is to perform a performance evaluation of Deep Learning Frameworks on an ARM-based architecture environment to compare performances and determine the best frameworks, models, and datasets.

#### **1.3 Objectives**

In order to attest to the goals of this work, it seeks to conduct a study of Deep Learning on ARM-based edge devices. In order to do so, specific goals have been assigned:

- To compare practical performances among two famous DL frameworks under a similar and fair environment configuration and upon the same models written similarly from the source.

- To understand the behavior of DL applications on SoC under various performance scenarios.

- To conduct and analyze a performance evaluation with a few famous Convolutional Neural Networks (CNN) models on ARM NVIDIA Jetson TX2.

- To detect limitations and spot a progress curve for CNNs training at GPU embedded ARM devices.

- To determine the best framework and models for embedded ARM devices in complex DL training workloads.

#### **1.4 Contributions**

This work is experimental research that aims to test a combination of DL frameworks, models, and datasets under a parameterized and fair training environment. This experimentation scenario focuses on performing training loads on SoC boards to compare two major frameworks' performance by checking training discrepancies and efficiency limitations.

This work evaluates the feasibility of training and deploying Deep Neural Networks on embedded GPU devices with and without GPU support. These networks are implemented under two different Deep Learning frameworks and focus on training CNNs for computer vision problems.

Also, this work evaluates and compares the performance of these two deep learning frameworks upon similar implementations of the same seven models, using reliable data set on top of the NVIDIA Jetson TX2 embedded platform.

Therefore, this work aims to conduct a performance evaluation study on current embedded GPU devices' most famous CNN models and datasets. Thus this was achieved in an NVIDIA Jetson TX2 cluster with four units using PyTorch and MxNet frameworks, each running of 7 CNN models and one medium-sized dataset into three configurations of CPU and two for GPU, thus totaling six possible hardware configurations.

The experiments revealed a characteristic better behavior for MxNet and another better scenario for PyTorch, both under specific hardware configurations that will be fur-

ther revealed and discussed in this work's experiments.

These experiments measured the impact of intense computations such as CNN models training and validation when processed with PyTorch framework regarding hard-ware metrics such as RAM memory, CPU and GPU utilization, but also investigating software metrics such as total execution time, average execution time per epoch, average power consumption, accuracy, loss, and top5 accuracy.

Besides that, this work has multiple applicable scenarios, such as mitigation systems for general network pane, especially in traffic monitoring systems and robotics (GAYA et al., 2016), and perhaps, also included in spatial technology.

Finally, this work contributed by elaborating a well-defined step-by-step tutorial <sup>2</sup> to aid future Jetson TX2 users to install and configure the board's environments, and also to help anyone who wishes to obtain the codes and organization for experimental research with CNNs.

# **1.5 Work Organization**

To approach all the previously mentioned topics, this work was divided as follows:

- Chapter 2 approaches deep learning background, which includes the entire explanation of techniques, key concepts, models, and frameworks. It is followed by state-of-the-art, which briefs the reader about important contributions to deep learning research in the recent past. After that, the related work subsection unveils the collection of works that attempted on doing similar topics.

- 2. Chapter 3 contains a detailed study regarding the related works to this research topic.

- 3. Chapter 4 contains a theoretical formalization that led to this work's solution and also highlights a few key contributions for this study.

- 4. Chapter 5 describes the test scenarios, specifications, results, and analysis.

- 5. Chapter 6 holds the closing remarks, future works, and acknowledgments.

<sup>&</sup>lt;sup>2</sup>https://github.com/Bfzanchetta/DLARM

### **2 BACKGROUND**

This chapter introduces the essential concepts of Deep Learning. This conceptual section highlights important techniques that evolved into Deep Learning and the current frameworks, such as MxNet and PyTorch, and shows some differences. This section also unravels different network types, models, and data sets for further understanding.

### **2.1 General View**

Over the years, many concepts have been developed on AI, most of which achieved great success on practical issues, such as Image Recognition, Facial Detection, Object Detection, Speech Recognition, Textual Prediction, and much more. Because of the success of this broad spectrum of applications, Deep Learning became a notorious learning option for algorithms.

Computational applications are often developed in logical steps to evolve from static into dynamic solutions, i.e., cancel the need for constant manual adjustments and automatize the so wished process. The desire to guide decision-making and introduce knowledge learning on computational applications guided the development of AI.

Before AI started to be recognized by what is known in current literature, many researchers attempted to introduce knowledge on computational systems. Two distinct approaches tackled different perspectives of acquiring and generating knowledge using logic but differing on specific approaches. Initial methods aimed to represent data as numbers and approximate functions to learn valuable information, while others aimed to store knowledge in databases and create rules of knowledge to guide the algorithm.

The attempt to introduce knowledge manually to the machine was named Knowledge Base Systems. These systems may be described as manual questions and answers tuples, stored in data structures and fed into logic programmable structures, thus generating a static organized base of knowledge. This approach depended on the manual entry of information, so it relied on specialists who could provide correct questions and answers precisely.

The literature cites (LENAT; GUHA, 1989) as one famous case, which presented two significant components: One inference engine and one database of statements in a language called CycL. Human staff entered statements into the database and struggled to develop formal rules of inference so that the algorithm could generate questions that the staff would answer. The staff entered a story about Fred shaving in the morning during the development. The system knew beforehand that people did not have electrical parts, but since Fred was holding an electric razor, the system inferred that "FredWhileShaving" possessed electrical parts. The system then asked whether Fred continued being a person while shaving.

Even though such systems appeared to gain knowledge, the algorithm was not learning because it did not apply self-made or nonlinear computations. Also, since the machine did not learn new information, it was inherent that the complete development of a particular instance of this model would make the specialist who fulfilled its database ultimately obsolete. These facts led this first attempt to fateful disuse. Still, these challenges of hard-coding knowledge demonstrated that it was essential that machines needed a technique to gain their knowledge with pattern extraction from raw data. Thus, the scientific community focused on initiatives that bestowed knowledge acquisition almost entirely to the machine, creating techniques that allowed the creation of techniques known today as Machine Learning (ML).

Almost at the same period as the earlier knowledge experiments, in 1939, with the publication of the Hodgkin-Huxley Model (HODGKIN; HUXLEY, 1939), science learned first-hand about neuron shape and the direction of nervous electrical response. The novelty of neuron cells and their functioning inspired McCulloch and Pitts in 1943 to publish a logical calculus basis for programmable neurons (MCCULLOCH; PITTS, 1943).

By doing so, this publication set formal guidelines that determined how to define and combine neural units in computational terms while also postulating that the neuron would only transmit the signal forward if it surpassed a threshold of inhibition into an excitation value. It was only with the introduction of this work that many researchers could implement computational neurons and thus, start experimenting with AI. Indeed, the bioinspired neuron is still the primary line of thinking and understanding neural networks.

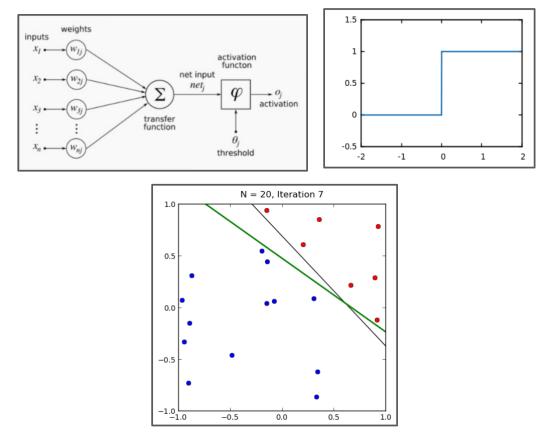

In 1958, Frank Rosenblatt introduced Perceptron (ROSENBLATT, 1958), the first neural model that used a linear function to perform the learning. To do so, the model (seen on Figure 2.1 to the left) multiplies data entries by the Perceptron weight's array and adds this result to a bias columnar array in order to generate an output. This output is passed on an activation function (see Figure 2.1 to the right) on some occasions and then subtracted by the expected output value of the previously annotated entry data to generate a prediction.

Figure 2.1: Perceptron Model Architecture (left), Activation Function (right) and Output (bottom)

The model stops training when the loss achieves a minimum value provided by the programmer, but until then, the training performs alterations on the weights to find great values for them and converge into a solution. It is vital to notice that the entry data is fed into the model, and the training generates an output, fixating a new and unique combination of weight values on the neuron itself. These weights represent the model's contribution that granted real learning to this network against no authentic learning from Knowledge Base Systems.

Finally, Perceptron's initial predictions (see Figure 2.1 at the bottom) on top of two groups of training data started agglutinating into positions that could be split into two distinct groups by at least one line. Thus, the Perceptron proved that it could learn to classify a binary dataset with success, thus gaining the fame of Linear Classifier.

In 1960, Widrow e Hoff published Adaline (WIDROW; HOFF, 1960), a Linear Unit neuron that may be considered as a similar alternative to the Perceptron. Both Perceptron and Adaline performed calculations on data characteristics known as features. They discovered how to linearly separate features into classes into an approach called Logistic Regression. By doing so, they learned how to approximate the best function that separates the data groups. The more complex these learned functions are, the more classes of data it can classify, but it also increases the training complexity and computational costs.

In a nutshell, Perceptron defined the training concept on neural networks that are still being used in the twenty-first century, which symbolizes the action of performing many calculation steps on a structure or object (model) with a training conjunct (data set or dataset) in hopes of regulating this model's parameters to perform a task with such data better. With this new concept, all network successors must contain a training method or function on which the model performs many proceedings to adjust its internal parameters for a very particular task.

Training a network is a pretty straightforward process that culminates on a set of model's internal variables (weights) specialized towards a problem representation and may be exported for later use once it converges. In this way, training mitigated the need to repeat itself every time the application needs to be used. In other words, a programmer who finds the best combination of weights that solves a particular problem may save the configuration for sharing or not. Also, due to the high number of operations over data, training consumes more computational resources and takes more time to finish than any other network proceedings. More details regarding training costs will be discussed further in this work.

The data entry conjunct is called dataset (DS) and is formed by many instances of the data used as input on the training step of the model. Since Perceptron was being developed, there was a great need for generous datasets, for small datasets would provide too little information for the model's adaptation. Datasets may contain images, text, or sounds and may or not present the respective labels which identify to what class a particular instance of the dataset belongs. More details regarding datasets will be discussed further in this work.

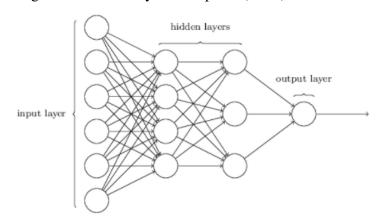

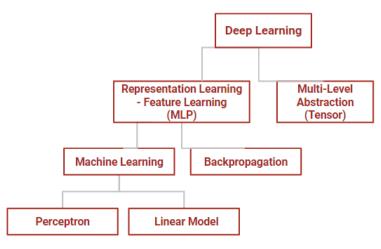

Some complex datasets revealed weak points on Perceptron's ability to converge its model into a complex solution. This problem was mitigated by attaching multiple Perceptron units into a computation graph, also named Multilayer Perceptron (MLP). This combination, seen in Figure 2.2, increased the entire network's time but also enabled the network to learn to classify more classes by dataset and to increase the prediction rates for the same early datasets of a single Perceptron.

Figure 2.2: Multi-layer Perceptron (MLP) Architecture

Also, regarding MLP, the first most remarkable difference from a single Perceptron resides in its architecture. Table 2.2 shows that the first Perceptron units in the MLP layer are responsible for being the first units to receive the input and transform it, thus gaining the name of the input layer. The intermediate Perceptrons receive the result of the input layer and the result of each other until it arrives in the last layer. This middle layer is called the hidden layer, and it is the most responsible for the procedures that engage in the gaining of learning. Finally, the output layer consists of neurons that specialize in classifying the process of the hidden layers into a probabilistic output, which is called the prediction.

This multilayer design fits well in the DL approach because this depth enables sequential learning as minor parts of a unique computer program. Each layer represents a memory footprint of the computer's state prior to the parallel execution of other sets of instructions. In this way, more depth leads to a higher number of instructions being executed in parallel. There are advantages in processing instructions sequentially, for current state instructions may access previous step values to aid in its processing.

The second and last key difference between MLP and early Perceptron resides in how these networks adjust their training. Early Perceptron networks performed a forward training and then conducted changes only in the following training step to reduce the model's prediction loss. MLP, on the other hand, allied Perceptron's logic above with a backward loss adjustment that took place right after a complete forwards pass. This new technique is called backpropagation, and it contributed towards a more significant gain of performance of the neural networks.

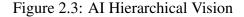

To summarize the evolution of AI, Figure 2.3 shows that Perceptron is the crucial element of Deep Learning, primarily due to its story that started thanks to its ability to separate classes linearly. Then, the concept of Machine Learning started by exploring the Perceptron and its strengths and checking its weakness. By uniting Perceptron with the backpropagation algorithm, the MLP started a field of ML, also called Representation Learning, or Feature Learning. Thus, networks strive to obtain the best weights to learn how to characterize features of the data.

As a solution to solve problems that Representation Learning could not solve, Deep Learning (DL) introduced representations that a combination of simpler ones may express. In this way, DL allows the model to create its complex concepts out of simple concepts. A clear concept of DL cannot be defined only with the definition of the Multilayer Perceptron (MLP), i.e., the MLP consists of a model that combines n-layers of simple Perceptrons, but simply connecting many MLPs only generates another bigger MLP. On the other hand, by allowing the algorithms to create their fundamental matrix of knowledge with the MLP, one must provide the data and let the algorithm develop its own more complex matrices of knowledge, thus increasing the model's representation scope.

For instance, a fundamental self-created matrix of an individual MLP in the hidden layer might learn to identify a point. Then, still without human interaction, the neurons can combine many instances of point with learning a higher concept such as line, or curve, which can then be used to develop even higher concepts such as surfaces, or eyes, or legs, and so on.

Summarizing DL, it may be described as teaching the machine to perform tasks that are intuitive to human beings but very complex to define in algorithms due to their variations. In this way, DL enables machines to learn their concepts and evolve these into more complex concepts, mitigating anomalies and granting more possibilities to the models' scope.

#### 2.2 Frameworks

Until Deep Learning, most models were hard-coded, but with the massive leap of complexity that DL provided, the development of DL frameworks became essential. New open-source frameworks were released to facilitate the implementation, training, evaluation, tests, and predictions on deep neural models.

Several of these frameworks presented special optimizations that could only be found in them. Since all frameworks are open source, developers soon realized how significant specific optimizations were and started doing it themselves. This scenario provided a race for better framework optimizations and tools for visualization. In this section, some of the most noteworthy of these frameworks will be briefed further in Table 2.1.

PyTorch (COLLOBERT; BENGIO; MARIÉTHOZ, 2002) introduces a deep learning tensor library with a series of optimizations, with GPU and Central Processing Unit (CPU). PyTorch has been created over regular Torch. So, it was developed to support Python targeting two main niches: a substitute of NumPy for GPU usage optimization and a deep learning platform with the promise of faster and flexible computations.

MxNet (CHEN et al., 2015) is another widely used DL framework. It is very famous for supporting great flexibility, primarily through viable options in image processing -part of it thanks to its tool Gluon-. This framework is among the pioneers in multi-GPU processing with Deep Learning and keeps good performance with state-of-the-art Convolutional and Long-Short Term Memory (LSTM) models.

Theano was dis-considered for this work because this project has been discontinued. The framework deeplearning4j was opted out of this work because it proved difficult to configure and install, with very confusing, incomplete, and void weblink tutorials.

Caffe and TensorFlow have opted out because they contain too many optimizers and stable releases that turned a simple installation and configuration into a difficult task. Finally, MxNet and PyTorch have very similar scripts, installation steps, sub-packages and match many versions of the sub-packages with little effort, thus reducing the time to install and configure the fair test environment.

| Deep Learning                                | Details                             |                                                       |                                                                                       |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------|

| Frameworks                                   | OS Support                          | PL Implementation                                     | PL Support                                                                            |

| PyTorch (COLLOBERT; BENGIO; MARIÉTHOZ, 2002) | Linux, Android,<br>Mac OS X, iOS    | Lua, LuaJIT, C,<br>CUDA, C++                          | C, Lua                                                                                |

| MxNet (CHEN et al., 2015)                    | Windows, Linux,<br>Mac OS           | C++, Python, R, Julia,<br>JavaScript, Scala, Go, Perl | C++, Python, Julia,<br>Matlab, JavaScript,<br>Go, R, Scala, Perl,<br>Wolfram Language |

| Theano (BASTIEN et al., 2012)                | Windows, Linux,<br>Mac OS, CentOS 6 | Custom C, Python                                      | C/C++, CUDA,<br>OpenCL, PTX,<br>CAL, AVX,                                             |

| Caffe (JIA et al., 2014)                     | Windows, Linux,<br>Mac OS           | C++                                                   | Python, C and C++                                                                     |

| deeplearning4j (GIBSON et al., 2016)         | Windows, Linux,<br>Mac OS           | Java, C, C++, CUDA                                    | Java, Scala, Clojure,<br>Kotlin                                                       |

| TensorFlow (ABADI et al., 2016)              | Windows, Linux,<br>Mac OS           | C, C++, Python                                        | Python, Java, C++,<br>Go                                                              |

Table 2.1: Details of the most used DL frameworks

## 2.3 Network Types

As researches in network design started benefiting from more complex learning functions, advanced optimization algorithms, and model design, scientists felt a necessity to create a taxonomy on deep neural networks' scope. The convention is that each deep model must be separated depending on its primordial operation.

An Artificial Neural Network (ANN), or just Neural Network (NN), may be defined by its purpose. Literature highlights three critical neural networks, which vary in their techniques and computational methods.

The first type of NN is called Feed Forward Neural Networks (FNN), and its history comes from plural attachments of single neurons like MLP into a connected graph. The critical point in this network is the training and optimizer functions that are called back in the training and fine-tuning stages. A simple linear model may be considered FF-type if it does not contain any other networks in its calculations.

This type of network is primitive in the Deep Learning field but still widely used. Since this network is known for its excellent connectivity, the results of co-adjacent units of the same network rely on the processing time of the previous unit, which respectively also depends on all previous connections and their times. For more straightforward tasks and simple networks, training might take less time and cost less -computationally speaking-, whereas higher networks with more connections and higher datasets increase the costs dearly.

Thus, most state-of-the-art networks introduced a technique called dropout, which consists of a rate between zero and one-hundred percent that will be the rate on which the network connections will be disabled during an entire forward network interaction. If the dropout is 0.5 (50%), half the network connections will be randomly turned off during each complete interaction between the input and output layers. This process reduces training time significantly because it forces the network to reinforce the connection between some neurons instead of training the influence of all-to-all paths. The state-of-the-art results show that deep models, especially those with over 1000 neurons in the Fully Connected layer, require some dropout to enable real training time.

CNN is considered one of the essential neural networks, especially in the image processing domain. The most outstanding contribution of this network is the introduction of convolution operations between tensors, which leverages over many matrix operations that would be costly in other techniques. Also, the image processing performed with the aid of the kernel technique boosts the convolution results and improves feature extraction.

For instance, current state-of-the-art convolutional network applications may easily contain over one million units. In this way, most deep networks benefit from parallel computing to perform convolutional and other costly operations.

In practical terms, convolution corresponds to the conversion of the input and kernel to the frequency domain using Fourier transform, performing point-wise multiplication of these two signals and converting back to the time domain by inverse Fourier transform (GOODFELLOW et al., 2016).

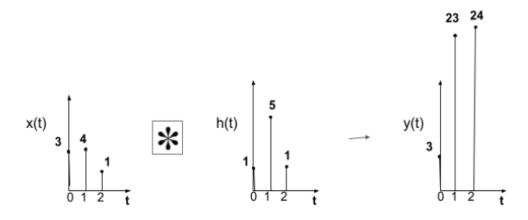

Figure 2.4 shows step-by-step on how the convolution takes place. The picture sample is stored into a data structure which is represented by the discrete pixel values in the x(t) function (to the left of 2.4). It is important to highlight that all discrete t values from x(t), h(t) and y(t) functions do not symbolize time, but simply represent a particular data spot for data representation.

The second element represented by h(t) of the convolution may represent another input data in other cases. However, in this case, it represents the convolutional kernel that will assist the transformation of this data during a specific convolutional layer. More information regarding the used kernels will be described in the next section and Table 4.2. Finally, both the input data (x(t)) and the kernel (h(t)) are processed by an iterative logic described in the captions of Figure 2.4 in order to obtain that particular convolutional result (y(t)).

Furthermore, the output observed in Figure 2.4 reveals the exaggerating effect of the convolutional filters in the input data, i.e., strictly positive kernels enhance all data values. In contrast, kernels with mixed positive and negative values might isolate only specific values. In a nutshell, these impacts of convolution improved the ability of Fully

Connected neurons to acquire more critical weights during training and thus, improved the overall prediction accuracy of neural networks in tasks such as Facial Recognition and Object Detection (GOODFELLOW et al., 2016).

Figure 2.4: Illustrated Example of Convolution

Iteration 1: Retrieve x(0) and the last element of h(t) and multiply them. Thus, (3.1) = 3Iteration 2: Retrieve x(0) and x(1), then multiply them respectively by h(2) e h(1). Then, add the partial results. (3.1) + (4.5) = 23Iteration 3: Multiply the values x(0), x(1) and x(2) respectively by h(2), h(1) and h(0).

Then add the three results. (3.1) + (4.5) + (1.1) = 24

Even though Convolution gives name to complex image recognition AI models, this operations is not new, it is a well-known mathematical operation. However, it still offers great advantages result-wise.

Regarding CNNs, this work unveils three of the basic operations in most Convolutional Neural Networks. A CNN comprises Convolutional Layer, Pooling Layer, or Dense Layer. Convolutional Layers usually take a sub-region of the image to apply a series of filters, kernels, and activation functions to produce a single output - also named a feature map.

Pooling layers serve as a tool to reduce the dimensionality of the data feature map by many computer vision techniques that reduce its size in the case of images. This reduction is made to shorten the processing time of the training steps, mainly because the images of several CNNs are too heavy, and their processing at total capacity takes a lot of computational energy and time, turning the project unfeasible.

The Dense Layer is usually applied in the final stage of the CNN, which contains the aforementioned MLP-based connections. Thus it performs the classification of the features that the convolutional layer enhanced. Theoretically, the more units in the Dense layer, the higher capacity of learning the model has. However, two factors must be accounted for: increasing few dense units causes significant complexity increases in training algorithms, and also, it is known that the excessive addition of neurons in MLP has a roof limit for performance gains.

Several typical applications use CNN, but due to this convolutional kernel, most applications focus on image problems and video -which is a series of images-.

Figure 2.5: Graphical Representation of the Models

FNN (in the left) unites multiple units that perform calculations (training), which modifies weights until their impact on data representation becomes feasible, i.e. it learns to extract features from the data; CNN (in the right) introduces early Computer Vision transformations to facilitate FNNs feature extraction

# 2.4 Models

The development of Deep Learning was fueled by many real-world problems that did not have accurate solutions until then, such as pattern detection, image recognition, image extraction, object detection, speech recognition, and word prediction.

These problems had to be solved by algorithms specializing in one of the solutions mentioned earlier by intensive training. The formal specification of data ingestion and transformation to solve these problems into a programming language is described as a DL model. The subsection below will further explain some of the CNN models used in the further tests.

### 2.4.1 CNN

Many CNN models were proposed in the literature. Among them, this work chose to describe five instances of models in order to attest to a better model choice for experimentation. These chosen models were: LeNet, AlexNet, VGG-16, ResNet, and Inception-V3.

LeNet is the first fruitful convolutional neural network developed in 1990 by Yan LeCunn and served as a precursor of more profound and more complex convolutional networks. Its primary purpose was to identify handwritten digits on zip codes, personal checks, and others. This task is described as classification on literature.

It was updated up to a LeNet5 version, which received 32x32 images and passed them through a convolutional layer that produces six feature maps reduced down to 28x28 bits. Then, these maps are subsampled, producing six feature images measuring 14x14 units in length. Then, it is passed to a further convolutional layer that generates 16 feature maps of size 10x10, followed by second downsampling, which returns 16 feature map units of 5x5 size. Then, the network feeds these 16 feature maps to a first fully connected layer with 120 units, followed by a second 84-units fully connected layer. The output layer contains ten units, which is vital for classifying ten-digit classes.

The differential of LeNet is that it was the first successful convolutional neural network in deep learning, and it introduced a 5x5 convolution filter kernel.

AlexNet was developed in 2012 by a group of researchers from the University of Toronto to classify 1.2 million images into one thousand classes, winning the ImageNet Large-Scale Visual Recognition Challenge (ILSVRC) that year. It takes ImageNet data set images and passes them through 5 convolutional layers, followed by three fully connected layers. The first and second convolutional layers are interleaved with Max Pooling layers only after the fifth convolutional layer.

This model takes 224x224x3 input images then passes them to a first convolutional layer that generates 96 feature maps, followed by a second convolutional layer generating 256 feature maps. Then, these maps are fed to Max Pooling layers, then fed to the third convolutional layer. This third layer is unique because its kernel maps are connected to both kernels from the two groups of feature maps of the second layer, whereas the second, fourth, and fifth layers only consider the previous layer, but not the parallel feature maps. This third convolutional layer contains 384 kernels sizing 3x3x256 connected to the normalized and pooled output from the second layer. The fourth layer possesses 384

kernels of 3x3x192, followed by the fifth convolutional layer with 256 kernels of the same size as the fourth. Then, the 256 feature maps pass through a Max Pooling, only to be fed to three fully connected layers, with 4096 neurons each and a dropout rate of 50%.

It is noteworthy that this model beat the other models on ILSVRC'12 by a considerable margin that year. Its five best predictions revealed a top error of 15.4%, while the second place obtained 26.2% for the same parameters. AlexNet contains more layer groups that may be computed in parallel, such is the fact that it results in a high number of layers, and this consequently demands higher memory than LeNet for intermediate data storage.

The VGG team entry in the ILSVRC-2014 image classification competition designed a 16 layer convolutional network, trained, validated, and tested with the ILSVRC-2012 dataset introducing new properties to convolutional networks.

The VGG-16 model receives RGB images and passes them through a series of convolutional layers with reduced kernel sizes. The authors argue that composing two 3x3 convolution layers, for instance, equals one 5x5 convolution, but with fewer training parameters and increasing nonlinearity due to twice as many ReLU operations. The model comprises two convolutions, max pool, two convolutions, max pool, three convolutions, max pool, three convolutions, max pool, three fully connected layers with two dropouts between them. With a total of 13 convolutional layers and three fully connected, coming to a total of 16 great layers, which justifies the model's name.

Once the training starts, the model receives 224x224x3 input images, then it passes by two convolutional layers of size 3x3, a stride of 1 and pad equals to 1 that produce 64 feature maps each. Then, ReLU activation and max-pooling with a receptive field of 2x2 and stride 2, which stays on the exact configuration for all max pooling operations of the network. The third and fourth layers convolute to generate 128 feature maps each, then applied max-pooling again. This convolutional and max-pooling configuration happens until the last convolution. Then, the fifth, sixth and seventh convolutional layers generate 256 feature maps, followed by max-pooling, followed by another three convolutional layers: the eighth, ninth, and tenth layers, all of which generate 512 feature maps. After these three layers, max-pooling takes place, and then the last three convolutional layers generate other 512 feature maps, namely: the eleventh, twelfth, and thirteenth convolutional layers. A final max pool follows these layers, only directed to three sequential fully connected layers of 4096 neurons with two 0.5 dropouts between them. The model then outputs the SoftMax layer with one thousand classes, thus finishing the training.

This network is significant because the input's volume has reduced spatial dimensions due to both max pooling and convolution. However, the number of feature maps generated on the training increases because kernel filters also increase as the model gets deeper layerwise. This option presents a viable option for DL scientists who focus more on higher datasets with a bit of trade-off to the model's graph training.

Built by Microsoft, ResNet is known for its 152-layers-deep convolutional network for object detection and image classification tasks. This model proved its success in ILSVRC 2015 competition by grating victory with a top error rate of 3.6%, and such an impressive rate represents lower values than the human error rate of 5-10%.

Previous networks were good function approximators. Thus, they learned an identity function f(x)=x that theoretically could be added to a good network without changing the output or compromising the network quality. However, in practical terms, the model needs to train all the network weights simultaneously, so this approach significantly reduced deeper network accuracy rates when combining identity networks. Still, the idea that a small network could learn identity function motivated this work to make this integration plausible. In order to tackle this issue, researchers presaged that by feedbacking the input directly to the output of this small network (f(x)+x), thus making identity mapping nearly optimal and simply allowing solvers to guide the weights of the many nonlinear layers toward zero in order to approach the small network identity mappings. With this crucial concept of a residual block, this work has a greater probability of learning the smaller network's identity function when f(x) equals zero than learning a new deep model's identity function from scratch. It proved a handy technique to train deeper models without degrading accuracy. In ResNet specifically, for every triad of convolution, ReLUs, and convolutional operations, the first convolutional operation's input is passed to the operation's output in the hope of learning the optimal identity mapping. In other networks, the attempt is to fit subjacent mapping to the original input to solve the classification problem.

- ResNet-152 receives 224x224x3 input image, and then the first convolution layer generates 64 feature maps of size 7×7 and stride 2, followed by a max pool of 3x3 and stride 2. Then, the authors described sets of building blocks that correspond to each residual block previously mentioned.

- The first set of building blocks is set with three layers' repetitions: 1x1 convolution generating 64 feature maps, 3x3 convolution generating 64 feature maps, and 1x1

convolution generating 256 feature maps. These three repetitions generate nine convolution layers.

- The second set of building blocks are set with eight repetitions of layers: 1x1 convolution generating 128 feature maps, 3x3 convolution generating 128 feature maps, and 1x1 convolution generating 512 feature maps. These three repetitions generate 24 convolution layers.

- The third set of building blocks are set with thirty-six repetitions of layers: 1x1 convolution generating 256 feature maps, 3x3 convolution generating 256 feature maps, and 1x1 convolution generating 1024 feature maps. These three repetitions generate 108 convolution layers.

- The fourth set of building blocks has three repetitions of layers: 1x1 convolution generating 512 feature maps, 3x3 convolution generating 512 feature maps, and 1x1 convolution generating 2048 feature maps. These three repetitions generate nine convolution layers.

Summing all convolutional layers so far, it comes to 151 convolutional layers. Finally, the model passes by an average pooling, fully connected, and SoftMax layer, 1000 classes.

VGG highly influenced this model because it preserved the decision to use smallersized kernel filters to the detriment of higher dimension kernels. Also, it is essential to mention that ResNet focused more on the residual blocks than on the numbers of neurons in the fully connected layer.

InceptionV3 is a Google convolutional neural network that is one of the state-ofthe-art models of this model's niche. It was designed as a more complex GoogLeNet, winning the ImageNetILSVRC-2014 competition in tasks such as Object detection with additional training data, classification, and localization with provided training data.

The model trained a more profound and broader convolutional neural network on top of the ILSVRC2012 dataset to perform image classification, localization, and object detection with high accuracy. This work introduced an unprecedented contribution: The Inception module. In a nutshell, the Inception module consists of a series of convolutions and max-pooling in a well-defined, parallel, but restricted order. Then, the results of these feature maps are merged later.

After performing a convolution, traditional methods perform either another convolution or a max-pooling in series during intermediate layers. When it comes to InceptionV3, the Inception module generalizes one start point into four parallel flows of convolution and max-pooling of predefined dimensions. These Inception modules may be seen as a process that generates four threads to explore different features from each flow during the filter concatenation phase. Anyone can write a custom Inception module and put it to test however this work introduced the three best modules tested and approved.

- The first Inception module consists of four flows: One flow containing 1x1 convolution, followed by two 3x3 convolutional layers, a second flow with 1x1 and 3x3 convolution, then the third flow with a pool followed by 1x1 convolution, and finally the fourth flow with one 1x1 convolution. It is important to highlight that these flows execute in parallel and have their final feature maps merged in the Filter Concatenation block, where the particular Inception module ends.

- 2. The second Inception module is similar to the first, but with different units of kernels and different sizes, which consists of four flows: The first flow has five sequential convolutional layers, with kernels: 1x1, 1x7, 7x1, 1x7, 7x1. The second flow has three sequential convolutional layers, with kernels: 1x1, 1x7, 7x1. The third and fourth flow remains the same.

- 3. The third Inception module repeats the same logic moreover as the previous two, but adds a sub-flow on flows, the description of their flows is as follows: The first flow has two serial convolutions sized 1x1 and 3x3, and it branches into two parallel 1x3 and 3x1 convolutions. The second flow has a first 1x1 convolution, branching into two parallel 1x3 and 3x1 convolutions. The third and fourth flow remains the same.

It is essential to highlight that these flows execute in parallel and have their final feature maps merged in the Filter Concatenation block, where the particular Inception module ends. This new contribution works because different kernel sizes extract unique granular levels of feature knowledge.

The work's model is presented in a well-defined set of layers: Starts with 3x3 convolution with stride 2, followed by 3x3 convolution with stride one and 3x3 padded convolution with stride 1. Then a 3x3 convolution with stride 2, followed by another 3x3 convolution with stride 1, one 3x3 convolution with stride two, and one more 3x3 convolution with stride 1. The feature maps are passed through 3 units of the first Inception module, followed by five units of the second Inception module and two units of the third Inception module. Concluding the network sequence, the following steps consist of passes on pool, linear, and softmax layers.

This model allows deeper models to be designed without much accuracy reduction while keeping kernel size relatively small and fewer fully connected neurons. The parallel convolutional layer model that Inception explored allowed the development of better networks.

### 2.4.2 Datasets

In order to obtain knowledge towards problem-solving, NNs require samples of data that may be annotated or not called datasets. These data sets may contain many domains and sizes that serve specific purposes, such as images for facial recognition and robotics, sounds for music processing, and texts for natural processing. Some of the most famous image datasets used in CNN models are listed below.

- CIFAR-10 (KRIZHEVSKY; NAIR; HINTON, 2014): it has 60,000 RGB images of 32x32x3 pixels representing 10 groups of animals and vehicles.

- MNIST (LECUN; CORTES; BURGES, 2010): contains 70,000 examples of monochromatic handwritten digits from 0 to 9 in 28x28x1 shape.

- ILSVRC'12 (Imagenet) (RUSSAKOVSKY et al., 2015): divides 1,281,167 RGB pictures (256x256x3) into 1000 classes of objects and animals, containing nearly 144 GB.

The datasets that were used in all related works and the present work, and also the reasons for using them in the present work, will be further discussed in Chapter 4.

#### 2.5 Background Final Remarks

This chapter described a DL overview, followed by its most noteworthy frameworks and network types. The network types section described many of the quintessential concepts of deep neural networks and their operations. Then, the model sections further explained the most famous networks in the state-of-the-art that have been used in this work, followed by an explanation about the datasets. Finally, the next chapter presents the fine-grained study regarding this work's research problem of the related studies.

# **3 RELATED WORK**

Training and evaluating Deep Learning models can be challenging due to hardware and time constraints. In order to address these issues, many works have proposed an evaluation on testing DL models on GPU-based SoC. However, most of these works perform training on x86-based machines with GPU and only validate their models on SoCs, or at the very least perform fine-tuning on the SoC and return to testing. However, some related work studied these DL on SoC by profiling some of the board's critical elements with several exciting strategies. These points were tabled and formed a good strategy for defining some of this work's experimental choices. These works are at this moment summarized.

#### 3.1 Deep Learning on Desktops and GPU-based SoC

Overall, GPUs are more expensive than CPUs; however, they show considerable gains in mathematical computations due to an increase in floating-point arithmetic and fast data processing parallelism. Also, the fast development of complex computer games and simulations engines boosted GPU evolution and availability thanks to market competition and the quick rate of evolution of these components.

Due to these factors, the DL model's processing on GPU dramatically reduced implementation and test times, thus allowing researchers to focus on frameworks and models advancements. Several works decided to take advantage of GPU processing on the Desktop environment to implement their DL solutions (HAN et al., 2016; QI; SPARKS; TALWALKAR, 2016) while recurring to SoC hardware for testing and deployment.

The **Efficient Inference Engine (EIE)** (HAN et al., 2016) [7] was proposed as an inference engine with an accelerator that performs custom multiplication of sparse matrix vectors and optimized weight handling on top of compressed Deep Neural Networks. These deep compressed nets were proposed previously in the literature under the coined term 'Deep Compression,' which essentially allows fitting large DNNs (such as AlexNet and VGGNet) entirely in on-chip SRAM. This compression is achieved by detecting and trimming the redundant connections of the network and by forcing many connections to share the same weight (HAN et al., 2015).

The work EIE evaluated AlexNet, VGGNet, and NeuralTalkLSTM models on Intel Core i-7 5930k desktop for CPU, NVIDIA GeForce GTX Titan X for desktop GPU, and NVIDIA Tegra K1 for mobile GPU. The work tested the models in compressed and uncompressed states on the Caffe framework. The experiments ran on nine benchmarks, and each experiment ran on batch sizes of 1 and 64. Then, they compared these experiments with custom EIE implementation. They were evaluated in function of performance -Computation Time (S), Gigaoperations per second (GOP/s) and speedup -, energy (economy generated by redundant operation removal) and design space exploration (which leverages Queue Depth, SRAM Width, and Arithmetic Precision).

This work is significant for SoC research because it belongs to a group of a select few that provide training test results. In contrast, other works focus primarily on finetuning models trained on the cloud or GPU desktops on the SoC due to its relatively shorter time to prepare a model that was already trained. However, that was not the case because EIE aimed to validate the way models responded to their engine even on SoC, thus contributing to its research.

**Paleo** (QI; SPARKS; TALWALKAR, 2016) [9] introduces an analytically performance model of deep learning frameworks. Its authors argue that each model's architecture carries declarative constraints related to its particular programming techniques on a training and evaluation basis. They also argue that these constraints may be extracted and mapped on hardware, software, and network guidelines to better scalability and performance evaluation. In order to do this, it uses techniques such as Hardware Acceleration, Software Acceleration, Parallelism, and Communication Schemes.

In this way, Paleo executes CNN experiments with AlexNet and VGG-16 while comparing TensorFlow's native metrics with their own regarding backward and forward pass-time (ms) in a 4GB NVIDIA TITAN X GPU desktop environment.

They also executed tests with NiN model, Inception V3, and AlexNet in Caffe, TensorFlow, and Cuda-convnet2 frameworks, respectively, and executed on NVIDIA K20X, NVIDIA K20, and NVIDIA K20 desktops, respectively. These tests aimed they describe in the results several graphics of comparison between Paleo and these frameworks, projecting future collaborations to readers.

Further experimentation tested NiN with FireCaffe instead of Paleo's Train Time and Speedup measurements, permutated on four scenarios with different workers and batch sizes on a Titan single-GPU hardware.

Also, they executed a prediction on Hybrid parallelism and Data parallelism (Train time in hours and speedup) instead of other work's AlexNet to validate Paleo on a desktop with 8 GPUs.

Finally, they conducted Generative Adversarial Networks (GAN), AlexNet, and Inception model evaluations on multiple server clusters with NVIDIA K80 GPUs linked through a 20 Gbps network. They oscillated the batch size number of workers and measured its effects on accuracy and speedup. This single experiment may classify this work as Cloud-based. However, it was a minority on the total experiments. Therefore it was classified as desktop-based.

The Paleo Project is significant due to its fine-grained performance evaluations and many frameworks and models. However, their more notable shortcomings relate to how vaguely they studied this vast amount of models and frameworks against one another. In other words, their work approaches many parts of deep learning, which gives readers perception of excellent workload volume. However, they only permute its variables on a select few states, which subsequently contradicts the reader's earlier notion.

### 3.2 Deep Learning on Cloud

Cloud computing allows users to purchase on-demand resources online and run applications with real-time monitoring of Memory, CPU power, GPU power, and storage capacity. It leverages the scalability, allowing the user's infrastructure to grow -horizontal and vertical growth- or reduce based on the user's demand or pre-configured preemptive settings.

The most significant upside of hiring Cloud computing revolves around the cost of such infrastructure. It costs less to instantiate a cloud virtual machine on a highperformance infrastructure than to purchase, install and maintain the physical cluster itself. The main bottleneck on Cloud computing refers to the network -mainly on the user's end since the traffic becomes essential to manipulate, transfer and monitor data and applications processed in the Cloud's infrastructure, as opposed to *in situ* which usually incurs in fewer network contentions.

Also, due to GPU's high purchasing costs, cloud providers implemented solutions that leveraged multiple powerful GPU cards allied with memory boosts, thus generating the GP-GPU clusters. These GP-GPUs can arbitrarily execute code as opposed to just executing rendering sub-routines, as it was performed until then (GOODFELLOW et al., 2016). NVIDIA's new programming language, CUDA, introduced this advancement, which allowed high-scale parallelism with higher memory bandwidth. Not long after its creation, this platform started being used on DL's research (CIREŞAN et al., 2012;

#### RAINA; MADHAVAN; NG, 2009).

The article (ICHINOSE et al., 2017) [6] regards cloud technologies privacy, with a specific experiment on sensor pieces of equipment towards pipeline processing in the Cloud. It proposes utilizing the Caffe framework, with a client symbolized by Raspberry Pi and the cloud server represented by GPGPU NVIDIA GeForce GTX 980. The analysis was conducted on a single feed-forward neural network: CIFAR-10 on the CIFAR-10 dataset.

The article confirmed that it was still more advantageous to perform the entire deep learning training workload on the Cloud than running it on the device itself at the time of this study. The results also showed how the limitations of Raspberry Pi in terms of graphical processing and non-volatile memory have greatly affected the experimental design on SoC.

### 3.3 Deep Learning Performance Evaluation Towards SoC

The work (ZHANG; WANG; SHI, 2018) [1] was conducted with the intent of testing multiple Deep Learning frameworks, alongside a few models on top of mobiles such as MacBook Pro, Intel FogNode, NVIDIA Jetson TX2, Raspberry Pi, and Nexus 6P. Amongst these Deep Learning frameworks, one may find TensorFlow, Caffe2, MXNet, PyTorch, and TensorFlow Lite. The latency, energy consumption, and memory foot-print were measured in two experiment cases. The models executed on CNN cases were AlexNet and SqueezeNet but in limited combinations of the previously mentioned frameworks and devices.

The work was very generalist regarding the choice of frameworks and devices, but it failed to mention the data sets. The training and validation methodologies were also not mentioned, just as the explanations regarding the metrics extraction. The article moves so quickly on the methodology section that it fails to explain if the training routines were executed in batches, their sizes, and these choices motivations. However, it is a very broad-sighted work that must be recognized for its contributions to many-to-many experiments with frameworks and devices.

The work (TAYLOR et al., 2018) [2] evaluates the performance of Inception, ResNet, and MobileNet CNN models with the ILSVRC 2012 dataset. The experiments ran on TensorFlow and NVIDIA Jetson TX2 hardware, proposing an evaluation of these models with a self-implemented machine learning algorithm based on KNN. The work used inference time, energy consumption, accuracy, precision, recall, and F1-score as validation metrics to compare their implementation and the two CNN models.

Also, (ESHRATIFAR; PEDRAM, 2018) [3] revealed how DNN has gained more practical utilities in the last few years. Amongst those networks, the work cites iPhone's Siri algorithm that executes DNN models on the Cloud. They argue that data transfer from mobile phones to the Cloud at all times is costly in terms of battery, 3G, and 4G wireless transfers.