## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### MATEUS BERNARDINO MOREIRA

# **Low Power Digitally Controlled Oscillator for IoT Applications**

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Advisor: Prof. Dr. Sergio Bampi Coadvisor: Dr. Filipe Dias Baumgratz

#### **CIP** — **CATALOGING-IN-PUBLICATION**

#### MOREIRA, MATEUS BERNARDINO

Low Power Digitally Controlled Oscillator for IoT Applications / MATEUS BERNARDINO MOREIRA. – Porto Alegre: PGMICRO da UFRGS, 2021.

84 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2021. Advisor: Sergio Bampi; Coadvisor: Filipe Dias Baumgratz.

1. Low-power design, low-voltage, digitally controlled oscillator (DCO),transformed-based oscillator, Unified Current-Control Model (UICM), Internet-of-Things. I. Bampi, Sergio. II. Baumgratz, Filipe Dias. III. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos André Bulhões Mendes

Vice-Reitora: Prof<sup>a</sup>. Patricia Pranke

Pró-Reitora de Ensino: Profa. Cíntia Inês Boll

Vice Pró-Reitor de Pós-Graduação: Prof. Júlio O. J. Barcelos

Diretora do Instituto de Informática: Profa. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Primeiramente gostaria de agradecer a Deus por tudo. Por toda a provisão, por me sustentar todos os dias da minha vida e por me proporcionar a conclusão do meu mestrado.

À minha esposa, Mariane, por sempre me apoiar, me incentivar e estar sempre ao meu lado nos momentos difíceis. Seu apoio fez toda a diferença durante todas as etapas dessa conquista.

Aos meus pais, Altamir e Eronita, por todo o suporte durante esta trajetória e durante a vida. Por sempre me motivarem a seguir em frente e correr atrás dos meus objetivos. Por todo auxílio e orações sempre.

Ao meu irmão, Cristiano, minha cunhada Suéllen, por me encorajarem sempre da melhor forma e fazerem sempre parte das minhas conquistas.

Aos meu sogros Nazáre e João, bem como meus cunhados, por todas as orações, incentivos e compreensão ao longo desse percurso.

À minhas aVós Maria, Lica e Antônia, que me servem como exemplos de motivação e força, por todo apoio e orações sempre.

Ao meu orientador Professor Dr. Sergio Bampi e ao meu co-orientador Dr. Filipe Dias Baumgratz por terem me fornecido esta oportunidade, pela orientação e, conhecimentos compartilhados que me guiaram a esta conquista. Ao Professor Sandro Binsfeld da UNISINOS por todo auxílio e discussões técnicas que me ajudaram muito durante meu mestrado.

Aos meus colegas dos Laboratórios 110, 217 e 215 da UFRGS, pela amizade, ajuda e momentos de descontração que contribuíram para essa tragetória tornando-a mais leve. Ao meus antigos colegas da extinta FLORIPA-DH, Roddy, Alberto e Juan pela amizade e conhecimentos partilhados ao longo deste caminho.

À CAPES e à FAPERGS pelo auxílio financeiro que possibilitaram a execussão do meu mestrado.

#### **ABSTRACT**

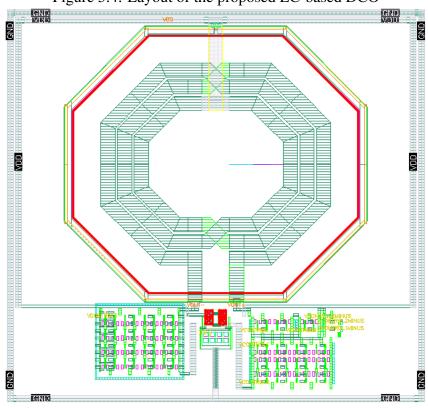

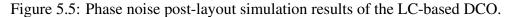

This work is focused on the design of a Low Power CMOS DCO for IEEE 802.11ah in IoT applications. The design methodology is based on the Unified current-control model (UICM), which is a physics-based model and enables an accurate all-region model of the operation of the device. Additionally, a transformer-based resonator has been used to solve the low-quality factor issue of integrated inductors. Two digitally controlled oscillators (DCO) have been implemented to show the advantages of utilizing a transformedbased resonator and the methodology based on the UICM model. These designs aim for the operation in low voltage supply (VDD) since VDD scaling is a trend in systems-onchip (SoCs), in which the circuitry is mostly digital. Despite the degradation caused by VDD scaling, new RF and analog circuits must deliver similar performance of the older CMOS nodes. The first DCO design was a low power LC-tank DCO, implemented in 40nm bulk-CMOS. The first design presented a DCO operating at 45% of the nominal VDD without compromise the performance. By reducing the VDD below the nominal value, this DCO reduces power consumption, which is a crucial feature for IoT circuits. The main contribution of this first DCO is the reduction of VDD scaling impact on the phase-noise do the DCO. The LC-based DCO operates from 1.8 to 1.86 GHz. At the maximum frequency and 0.395 V VDD, the power consumption is a mere 380  $\mu$ W with a phase-noise of -119.3 dBc/Hz at 1 MHz. The circuit occupies an area of 0.46 mm<sup>2</sup> in 40 nm CMOS, mostly due to the inductor. The second DCO design was a low-power transformer-based DCO design, implemented in 28nm bulk-CMOS. This second design aims for the VDD reduction to below 0.3 V. Operating in a frequency range similar to the LC-based DCO, the transformer-based DCO operated with 0.280 V VDD with a power consumption of 97  $\mu$ W. Meanwhile, the phase-noise was -101.95 dBc/Hz at 1 MHz. Even in the worst-case scenario (i.e., slow-slow and 85°C), this second DCO was able to operate at 0.330 V VDD, consuming 126  $\mu$ W, while it keeps a similar phase-noise performance of the typical case. The core circuit occupies an area of 0.364 mm<sup>2</sup>.

**Keywords:** Low-power design, low-voltage, digitally controlled oscillator (DCO), transformed-based oscillator, Unified Current-Control Model (UICM), Internet-of-Things.

#### **RESUMO**

Este trabalho objetiva o projeto de um DCO de baixa potência em CMOS para aplicações de IoT e aderentes ao padrão IEEE 802.11ah. A metodologia de projeto é baseada no modelo de controle de corrente unificado (UICM), que é um modelo com embasamento físico que permite uma operação precisa em todas as regiões de operação do dispositivo. Adicionalmente, é utilizado um ressonador baseado em transformador visando solucionar os problemas provenientes do baixo fator de qualidade de indutores integrados. Para destacar as melhorias obtidas com o projeto do ressonador baseado em transformador e com a metodologia baseada no modelo UICM, dois projetos de DCO são realizados. Esses projetos visam a operação com baixa tensão de alimentação (VDD), uma vez que o escalonamento do VDD é uma tendência em sistemas em chip (SoCs), em que o circuito é majoritariamente digital. Independente da degradação causada pelo escalonamento de VDD, circuitos analógicos e de RF atuais devem oferecer desempenho semelhante ao alcançado em tecnologias CMOS mais antigas. O primeiro projeto foi um DCO de baixa potência com tanque LC, implementado em tecnologia bulk-CMOS de 40nm. O primeiro projeto apresentou uma operação a 45% do VDD nominal sem comprometer o desempenho. Ao reduzir o VDD abaixo do valor nominal, este DCO reduz o consumo de energia, que é uma característica crucial para circuitos IoT. A principal contribuição deste DCO é a redução do impacto do escalonamento do VDD no ruído de fase. O DCO com tanque LC opera de 1,8 a 1,86 GHz. Na frequência máxima e com VDD de apenas 0,395 V, o consumo de energia é  $380 \,\mu\text{W}$  e o ruído de fase é -119,3 dBc/Hz a 1 MHz. O circuito ocupa uma área de 0.46 mm<sup>2</sup> em processo CMOS de 40 nm. O segundo projeto foi um DCO de baixa potência baseado em transformador, implementado em tecnologia bulk-CMOS de 28nm. Este projeto visa a redução de VDD abaixo de 0,3 V. Operando em uma faixa de frequência semelhante ao primeiro DCO, o DCO baseado em transformador opera com VDD de 0,280 V e com consumo de potência de 97  $\mu$ W. O ruído de fase foi de -101,95 dBc/Hz a 1 MHz. Mesmo no pior caso de processo, este DCO opera a um VDD de 0,330 V, consumindo 126  $\mu$ W, com o ruído de fase semelhante ao caso típico. O circuito ocupa uma área de 0.364 mm<sup>2</sup>.

**Palavras-chave:** Projeto de baixa potência, baixa tensão, oscilador digitalmente controlado (DCO),oscilador baseado em transformador, internet das coisas.

#### LIST OF ABBREVIATIONS AND ACRONYMS

IoT Internet of Things

WiFi Wireless Network based on IEEE 802.11 standard

BLE Bluetooth Low Energy

NFC Near Field Communication

RFID Radio-Frequency Identification

LNA Low Noise Amplifier

PLL Phase Locked Loop

ADPLL All Digital Phase Locked Loop

PDKs Process Design Kits

TSMC Taiwan Semi-Conductors

WPAN Wireless Personal Area Network

VCO Voltage Controlled Oscillator

DCO Digitally Controlled Oscillator

TDC Time to Digital Converter

DLF Digital Loop Filter

FREF Reference Frequency

FCLK Output Variable Clock

DTC Digital to time Converter

PHR\_F Fractional part of the reference Phase

PHR Reference Phase

FCW Frequency Command Word

CKR Re-time Reference Rate

OTW Oscillator Tuning Word

WI Weak Inversion

MI Moderate Inversion

SI Strong Inversion

PN Phase Noise

FOM Figure Of Merit

PFN Power-Frequency-Normalized

PGR Patterned Ground Shield

DRC Design Rule Check

UICM Unified Current-Control Model

SNR Signal to Noise Ratio

ACR Adjacent Channel Rejection

# LIST OF SYMBOLS

| $\omega_0$ | central frequency in radians   |

|------------|--------------------------------|

| $Q_p$      | Primary Quality Factor         |

| $Q_s$      | Secondary Quality Factor       |

| $I_D$      | Drain Current of Transistor    |

| $I_s$      | Specific Current of Transistor |

| $i_f$      | Inversion Level                |

| n          | Slope Factor                   |

| $n_L$      | Inductance Ratio               |

| $V_{T0}$   | Equilibrium Threshold Voltage  |

| $gm_g$     | Gate transconductance          |

| GM         | Large Signal Transconductance  |

| $k_m$      | Coupling Factor                |

| $R_p$      | Inductor Parallel Resistance   |

| $R_s$      | Inductor Series Resistance     |

| $\phi_t$   | Thermal Voltage                |

| $I_{tail}$ | Tail Transistor current        |

| $K_B$      | Boltzmann Constant             |

| T          | Temperature Coefficient        |

| $P_{DC}$   | DC Power                       |

| $f_0$      | Central Frequency              |

| $C_{wi}$   | Inter-winding capacitance      |

| $C_{ox}$   | Oxide Capacitance              |

| $R_{si}$   | Substrate resistance           |

|            |                                |

Primary Inductance

$L_P$

$L_S$  Secondary Inductance

$V_G$  Gate Voltage

$V_P$  Pinch-Off Voltage

$I_{SH}$  Sheet Normalization Current

$V_{FB}$  Flat Band Voltage

$\phi_F$  Fermi Potential

$i_{fmax}$  Maximum inversion Level

$V_{dsat}$  Drain to Source Saturation Voltage

$V_{dstail}$  Drain to Source Saturation Voltage of tail transistor

# LIST OF FIGURES

| Figure 2.1 PLL classical topology                                                   | 19   |

|-------------------------------------------------------------------------------------|------|

| Figure 2.2 Charge-Pump PLL.                                                         |      |

| Figure 2.3 ADPLL classical topology                                                 | 20   |

| Figure 2.4 Flash TDC Architecture                                                   | 21   |

| Figure 2.5 DTC-TDC counter-based ADPLL topology                                     | 22   |

| Figure 2.6 (a) Complementary push-pull LC oscillator. (b) NMOS-only LC oscillator   | r.23 |

| Figure 2.7 Schematic of binary switchable capacitance.                              | 23   |

| Figure 2.8 Capacitance vs Voltage Curve of MOS Varactor.                            | 25   |

| Figure 2.9 (a) Resonant tank circuit response to a current impulse without negative |      |

| resistance. (b) Resonance tank circuit response to a current impulse with           |      |

| negative resistance.                                                                |      |

| Figure 2.10 Tail Current versus Tank Amplitude Voltage                              | 27   |

| Figure 2.11 (a) Spectrum of the ideal oscillator output tone. (b) Spectrum of the   |      |

| output tone from oscillator with phase noise.                                       |      |

| Figure 2.12 Phase Noise Definition.                                                 |      |

| Figure 2.13 Phase Noise versus Offset from the Carrier.                             |      |

| Figure 2.14 LC-VCO with tail inductors.                                             |      |

| Figure 2.15 NMOS-Only with Alternating current source Oscillator                    |      |

| Figure 2.16 Dual Class-C Oscillator.                                                |      |

| Figure 2.17 DCO with Trifilar Coil-based resonator                                  |      |

| Figure 2.18 Gate-to-source transformer-feedback ULV VCO                             |      |

| Figure 2.19 Transformer-based stacked-gm DCO.                                       |      |

| Figure 2.20 Transformer-Based DCO                                                   | 38   |

| Figure 3.1 Transformer Based Resonator Parallel Resistance                          | 40   |

| Figure 3.2 (a) Square Planar Transformer. (b) Octagonal Planar Transformer          |      |

| Figure 3.3 (a) Square Stacked Transformer. (b) Octagonal Stacked Transformer        |      |

| Figure 3.4 Transformer lumped model                                                 |      |

| Figure 4.1. Cell                                                                    | 40   |

| Figure 4.1 Coil $\pi$ -model.                                                       |      |

| Figure 4.2 The simulated gmg/id vs. VG plot for an NMOS 40nm transistor             |      |

| Figure 4.3 Slope factor curve for tsmc 40nm tecnology                               | 50   |

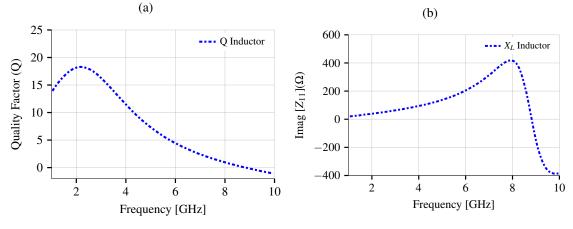

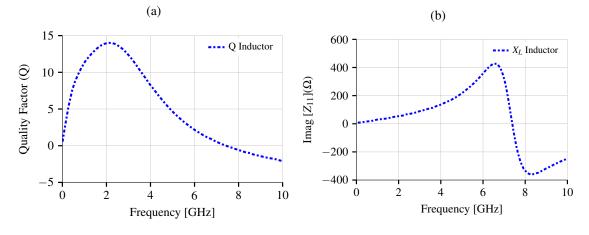

| Figure 5.1 (a) Quality factor behavior. (b) Imaginary part of Inductor impedance    | 55   |

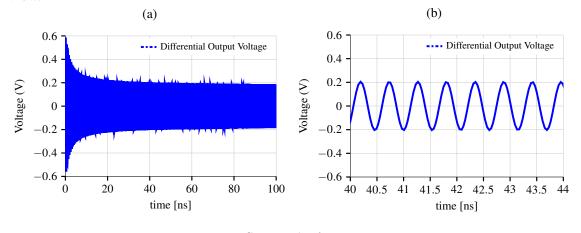

| Figure 5.2 (a) Differential Output Voltage behavior. (b) Differential Output Volt-  |      |

| age zoom view                                                                       | 57   |

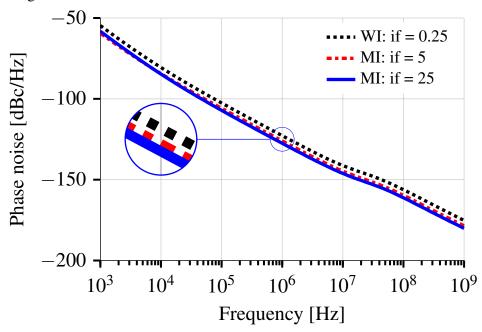

| Figure 5.3 Phase noise schematic simulation results of LC-based DCO                 |      |

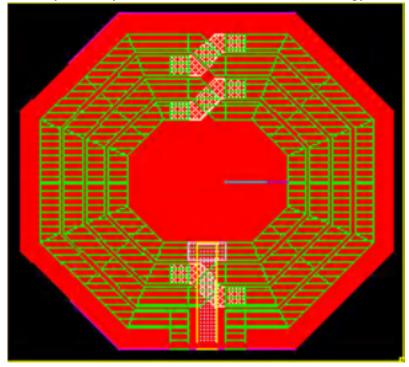

| Figure 5.4 Layout of the proposed LC-based DCO                                      |      |

| Figure 5.5 Phase noise post-layout simulation results of the LC-based DCO           |      |

| Figure 5.6 Layout of Symmetric Inductor in 28nm Technology from TSMC                |      |

| Figure 5.7 (a) Quality factor behavior. (b) Imaginary part of Inductor impedance    |      |

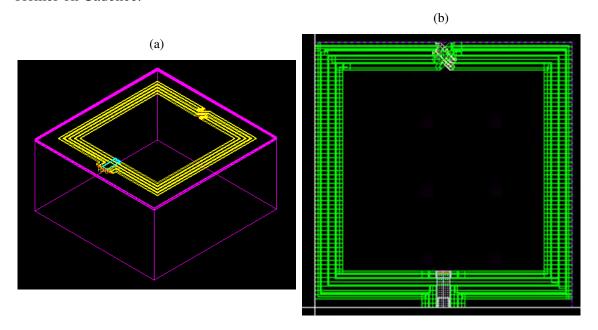

| Figure 5.8 (a) 3D view of the transformer on EM Simulation. (b) Layout of the       |      |

| Transformer on Cadence.                                                             | 62   |

| Figure 5.9 Setup for 2-port EM Simulation of the Transformer.                       |      |

| Figure 5.10 (a)Imaginary Part of Z11. (b) Imaginary Part of Z22                     |      |

| Figure 5.11 (a) Primary Quality Factor. (b) Secondary Quality Factor                |      |

| Figure 5.12 Comparison between EM simulations of the Transformer layout and         |      |

|                                                                                     |      |

| Figure 5.13 (a) Primary Quality Factor Plot. (b) Secondary Quality Factor Plot | 65 |

|--------------------------------------------------------------------------------|----|

| Figure 5.14 Parallel Resistance from Transformer                               | 66 |

| Figure 5.15 VG to gmg/id plot in a 28nm technology                             | 66 |

| Figure 5.16 VG to n plot in a 28nm technology                                  | 67 |

| Figure 5.17 Schematic of Proposed Transformer Based DCO with Output Buffers    | 67 |

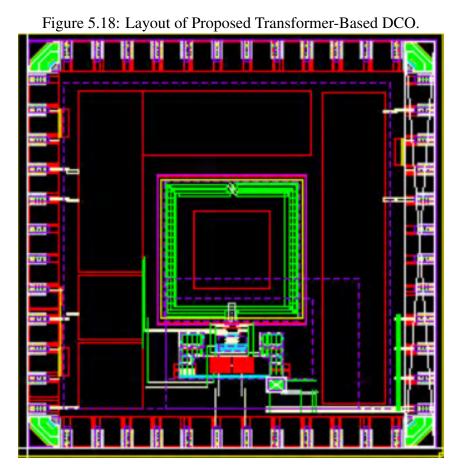

| Figure 5.18 Layout of Proposed Transformer-Based DCO.                          | 68 |

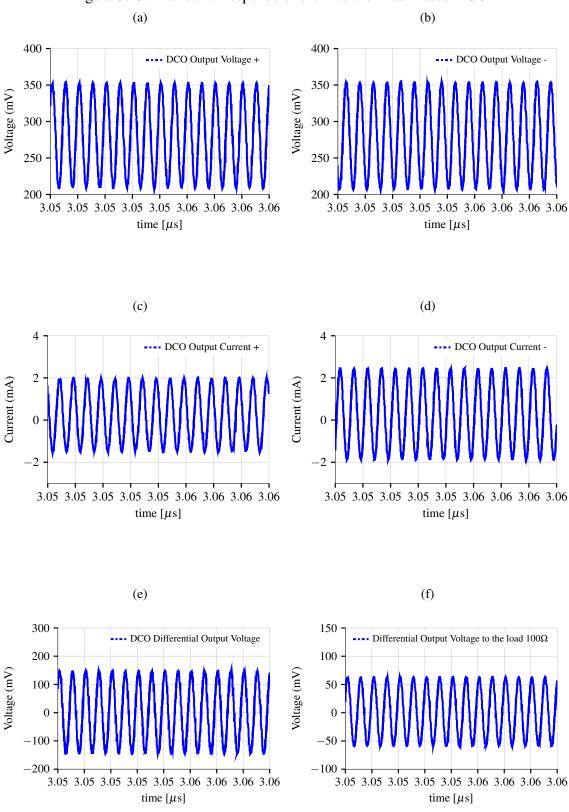

| Figure 5.19 Transient Response of the Transformed-Based DCO                    | 70 |

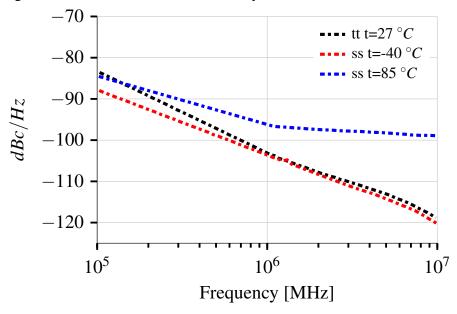

| Figure 5.20 Phase Noise Corners Analysis of Transformer-Based DCO              | 71 |

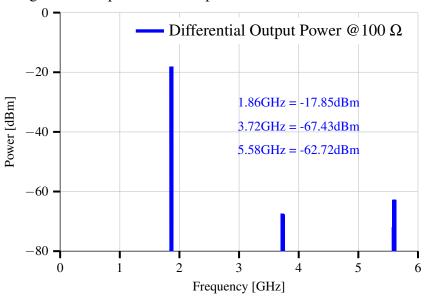

| Figure 5.21 Spectrum of Output Power delivered to the Load                     | 72 |

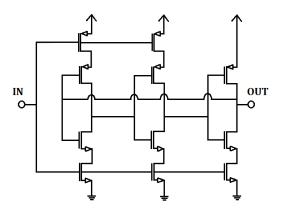

| Figure 6.1 Future Transformer-Based DCO Topology to decrease the process vari- |    |

| ations impact                                                                  | 76 |

| Figure 6.2 Low Power Divider by 2 Topology                                     | 76 |

| Figure B.1 Die Pin Diagram.                                                    | 84 |

|                                                                                |    |

# LIST OF TABLES

| Table 2.1 | State of Art                                            | 37 |

|-----------|---------------------------------------------------------|----|

| Table 5.1 | Specifications of WiFi HaLoW ADPLL system               | 54 |

|           | LC-Based DCO Power Reduction Analysis                   |    |

| Table 5.3 | LC-Based DCO Parameters                                 | 58 |

| Table 5.4 | LC-Based DCO Power Consumption Corner Analysis          | 58 |

| Table 5.5 | Transformer Parameters                                  | 65 |

| Table 5.6 | The transformer-Based DCO Parameters                    | 69 |

| Table 5.7 | Transformer Based DCO Power Consumption Corner Analysis | 71 |

| Table 5.8 | Comparison with the State of Art                        | 73 |

# **CONTENTS**

| 1 INTRODUCTION                                                                                           | 15 |

|----------------------------------------------------------------------------------------------------------|----|

| 1.1 Motivation                                                                                           | 15 |

| 1.2 Goals                                                                                                | 17 |

| 1.3 M.Sc. Thesis Organization                                                                            | 17 |

| 2 DIGITALLY CONTROLLED OSCILLATOR                                                                        | 19 |

| 2.1 Introduction to Low-Power Frequency Synthesizers                                                     | 19 |

| 2.2 All-Digital PLL (ADPLL)                                                                              | 20 |

| 2.3 Introduction to Digitally Controlled Oscillator(DCO)                                                 | 22 |

| 2.4 Tank Losses                                                                                          |    |

| 2.5 Start-up and Steady-State Conditions                                                                 | 26 |

| 2.6 Phase Noise in Weak inversion Oscillators                                                            |    |

| 2.7 Figures of merit for Oscillators                                                                     | 30 |

| 2.8 State of Art for Low Power Oscillators                                                               |    |

| 2.9 Proposed Topology                                                                                    | 38 |

| 2.10 Conclusion                                                                                          |    |

| 3 TRANSFORMER BASED RESONATOR                                                                            | 40 |

| 3.1 Introduction                                                                                         | 40 |

| 3.2 Principle of Operation                                                                               | 40 |

| 3.3 Transformer Layout                                                                                   |    |

| 3.4 Transformer Simulations                                                                              | 42 |

| 3.5 Time Domain Model                                                                                    | 43 |

| 3.6 Conclusion                                                                                           | 44 |

| 4 DESIGN METHODOLOGY                                                                                     | 45 |

| 4.1 Introduction                                                                                         | 45 |

| 4.2 Transformer Design and Parameters Extraction                                                         | 45 |

| 4.3 Transistor Parameters Extraction                                                                     |    |

| 4.4 Cross-Coupled Pair                                                                                   | 50 |

| 4.5 Minimum Supply Voltage                                                                               |    |

| 4.6 Capacitor bank                                                                                       |    |

| 4.7 Conclusion                                                                                           | 52 |

| 5 DCO DESIGNS                                                                                            | 53 |

| 5.1 DCO system requirements                                                                              | 53 |

| 5.2 Inductor-Based DCO Design in 40nm                                                                    | 54 |

| <ul><li>5.2 Inductor-Based DCO Design in 40nm</li><li>5.3 Transformer-Based DCO Design in 28nm</li></ul> | 60 |

| 6 CONCLUSION AND FUTURE WORKS                                                                            |    |

| REFERENCES                                                                                               | 77 |

| APPENDIX A — LIST OF PUBLICATIONS BY THE AUTHOR                                                          | 82 |

| A.1 Conference Papers  APPENDIX R — DOCUMENTATION FOR MEASUREMENTS                                       |    |

| APPENDIX R DOCUMENTATION FOR MEASUREMENTS                                                                | 83 |

#### 1 INTRODUCTION

#### 1.1 Motivation

The growth of devices connected to the internet with the passing of years increases the interest in the study and development of electronic devices for the IoT (*Internet of Things*). The concept of the IoT is defined by a network composed by smart devices that can exchange information with similar ones through wireless channels, without any human interaction.(SRINIVASAN; ARUMUGAM, 2016). The objects that compose the IoT network can be sensors, *Radio-Frequency Identification* (RFID) tags, actuators, mobile cell phone and others. Furthermore, there are several different protocols which connect these devices as *Wireless Network based on IEEE 802.11 Standard* (WiFi), Bluetooth, *Bluetooth Low Energy* (BLE), *Near Field Communication* (NFC), Zigbee, RFID protocols and a mobile phone network. (MASI, 2018).

The WiFi, which is defined as the IEEE 802.11 standard, was created to perform a wireless connection between computers. The WiFI was created for short range communications, which fall in a range of up to 100 meters. The Bluetooth standard was created for providing communication between devices on the range of a few meters. This standard of communication was intended to substitute the transfer cables in consumer electronics. The WiFi standard and the Bluetooth do not support a lot of devices connected at the same time in the same network with low data rates and low power consumption, as the IoT applications require(FERRO; POTORT, 2005)(PAALA et al., 2019).

The Zigbee standard is suitable for applications that require low data transmission rates, low power consumption, and a lot of devices connected to the same network. These features make this protocol suitable for IoT applications. This protocol emerged as an alternative to the WiFi and the Bluetooth standards to reduce the front-end power consumption. This standard reduces power consumption keeping, however, the same range of the WiFI(ELARABI; DEEP; RAI, 2015).

The RFID protocol uses two main devices to perform the communication: the TAG and the reader. The TAG is the device which contains the information that will be read wirelessly. The reader can also modify the information coming from the TAG. The RFID protocol permits a very low power communication due to the possibility of the implementation of passive TAGs. The limitation of this protocol is that the communication range is on average 7 meters or much less (below one meter)(SAFKHANI et al., 2012).

The NFC standard, as the name suggests, is applied in very short communications range. This standard was created by NXP together with Nokia and Sony. This standard makes possible communications by means of a device that reads from and writes information to a card. In this mode of operation the device acts as a reader. Furthermore, the most popular use of this protocol is the data transfer between two handsets by coil tapping. In addition, there is a third mode that emulates a card which will have its information read by an external reader (CHENG et al., 2009).

The most widespread standard for short-range IoT communication in low-cost consumer electronics is the BLE. It is capable of fulfilling the low power requirements of IoT(KUO et al., 2017). This standard is defined as *wireless personal area network* (WPAN) and achieves a communication range of 100 meters(BERTULETTI et al., 2016). The WiFi-HaLow standard (IEEE 802.11ah) can increase considerably the communication range, up to 1 km. The sub-GHz frequency of operation makes possible a low power consumption with a low data rate. This characteristic, added to the longer distance range, makes WiFi-HaLow a competitive solution for wireless sensor networks, IoT applications, and overall applications which demand lots of devices connected and very low power consumption in each device(ANDRADE et al., 2017).

The number of connected IoT devices is estimated to double in five years, and has reached about 24 billion connections in 2020. Although there has been a considerable growth in the number of connections over the years, the IoT applications are just beginning to scale up. (GSM Association, 2020). Furthermore, there are estimates that the market of IoT sensors will reach an mark of 27 billion US dollars by 2021(FORBES, 2020)(CHERNYSHEV et al., 2017). These data corroborates the first predictions of the increase in the number of connections by IoT devices in the next years.

To improve the efficiency of the IoT network, the design of Ultra-Low Power Transceivers becomes necessary to enhance the battery lifetime of autonomous or semi-autonomous nodes. Furthermore, when lots of devices are connected to the IoT network, the battery replacement of each one becomes highly impractical or undesired(LEE et al., 2018).

In the RF transceiver front-end, the 3 most power-hungry blocks are: the *Low Noise Amplifier* (LNA) in the receiver, oscillator in the *Phase Locked Loop* (PLL) or *All Digital Phase Locked Loop* (ADPLL), and the power amplifier in the transmitter. In particular, reducing the power consumption of the oscillator is a considerable challenge since the power level impacts directly the phase-noise performance (YU et al., 2017)(KANG;

#### 1.2 Goals

This Master's thesis is focused on the Design of a Low Power DCO for the WiFi-Halow Standard (IEEE 802.11ah) which enables low power consumption and long-range transmission due to the center frequency of operation below 1 GHz (BA et al., 2018). Furthermore, these features make this standard suitable to IoT and therefore to this work (ANDRADE et al., 2017), which is focused in the low power applications. The Wi-Fi Halow standard has different frequency bands for each country: 863-868 MHz in Europe, 902–928 MHz in the USA and Brazil, and 916.5–927.5 MHz in Japan. The most common channel bandwidths adopted in 802.11.ah (Wi-Fi Halow) are 1 MHz and 2 MHz(ADAME et al., 2014).

The goal of this work is to achieve results comparable with the state of art in controlled oscillators, in terms of power consumption without compromising the phase noise performance required for the given wireless standard. The weak inversion operation of the transistors in the DCO and the transformed-based resonator are two relevant techniques to be explored in this thesis. Both approaches are not new in the literature. However, they remain excellent design options for low power oscillation design(LEE; MOHAMMADI, 2007a)(GHORBEL et al., 2018)(BABAIE; SHAHMOHAMMADI; STASZEWSKI, 2015a). In this work the operational frequency is 1.8 GHz, twice the WiFi HaLow standard. The *Process Design Kits* (PDKs) used to Design the DCOs in this Master's thesis are the 40nm and 28nm both from *Taiwan Semiconductor Manufacturing Company* (TSMC).

#### 1.3 M.Sc. Thesis Organization

Aiming to cover all basics related to the DCO, chapter 2 of this Master's thesis addresses an introduction to PLLs and to frequency synthesizers. The main characteristics, the most popular topologies of cross-coupled oscillators, and an introduction to the phase-noise are also presented in this chapter. The principle of transformer loading in the context of DCO is covered in chapter 3. In chapter 4 the I-V transistor model used for analytical modelling of device operation is reviewed, as it provides basic design equa-

tions. Furthermore, the transistor threshold voltage extraction method used here is also derived in chapter 4. Aiming to arrive at the best compromise in the topology of the low power oscillator, in chapter 5 two DCO designs are developed and compared: one with only inductor-based resonator and another with transformer-based resonator. Finally in chapter 6 the conclusions and future works proposed are presented.

#### 2 DIGITALLY CONTROLLED OSCILLATOR

#### 2.1 Introduction to Low-Power Frequency Synthesizers

Frequency synthesizers are defined as circuits that generate a single or multiple frequencies from a reference one(RADER; GOLD, 1971). The most common example of synthesizer is the *phase-locked loop* (PLL). The PLL is largely used to generate a reference frequency inside the integrated transceivers. The main objective of this block is to obtain a precise reference frequency and phase to be delivered to the system, with a low phase-noise.

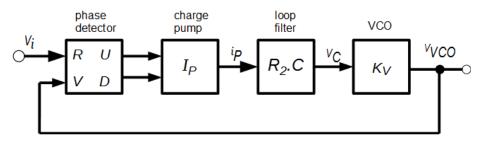

The main topology of this block (Figure 2.1) is composed by: a phase-detector, a low-pass filter, a voltage controlled oscillator and a negative feedback loop. The phase detector compares the phase of the incoming and more stable (with regards to temperature, voltage, and process variations) signal from from the reference input signal with the output frequency from VCO. The phase detector generates a DC voltage signal with high-frequency components which are filtered by the low pass filter. The resulting low frequency voltage signal (Vcont) controls the frequency of the oscillator.

Figure 2.1: PLL classical topology.

Vin Opp VpD LPF Vcont VCO Vout Pout

Source: Adapted from (RAZAVI, 1998)

Figure 2.2: Charge-Pump PLL.

Source: Adapted from (LU; LIU; LI, 2014)

The Charge-Pump based PLL is another basic architecture of the PLL which is described by improvement in the static phase error and the capture range of the PLL. In

this topology, the low pass filter from the basic topology is replaced by the loop filter, and the charge pump is added after the phase detector to convert the digital signal into current. The loop filter acts as a current-to-voltage conversion to process the signal that comes from the charge-pump. Figure 2.2 shows the conceptual architecture of the Charge-Pump Based PLL(LU; LIU; LI, 2014)(RAZAVI, 1998).

## 2.2 All-Digital PLL (ADPLL)

The high scalability of the CMOS processes from generation to generation, which allows by the dimensional scaling the reduction of power consumption and an increase in the number of transistors on the same chip, makes the digital approach a good choice instead of analog ones for certain range of functions. The all-Digital phase-locked loop arises from this concept. Furthermore, the digital design methodology and robustness for developing this block solves some problems posed by the more traditional analog PLLs. The ADPLL consumes less area, as it does not require the large analog filters necessary in the conventional PLL. Hence, all circuit is on-chip, which differs from the analog charge-pump PLL that usually needs off-chip resistors and capacitors to implement the loop-filter, aiming to achieve low PLL bandwidth (FERREIRA et al., 2019) (JANG; JEONG; JEON, 2018).

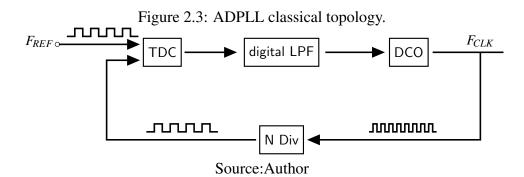

Figure 2.3 presents the most common ADPLL topology composed by: a Time-to-Digital Converter (TDC) which detects the phase error between *Output Variable Clock*(FCLK) and the Reference Frequency (FREF) clock, a Digital Loop Filter (DLF) that locks DCO in frequency and phase, and a Digitally-Controlled Oscillator (DCO) which generates the output variable frequency clock FCLK. In addition, after the oscillator, a frequency divider, which transforms the analog output of DCO into a digital one is placed. The most common DCO topology is an LC-based oscillator, since it introduces less phase-noise than other topologies like the ring oscillators.

Star D(0) D(N-1) D(N) D(N)

Figure 2.4: Flash TDC Architecture.

Source: Author

The most common architecture of the TDC is based on Delay line elements. The Flash TDC architecture is presented by Figure 2.4. The start and stop signals of flash TDC are the (FCLK) and (FREF) respectively. The variable reference clock signal coming from the oscillator is delayed in the delay chain. The stop signal controls the clock of the sampling flip-flops. The measure of a time interval is indicated by the start and stop signals. When the signal coming from the oscillator pass through the delay element, the corresponding sampling flip-flop set its output to high. Hence, when the clock signal has still not reached through the rightmost delay elements, the corresponding memory elements remain with their outputs low. The digital thermometer scale is decoded into a binary word, hence the conversion of the time-interval duration to a digital word (a TDC). The resolution period is defined as the unit delay in an element in the delay line (FERREIRA et al., 2019).

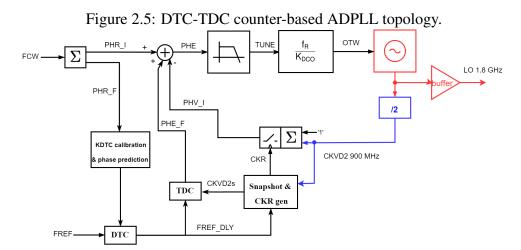

The ADPLL topology which can reduce the power consumption considerably while also decreasing the spurs levels of the ADPLL is the DTC counter-based ADPLL topology presented in the Figure 2.5. The digital to time converter (DTC) acts as a delay line, which is in charge of delay the reference clock with the information coming from the fractional part of the reference phase (PHR\_F)(CHEN et al., 2015). This architecture is based on the phase prediction method described in (ZHUANG; STASZEWSKI, 2012), which is composed of an accumulator, a DTC, and a TDC. The frequency control work (FCW) is accumulated and creates the fractional and integer parts of the reference phase (PHR). In addition, it makes part of the phase-detection the snapshot, the re-time reference rate (CKR), and the variable frequency accumulator.

The frequency command word (FCW) is the rate of the output frequency coming

from the oscillator by the reference frequency FREF. In this topology, the bits requirements of TDC can be reduced due to the presence of the DTC. The DTC delays the reference signal by the control of the fractional part of the reference phase  $(PHR_F)$ . Hence, the signal that comes from the DTC is almost in phase with the signal coming from the snapshot, which results in a decrease in the required bits of the TDC block. This reduction on the TDC bits saves power and also contributes to decrease the magnitude of spurs. The DTC can consume less power with the same number of bits of the TDC. The DTC dominates the spurs level in the DTC-based architecture. However, the spurs problem stemming from the DTC can be solved with the gain calibration technique.

Source: The Author

#### 2.3 Introduction to Digitally Controlled Oscillator(DCO)

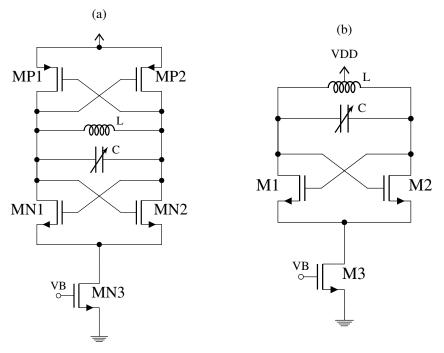

The main LC-oscillator topologies presented in the literature are shown in Figure 2.6. They are the NMOS-only topology and the complementary push-pull. On one hand, the first is more suitable for supply voltage scaling. On the other hand, the second one takes advantage of the so-called current reuse to save power. In addition, the complementary push-pull topology suffers from higher capacitance from routing due to the additional PMOS cross-couple pair. Hence, the extra transconductance source becomes a problem in a weak inversion operation. For the ultra low power operation, the NMOS-only is also more suitable due to the larger transistor sizing requirements. The tuning range from complementary push-pull also results less in this application.

The main differences between a voltage controlled oscillator and a digitally controlled one are addressed to the frequency control method. The first receives a voltage

stimulus to set the oscillation frequency. The second delivers the output voltage with the frequency set by the Oscillator Tune Word (OTW) that is provided at the output of a digital filter. The Digitally-Controlled Oscillator (DCO) represents the heart of the ADPLL, which is in charge of delivering the desired variable frequency.

Figure 2.6: (a) Complementary push-pull LC oscillator. (b) NMOS-only LC oscillator.

Source: Author

Figure 2.7: Schematic of binary switchable capacitance.

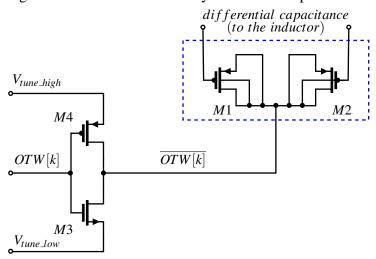

Source: Adapted from (STASZEWSKI et al., 2003)

The binary switchable capacitance method to control the DCO frequency is shown on Figure 2.7. The cell comprises two PMOS transistors connected in a differential varactor configuration. Hence, the voltages  $V_{tunehigh}$  and  $V_{tunelow}$  set the unit cell to the high

or low-capacitance mode. The capacitor bank is formed by different number of these unit cells. Each bit of the OTW sets one of these cells to the required capacitance mode.

The quality factor of the resonator limits the maximum number of bits. The increase in the number of bits results in a decrease in the quality factor of the resonator. Furthermore, the number of bits also limits the tuning range due to the added resultant capacitance from routing. The number of bits also sets the resolution of the DCO. Therefore, there is a trade-off between the tuning range of the DCO and the maximum resolution that can be achieved. The resolution must be equal or less than the channel bandwidth to avoid locking problems into ADPLL.

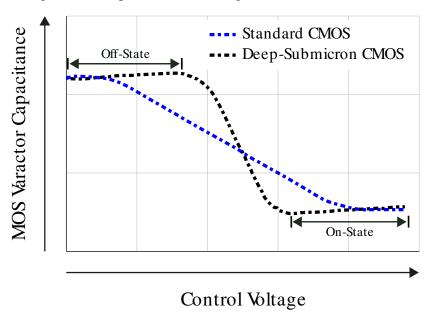

The binary switchable capacitance becomes a solution to the highly non linear capacitance versus control voltage behavior of the CMOS varactors. This problem is increased in the deep-submicron CMOS process, which reduces considerably the linear range of the varactors. This results in the considerable increase in the gain of oscillator, which results in more sensitivity to noise and process variations. Figure 2.8 shows the behavior of the varactors in a conventional and in a deep-submicron CMOS process. The oscillation gain is derived from the following equation:

$$K_{VCO} = \Delta_f / \Delta_V \tag{2.1}$$

The binary switchable capacitance method then reduces the impact of the noise and the process variations due to the operation on the two modes only to each bit. This makes this method less prone to process variation as the circuit is not required to work in the linear region of the curve. In the linear region of the curve any threshold variation due to process will result in a considerable change in the oscillator frequency of operation (STASZEWSKI et al., 2003).

#### 2.4 Tank Losses

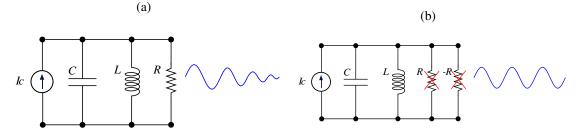

The LC-Oscillators described earlier has the negative resistance as the principle of oscillation. A LC-tank, when excited by a pulse of current, starts to oscillate with a frequency of the periodic signal equal to resonance frequency of resonator. In an ideal case, which the tank do not have losses, the oscillation remains stable. However, in the real scenario, when the tank resonates, remains the resistance which represents the losses of the resonator. Hence, the signal is dissipated in the resistor and the oscillation die.

Figure 2.8: Capacitance vs Voltage Curve of MOS Varactor.

Source: Adapted from (STASZEWSKI et al., 2003)

Figure 2.9(a) represents this phenomena.

To avoid this problem and sustain the oscillation, the losses must be cancelled. The solution to this issue is to provide a negative resistance, which cancels the resultant resistance at resonance as Figure 2.9(b) shows(RAZAVI, 1998). The most common circuit configuration which provides a negative resistance is the cross-coupled pair. In the case of complementary push-pull topology, the NMOS pair provides one and the PMOS pair provide the second one. Hence, the negative resistances are added to cancel the resistance of the tank.

Figure 2.9: (a) Resonant tank circuit response to a current impulse without negative resistance. (b) Resonance tank circuit response to a current impulse with negative resistance.

Source: Adapted from (RAZAVI, 1998)

In the LC-based oscillator, the losses of the resonator are dominated by parallel

resistance of the inductor  $(R_p)$  given by:

$$R_p \approx L^2 \omega_0^2 / R_s \tag{2.2}$$

where  $R_s$  is the series resistance, L is the inductance and  $\omega_0$  is the DCO frequency of operation. This equation shows that by increasing the size of the inductor the parallel resistance will also increase. However, this assumption is limited by the self-resonance frequency of the inductor which limits the maximum size of the inductive element by required frequency of operation. In addition, the quality factor of the coil also decreases by the increases of the its series resistance. When the coil increases the series resistance also increases resulting in a decrease in the quality factor of the inductor. Equation 2.2 shows the impact of the quality factor represented by R\_s. To solve this problem related to the size of the inductor, the most useful strategy is to improve the quality factor (Q) of the device. The power consumption of the classical LC oscillator is inversely proportional to the quality factor of the inductor. Integrated oscillators on bulk silicon CMOS processes suffer from low quality factors. The quality factor of the inductor, which represents an efficiency parameter, is derived as:

$$Q = L\omega_0/R_s \tag{2.3}$$

To maximize the quality factor of inductor we need to reduce its series resistance  $(R_s)$ . In addition, increasing the operating frequency of the system also helps to improve the quality, up to a certain frequency range (RAZAVI, 1997).

#### 2.5 Start-up and Steady-State Conditions

The oscillator starts when the transconductance  $(gm_g)$  of the transistors in the cross-coupled pair is larger than tank losses, which are represented by the parallel resistance of the inductor  $R_p$ . This condition is defined as

$$gm_g \geqslant \frac{2}{R_p}.$$

(2.4)

After the oscillator starts, the voltage across the tank increases and the oscillator starts to function as a large signal block. Furthermore, the cross-coupled pair works as a current source. In this regime, the small-signal transconductance of the transistor which is derived

from 2.5 is no longer useful. The transconductance from the cross-coupled pair must be replaced and represented by equation 2.6(TOUMAZOU; MOSCHYTZ; GILBERT, 2004):

$$gm_g = \frac{2I_S}{n\phi_t}(\sqrt{1+i_f} - 1) \approx \frac{I_D}{n\phi_t}$$

(2.5)

$$GM = \frac{2I_D}{V_{tank}} \tag{2.6}$$

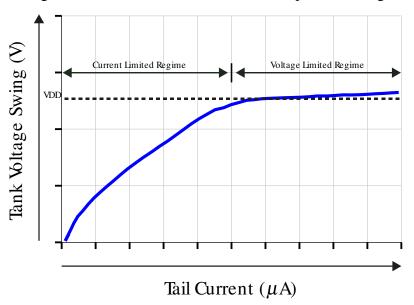

Equation 2.6 shows that the large signal transconductance decreases with an increased voltage amplitude across the tank. Therefore, the start-up condition is not capable of keeping the oscillation causing it not to be sustained. The oscillator operates either in a current-limited regime or in a voltage-limited regime. During the current-limited operation, the voltage amplitude is given by

$$V_{tank} = I_{tail}R_p (2.7)$$

Figure 2.10: Tail Current versus Tank Amplitude Voltage

Source: Adapted from (TOUMAZOU; MOSCHYTZ; GILBERT, 2004; HAJIMIRI; LEE, 1999)

where  $I_{tail}$  is the tail current and  $R_p$  is the tank parallel resistance. Meanwhile, during the voltage-limited operation, the voltage amplitude across the tank is approximately equal to VDD (TOUMAZOU; MOSCHYTZ; GILBERT, 2004; HAJIMIRI; LEE, 1999). Figure 2.10 shows the behavior of the voltage amplitude across the tank in these two regimes. Assuming that the maximum voltage across the tank is VDD and its value

will not exceed 400 mV for ultra-low voltage oscillators, which represents approximately  $16\phi_t$ . The new condition derived from 2.8 satisfies both the start-up and the steady-state conditions.

$$gm_g \geqslant \frac{4}{R_p}.$$

(2.8)

#### 2.6 Phase Noise in Weak inversion Oscillators

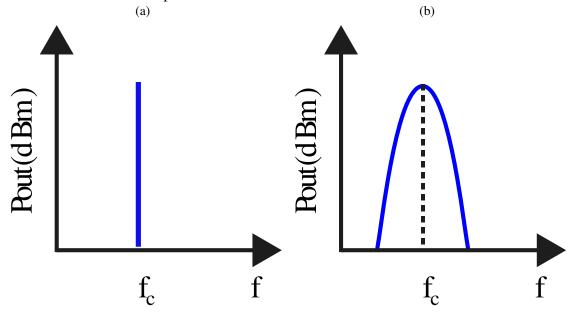

An ideal LC-oscillator presents an output signal at the resonance frequency of its passive components. This results in an output signal precisely at the resonance frequency and without of any other components. The spectrum of this signal is presented on the Figure 2.11(a). However, the LC tank is not ideal and has a finite quality factor. The noise coming from trapped charges in transistors channel/oxide interfaces and from other sources can perturb the output signal resulting in noise in the oscillation phase, or phase-noise for short. The real output spectrum of an LC-oscillator can be observed in the Figure 2.11(b). It is possible to observe that the signal has a power output in other frequencies. The output power decreases when the frequency moves away from the carrier frequency. Hence, when it is plotted the phase-noise versus offset from the carrier, the shape of the curve is a descending line.

Figure 2.11: (a) Spectrum of the ideal oscillator output tone. (b) Spectrum of the output tone from oscillator with phase noise.

Source: Adapted from (RAZAVI, 1998)

The phase-noise is computed at a frequency offset from the carrier considering a bandwidth of 1 Hz. The signal of this bandwidth is measured at an offset from the carrier and normalized to the power of the carrier. Hence, the phase-noise is measured in dBc/Hz. Figure 2.12 shows this quantification.

$f_{c} \xrightarrow{f} f$

Figure 2.12: Phase Noise Definition.

Source: Adapted from (RAZAVI, 1998)

Figure 2.13: Phase Noise versus Offset from the Carrier.

Source: Adapted from (Hajimiri; Lee, 1998)

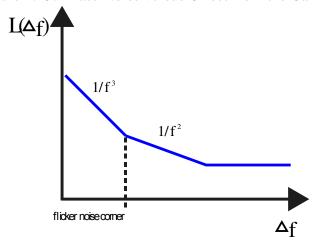

The phase-noise (PN) of an oscillator is a fundamental characteristic since it describes the oscillator spectrum purity around  $f_0$ (Hajimiri; Lee, 1998). At a frequency offset,  $\Delta f$ , from  $f_0$ , the PN spectrum exhibits three regions:  $\frac{1}{f}$ ,  $\frac{1}{f^2}$ , and  $\frac{1}{f^3}$ . Figure 2.13 shows the illustration of these three regions. The CMOS transistor is the main noise con-

tributor in  $\frac{1}{f^2}$  and  $\frac{1}{f^3}$  regions. Each of those regions has a different mechanism triggering the PN. For instance, the PN is triggered by the flicker noise in the  $\frac{1}{f^2}$  region and by white noise in the  $\frac{1}{f^3}$  region. Due to the relation between PN and noise of the transistors, it is possible to establish a relation between PN and the forward inversion level ( $i_f$ ) (Hajimiri; Lee, 1998; Fiorelli; Peralias; Silveira, 2011a; Cunha; Schneider; Galup-Montoro, 1998). PN in the regions  $\frac{1}{f^2}$  and  $\frac{1}{f^3}$  are respectively given by

$$\mathcal{L}_{1/f^2}(\Delta f) = 10\log\left(k_B T \frac{4\pi^2 \Gamma_{rms}^2}{g m_g n^2 \phi_T^2} \frac{\lambda}{(i_f + 1)Q^2}\right) + 10\log\left(\frac{f_O^2}{\Delta f^2}\right)$$

and

$$\mathcal{L}_{1/f^3}(\Delta f) = 10\log\left(\frac{\Gamma_{av}^2 K_{F,n}'}{4WL} \frac{\pi^2}{n^2 \phi_T^2} \frac{1}{(i_f + 1)Q^2}\right) + 10\log\left(\frac{f_O^2}{\Delta f^3}\right),\,$$

where  $\lambda$  is the excess noise factor of the white noise,  $k_B$  is the Boltzmann constant, T is the absolute temperature,  $\Gamma_{rms}$  is the root mean square (rms) value of the impulse sensitivity function  $\Gamma$  (Hajimiri; Lee, 1998),  $K'_{F,n}$  is the NMOS transistor normalized flicker noise constant, and  $\Gamma_{av}$  is the average value of the impulse sensitivity function as defined in (Hajimiri; Lee, 1998).

Since the transistor biased in weak-inversion (WI) has large dimensions, it has a low flicker noise. Conversely, the white noise has similar values regardless of the region of operation. The main difference is the type of noise that dominates the white noise. In WI, the white noise is mainly composed of shot noise. Meanwhile, in moderate-inversion (MI) and strong-inversion (SI), white noise is dominated by thermal noise. Since all the regions (WI, MI, and SI) have similar values for white noise, but the WI region presents a lower flicker noise than the other two regions, one can conclude that the WI region presents the lowest PN (LEE; MOHAMMADI, 2007b). Consequently, it is highly recommended to bias the transistors in WI when targeting ultra-low-power applications. Not only for power efficiency reason but for PN improvement as well.

#### 2.7 Figures of merit for Oscillators

The Figure of merit is a standard to compare oscillators designed for different purposes with the same metric. The most popular figure of merit for oscillator is derived from the Equation 2.9:

$$FOM = \mathcal{L}_{offset} - 20 \log \left( \frac{f_0}{f_{offset}} \right) + 10 \log \left( \frac{P_{DC}}{1mW} \right)$$

(2.9)

Where the  $\mathcal{L}_{offset}$  represents the phase noise from a measured offset from carrier,  $f_0$  is the oscillation frequency and  $P_{DC}$  denotes the power consumption of the block. The main issue of this figure of merit is that the phase noise represent the greater impact of FOM. Therefore, to express the merit of ultra-low-power designs, this figure of merit will not be useful or realistic(WANG et al., 2007).

In order to analyze the performance, the figure of merit useful in the literature is the power-frequency-normalized (PFN) and can be derived from(LEE; MOHAMMADI, 2007b):

$$PFN = 10 \log \left[ \left( \frac{kT}{P_{DC}} \right) \left( \frac{f_0}{f_{offset}} \right)^2 \right] - \mathcal{L}_{offset}$$

(2.10)

Where the k is the boltzmann constant and T is the temperature. The main issue concerning this figure-of-merit (FOM) is: it only adds the impact of the temperature on the first one. Furthermore, as in the equation 2.9, the relation of the frequency from carrier to the offset frequency is squared. This results that oscillators which operate at higher frequencies achieve in general better PFN. To address this issue and to compute the impact of this work related to power consumption at the state-of-art, a new figure-of-merit is proposed in this work:

$$FOM = \mathcal{L}_{offset} - 20\log\left(\frac{f_0}{f_{offset}}\right) + 40\log\left(\frac{P_{DC}}{1mW}\right)$$

(2.11)

This figure of merit is a modification of equation 2.9. The impact of power consumption in the FOM is increased. This metric is chosen because this work aims to achieve ultra-low power consumption. Furthermore, the term in the equation which describes the oscillator power consumption is raised to the fourth power. Therefore, the impact of the power consumption of the oscillator will be increased.

#### 2.8 State of Art for Low Power Oscillators

The firsts integrated transceivers date back to the 1980s and were addressed to mobile telecommunications (LEENAERTS; TANG; VAUCHER, 2003). The device tech-

nology used in those early designs are bipolar transistors which consume more power and allow for a lower integration than CMOS. Both features added to a high degree of integration between digital and analog circuits, making the CMOS process the most useful not only for integrated transceivers but also for the majority of the integrated analog circuits. In the beginning, the higher achievable operating frequency of the bipolar process in comparison to the then-available CMOS made the bipolar a better choice to design transceiver(HABEKOITE et al., 1987). Nowadays, this assumption is not true due to the scalability of CMOS process which enables high frequency of operation(KANG; NIKNE-JAD, 2013)(VOLKAERTS; STEYAERT; REYNAERT, 2011)(LOO; WIN; YEO, 2018).

The main difference of performance of the transceivers over the last passing years refers to the power consumption. The power supply reduction is directly impacted by the reduction of the oxide thickness added to the decrease of the threshold voltage of transistor. It is possible to note this in the voltage controlled oscillators from (BOUZERARA; ELAROUSSI, 2005) and (YU et al., 2006). The first one is an adapted push-pull complementary topology with a LC-resonator and an inductive source degeneration technique to reduce the phase-noise. This work presents a power consumption of 2.8mW with 1.8V of supply voltage and was designed for a 350nm CMOS technology. The second design shows a big improvement in the power consumption with differential Colpitts topology designed for a 180nm CMOS technology. This VCO achieves a power consumption of 1.2mW with a power supply of 1V. Furthermore, both oscillators operates at the same frequency of 1.8GHz.

A different approach to improve the power efficiency of a cross-coupled voltage controlled oscillator is presented in (LEE; MOHAMMADI, 2007b). The architecture used by the author is the NMOS-only structure with an LC-resonator and a two tail inductors. The figure 2.14 shows the architecture proposed by author. The tail inductors are added to reduce the phase-noise from the tail transistor and they also help to save power. However, the main design technique employed in this work is the weak inversion operation of the transistors. Furthermore, this work explores the exponential relation between current and voltage of the FET device in weak inversion operation to obtain the maximum gm to Id ratio. As a result of this design topology choice, the power consumption achieved in this work is merely 0.43mW with a very simple topology. Moreover, the resulting phasenoise is  $-106~\mathrm{dBc/Hz}$  at a  $400\mathrm{kHz}$  offset from the carrier. The oscillation frequency in this example  $2.63\mathrm{GHz}$ .

$L_1$   $M_1$   $M_2$   $M_1$   $M_2$

Figure 2.14: LC-VCO with tail inductors.

Source: Adapted from (LEE; MOHAMMADI, 2007b)

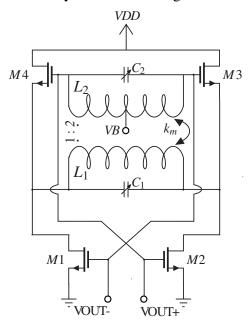

In (BABAIE; SHAHMOHAMMADI; STASZEWSKI, 2015b) the goal of the author is to combine the supply voltage scaling advantage from NMOS-only topology with the current efficiency characteristic of complementary push-pull to improve power consumption. Hence, a new configuration of the oscillator which transforms the fixed current source of the NMOS-only topology in a one that changes the direction during a half of oscillation period as complementary push-pull topology is proposed. The proposed architecture is presented in figure 2.15. Furthermore, with this architecture, the authors achieve operation for supply voltage below 0.5V with current efficiency. To achieve this mode of operation it was necessary to implement a transformer-based resonator which also improves the quality factor of the tank. The achieved supply voltage and power consumption were 0.5V and 0.5mW, respectively, at the 4.8GHz central frequency. The phase noise also improves with the switching current operation and thus results in -139 dBc/Hz at 10 MHz of offset from the carrier.

Figure 2.15: NMOS-Only with Alternating current source Oscillator.

Source: Adapted from (BABAIE; SHAHMOHAMMADI; STASZEWSKI, 2015b)

The change in the conduction angle of the oscillator is a technique to improve the phase noise. The class-C is the choice in (OKADA et al., 2009) which on one hand improves the phase noise and on the other hand cannot operate with a low supply voltage. To solve this problem the author proposed a dual conduction Class-C operation, which is presented in the figure 2.16. Hence, the circuit is composed of two cross-coupled pair to perform a dual operation. Each one of these pairs of transistors operates with different bias sources and consequently with a distinct conduction angle. Hence, the work achieves ultra low power operation without compromising the phase-noise. The dual class-C idea operates at  $4.5 \, \mathrm{GHz}$  and consumes  $0.114 \, \mathrm{mW}$  with  $-104 \, \mathrm{dBc/Hz}$  at  $1 \, \mathrm{MHz}$ .

M3  $\overline{\phantom{a}}$   $\overline{\phantom{a}}$

Figure 2.16: Dual Class-C Oscillator.

Source: Adapted from (OKADA et al., 2009)

Figure 2.17: DCO with Trifilar Coil-based resonator.

Source: Adapted from (LI et al., 2017)

The class-F operation is another possibility to design low power oscillators due to the voltage gain obtained from the transformer. However, the minimum supply voltage cannot be below the value of the threshold of the transistor. To solve this problem, in (LI et al., 2017) a new circuit is proposed, adapted from the class-F oscillator. It uses a Trifilar-Coil as the inductive element of the resonator. Consequently, the voltage gain from the transformer is improved and the minimum supply results possible below the threshold of the device. The technology used in this work is the 16nm FinFet CMOS and the design needs 0.6mW of power consumption for the oscillator. The supply voltage is reduced to 0.2V and the phase noise is -134dBc/Hz at 1MHz. The architecture of this oscillator with the trifilar-coil implementation is shown in figure 2.17.

Another design that also works with a very low supply voltage of 0.2V is presented by (YANG et al., 2019). Figure 2.18 shows the topology chosen by its authors. The extremely low voltage supply results in a power consumption of 0.67mW. The central frequency is 2.4GHz and the phase noise results in  $-119 \mathrm{dBc/Hz}$  at 1MHz offset. The proposed design is based on improving the problems addressed with the transformer feedback oscillator and with the Trifilar-Coil based on class-F operation discussed earlier. The new circuit uses a gate to source feedback instead of gate to drain feedback from class-F or source to drain from basic transform feedback topology. The transformer design also is a different one. Both coils are vertically coupled which results in a very challenging design due to the different sheet resistance from metals of each coil. The vertically coupled coils result in a lower quality factor to the secondary in comparison to the primary. The

final circuit results in just one cross-coupled pair composed of NMOS transistor, added to a transformer based resonator.

VOUT+  $\begin{array}{c}

VDD \\

M1 \\

L_2 \\

\vdots \\

L_1 \\

C_1

\end{array}$ VOUT-

Figure 2.18: Gate-to-source transformer-feedback ULV VCO.

Source: Adapted from (YANG et al., 2019)

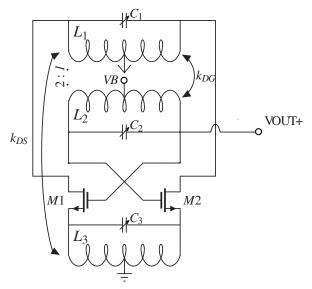

A new topology of the oscillator, which is presented in the figure 2.19, was recently added to the state of art by (LIU et al., 2019). The frequency control of this oscillator is made digitally, thus this circuit is a digitally controlled oscillator instead of a voltage controlled oscillator. The goal of this design is to add this oscillator to a low power fractinonal-N ADPLL. This design also aims reduce the power consumption below 0.5mW. The circuit is composed by two NMOS cross-coupled pairs to improve the achievable transconductance. Both cross-coupled pairs are coupled by a transformer which composed the resonator together of the capacitors bank of each side of coils. The final power consumption of this design is merely 0.107mW, the phase-noise is 107dBc/Hz at 1MHz offset from the carrier, and the oscillation frequency is 2.46GHz.

Table 2.1: State of Art Source: Author

|                         | I*            | П*            | III*          | IV*            | V*             | VI*             |

|-------------------------|---------------|---------------|---------------|----------------|----------------|-----------------|

| Process<br>(nm)         | 180           | 65            | 28            | 16             | 40             | 180             |

| Phase Noise<br>(dBc/Hz) | -104<br>@1MHz | -107<br>@1MHz | -119<br>@1MHz | -134<br>@10MHz | -139<br>@10MHz | -106<br>@400kHz |

| Frequency<br>(GHz)      | 4.5           | 2.46          | 2.24-2.6      | 3.2-4.0        | 4.8            | 2.63            |

| VDD<br>(V)              | 0.2           | 0.45          | 0.2           | 0.2            | 0.5            | 0.45            |

| Power<br>(mW)           | 0.114         | 0.107***      | 0.67***       | 0.6            | 0.48           | 0.43***         |

<sup>\*</sup>Measurement Results I-(OKADA et al., 2009)

Figure 2.19: Transformer-based stacked-gm DCO.

Source: Adapted from (LIU et al., 2019)

To list all the relevant features of the designs previously reviewed and to compare their most important results, Table 2.1 summarizes the main figures achieved by their authors. The table 2.1 will be used in chapter 5 as reference to compare with results achieved in the course of this Master's thesis.

<sup>\*\*</sup>Simulation Results II-(LIU et al., 2019)

\*\*\*Without Output Buffer III-(YANG et al., 2019)

IV-(LI et al., 2017) V-(BABAIE; SHAHMOHAMMADI; STASZEWSKI, 2015b)

VI-(LEE; MOHAMMADI, 2007b)

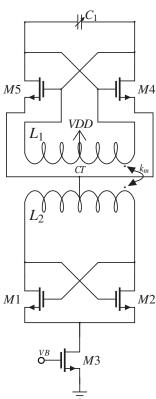

## 2.9 Proposed Topology

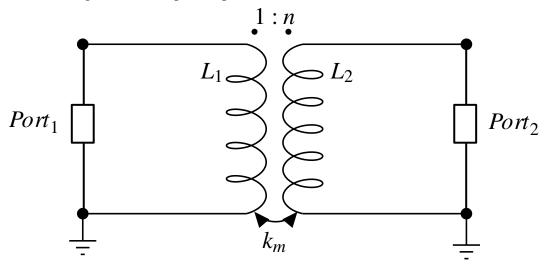

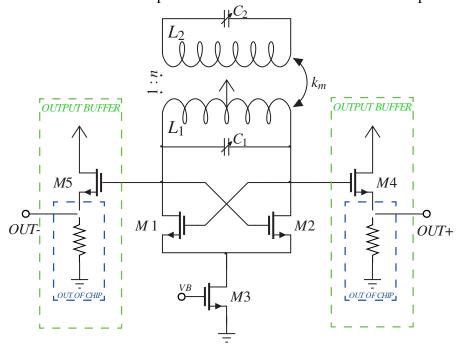

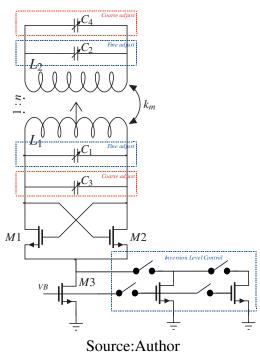

The main objective of this work is to design an ultra-low voltage digitally controlled oscillator that achieves a power consumption comparable to the state of art without compromising its phase-noise. Furthermore, the goal of this work is to achieve low power operation with a basic topology and then to prove that it is possible to design it with transistors operating only in weak inversion - a new design approach to the DCO - combined with improvements in the design of the resonator. To achieve this, the topology presented in Figure 2.20 is proposed and will be developed further in the next chapters.

$L_2$   $L_2$   $L_1$   $L_1$   $L_1$   $L_1$   $L_2$   $L_3$   $L_4$   $L_4$   $L_4$   $L_4$   $L_5$   $L_5$   $L_5$   $L_6$   $L_7$   $L_8$   $L_8$

Figure 2.20: Transformer-Based DCO

Source: Adapted from (EL-GOUHARY; NEIHART, 2011)

The topology is an NMOS-only presented at the beginning of this chapter. The main improvement addressed here is the transformed-based resonator, which increases the parallel resistance of the tank. With the proposed topology it is expected to show later that the current consumption can decrease due to the transformer in the resonator. Furthermore, the minimum required supply voltage for oscillation is also reduced due to its inherent single cross-coupled pair.

#### 2.10 Conclusion

In this chapter the basics of the frequency synthesizers and PLLs were presented. Furthermore, the basic topologies of PLLs and ADPLL with the main differences and functionalities were summarized. This chapter also had the purpose of showing the main functionality of the oscillators in the PLLs and ADPLLs. In addition, the motivation behind the intensive digital approach to the Phase Locked loop is discussed. The main topologies of digitally controlled oscillators present in the literature were summarized in this chapter. The main figures of merit described in the literature were reviewed. The issues of the losses in the resonator and the conditions to sustain an oscillation were also discussed. The direct relation between the weak inversion operation and the phase noise was addressed. Finally, the proposed topology to achieve the goals of this Master's thesis was presented.

#### 3 TRANSFORMER BASED RESONATOR

#### 3.1 Introduction

The improvements of the inductor in the LC-based oscillator is limited by the technology. As discussed previously, the goal of this work is to obtain the maximum quality factor of the inductor, henceforth achieving the maximum parallel resistance for the resonator with a minimum required area. The expectation is that less power consumption will be required from the oscillator and the phase noise will be also improved. Ultra-low power operation demands a very high-quality factor to satisfy the power consumption and phase noise requirements. In addition, with a single inductor designed in the latest technologies (i.e. 40nm CMOS for one particular design in chapter 5) it is difficult to improve the DCO design. From this need, the transformer based resonator arises as a viable option or solution (STRAAYER; CABANILLAS; REBEIZ, 2002).

# 3.2 Principle of Operation

The transformer resonator is a very useful approach when the ultra-low power consumption is required. In comparison to the oscillator that uses an LC resonator, the phase noise can be improved by 6 dB just by the transformer-based resonator implementation. The phase-noise improvement results from the bandwidth reduction by the increase of the quality factor (BAEK et al., 2003). Figure 3.1 shows a transformer-based resonator implementation.

$\begin{array}{c|c} I_p & 1:n \\ \hline \\ + & L_1 \\ \hline \\ C_1 & C_2 \\ \hline \\ K_p & - \\ \hline \\ K_m & - \\ \hline \end{array}$

Figure 3.1: Transformer Based Resonator Parallel Resistance

Source: Adapted from (BABAIE et al., 2016)

The transformer results in only a parallel resistance when  $C_1$  and  $C_2$  resonate with the  $L_1$  and  $L_2$  respectively. The parallel resistance at the resonance is derived from the Equation 3.1(BABAIE et al., 2016).

$$R_p \approx L_1 \omega_0 Q_1 \left( 1 + k_m^2 \frac{Q_2}{Q_1} \right) \tag{3.1}$$

Where  $Q_1$  and  $Q_2$  are respectively the quality factors of the first (primary) and second (secondary) coils, and  $k_m$  is the transformer coupling coefficient. If  $k_m$  is 1 and  $Q_1$  and  $Q_2$  are the same, which is an ideal situation, the  $R_p$  of the transformer-based resonator is two times larger than the  $R_p$  of the single-inductor-based. This assumption also considers that the inductance of the single-inductor and the of the primary and the secondary of the transformer is the same. Just this doubling helps to reduce the oscillator power consumption.

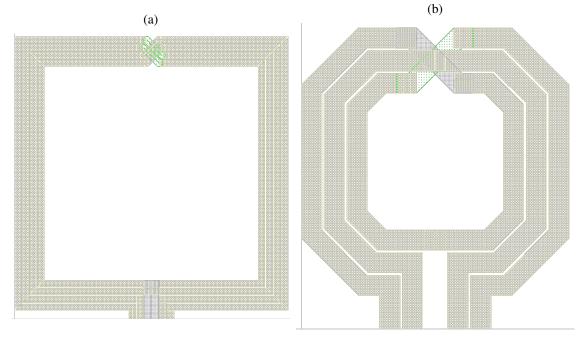

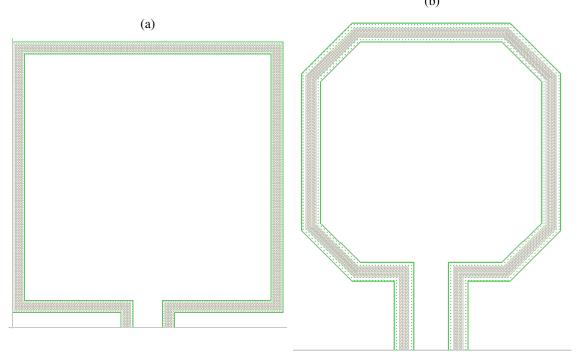

## 3.3 Transformer Layout

The shape of the transformer layout is an essential part of its design. The most common shapes are the square and the octagonal. On one hand, the shape octagonal can slightly improve the quality factors of each coil of the transformer. On the other hand, the shape square can achieve much higher inductance on each coil due to the increase in the total length of coils. This behavior is similar to a simple inductor.

Furthermore, the coupling method also impacts the performance of the transformer. There are two most useful coupled methods on the actual CMOS technologies: the stacked and the planar approaches. The stacked method improves the coupling factor in comparison to the planar one. However, the quality factor of secondary is increased on the planar method due to the possibility of using the same top-level metal of the primary. The ultra-thick metal generally is the top-level of metal. Furthermore, in the most current technologies, there is only one ultra-thick metal. In the stacked topology, the primary and secondary must be performed in different levels of metal films, which decrease the quality factor of the secondary coil (LONG, 2000)(LEITE, 2011). Figure 3.2 shows the configurations of planar transformer while Figure 3.3 shows the stacked one.

In the 28 nm technology which is used in this work, there are only three metal layers (M8, M9, and AP) thicker than the other underlying thin metals. However, there is only one ultra-thick metal: the M9. Hence, the planar topology is a better choice in this

case. The impact on the quality factor of the secondary coil when the stacked topology is used will be much higher than the impact in the coupling factor when the planar one is used.

Another challenge in the transformer design, when it refers to CMOS processes, is that it suffers from substrate loss. The main problem here is the finite resistivity of the substrate. This conductive behavior of the substrate combined with the capacitive coupling between the conductors and substrate makes that current flows through it. Furthermore, eddy currents also flows in the substrate due to the electromagnetic induction. These losses further decrease the quality factors of the coils. To avoid this problem, the insertion of the Patterned Ground Shield (PGR) is an option and used in (EL-GHARNITI; KERHERVE; BEGUERET, 2006), while the floating shield is used in(CHEUNG; LONG, 2006). The main problem here is that, even presenting favorable results in frequencies below 10 GHz, both solutions do not present a significant impact on the quality factor at frequencies below 2 GHz, which is the case for the oscillator focused in this work.

Figure 3.2: (a) Square Planar Transformer. (b) Octagonal Planar Transformer.

Source: Author

# 3.4 Transformer Simulations

To simulate the transformer together with the layout of the DCO in the Cadence ambient, it is necessary to design and simulate it in an electromagnetic simulator to com-

Figure 3.3: (a) Square Stacked Transformer. (b) Octagonal Stacked Transformer.

pute its effects and extract its time-domain model. To design and simulate the transformer, this work uses two electromagnetic simulators: the ASITIC and the Advanced Design System ADS from Keysight. The first one, to obtain the first layout which will be adjusted to satisfy DRC issues in the layout editor environment (also Cadence Virtuoso(TM) herein). Furthermore, the ASITIC also helps to get the preliminary results from the transformer simulations. The second, to finish the electromagnetic simulations using the momentum microwave results of the transformer and to extract the time domain model in order to execute the final simulations with the layout of the oscillator.

## 3.5 Time Domain Model

The first step to extract the time domain model of the transformer is to choose a lumped model that represents precisely the behavior of the transformer in the required frequency range. The oscillator proposed in this work operates at 1.8GHz, which corresponds to the double of the WiFi-HaLow standard central frequency in some countries. Hence, the size of the transformer decreases and, thus, the overall quality factor increases. Figure 3.4 shows the model which will be used in this work. The lumped model is composed by a two  $\pi$ -model of each coil coupled by a coupling factor  $k_m$ . The  $R_{ss,sp}$ ,  $C_{s,p}$ ,

Figure 3.4: Transformer lumped model

Source: Adapted from (KANG; GIL; SHIN, 2005)

and  $L_{s,p}$  are respectively the resistances, the capacitances, and the self-inductances of the coils. Additionally, the impedances  $Z_{sh1-4}$  model the coupling to the substrate.

# 3.6 Conclusion

This chapter dealt with the impact of the transformer-based resonator in the power consumption of the oscillator. Furthermore, the improvements in the phase-noise of this block are also discussed. Additionally, the steps and methods for integrated transformer simulations were exposed. To conclude, the time domain model which is used for the transformer in this design was showed.

#### **4 DESIGN METHODOLOGY**

#### 4.1 Introduction

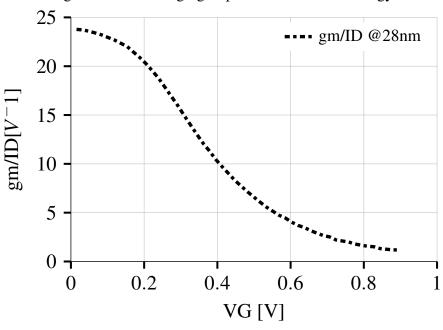

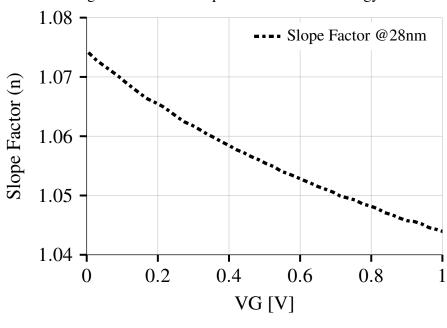

The design of a low power LC-oscillator can be split into main steps. The first remains about the minimizing the losses of the resonator to improve both the power consumption and the phase-noise of the oscillator. The second is related to the sizing and the bias condition of the transistors which impacts on the noise contribution by the devices. The transistor must be sized to achieve the required transconductance to satisfy the start-up and steady-state conditions. Furthermore, the noise contribution of the transistor changes with the inversion level as presented earlier. In the deep-submicron process, the maximum  $gm/I_d$  achieved is lower than the obtained in old technologies. To achieve the same power consumption it is necessary to compensate the difference of the  $gm/I_d$  by the improvement of the quality factor of the resonator.

The present study proposes a new design methodology for oscillators aiming to optimize circuit performance at low power. The methodology is based on the Unified Current-Control Model (UICM) which is a physics-based model and enables an accurate all-region modeling of the operation of the device (Cunha; Schneider; Galup-Montoro, 1998), not based on an empirical model such as (Fiorelli; Peralias; Silveira, 2011b). In addition, the proposed methodology also describes the design of a transformer to maximize the  $R_p$  seen by the cross-coupled differential pair. In this design, the required  $\omega_0$  is twice the operating frequency of the WiFi HaLow standard, i.e.  $2\pi \times 1.8$  GHz (in rads/sec).

The methodology is presented by the following steps: first is presented the transformer design and parameters extraction, the method to extract the parameters of the transistor is showed in section 4.3, the sizing of the transistor and the minimum  $V_{DD}$  required to sustain the oscillation are discussed in the sections 4.4 and 4.5 respectively.

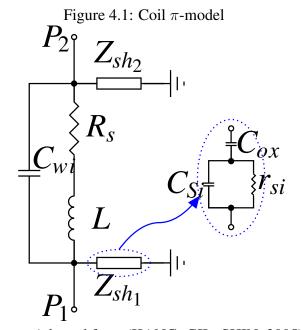

# 4.2 Transformer Design and Parameters Extraction

The first step in the design is related to the configuration of the transformer and to extract its equivalent time-domain model. The transformer is designed to achieve the maximum  $R_p$  possible. As described by Equation 3.1, the  $R_p$  depends on both quality factors of the primary and secondary coils. The coupled factor also impacts on the max-

imum achievable parallel resistance. The best-coupled method in the technology used (TSMC 28nm) is the planar one. This is due to there is only one ultra-thick metal in this technology. When there is a high difference in the sheet resistance to the metals of the primary and secondary coils the quality of the secondary coil, which is designed on the lower metal, is severely impacted. The best configuration of the number of turns to the primary and secondary must be checked too. There is an impact on the quality factor by the number of turns of both primary and secondary coils due to the crossing of metals. To check the best configuration to the transformer considering the number of turns and width of primary and secondary and better metals to primary and secondary, ASITIC and ADS from Keysight software are used.

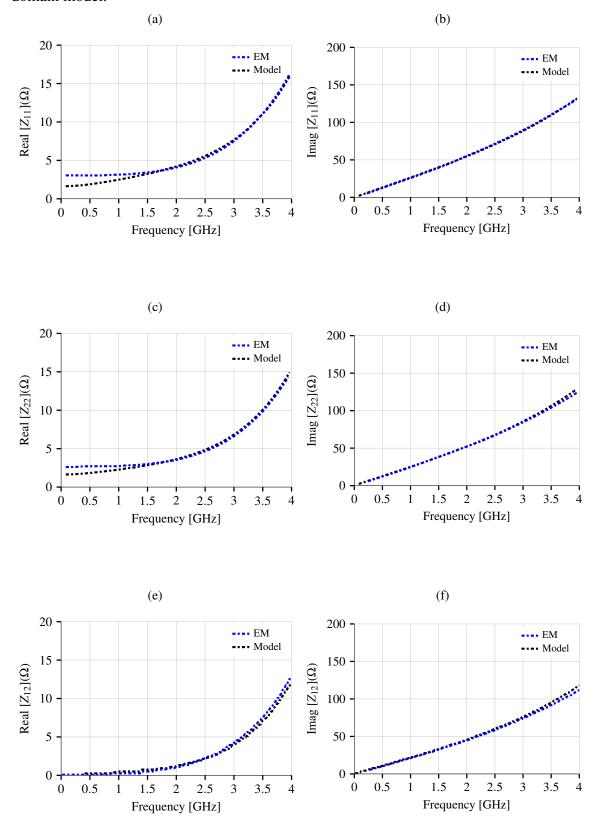

To extract the equivalent  $\pi$ -model of each coil from the S-parameter simulation. Each coil is extracted separately, first to obtain the  $\pi$ -model presented in Figure 4.1. Where  $R_s$ ,  $C_{wi}$ , and L are respectively the parasitic resistance, the inter-winding capacitance, and the inductance of the coil. Additionally, the impedances  $Z_{sh1-2}$  model the coupling to the substrate. Furthermore,  $P_1$  and  $P_2$  represents the two ports in the simulation. Each coil was simulated in a two-port electromagnetic simulation and the parameters are extracted from S-parameters results. First, the inductor L is extracted at low-frequency from the following equation (SCHIMPF; BENNA; PROETEL, 2001):

$$L = \frac{im\left[\frac{1}{Y_{21}}\right]}{U} \tag{4.1}$$

After computing the inductance, the inter-winding capacitance  $C_{wi}$  is extracted from the resonance of  $im(1/Y_{21})$  which results:

$$C_{wi} = \frac{1}{\omega^2 L} \tag{4.2}$$

The parasitic resistance  $(R_s)$  is also extracted from the low-frequency analysis of  $Y_{21}$  as follows:

$$R_s = real \left[ \frac{1}{Y_{21}} \right] \tag{4.3}$$

The first step is to extract the oxide capacitance  $(C_{ox})$  also from a low-frequency analysis. At low-frequencies, the influence from the substrate becomes negligible. The oxide capacitance from both sides of the model are extracted from the following equations

(KANG; GIL; SHIN, 2005):

$$C_{ox1} = -\frac{1}{\omega Im \left[\frac{1}{Y_{11} + Y_{12}}\right]} \tag{4.4}$$

$$C_{ox2} = -\frac{1}{\omega Im \left[ \frac{1}{Y_{22} + Y_{12}} \right]} \tag{4.5}$$

To compute the influence of the substrate, the analysis must be done at high-frequencies. Therefore, the  $r_{si}$  and  $C_{si}$  from both sides of the model are extracted at high frequencies using the following equations (CHEN et al., 2008):

$$r_{si1} = \frac{1}{Real \left[ Y_{11} + Y_{12} \right]} \tag{4.6}$$

$$r_{si2} = \frac{1}{Real\left[Y_{22} + Y_{12}\right]} \tag{4.7}$$

$$C_{si1} = \frac{Im\left[Y_{11} + Y_{12}\right]}{\omega} \tag{4.8}$$

$$C_{si2} = \frac{Im\left[Y_{22} + Y_{12}\right]}{\omega} \tag{4.9}$$

After computing all parameters of the  $\pi$ -model for each coil, a two-port electromagnetic simulation of the transformer must be performed to compute the coupling factor between two coils and then to obtain the model of Figure 3.4. The  $k_m$  is obtained from the Z-parameter simulation of the transformer, and it is given by (LEITE et al., 2009),

$$k_m = \sqrt{\frac{imag(Z_{12}) imag(Z_{21})}{imag(Z_{11}) imag(Z_{22})}}.$$

(4.10)

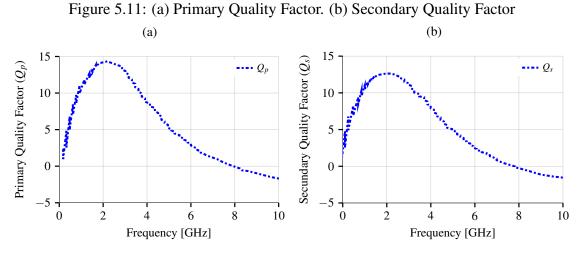

After computing the complete model of the transformer, a new simulation must be performed in order to execute the fine adjusts. In addition, the quality factor, which is defined by the ratio between the energy stored to the energy dissipated by Joule heating, for each coil of the transformer is computed from the 2-port electromagnetic simulation and are derived from the following equations:

$$Q_p = \frac{im(Z_{11})}{real(Z_{11})} \tag{4.11}$$

$$Q_s = \frac{im(Z_{22})}{real(Z_{22})} \tag{4.12}$$

Furthermore, the inductance of primary and secondary are extracted from the ratio of the imaginary part of the impedance to the  $\omega$  corresponding the frequency of operation. From the equations below are derived the primary and secondary inductances at a two port measurement.

$$L_p = \frac{im(Z_{11})}{\omega_0} \tag{4.13}$$

$$L_s = \frac{im(Z_{22})}{\omega_0} \tag{4.14}$$

The inductance ratio, which impacts directly on the transformer voltage gain, is derived from the following equation:

$$n_L = L_2/L_1 (4.15)$$

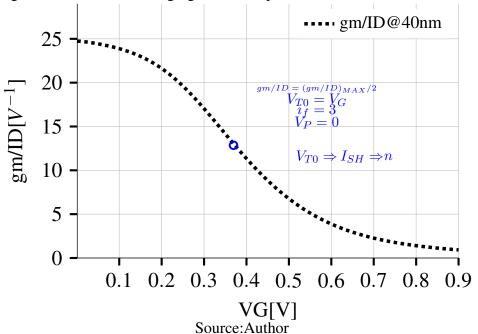

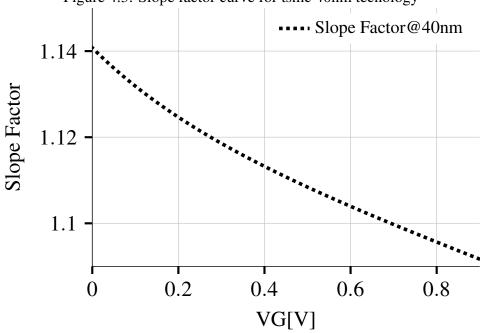

Source: Adapted from (KANG; GIL; SHIN, 2005)