## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### VANESSA FURTADO DE LIMA

## Single-Trimming Resistorless CMOS Sub-Bandgap Voltage References for High Precision Applications

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Advisor: Prof. Dr. Hamilton Duarte Klimach

#### CIP - CATALOGING-IN-PUBLICATION

Lima, Vanessa Furtado de

Single-Trimming Resistorless CMOS Sub-Bandgap Voltage References for High Precision Applications / Vanessa Furtado de Lima. – Porto Alegre: PGMICRO da UFRGS, 2021.

88 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2021. Advisor: Hamilton Duarte Klimach.

1. CMOS analog design. 2. Voltage reference. 3. High precision. 4. Trimming. 5. Low power. I. Klimach, Hamilton Duarte. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos André Bulhões Vice-Reitora: Prof<sup>a</sup>. Patricia Pranke

Pró-Reitora de Ensino: Profa. Cíntia Inês Boll

Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGMENTS**

First, I would like to thank my family for always supporting me. They always believed in the power of education, the importance of science, and taught me to seek knowledge.

Moreover, a special thanks to my advisor Prof. Hamilton Klimach, for always suggesting improvements, helping me, being an excellent teacher, and for being an example of a great professional. In these years, I've also learned so much from the people in Lab 110. I appreciated all the help I received from Prof. Bampi, Israel, Carlos, César, Bruno, and Diogo.

I entered in the microelectronics field because of the IC Brazil Program. Then, I am very honored to have been part of such a good experience that made me discover this amazing microelectronics world.

Finally, I am very grateful for the financial support from CAPES and IMEC/Mini@sic for chip fabrication.

## **ABSTRACT**

A voltage reference is a relevant circuit class since its output voltage should generate an accurate reference for many analog, mixed-signal, and digital applications. This type of circuit works based on the mutual compensation of the temperature dependencies of two electrical quantities. Considering that these quantities also depend on the fabrication process, the voltage reference performance is heavily affected by fabrication variability. The reduction or compensation of the variability impact on the reference performance is a considerable design challenge, required to increase its precision and robustness. Hence, this work proposes two sub-bandgap voltage references that are designed to reduce the variability impact on the reference voltage to enhance its precision. A BJT biasing circuit, a self-cascode MOSFET, an unbalanced differential pair and a high-slope PTAT structure were analyzed to understand how to minimize the main error sources, such as fabrication variability and intrinsic non-linearities. From this investigation, a sheet specific current  $(I_{SO})$  source was implemented for biasing a BJT to reduce the variability of its generated base-emitter voltage. Also, the self-cascode MOSFET and the unbalanced differential pair architectures were chosen to form the proposed voltage references. A single-point trimming strategy was presented to reduce the temperature sensitivity of the circuits. The voltage references topologies are analytically described and the UICM model was used to design the circuits. The circuits are resistorless and were designed in a 180 nm process. Also, the performance of the voltage references were evaluated through post-layout simulation. Then, the proposed sub-bandgap reference with self-cascode MOSFETs (SBSCM) presented a 592 mV reference voltage with a typical temperature coefficient (TC) of 3.6 ppm/°C, while consuming just 40.8 nW under 1.8 V of power supply. The sub-bandgap reference with an unbalanced differential pair (SBDF) resulted in a 607 mV reference voltage with a typical TC of 8.3 ppm/°C and consuming 40 nW under 1.8 V of supply voltage. Monte-Carlo simulations demonstrated the sensitivity of the implemented design to fabrication variability. Considering the variability impact and the trimming scheme, the SBSCM and the SBDF presented an average TC of 6.9 ppm/°C and 11 ppm/°C, respectively. The circuit's performance presented low power consumption and TC with an accurate output voltage while occupying a small silicon area.

**Keywords:** CMOS analog design, voltage reference, high precision, trimming, low power.

# Referências de Tensão Sub-Bandgap CMOS sem Resistores com um Único Ajuste para Aplicações de Alta Precisão.

### **RESUMO**

A referência de tensão é uma classe de circuito relevante já que sua tensão de saída deve gerar uma referência precisa para muitas aplicações analógicas, de sinais mistos e digitais. Esse tipo de circuito funciona baseado na compensação mútua de dependências de temperatura de duas grandezas elétricas. Considerando que essas grandezas também dependem do processo de fabricação, o desempenho das referências de tensão são profundamente afetadas pela variabilidade de fabricação. A redução ou compensação do impacto da variabilidade no desempenho da referência é um desafio considerável de projeto, necessário para aumentar sua precisão e robustez. Por isso, esse trabalho propõe duas referências de tensão do tipo sub-bandgap que são projetadas para reduzir o impacto da variabilidade na referência de tensão para aumentar a precisão. Um circuito de polarização de um transistor bipolar, um MOSFET self-cascode, um par diferencial desbalanceado e uma estrutura PTAT high-slope foram analisadas para identificar como minimizar as principais fontes de erros, como a variabilidade de fabricação e não-linearidades intrínsecas. A partir dessa investigação, uma fonte de corrente  $I_{SQ}$  foi implementada para alimentar um transistor bipolar e reduzir a variabilidade da tensão de base-emissor gerada. Além disso, as estruturas de MOSFET self-cascode e do par diferencial desbalanceado foram escolhidos para formar as referências de tensão propostas. Uma estratégia de calibração em um único ponto foi apresentada para reduzir a sensibilidade à temperatura do circuito. As topologias de referências de tensão são descrevidas analiticamente e o modelo UICM foi utilizado para projetar o circuito. Os circuitos não possuem resistores e foram projetados em um processo de 180 nm. Além disso, o desempenho dos circuitos é avaliado através de simulações feitas após o layout. Então, a referência sub-bandgap com MOS-FET self-cascode (SBSCM) apresentou uma referência de tensão de 592 mV com um coeficiente de temperatura (TC) típico de 3.6 ppm/°C, consumindo 40.8 nW com uma fonte de alimentação de 1.8 V. A referência sub-bandgap com o par diferencial desbalanceado (SBDF) resultou em uma referência de tensão de 607 mV com um TC típico de 8.3 ppm/°C e consumindo 40 nW com 1.8 V de tensão de alimentação. Simulações do tipo Monte Carlo demonstraram a sensibilidade do projeto implementado à variabilidade. Considerando o impacto da variabilidade e a calibração proposta, as referências SBSCM e SBDF apresentaram um TC médio de 6.9 ppm/°C e 11 ppm/°C, respectivamente. O desempenho dos circuitos apresentou um baixo consumo de potência e coeficiente de temperatura com uma tensão de saída precisa, ocupando uma pequena área de silício.

**Palavras-chave:** projeto analógico CMOS, referências de tensão, alta precisão, calibração, baixo consumo.

## **LIST OF FIGURES**

| 1.1<br>1.2 | Wireless electrochemical readout chip proposed by TSAI et al. (2018). System block diagram of the readout IC proposed by HUSSAINI | 16 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | et al. (2019)                                                                                                                     | 16 |

| 1.3        | Basic concept of a bandgap voltage reference                                                                                      | 17 |

| 1.4        | Temperature variation of a voltage reference                                                                                      | 18 |

| 2.1        | Schematic of the bandgap voltage reference proposed by WIDLAR                                                                     |    |

|            | (1971)                                                                                                                            | 20 |

| 2.2        | Topology of the bandgap voltage reference proposed by KUIJK (1973).                                                               | 20 |

| 2.3        | Bandgap voltage reference reported in BROKAW (1974)                                                                               | 20 |

| 2.4        | Voltage reference proposed by TSIVIDIS; ULMER (1978)                                                                              | 21 |

| 2.5        | Schematic of the PTAT cells proposed by VITTOZ; NEYROUD (1979).                                                                   | 22 |

| 2.6        | Bandgap voltage reference reported in MEIJER; SCHMALE; ZA-                                                                        |    |

|            | LINGE (1982)                                                                                                                      | 22 |

| 2.7        | Second-order temperature compensation proposed by SONG; GRAY                                                                      |    |

|            | (1983)                                                                                                                            | 23 |

| 2.8        | Sub-bandgap voltage reference reported in BANBA et al. (1999)                                                                     | 23 |

| 2.9        | Schematic of the resistorless bandgap voltage reference proposed by                                                               |    |

|            | BUCK et al. (2002)                                                                                                                | 23 |

| 2.10       | Voltage reference proposed by UENO et al. (2009)                                                                                  | 25 |

| 2.11       | Typical bandgap voltage reference reported in KUIJK (1973)                                                                        | 27 |

| 2.12       | Schematic of the bandgap voltage reference proposed by GE et al.                                                                  |    |

|            | (2011).                                                                                                                           | 28 |

| 2.13       | Architectures of proposed (a) BGR and (b) sub-BGR circuits pro-                                                                   | 20 |

| 2.14       | posed by OSAKI et al. (2013)                                                                                                      | 29 |

| 2.14       | Bandgap voltage reference proposed by OSAKI et al. (2013)                                                                         | 30 |

| 2.15       | Schematic of the switched bandgap reference proposed by KLIMACH                                                                   | 31 |

| 2.16       | et al. (2013)                                                                                                                     | 33 |

| 2.10       | Start-up circuit, reference current and CTAT generator reported in                                                                | 33 |

| 2.17       | ZHANG et al. (2018)                                                                                                               | 33 |

| 2.18       | Voltage reference proposed by OLIVEIRA et al. (2018)                                                                              | 35 |

| 2.19       | Bandgap concept presented in MING et al. (2018)                                                                                   | 36 |

| 2.19       | Schematic of the bandgap voltage reference proposed by MING et al.                                                                | 30 |

| 2.20       | (2018)                                                                                                                            | 37 |

| 2.21       | Bandgap concept proposed by ZHOU et al. (2019)                                                                                    | 38 |

| 2.22       | Bandgap voltage reference reported in ZHOU et al. (2019)                                                                          | 38 |

|            | Zumagup vottage telefence reported in Ziroo et al. (2017)                                                                         | 50 |

| 3.1  | BJT bias circuit proposed by MATTIA; KLIMACH; BAMPI (2014).                                 | 42 |  |

|------|---------------------------------------------------------------------------------------------|----|--|

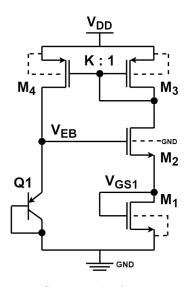

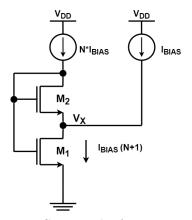

| 3.2  | Simulated BJT bias circuit schematic $(N = 2; K = 1)$                                       | 44 |  |

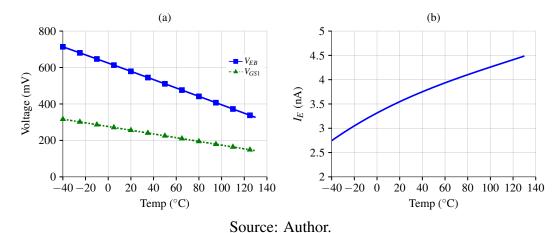

| 3.3  | (a) $V_{EB}$ and $V_{GS1}$ voltages over temperature; (b) $I_E$ current over temperature    |    |  |

| 2.4  | 1                                                                                           |    |  |

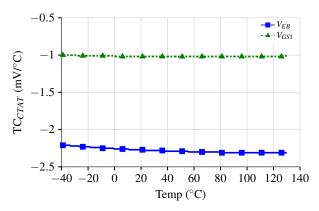

| 3.4  | $V_{EB}$ and $V_{GS1}$ derivatives over temperature                                         | 45 |  |

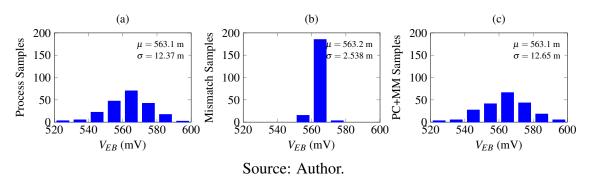

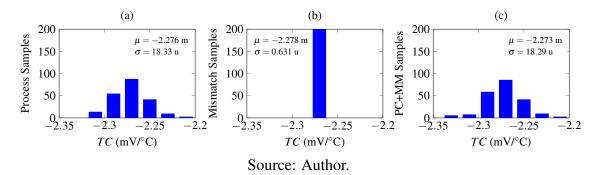

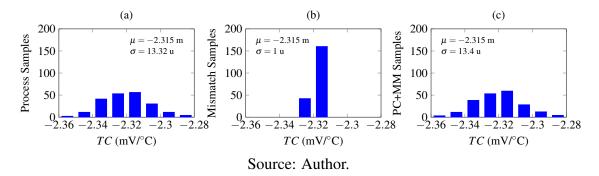

| 3.5  | MC simulations histograms of $V_{EB}$ voltage at 27°C. Average process                      |    |  |

|      | variation on (a); Local mismatch on (b); Combined on (c)                                    | 45 |  |

| 3.6  | MC simulations histograms of $TC$ . Average process variation on (a);                       |    |  |

|      | Local mismatch on (b); Combined on (c)                                                      | 45 |  |

| 3.7  | (a) Self-Cascode MOSFET PTAT generator and (b) unbalanced dif-                              |    |  |

|      | ferential pair schematic                                                                    | 47 |  |

| 3.8  | High-Slope PTAT generator schematic                                                         | 49 |  |

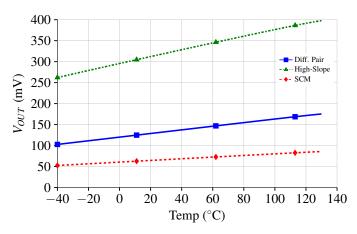

| 3.9  | PTAT voltages vs temperature                                                                | 50 |  |

| 3.10 | PTAT derivatives vs temperature                                                             | 51 |  |

| 3.11 | Cascaded (a) SCM and (b) unbalance differential pair topologies                             | 51 |  |

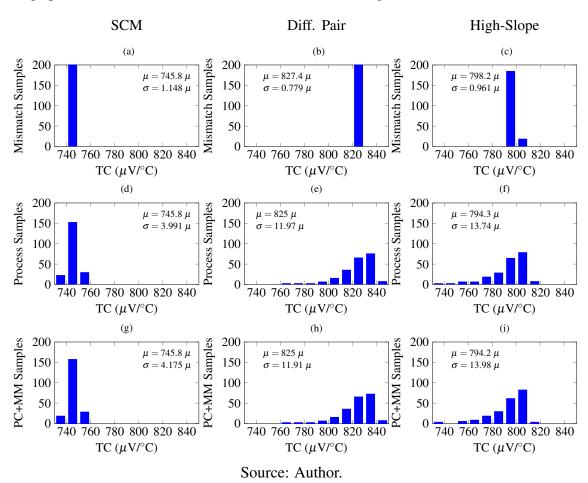

| 3.12 | MC simulations histograms of TC. Local mismatch on (a), (b) and                             |    |  |

|      | (c); Average process variation on (d), (e) and (f); Combined on (g),                        |    |  |

|      | (h) and (f)                                                                                 | 52 |  |

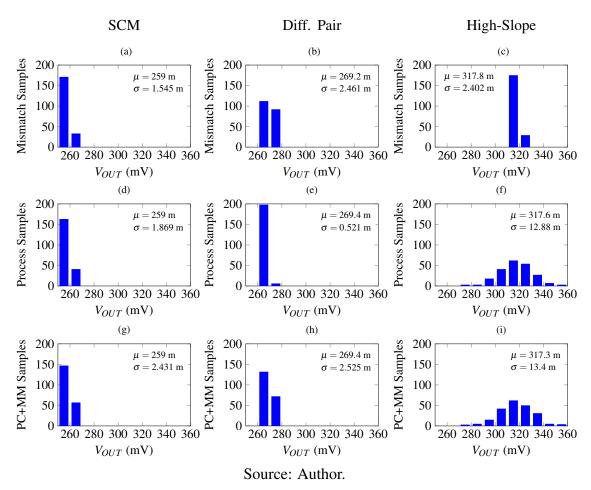

| 3.13 | MC simulations histograms of a PTAT output voltage at 27°C. Local                           |    |  |

|      | mismatch on (a), (b) and (c); Average process variation on (d), (e)                         |    |  |

|      | and (f); Combined on (g), (h) and (f)                                                       | 53 |  |

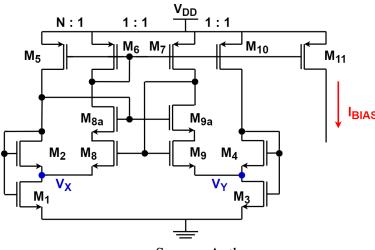

| 4.1  | $I_{SQ}$ current source presented in CAMACHO-GALEANO et al. (2008).                         | 55 |  |

| 4.2  | Biasing relations for the SCM                                                               | 55 |  |

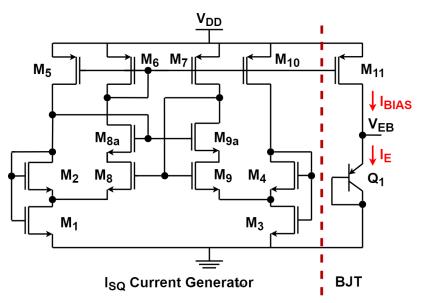

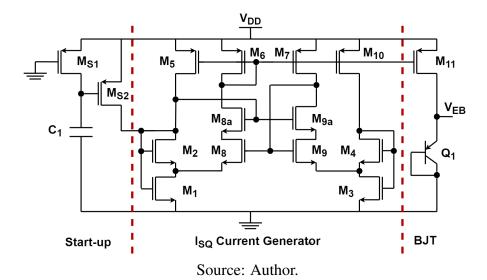

| 4.3  | $I_{SQ}$ current generator used to bias the $Q_1$ BJT                                       | 56 |  |

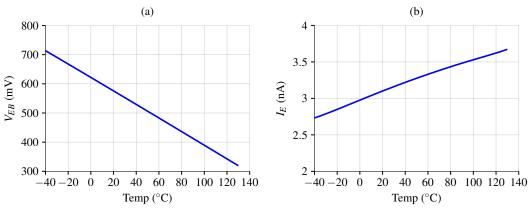

| 4.4  | (a) $V_{EB}$ voltage and (b) $I_E$ current over temperature                                 | 57 |  |

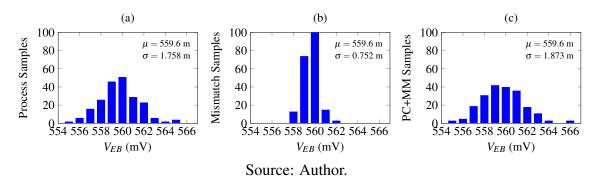

| 4.5  | MC simulations histograms of $V_{EB}$ voltage at 27°C. Average process                      |    |  |

|      | variation on (a); Local mismatch on (b); Combined on (c)                                    | 57 |  |

| 4.6  | MC simulations histograms of $TC$ . Average process variation on (a);                       |    |  |

|      | Local mismatch on (b); Combined on (c)                                                      | 58 |  |

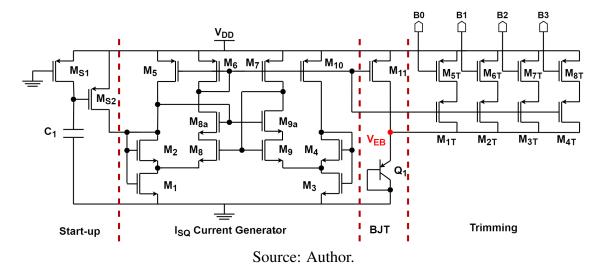

| 4.7  | BJT with $I_{SQ}$ current source and start-up circuit                                       | 58 |  |

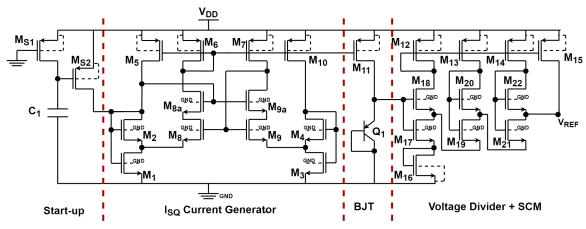

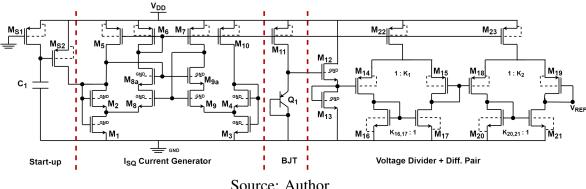

| 4.8  | Schematic of the proposed SBSCM reference circuit                                           | 59 |  |

| 4.9  | Schematic of the proposed SBDF reference circuit                                            | 61 |  |

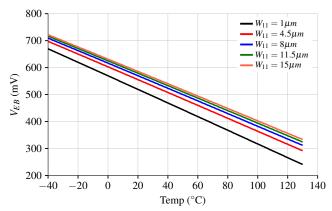

| 4.10 | $V_{EB}$ voltage over temperature with different $W_{11}$                                   | 63 |  |

| 4.11 | $V_{EB}$ voltage at 27°C over $W_{11}$                                                      | 64 |  |

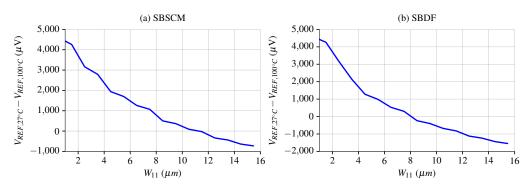

| 4.12 | $\Delta V_{REF(27,100^{\circ}C)}$ over $W_{11}$                                             | 64 |  |

| 4.13 | $\Delta V_{REF(27,100^{\circ}C)}$ over TC                                                   | 65 |  |

| 4.14 | BJT biasing circuit with a trimming structure                                               | 65 |  |

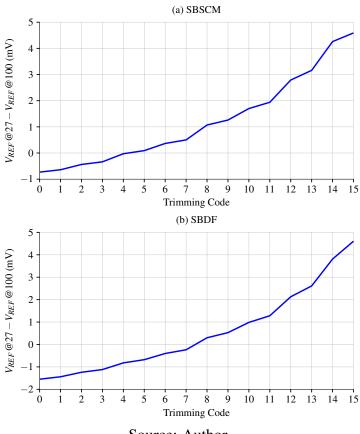

| 4.15 | $V_{REF,27^{\circ}C} - V_{REF,100^{\circ}C}$ voltage versus trimming code                   | 67 |  |

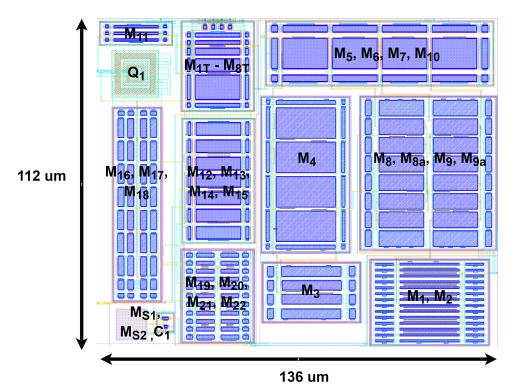

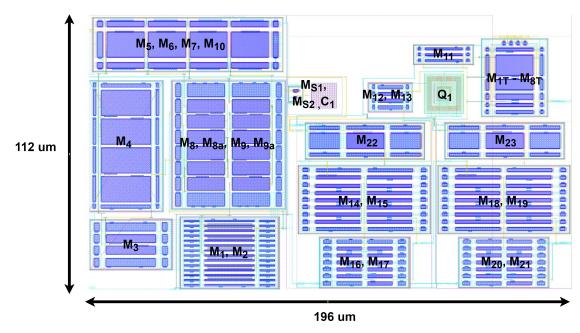

| 5.1  | Sub-bandgap with SCMs layout                                                                | 68 |  |

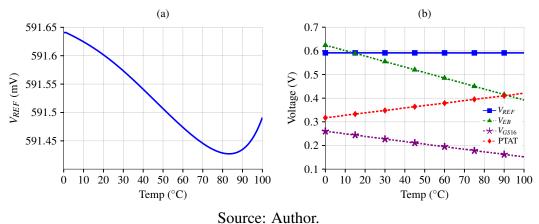

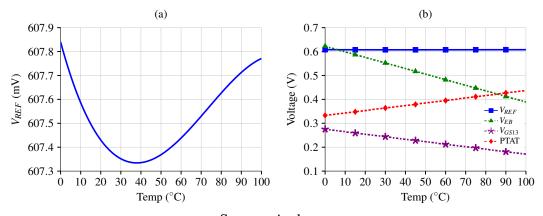

| 5.2  | (a) $V_{REF}$ ; (b) $V_{REF}$ , $V_{EB}$ , $V_{GS16}$ , and PTAT voltages over temperature. | 69 |  |

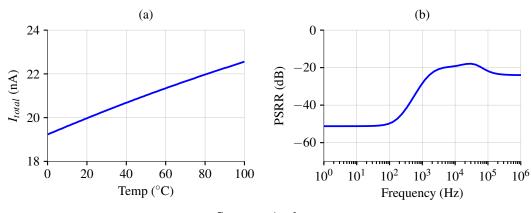

| 5.3  | (a) $I_{total}$ over temperature; (b) PSRR over frequency                                   | 69 |  |

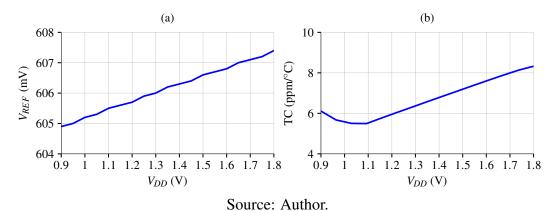

| 5.4  | (a) LS; and (b) TC over power supply                                                        | 70 |  |

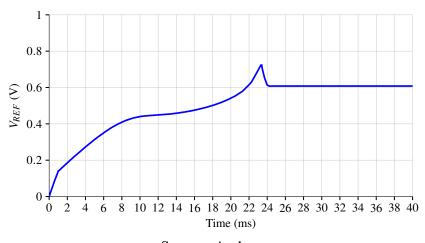

| 5.5  | Start-up behavior                                                                           | 70 |  |

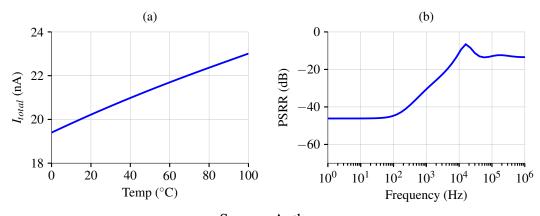

| 5.6  | $V_{REF}$ and TC Monte Carlo results (untrimmed). Local mismatch on                         |    |  |

|      | (a) and (b); Average process variation on (c) and (d); Combined on                          |    |  |

|      | (e) and (f)                                                                                 | 71 |  |

|      |                                                                                             |    |  |

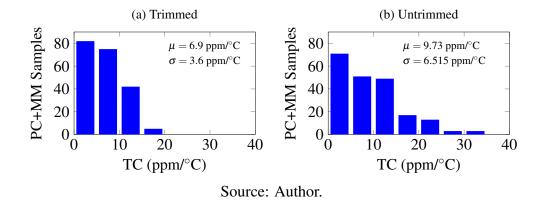

| 5.7  | Monte Carlo results of TC considering process and mismatch for                              |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | trimmed and untrimmed circuit                                                               | 72 |

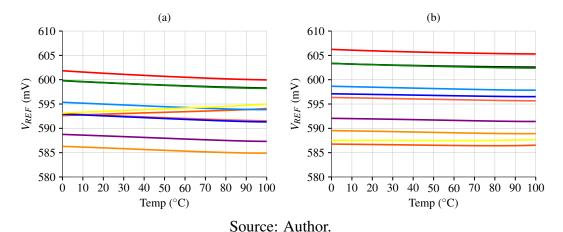

| 5.8  | Temperature dependence of $V_{REF}$ (a) before and (b) after trimming                       | 72 |

| 5.9  | Sub-bandgap with unbalanced differential pair layout                                        | 73 |

| 5.10 | (a) $V_{REF}$ ; (b) $V_{REF}$ , $V_{EB}$ , $V_{GS13}$ , and PTAT voltages over temperature. | 73 |

| 5.11 | (a) $I_{total}$ over temperature; (b) PSRR over frequency                                   | 74 |

| 5.12 | (a) LS; and (b) TC over power supply                                                        | 74 |

| 5.13 | Start-up behavior                                                                           | 74 |

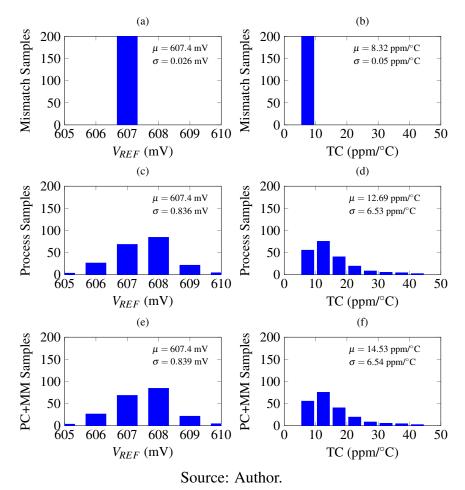

| 5.14 | $V_{REF}$ and TC Monte Carlo results. Local mismatch on (a) and (b);                        |    |

|      | Average process variation on (c) and (d); Combined on (e) and (f)                           | 75 |

| 5.15 | Monte Carlo results of TC considering process and mismatch for                              |    |

|      | trimmed and untrimmed circuit                                                               | 75 |

| 5.16 | Temperature dependence of $V_{REF}$ (a) before and (b) after trimming                       | 76 |

| D.1  | Trimming procedure flowchart                                                                | 88 |

## **LIST OF TABLES**

| 2.1 | Reported Results Summary in UENO et al. (2009)                                         | 27 |

|-----|----------------------------------------------------------------------------------------|----|

| 2.2 | Performance Summary GE et al. (2011)                                                   | 29 |

| 2.3 | Measured Results Summary OSAKI et al. (2013)                                           | 31 |

| 2.4 | Simulated Results Summary KLIMACH et al. (2013)                                        | 32 |

| 2.5 | Reported Results Summary in ZHANG et al. (2018)                                        | 34 |

| 2.6 | Measured Results Summary OLIVEIRA et al. (2018)                                        | 36 |

| 2.7 | Results Summary MING et al. (2018)                                                     | 37 |

| 2.8 | Measured Results Summary ZHOU et al. (2019)                                            | 39 |

| 2.9 | Comparison of Recent Published CMOS Voltage References                                 | 40 |

| 3.1 | Performance summary of the circuit in 180 nm CMOS at $V_{DD}$ = 1.8V.                  | 46 |

| 3.2 | Dimensions and $i_f$ of the transistors                                                | 50 |

| 3.3 | Performance comparison between PTAT circuits in 180 nm CMOS at $V_{DD} = 1.8 \text{V}$ | 53 |

| 4.1 | Dimensions of the MOSFETs                                                              | 56 |

| 4.2 | Performance comparison of BJT biasing in 180 nm CMOS at $V_{DD}$ = 1.8V                | 58 |

| 4.3 | Dimensions of the MOSFETs                                                              | 61 |

| 4.4 | Dimensions of the MOSFETs                                                              | 62 |

| 4.5 | $V_{EB}$ and $\partial V_{EB}/\partial T$ comparison for different $W_{11}$ sizes      | 63 |

| 4.6 | Dimensions of the MOSFETs                                                              | 66 |

| 4.7 | Trimming code associated to a binary word                                              | 66 |

| 5.1 | Performance summary of SBSCM                                                           | 72 |

| 5.2 | Performance summary of SBDF                                                            | 76 |

| 5.3 | Comparison of Recent CMOS Voltage References                                           | 78 |

## LIST OF ABBREVIATIONS AND ACRONYMS

AC Alternating Current

ADC Analog-to-Digital Converter

ASIC Aplication Specific Integrated Circuit

BEVL Base-Emitter Voltage Linearization

BGR Bandgap Reference

BJT Bipolar Junction Transistor

BVS Battery Voltage Supervisor

CMOS Complementary metal-oxide-semiconductor

CTAT Complementary to Absolute Temperature

DAC Digital-to-Analog Converter

DC Direct Current

FoM Figure of Merit

HOCCG High-order Curvature Compensation Generator

IC Integrated Circuit

IoT Internet of Things

IMEC Interuniversity Microelectronics Centre

LS Line Sensitivity

MC Monte Carlo

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor Field Effect Transistor

MM Mismatch

NMOS N-channel MOSFET

NWE Narrow-Width Effect

PC Process

PMOS P-channel MOSFET

PMU Power Management Unit

PSR Power Supply Rejection

PTAT Proportional to Absolute Temperature

RF Radio Frequency

RLSBCS Resistorless Self-Biased Current Sources

RSCE Reverse Short-Channel Effect

SBDF Sub-bandgap with Unbalanced Differential Pair

SBSCM Sub-bandgap with Self-Cascode MOSFETs

SCM Self-Cascode MOSFET

SoC System on Chip

TC Temperature Coefficient

TSMC Taiwan Semiconductor Manufacturing Company

UICM Unified Current-Control Model

ULP Ultra-low Power

VSC Voltage Step Compensation

WI Weak Inversion

WSN Wireless Sensor Networks

## **CONTENTS**

| 1 II                                                        | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                   |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.1                                                         | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                   |

| 1.2                                                         | Ideal Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                   |

| 1.3                                                         | Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                   |

| 1.4                                                         | Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                                   |

| 2 II                                                        | NTEGRATED VOLTAGE REFERENCES EVOLUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19                                                                   |

| 2.1                                                         | Classic References                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                   |

| 2.2                                                         | Performance and Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24                                                                   |

| 2.3                                                         | Recent Developments on CMOS Voltage References                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                   |

| 2.3.1                                                       | Self Cascode Cells and Diode-Connected NMOS                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                                                                   |

| 2.3.2                                                       | Bandgap Reference with a Single Trim                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26                                                                   |

| 2.3.3                                                       | Bandgap with Cascaded Differential Pairs                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                   |

| 2.3.4                                                       | A Switched-Capacitor Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                   |

| 2.3.5                                                       | Voltage Reference with High-Slope PTAT Generator                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                   |

| 2.3.6                                                       | A 3-Transistor Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                                   |

| 2.3.7                                                       | Bandgap Reference with Successive Voltage-Step Compensation                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                                                   |

| 2.3.8                                                       | Bandgap Reference with Base-Emitter Voltage Linearization                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                   |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| 2.3.6                                                       | Performance Summary of the State-of-The-Art                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                   |

| 2.4                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| 2.4                                                         | Performance Summary of the State-of-The-Art                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                   |

| 2.4<br>3 (                                                  | Performance Summary of the State-of-The-Art                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39<br>41                                                             |

| 2.4<br>3 0<br>3.1                                           | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit                                                                                                                                                                                                                                                                                                                                                    | 39<br>41<br>41                                                       |

| 2.4<br>3 (3.1<br>3.1.1                                      | Performance Summary of the State-of-The-Art                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39<br>41<br>41<br>42                                                 |

| 2.4 3 0 3.1 3.1.1 3.2                                       | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology                                                                                                                                                                                                                                                                                       | 39<br>41<br>41<br>42<br>45                                           |

| 2.4 3 (3.1 3.1.1 3.2 3.2.1                                  | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators                                                                                                                                                                                                                                                                                                                           | 39<br>41<br>41<br>42<br>45<br>46                                     |

| 2.4 3 (3.1) 3.1.1 3.2 3.2.1 3.2.2                           | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology                                                                                                                                                                                                                                                | 39<br>41<br>41<br>42<br>45<br>46<br>47                               |

| 2.4 3 (3.1) 3.1.1 3.2 3.2.1 3.2.2 3.2.3 3.2.4               | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology  High-Slope Topology                                                                                                                                                                                                                           | 39<br>41<br>41<br>42<br>45<br>46<br>47<br>48                         |

| 2.4 3.1 3.1.1 3.2 3.2.1 3.2.2 3.2.3 3.2.4 4 F               | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology  High-Slope Topology  Circuit Design and Performance Comparison                                                                                                                                                                                | 399<br>411<br>412<br>45<br>466<br>477<br>488<br>49                   |

| 2.4 3.1 3.1.1 3.2 3.2.1 3.2.2 3.2.3 3.2.4 4 F               | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology  High-Slope Topology  Circuit Design and Performance Comparison  PROPOSED SUB-BANDGAP VOLTAGE REFERENCES  BJT circuit with $I_{SQ}$ current  Sub-Bandgap Reference with Self-Cascode MOSFETs                                                   | 399<br>411<br>412<br>45<br>46<br>47<br>48<br>49<br>54                |

| 2.4 3                                                       | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology  High-Slope Topology  Circuit Design and Performance Comparison  PROPOSED SUB-BANDGAP VOLTAGE REFERENCES  BJT circuit with $I_{SQ}$ current                                                                                                    | 39<br>41<br>41<br>42<br>45<br>46<br>47<br>48<br>49<br>54             |

| 2.4 3.1 3.1.1 3.2 3.2.1 3.2.2 3.2.3 3.2.4 4 F 4.1 4.2       | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology  High-Slope Topology  Circuit Design and Performance Comparison  PROPOSED SUB-BANDGAP VOLTAGE REFERENCES  BJT circuit with $I_{SQ}$ current  Sub-Bandgap Reference with Self-Cascode MOSFETs                                                   | 39<br>41<br>41<br>42<br>45<br>46<br>47<br>48<br>49<br>54<br>54<br>59 |

| 2.4 3.1 3.1.1 3.2 3.2.1 3.2.2 3.2.3 3.2.4 4 F 4.1 4.2 4.2.1 | Performance Summary of the State-of-The-Art  CTAT AND PTAT VOLTAGE GENERATORS  CTAT Voltage Generators  Resistorless BJT Bias Circuit  PTAT Voltage Generators  Self-Cascode MOSFET (SCM) Topology  Unbalanced Differential Pair Topology  High-Slope Topology  Circuit Design and Performance Comparison  PROPOSED SUB-BANDGAP VOLTAGE REFERENCES  BJT circuit with $I_{SQ}$ current  Sub-Bandgap Reference with Self-Cascode MOSFETs  Design Methodology of the PTAT Voltage Generator | 39<br>41<br>41<br>42<br>45<br>46<br>47<br>48<br>49<br>54<br>59<br>60 |

| 5          | IMULATION RESULTS                                       | 68 |

|------------|---------------------------------------------------------|----|

| <b>5.1</b> | Sub-Bandgap Reference with Self-Cascode MOSFETs         | 68 |

| <b>5.2</b> | Sub-Bandgap Reference with Unbalanced Differential Pair | 71 |

| 5.3        | Comparison with the State-of-The-Art                    | 76 |

|            | Future Works                                            |    |

| RE         | ERENCES                                                 | 81 |

| ΑP         | ENDIX A LIST OF PUBLICATIONS                            | 85 |

| ΑP         | ENDIX B UICM MOSFET MODEL                               | 86 |

| ΑP         | ENDIX C MATLAB CODE                                     | 87 |

| ΑP         | ENDIX D TRIMMING PROCEDURE                              | 88 |

## 1 INTRODUCTION

In this chapter, we explore the importance and applications of voltage references in numerous electronic systems. First, the motivation for this work is defined as well as how the current performance requirements challenge the design of a voltage reference. Also, we discuss some necessities for circuits with low variability to increase the precision of a reference voltage. The concept of an ideal voltage reference is presented. Finally, we state the main objectives of this thesis and describe the work structure.

#### 1.1 Motivation

The emergence of Internet of Things (IoT) systems and their advances increasingly demand low power, low cost, and high precision integrated circuits. Nowadays, the IoT market comprises implantable medical devices, wearable electronics, wireless sensors, and energy harvesting systems. As power consumption is a significant concern, IoT devices can be battery powered or include a self-powering solution such as a harvesting system.

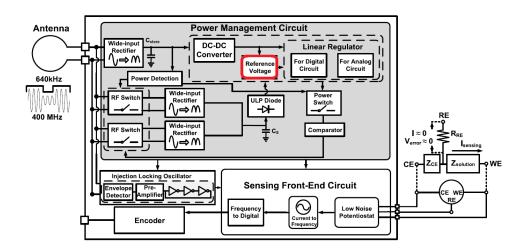

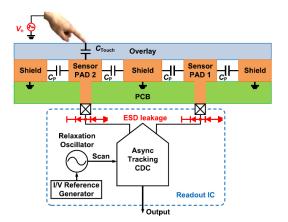

Considering these market trends, a batteryless transceiver for wireless sensor networks (WSN) that allows a maintenance-free operation was developed by PAPOTTO et al. (2014). Another batteryless and self-powered device was proposed by HUANG et al. (2014), where a system on chip (SoC) was designed to monitor real-time multiple physiological parameters for a biomedical purpose. Moreover, for battery operated applications LEE et al. (2016) proposed a battery voltage supervisor (BVS) that monitors the energy transferred from the energy harvester to a battery and avoids permanent damage in the power system. Also, a power management unit (PMU) which can be connected to Li-ion batteries was presented by SHI et al. (2018). An application specific integrated circuit (ASIC) for power management of batteryless wireless sensors was implemented in FAN et al. (2018). This proposed ASIC integrates a power management system with a temperature sensor. Focusing on chemical sensing, TSAI et al. (2018) proposed a wirelessly-powered electrochemical readout interface circuit as shown in Fig. 1.1. The power management block delivers a stable power supply to the sensor considering the environmental variations that change RF power magnitude collected through a harvesting system. In wearable and mobile devices, sleep modes are commonly employed to avoid recharging the system battery several times a day. Therefore, an event-detector sensor is used in a watchdog circuit to wake up the device. For this purpose, HUSSAINI et al. (2019) proposed a readout circuit for capacitive touch sensors, as shown in Fig. 1.2. In CMOS image sensors, a temperature sensing for thermal management has been used to optimize the image sensor accuracy since the circuit can be thermal sensitive. Then, XIE; THEUWISSEN (2019) presented an on-chip smart temperature sensor for image sensors that can also be implemented for thermal sensing network.

Figure 1.1: Wireless electrochemical readout chip proposed by TSAI et al. (2018).

Source: TSAI et al. (2018).

Figure 1.2: System block diagram of the readout IC proposed by HUSSAINI et al. (2019).

Source: HUSSAINI et al. (2019).

In all these cited developments, a voltage reference circuit is needed. Therefore, it shows that voltage references are indispensable building blocks of many analog, mixed-signal, radio-frequency, and even digital circuits, providing references for on-chip power management systems, for smart sensors, for signal conditioning and signal measurement, or for build blocks such as analog to digital converters (ADCs) and digital to analog converters (DACs). Moreover, the reference voltage accuracy certainly determines the maximum achievable performance of its biased circuits, demonstrating that a high precision voltage reference is fundamental in a microelectronic system.

The reference voltage is required to be almost independent of supply voltage, temperature, and process variations. Therefore, considering the companies established priority to design reliable, low voltage and high precision integrated circuits (ICs), the development and improvements in voltage references blocks are extremely important nowadays. The voltage reference performance suffers from the limited controllability of the fabrication steps and the effect of variability on the reference signal sometimes is not discussed in

detail. However, it is relevant because these fabrication uncertainties produce significant variations in voltage reference circuits and degrade the reference accuracy. Therefore, it impacts on manufacturing cost by increasing trimming requirements, test time, circuit complexity, and decreasing yield. Then, the reduction or compensation of the fabrication variability impact on the reference performance is a great design challenge required to increase its precision and robustness.

There are several approaches to design voltage references in CMOS technology and throughout the years some solutions were proposed in order to improve the performances of these circuits. Amongst state-of-the-art circuits, one can find voltage references designed to meet the demanding low power consumption, low supply voltage and small area requirements. However, it is difficult to find strategies that combine low voltage and power consumption, low temperature sensitivity and low fabrication variability impact.

## 1.2 Ideal Voltage Reference

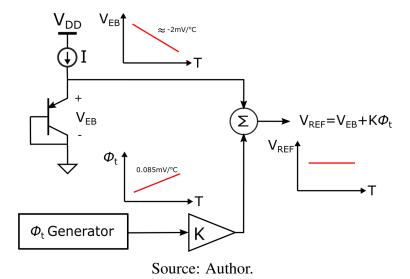

An ideal voltage reference is a circuit that generates an output voltage insensitive to variations in temperature, operating voltage, load current, and fabrication variability. The bandgap voltage reference (BGR) is a commonly applied voltage reference circuit, and its basic concept is shown in Fig. 1.3. Essentially, a voltage reference works based on the mutual compensation of temperature dependencies of two electrical quantities. The temperature-independence is achieved by adding a voltage proportional to absolute temperature (PTAT) with a voltage that is complementary to absolute temperature (CTAT). This bandgap voltage reference generates a reference voltage of approximately 1.23 V, that is approximately the extrapolated bandgap potential of Silicon.

Figure 1.3: Basic concept of a bandgap voltage reference.

The ideal behavior of a reference voltage is degraded by multiple sources of errors that affect the circuit. Hence, the nonlinear terms of the CTAT and PTAT voltages generate a curvature error resulting in a significant temperature coefficient, as shown in Fig. 1.4. Also, mismatches, offsets, second-order effects, supply voltages variations, and process deviations decrease the voltage reference accuracy.

Figure 1.4: Temperature variation of a voltage reference.

## 1.3 Objectives

Considering the important role of voltage references for biasing IC blocks, this thesis primary purpose is to develop voltage reference circuits that present a high performance combining low power consumption and low fabrication variability to achieve the current precision and robustness requirements for microelectronics systems. This work also aims to study and analyze distinct circuit structures to propose performance improvements in the voltage reference design.

## 1.4 Organization

This work is organized as follows: a review on the evolution of integrated voltage references, followed by a chronological survey of recent developments, and a performance comparison between the state-of-art circuits are presented in Chapter 2. In Chapter 3, a detailed analysis of CTAT and PTAT voltage generators is discussed to explore the limitations of each studied structure. Then, Chapter 4 presents the proposed idea to develop two voltage references designs and a trimming technique to enhance circuit performance. Chapter 5 shows the post-layout simulation results of the proposed circuits and summarizes the performance of the voltage reference with other published works. Finally, Chapter 6 presents our main conclusions and explores future steps through this research topic.

## 2 INTEGRATED VOLTAGE REFERENCES EVOLUTION

This chapter presents a chronological review of earlier voltage references designs. Also, the main performance metrics of voltage reference circuits are presented. Then, we expose the most recent developments in the area and the last section evaluates recent advances.

### 2.1 Classic References

The concept of a bandgap reference was proposed by HILBIBER (1964) but the first practical implementation was presented by WIDLAR (1971). Widlar's reference did not use zener diode as previous discrete circuits employed (HILBIBER, 1964). Thus, the voltage reference proposed by Widlar implemented bipolar technology using the positive temperature coefficient of emitter-base differential voltage of two transistors operating at different emitter current densities, that is proportional to the thermal voltage  $\phi_T$ , added to a negative temperature coefficient of a transistor emitter-base voltage. The idea is the mutual compensation of these temperature dependencies. Therefore, a simple weighted sum between these two voltages generates a low temperature coefficient reference voltage of 1.205 V (i.e., approximately the silicon bandgap voltage).

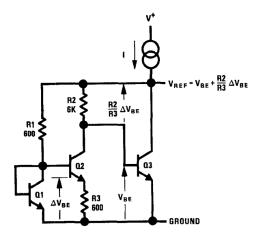

The BGR circuit is shown in Fig. 2.1. In this circuit  $Q_1$  operates with a high current density, the current density of  $Q_2$  is about 10 times lower, and the emitter-base voltage difference  $\Delta V_{BE}$  between  $Q_1$  and  $Q_2$  appears across  $R_3$ .  $Q_3$  is defined as a gain stage that regulates the output voltage formed by the  $Q_3$  emitter-base voltage  $V_{BE}$  plus the drop across  $R_2$ , that is proportional to  $\Delta V_{BE}$ , since currents in  $R_2$  and  $R_3$  are approximately the same.

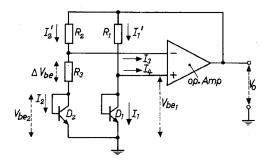

Another topology for a bandgap voltage was proposed by KUIJK (1973), as shown in Fig. 2.2. This circuit uses two bipolar junction transistors (BJTs) connected as diodes and an operational amplifier. The emitter-base voltage difference  $\Delta V_{BE}$  appears across  $R_3$  and defines the emitter current  $I_2$ , which is proportional to absolute temperature. The BJT  $D_1$  shows a proportional decrease with temperature. Thus, to provide a temperature independent output  $V_o$  the resistors values of  $R_1$ ,  $R_2$  and  $R_3$  need to be adjusted.

One year later, BROKAW (1974) presented a BGR that uses two BJTs and collector-current sensing to establish the bandgap voltage. As shown in Fig. 2.3, the circuit regulates the transistors base voltage making the collector currents  $I_{C1}$  and  $I_{C2}$  match. The  $\Delta V_{BE}$  between  $Q_1$  and  $Q_2$  appear across  $R_2$  and current in  $R_1$  is twice that in  $R_2$ . The voltage across  $R_1$  varies directly with temperature. Then, this voltage is used to compensate the negative temperature coefficient of  $V_{BE}$ . The output voltage  $V_{OUT}$  is the sum of  $V_{BE,Q1}$  and the voltage across  $R_1$ .

In 1977, Eric Vittoz established the weak inversion (WI) operation of MOS transistors

Figure 2.1: Schematic of the bandgap voltage reference proposed by WIDLAR (1971).

Source: WIDLAR (1971).

Figure 2.2: Topology of the bandgap voltage reference proposed by KUIJK (1973).

Source: KUIJK (1973).

Figure 2.3: Bandgap voltage reference reported in BROKAW (1974).

Source: BROKAW (1974).

for CMOS analog integrated circuits. The weak inversion (or subthreshold) operation was described by a model suitable for circuit design and also verified experimentally in VITTOZ; FELLRATH (1977). Circuits like current references, a quartz oscillator, and a bandpass amplifier were implemented using the WI operation and were able to prove the WI operation reliability.

The first CMOS voltage reference using WI operation was published by TSIVIDIS; ULMER (1978). In this work, a positive temperature coefficient was developed with a MOSFET unbalanced differential pair in WI. Then, the difference of the gate-to-source voltage ( $V_{GS}$ ) of two MOS transistors ( $M_1$  and  $M_2$ ) in WI region and biased with different currents densities resulted in a PTAT voltage. For satisfactory temperature compensation, the PTAT voltage generators ( $M_1$ - $M_2$ ) were cascaded in series to achieve a higher voltage. The negative temperature coefficient voltage is generated through a bipolar transistor Q. The CTAT and PTAT voltages are added to form the output voltage  $V_O$ . The proposed bandgap voltage reference with transistors operating in WI is shown in Fig. 2.4.

Figure 2.4: Voltage reference proposed by TSIVIDIS; ULMER (1978).

Source: TSIVIDIS; ULMER (1978).

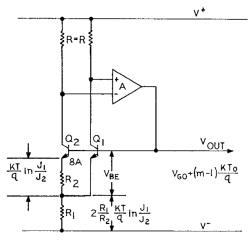

Although TSIVIDIS; ULMER (1978) used transistors in WI, the need to sum up three gate-to-source voltages did not let the circuit operate with low supply voltages. Therefore, in 1979, Vittoz developed a novel PTAT voltage generator. This circuit is composed of stacked self-cascode PTAT voltage generators with transistors operating in WI as shown in Fig. 2.5. Employing this novel PTAT cell, a CMOS bandgap reference voltage was proposed (VITTOZ; NEYROUD, 1979). The reference voltage was generated by a base-emitter voltage of a bipolar transistor combined with the stacked self-cascode PTAT voltage generator. Results showed that the bandgap reference operated with a supply voltage as low as 1.3 V and a drain current below  $1\mu\text{A}$ .

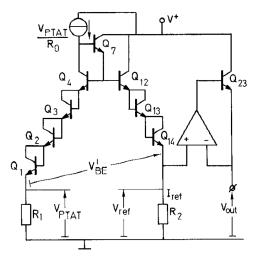

Seeking to reduce the temperature dependence of a bandgap reference output voltage, Meijer proposed a circuit configuration for compensating the thermal nonlinearity of the BJT base-emitter voltage (MEIJER; SCHMALE; ZALINGE, 1982). Meijer stated that for a BJT biased by a PTAT current, the thermal nonlinearity in  $V_{BE}$  is about 25% less than that of a BJT biased at a constant current. Then, the nonlinearity of  $V_{BE}$  is dependent on the bias current. So, the nonlinearity compensation can be optimized by properly choosing the bias current. The curvature-corrected bandgap circuit is shown in Fig. 2.6. In this topology the base-emitter junctions of  $Q_1$ - $Q_4$  are biased by a PTAT current and a temperature independent current ( $I_{ref}$ ) biases the base-emitter junctions of  $Q_{12}$ - $Q_{14}$ . Thus, subtracting  $V_{BE}$  of  $Q_{12}$ - $Q_{14}$  from  $V_{BE}$  of  $Q_1$ - $Q_4$  resulted in a voltage  $V_{BE}'$  with a improved thermal linearity. The series resistor  $R_1$  canceled the linear portion of  $V_{BE}'$  temperature dependence resulting in a reference voltage at the emitter of  $Q_{14}$ . The  $I_{ref}$  current is obtained when a temperature-independent resistor is employed for  $R_2$ . Finally, the output voltage ( $V_{out}$ ) is regulated by the series transistor  $Q_{23}$  and the error amplifier.

Figure 2.5: Schematic of the PTAT cells proposed by VITTOZ; NEYROUD (1979).

Source: VITTOZ; NEYROUD (1979).

Figure 2.6: Bandgap voltage reference reported in MEIJER; SCHMALE; ZALINGE (1982).

Source: MEIJER; SCHMALE; ZALINGE (1982).

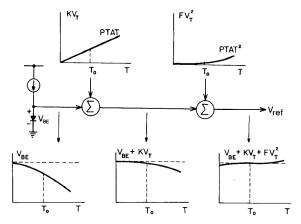

In order to further improve the temperature stability of the bandgap reference, SONG; GRAY (1983) implemented a second-order temperature compensation. The proposed reference added linear and quadratic PTAT correction voltages to  $V_{BE}$ . Then, the reference voltage ( $V_{ref}$ ) should drift only due to higher order temperature variations; this concept is shown in Fig. 2.7.

Through the years, the CMOS technology supply-voltage downscaling increased the demand for novel bandgap topologies to meet this requirement. Then, BANBA et al. (1999) proposed a sub-bandgap reference (Sub-BGR) circuit to operate with sub-1 V supply. As shown in Fig. 2.8, the reference voltage is determined mainly by the resistance ratio of R2, R3, and R4, indicating that this circuit can provide a wide range of output values. Therefore, the supply voltage for the proposed bandgap can be lowered according to  $V_{ref}$ , demonstrating the sub-1 V operation.

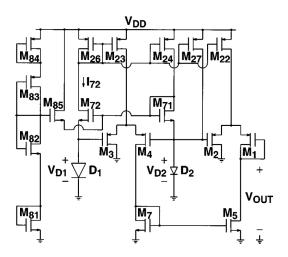

The use of resistors inevitably increases the chip size, and it also results in an increased cost of fabrication. To overcome these drawbacks, BUCK et al. (2002) presented a BGR without resistors. The proposed circuit is shown in Fig. 2.9. The difference between

Figure 2.7: Second-order temperature compensation proposed by SONG; GRAY (1983).

Source: SONG; GRAY (1983).

Figure 2.8: Sub-bandgap voltage reference reported in BANBA et al. (1999).

Source: BANBA et al. (1999).

the forward bias voltages across two diodes ( $\Delta V_D = V_{D2} - V_{D1}$ ) is multiplied by a gain obtained by using ratioed transistors with the inverse function technique (TORRANCE; VISWANATHAN; HANSON, 1985) to generate the PTAT term. This term is compensated by the CTAT behavior of the diode D1, resulting in an output voltage that is equal to a reference voltage.

Figure 2.9: Schematic of the resistorless bandgap voltage reference proposed by BUCK et al. (2002).

Source: BUCK et al. (2002).

#### 2.2 Performance and Metrics

The performance of a voltage reference circuit is quantified by many specification parameters, and one of the most important is the temperature coefficient (TC). Considering that the circuit physical characteristics vary with the temperature, the TC is a fundamental parameter that measures the maximum sensitivity of the reference voltage over a defined temperature range, and it is usually given in ppm/°C. The TC can be expressed as (GRAY; MEYER, 1993)

$$TC = \frac{V_{REFmax} - V_{REFmin}}{(T_{max} - T_{min})V_{REF27^{\circ}C}} \times 10^{6}$$

(2.1)

where  $V_{REFmax}$  and  $V_{REFmin}$  are the maximum and minimum reference voltage values within the operating temperature range  $(T_{max} - T_{min})$  and  $V_{REF27^{\circ}C}$  is the reference voltage at 27 °C.

Another relevant metric is the reference voltage sensitivity on supply voltage variations. This dependency is known as Line Sensitivity (LS) if related only to DC, and its unit is %/V. The LS can be written as

$$LS = \frac{\Delta V_{REF}}{\Delta V_{DD} \times V_{REF\mu}} \times 100\%$$

(2.2)

where  $\Delta V_{REF}$  is the difference of the reference voltage within the supply voltage  $(V_{DD})$  range considered,  $\Delta V_{DD}$  is the operating  $V_{DD}$  range and  $V_{REF\mu}$  is the mean value of the reference voltage within the  $\Delta V_{DD}$ .

Power Supply Rejection (PSR) is the circuit ability to reject AC interferences coming from the supply voltage and measured in dB over a defined frequency range. The PSR is defined as

$$PSR = 20 \log \left( \frac{V_{REF,AC}(f)}{V_{DD,AC}(f)} \right)$$

(2.3)

where  $V_{REF,AC}(f)$  is an AC coupled reference voltage at the output of the voltage reference circuit and  $V_{DD,AC}(f)$  is the power supply with incoming noise at a frequency f (KOK; TAM, 2013).

Variability impacts the circuit performance and can be classified by two kinds of variations: process and mismatch. Process variation is defined as an uncertainty that affects similar devices of a circuit in the same way and then does not produce mismatch among these devices. It impacts only the performance parameters that depend on the absolute value of physical quantities. Mismatch variations can be explained as an uncertainty that affects each similar device of a circuit differently and then produces mismatch among these devices. It also impacts performance parameters that depend on the ratio of physical quantities.

Thus, the reference voltage variation due to fabrication variability or variability coefficient can be quantified by the standard deviation and mean value ratio  $(\sigma/\mu)$  and is given in %. The variability also impacts the TC because, within several samples of voltage references, different temperature sensitivities are found. Hence, it is essential to evaluate the minimum, average, and maximum TC. Furthermore, classical specifications are important, such as: silicon area, power consumption, and minimum supply voltage.

A Figure of Merit (FoM) can be used to provide a comparative result that represents the overall performance of a voltage reference. Prof. Willy Sansen proposed a FoM that considers the main performance parameters, such as temperature range, TC, power consumption, and silicon area, and can be defined as follows (SANSEN, 2015)

$$FoM_{Sansen} = \frac{(T_{max} - T_{min})^2}{TC.Power.Area} \cdot \frac{1}{10^{16}}$$

(2.4)

However, this FoM does not consider the voltage reference deviation due to the variability impact. Additionally, the power consumption and silicon area have the same emphasis of TC on (2.4). Thus, for a better evaluation of a voltage reference considering high precision applications, we propose a similar FoM, expressed in (2.5), where  $V_{REF}$   $\sigma/\mu$  parameter is the reference voltage relative deviation considering fabrication variability.

$$FoM = \frac{T_{max} - T_{min}}{(TC)^2 \cdot Power \cdot Area \cdot (V_{REF} \sigma/\mu)^2} \cdot \frac{1}{10^{23}}$$

(2.5)

In this new FoM, the TC and  $V_{REF}$   $\sigma/\mu$  are squared because theses parameters are a priority when generating an accurate reference voltage. The power consumption and silicon area are still present to meet the demanding low power consumption and small area requirements. The temperature range of the voltage reference is also a relevant parameter that is considered in this FoM. The division by  $10^{23}$  was added for better visualization of the FoM values.

All these metrics are used to analyze voltage references designs and to evaluate the recent circuits presented in the next section.

## 2.3 Recent Developments on CMOS Voltage References

#### 2.3.1 Self Cascode Cells and Diode-Connected NMOS

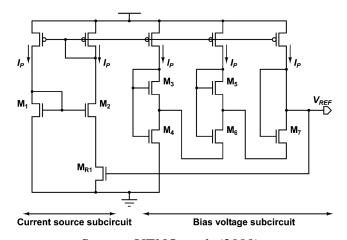

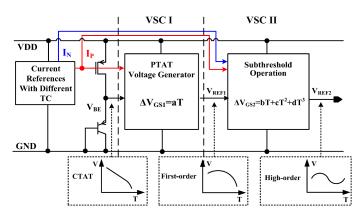

The circuit in UENO et al. (2009) consists of subthreshold MOSFETs and uses no resistors. The schematic of the voltage reference is shown in Fig. 2.10.

Figure 2.10: Voltage reference proposed by UENO et al. (2009).

Source: UENO et al. (2009).

A current source circuit generates a current  $I_P$ . Through a current mirror, the two self-cascode PTAT generators and the diode-connected NMOS are biased by  $I_P$ . The gate-source voltage  $V_{GS1}$  is equal to the sum of gate-source voltage  $V_{GS2}$ , and drain-source voltage  $V_{DSR1}$ . The drain-source voltage  $V_{DSR1}$  can be written as

$$V_{DSR1} = n\phi_T ln(\frac{S_2}{S_1}) \tag{2.6}$$

where n is the subthreshold slope factor,  $\phi_T$  is the thermal voltage and S is the aspect ratio (W/L).

The bias current  $I_P$  in M1 and M2 are equal and is given by

$$I_{P} = S_{R1}\mu C_{OX}(V_{REF} - V_{TH})n\phi_{T}ln(\frac{S_{2}}{S_{1}})$$

(2.7)

where  $\mu$  is the carrier mobility,  $C_{OX}$  is the gate-oxide capacitance and  $V_{TH}$  is the threshold voltage of a MOSFET.

The gate-source voltages  $(V_{GS3}-V_{GS7})$  form a closed loop and the reference voltage  $V_{REF}$  is given by

$$V_{REF} = V_{GS4} - V_{GS6} - V_{GS5} + V_{GS7} = V_{TH} + n\phi_T ln(\frac{3I_P}{S_4 I_0}) + n\phi_T ln(\frac{2S_3 S_5}{S_6 S_7}) \quad (2.8)$$

where  $I_0 = \mu C_{OX}(n-1)\phi_T^2$ .

The threshold voltage has a CTAT behavior and  $\phi_T$  a PTAT behavior. Thus, from expression (2.8), the reference voltage can be obtained by adjusting the transistors ratios. A zero TC can be achieved by setting the aspect ratios  $S_i$  considering  $\partial V_{REF}/\partial T=0$ . The authors stated that the generated reference voltage equals to the threshold voltage of MOSFETs at 0 K ( $V_{TH0}$ ). The current  $I_P$  can be rewritten as

$$I_P = S_{R1} \mu C_{OX} k n \phi_T ln(\frac{S_2}{S_1})$$

(2.9)

where k is the TC of  $V_{TH0}$ . This expression (2.9) demonstrate that the current is independent of  $V_{TH0}$ . The parameter k suffer less impact of process variability than  $V_{TH0}$ . Thus,  $I_P$  is less affected by process variations. However, since  $V_{REF} = V_{TH0}$  the reference voltage is less accurate due to process variation. The authors designed the circuit using large values for W and L and appropriate layout techniques to reduce the mismatch impact, but the reference will still significantly deviate due to process variability.

The TC of the reference voltage depends on channel doping concentration  $(N_A)$ , and this concentration is process-dependent. Although TC can change with process variation, this change is minimal because the authors calculated that TC is a logarithmic function of  $N_A$ . Moreover, computer simulations showed that the threshold voltage changes by  $\pm 20\%$  with  $N_A$  and its TC by  $\pm 2\%$

The authors fabricated the proposed circuit in a standard  $0.35~\mu m$  CMOS process and measured 17 samples from the same wafer. Table 2.1 presents the performance summary of the prototype chip. Analyzing the measured results, one can confirm the impact of process variability in the reference voltage. Therefore, a trimming scheme can be useful to this topology to correct its deviation due to variability. It is also relevant to avoid an output voltage that depends on the threshold voltage of transistors due to its process variations.

### 2.3.2 Bandgap Reference with a Single Trim

GE et al. (2011) proposed a BGR with a trimming circuit to compensate process variations and achieve an accurate reference. First, the authors studied error sources in a typical bandgap topology (KUIJK, 1973), as shown in Fig. 2.11. The nonlinear temperature dependence of the BJT base-emitter voltage  $V_{BE}$ , the opamp offset, and process variation of  $V_{BE}$  and  $V_{BE}$  difference ( $\Delta V_{BE}$ ) are factors that degrade the precision of a voltage reference.

| Specification         | This work                 |

|-----------------------|---------------------------|

| Process               | $0.35~\mu\mathrm{m}$ CMOS |

| Temp. Range           | -20 - 80 °C               |

| Supply Voltage        | 1.4 - 3 V                 |

| $\overline{}V_{REF}$  | 745 mV                    |

| $V_{REF} \sigma/\mu$  | 0.87 %                    |

| $TC_{avg}$            | 15 ppm/°C                 |

| $\overline{TC_{min}}$ | 7 ppm/°C                  |

| $TC_{max}$            | 45 ppm/°C                 |

| Line Sensitivity      | 20 ppm/V                  |

| PSRR                  | -45dB(@100 Hz)            |

| Power Consumption     | 0.3 μW(@1.4 V)            |

| Silicon Area          | $0.055 \text{ mm}^2$      |

Table 2.1: Reported Results Summary in UENO et al. (2009).

Figure 2.11: Typical bandgap voltage reference reported in KUIJK (1973).

Source: GE et al. (2011).

The  $V_{BE}$  is determined by its collector current  $I_C$  and saturation current  $I_S$ . Considering that  $I_S$  deviates from its nominal value,  $V_{BE}$  can be written as

$$V_{BE} = \phi_T ln \frac{I_C}{I_S + \Delta I_S} \tag{2.10}$$

where  $\phi_T$  is the thermal voltage and  $\Delta I_S$  the deviation of  $I_S$ . Therefore, the  $V_{BE}$  spread due to the saturation current spread is PTAT and can be removed by a PTAT trim. The collector current  $I_C$  can also deviate as a result of resistance variations of  $R_1$  and  $R_2$ . Considering the resistance spread as a fractional deviation  $\delta_R$ ,  $V_{BE}$  can be rewritten as

$$V_{BE} = \phi_T ln \frac{\frac{I_C}{1 + \delta_R}}{I_S}.$$

(2.11)

Assuming  $\delta_R$  is temperature independent, expression (2.11) demonstrate that this  $V_{BE}$  variation is also PTAT. Finally, BJT current gain  $\beta_F$  impact  $V_{BE}$  and if  $\beta_F$  deviates from its nominal value,  $V_{BE}$  is given by

$$V_{BE} = \phi_T ln(\frac{I_E}{I_S} \frac{\beta_F + \Delta \beta_F}{1 + \beta_F + \Delta \beta_F})$$

(2.12)

where  $I_E$  is the emitter current of the BJT, and  $\Delta \beta_F$  is the deviation of  $\beta_F$ . All these PTAT deviations can be reduced by a single room temperature trim.

The PTAT term in a BGR is generated by two BJTs biased at different current densities and  $\Delta V_{BE}$  can be written as

$$\Delta V_{BE} = \frac{R_1}{R_2} \phi_T ln(\frac{I_{C1}}{I_{C2}}N)$$

(2.13)

where  $I_{C1}$  and  $I_{C2}$  are collector currents of  $Q_1$  and  $Q_2$ . Then, the temperature drift of these collector currents will degrade the bandgap voltage  $(V_{BG})$  accuracy. To overcome this error, a matched resistor based topology was employed. The authors stated that the resistor mismatch is more stable over temperature.

The offset of an opamp is typically non-PTAT; therefore, it is difficult to reduce with a PTAT trim. Thus, the offset can be removed by a chopping technique. This chopping is better than the auto-zeroing technique in terms of noise performance and because the opamp output is continuously available. The curvature correction of  $V_{BE}$  follows MEIJER; SCHMALE; ZALINGE (1982).

The BGR is shown in Fig. 2.12, and it was fabricated in a standard 0.16  $\mu$ m CMOS process and measured 61 samples from the two batches. Table 2.2 summarizes the performance of the proposed bandgap reference. This circuit achieved excellent results in terms of variability. However, the main drawback is the power dissipation. Such a high power consumption is due to the sophisticated strategies that were used to reduce variability deviations.

Figure 2.12: Schematic of the bandgap voltage reference proposed by GE et al. (2011).

Source: GE et al. (2011).

#### 2.3.3 Bandgap with Cascaded Differential Pairs

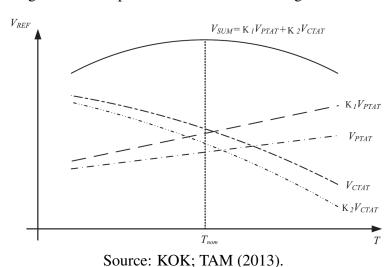

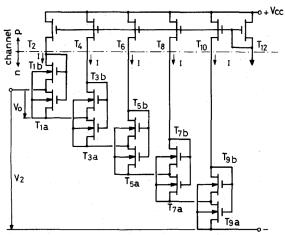

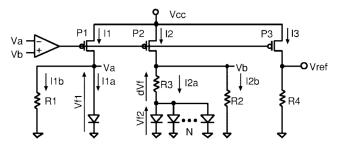

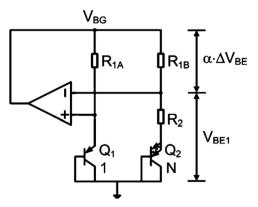

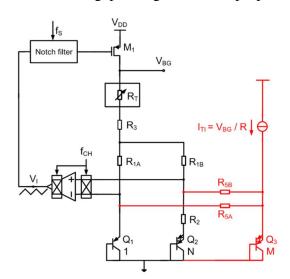

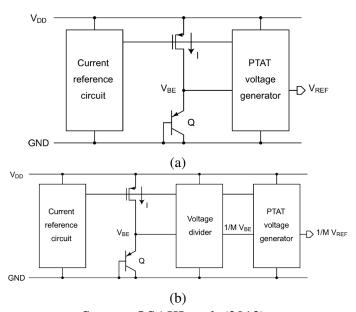

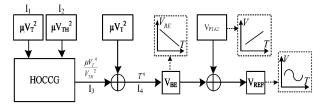

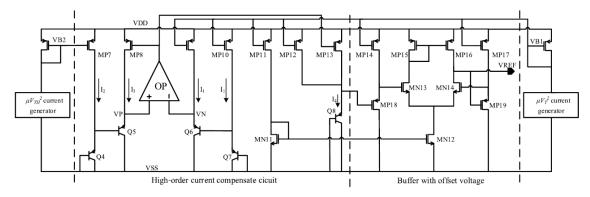

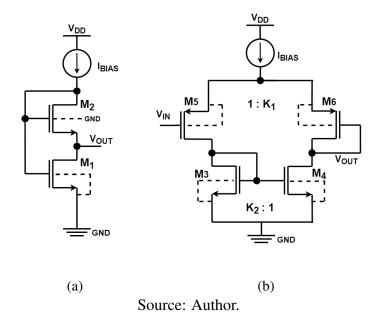

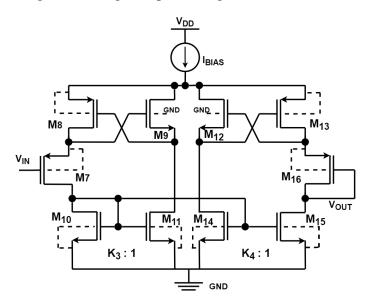

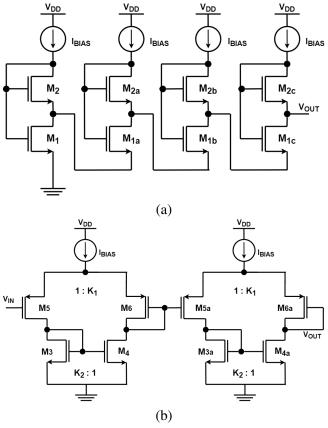

All-MOSFETs voltage references usually operate with low power consumption because of the WI operation of transistors. However, these circuits provide reference voltages based on the threshold voltage of MOSFETs. Classical bandgap topologies use BJT and resistors to generate a PTAT voltage, which impact on power consumption and silicon area. Then, OSAKI et al. (2013) implemented a topology employing a BJT to generate the CTAT voltage and cascaded MOSFETs unbalanced differential pairs as the PTAT term. The authors proposed a resistorless bandgap and a sub-bandgap circuit, and its architectures are shown in Fig. 2.13.

| Specification        | This work                 |

|----------------------|---------------------------|

| Process              | $0.16~\mu\mathrm{m}$ CMOS |

| Temp. Range          | -40 - 125 °C              |

| Supply Voltage       | 1.8 V                     |

| $V_{REF}$            | 1.0875 V                  |

| $V_{REF} \sigma/\mu$ | 0.05 <sup>a</sup> %       |

| $TC_{min}$           | 5 <sup>a</sup> ppm/°C     |

| $TC_{max}$           | 12 <sup>a</sup> ppm/°C    |

| PSRR                 | 74dB(@DC)                 |

| Power Consumption    | 99 μW                     |

| Silicon Area         | $0.12 \text{ mm}^2$       |

Table 2.2: Performance Summary GE et al. (2011).

<sup>a</sup>Trimmed;

Figure 2.13: Architectures of proposed (a) BGR and (b) sub-BGR circuits proposed by OSAKI et al. (2013).

Source: OSAKI et al. (2013).

The PTAT voltage is generated through a differential pair with a current mirror, illustrated in Fig. 2.14. Considering MOSFETs in WI operation, their gate-to-gate voltage  $V_{GG}$  can be expressed as

$$V_{GG} = V_{GS,D2} - V_{GS,D1} = n\phi_T ln(\frac{S_{D1}S_{M2}}{S_{D2}S_{M1}})$$

(2.14)

where  $V_{GS,D1}$  and  $V_{GS,D2}$  are gate-source voltages of  $M_{D1}$  and  $M_{D2}$ ,  $\phi_T$  is the thermal voltage and S is the aspect ratio (W/L), and n is the subthreshold slope factor. Thus, the PTAT term can be adjusted by the aspect ratios of transistors  $M_{D1}$ ,  $M_{D2}$ ,  $M_{M1}$  and  $M_{M2}$ . To achieve a PTAT voltage that is able to cancel the  $V_{BE}$  temperature behavior, the differential pairs can be cascaded, resulting in a total gate-to-gate voltage  $V_{GG}$  given by

$$\sum_{i=1}^{N} V_{GG,i} = \sum_{i=1}^{N} n\phi_T ln(\frac{S_{D2i-1}S_{M2i}}{S_{D2i}S_{M2i-1}})$$

(2.15)

where N is the number of differential pairs. So, the output voltage  $V_{REF}$  can be written as

$$V_{REF} = V_{BE} + \sum_{i=1}^{N} n\phi_T ln(\frac{S_{D2i-1}S_{M2i}}{S_{D2i}S_{M2i-1}})$$

(2.16)

and from expression 2.16 it is possible to achieve the bandgap voltage of the silicon by appropriate choice of N and aspect ratio os transistors.

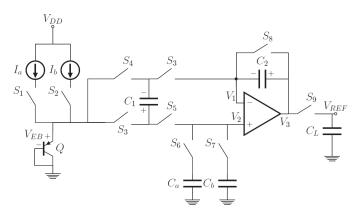

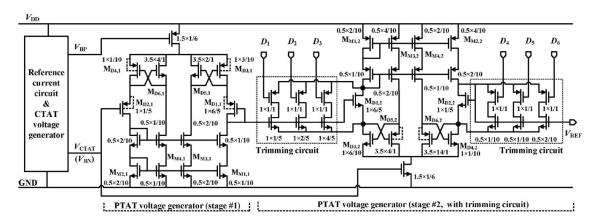

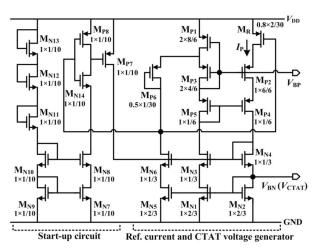

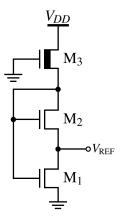

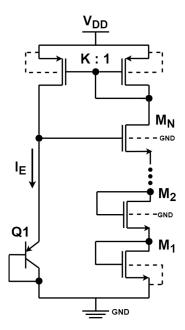

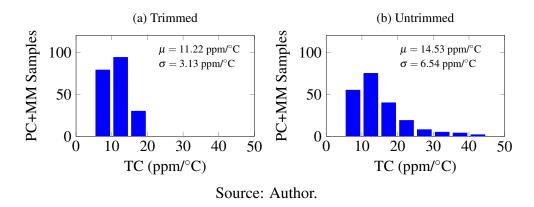

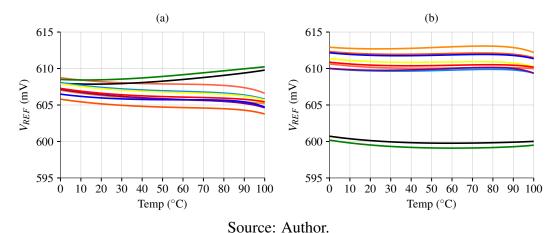

A nano-ampere current reference circuit was used to bias the BJT and the PTAT term through current mirrors. This bias current also impacts on  $V_{BE}$  deviations. Then, it was chosen a reference current that generates a bias current tolerant with threshold voltage variations.