#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### THIAGO SANTOS COPETTI

### Reliability Evaluation of FinFET-based SRAMs in the Presence of Resistive Defects

Thesis presented in partial fulfillment of the requirements for the degree of PhD in Microelectronics

Advisor: Prof. Dr. Tiago Roberto Balen Coadvisor: Prof<sup>a</sup>. Dr<sup>a</sup>. Letícia Maria Bolzani

Poehls

#### **CIP** — **CATALOGING-IN-PUBLICATION**

Copetti, Thiago Santos

Reliability Evaluation of FinFET-based SRAMs in the Presence of Resistive Defects / Thiago Santos Copetti. – Porto Alegre: PGMICRO da UFRGS, 2021.

121 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2021. Advisor: Tiago Roberto Balen; Coadvisor: Letícia Maria Bolzani Poehls.

1. FinFET. 2. SRAM. 3. Resistive Defects. 4. SPICE. 5. TCAD. 6. Reliability. 7. Single Event Transient Modeling. I. Balen, Tiago Roberto. II. Poehls, Letícia Maria Bolzani. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos André Bulhões

Vice-Reitora: Profa. Patricia Helena Lucas Pranke

Pró-Reitor de Pós-Graduação: Prof. Júlio Otávio Jardim Barcellos

Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### THIAGO SANTOS COPETTI

## Reliability Evaluation of FinFET-based SRAMs in the Presence of Resistive Defects

Orientador: Dr. Tiago Roberto Balen

Coorientador: Dra. Letícia Maria Bolzani Poehls

# DEDICATION

I dedicate this work to my wife, my parents, and my siblings.

#### **ACKNOWLEDGMENT**

Firstly, I would like to thank my advisors and friends, Prof. Dr. Tiago Balen that gave me support, guidance, and all the instructions that he gave me all these years during my doctorate for the development of this work, and Prof. Dr. Letícia Poehls for all the incentives and guidance for me to continue my studies after my master's graduation.

I want to thank the colleagues from three research groups that were important to me through my formation. First, the Laprot/UFRGS group welcomed me when I come to UFRGS. It was important the companionship of Dr. Raphael Brum, Dr. Thiago Both, Dr. Alan Rossetto, Dr. Fabio Vidor, M.Sc. Gabriela Furtado, M.Sc. Paulo Aguirre, Dr. Pablo Vaz, and also Prof. Dr. Wilson Wirth.

Other important colleagues are from the EASE / PUCRS laboratory, where I did the master course, and I keep in contact through my coadvisor. So, I would like to thanks the contribution of Eduardo Brum and mainly M.Sc. Guilherme Medeiros contributed a lot to this work with discussions and the development of the first model of tool used in this work by the time he spent at PUCRS, and also he helped me with guidance and companionship during that time I was abroad during my internship.

Also, I acknowledge Prof. Dr. Said Hamdioui that receive and oriented me through the six months period abroad in the group of Computer Engineering at TU Delft in the Netherlands, together with the assistance of Dr. Mottaqiallah Taouil. Then, I want to thank the companionship of the group members: Dr. Cezar Reinbrecht, M.Sc Troya Koylu, and M.Sc. Moritz Fieback.

I want to thank my parents, Humberto and Maria Copetti, for all the support and encouragement to keep studying all my life. My bother and sisters, Ing. Lucas, Cristina, and Camila Copetti, for their continuous encouragement. Also, I want to give a special acknowledgment to my wife Eliza Vargas that I met while I was at the end of my doctorate, and we got married this year. She always supported and encouraged me to improve my work, even that it had cost the time that I have to spend with her.

Finally, I would like to thank the Federal University of Rio Grande do Sul and the PPGMICRO for the opportunity, structure, and resources to give my research and for the Capes that gave me my doctorate scholarship and my sandwich scholarship to the Delft University of Technology, which I also am grateful for its reception and accommodation.

#### **ABSTRACT**

The development of Fin Field Effect Transistor (FinFET) has made possible the continuous scaling-down of Complementary Metal-Oxide-Semiconductor (CMOS) technology, overcoming issues caused by the Short-Channel Effects. In parallel, the increasing need to store more and more information has resulted in the fact that Static Random-Access Memories (SRAMs) occupy a great part of integrated systems. Manufacturing process deviations have introduced different types of defects, strong and weak, that directly affect the SRAM's reliability, causing different faults. One of the main factor that reduces the reliability and the lifetime of the FinFET-based SRAMs are the weak resistive defects. Weak resistive defects are considered the most important cause of test escapes, since opposing the strong resistive defects, that is easily detectable, weak defects require more than one consecutive operation for being propagated at logic level. In this context, this work investigates resistive defect implications on the reliability of FinFET-based SRAMs along with the combined effects of ionizing particle impacts in the SRAM transistors considering the presence of such resistive defects. Firstly, a study on functional implications regarding manufacturing resistive defects in FinFET-based SRAMs is presented. In more detail, a complete analysis of static and dynamic fault behavior is performed through electrical simulations of FinFET-based SRAMs considering different technological nodes. The results show that the sensitivity to this kind of defect is related to the size of technology, in which higher technological nodes are more sensitive to open defects and smaller technologies are sensitive to bridge defects. Secondly, a TCAD model of a FinFET-based SRAM cell was developed in order to allow the evaluation of cell sensitivity to ionizing particles causing Single Event Upsets (SEUs). In this part of the work was developed a new model representing ion strike in FinFET-based SRAM cells. Then, SPICE simulations were performed considering the current pulse parameters obtained with TCAD. Finally, weak resistive defects are injected into the FinFET-based SRAM cell. Results show that weak defects may have either a positive or negative influence on the cell reliability, depending on the position where it is, against SEUs caused by ionizing particles.

**Keywords:** FinFET. SRAM. Resistive Defects. SPICE. TCAD. Reliability. Single Event Transient Modeling.

#### **RESUMO**

O desenvolvimento do Fin Field Effect Transistor (FinFET) tornou possível a redução contínua da tecnologia Complementary Metal-Oxide-Semiconductor (CMOS), contornando os problemas causados pelos efeitos de canal curto. Paralelamente, a crescente necessidade de armazenar grande quantidade de informação resultou no fato de que Static Random-Access Memories (SRAM) ocupam grande parte dos sitemas integrados. A variabilidade dos processos de fabricação pode causar vários tipos de defeitos, fortes e fracos, que afetam diretamente a confiabilidade de SRAMs, propagando diferentes tipos de falhas. Um dos principais fatores que reduzem a confiabilidade e a vida útil das SRAMs baseadas em FinFET são os defeitos resistivos fracos. Os defeitos resistivos fracos são considerados a causa mais importante de "test escape", pois ao contrário dos defeitos resistivos fortes, que são facilmente detectáveis, os defeitos fracos requerem mais de uma operação consecutiva para serem propagados em nível lógico Neste contexto, além da investigação dos defeitos resistivos fracos, este trabalho propõe investigar os efeitos de impacto de partículas ionizantes na confiabilidade de SRAMs baseadas em FinFET na presença destes defeitos. Primeiramente, é apresentado um estudo das implicações funcionais de defeitos resistivos de manufatura em SRAMs baseadas em FinFET. Mais detalhadamente, uma análise completa do comportamento de falha estática e dinâmica é realizada por meio de simulações elétricas em um bloco de memória SRAM baseado em tecnologia FinFET, considerando diferentes nós tecnológicos. Os resultados mostram que o grau de sensibilidade ao tipo de defeito está relacionado ao tamanho da tecnologia, sendo que nodos tecnológicos maiores são mais sensíveis a defeitos de circuito aberto (open) e tecnologias menores são mais sensíveis a defeitos de curto circuito (bridges). Posteriormente, um modelo TCAD de uma célula SRAM baseada em FinFET foi desenvolvido para permitir a avaliação do impacto de partículas ionizantes que causam o Single Event Upsets (SEUs). Nesta parte do trabalho, foi desenvolvido um novo modelo de curva para a representar o ataque iônico em células SRAM baseadas em FinFET. Em seguida, foram realizadas simulações SPICE considerando os parâmetros do pulso de corrente obtidos com o simulador TCAD. Finalmente, defeitos resistivos fracos foram injetados na célula SRAM baseada em FinFET. Os resultados mostram que defeitos fracos podem ter uma influência positiva ou negativa na confiabilidade das células contra SEUs causados por impacto de partículas ionizantes.

**Palavras-chave:** FinFET, SRAM, Defeitos Resistivos, SPICE, TCAD, Confiabilidade, Modelagem de *Single Event Transient*.

#### LIST OF ABBREVIATIONS AND ACRONYMS

A-CELL Aggressor cell

ASET Analog Single Event Transient

ASU Arizona State University

BL Bit Line

BOX Buried Oxide

BPTM Berkeley Predictive Technology Model

BSIM Berkeley Short-channel Insulated Gate Field Effect Transistor Model

CMG Common MultiGate

CMOS Complementary Metal-Oxide-Semiconductor

DC Direct Current

dDRDF dynamic Deceptive Read Destructive Fault

DELTA Depleted Lean-Channel Transformer

DGFET Double-Gate Field Effect Transistor

DGMOS Double-Gate Metal-Oxide-Semiconductor

DIBL Drain-Induced Barrier Lowering

dIRF dynamic Incorrect Read Fault

DRAM Dynamic Random Access Memory

DRDF Deceptive Read Destructive Fault

dRDF dynamic Read Destructive Fault

El Electrostatic Integrity

FDSOI Fully Depleted SOI

FET Field Effect Transistor

FFM Functional Fault Model

FinFET Fin Field Effect Transistor.

FOX Field Oxide

FP Fault Primitive

GAA gate-all-around

GOS Gate Oxide Short

HD High-Density

HFin Height of Fin

HP High-performance

IC Integrated Circuit

IGFET Insulated Gate Field Effect Transistor

ILD Inter Layer Dielectric

IRF Incorrect Read Fault

ITRS International Technology Roadmap for Semiconductors

LET Linear Energy Transfer

LP Low Power

LSTP Low-STandby Power

LV Low Voltage

MBU Multi-Bit Upset

MCU Multi-Cell Upset

MIGFET Multiple Independent Gate Field Effect Transistor

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

MuG Multiple-Gate

NFin Number of Fin

NMOS Negative Metal-Oxide-Semiconductor

PD Pull-Down

PDK Process Design Kit

PDSOI Partially Depleted Silicon-On-Insulator

PG Pass Gate

PMOS Positive Metal-Oxide-Semiconductor

PTM Predictive Technology Model

PTM-MGPredictive Technology Model for Multi-Gate

PU Pull-Up

PUCRS Pontifícia Universidade Católica do Rio Grande do Sul

RAM Random Access Memory

RDF<sup>1</sup> Random Dopant Fluctuations

RDF<sup>2</sup> Read Destructive Fault

RF Radio Frequency

SCE Short-Channel Effect

SEB Single Event Burnout

SEE Single Event Effect

SEFI Single Event Functional Interrupt

SEL Single Event Latch-up

SET Single Event Transient

SEU Single Event Upset

SoC Systems on Chip

SOF Stuck-Open Fault

SOI Silicon-On-Insulator

SRAM Static Random Access Memory

SNM Static Noise Margin

STI Shallow Trench Isolation

TCAD Technology Computer-Aided Design

TF Transition Fault

TFin Thickness of Fin

TSMC Taiwan Semiconductor Manufacturing Company

UFRGS Universidade Federal do Rio Grande do Sul

UTBB Ultra-thin Body and Buried Oxide

V-CELL Victim cell

VDSM Very Deep Sub-micron

VDT Voltage-Doping Transformation

VTC Voltage Transfer Characteristic

WL Word Line

#### LIST OF SYMBOLS

A ampere

CF<sub>ds</sub> Disturb Coupling Fault

CF<sub>ir</sub> Incorrect Read Coupling Fault

CF<sub>rd</sub> Read Disturb Coupling Fault

CF<sub>tr</sub> Transition Coupling Fault

cm Centimeter

cm<sup>2</sup> Centimeter squared

d Material density

e Electronic Charge

F Faulty behavior observed

GaAs Gallium Arsenide

GHz Gigahertz

GND Ground

HfO<sub>2</sub> Hafnium Oxide

$k\Omega$  Kilo ohms

$I_{DS}$  Current of drain to source

$I_{off}$  Off Current

$I_{\it off\_norm}$  Normalized Off Current

I<sub>peak</sub> Peak Current

I<sub>plateau</sub> Plateau Current

I<sub>sat</sub> Saturated Current

Isat\_norm Normalized Saturated Current

$I_{Thresh}$  Threshold Current

L Channel length

$L_{eff}$  Effective channel length

LET\_f Threshold Linear Energy Transfer as a function of the length

LET<sub>th</sub> Threshold Linear Energy Transfer

MeV Mega Electron Volt

mg Milligram

nm Nanometer

ns Nanosecond

pA Picoampere

pC Picocoulomb

ps Picosecond

Q<sub>crit</sub> Critical Charge

Q<sub>coll</sub> Collected Charge

Q<sub>dep</sub> Deposited Charge

Q<sub>exc</sub> Excess Charge

Q<sub>exc\_alt</sub> Altered Excess Charge

Qexc\_nom Nominal Excess Charge

R Output or read operation

R<sub>crit</sub> Critical Resistance

S Sensitizing sequence

S<sub>aa</sub> Stress aggressor-aggressor

S<sub>av</sub> Stress aggressor-victim

Si Silicon

$S_{va}$  Stress victim-aggressor

$S_{\nu\nu}$  Stress victim-victim

T Device Thickness

$t_{dep}$  Thickness of deep electric field penetration

TiN Titanium Nitride

Trademark Trademark

$t_{ox}$  Thickness of gate oxide

$V_{bi}$  Built-in voltage

V<sub>DD</sub> Voltage drain supply

$V_{DS}$  Voltage of drain to source

$V_{GS}$  Voltage of gate to source

$V_{TH}$  Threshold voltage

$V_{THCC}$  Short channel threshold voltage

$V_{TH\infty}$  Long channel threshold voltage

W Channel width

W<sub>eff</sub> Effective channel width

W<sub>min</sub> Minimum channel width

wt\_hi radius of heavy-ion defined as the perpendicular from the track

$x_j$  Thickness of source and drain junction

$\varepsilon_{si}$  Permittivity constant of silicon

$\varepsilon_{ox}$  Permittivity constant of silicon oxide

$\mu$ A Microampere

μm Micrometre

$\tau_1$  Rise Timing Constant

$\tau_2$  Fall Timing Constant

#### LIST OF FIGURES

| 2.1         | Comparative between (a) bulk and (b) SOI FinFET                                                                                                                      |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2         | Bulk FinFET with Hard Mask                                                                                                                                           |    |

| 2.3         | FinFET Schematic (a) nFinFET, (b) pFinFET                                                                                                                            |    |

| 2.4         | FinFET Defects                                                                                                                                                       |    |

| 2.5         | The circuit for fins stuck-on in a logic gate.                                                                                                                       |    |

| 2.6         | 6T-Cell SRAM Schematic.                                                                                                                                              |    |

| 2.7         | Simplified Layout of the 6T FinFET-based SRAM a) HD b) LV c) HP                                                                                                      | 40 |

| 3.1         | Resistive-open Defect characterized in an SRAM cell.                                                                                                                 | 42 |

| 3.2         | Resistive-bridge defect characterized in an SRAM cell.                                                                                                               | 42 |

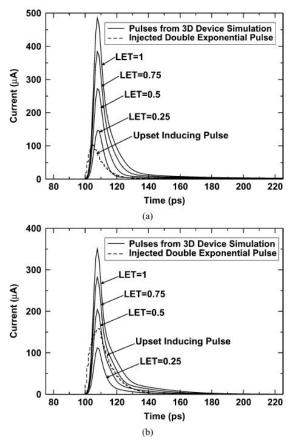

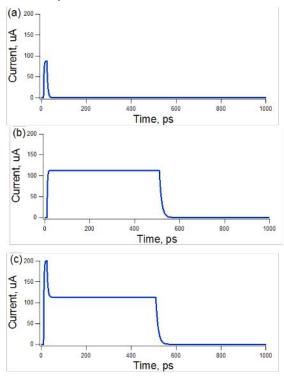

| 3.3         | Charge collection photo-current profiles (plain lines) resulting from 3-D TCAD simulation of heavy-ion strikes on (a) an NMOS transistor, and (b) a PMOS transistor. | 50 |

| 3.4         | Electrical configuration of the experiment in (ROYER; GARCIA-REDONDO                                                                                                 |    |

| J. <b>T</b> | LOPEZ-VALLEJO, 2015): (a) Schematic of current pulse induced by the particle strike in the node of SRAM and (b) Current pulse induced by a                           | ,  |

|             | neutron strike.                                                                                                                                                      | 51 |

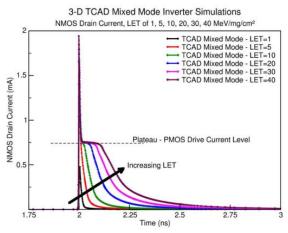

| 3.5         | 3D TCAD simulations results showing single-event induced nMOS drain current for various LET values from the work in (KAUPPILA et al., 2009).                         | 52 |

| 3.6         | Drain Current with plateau modeled: (a) short peak, $I_{Prompt}(t)$ , (b) sus-                                                                                       | 32 |

|             | tained, $I_{Hold}(t)$ , and (c) dual double-exponential current sources                                                                                              | 53 |

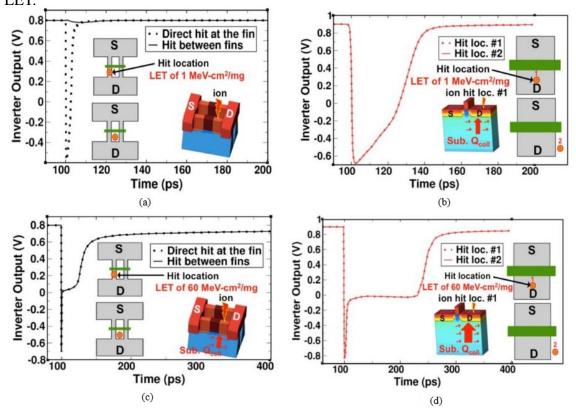

| 3.7         | Impact of transistor structure on low-LET 3D TCAD single-event tran-                                                                                                 |    |

|             | sient response: (a) 16 nm bulk FinFET inverter low-LET, (b) 28 nm bulk                                                                                               |    |

|             | planar inverter low-LET, (c) 16 nm bulk FinFET inverter high-LET and (d) 28 nm bulk planar inverter high-LET.                                                        | 54 |

| 4 1         |                                                                                                                                                                      |    |

| 4.1         | Resistive-open defects injected into an SRAM cell.                                                                                                                   |    |

| 4.2<br>4.3  | Resistive-bridge defects injected into an SRAM cell.  Defect Injection Flow.                                                                                         |    |

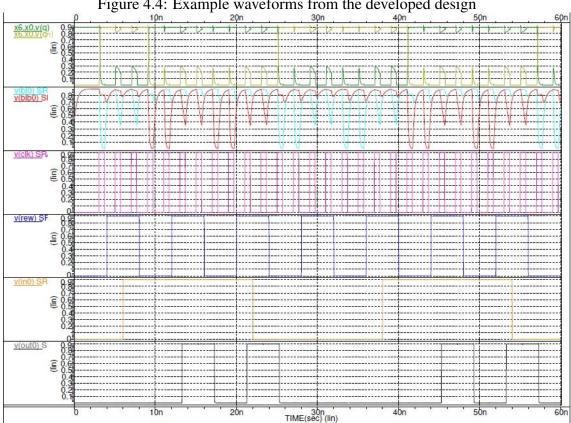

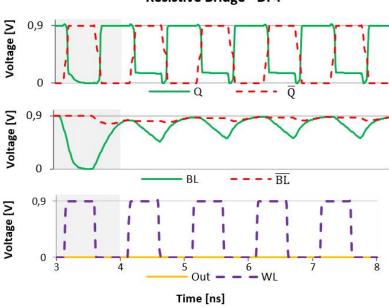

| 4.3<br>4.4  | Example waveforms from the developed design                                                                                                                          |    |

| 4.4<br>4.5  | Faults observed during simulations of SRAM cells affected by resistive-                                                                                              | 39 |

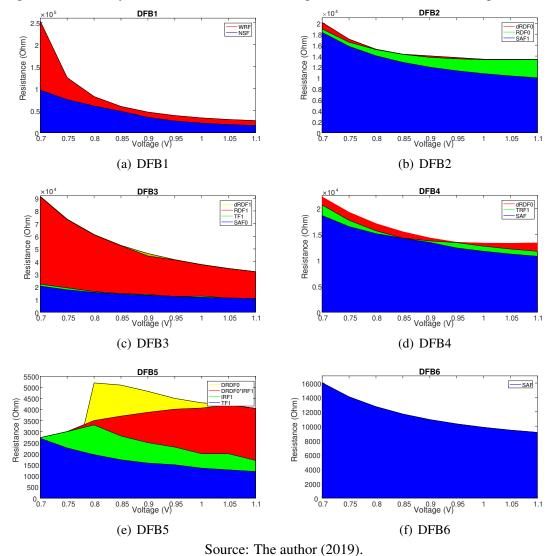

| 4.5         | open defects of different magnitudes                                                                                                                                 | 60 |

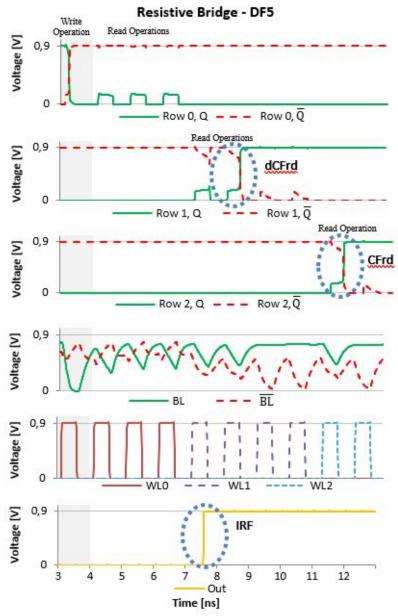

| 4.6         | Example of a dDRDF-7 occurring with a DFO3 of 71.5 k $\Omega$                                                                                                        | 61 |

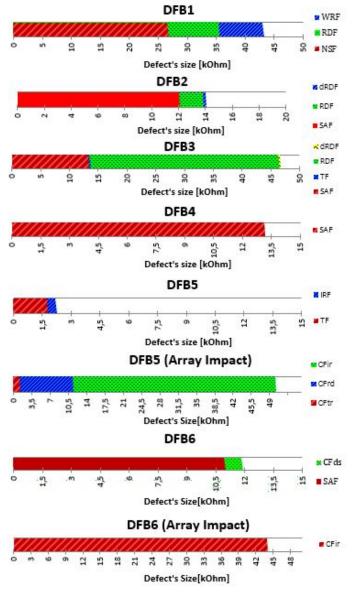

| 4.7         | Faults observed during simulations of SRAM cells affected by resistive-                                                                                              | O1 |

| 1.,         | bridge defects of different magnitudes.                                                                                                                              | 62 |

| 4.8         | Simulation output of a cell affected by a resistive-bridge causing faults on                                                                                         |    |

|             | other cells of the array.                                                                                                                                            | 63 |

| 4.9         | Simulation output of a cell affected by a resistive-bridge defect suffering                                                                                          |    |

|             | a destruction fault caused by an operation in a neighbour cell                                                                                                       | 64 |

| 4.10        | Simulation output of a cell affected by a resistive-bridge defect connect-                                                                                           |    |

|             | $\overline{Q}$ to the word line                                                                                                                                      | 65 |

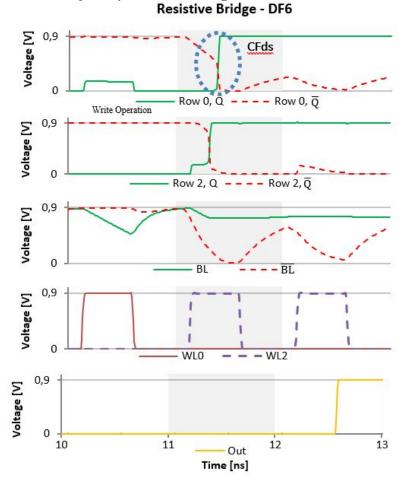

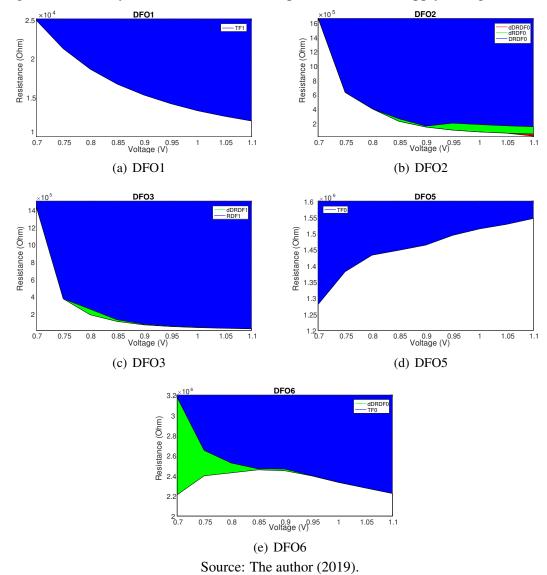

| 4.11        | Faulty behavior associated to Open Defects with supply voltage variation                                                                                             | 66 |

| 4.12        | Faulty behavior associated to Bridge Defects with source voltage variation.                                                                                          | 67 |

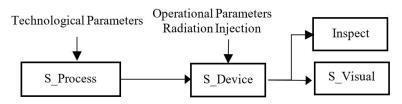

| 5.1         | Simulation flow used in TCAD.                                                                                                                                        | 78 |

| 5.2         | FinFET-based SRAM cell with injected defects and transient current                                                                                                   |    |

| 5.3         | FinFET LV SRAM cell implemented in this work: (a) top view; (b) 3D                                                                                                   |    |

|             | view without gate and metals                                                                                                                                         | 82 |

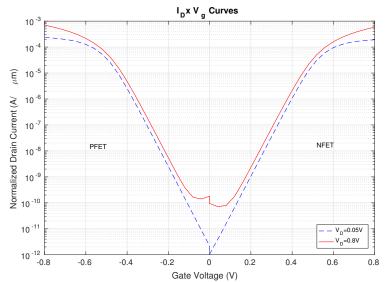

| 5.4  | Normalized Drain Current x Gate Voltage Curves from the modeled Fin-FETs.                                                                      | . 83 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.5  | Hold SNM butterfly curve.                                                                                                                      |      |

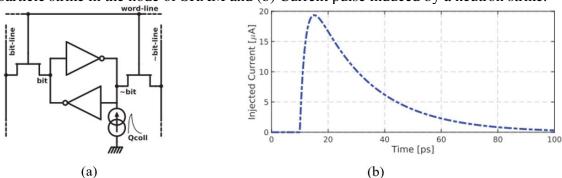

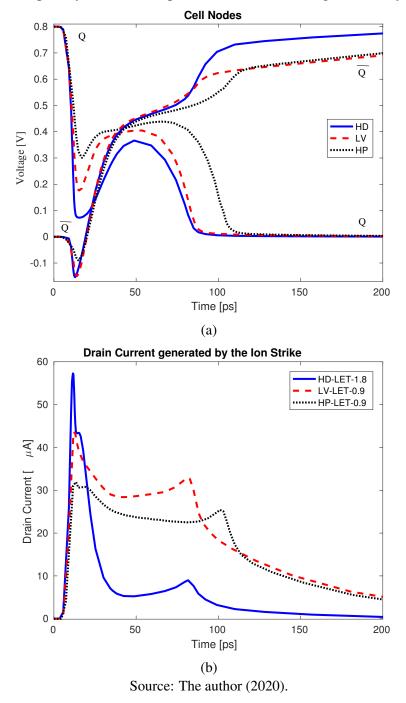

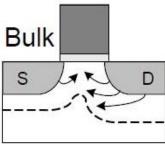

| 5.6  | Bit-flip analysis: (a) Bit-flip in the cell; (b) Current generated by the ion strike.                                                          | . 85 |

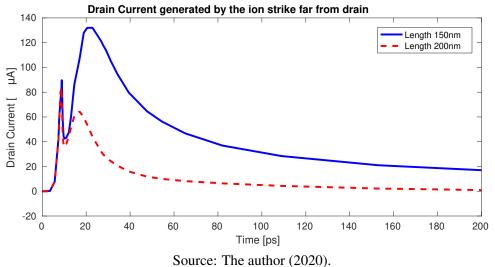

| 5.7  | Drain current with different charge track length implemented with ion far from the drain.                                                      |      |

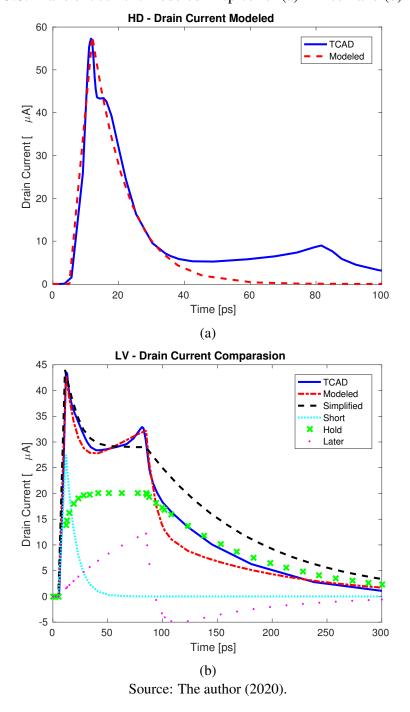

| 5.8  | Transient current modeled in spice for (a) HD cell and (b) LV cell                                                                             |      |

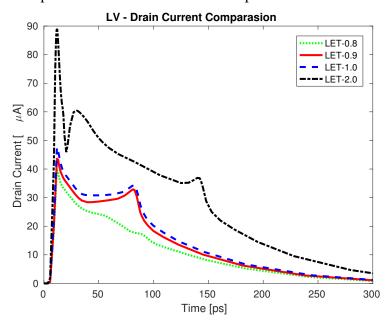

| 5.9  | Comparison of curves with different particle LETs for LV cell (TCAD)                                                                           |      |

| A.1  | Electric field lines between source and drain in the channel region in bulk MOSFET.                                                            | .108 |

| A.2  | Drain-Induced Barrier Lowering x Effective Channel Length for Single-gate/bulk and Double-gate.                                                |      |

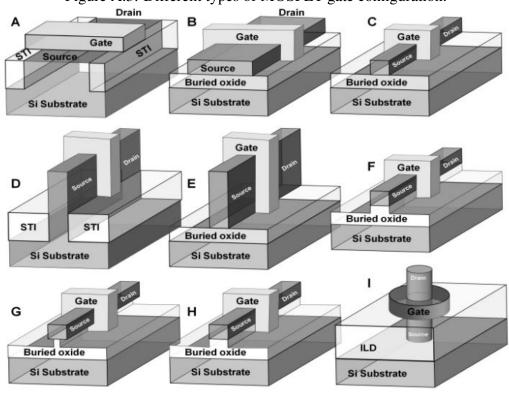

| A.3  | Different types of MOSFET gate configuration.                                                                                                  |      |

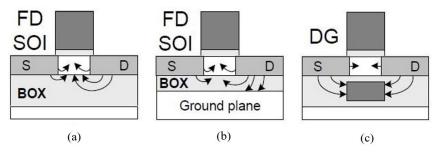

|      | Electric field lines between source and drain on the channel region: (a) in the traditional FDSOI MOSFET (b) in the channel region on UTBB SOI |      |

|      | MOSFET (c) in the channel region on Double-Gate MOSFET                                                                                         | .111 |

| A.5  | SOI MOSFET Triple Gate Structures                                                                                                              |      |

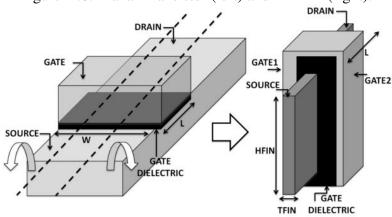

| A.6  | Planar Transistor (left) and FinFET (right)                                                                                                    | .114 |

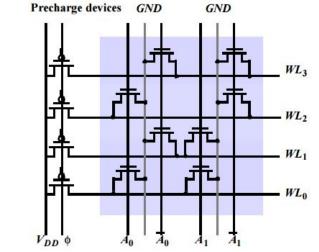

| A.7  | SRAM Block.                                                                                                                                    |      |

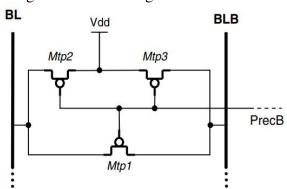

| A.8  | Pre-charge circuit schematic.                                                                                                                  | .115 |

| A.9  | Differential sense amplifier schematic                                                                                                         | .116 |

| A.10 | Write driver schematic                                                                                                                         | .117 |

| A.11 | Schematic of NOR Dynamic Line Decoder                                                                                                          | .117 |

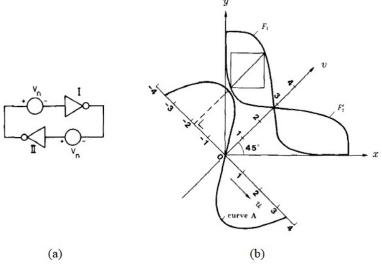

| A.12 | (a) Logic gate of SRAM bit cell with the source voltage Vn to SNM sim-                                                                         |      |

|      | ulation and (b) sample SNM – the side of the smaller square fitted inside the "eye"                                                            | .118 |

| A.13 | Schematic of a 6T SRAM bit cell with noise voltage sources for measuring SNM                                                                   |      |

| A.14 | Equivalent SRAM circuit during storage mode (a) and circuit to measure hold SNM (b)                                                            |      |

| A.15 | Equivalent SRAM circuit during read access (a) and circuit to measure read SNM (b)                                                             |      |

| A.16 | Equivalent SRAM circuit during write mode (a) and circuit to measure                                                                           | 0    |

| 0    | write SNM (b)                                                                                                                                  | .120 |

|      |                                                                                                                                                |      |

#### LIST OF TABLES

| 2.1<br>2.2 | Supply voltage and physical parameters of PTM-MG technology by nodes . Number of fins for FinFET SRAM cells              | 38<br>39 |

|------------|--------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1        | Functional Fault Models and their respective Fault Primitives                                                            | 46       |

| 4.1        | Critical Resistance Values for Different Temperatures                                                                    | 68       |

| 4.2        | Fault behavior when considering temperatures next to the nominal temperature of 27 °C                                    | 70       |

| 4.3        | Critical resistances for SRAMS designed in different technological nodes considering resistive-open defects, at 27 °C    | 71       |

| 4.4        | Critical resistances for SRAMS designed in different technological nodes considering resistive-open defects, at 125 °C   | 71       |

| 4.5        | Critical resistances for SRAMS designed in different technological nodes                                                 |          |

| 4.6        | considering resistive-open defects, at -40 °C                                                                            | 72       |

|            | considering resistive-bridge defects, at 27 °C.                                                                          | 73       |

| 4.7        | Critical resistances for SRAMS designed in different technological nodes considering resistive-bridge defects, at 125 °C | 74       |

| 4.8        | Critical resistances for SRAMS designed in different technological nodes                                                 |          |

|            | considering resistive-bridge defects, at -40 °C                                                                          | 75       |

| 5.1        | Adopted Physical Parameters for FinFETs                                                                                  | 78       |

| 5.2        | Number of fins of different SRAM cells design                                                                            | 81       |

| 5.3        | Electrical Characteristics of the FinFET Modeled in TCAD                                                                 | 82       |

| 5.4        | Static Noise Margin for FinFET-based SRAM Developed in TCAD                                                              | 83       |

| 5.5        | Threshold LET and Deposited Charges (TCAD)                                                                               | 86       |

| 5.6        | Excess Charge Configuration                                                                                              | 89       |

| 5.7        | Weak resistive defects that increase the SEU sensitivity of the studied SRAM cells                                       | 90       |

| 5.8        | Weak resistive defects that prevent bit-flips, considering the critical excess                                           |          |

|            | charge (spice)                                                                                                           | 91       |

#### CONTENTS

| 1 Intro | duction   |              |                                              | 25 |

|---------|-----------|--------------|----------------------------------------------|----|

| 1.1     | Goal a    | nd Contrib   | outions of this Thesis                       | 28 |

| 1.2     | Thesis    | Organizat    | ion                                          | 29 |

| 2 Chall | enges of  | Miniatur     | rization, FinFET and SRAM                    | 31 |

| 2.1     | Challe    | nges of M    | iniaturization                               | 31 |

| 2.2     | The Ty    | pes of Fir   | FET Technology                               | 33 |

| 2.3     | FinFE'    | T Characte   | eristics                                     | 34 |

|         | 2.3.1     | FinFET.      | Advantages                                   | 34 |

|         | 2.3.2     | Defects i    | n FinFET Technology                          | 35 |

|         | 2.3.3     | Predictiv    | e Models for Electrical Simulations          | 37 |

| 2.4     | SRAM      | I Circuit    |                                              | 38 |

| 2.5     | FinFE'    | T-Based S    | RAM Configuration                            | 39 |

| 3 Fault | s in Finl | FET-based    | I SRAM                                       | 41 |

| 3.1     | Resisti   | ive Defects  | s Definition                                 | 41 |

| 3.2     | Fault N   | Models As    | sociated to Resistive Defects                | 43 |

| 3.3     | Defect    | s in FinFE   | T-based SRAM Technology                      | 45 |

| 3.4     | Study     | of Radiation | on Effects in FinFETs                        | 47 |

|         | 3.4.1     | Single E     | vent Effect                                  | 47 |

|         | 3.4.2     | Single E     | vents in SRAM Blocks                         | 48 |

|         | 3.4.3     | Drain Cu     | nrrent under SEE in SRAM in new Technologies | 51 |

| 4 Relia | bility Aı | nalysis of   | FinFET-based SRAM under Resistive Defects    | 55 |

| 4.1     | Specifi   | ication      |                                              | 55 |

| 4.2     | Simula    | ation Setup  | <b>5</b>                                     | 55 |

|         | 4.2.1     | Modeled      | Defects                                      | 56 |

|         | 4.2.2     | Evaluation   | on of Defect Size on Fault Behavior          | 57 |

| 4.3     | Valida    | tion         |                                              | 58 |

|         | 4.3.1     | Results of   | of Resistive Defect Analysis                 | 59 |

|         |           | 4.3.1.1      | Resistive-Open Defects                       | 60 |

|         |           | 4.3.1.2      | Resistive-Bridge Defects                     | 60 |

|         |           | 4.3.1.3      | Impact of power supply variation             | 64 |

|   |        |           | 4.3.1.4     | Analysis considering different operating temperatures | 68  |

|---|--------|-----------|-------------|-------------------------------------------------------|-----|

|   |        |           | 4.3.1.5     | Impact of Temperature on Occurrence of Dynamic Faults | 69  |

|   |        |           | 4.3.1.6     | Analysis considering different technology nodes       | 70  |

| 5 | Evalu  | ating t   | he Impact   | t of Ionizing Particles on FinFET-based SRAMs with    |     |

|   | Wea    | k Resis   | tive Defec  | ts                                                    | 77  |

|   | 5.1    | Specifi   | cation and  | Implementation                                        | 77  |

|   |        | 5.1.1     | SRAM C      | Cell Modeling in TCAD                                 | 77  |

|   |        | 5.1.2     | Modeling    | g Ion Strike                                          | 78  |

|   |        | 5.1.3     | Injecting   | Resistive Defects                                     | 80  |

|   | 5.2    | Valida    | tion        |                                                       | 81  |

|   |        | 5.2.1     | SRAM C      | Cell Validation                                       | 81  |

|   |        | 5.2.2     | Results o   | f TCAD single event transient simulations             | 84  |

|   | 5.3    | Evalua    | tion: Influ | ence of resistive deffects on SEU reliability         | 88  |

| 6 | Concl  | usions    |             |                                                       | 93  |

|   | 6.1    | Future    | Works       |                                                       | 95  |

| 7 | Public | cations ( | during the  | PhD period                                            | 97  |

| R | eferen | ces       |             |                                                       | 99  |

| A | PPEN   | DIX A     | — Additio   | onal Background                                       | 107 |

|   | A.1    | Short (   | Channel Ef  | fect                                                  | 107 |

|   | A.2    | State-o   | of-the-Art  | of MOSFET                                             | 109 |

|   |        | A.2.1     | SOI MOS     | SFET                                                  | 109 |

|   |        |           | A.2.1.1     | Single Gate SOI MOSFET                                | 110 |

|   |        |           | A.2.1.2     | Double Gate SOI MOSFET                                | 111 |

|   |        |           | A.2.1.3     | Triple Gate SOI MOSFET                                | 112 |

|   |        |           | A.2.1.4     | Quadruple Gate SOI MOSFET                             | 113 |

|   | A.3    | Fin Qu    | ıantization |                                                       | 113 |

|   | A.4    | SRAM      | I Block Str | ructure                                               | 114 |

|   | A.5    | Static    | Noise Mar   | gin                                                   | 117 |

|   | A.6    | Fault 7   | Theory      |                                                       | 119 |

|   |        | A.6.1     | Fault Cla   | ssification                                           | 121 |

#### 1 INTRODUCTION

Along the evolution of the Metal-Oxide-Semiconductor Field-Effect Transistors (MOS-FETs) technology in Very Deep Sub-Micron (VDSM) circuits, Moore's law (MOORE et al., 1965) has been followed doubling the number of transistors in the same area every eighteen months. This has occurred since the commercial implementation of the first Integrated Circuit (IC).

However, with the increase of leakage current and Short-Channel Effects (SCEs) observed in the Complementary Metal-Oxide-Semiconductor (CMOS) technology, it was not feasible to shrink transistor feature size below 22 nm using MOSFET (HARUTYUNYAN; TSHAGHARYAN; ZORIAN, 2015). To continue the scaling down of technology nodes, Fin Field-Effect Transistors (FinFETs) were introduced as an alternative transistor technology to replace planar CMOS devices. FinFET is built as a multi-gate transistor. In other words, the FinFET channel has the shape of a fin and is involved by the gate, all placed on top of oxide. This design approach improves the electrostatic control of the transistor's channel (HUANG et al., 1999) and hence solves some of the aforementioned problems evolving planar CMOS technology for nodes beyond 22 nm. In more detail, leakage current, SCEs, and Random Dopant Fluctuations (RDFs) are mostly eliminated as doping levels are reduced to a minimum in FinFETs (VILLACORTA; SEGURA; CHAMPAC, 2016). Consequently, the majority of microelectronic companies are gradually replacing planar CMOS transistors with FinFETs in their state-of-the-art processors.

As a result of these changes in technological paradigms caused by the introduction of FinFET technology, several circuit devices needed to be redesigned, tested, and evaluated. In parallel, due to the always-increasing need to store more and more information on chips, Static Random-Access Memories (SRAMs) have become the main contributor to the overall area of integrated systems (WILSON, 2013) and hence are cited as particularly important, motivating this work's focus. Further, SRAMs are designed at the dimensional limits of technology, being statistically more likely to be affected by manufacturing defects (BOSIO et al., 2012), generating the need for intensive test procedures during the manufacturing stage. Therefore, SRAMs require efficient testing, i.e., tests with high fault coverage and low cost. Resistive defects have traditionally been a concern in the CMOS technology test scenario. More recently, this concern shifted towards weak resistive-open and weak resistive-bridge defects as their probability of occurrence may

increase in nanometer technologies due to the ever-growing number of interconnections between layers (DILILLO et al., 2004).

While the influence of resistive defects in circuit parameters (e.g. voltage, current) is irrefutable, it is easier to evaluate their impact by analyzing which faulty behaviors they lead to. Functional faults are deviations from expected behavior of the memory under a set of operations (GOOR; AL-ARS, 2000). Faults can be static (whose propagation occurs with one operation only) and dynamic, where at least two consecutive operations are required to sensitize the fault. Weak defects generally cause dynamic timing dependent faults, meaning that at least a 2-pattern sequence is necessary to sensitize them (BORRI et al., 2005). Moreover, the number of dynamic faults is directly correlated to the presence of weak resistive defects (DUBEY; GARG; MAHAJAN, 2010).

With the scaling down of technological nodes, resistive defects are likely to be one of the main reliability challenges in IC design (SIMSIR; BHOJ; JHA, 2010). These defects have been modeled and studied in CMOS technology and are known to generate dynamic faults (BORRI et al., 2005). However, the detection of weak resistive defects and, therefore, dynamic faults may not be trivial. In fact, open/resistive vias are the most common origin of test escapes in deep-submicron technologies (NEEDHAM; PRUNTY; YEOH, 1998). Thus, a complete understanding of this specific type of defect and the faults it causes is essential to improve manufacturing test procedures. Commonly, dynamic faults have been related to two aspects: the physical position and size of the defect. Varying defect positions have been evaluated for planar CMOS SRAM cells and the classification into either resistive-open, a resistor between two circuit nodes that share a connection, or resistive-bridge, a resistor between two nodes that should not be connected was established (HAMDIOUI; GOOR, 2000). Regarding defect size, it can be used to estimate the fault's strength. As previously mentioned, weak defects are defects able to sensitize dynamic faults; simulating different defect sizes allows to identify the specific resistance necessary to start sensitizing a certain defect at logic level. This resistance, known as critical resistance, defines the threshold between a fault-free and faulty behavior.

Traditionally, the characterization of fault behavior observed in defective SRAM cells has been performed following a well-established methodology based on SPICE electrical simulations. Many works focused on evaluating the resistance in which a certain defect starts to sensitize faults. This resistance, known as critical resistance, is the threshold between a fault-free and faulty behavior (SEGURA et al., 1992). Critical resistances

of resistive-open defects were investigated in (DILILLO et al., 2004; BORRI et al., 2005; DILILLO et al., 2005; VATAJELU et al., 2013; MARTINS et al., 2016) adopting technological nodes of 130 nm down to 40 nm, while critical resistances of resistive-bridge defects were investigated in (FONSECA et al., 2010a; FONSECA et al., 2010b) adopting technological nodes of 90 nm down to 40 nm.

However, all these previous researches were conducted using planar CMOS technology. So far, little research has been conducted considering resistive defects in FinFET memories. In (HARUTYUNYAN et al., 2014a), the authors modeled resistive open and bridge defects taking into account the physical structure of 28 nm FinFET devices aiming to observe possible unique faults of this technology. No further works have been proposed focusing on smaller nodes. This is especially worrisome since 10 nm FinFET devices are currently in production (INTEL, 2018a; SAMSUNG, 2018; INSIGHTS, 2017).

Another important topic to be discussed is the Single Event Effects (SEEs) which occur in ICs, as the Single Event Upset (SEU) when dealing with SRAMs. This event leads to functional faults in circuit operation, known as soft errors. It is usually caused by the incidence of an ionizing particle in the device. The ionizing particle generates a current pulse inside the transistor. For older technologies, the current pulse was accurately modeled by a double exponential current waveform. However, for the actual technologies as the FinFET, the current pulse shape becomes much more complex, and its behavior still need to be correctly modeled (NICOLAIDIS, 2011). Furthermore, a characterization of a current pulse for FinFET SRAM is discussed in this work.

It is known from the literature that radiation can lead to soft errors in FinFETs (as bit-flips in SRAM cell) even at ground level (HUBERT; ARTOLA; REGIS, 2015; ROYER; GARCIA-REDONDO; LOPEZ-VALLEJO, 2015). Some studies consider a comparative analysis of SEEs between FinFET and other technologies (planar CMOS and SOI) (HUBERT; ARTOLA; REGIS, 2015), where this work also perform an analysis with FinFET-based SRAM at different altitude levels. An analysis of weak resistive defects was already carried out for planar SRAM cells in many works as in (HAMDIOUI; GOOR, 2000). Further, an analysis of the radiation susceptibility of CMOS SRAM cells in the presence of weak resistive defects is presented in (MEDEIROS; POEHLS; VARGAS, 2016). Considering this, we propose to analyze the influence of weak resistive defects on the FinFET-based SRAM robustness under single event effects. Because the FinFET structure is physically more complex than planar CMOS, a more precise and realistic simulation tool is necessary. Thus, a FinFET-based SRAM cell is modeled using

Technology Computer-Aided Design (TCAD) and simulations of ionizing particle impacts are carried out at physical level. Further, the transient current generated by such event is modeled at electrical level.

#### 1.1 Goal and Contributions of this Thesis

The introduction of new transistor technologies in the industry, such as FinFET, and the migration of circuit designs to this technology, justify the studies to ascertain the reliability of the system, and tests must be improved to ensure this. Thus, this work presents an investigation of the behavior of FinFET-based SRAM cells affected by weak defects with an initial focus on resistive defects. In particular, this work intends to map and determine how manufacturing defects, specifically resistive-open and resistive-bridge defects, impact in the behavior of FinFET SRAM cells. Resistive defects with different magnitudes were injected in-memory bit cells aiming to detect static and dynamic faults. The analysis was performed through electrical simulations using Hspice<sup>TM</sup> software and adopting Predictive Technology Model (PTM) (ASU, 2011) of multi-gate transistors based on 20 nm, 16 nm, 14 nm, 10 nm, and 7 nm bulk FinFET.

In the end, reliability studies were conducted considering the injection of ionizing particles over an SRAM cell modeled in a TCAD software (Sentaurus<sup>TM</sup>). The main goal is to obtain by physical simulation: the minimum value of Linear Energy Transfer (LET) of an incident particle that results in a bit-flip (LET<sub>th</sub>, or threshold LET) for FinFET SRAM cells designed in a technology node of 14 nm; the proposal of a SPICE model for the obtained current curves; and the study of the impact of resistive defects on the reliability of FinFET SRAM cells under single events.

To clarify, the contributions of this thesis are:

- A full mapping of the faults caused by resistive defects in the FinFET-based SRAM block considering, single and couple faults, static and dynamic faults, different operation temperatures, also considering a low variation of temperature for weak defects analysis, and several technology nodes;

- Study the behavior from the impact of an ionizing particle in a FinFET-based SRAM cell, considering three kinds of layout configuration;

- Developing of new equations for the implementation of bit-flips caused by SEE in FinFET-based SRAM cell for electrical simulation, considering different cell's layout configuration;

- Finally, the evaluation of the effect combined of weak resistive defects and SEE in FinFET-based SRAM cells.

#### 1.2 Thesis Organization

Chapter 2 presents the theoretical basis for the understanding of this work, as the challenges of miniaturization, thus, there is the introduction of FinFET technology and SRAM circuit. Then, in Chapter 3 is the background focused on resistive defects and the problem of radiation effects in electronic devices is presented in order to introduce the background necessary to follow chapter 5.

Chapter 4 presents the reliability evaluation of FinFET-based SRAM under resistive defects, its method of implementation, and the validation of the design already developed. Chapter 5 presents the TCAD simulations of SEE over the FinFET-based SRAM, and the proposal of a SPICE model to inject the currents whit the shapes observed in the physical simulations. Chapter 6 describes the final remarks and future works that could be done using the obtained data and simulation models developed in this work. Finally, in Chapter 7 the list of publications achieved during the doctorate period is shown.

In Appendix A, there is some complementary background as the Short Channel Effect, which is explained to justify the development of new device technologies. Next, other kinds of commercial state-of-the-art devices are presented, the SOI MOSFET. Next, the design of an SRAM block is briefly explained. Thus, definitions of Test Theory and Fault Models associated with resistive defects are explained.

#### 2 CHALLENGES OF MINIATURIZATION, FINFET AND SRAM

This chapter will present a discussion about the challenges of miniaturization of Integrated Circuits (ICs). Then, it will present the two focus elements of this work: the FinFET technology with its characteristics, with a brief description of the Predictive Technology Model (PTM) adopted as a model in this work. Finally, the design of an SRAM block and its operation are explained, followed by the emphasis on a FinFET-based SRAM.

#### 2.1 Challenges of Miniaturization

During the last decades, advances in Very Deep Sub-Micron (VDSM) technology allowed the technology miniaturization according to Moore's law, which predicted the number of transistors in the same area to double every eighteen months (MOORE et al., 1965). However, the nature of scaling has already changed. There is a growing concern that scaling of devices in any form is slowing down, and there is a good chance that it will eventually become infeasible to cost-effectively manufacture devices below a certain feature size (ROY et al., 2013).

In this context, the scaling roadmap for ICs has been extrapolated from the current Moore's law regime into three main domains, namely 1) More-Moore; 2) Beyond CMOS; and 3) More-than-Moore. The first domain is expected to deal with traditional silicon Complementary Metal-Oxide Semiconductors (CMOS) and its scalability, in other words, the continuation of Moore's Law is known as the "More Moore" domain (HEINIG et al., 2014). The "Beyond CMOS" domain consists of various nanotechnologies beyond ultimately scaled CMOS (e.g., carbon nanotubes, Si nanowire, spintronics, etc.), which can potentially replace silicon and CMOS in the future. The "More-than-Moore" domain encompasses various disruptive device paradigms such as flexible electronics, nanoelectromechanicals (NEMS), biochips, heterojunction devices, solar cells, fuel cells, etc. Note that the devices in the "More-than-Moore" domain are not necessarily nanoscale, and they often provide auxiliary functions that cannot easily be realized in CMOS technology. Considering the "More-Moore" domain, the continuous evolution of Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) technology has been enabling miniaturization and aggressive technology integration.

Focusing on the More-Morre domain, initially some enhancement techniques to increase performance were implemented along with the reduction of the transistor tech-

nology. Among the proposed solutions is the Strain technique, which is a technique to generate traction or compression in the transistor channel, increasing the mobility in planar Complementary Metal-Oxide-Semiconductor (CMOS) technologies. Furthermore, an N-channel MOS (NMOS) transistor uses traction to keep away the atoms, improving the mobility of the electrons; on the other hand, on P-channel MOS (PMOS) the channel compression causes the atoms to approach, facilitating the mobility of the gaps through the crystal lattice (ROBERDS; DOYLE, 2003).

Continuing the miniaturization process, the leakage current in traditional CMOS transistor at the gate became significant, and may not be more ignored in the future. With this in mind, there was a need for the introduction of high-K oxide (Hafnium Oxide — HfO<sub>2</sub>), to increase the value of dielectric strength in insulation, thereby decreasing the leakage current, and the return of metal (Titanium Nitride — TiN) to the transistor's gate between the insulation and the polysilicon to prevent depletion therein. This way, the traditional CMOS transistor was reached, the limit being the technological node of 20 nm (COLINGE et al., 2008).

Starting from transistors with 22 nm technological nodes of MOSFET technology, the gate terminal begins to lose control over the potential distribution and current flow of the channel region of the transistor. This happens due to the phenomenon of the Short Channel Effect (SCE), which occurs due to the proximity between the source and the drain. The electric field created by these two terminals interferes in the field created by the gate. This compromises the entire operation of the device. Facing this adversity, new types of transistors have emerged to overcome the problem. There are two types currently used, the Silicon-On-Insulator (SOI) MOSFET and MultiGate devices, which will be mentioned in the text as FinFET, where through these technologies it is possible to continue the evolution of the technological nodes (COLINGE et al., 2008).

Nowadays, FinFET technology is already replacing CMOS transistors in state-of-the-art ICs by major electronics companies such as Intel which uses the term trigate (IN-TEL, 2018a), and Samsung (SAMSUNG, 2018). These references have already migrated to FinFET technology owing to its reduced short channel effects, electrostatic characteristics (TANG et al., 2001; YU et al., 2002; CHANG et al., 2011), and its compatibility with standard CMOS manufacturing process (COLINGE et al., 2008).

#### 2.2 The Types of FinFET Technology

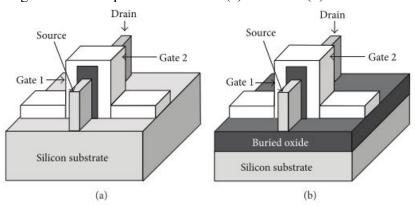

There are some alternatives to the method of manufacturing FinFET devices. The FinFETs can be SOI FinFET or bulk FinFET. Although FinFETs implemented on SOI slides are quite common, the FinFETs have been also implemented in conventional wafers. Figure 2.1 shows a comparison between FinFET implemented on conventional wafers (bulk) and SOI. In bulk FinFETs all fins share the same silicon substrate (this is called bulk). On the other hand, in SOI FinFETs, all fins are physically isolated. SOI technology is briefly explained in the Appendix A.

Figure 2.1: Comparative between (a) bulk and (b) SOI FinFET.

Source: BHATTACHARYA; JHA,2014.

The two types of FinFETs have characteristics that are close enough in terms of cost, performance, and production, so both probably will coexist in the market, for some years However many companies are preferring to use bulk technology because it is easy to migrate from traditional MOSFET technology (BHATTACHARYA; JHA, 2014), and it is the technology used by Intel Company because this work will focus in the Bulk FinFET technology.

Bulk FinFET was developed and used by Intel starting in the 22 nm node in 2012 (AUTH, 2012), using the triple gate model, they chose it due to the lower manufacturing cost because, and it uses the planar CMOS fabrication model as a basis. The electrical characteristics from bulk FinFET are lower than the SOI FinFET, but the lower manufacturing cost is enough to it be adopted by Intel (CHI, 2012). It is interesting to mention that the FinFET maybe be built with a dense insulator, a hard mask in the top of the gate as shown in Figure 2.2 (FOX means Field Oxide layer), turning this form as a Double-Gate type.

Figure 2.2: Bulk FinFET with Hard Mask

Source: COLINGE et al.,2008.

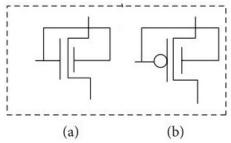

In Figure 2.3 it is presented the electrical schematic symbol of the FinFET transistors, there is no difference in the symbols for SOI or bulk FinFET.

Figure 2.3: FinFET Schematic (a) nFinFET, (b) pFinFET

Source: BHATTACHARYA; JHA,2014.

#### 2.3 FinFET Characteristics

Once the bulk FinFET is the main device that will be treated in this work, its manufacturing characteristics will be discussed below. Firstly, it is presented how to size FinFETS (determine the number of fins), and thus some FinFET types ere presented.

#### 2.3.1 FinFET Advantages

The main advantages of FinFET technology, according to (BHATTACHARYA; JHA, 2014; SIDDHARTHAN; MEENAKSHI, 2013) over planar CMOS technology are:

- An excellent control over the conduction channel by the gate. The sub-threshold behavior of FinFETS is near the ideal, which is very difficult to achieve in a planar MOSFET;

- Short channel effects are reduced due to excellent channel control;

- High-density integration, due to its three-dimensional structure;

- Low variability: the fin's body is slightly doped, it reduces the effects of Random Dopant Fluctuations (RDF);

- The FinFET can operate at lower voltages than planar technology reducing both dynamic and static consumption;

- In FinFET-based SRAM cells, the Static Noise Margin (SNM), which is the minimum voltage noise to change the value of a cell, is much higher than the planar transistor due to the low RDF in FinFET.

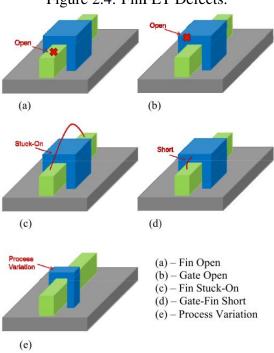

### 2.3.2 Defects in FinFET Technology

FinFET fault models must be established since the conventional models may not cover all possible aspects of defects in the technology as presented in (HARUTYUNYAN et al., 2014a). These models are still under study by the academic community. It is important to notice that the defect is a physical abnormality in the device, and the fault model is how that defect manifests itself in the circuit. Therefore, the possible defects that can occur in FinFET must be observed. Figure 2.4 presents the reevaluation of some types of defects. These defects are:

- (a) Fin Open: Open defect in fin;

- (b) Gate Open: Open defect in the gate;

- (c) Fin Stuck-On: short defect between source and drain;

- (d) Gate-Fin Short: Short defect between gate and fin;

- (e) Process Variation: Process variations and parameters variations of fin.

The analysis focused on FinFET-based SRAMs should consider the following defects: shorts and opens between memory cells, shorts and opens internally in a cell, as well as peripheral defects occurring in circuits such as address decoders or sense amplifiers (HARUTYUNYAN et al., 2014a). It is important to mention that, for the above-presented defects, the types a), b), c) and d) may manifest as resistive defects.

Studies about the stuck-open faults (SOF) on FinFET devices were performed in (VAZQUEZ et al., 2009) and (CHAMPAC et al., 2012), and reports that the classical SOF behavior is altered by the increase of leakage current and the smaller node capacitances in

Figure 2.4: FinFET Defects.

Source: HARUTYUNYAN et al., 2014a.

the device. The current from SOF in FinFET is a combination of classical and nonclassical responses in function of the fan-out, fan-in, clock period, leakage current, noise,  $V_{DD}$ , and temperature. The work proposes two vector strategies to improve the robustness of SOF detection in the presence of leakage current. Also, authors in (SIMSIR; BHOJ; JHA, 2010) and (BHOJ; SIMSIR; JHA, 2011) propose a fault modeling for FinFET applying open and short defects in logic gates (INV and NAND). It was verified that most opens and shorts in FinFET logic circuits have corresponding fault models in planar CMOS.

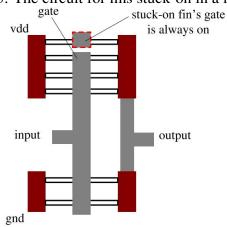

In (LIU; XU, 2012) various types of defects on logic circuits with FinFETs were studied. The defects were considered in the fins: stuck-on, stuck-open, and gate oxide short. It was verified that different number of fins result in different faulty behaviors. The proportion of defective fins determine if the device is faulty-free, or if it has a stuck-open fault or delay fault. Furthermore, because the characteristic configuration of FinFET, one defect can be propagated through the back gate of a fin, thus, new test generation strategies are required to detect delay faults. Also, it was verified that any incorrect doping or geometrical imperfection on the crystal structure in the fin will make the whole fin as a wire. Furthermore, any connection between the source and the drain will also make the fins act similarly to a wire, as illustrated in Fig 2.5. In both cases, the fin will be always in short between the drain and source.

Figure 2.5: The circuit for fins stuck-on in a logic gate.

# Source: LIU; XU,2012.

#### 2.3.3 Predictive Models for Electrical Simulations

The Predictive Technology Model (PTM) (ASU, 2011) developed by the Arizona State University (ASU) was initially developed for electrical simulation for planar CMOS technology nodes up to 20 nm based on the BSIM4 model (BERKELEY). The ASU PTM model improved the methodology of the Berkeley Predictive Technology Model (BPTM) (CAO et al., 2000) that uses empirically extraction model parameters from early-stage silicon data, the ASU PTM take into account significant physical correlations among parameters. In the work (SINHA et al., 2012), the PTM for multi-gate transistors (PTM-MG), for sub-20 nm technology nodes (FinFETS), was developed using BSIM-CMG (Berkeley Short-channel IGFET Common Multi-Gate) model (DUNGA et al., 2008), with the nodes of 20 nm, 16 nm, 14 nm, 10 nm, and 7 nm. This electric model has been used to describe the behavior of both bulk FET and SOI FET (COLINGE et al., 2008). The PTM-MG has two application-specific versions, high performance (HP) and low-standby power (LSTP). This second was used in the work presented in the thesis because of the low leakage current, between the drain and source when the transistor is cut off (ASU, 2011). The parameters of PTM-MG technology and the supply voltage for each node are presented in Table 2.1. It is important to mention, that because it is a predictive model, certain differences and limitations can be found in the model and may influence the results slightly compared to commercial technologies. As a curiosity, it is valid to mention that it was developed in (CLARK et al., 2016) in collaboration with ARM Ltd a 7 nm predictive process design kit (PDK) called the ASAP7 PDK for design layout in academic use.

Table 2.1: Supply voltage and physical parameters of PTM-MG technology by nodes

| Parameter                | Technological Node |       |       |       |      |  |

|--------------------------|--------------------|-------|-------|-------|------|--|

| 1 at afficter            | 20 nm              | 16 nm | 14 nm | 10 nm | 7 nm |  |

| Supply Voltage (V)       | 0.90               | 0.85  | 0.80  | 0.75  | 0.70 |  |

| Gate Lenght (nm)         | 24.0               | 20.0  | 18.0  | 14.0  | 11.0 |  |

| Fin Height (nm)          | 28.0               | 26.0  | 23.0  | 21.0  | 18.0 |  |

| Fin Thickness(nm)        | 15.0               | 12.0  | 10.0  | 8.00  | 6.50 |  |

| Effective Width (nm)     | 71.0               | 64.0  | 56.0  | 50.0  | 42.5 |  |

| Oxide thickness (nm)     | 1.40               | 1.35  | 1.30  | 1.20  | 1.15 |  |

| Work-function - NFET(eV) | 4.56               | 4.59  | 4.60  | 4.60  | 4.61 |  |

| Work-function - PFET(eV) | 4.62               | 4.59  | 4.57  | 4.57  | 4.56 |  |

Source: ASU 2011.

## 2.4 SRAM Circuit

In digital circuits, the manipulated information needs to be stored in systems suitable for this purpose: the memories. Memory circuits can be classified according to their volatility. Volatile memories lose information stored when the power supply is removed, opposing the non-volatile type. The memory circuit studied in this work will be one of the volatile types, specifically the Random Access Memory (RAM).

There are two types of MOSFET RAMs: dynamic and static. Dynamic RAMs (DRAMs) store the binary data in capacitors, and allow for a larger reduction of the cell area, however, require more elaborate read and write circuits. On the other hand, static RAM (SRAM), which is the focus of this work, uses cross-coupled inverters as storage cells for information.

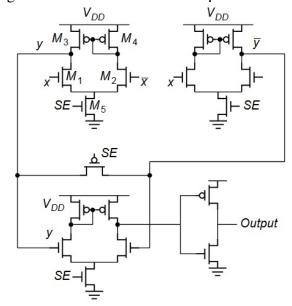

The SRAM adopted in this work is the 6T type, because it is the model most widely used of SRAM (NEISSER; WURM, 2015). It is composed of a set of six transistors ( $Q_n$ ) as shown in Figure 2.6. The cell consists of two inverters with cross-connections and two access nMOS transistors. The access transistors are activated when Word Line (WL) is selected with logic value '1', thus connecting one of the inverters to the Bit Lines (BL) and its opposite polarity counterpart ( $\overline{BL}$  or BLB). The access transistors act as a transmission gate, allowing bi-directional current flow between the cell and the BL and BLB columns. It is important to mention that the SRAM cell structure is divided into three parts with its proper notation (PU: PG: PD), where PU, PG, and PD are respectively: the pull-up (the two PMOS transistors from inverters); the pass gate consisting of two NMOS transistors; and finally, the pull-down are the two NMOS transistors from inverters. The SRAM block structure, its modes of operations, and Static Noise Margin (SNM) are presented in the Appendix A.

BLB BL WL Q4 Q4 Q6 Q6

Figure 2.6: 6T-Cell SRAM Schematic.

Source: SEDRA; SMITH,2004.

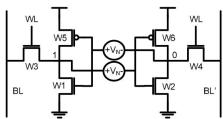

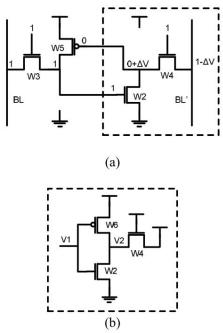

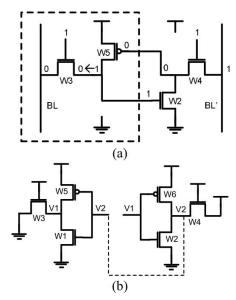

# 2.5 FinFET-Based SRAM Configuration

In SRAM blocks designed with planar CMOS technology, the cell size is optimized to provide stable operation as provide similar time for read and write operations, and increase the noise tolerance. In FinFET technology, the discrete nature of fins (limited to a quantized number) impacts the design of the cell. Therefore, it is not possible to design the cell with an ideal robustness ratio such as in CMOS. Therefore, this increases the need for auxiliary circuits to provide adequate robustness, especially for the smaller cells (BURNETT et al., 2014).

Throughout the published works, many configurations have been defined for SRAM cell design. Three main approaches have been used as presented in (BURNETT et al., 2014), (JAN et al., 2012) and (KARL et al., 2013): the high-density (HD); the low voltage (LV) - which can also be referred to as low power (LP); and the high performance (HP). These settings use different numbers of fins for each part of the cell configuration (PU: PG: PD). The HD, LV and HP configurations are: (1:1:1), (1:1:2), and (1:2:2). This relation of transistor sizes can be checked in Table 2.2. JA layout simplified of the 6T FinFET-based SRAM for the three structures: HD, LV, and HP cells are depicted in Figure 2.7. In the Figure, in green is represents the Fins, and in red the gates.

Table 2.2: Number of fins for FinFET SRAM cells

| Configuration | (PU:PG:PD) |  |  |

|---------------|------------|--|--|

| HD            | (1:1:1)    |  |  |

| LV            | (1:1:2)    |  |  |

| HP            | (1:2:2)    |  |  |

Source: BURNETT et al., 2014.

With the objective of comparing electrical characteristics of FinFET-based SRAM of a 20 nm technology with a CMOS-based of 22 nm node, a study comparing physi-

PD PU PD (Gate)

(Fin)

(a)

6T FinFET SRAM HP

PG PU PD (Gate)

PD PU PD (Gate)

PD PU PD (Gate)

(Fin)

(b)

(c)

Figure 2.7: Simplified Layout of the 6T FinFET-based SRAM a) HD b) LV c) HP. 6T FinFET SRAM HD

Source: Copetti, 2021 based on the description given in BURNETT et al., 2014.

cal/electrical characteristics of 6T and 8T-SRAM was performed in (FARKHANI et al., 2014). The comparison confirms that FinFET presents lower process variations, lower leakage power consumption, more robustness, and reliability.

### 3 FAULTS IN FINFET-BASED SRAM

This Chapter is presented some faults sources for the FinFET-based SRAM circuit that will be the research focus of this work, it is the resistive defects and the faults from radiation effects. Initially, the defects for planar CMOS are presented as a comprehension of how the defects could happen in FinFET technology, followed by the fault models related to SRAM blocks. Then, the existing study about the defects in FinFET-based SRAM technology is presented. Finally, the impact of single effects generate for radiation sources on FinFET-based SRAM is discussed.

### 3.1 Resistive Defects Definition

This work intends to study the behavior of defective memory cells under resistive defects. Therefore, a description of this kind of defect will be presented, along with the forms of manifestation and the methods used to identify and analyze it.

Resistive Defects are divided into resistive-open and resistive-bridge. The resistive-open defect is defined as a resistor between two nodes of a circuit that should be connected. When the resistive value between the nodes is high, a special case of this defect takes place that generates a well-known fault called stuck-open, thus blocking the transmission of the signal in the circuit (LI; TSENG; MCCLUSKEY, 2001). The Fault theory is presented in the Appendix A.

The resistive-bridge defect is defined as a resistor between two nodes of the circuit which should not be connected, forming a short. When the resistive value between the nodes is very high, it manifest as a special case of this defect that generates a well-known fault called stuck-at, thus locking the node with other nodes or supply signal (FONSECA et al., 2010a).

For ten years now, a variation of the resistive defect has received more attention, it is named weak resistive defect (or simply weak defect) which may result in dynamic faults. Different from the static faults which always cause a wrong value in the circuit, the dynamic faults are not noticeable in many manufacturing tests because they are designed to detect static faults (HAMDIOUI et al., 2003; HAMDIOUI et al., 2006). Weak defects may cause small voltage disturbance of the node of cell in SRAMs, that can generate time-dependent faults, that is, faults that occur at certain time intervals performing repetitive

operations in the cell (HAMDIOUI; GOOR, 2000). These faults will become recurrent as the circuit degrades.

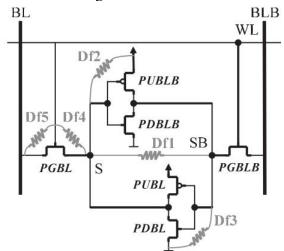

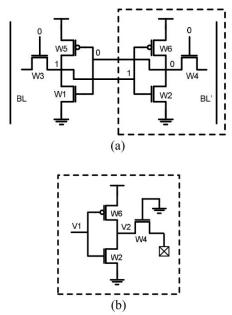

The work developed in (DILILLO et al., 2004) models, in an SRAM cell, the dynamic behavior caused by resistive-open, through resistors inserted in the nodes of the circuit (by simulation), as it can be observed in Figure 3.1. Each resistor has been named with a Df (Defect) from 1 to 6.

WLS

Vdd

Vdd

Mtp2

Mtp2

Mtp2

Mtp2

Mtp3

Vdd

Mtp4

Mtp4

Mtp4

Mtp4

Mtp4

Mtp4

Mtp4

Mtp4

Mtp5

Mtp5

Mtp6

Mtp7

Figure 3.1: Resistive-open Defect characterized in an SRAM cell.

Source: DILILLO et al. 2004.

Another work was developed in (FONSECA et al., 2010a) that models, in an SRAM cell, the dynamic resistive-bridge defects through resistors inserted between the nodes of the circuit, as can be observed in Figure 3.2. Again, each resistor has been named with a Df (Defect) from 1 to 5.

Figure 3.2: Resistive-bridge defect characterized in an SRAM cell.

Source: FONSECA et al. 2010a.

#### 3.2 Fault Models Associated to Resistive Defects

The existence of imperfections in the manufacturing process may lead the memory cells to be affected by manufacturing defects such as resistive-open and/or resistive-bridge defects that can compromise the correct behavior of the device. These defects can be characterized as strong or weak defects based on the nature of the fault they sensitize: strong defects are usually related to static faults, while weak defects are associated with dynamic faults. Faulty behaviors can be specified using Fault Primitives (FP), which characterizes the sensitizing sequence (S), the faulty behavior observed (F), and the output of read operations (R) (GOOR; AL-ARS, 2000), it follows the notation <S/F/R>. A non-empty set of fault primitives is known as a Functional Fault Model (FFM). The FPs can be classified as static or dynamic according to the number of required operations in order to sensitize the fault. Furthermore, the number of necessary operations to sensitize the fault may depend on many factors, such as defect resistance, operating temperature, process corner, among others (DILILLO et al., 2005).

Additionally, an FP can also be classified by the number of cells involved: single-cell and multi-cell FP. In a single-cell FP, faulty behaviors are only observed in the defective cell. In multi-cell FP (also known as coupling-faults), two cells (or two groups of cells) interact to produce a fault. The cell that suffers the faulty behavior is the victim (v-cell), while the cell that triggers the fault is the aggressor (a-cell). It is important to note that the resistive defect may be present either in the a-cell and/or in the v-cell (GOOR; AL-ARS, 2000; HAMDIOUI; AL-ARS; Van De Goor, 2002). Whereas an FFM is defined as a set of FPs, FFM will assume their characteristics, resulting in the following classifications: static and dynamic FFM; single-cell and multi-cell FFM. In more details, FFMs can represent the following fault space that was considered in this work, and described in (GOOR; AL-ARS, 2000):

- State Fault (SF<sub>x</sub>) (GOOR; AL-ARS, 2000): a cell is said to have a SF if its logic value flips when no operation is performed on it;

- Transition Fault (TF<sub>x</sub>) (GOOR; AL-ARS, 2000): a cell is said to have a TF if it fails to undergo a transition from '0' to '1' when it is written;

- Write Disturb Fault (WDF<sub>x</sub>) (GOOR; AL-ARS, 2000): a cell is said to have a WDF if a non-transition write operation causes a transition in it;

- Read Destructive Fault (RDF<sub>x</sub>) (ADAMS; COOLEY, 1996): a cell is said to have an RDF if a read operation performed on the cell changes the data in the cell and returns the incorrect value to the output. This type of fault can also have a dynamic behavior classified as dRDF<sub>xy</sub> (GOOR; AL-ARS, 2000);

- Deceptive Read Destructive Fault (DRDF<sub>x</sub>) (ADAMS; COOLEY, 1996): a cell is said to have a DRDF if a read operation performed on the cell returns the correct logic value, but changes the contents of the cell. This type of fault can also have a dynamic behavior classified as dDRDF<sub>xv</sub> (GOOR; AL-ARS, 2000);

- Incorrect Read Fault (IRF<sub>x</sub>) (GOOR; AL-ARS, 2000): a cell is said to have an IRF if a read operation performed on the cell returns an incorrect logic value, even though the correct value is still stored in the cell. This type of fault can also have a dynamic behavior classified as dIFR<sub>xy</sub> (GOOR; AL-ARS, 2000);

- Stuck-at Fault (SAF $_x$ ) (GOOR, 1991): a cell is said to have a SAF (also know State Fault) when the cell is stuck and stores only one logic value '0' or '1';

- No Store Fault (NSF) (FONSECA et al., 2010a): this fault is the opposite of SAF, where a cell with NSF cannot retain any logic value in their nodes;

- Weak Read Fault (WRF) (FONSECA et al., 2010a): a cell is said to have a WRF when, during the read operation, the sense amplifier cannot produce the correct logic output due to the small voltage difference between bit lines.

There is also a special analysis of dynamic fault, which can manifest in one cell through the influence of another cell. Therefore, operations are performed on aggressor cell (a-cell), but the activation through *WL* affects a victim cell (v-cell) on the same line. It is known as dynamic two-cell FFM (HAMDIOUI; AL-ARS; Van De Goor, 2002).

- Disturb Coupling Fault (CFds) (GOOR; AL-ARS, 2000): This fault occurs in groups of at least two cells where it is sensitized when a read or write operation in an acell affects v-cell or a group of v-cells, forcing them to change their stored values. This type of fault can also have a dynamic behavior classified as dCFds<sub>x;yz</sub> (GOOR; AL-ARS, 2000);

- Transition Coupling Fault (CFtr) (GOOR; AL-ARS, 2000): This fault occurs when a transition write operation performed on the v-cell fails due to a given logic value

stored in the a-cell. Thus, the fault is sensitized by a write operation on the v-cell and setting the a-cell into a given state;

- Read Disturb Coupling Fault (CFrd) (GOOR et al., 1996): This fault occurs when a read operation performed on v-cell changes the data in the cell and returns the incorrect value on the output if a given value is present in the a-cell. This type of fault can also have a dynamic behavior classified as dCFrd<sub>x;yz</sub> (GOOR; AL-ARS, 2000);

- Incorrect Read Coupling Fault (CFir) (GOOR; AL-ARS, 2000): This fault occurs when a read operation performed on v-cell returns an incorrect value on the output when a given value is present in the a-cell. This type of fault can also have a dynamic behavior classified as dCFir<sub>x:vz</sub> (GOOR; AL-ARS, 2000).

Table 3.1 shows the FFMs observed in this work and their respective FPs. As previously mentioned, an FFM is composed of a set of FPs represented by <S/F/R>. On single-cell faults, S may assume none or one operation of read or write for a static FFM, and two or more operations for dynamic FFM.

For simplification purposes, the FPs of dynamic FFMs are represented by only two operations. F represents the faulty behavior of the cell and is represented by a logic '1' or '0'. R is the output of a read operation, represented by a logic '0' or '1'. If no read operation is performed, '-' is adopted, the symbol  $\forall$  means that any write operation can be performed. For coupling faults, S assumes the form of x;y, where x is the operation in the a-cel,l and y is for v-cell. Furthermore, xx is used to represent a dynamic behavior of more than one operation. It is important to note that, in this work, dynamic FPs are comprised of a write operation followed by consecutive n read operations. Thus, it is necessary to repeatedly read a cell and evaluate the retrieved value (GOOR; AL-ARS, 2000).

### 3.3 Defects in FinFET-based SRAM Technology

In the literature there are some studies related to defects in FinFET-based SRAMs. The paper (LIN; CHAO; HSU, 2013), was investigated the gate oxide short (GOS) effects in FinFETs. This work proposes one test method to FinFET-based SRAM. It was discovered the behavior in FinFET of saturation drain current decreasing are more difficult to detect over the planar CMOS. These tests can detect undetectable GOSs of traditional tests.

Table 3.1: Functional Fault Models and their respective Fault Primitives.