#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

MARCELO BRANDALERO

## MuTARe: A Multi-Target, Adaptive Reconfigurable Architecture

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Antonio Carlos Schneider Beck Coadvisor: Prof. Dr. Luigi Carro

Porto Alegre March 2019 Brandalero, Marcelo

MuTARe: A Multi-Target, Adaptive Reconfigurable Architecture / Marcelo Brandalero. – Porto Alegre: PPGC da UFRGS, 2019.

142 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– Brazil, 2019. Advisor: Antonio Carlos Schneider Beck; Coadvisor: Luigi Carro.

1. Computer architecture. 2. Reconfigurable architecture. 3. Adaptable architecture. 4. Approximate computing. 5. Nearthreshold voltage computing. I. Beck, Antonio Carlos Schneider. II. Carro, Luigi. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PPGC: Prof<sup>a</sup>. Luciana Salete Buriol Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"A reliable way to make people believe in falsehoods is frequent repetition, because familiarity is not easily distinguished from truth. [...] Our comforting conviction that the world makes sense rests on a secure foundation: our almost unlimited ability to ignore our ignorance." — DANIEL KAHNEMAN

#### AGRADECIMENTOS

Realizar um doutorado não é uma tarefa fácil. Requer tempo, esforço, e, acima de tudo, apoio. Muito apoio, pois é um caminho longo, com muitas quedas e obstáculos. Nunca vou esquecer do comentário que ouvi de dois professores sobre o processo, antes de iniciá-lo. O primeiro me disse que, durante um doutorado, eu iria solucionar um problema, mas que apenas uma solução não seria o suficiente. Eu teria que ir adiante, investigar alternativas, acertar e errar muitas vezes antes de estar satisfeito com uma das soluções atingidas, sendo necessária muita persistência durante o processo. O segundo me disse que, durante o doutorado, eu iria ver meus colegas que se formaram comigo prosperarem financeiramente com seus trabalhos na indústria, e eu teria que achar al-guma forma de conforto com os salários inferiores pagos pela academia. Hoje, passado o processo todo, posso dizer que ambas as afirmações estavam corretas.

Gostaria de agradecer em primeiro lugar aos meus pais por todo o apoio fornecido nesta trajetória, tanto emocional como financeiro. Eles sempre me inspiraram a acreditar em um futuro melhor e seguir adiante, não importando o quão difícil o caminho à frente pudesse parecer, ao mesmo tempo que me ofereciam a mão sempre que eu precisasse.

Em segundo lugar, gostaria de agradecer ao meu orientador, Prof. Antonio Carlos Schneider Beck, por toda a paciência que teve em me orientar durante quatro anos como doutorando e seis anos como aluno. Sei que não foram poucos os meus tropeços durante o caminho, e ainda assim ele acreditou em mim e me apoiou. Posso dizer que levo muitos aprendizados destas experiências, não apenas técnicos, mas também pessoais. Também merecem um agradecimento especial o Prof. Luigi Carro e o Prof. Muhammad Shafique pelas contribuições técnicas ao desenvolvimento desta tese.

Em terceiro lugar, é muito difícil falar de apoio e não lembrar dos amigos. Nunca fui uma pessoa de muitas amizades, mas sempre valorizei muito cada uma delas. Não citarei nomes, pois corro o risco de omitir pessoas que foram muito importantes para mim nesta trajetória, mas creio que cada uma delas saiba o quão importante sua participação na minha vida foi até aqui. Um agradecimento especial também deve ser feito a todos os colegas de laboratório, companheiros de pesquisa e que dividiram comigo muitos dos desafios encontrados nos últimos anos.

Finalmente, um agradecimento especial à minha namorada Roberta por todo o apoio e carinho neste difícil último ano, e por ter mostrado a mim uma nova forma de viver a vida.

#### ABSTRACT

Power consumption, earlier a design constraint only in embedded systems, has become the major driver for architectural optimizations in all domains, from the cloud to the edge. Application-specific accelerators provide a low-power processing solution by efficiently matching the hardware to the application; however, since in many domains the hardware must execute efficiently a broad range of fast-evolving applications, unpredictable at design time and each with distinct resource requirements, alternatives approaches are required. Besides that, the same hardware must also adapt the computational power at run time to the system status and workload sizes. To address these issues, this thesis presents a general-purpose reconfigurable accelerator that can be coupled to a heterogeneous set of cores and supports Dynamic Voltage and Frequency Scaling (DVFS), synergistically combining the techniques for a better match between different applications and hardware when compared to current designs. The resulting architecture, MuTARe, provides a coarse-grained regular and reconfigurable structure which is suitable for automatic acceleration of deployed code through dynamic binary translation. In extension to that, the structure of *MuTARe* is further leveraged to apply two emerging computing paradigms that can boost the power-efficiency: Near-Threshold Voltage (NTV) computing (while still supporting transparent acceleration) and Approximate Computing (AxC). Compared to a traditional heterogeneous system with DVFS support, the base MuTARe architecture can automatically improve the execution time by up to  $1.3\times$ , or adapt to the same task deadline with  $1.6 \times$  smaller energy consumption, or adapt to the same low energy budget with  $2.3 \times$  better performance. In NTV mode, *MuTARe* can transparently save further 30% energy in memory-intensive workloads by operating the combinatorial datapath at half the memory frequency. In AxC mode, *MuTARe* can further improve power savings by up to 50% by leveraging approximate functional units for arithmetic computations.

**Keywords:** Computer architecture. reconfigurable architecture. adaptable architecture. approximate computing. near-threshold voltage computing.

#### MuTARe: Uma Arquitetura Multi-Proposito Adaptativa e Reconfigurável

#### **RESUMO**

Consumo de potência, antigamente um limitante no projeto apenas de sistemas embarcados, hoje é um dos principais objetivos de otimização em todos os domínios de dispositivos, desde a computação na núvem até a computação na borda. Aceleradores de propósito específico são capazes de fornecer uma solução para o processamento de baixa potência ao adequar o hardware à aplicação; porém, visto que, em diversos domínios, o hardware necessita executar uma ampla gama de aplicações, cada uma com diferentes requisitos computacionais, abordagens alternativas se fazem necessárias. Além disso, o mesmo hardware precisa se adequar, em tempo de execução, ao estado do sistema e tamanho da carga de trabalho, aumentando o poder computacional ao executar uma tarefa exigente e reduzindo-o quando inativo. De forma a resolver estes problemas, esta tese apresenta um acelerador de proposito geral que pode ser acoplado a um conjunto heterogeneo de cores e suporta DVFS, sinergisticamente combinando técnicas para uma melhor combinação entre diferentes aplicações e hardware quando comparado aos designs existentes hoje. A arquitetura resultante, MuTARe, provê uma estrutura regular e reconfigurável que é adequada para aceleração automática de código já exisente através de tradução binária. Além disso, *MuTARe* também provê uma estrutura adequada para aplicar dois emergentes paradigmas de computação que podem aumentar a eficiencia de potência: computação no nível da tensão de threshold (mantendo a capacidade de aceleração transparente) e computação aproximativa. Comparado a um sistema heterogeneo tradicional com suporte a DVFS, a arquitetura MuTARe base pode automaticamente melhorar o tempo de execução em 1.3×, ou adaptar-se para o mesmo baixo tempo de execução com uma redução de  $1.6 \times$  no consumo energético, ou adaptar-se para o mesmo baixo nível de energia com  $2.3 \times$  melhor performance. No modo *near-threshold*, *MuTARe* pode melhorar o consumo de potência de forma transparente em mais 30% em tarefas que exigem bastante memória operando o circuito combinacional à metade da frequencia da memória. No modo computação aproximativa, MuTARe consegue melhorar o consumo de potência em até mais 50% usando unidades funcionais aproximativas para as computações.

**Palavras-chave:** arquiteturas de computadores, arquiteturas reconfiguráveis, arquiteturas adaptativas, computação aproximativa, computação no nível da tensão de threshold.

#### LIST OF ABBREVIATIONS AND ACRONYMS

- V<sub>dd</sub> Operating Voltage.

- $V_{th}$  Threshold Voltage.

- f Operating Frequency.

- ALU Arithmetic-Logic Unit.

- ANN Artificial Neural Network.

- ASIC Application-Specific Integrated Circuit.

- AxC Approximate Computing.

- BB Basic Block.

- BT Binary Translation.

- CAD Computer-Aided Design.

- CCA Configurable Compute Accelerator.

- CGRA Coarse-Grained Reconfigurable Array.

- CLB Configurable Logic Block.

- CMP Chip Multi-Processor.

- CPU Central Processing-Unit.

- CReAMS Custom Reconfigurable Arrays for Multiprocessor Systems.

- DCT Discrete Cosine Transform.

- DFG Data-Flow Graph.

- DIM Dynamic Instruction Merging.

- DSE Design-Space Exploration.

- DVFS Dynamic Voltage and Frequency Scaling.

- DySER Dynamically Specializing Execution Resources.

- EDP Energy-Delay Product.

- FA Full Adder.

- FGRA Fine-Grained Reconfigurable Array.

- FP Floating-Point.

- FPGA Field-Programmable Gate Array.

- FU Functional Unit.

- GPP General-Purpose Processor.

- GPU Graphics Processing Unit.

- HARTMP Heterogeneous Arrays for Reconfigurable and Transparent Multicore Processing.

- HPC High-Performance Computing.

- iACT Intel Approximate Computing Toolkit.

- IDCT Inverse Discrete Cosine Transform.

- ILP Instruction-Level Parallelism.

- IMPACT IMPrecise adders for low-power Approximate CompuTing.

- IoT Internet-of-Things.

- ISA Instruction-Set Architecture.

- ISE Instruction-Set Extension.

- LSB Least-Significant Bit.

- LUT Lookup Table.

- ME Motion Estimation.

- MuTARe Multi-Target Adaptive Reconfigurable Architecture.

- NPU Neural Processing Unit.

- NRE Non-Recurrent Engineering.

- NTV Near-Threshold Voltage.

- OoO Out-Of-Order.

- OP Operating Point.

- PC Program Counter.

- PE Processing Element.

- PSNR Peak Signal-to-Noise Ratio.

- PSoC Programmable System-On-Chip.

- PVT Process-Voltage-Temperature.

- RISP Reconfigurable-Instruction-Set Processor.

- RMSE Root-Mean-Squared Error.

- ROB Re-Order Buffer.

- RTL Register-Transfer Level.

- RU Reconfigurable Unit.

- SAD Sum of Absolute Differences.

SIMD Single Instruction Multiple Data.

SNNAP Systolic Neural Network Accelerator in Programmable Logic.

SoC System-on-Chip.

SRAM Static Random-Access Memory.

SSIM Structural Similarity Index.

STV Super-Threshold Voltage.

SVM Support Vector Machine.

TLP Thread-Level Parallelism.

VOS Voltage Over-scaling.

## LIST OF FIGURES

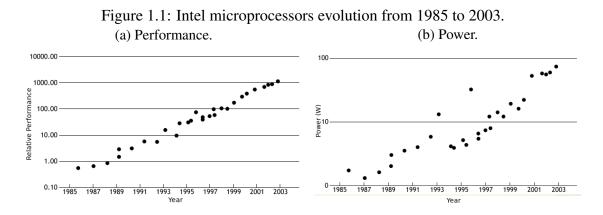

| Figure 1.1  | Intel microprocessors evolution from 1985 to 2003                            | .15 |

|-------------|------------------------------------------------------------------------------|-----|

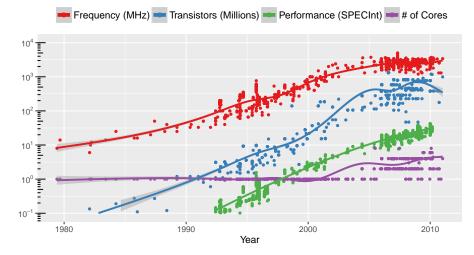

| Figure 1.2  | Microprocessor evolution in the last 30 years.                               | .17 |

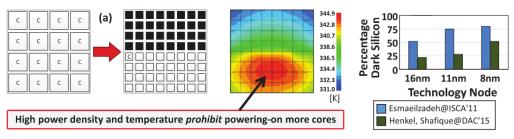

| Figure 1.3  | The dark silicon problem.                                                    | .17 |

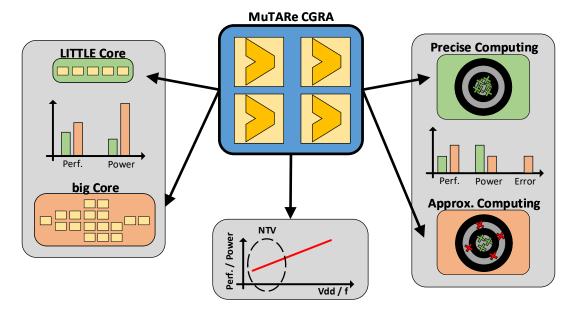

| Figure 1.4  | Overview of the proposed MuTARe architecture.                                | .20 |

| Figure 2.1  | Overview of a RISP                                                           | .24 |

|             | Code transformation in a RISP.                                               |     |

| Figure 2.3  | Comparison between an FPGA and a CGRA                                        | .27 |

| Figure 2.4  | Overview of the Warp Processor                                               | .29 |

| Figure 2.5  | Overview of the Thread Warping approach                                      | .29 |

| Figure 2.6  | Overview of the CCA hardware.                                                | .30 |

|             | Overview of the DIM system                                                   |     |

| Figure 2.8  | Overview of the CReAMS and HARTMP systems                                    | .31 |

| Figure 2.9  | Overview of the DySER system.                                                | .32 |

| Figure 2.10 | ) Code transformation and execution in the DySER system                      | .32 |

| Figure 2.11 | 1 The DynaSpAM system                                                        | .34 |

| Figure 2.12 | 2 Effects of voltage scalability in delay and energy consumption             | .35 |

| Figure 2.13 | 3 Impact in maximum frequency as $V_{dd}$ is lowered (logic vs memory)       | .37 |

| Figure 2.14 | 4 Impacts of variability in STV and NTV voltage levels.                      | .38 |

| Figure 2.15 | 5 Overview of the approximate computing paradigm.                            | .42 |

| Figure 2.16 | 5 Distinct quality levels for an image when using RMSE as metric             | .43 |

| Figure 2.17 | 7 Images affected by distinct forms of error, with the same RMSE value       | .44 |

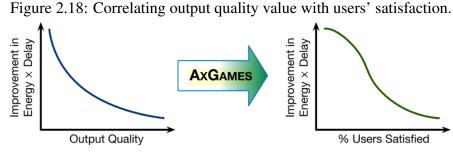

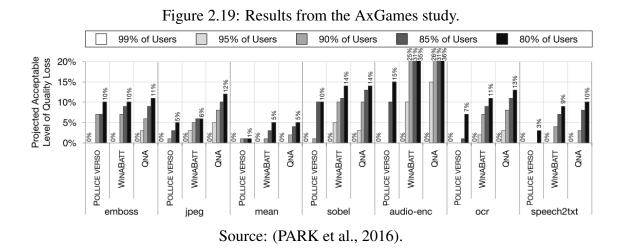

| Figure 2.18 | <sup>3</sup> Correlating output quality value with users' satisfaction       | .46 |

| Figure 2.19 | P Results from the AxGames study.                                            | .46 |

| Figure 2.20 | ) Implementation of 2x2 matrix multiplication at distinct abstraction levels | .47 |

|             | Variable and code region annotation for approximate computing                |     |

| Figure 2.22 | 2 Example of using the EnerJ framework                                       | .51 |

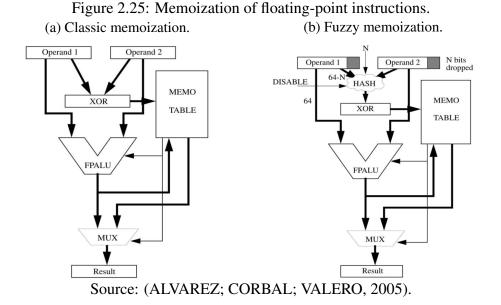

|             | 5 Memoization of floating-point instructions.                                |     |

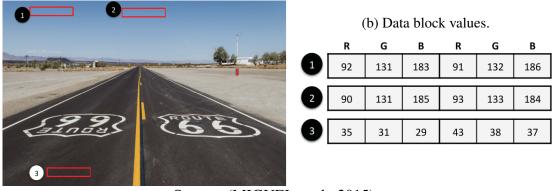

| Figure 2.26 | 5 Data redundancy in image processing applications                           | .56 |

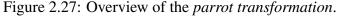

|             | 7 Overview of the <i>parrot transformation</i> .                             |     |

| Figure 2.28 | B Design space for implementing an NPU.                                      | .57 |

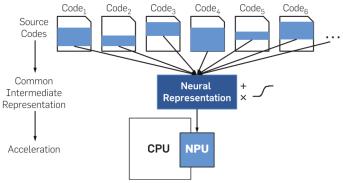

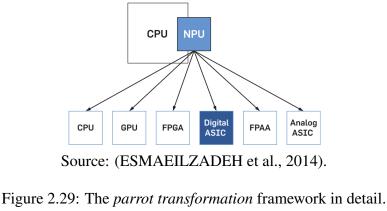

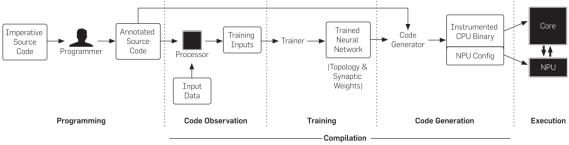

|             | P The parrot transformation framework in detail                              |     |

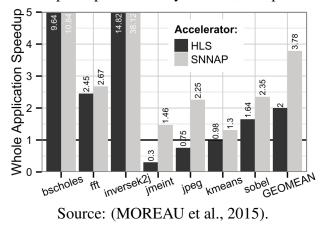

|             | ) Speedup achieved by SNNAP, compared to HLS.                                |     |

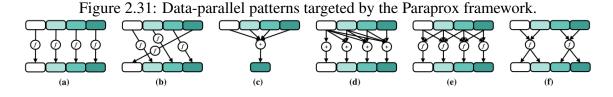

| Figure 2.31 | Data-parallel patterns targeted by the Paraprox framework.                   | .61 |

| Figure 3.1  | Overview of MuTARe.                                                          | .64 |

| Figure 3.2  | Overview of MuTARe's RU.                                                     | .65 |

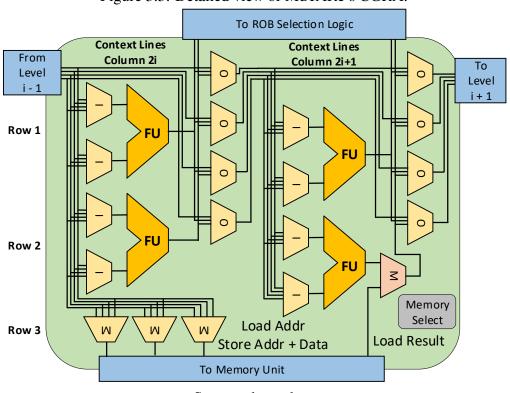

| Figure 3.3  | Detailed view of MuTARe's CGRA.                                              | .66 |

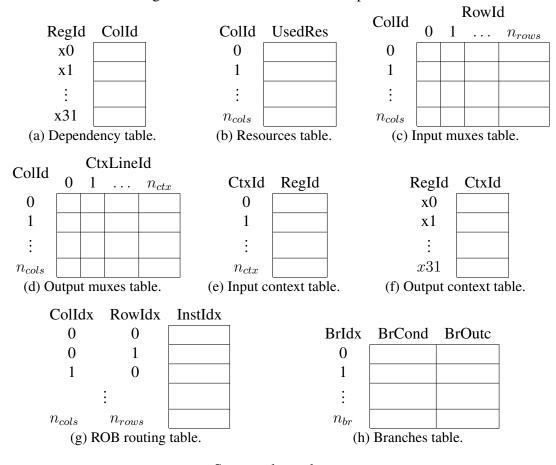

|             | Tables used in the BT process.                                               |     |

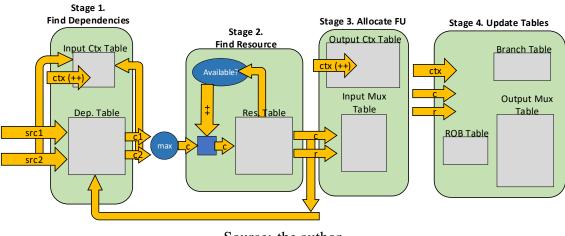

| Figure 3.5  | Overview of MuTARe's BT unit.                                                | .70 |

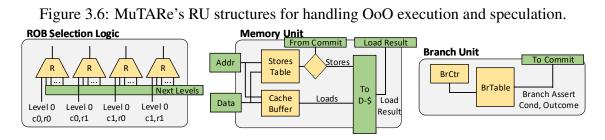

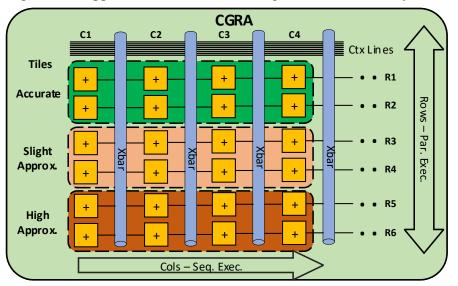

|             | MuTARe's RU structures for handling OoO execution and speculation            |     |

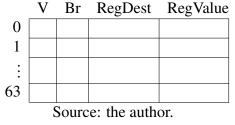

|             | Approx-MuTARe's CGRA organized into accuracy tiles.                          |     |

|             | Design flow for Approx-MuTARe                                                |     |

|             | NTV-MuTARe's voltage islands organization.                                   |     |

|             | Accelerated chains of memory operations in NTV-MuTARe                        |     |

| Figure 4.5  | Variability management strategy employed by NTV-MuTARe.                      | .85 |

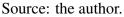

| Figure 5.1  | gem5 simulation flow                                                         | .88 |

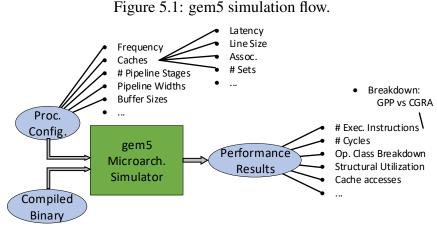

| Figure 5.2  | CACTI flow                                                               | 89   |

|-------------|--------------------------------------------------------------------------|------|

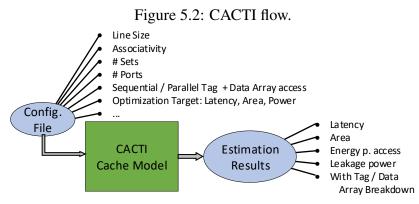

| Figure 5.3  | McPAT flow.                                                              | 90   |

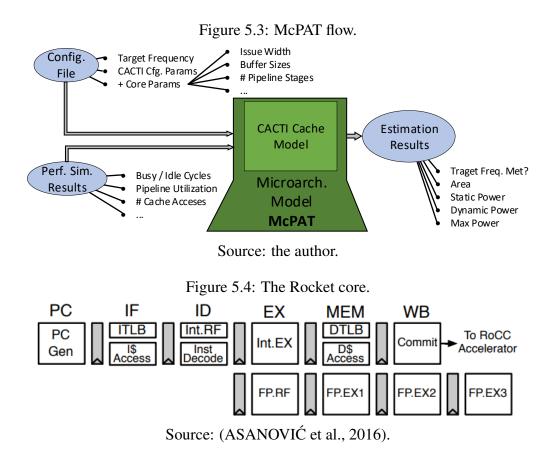

| Figure 5.4  | The Rocket core                                                          | 90   |

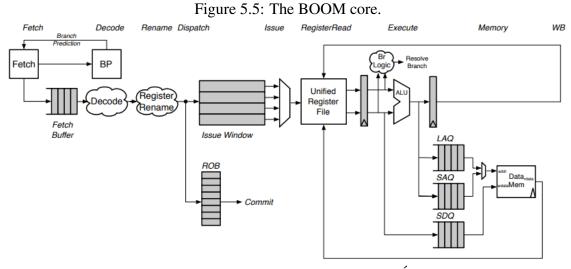

| Figure 5.5  | The BOOM core.                                                           | 91   |

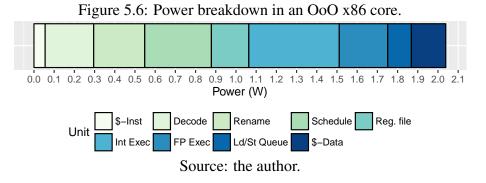

| Figure 5.6  | Power breakdown in an OoO x86 core.                                      | 93   |

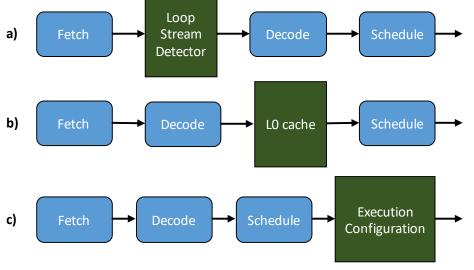

| Figure 5.7  | Using MuTARe's CGRA to cache instruction schedules in OoO cores          | 94   |

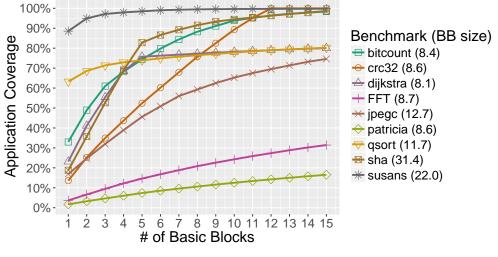

| Figure 5.8  | Number of unique basic blocks required to cover an application           | 96   |

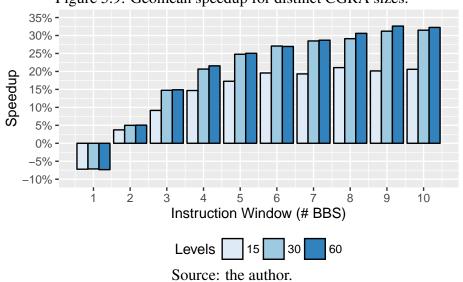

|             | Geomean speedup for distinct CGRA sizes.                                 |      |

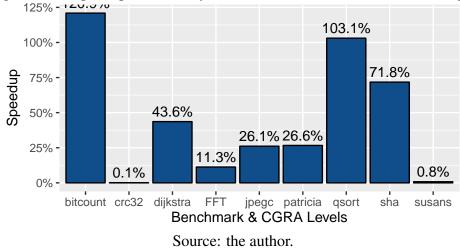

| Figure 5.10 | ) Speedup achieved by each benchmark with the 30-level design            | 97   |

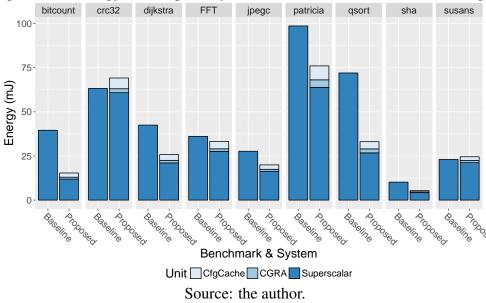

| Figure 5.11 | Energy consumption by each benchmark with the 30-level design            | 98   |

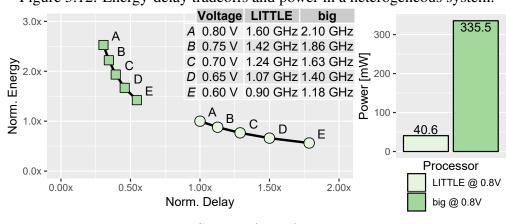

|             | 2 Energy-delay tradeoffs and power in a heterogeneous system             |      |

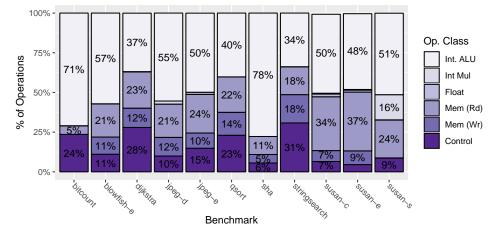

| Figure 5.13 | Benchmark operation class mix                                            | .100 |

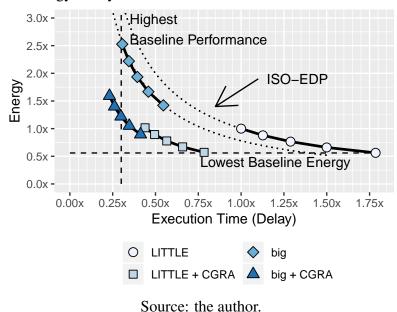

| Figure 5.14 | Energy-Delay curves for different execution units and DVFS levels        | .103 |

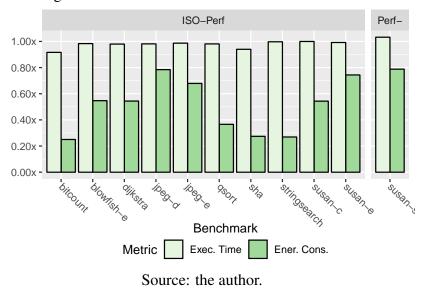

|             | 5 Results from <i>t</i> -constrained execution                           |      |

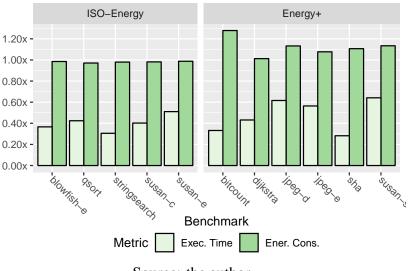

|             | 6 Results from <i>e</i> -constrained execution                           |      |

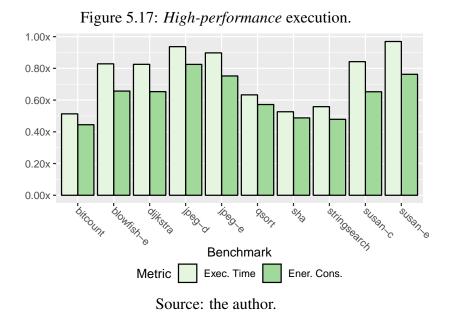

|             | 7 High-performance execution                                             |      |

| Figure 5.18 | B Performance and energy consumption under the effects of task migration | .107 |

| 0           | Benchmarks operation class mix.                                          |      |

|             | ) Energy-Delay tradeoffs and optimal operating region                    |      |

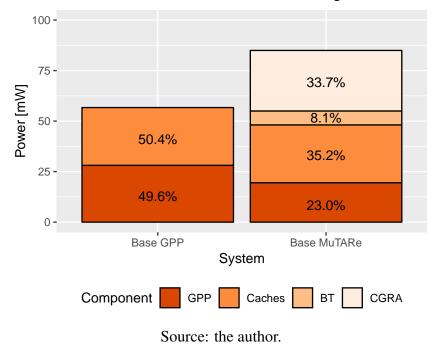

| •           | Power breakdown with and without reconfigurable acceleration             |      |

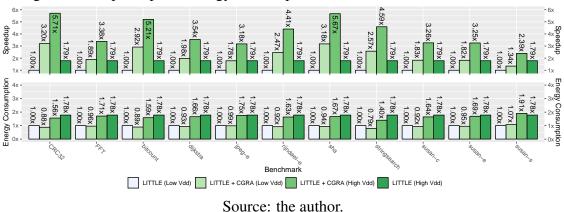

|             | 2 Speedup and energy consumption in a LITTLE core and in MuTARe          |      |

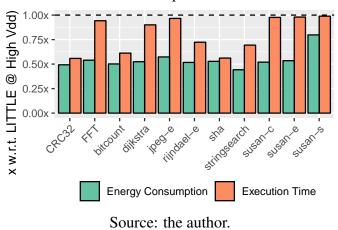

|             | 3 MuTARe's behavior in performance-constrained execution.                |      |

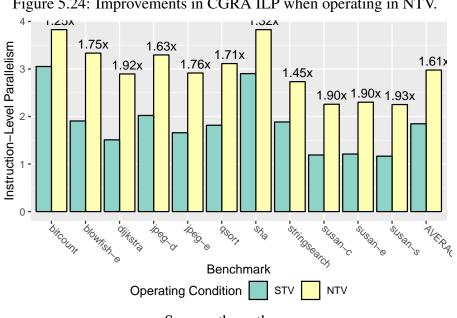

|             | Improvements in CGRA ILP when operating in NTV.                          |      |

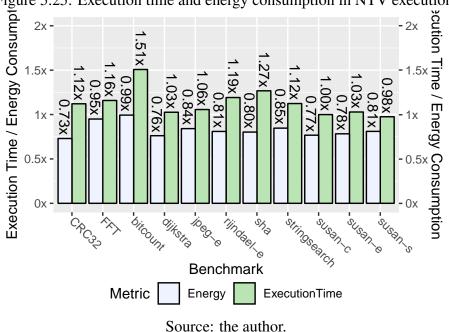

|             | 5 Execution time and energy consumption in NTV execution                 |      |

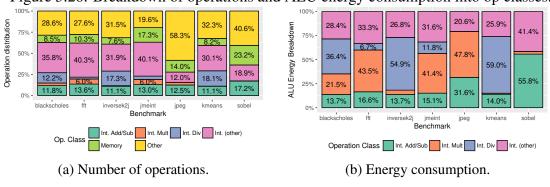

| -           | 6 Breakdown of operations and ALU energy consumption into op classes.    |      |

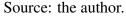

|             | 7 Output quality distribution of approximate FUs                         |      |

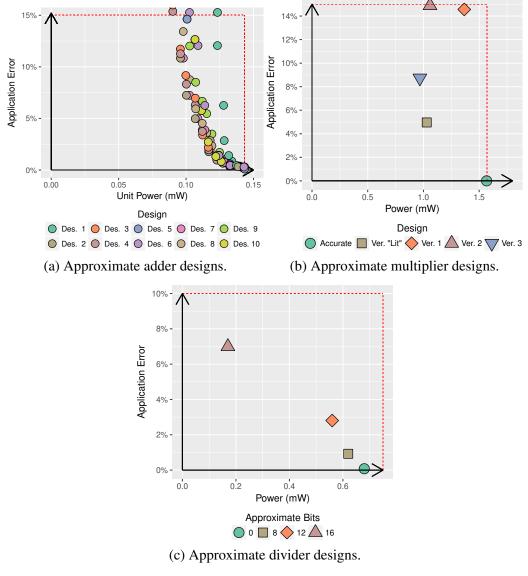

|             | B Design space of approximate multi-bit adders and multipliers           |      |

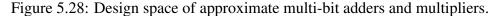

|             | Application speedup when executing in the CGRA                           |      |

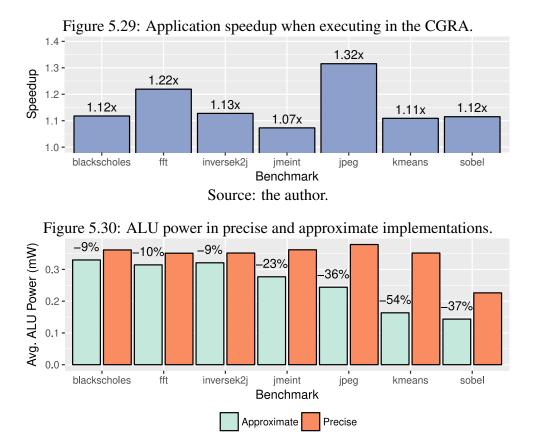

|             | ) ALU power in precise and approximate implementations.                  |      |

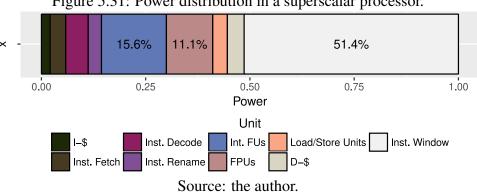

| Figure 5.3  | Power distribution in a superscalar processor                            | .123 |

|             |                                                                          |      |

### LIST OF TABLES

| Table 1.1         Device scaling in the Dennard and Post-Dennard eras.         |             |

|--------------------------------------------------------------------------------|-------------|

| Table 2.1 Example of error metrics used for distinct applications              | 45          |

| Table 2.2 Language constructs for approximation in EnerJ                       |             |

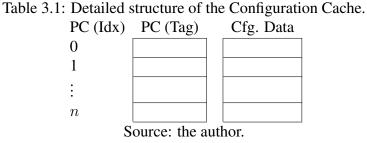

| Table 3.1 Detailed structure of the Configuration Cache.                       | 73          |

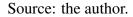

| Table 3.2         Structure of the simplified ROB used for storing operation's | results74   |

| Table 5.1 Baseline processor parameters.                                       |             |

| Table 5.2 CGRA parameters.                                                     |             |

| Table 5.3 Detailed results for the execution with 30 levels                    | 97          |

| Table 5.4 Benchmark groups                                                     |             |

| Table 5.5 CGRA parameters.                                                     |             |

| Table 5.6 Rocket and BOOM synthesis results                                    |             |

| Table 5.7 Cache parameters and results from FinCACTI.                          |             |

| Table 5.8 Modeling parameters for the <i>big</i> core.                         |             |

| Table 5.9 Detailed performance results.                                        |             |

| Table 5.10 Evaluation scenarios.                                               |             |

| Table 5.11 Execution times for an image processing pipeline in two so          | cenarios109 |

| Table 5.12 Benchmark groups                                                    |             |

| Table 5.13 Microarchitectural performance for each benchmark                   |             |

| Table 5.14 Baseline processor parameters.                                      |             |

| Table 5.15 Approximate FUs modes selected in the DSE step                      |             |

| Table 5.16 Logic function implemented by the approximate FUs selec             |             |

| Table 5.17 Selected approximation modes and corresponding error                |             |

|                                                                                |             |

## CONTENTS

| 1 INT | <b>TRODUCTION</b>                                                  | .15 |

|-------|--------------------------------------------------------------------|-----|

| 1.1 C | Current challenges in microprocessor design                        | .17 |

|       | cope of this thesis                                                |     |

|       | Contributions of this thesis                                       |     |

| 1.4 S | tructure of this thesis                                            | .22 |

|       | CKGROUND                                                           |     |

|       | econfigurable Architectures                                        |     |

| 2.1.1 | Classification of Reconfigurable Architectures                     | .24 |

|       | Implementations of Reconfigurable Architectures                    |     |

|       | WFS and NTV Computing                                              |     |

|       | Challenges in NTV Operation                                        |     |

|       | Solutions for NTV Operation                                        |     |

|       | pproximate Computing                                               |     |

| 2.3.1 | Assessing Application Quality                                      | .42 |

|       | Determining approximable computations                              |     |

|       | Strategies for approximation                                       |     |

|       | Contributions to the State-of-the-Art                              |     |

|       | TARE - BASE ARCHITECTURE                                           |     |

|       | Overview of MuTARe                                                 |     |

|       | IuTARe's Components                                                |     |

|       | Reconfigurable Unit                                                |     |

|       | Binary Translation Module                                          |     |

|       | Configuration Cache                                                |     |

|       | Interface with GPP                                                 |     |

|       | TARE - EXTENDED ARCHITECTURE                                       |     |

|       | pprox-MuTARe                                                       |     |

|       | Architectural Changes                                              |     |

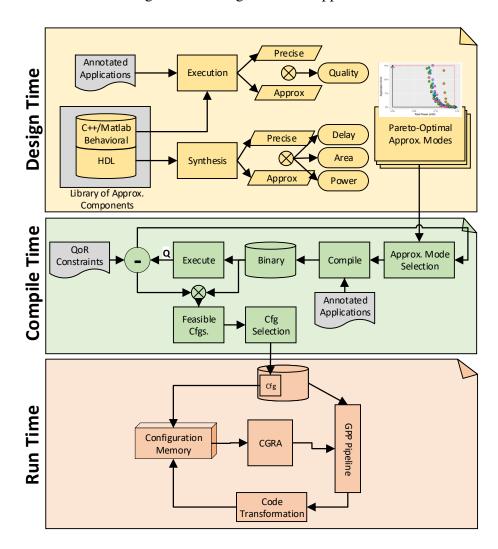

|       | Design, Compilation and Execution Flow Changes                     |     |

|       | TV-Aware MuTARe                                                    |     |

|       | Architectural Changes                                              |     |

|       |                                                                    |     |

|       | fethodology overview, metrics and tools                            |     |

|       | Methodology                                                        |     |

|       | Tools: The gem5 Simulator<br>Tools: CACTI                          |     |

|       | Tools: McPAT                                                       |     |

|       | Tools: Rocketchip Generator                                        |     |

|       | Tools: for Logic Synthesis                                         |     |

|       | Tools: DVFS model                                                  |     |

|       |                                                                    |     |

|       | Tools: Approximate FU models                                       |     |

|       | Scenario 1: High-Performance Computing for General-Purpose Domains |     |

|       | Scenario 2: Heterogeneous Computing for Mobile Domains             |     |

|       | Scenario 2: Ultra Low-Power Computing for Emerging IoT Domains     |     |

|       | Scenario 4: Approximate Computing for Error-Tolerant Domains       |     |

|       | NCLUSIONS                                                          |     |

|       | uture Work                                                         |     |

| O.I L |                                                                    | L4J |

| 6.2 Publications and Presentations                 |  |

|----------------------------------------------------|--|

| 6.2.1 Publications in the Scope of this Thesis     |  |

| 6.2.2 Publications as a Result from Collaborations |  |

| 6.2.3 Presentations                                |  |

| REFERENCES                                         |  |

#### **1 INTRODUCTION**

The microprocessor design landscape has changed dramatically over the last 40 years. For long after the first microprocessors were invented, improvements in CMOS transistor manufacturing followed Moore's and Dennard's scaling rules, allowing for smaller, more efficient and cheaper devices (MOORE, 1965; DENNARD et al., 1974). By that time, performance could be improved in a way that was entirely transparent to the programmers mainly for two reasons. First, smaller transistors presented less capacitance and could be charged faster, allowing circuits to operate at higher frequencies. Second, hardware designers were able to leverage the additional transistors to implement micro-architectural improvements that allowed multiple instructions to execute concurrently, exploiting the Instruction-Level Parallelism (ILP) that the applications presented (OLUKOTUN; HAMMOND, 2005). Given this transparency, programmers and endusers requiring more performance needed only wait for the next processor generation, as the performance was increasing exponentially (Fig. 1.1a). However, while the scaling rules promised constant power density as technology evolved, in practice device power has increased over the years (Fig. 1.1b), mostly because the operating voltage scaled slower than Dennard's predictions. For this reason, the contribution of static power (ignored in Dennard's original model) to the total power has significantly increased over the years (BOHR, 2007). However, since cooling technologies did not evolve proportionally, hardware designers reached a *power wall* - a limitation in the maximum power that any chip could sustain. Therefore, as transistors entered the nano-era, the strategy to keep increasing operation frequencies and providing transparent performance improvements proved to be unsustainable. Table 1.1 illustrates the power impacts of scaling, for a factor S, before and after Dennard's model broke down in the first years of the last decade.

|                         | Dennard Scaling         | Post-Dennard Scaling |

|-------------------------|-------------------------|----------------------|

| Device Count            | $S^2$                   | $S^2$                |

| <b>Device Frequency</b> | S                       | S                    |

| Device power (cap)      | $\frac{1}{S}$           | $\frac{1}{S}$        |

| Device power (Vdd)      | $\frac{\tilde{1}}{S^2}$ | 1                    |

| Power Density           | ĩ                       | $S^2$                |

Table 1.1: Device scaling in the Dennard and Post-Dennard eras.

Source: (SHAFIQUE; GARG, 2017).

The *power wall* has led, in the last fifteen years, to a shift in the microprocessor design paradigm, as can be seen in Fig. 1.2. Even though the technology itself allowed for frequency increases, these would incur power overheads that would breach the power wall. Moreover, designers realized that processors had reached a stage in which exploiting additional ILP provided only marginal performance increases due to the practical limitation in the parallelism available from applications (WALL, 1991).

At the same time, however, new application domains emerged with the rise of High-Performance Computing (HPC) systems and the Internet, requiring processing of multiple independent tasks or requests simultaneously. These restrictions and demands led to the development of the first Chip Multi-Processors (CMPs), a solution integrating multiple processor cores with shared memory into the same die which could improve the performance in these emerging workloads without the power overheads of frequency increases (BORKAR et al., 2005). Besides accelerating applications with independent concurrent tasks, multicore processors offered the possibility of scalable linear speedups even to a single application. However, in that case, programmers were required to segment the applications into independent tasks to expose the Thread-Level Parallelism (TLP) that they presented - a task which is often non-trivial (BLAKE et al., 2010).

The CMPs solution just describedd provided for many years a scalable solution to increase performance, but this approach has also been challenged in the last decade (ESMAEILZADEH et al., 2012). Voltage scaling has significantly slowed down to avoid exacerbating static power, an issue which becomes more critical as technology scales (MUDGE, 2001) and has lead to even more power consumption increases across generations (SHAFIQUE; GARG, 2017). Therefore, modern designs have again reached a stage where the *power wall* prevents the scalability of the current approach. Because of that, not all cores in the chip can be turned on at the same time, an issue which was then named *dark silicon* (TAYLOR, 2013) and is illustrated in Fig. 1.3a. The figure shows the effect of turning on all cores in a contiguous region of the chip simultaneously: power density

#### Figure 1.2: Microprocessor evolution in the last 30 years.

Source: the author. Data provided by CPU DB (DANOWITZ et al., 2012).

Figure 1.3: The dark silicon problem.

(a) Power densities and temperature profile when all cores (b) Predictions for the in a contiguous region are simultaneously on. dark silicon amount.

Source: (SHAFIQUE; GARG, 2017).

and temperature increase up to a point where the chip may stop functioning correctly. Recent works estimate that the amount of *dark silicon*, i.e., the fraction of the chip that needs to be underutilized to keep it operating within the target power envelope, can reach up to 50% of the chip at the 8 nm technology node (HENKEL et al., 2015), as can be seen in Fig. 1.3b.

#### 1.1 Current challenges in microprocessor design

The end of multicore scaling, in which the tight power envelopes prohibit the straightforward deployment of more cores to improve performance, has caused another significant paradigm change in microprocessor design. Now, more than before, micro-processors are moving away from the concept of general-purpose processing and being designed with particular applications in mind to sustain performance improvements with

power efficiency. To do so, without losing generality, General-Purpose Processors (GPPs) are *extended* with *accelerators*, application-specific designs tailored for efficiently exploiting the sort of parallelism available in each application (PATEL; HWU, 2008). While accelerators allow for the best possible efficiency by perfectly matching the application to the hardware, their use introduces a systemic cost impact (in hardware design and software development) which persists despite several advancements in the field (HWU; PATEL, 2018). From the hardware design perspective, since processors become specialized at design time to a particular (group of) application(s), the target market for each design is restricted, increasing the Non-Recurrent Engineering (NRE) costs. Besides, designers must now have an understanding of the application domain, making them a more valuable (and costly) resource than earlier. From the software development perspective, because accelerators must be programmed using special instructions, the code must be (re)structured in order to leverage the accelerator efficiently, or special (automatic) tools must be deployed to that end. In any case, extensive development effort or programmer's training in the tools is required, both of which increase production costs.

#### **1.2 Scope of this thesis**

The above discussion suggests that, while the excellent match between software and hardware makes accelerators highly-efficient execution units, capable of addressing the performance and power challenges just described, they introduce significant costs to the hardware and software development processes. Besides, since their design is fixed, they cannot adapt well to workload sets that change over time. In domains where applications are constantly evolving at a fast pace, such as in the Internet-of-Things (IoT), application-specific designs may have a too high cost that prohibits their utilization (ADEGBIJA et al., 2018). As a consequence, *accelerators* could be significantly improved if they were *more generic*, had *smaller programmability costs* and had better *run-time adaptation* capabilities.

Considering this context, *reconfigurable accelerators* present an alternative that can address most of the issues associated with application-specific ones. These devices typically consist of arrays of Processing Element (PE) with programmable interconnects, allowing customized datapaths that match each application's needs to be defined at run time. While not as efficient as an *application-specific* accelerator, they can provide considerable efficiency improvements compared to GPP while amortizing the design costs and increasing the range of applications the device can run. Moreover, *reconfigurable accelerators* can be leveraged transparently for automatic acceleration of code that is already deployed with techniques such as dynamic binary translation, reducing the cost overheads in the development process. Moreover, as will be shown in this thesis, they provide a suitable structure for combining other techniques, such as *approximate computing* and *near-threshold voltage* computing.

#### **1.3** Contributions of this thesis

To address the challenges in designing and programming accelerators, and to provide a wider adaptability range than current reconfigurable accelerators, this thesis presents Multi-Target Adaptive Reconfigurable Architecture (MuTARe). MuTARe synergistically combines multiple adaptability techniques for transparent adaptation between different applications and the hardware when compared to current reconfigurable designs. It is *multi-target* in the sense that it can be *targeted* towards different application domains and, besides adapting to each application, can also dynamically adapt to different *target* metrics, such as meeting a performance target while saving power or meeting a power target while maximizing performance. MuTARe goes beyond traditional reconfigurable architectures by providing support for two emerging computing paradigms that can further boost the power efficiency: *near-threshold voltage computing* and *approximate computing*.

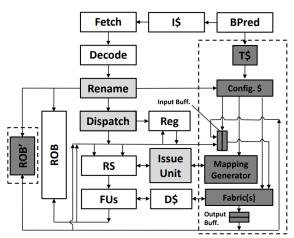

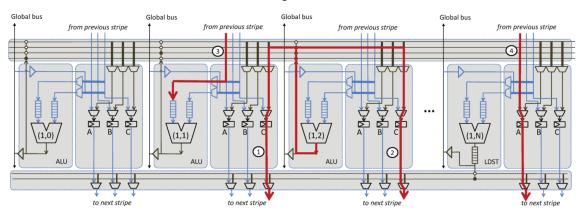

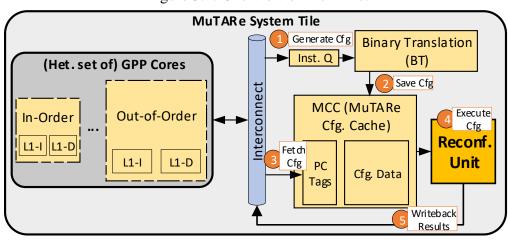

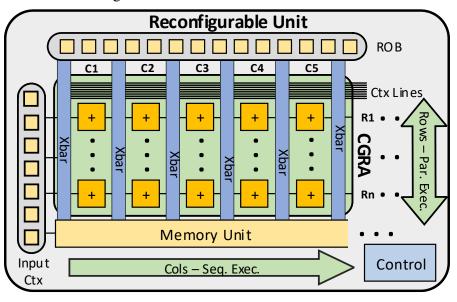

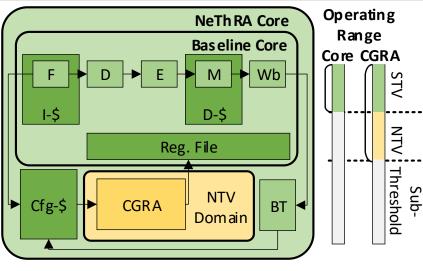

Fig. 1.4 presents an overview of the MuTARe architecture. The heart of MuTARe is a parametrisable and combinatorial Coarse-Grained Reconfigurable Array (CGRA) that can be coupled to different forms of GPP core: *in-order* cores (for low-power domains, such as IoT), *Out-Of-Order (OoO)* cores (for high-performance domains, such as HPC), or even both of them in a *big.LITTLE*-like setup (for mobile domains requiring a wide adaptability range). The acceleration capabilities can be combined with Dynamic Voltage and Frequency Scaling (DVFS) to precisely adjust for the performance levels required, lowering the Operating Frequency (f) and Operating Voltage ( $V_{dd}$ ) when possible to reduce power consumption. With these techniques, MuTARe can work transparently for already deployed binaries by providing, as a dedicated hardware module, a dynamic binary translation algorithm that automatically maps recurring instruction sequences into the CGRA for acceleration.

In the first step to move beyond traditional reconfigurable architectures, MuTARe

Figure 1.4: Overview of the proposed MuTARe architecture.

Source: the author.

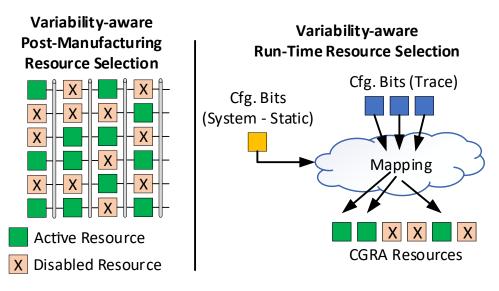

provides support for the operation in the Near-Threshold Voltage (NTV) range, where the lowest-energy operating point is typically found (MITTAL, 2015). In this challenging operating environment, memories become more prone to failure, and the effects of Process-Voltage-Temperature (PVT) variation are increased, requiring the use of special techniques during design to address these issues. MuTARe avoids these difficulties by providing a suitable structure for NTV computing: a combinatorial CGRA with a separate voltage domain from the memories, which is also a regular structure that may be designed with overprovisioned PEs to address variability issues. This operating mode can also be activated transparently, with no need to recompile existing code, and provides a considerable boost to power efficiency especially in memory-bound applications.

In a second step to improve over reconfigurable architectures, MuTARe provides support for Approximate Computing (AxC) to improve power efficiency in emerging error-tolerant workloads. While many works have shown the power benefits of deploying approximate functional units (SHAFIQUE et al., 2016), GPPs are typically unsuitable for this approach since the most significant fraction of power consumption is spent in control, rather than in processing. When moving the execution from the GPP to a combinatorial CGRA, however, the potential benefits of approximate functional units can be leveraged to their full extension. Support for approximate computing requires Instruction-Set Architecture (ISA) extensions to configure the accuracy, since that is a piece of semantic information that must be provided by the application developer, so this execution mode introduces to the base architecture Instruction-Set Extensions (ISEs) that may be used towards that end.

The contributions of this thesis can be summarized as follows:

- A reconfigurable architecture based on a GPP-CGRA coupling, where the GPP may take any form of core (including heterogeneous arrangements with complex OoO cores), which supports DVFS to balance the acceleration capabilities and power consumption. Compared to existing reconfigurable architectures, MuTARe can transparently accelerate existing code, be coupled to any form of processor core and can leverage DVFS to match the performance improvements provided by automatic CGRA acceleration with the performance target, lowering the frequency if slack is available to save additional power.

- A reconfigurable architecture with a suitable structure for computing in the NTV domain. Compared to previous works that use NTV to save power, this one is the first where NTV is used in the context of single-threaded applications. The enhanced ILP exploitation provided by MuTARe's CGRA can partially compensate the performance loss from low-frequency operation, especially in workloads which are memory-bound, and its reconfigurable fabric enables simpler approaches to variablility management.

- A reconfigurable architecture that can leverage the benefits of AxC and provide additional performance improvements and power savings in emerging error-tolerant domains. Compared to existing works oin AxC, this is the first one where a *reconfigurable accelerator* is used for approximate computations, presenting the advantage of maintaining general-purpose processing capabilities while leveraging the full benefits of reduced power consumption in approximate functional units, since the power consumption is switched from control in the GPP to computatin in the CGRA's PEs.

The result is an architecture that can be tuned at design time to better adapt for low-power or high-performance, and at run-time adapt to the application being executed and improve the efficiency.

#### **1.4 Structure of this thesis**

The current chapter has presented an introduction to this thesis, with the problem it addresses, the scope and an overview of the solution: the MuTARe architecture. The remainder of this document is organized as follows.

Chapter 2 present background information for understanding this thesis. It covers reconfigurable accelerators, DVFS and NTV computing, and approximate computing, all of which are concepts exploited by MuTARe.

Chapter 3 presents the base architecture of MuTARe, a GPP core to which a reconfigurable accelerator with dynamic instruction mapping support is coupled and which can leverage DVFS to adapt to a performance target.

Chapter 4 presents extensions to increase the adaptability range of MuTARe, namely MuTARe with NTV support, and approximate MuTARe.

Chapter 5 presents the methodology and tools used to evaluate MuTARe under very distinct comparison scenarios.

Finally, Chapter 6 presents the conclusions of this work, summarizing the vital contributions and results, points towards future research directions and presents the publications by the author in the scope of this thesis.

#### **2 BACKGROUND**

This chapter presents background information essential for the understanding of this thesis. It covers reconfigurable architectures, DVFS, and NTV computing, and approximate computing. For each of these techniques, examples of systems that use them are presented and also the key novelties of the MuTARe architecture.

#### 2.1 Reconfigurable Architectures

*Reconfigurable accelerators* are hardware units with the ability to specialize to an application at run time by modifying their structure. Systems where these accelerators are coupled to GPP are referred to as Reconfigurable-Instruction-Set Processors (RISPs) (BARAT; LAUWEREINS, 2000)<sup>1</sup>. Through this specialization, reconfigurable accelerators are able to achieve better performance and energy consumption than the GPPs they are coupled to; however, given the flexibility to adapt the hardware structure at run time to different applications, they are usually not as efficient as dedicated Application-Specific Integrated Circuits (ASICs). In summary, these circuits fill a gap between software and hardware implementations of algorithms (COMPTON; HAUCK, 2002; BECK; CARRO, 2010).

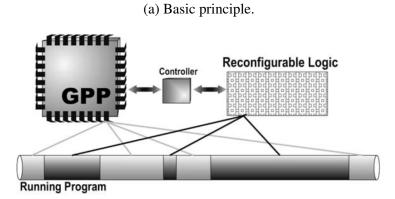

Fig. 2.1 shows how execution works in a RISP. Instructions sequences are executed either in the GPP (when presenting low potential for acceleration, as shown in light gray in the figure) or in the reconfigurable accelerator (when they have high potential for acceleration, as shown in dark gray). A hardware controller handles the configuration, communication and synchronization process between the two execution units. To determine the code sequences which should execute in the accelerator, the hot regions of code (i.e. regions which account for a high fraction of the application's execution time or energy consumption) must be selected (step 1) and transformed into reconfigurable instructions (step 2).

This section proceeds by discussing a classification scheme for RISPs, and then presents relevant implementation examples considering the scope of this work.

<sup>&</sup>lt;sup>1</sup>There is no standard taxonomy in the field, so this form of system has been called many names in the past years, such as *reconfigurable architecture/system*, *spatial architecture*, and some authors even avoid using any specific terms at all, speaking instead of "*a system with configurable components*".

Figure 2.1: Overview of a RISP.

(b) Steps required to map, execute, and write back program regions in the reconfigurable accelerator.

Source: (BECK; CARRO, 2010).

#### 2.1.1 Classification of Reconfigurable Architectures

This work uses a classification scheme similar to the one used by Beck and Carro, which covers (among others) three criteria: *code analysis and transformation, granular-ity*, and *processor coupling* (BECK; CARRO, 2010).

Fig. 2.1b presents a detailed view of each of the steps involved when executing an application in a RISP, from application source code specification to execution results.

The **code analysis and transformation** phase, depicted in steps 1 and 2, can be carried out either **statically** (*offline*, at compile time) or **dynamically** (*online*, at run time). Static schemes are simpler because the application source code is available, but they usually rely on programmer intervention (to identify regions of code that will be accelerated) or compiler modifications (to automatically select these regions). Dynamic schemes, on the other hand, although more complex to implement, present the following advantages:

- They take as input the application binary rather than the source code; therefore, both already-deployed as well as new applications are supported and can leverage the reconfigurable unit for acceleration.

- They have access to dynamic information (such as the frequency of executed code regions) and, therefore, optimization opportunities that are not available at compile time.

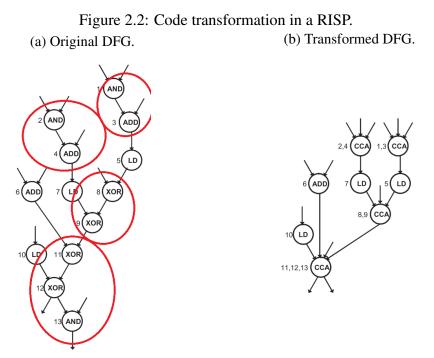

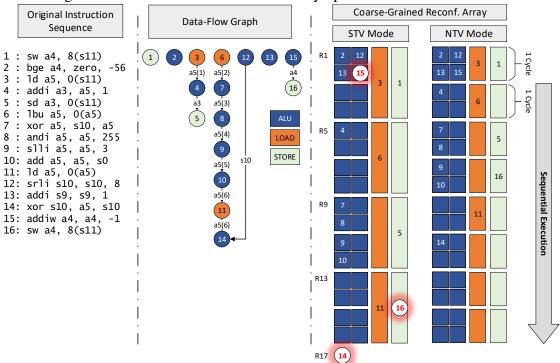

The process of dynamically transforming code from one ISA for execution in another one (e.g. a reconfigurable accelerator) is commonly named *binary translation* (ALT-MAN; KAELI; SHEFFER, 2000). Most of these strategies use graph analysers that work on an application's Data-Flow Graph (DFG) to determine computations that can be transformed into reconfigurable instructions. To illustrate how this process is done, consider Fig. 2.2, which depicts the instructions in an application's basic block (graph nodes) and the data dependencies among them (graph edges). In this particular case, four code regions with data dependencies were transformed into reconfigurable instructions (denoted by CCA in the transformed DFG) that can execute in a single cycle, reducing the height of the DFG from 8 to 4. The height of the DFG represents the number of cycles it would take to execute the kernel in case an unlimited amount of functional units were available (, each of which can execute each instruction in a single cycle). Therefore, in this example, the potential speedup is  $\frac{8}{2} = 2 \times$ .

The accelerator's **granularity** refers to *size* of the reconfigurable logic blocks. There are two categories:

- Fine-Grained Reconfigurable Arrays, in which the reconfigurable logic blocks implement bit-level operations;

- CGRAs, in which the reconfigurable logic blocks implement word-level operations.

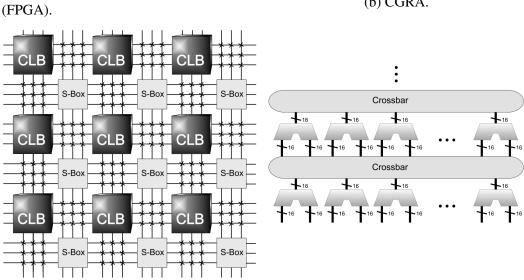

To illustrate the difference, consider Fig. 2.3, which compares both granularities. The Fine-Grained Reconfigurable Array is implemented using an FPGA, which consists of Configurable Logic Blocks (CLBs) and switch-boxes. Each CLB contains an N-input

Source: (CLARK et al., 2004).

Lookup Table (LUT) and a flip-flop; they may be connected arbitrarily by configuring the switch-boxes and therefore implement logical functions of multiple inputs and outputs. The CGRA is a matrix of Arithmetic-Logic Units (ALUs) with crossbar connections between the rows.

While Fine-Grained Reconfigurable Arrays (FGRAs) provide the highest flexibility, there is a tradeoff: the configurations are significantly larger than in CGRAs (as more flexibility implies more configuration bits), and therefore they require larger storage space and also longer configuration times. For this reason, FGRAs are more effective in cases where a circuit needs to be reconfigured only a few times during execution, such as in filter applications (which execute a single hotspot the whole time), and CGRAs tend to be more efficient to implement applications consisting of multiple hotspots.

**Coupling** refers to how the reconfigurable accelerator synchronizes execution and communicates data with the GPP in the system. There are two forms: the accelerator can either be located inside the processor core (having direct access to the register file and first-level caches), in which case it is classified as *tightly-coupled*, or it can be located outside, in which case it is classified as *loosely-coupled*. There is a tradeoff in communication time and circuit speed. Loosely-coupled accelerators can include private memories and operate in a distinct frequency domain as the main processor, and therefore do not affect its critical path. On the other hand, communication must be done via higher-level caches or main memory, which can be significantly slower than in tightly-coupled accel-

Figure 2.3: Comparison between an FPGA and a CGRA. Field-Programmable Gate Array (b) CGRA.

Source: (BECK; CARRO, 2010).

erators.

(a)

A recent work has investigated the tradeoffs involved in computing using tightlycoupled and loosely-coupled accelerators, and shows the performance advantages of looselycoupled ones with private memory (COTA et al., 2015). This work, however, uses a tightly-coupled accelerator, since the goal is to provide transparent reconfigurable acceleration of alraedy deployed code (without needing to rewrite code for using local memories) and fast reconfiguration times.

#### 2.1.2 Implementations of Reconfigurable Architectures

Reconfigurable architectures have been studied for quite some time and have been the subject of many surveys over the years (BARAT; LAUWEREINS, 2000; COMPTON; HAUCK, 2002; BECK et al., 2008; WIJTVLIET; WAEIJEN; CORPORAAL, 2016). Most of these architectures use static strategies to generate instructions for the reconfigurable fabric. Since this work uses a dynamic strategy, static architectures are only briefly described here due to their historical significance.

Concise (KASTRUP; BINK; HOOGERBRUGGE, 1999) and Chimaera (YE et al., 2000) use a tightly coupled Reconfigurable Unit (RU) that works as an ordinary functional unit and limited to combinational logic only. The GARP machine (CALLA-HAN; HAUSER; WAWRZYNEK, 2000) comprises a MIPS-compatible processor with a

loosely-coupled and fine-grained RU. REMARC (MIYAMORI; MIYAMORI; OLUKO-TUN, 1998) also uses a fine-grained RU and works as a loosely coupled coprocessor. RaPiD (CRONQUIST et al., 1998) and Piperench (GOLDSTEIN et al., 2000) are examples of architectures using coarse-grained RUs. The main novelty of the Piperench architecture is the concept of *pipelined reconfiguration*: given kernel is broken into pieces that can be reconfigured and executed on demand. Afterwards, in a process called virtualization, they are multiplexed in time and space to be executed in the reconfigurable logic. The Molen (VASSILIADIS et al., 2004) microcoded RU is fine-grained, loosely-coupled, and works together with a PowerPC processor core. DISC (WIRTHLIN; HUTCHINGS, 1995), OneChip (WITTIG; CHOW, 1996), PRISM-II (WAZLOWSKI et al., 1993) are other reconfigurable architectures that employ standard fine-grained FPGA resources. In the group of coarse-grained RUs, one could also include: Pact-XPP (BAUMGARTE et al., 2003), Morphosys (SINGH et al., 2000), Pleiades (ZHANG et al., 2000) and ADRES (MEI et al., 2003). Furthermore, there are reconfigurable architectures that are very similar to dataflow machines. For instance, TRIPS is based on a hybrid von-Neumann/dataflow architecture that combines an instance of coarse-grained, polymorphous grid processor core with an adaptive on-chip memory system (SANKARALINGAM et al., 2003). TRIPS uses three different execution modes, focusing on instruction-, dataor thread-level parallelism. Wavescalar (SWANSON et al., 2003) is another example, and its implementation is very similar to the structure found in TRIPS.

All of the systems just described require dedicated instructions implemented in the ISA to program the RU. Next, a few systems supporting automatic code generation are described in more detail due to their relevance to the scope of this thesis.

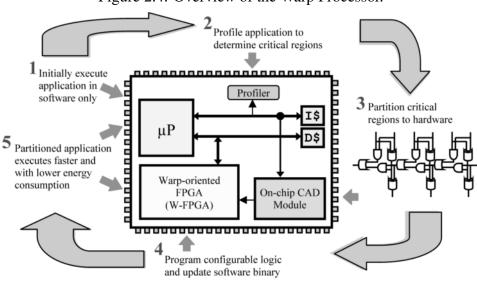

The **Warp Processor**, shown in Fig. 2.4, is one of the first systems to use a dynamic strategy to map application code while it executes into a RU (LYSECKY; STITT; VAHID, 2006). The Warp Processor consists of an ARM core, a profiler, a dedicated Computer-Aided Design (CAD) processor and a simplified FPGA, and works as follows. While the program executes normally in the ARM core, the profiler identifies the critical kernels within the application. Then, the dedicated CAD processor executes special CAD tools to transform the software regions into custom hardware using the FPGA's resources. The program binary is then updated to run critical kernels in the FPGA rather than the ARM core. A mutually-exclusive execution model is used to switch execution from the ARM processor to the custom hardware next time one of the critical kernels is executed. Since the main processor and the FPGA share the same data cache, issues with cache

coherency and consistency are avoided.

Figure 2.4: Overview of the Warp Processor.

Source: (LYSECKY; STITT; VAHID, 2006).

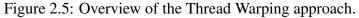

The **Thread Warping** approach, shown in 2.5, extends the Warp Processor to multicore systems, sharing a single reconfigurable FPGA fabric across multiple cores (STITT; VAHID, 2011). The approach uses operating system support to identify thread functions to map to the FPGA.

Source: (STITT; VAHID, 2011).

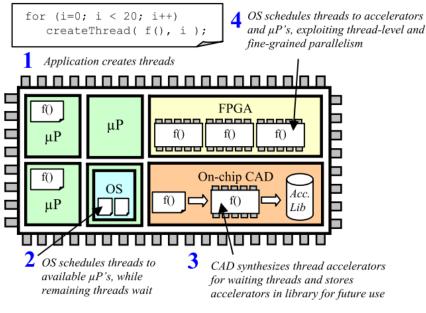

The **Configurable Compute Accelerator (CCA)** (CLARK et al., 2004), depicted in Fig. 2.6, uses a configurable matrix of functional units tightly coupled to the processor

pipeline as an additional functional unit. It can be used to implement regions of code with four inputs and two outputs consisting of basic logic and arithmetic operations. Static and dynamic approaches are proposed for generating custom CCA instructions from application kernels. In the dynamic approach, application kernels are discovered at runtime using a graph analyser and transformed into special CCA instructions, which replace the Central Processing-Unit (CPU) ones in the system's trace cache. CCA instructions may not include memory accesses, which restricts their scope, and are limited to very short regions with small input sizes.

Source: (CLARK et al., 2004).

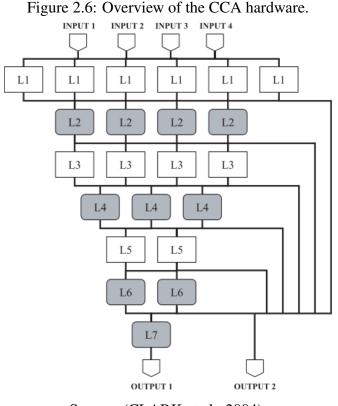

The **Dynamic Instruction Merging (DIM)** system, shown in 2.7, uses a CGRA that is tightly coupled to a MIPS processor (BECK; RUTZIG; CARRO, 2014). With a simplified hardware binary translation algorithm, application kernels are dynamically transformed into CGRA configurations and saved in a dedicated cache. Unlike the CCA, the system accesses the dedicated cache using the program counter Program Counter (PC) of the application kernels to check if they can execute in the array.

**Custom Reconfigurable Arrays for Multiprocessor Systems (CReAMS)** extends DIM by proposing an homogeneous system consisting of multiple reconfigurable processors, thereby also allowing the exploitation of TLP (RUTZIG; BECK; CARRO, 2013). **Heterogeneous Arrays for Reconfigurable and Transparent Multicore Pro**-

Figure 2.7: Overview of the DIM system.

Source: (BECK; RUTZIG; CARRO, 2014).

**cessing (HARTMP)** improves over CReAMS by considering a multi-core system of heterogeneous processors with homogeneous ISA (SOUZA et al., 2016). Fig. 2.8 illustrates the difference between both approaches.

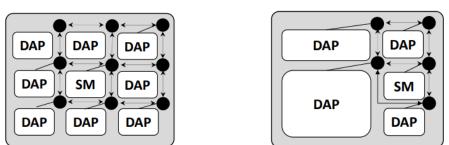

Figure 2.8: Overview of the CReAMS and HARTMP systems. (a) CReAMS. (b) HARTMP.

Source: (SOUZA et al., 2016).

**Dynamically Specializing Execution Resources (DySER)** is a coarse-grained reconfigurable accelerator, tightly coupled to the processor's execution unit, with the claim to unify *functionality and parallelism specialization* into a single hardware (GOVIN-DARAJU et al., 2012). This is an interesting distinction made by the authors which deserves better clarification:

• *parallelism specialization* uses homogeneous hardware resources with wide and independent interconnects. Vector processors, Single Instruction Multiple Data (SIMD), and Graphics Processing Unit (GPU) are strategies that exploit this form

of specialization;

• *functionality specialization* uses heterogeneous, task-specific resources and routing. The works discussed in this section are examples of strategies to exploit this form of specialization.

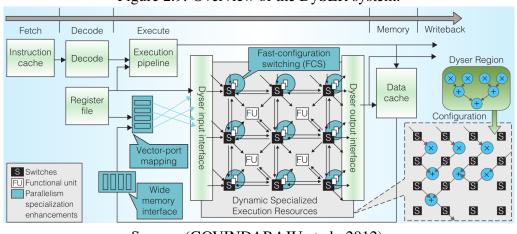

Figure 2.9: Overview of the DySER system.

Source: (GOVINDARAJU et al., 2012).

An overview of the DySER system is presented in Fig. 2.9. The reconfigurable accelerator consists of a matrix of heterogeneous functional units surrounded by programmable switches that can route data to the adjacent tiles, forming a hardware data path once configured. This accelerator is integrated to the processor's execution stage, which acts as a load/store engine to feed the DySER hardware.

```

Figure 2.10: Code transformation and execution in the DySER system.(a) DFG.(b) CPU execution.(c) DySER transformation.(d) DySER execution.

```

Source: (GOVINDARAJU et al., 2012).

A comparison between CPU and DySER execution is provided in Fig. 2.10. In Fig. 2.10a, the DFG of a selected code region is presented. It is a 4-input, 1-output

code pattern (similar to a reduction) consisting of multiplications and sums. Fig. 2.10b shows how this sequence would execute in a 2-issue superscalar processor when invoked twice. A total of 13 cycles are required. Fig. 2.10c shows how this DFG is adapted for execution in DySER: the computation subregion is extracted, and the loads/stores are left for execution in the CPU to exploit its structures that support memory parallelism. Finally, Fig. 2.10d shows how this same execution occurs in DySER, and the opportuniity to pipeline both invocations resulting in a total of only 8 cycles to execute the region. DySER was originally programmed by using a special compiler that selected the regions that will be offloaded to the RU. Later, the **DORA** automatic code generation system was developed for DySER, with support for automatic code transformation (WATKINS; NOWATZKI; CARNO, 2016).

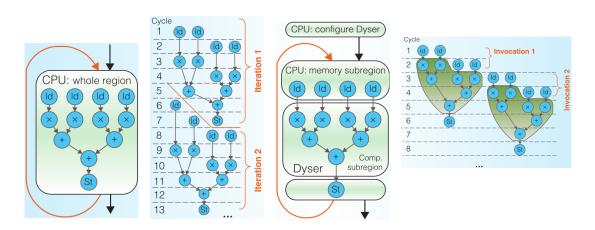

**DynaSpAM**, presented in Fig. 2.11, is a reconfigurable accelerator coupled to an OoO superscalar pipeline (LIU et al., 2015). The insight of the work is that the existing OoO scheduling logic can be leveraged, with some adaptions, to simultaneously allocate instructions in the pipeline and translate instruction sequences for execution in a CGRA. Moreover, an additional Re-Order Buffer (ROB) is used to hold results of the instructions executed in the CGRA, allowing for in-order commit as is done in the superscalar.

#### 2.2 DVFS and NTV Computing

Considering the relationship between  $V_{dd}$  and power consumption, many modern processors support DVFS, a technique that allows tuning the processor's  $V_{dd}$  and frequency at run time, providing a knob to trade high performance (by setting the frequency to a high level) for improved power and energy consumption (by lowering the  $V_{dd}$  and the frequency) (BURD et al., 2000).

The Alpha-Power Law model provides a good approximation for the expected relationship between  $V_{dd}$ , f, and transistors' power consumption (SAKURAI; NEWTON, 1990). The primary knob in DVFS is  $V_{dd}$ , since it impacts both static and dynamic power consumption. As  $V_{dd}$  is reduced, however, capacitance charge time increase as a result from smaller currents. As a consequence, the circuit must run at a lower frequency (f). The relationship between delay  $T = \frac{1}{f}$  and  $V_{dd}$  can be expressed as

$$T \propto \frac{V_{dd}}{(V_{dd} - V_{th})^{\alpha}}.$$

(2.1)

# Figure 2.11: The DynaSpAM system. (a) Overview.

(b) Reconfigurable fabric.

Source: (LIU et al., 2015).

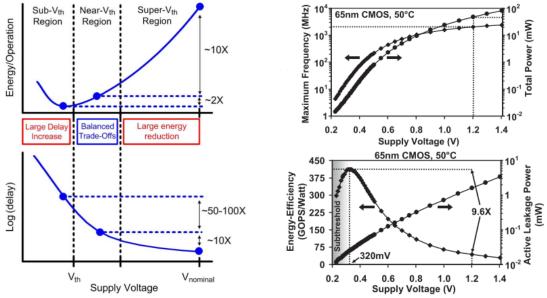

In the equation above,  $\alpha$  is a technology-dependent parameter named *velocity saturation index*, estimated at around 1.9 for current 7nm nodes (GUO et al., 2017), and  $V_{th}$  is the transistor's Threshold Voltage, estimated at about 159 mV for the 7nm FinFET node (PINCKNEY et al., 2017)<sup>2</sup>. This relationship shows that, as  $V_{dd}$  is lowered from the nominal voltage, the frequency initially descreases by only a small amount,  $V_{th}$  is still much smaller than  $V_{dd}$ . However, as  $V_{dd}$  approaches  $V_{th}$ , Eq. 2.1 becomes more sensitive to changes in  $V_{dd}$  and the impact in delay is larger. This effect can be visualized in the lower part of Fig. 2.12.

The result of DVFS is a major, monotonical reduction in static and dynamic power

<sup>&</sup>lt;sup>2</sup>This is only a reference value for the Threshold Voltage ( $V_{th}$ ), since  $V_{th}$  can actually be tuned at design time to balance between static power consumption and performance.

Figure 2.12: Effects of voltage scalability in delay and energy consumption.

Source: To the left, results by Univ. Michigan (DRESLINSKI et al., 2010); to the right, results by Intel (KAUL et al., 2012).

consumption  $(P_S, P_D)$ , since

$$\frac{P_D \propto V_{dd}^2 f}{P_S \propto V_{dd} I_S}$$

(2.2)

In Eq. 2.2,  $I_S$  is the current in the transistor's *source*, which is also a function of  $V_{dd}$ . While power consumption decreases with  $V_{dd}$  and f, however, the energy consumption depends on the ratio between the increase in task delay and the reduction in power consumption, since E = PT (where  $T = \frac{1}{f}$ ). Plugging together the relationships in Eq. 2.1 and Eq. 2.2 yields:

Eq. 2.3 shows that the dynamic energy monotonically decreases as  $V_{dd}$  is lowered, since the dynamic power depends on f. The static energy, however, initially decreases as  $V_{dd}$  is lowered (influence of  $V_{dd}$  and  $I_S$ , with small increase in T) but then presents a tipping point as the task delay increases faster when approaching  $V_{th}$  (large influence of T). Since  $E(V_{dd}) = E_S(V_{dd}) + E_D(V_{dd})$ , there's a value of  $V_{dd}$  that minimizes energy consumption by balancing the increase in static energy with the decrease in dynamic energy, and this tipping point happens exactly where

$$\frac{\partial E_S}{\partial V_{dd}} = -\frac{\partial E_D}{\partial V_{dd}} \tag{2.4}$$

Different works have investigated the operating point (value of  $V_{dd}$ ) where Eq. 2.4 is satisfied and execution can be carried out with minimum energy consumption. This value is technology-dependent, however, and hard to estimate precisely. Nevertheless, some preliminary works estimated it to lie in the transistor's subthreshold region, where  $V_{dd} \leq V_{th}$  (DRESLINSKI et al., 2010; KARPUZCU et al., 2012). More recent studies, on the other hand, estimate it to lie in the near-threshold region, with  $V_{dd}$  slightly higher than  $V_{th}$  (KAUL et al., 2012; KHARE; JAIN, 2013; PINCKNEY et al., 2017). These findings, shown in Fig. 2.12, have sparked interest in NTV computing as a means to address the power wall limitation in modern designs (MITTAL, 2015).

Operation in the NTV region, however, raises several challenges that must be addressed with special design strategies. As a consequence, DVFS in typical processors is restricted to the Super-Threshold Voltage (STV) region, with  $V_{dd}$  set between 70-100% of the nominal voltage (DRESLINSKI et al., 2010). The design challenges of NTV operation, as well as state-of-the-art techniques used to address those challenges, are presented in detail in the next subsections.

#### **2.2.1 Challenges in NTV Operation**

**Performance degradation.** The first issue with NTV computing is the significant performance degradation from the low-frequency operation, with previous works estimating the delay to increase by about  $10 \times$  when moving from STV to NTV (see Fig. 2.12). Modern applications, however, require processing speeds compatible with todays's standards. Therefore, alternative strategies must be used to compensate for that performance loss, otherwise NTV operation must be restricted to the few applications without strong performance requirements.

Scalability differences between logic and memory. As voltage is scaled down, the delay of logic and state-holding elements present different responses. In particular, the delay of memories start to degrate faster, and in practice cannot be lowered below a given limit due to increased error vulnerability (BACHA; TEODORESCU, 2014). As a consequence, memories require redesign for NTV or be strategically placed in a separate voltage islands operating at higher levels.

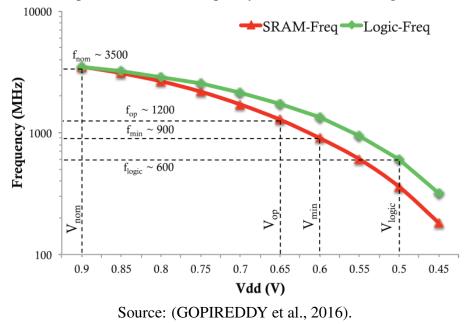

Fig. 2.13 illustrates this effect with experiments carried out in a recent work (GOPIREDDY et al., 2016). It shows how the maximum frequency a logic block and an Static Random-Access Memory (SRAM) block in a processor can run under the ef-

Figure 2.13: Impact in maximum frequency as  $V_{dd}$  is lowered (logic vs memory).

fects of voltage scaling, considering both are designed for a nominal 3500 MHz @ 0.9V (labeled as  $V_{nom}$  in the plot). The SRAM voltage can only be lowered down until 0.6V (labeled as  $V_{min}$ ) as levels below that start affecting the cell's ability to reliably store data. For this voltage level, the memory runs at about 900 MHz; the logic cell can run at the same frequency at a lower voltage level, 0.55V, which, according to equation 2.2, could yield a further 16% reduction in dynamic power consumption given the quadratic relationship with  $V_{dd}$ .

**Increases in process variability.** Process variations affect the transistor parameters non-uniformely across a manufactured processor. These variations result in frequency and power consumption differences among cores in a chip, and are exacerbated when operating in the NTV range. The reason for that is that small deviations in  $V_{th}$  (process variation) affect the ratio  $\frac{V_{dd}}{V_{th}}$  and the difference  $V_{dd} - V_{th}$  more when  $V_{dd}$  is closer to  $V_{th}$ .

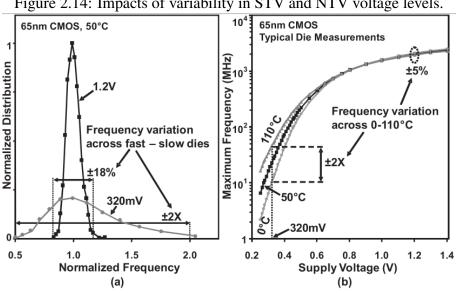

Fig. 2.14 shows this effect precisely. The left plot shows the probability density function for the frequency a core can achieve after manufacturing. The x axis shows the normalized operating frequency and the y axis the probability density of that given frequency. Two curves are shown: one for  $V_{dd} = 1.2$ V (STV) and one for  $V_{dd} = 320$ mV (NTV). In the core designed for 1.2V,  $\sigma = \pm 18\%$ , which means that roughly 70% of all cores will run at a frequency between  $0.82 \times$  and  $1.18 \times$  the target frequency. When the chip is designed for  $V_{dd} = 320$ mV, however,  $\sigma = \pm 2 \times$ , which means that roughly 70% of all cores will run at a frequency between  $0.5 \times$  and  $2 \times$ . As a consequence, the unpredictabnility increases. As mentioned earlier, when  $V_{dd}$  lies closer to  $V_{th}$ , the impacts

Figure 2.14: Impacts of variability in STV and NTV voltage levels.

Source: (KAUL et al., 2012).

of  $V_{th}$  in frequency after manufacturing are exacerbated according to Eq. 2.1.

The right plot in the same figure shows the effects that temperature may have on the chip, since temperature also affects the  $V_{th}$  level. At STV, the difference will be only 5% between a chip operating at 50°C or 0°C. At NTV, however, this difference can also be as high as  $2 \times$ .

VARIUS-NTV is a tool developed to model the microarchitectural variability in an NTV processor (KARPUZCU et al., 2012). It is used by most of the NTV works to predict the delay and power variations within a multi-core die.

## 2.2.2 Solutions for NTV Operation

Increasing performance with dim multi-cores. As discussed in Chapter 1, the scalability of multi-core processors is currently constrained by the power wall. NTV provides a solution to that issue, with nearly-quadritic improvements to power consumption (see Eq. 2.2). As a consequence, an increased number of cores can be simultaneously switched on. This is the key idea introduced by the work of Pinckney et al. (PINCK-NEY et al., 2013): by rewriting an application for parallel execution and running it in a voltage-scaled multi-core operating at NTV, converting *dark silicon* (cores turned off) into *dim silicon* (all cores on, at low voltage/frequency), it is possible to reduce energy consumption by an avergage  $4 \times$  while mantaining the same performance level as in serial execution. A similar analysis considering the impacts of emerging FinFET devices was carried out more recently (PINCKNEY et al., 2017). According to the study, the benefits of NTV in energy consumption (following the same idea of maintaining the performance levels of serial execution) have dropped significantly in the last nodes of planar transistors, but as the switch to FinFET occurred the gains were boosted due to a major decrease in  $V_{th}$  (372mV in the 20nm node and 165mV in the 14nm node). In 7nm, the energy gains from the same setup (dim multicore versus serial execution) are estimated at  $8.2 \times$ .

Most state-of-the-art designs employing NTV use it as a means to reduce the power consumption of each core, enabling more cores to be switched on under the same power envelope. While this approach enables the effective acceleration of parallel work-loads, it is not suitable for single-threaded workloads.

Separating voltage islands inside the core. Work by Zhai et al. proposes operating the pipeline and L1 caches in separate voltage islands, considering the different scalability of  $V_{dd}$  for each structure demonstrated in Fig. 2.13. Caches run at twice the frequency as the cores, and therefore can sustain twice the memory bandwidth while still allowing the core logic to be scaled down to optimal levels (ZHAI et al., 2007).

ScalCore extends the approach not only to pipeline and caches, but also to critical structures inside the pipeline which are typically implemented as SRAM, such as the register file, the instruction queues and the ROB (GOPIREDDY et al., 2016). The key insight is to design a core that can achive voltage-scalability, being able to operate in the NTV range and leverage the benefits without, however, incurring any overheads when operating back in STV.

**Separating voltage islands inside the chip.** A few works have addressed the variability issue by defining multiple voltage and frequency domains in a chip and assigning them values post-manufacturing according to the varability results. Work of Silvano et al. (SILVANO et al., 2014) cites four strategies for this assignment: Single-Voltage Single-Frequency (SVSF), Single-Voltage Multi-Frequency (SVMF), Multi-Voltage Single-Frequency (MVSF), and Multi-Voltage Multi-Frequency (MVMF). SVSF is the simplest and most conservative approach, which assigns the same voltage and frequency to all cores and structures in a die. While the strategy is sufficient for an STV processor, considering the low variability, it would result in over-pessimistic assumptions for the maximum frequency considering the high variability in NTV. On the other hand, the Multi-Voltage or Multi-Frequency approaches are more flexible, but require the use of special components to interface between different domains, and the use of special techniques for determining the optimal voltage and frequency assignments for each domain.

In the same work, an MVSF strategy for sustaining performance from STV levels while computing at NTV (with higher number of cores, while still reducing the energy consumption) is used for this assignment: first, the lowest-required frequency for sustaining STV performance is computed, and then the voltage domains for achieving that frequency are allocated. The result is a frequency-homogeneous multi-core. A MVMF extention to this scheme, which results in a heterogeneous multi-core and can be particular efficient in applications with workload disbalance among threads is also presented (SILVANO et al., 2014).

Kaul et al. propose a simpler approach, suitable for many-core sytems (KAUL et al., 2012). The authors argue for a simple SVMF strategy where the nearest-possible operation frequency is assigned to each core. Then, according to the Law of Large Numbers, the overall throughput of the system should not be affected.

EnergySmart takes a similar, SVMF approach, arguing for the inneficiency of MVbased schemes due to the high amount of area and low energy efficiency of on-chip voltage regulators (KARPUZCU et al., 2013). The proposed strategy is also coupled to a scheduling algorithm assigns tasks to the performance-heterogeneous cores to maximize performance per watt.

Kiamehr et al. propose a temperature-aware voltage scaling approach, showing that ambient temperature information (which is typically very close to circuit temperature, when operating at NTV) can be leveraged to better tune the optimal  $V_{dd}$  level and reduce energy consumption compared to temperature-unaware schemes (KIAMEHR et al., 2017).

## 2.3 Approximate Computing

Approximate computing is a design paradigm that enables trade-offs in the quality of an application's results for improvements in other metrics such as performance or energy consumption. It is based on the observation that many modern application domains, such as computer vision, gaming, machine learning, data mining, dynamic simulations and data mining present a *forgiving nature* (i.e., they can tolerate controlled deviations in the output without compromising the functionality) due to at least one of the following characteristics (CHAKRADHAR; RAGHUNATHAN, 2010):

• Noisy inputs: Real-world data is, by nature, noisy due to measurement errors. Any

application processing noisy data has already introduced some degree of error in the output and, therefore, can tolerate approximation in its computations.

- Large, redundant data-sets: Some applications process large amounts of data with significant similarity between input elements, for instance image/video processing and machine-learning applications. In such scenarios, approximation can be used to remove this redundancy with only small impact in the quality.

- No perfect result: Heuristics, which are a form of approximating a computation, are often used when solving complex problems for which an exact solution is either unavailable or computationally intractable. Other approximation techniques may also be applied in such scenarios.

- Limited perceptual ability of users: In many cases, a *good-enough* application result is sufficient because the user would not be able to notice any difference between that and the *precise* result. Many lossy-compression algorithms are based on this idea ((ESR), 2011).

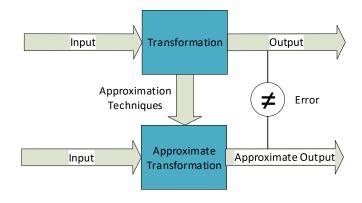

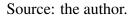

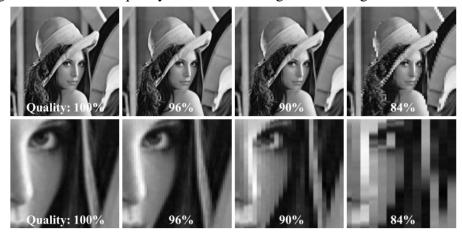

The observation above raises an opportunity to exploit these common characteristics as a design paradigm to enable performance or energy improvements. Fig. 2.15 shows an overview of the Approximate Computing paradigm. Given the abstract notion of an algorithm, which is a transformation from inputs into outputs, implemented either as software or hardware, approximate computing consists of finding an approximate, more efficient version of the same implementation by using approximation techniques. The approximate transformation produces an approximate output which can be compared with the precise one, and an error measurement can be established. An important assumption in approximate computing is that the output of the approximate transformation must contain only *small deviations* from the precise one. In this sense, approximation techniques that can cause the system to abruptly crash or change the *structure of the output* (i.e. change the number of output elements, or the output encoding) are still considered unacceptable.

Considering the above discussion, this work uses a terminology similar to the one defined in a previous work to classify when an approximation technique produces acceptable results or not (REHMAN; SHAFIQUE; HENKEL, 2012). An application output falls into one of the three categories:

- precise output : the output produced by the precise program.

- **approximate output**: an output that is incorrect, but acceptable as an approximation of the correct one. The *structure* of the output is preserved (e.g. if the precise

Figure 2.15: Overview of the approximate computing paradigm.

output is an image, the approximate output must also be an image of the same size) and an error metric can be computed.

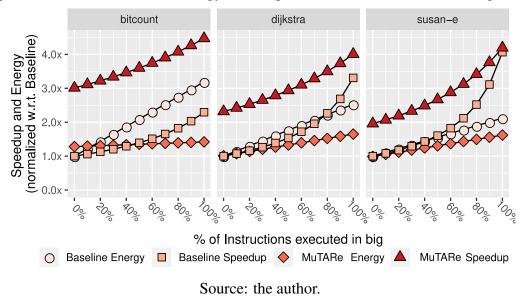

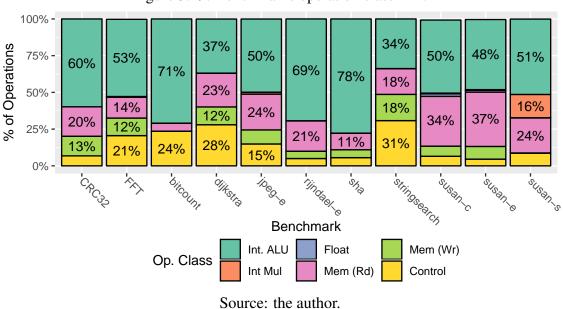

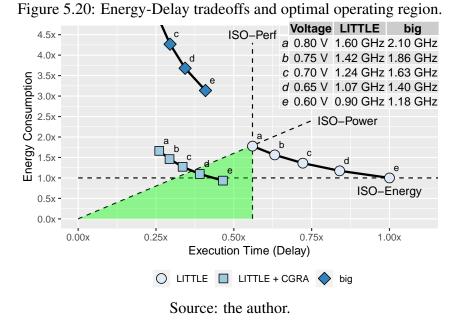

• **invalid output** : this is an output that is incorrect and unacceptable as an approximation. This is the case when the application terminates abruptly, crashes, produces an output without the correct *structure* or does not produce any output at all.