# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

## CHARLES CARDOSO DE OLIVEIRA

# Odin: Online, Non-Intrusive and Self-Tuning DCT and DVFS to Optimize OpenMP Applications

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Advisor: Prof. Dr. Antonio Carlos S. Beck

#### CIP — CATALOGING-IN-PUBLICATION

Oliveira, Charles Cardoso de

Odin: Online, Non-Intrusive and Self-Tuning DCT and DVFS to Optimize OpenMP Applications / Charles Cardoso de Oliveira. – Porto Alegre: PPGC da UFRGS, 2019.

92 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2019. Advisor: Antonio Carlos S. Beck.

1. Thread-level parallelism exploitation. 2. DVFS. 3. OpenMP. 4. Energy and performance optimization. 5. Runtime environments. I. Beck, Antonio Carlos S.. II. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof. João Luiz Dihl Comba

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Primeiramente, agradeço a Deus por me ajudar a superar as dificuldades durante o desenvolvimento deste trabalho. Agradeço também ao apoio recebido pela família.

Agradeço ao professor Antonio Carlos Schneider Beck Filho pela orientação durante todo o mestrado. Agradeço ao Arthur Francisco Lorenzon e a Janaína Schwarzrock, por compartilharem da sua experiência na área para o desenvolvimento do trabalho.

Ao professor Luigi Carro, por suas ótimas aulas ministradas que contribuíram bastante para minha evolução na área. Ao professor Marcus Ritt, que auxiliou no desenvolvimento da técnica principal deste trabalho.

Finalmente, aos colegas de laboratório que sempre estiveram à disposição para esclarecer qualquer dúvida que surgisse.

#### **ABSTRACT**

Modern applications have pushed multithreaded processing to another level of performance and energy requirements. However, in most cases using the maximum number of available cores running at the highest possible operating frequency will not deliver the best Energy-Delay Product (EDP), since there are many aspects that prevent linear improvements when exploiting them. Moreover, the many parallel regions that compose an application may vary in behavior depending on characteristics that can be only known at run-time: input set, microarchitecture, and number of available cores. To solve this problem, we propose Odin: an online and lightweight self-tuning approach that optimizes OpenMP applications for EDP. While its dynamic nature makes it capable of adapting to the changing environment, it is totally transparent to both designer and end-user. Therefore, Odin does not need any source or binary code modifications, so potentially any dynamically linked parallel OpenMP executable file can be optimized with zero effort. By implementing different online strategies, we show that Odin can transparently improve EDP, on average, in 37.6% when compared to the regular OpenMP execution with DVFS set to ondemand. Additionally, we implement an alternative offline approach that uses a genetic algorithm for optimizing the parallel applications, showing that Odin can achieve similar results to it. Finally, we evaluate Odin's learning overhead and solution quality by comparing it to an exhaustive local search, which is the optimal configuration for each parallel region.

**Keywords:** Thread-level parallelism exploitation. DVFS. OpenMP. energy and performance optimization. runtime environments.

# Odin: DCT e DVFS Online, Não-Intrusivo e Auto-Ajustável para otimizar aplicações OpenMP

## **RESUMO**

Aplicações modernas têm levado o processamento paralelo a outro nível de requisitos em desempenho e energia. Entretanto, na maioria dos casos, usar o número máximo de núcleos disponíveis executando na maior frequência possível não oferecerá o melhor Energy-Delay Product (EDP), pois existem vários aspectos que impedem melhorias lineares ao explorá-los. Além disso, as várias regiões paralelas que compõem uma aplicação podem variar em comportamento dependendo de características que podem ser conhecidas apenas em tempo de execução: conjunto de entradas, microarquitetura e número de núcleos disponíveis. Para resolver esse problema, propomos Odin: uma abordagem de autoajuste online e leve que otimiza as aplicações OpenMP para EDP. Enquanto sua natureza dinâmica torna-o capaz de adaptar-se em um ambiente variante, ele também é totalmente transparente para ambos desenvolvedor e usuário final. Portanto, Odin não necessita de nenhuma modificação em código-fonte ou binário, logo potencialmente qualquer arquivo executável OpenMP que seja ligado dinamicamente pode ser otimizado sem nenhum esforço. Ao implementar diferentes estratégias online, nós mostramos que Odin pode de forma transparente melhorar o EDP, em média, em 37.6% quando comparado ao método regular de execução OpenMP com o DVFS configurado para ondemand. Adicionalmente, nós implementamos uma abordagem alternativa offline que usa um algoritmo genético para otimizar as aplicações paralelas, mostrando que Odin pode alcançar resultados similares a ela. Finalmente, nós avaliamos o custo de aprendizado e qualidade da solução de Odin comparando-o com uma busca local exaustiva, que é a configuração ótima para cada região paralela.

**Palavras-chave:** Exploração de paralelismo em nível de threads, DVFS, OpenMP, otimização de desempenho e energia, ambientes em tempo de execução.

# LIST OF ABBREVIATIONS AND ACRONYMS

CMOS Complementary Metal-Oxide-Semiconductor

DCT Dynamic Concurrency Throttling

DVFS Dynamic Voltage and Frequency Scaling

EDP Energy-Delay Product

HPC High-Performance Computing

ILP Instruction-Level Parallelism

IoT Internet of Things

MPI Message Passing Interface

NUMA Non-Uniform Memory Access

RAPL Running Average Power Limit

SMT Simultaneous Multithreading

TLB Translation Lookaside Buffer

TLP Thread-Level Parallelism

# LIST OF FIGURES

| Figure 1.1 The evolution of the power consumption based on the top 10 HPC sys-                 |     |

|------------------------------------------------------------------------------------------------|-----|

| tems of the Top500 list.                                                                       | 18  |

|                                                                                                |     |

| Figure 2.1 Example of DVFS levels                                                              | 25  |

| Figure 2.2 Example of parallel program using OpenMP.                                           | 28  |

| Figure 2.3 Issue-width saturation                                                              |     |

| Figure 2.4 Off-chip bus saturation                                                             |     |

| Figure 2.5 Data-synchronization saturation                                                     |     |

| Figure 2.6 Impact of the number of threads on the performance and energy                       |     |

| Figure 2.7 Impact of the frequency on the execution time                                       | 33  |

| Figure 5.1 The operators of the Genetic Algorithm                                              | 49  |

| Figure 5.2 Representation of the chromosome used in the algorithm.                             |     |

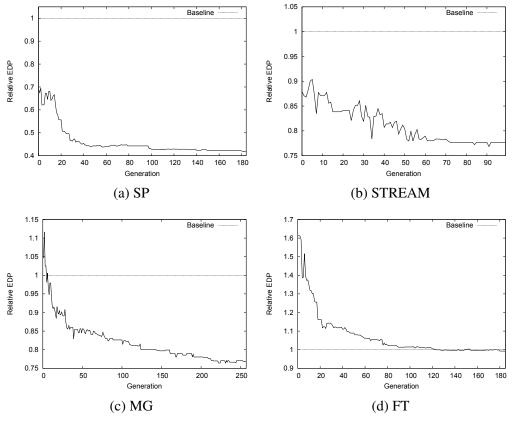

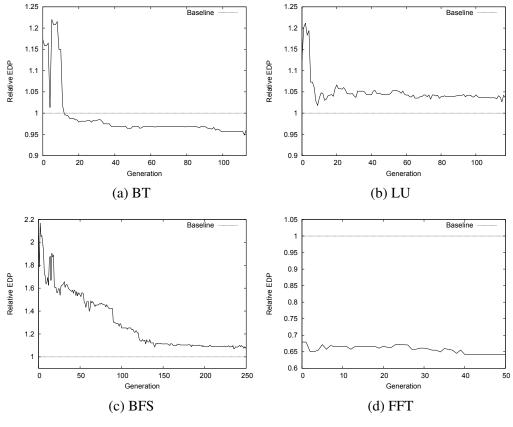

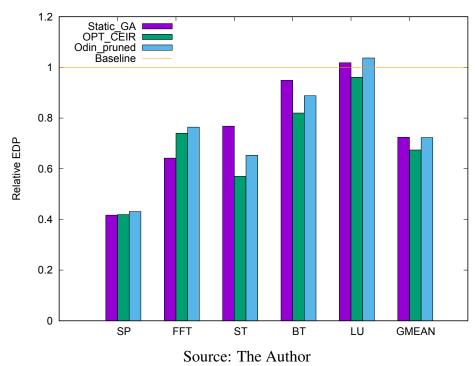

| Figure 5.3 The GA results from each benchmark normalized to the baseline EDP                   |     |

| Figure 5.4 The GA results from each benchmark normalized to the baseline EDP                   |     |

| Figure 5.5 Best results found by our algorithm for each benchmark and the geo-                 |     |

| metric mean (GMEAN) normalized to the baseline EDP.                                            | 58  |

|                                                                                                |     |

| Figure 6.1 Example of Fibonacci algorithm pruning the search space                             | 64  |

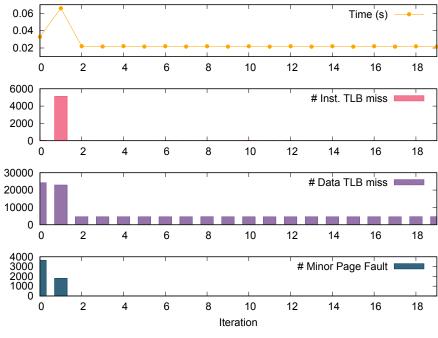

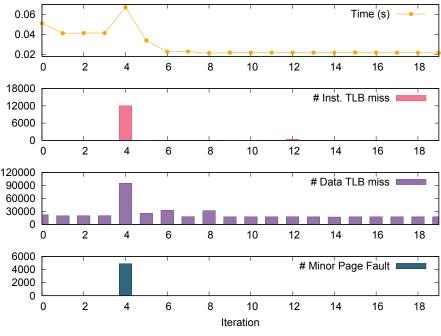

| Figure 6.2 The impact of the virtual memory events on the execution time of the                |     |

| JA benchmark (32 Threads).                                                                     | 66  |

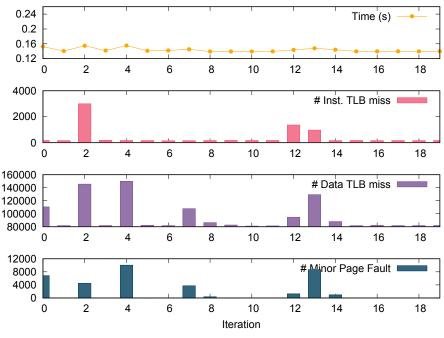

| Figure 6.3 The impact of the virtual memory events on the execution time of the                |     |

| SP benchmark (16 Threads)                                                                      | 67  |

| Figure 6.4 The impact of the virtual memory events on the execution time of the                | 60  |

| SP benchmark (32 to 16 threads).                                                               |     |

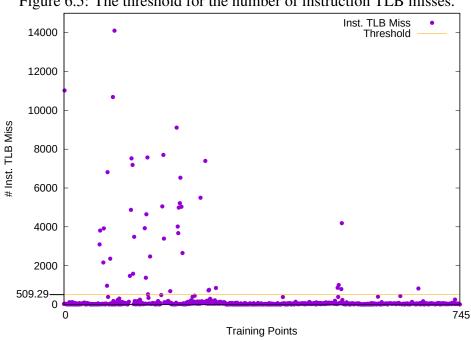

| Figure 6.5 The threshold for the number of instruction TLB misses                              |     |

| Figure 6.6 OpenMP static scheduler assigning block of iterations to each thread                |     |

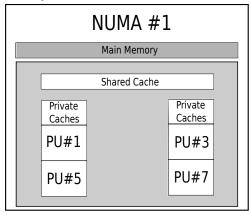

| Figure 6.7 Example of a NUMA system with two nodes.                                            | /0  |

| Figure 6.8 Example of OpenMP scheduling on top of a NUMA system with two                       | 70  |

| nodes.                                                                                         |     |

| Figure 6.9 Example of memory locality noise in the ST benchmark                                | / 1 |

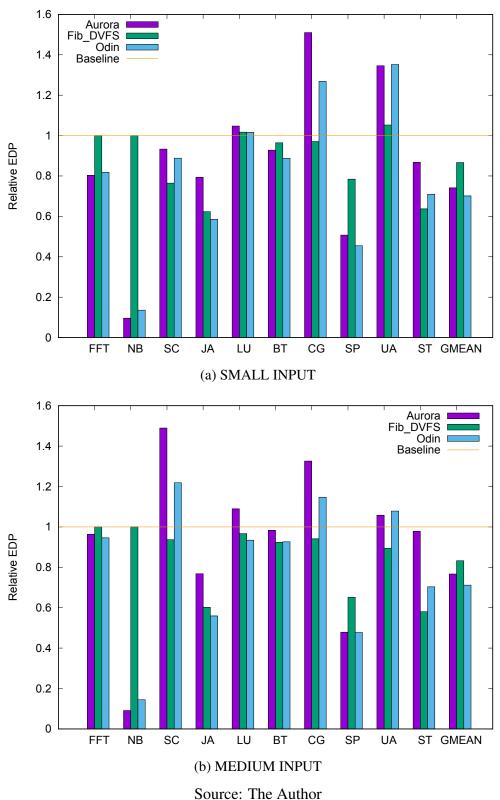

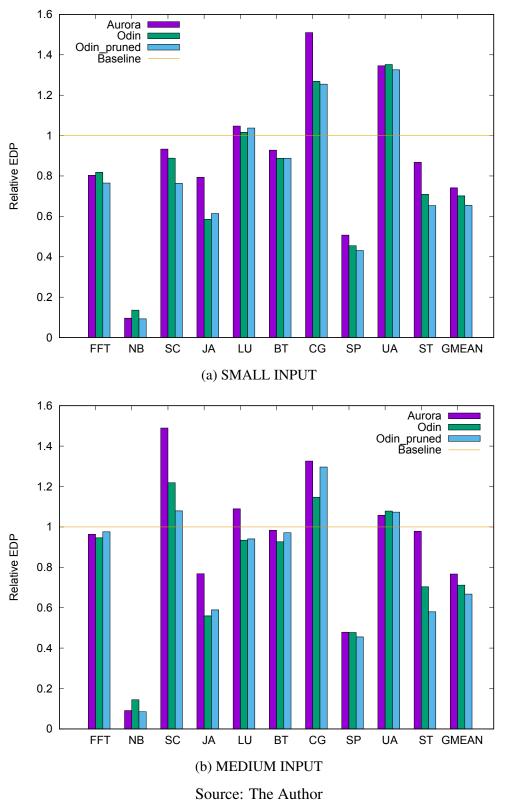

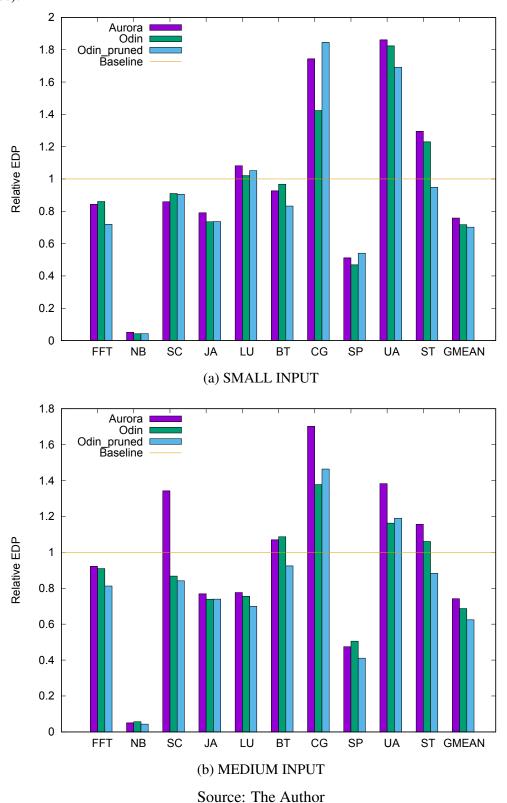

| Figure 6.10 The results from each benchmark normalized to the baseline EDP (24 logical cores). | 77  |

| Figure 6.11 The results from each benchmark normalized to the baseline EDP (32)                | / / |

| logical cores)                                                                                 | 78  |

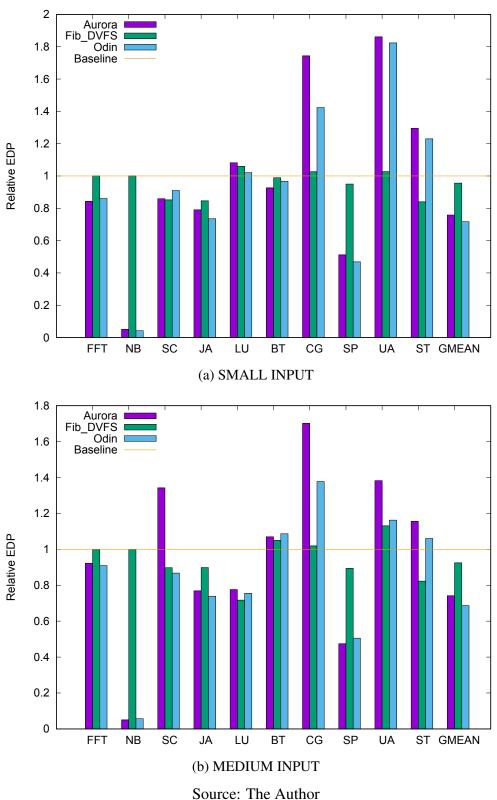

| Figure 6.12 The results from each benchmark normalized to the baseline EDP (24                 | / 0 |

| logical cores)                                                                                 | 81  |

| Figure 6.13 The results from each benchmark normalized to the baseline EDP (32)                | 01  |

| logical cores).                                                                                | 82  |

| Figure 6.14 The results for Dynamic and Static strategies normalized to the base-              | 02  |

| line EDP.                                                                                      | 83  |

|                                                                                                |     |

| Figure A.1 The results from each benchmark normalized to the baseline EDP (24                  |     |

| logical cores).                                                                                | 92  |

| Figure A.2 The results from each benchmark normalized to the baseline EDP (32                  |     |

| logical cores)                                                                                 | 92  |

# LIST OF TABLES

| Table 3.1 Comparison of Odin with the related work                                                                   | 42 |

|----------------------------------------------------------------------------------------------------------------------|----|

| Table 5.1 Main characteristics of the system                                                                         |    |

| Table 5.2 Best pair of the number of threads and CPU frequency level (MHz) found by our GA for each parallel region. | 57 |

| Table 6.1 Main characteristics of the systems                                                                        | 74 |

| Table 6.2 Learning time (%) of each benchmark for the online strategies – 24 cores system                            | 75 |

| Table 6.3 Learning time (%) of each benchmark for the online strategies – 32 cores                                   |    |

| system                                                                                                               | 13 |

# **CONTENTS**

| 1 INTRODUCTION                                                               | 17                   |

|------------------------------------------------------------------------------|----------------------|

| 1.1 Scalability and Variables Involved                                       |                      |

| 1.2 Contributions                                                            |                      |

| 1.3 Organization of this Dissertation                                        |                      |

| 2 FUNDAMENTAL CONCEPTS                                                       |                      |

| 2.1 Energy and Power Consumption                                             |                      |

| 2.1.1 Dynamic Power                                                          |                      |

| 2.1.2 Static Power                                                           |                      |

| 2.1.3 Energy-Delay Product                                                   |                      |

| 2.1.4 Dynamic Voltage and Frequency Scaling for Power Management             | 2 <del>.</del><br>25 |

| 2.2 Parallel Programming                                                     |                      |

| 2.2.1 OpenMP                                                                 |                      |

| 2.3 Scalability of Parallel Applications                                     |                      |

|                                                                              |                      |

| 2.3.1 Number of Threads                                                      |                      |

| 2.3.2 CPU Frequency                                                          |                      |

| 3 RELATED WORK                                                               |                      |

| 3.1 Adaptation of the Number of Threads                                      |                      |

| 3.2 CPU Frequency Level                                                      |                      |

| 3.3 CPU Frequency Level and Number of Threads                                |                      |

| 3.4 Our Contributions                                                        |                      |

| 4 PROBLEM DEFINITION AND SEARCH STRATEGIES                                   |                      |

| 4.1 Problem Definition                                                       | 45                   |

| 4.2 Search Strategies                                                        | 46                   |

| 4.2.1 Offline Strategies                                                     | 46                   |

| 4.2.1.1 Optimal configuration for each individual region (OPT_CEIR)          | 46                   |

| 4.2.1.2 Genetic Algorithm – Globally Near Optimal Configurations (Static_GA) | 46                   |

| 4.2.2 Online Strategies                                                      |                      |

| 4.2.2.1 Only DCT (Aurora)                                                    |                      |

| 4.2.2.2 Odin – DCT + DVFS using Fibonacci Search (Odin)                      |                      |

| 5 GENETIC ALGORITHM                                                          |                      |

| 5.1 Background                                                               |                      |

| 5.2 Our approach                                                             |                      |

| 5.3 Implementation                                                           |                      |

| 5.4 Methodology                                                              |                      |

| 5.4.1 Benchmarks                                                             |                      |

| 5.4.2 Execution Environment.                                                 |                      |

| 5.5 Experimental Results                                                     |                      |

| •                                                                            |                      |

| 5.6 Discussion                                                               | 58                   |

|                                                                              | <b>5</b> 0           |

| TO OPTIMIZE OPENMP APPLICATIONS                                              |                      |

| 6.1 Odin Integration to OpenMP                                               |                      |

| 6.2 Optimization Strategy                                                    |                      |

| 6.2.1 The search algorithm                                                   |                      |

| 6.3 Sample Selection                                                         |                      |

| 6.3.1 Virtual Memory                                                         |                      |

| 6.3.2 Memory Locality                                                        |                      |

| 6.4 Methodology                                                              |                      |

| 6.4.1 Benchmarks                                                             | 72                   |

| 6.4.2 Execution Environment                                  | 73 |

|--------------------------------------------------------------|----|

| 6.5 Experimental Results                                     | 74 |

| 6.5.1 Online Learning Overhead                               |    |

| 6.5.2 EDP Comparison                                         | 76 |

| 6.5.2.1 Strategies using only one knob vs Odin               | 76 |

| 6.5.2.2 Odin pruned                                          | 80 |

| 6.5.2.3 Dynamic x Static strategies                          | 80 |

| 7 FINAL CONSIDERATIONS                                       | 85 |

| 7.1 Future Work                                              | 86 |

| REFERENCES                                                   | 87 |

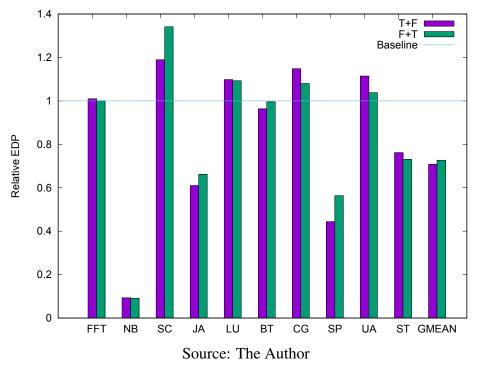

| APPENDIX A — OTHER STRATEGIES                                | 91 |

| A.1 Description: #Threads+DVFS (T+F) and DVFS+#Threads (F+T) | 91 |

| A.2 Results                                                  |    |

#### 1 INTRODUCTION

Demands for High-Performance Computing (HPC) systems have been growing due to technologies such as Cloud Computing, which has emerged as an essential computing paradigm, enabling ubiquitous and convenient on-demand access through the Internet to systems having configurable computing resources (KOBUSIŃSKA et al., 2018). Also, another notable technology trend that nowadays is gaining increasing attention is the Internet of Things (IoT). In IoT, intelligent embedded devices and sensors are interconnected in a dynamic and global network infrastructure (KOBUSIŃSKA et al., 2018). Besides that, devices such as smartphones and tablets complement this large embedded systems market.

For both fields, HPC and embedded devices, there are new applications that compute huge amounts of data, such as machine learning, smarter search mechanisms, big data in general, biomedical, and video and audio recognition, which have been pushing multithreaded processing to another level of performance requirements. However, power consumption is directly proportional to this increasing availability of data to compute.

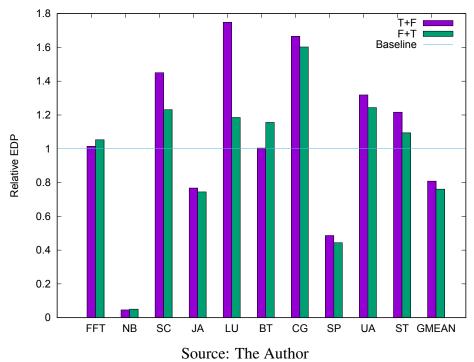

Figure 1.1 shows the evolution of the power consumption (mean and maximum values) for the top 10 HPC systems in the last ten years based on the Top500 list (TOP500, 2019). As one can observe, on average, the power consumption had an increase of almost six times, while the system presenting the highest consumption grows up approximately eight times – exceeding the 18 MW mark – in the last decade. Therefore, the HPC systems are more likely to spend more funds on energy and cooling systems – as heating will increase from this large power dissipation – to maintain the services running. On top of that, a lot of current embedded systems are rapidly increasing in complexity, and hence, consuming more power. Since these systems are dependent on batteries, this rising complexity will decrease their battery lifetime.

Considering this scenario, the traditional way of executing parallel applications is using the maximum number of hardware threads available on the system at the maximum frequency or under the responsibility of the Operating System, which changes the frequency based on the CPU load. However, this conventional approach (i.e., the maximum number of threads and CPU frequency) does not always deliver the best performance and energy results. Therefore, this work uses two techniques for improving the outcome in performance and energy (expressed by Energy-Delay product, or EDP) of parallel applications: (i) **Dynamic Concurrency Throttling (DCT)**, which allows for changing the

Figure 1.1: The evolution of the power consumption based on the top 10 HPC systems of the Top500 list.

Source: The Author

number of threads of a parallel application at run-time; (*ii*) **Dynamic Voltage and Frequency Scaling (DVFS)** that dynamically adjusts the operating voltage and frequency of the CPU.

However, most applications are already deployed, which means that in many times the source code is not available for instrumentation and recompilation. Intel/ARM instruction set architectures (ISAs) have been showing that binary compatibility is mandatory, so one can reuse legacy code and maintain traditional programming paradigms and libraries. Hence, software transparency, which allows to optimize the target application without the need for recompiling it, plays a decisive role in the large adoption of any new solution. Thus, we implement our framework to be transparent, targeting the applications parallelized with OpenMP, which is a popular parallel programming interface.

#### 1.1 Scalability and Variables Involved

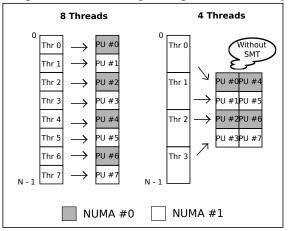

As previously stated, not always the maximum number of available logical cores executing threads will provide the best outcome in energy and performance (represented by EDP), because many aspects prevent linear improvements as one increases the number of threads. Consider, for example, the Simultaneous Multithreading (SMT) technology, which permits more than one thread allocated to one physical core. The threads competing

for processor resources may cause a contention that degrades the overall performance (RAASCH; REINHARDT, 2003). Besides that, some applications make many memory requests and, as the off-chip bus has a limited bandwidth, the memory system can saturate as we increase the concurrency level (JOAO et al., 2012). Finally, a group of threads generally requires a synchronization point, which is a phase for data exchange that permits only one thread executing at the time, so increasing the number of threads may result in loss of benefits achieved in the parallel region (SULEMAN; QURESHI; PATT, 2008). We discuss in details each of these problems later.

Moreover, the current operating systems embed tools for power management, such as DVFS, which adapts the operating frequency and voltage at run-time according to the application at hand and has also been extensively exploited to improve energy (COCHRAN et al., 2011; LI; MARTINEZ, 2006; SENSI, 2016). A DVFS system takes advantage of the processor idleness (usually provoked by I/O operations or by memory requests) to achieve cubic power reduction, since voltage has quadratic influence in dynamic power. However, in the same way as the level of concurrency exploitation, using the maximum possible operating frequency will not always result in the highest EDP improvements, although it will very likely deliver the best performance. In this context, it is only natural to imagine that one may improve the EDP of a parallel application by tuning DCT and DVFS.

Besides that, one must also consider that parallel applications may comprise many parallel regions with different behaviors. Each of these regions may have an optimal number of threads that will deliver the best result in terms of performance or energy. Moreover, other aspects, such as the kind of executed instructions and amount of shared data may impact DVFS. Thus, considering that the system has  $\mathbf{C}$  cores,  $\mathbf{L}$  voltage/frequency levels, and  $\mathbf{P}$  parallel regions for each program, we have  $(C \times L)^P$  possibilities considering the global configuration targeting a specific non-functional requirement. Given the huge amount of possible solutions, this exponential behavior easily becomes impractical for an exhaustive search.

Based on this discussion, we can state two essential characteristics for optimizing parallel applications:

• Adaptability: related to the ability to adapt itself according to the application with respect to parameters that are known only at run-time, such as the number of available cores, system microarchitecture, and the input-set. In such cases, offline solutions will not suffice, since when the environment changes, the offline analysis

must be re-executed. In Chapter 5, we show a framework using a genetic algorithm that although the positive results, presents this limitation.

• Transparency: the lack of transparency comes from the necessity of transforming code, which can be manual or automatic (by using special languages or toolchains). This implies modifications in the source or binary codes, or requires the use of an Application Programming Interface (API) that is not conventional or widely used. However, as said before, many applications are already deployed, which means that in many times the source code is not available for instrumentation and recompilation. Most importantly, code annotation also involves the user, since it must analyze the source code and have particular knowledge of the application that must be optimized. Therefore, this task could only be performed by experienced programmers with full access to the code.

Finally, there are many solutions for DCT without DVFS and vice versa, but only a few that consider both. However, although some of them present adaptability, all of them lack software transparency.

#### 1.2 Contributions

This dissertation makes the following contribution:

• Odin: a tool capable of automatically tuning, at run-time, the number of threads and DVFS for each parallel region of any OpenMP application. Because of its dynamic adaptability, Odin covers all cases discussed previously: it deals with the intrinsic characteristics of the application, the particularities of each parallel region, and can automatically adapt according to the microarchitecture, the number of available cores and the current input set, converging to either an optimal or a near optimal solution, and resulting in significant EDP gains. Odin was built on top of the original OpenMP library, it is completely transparent to both designer and end-user: given an OpenMP application binary, Odin runs on it without any code changes.

As a secondary contribution of this work, we also developed another framework to search for the optimal number of threads and CPU frequency level to execute each parallel region and that works at static time (prior execution). It is also automatic and transparent and built on top of the original OpenMP library. It implements an optimization algorithm based on a genetic algorithm that optimizes the entire application EDP. As an advantage,

this framework can search in a broader space of exploration because of its static essence. It also presents no costs w.r.t. to the learning overhead at runtime. For that, it has more opportunities to find near optimal solutions. On the other hand, it cannot benefit from many aspects that only dynamic strategies are offered.

## 1.3 Organization of this Dissertation

Chapter 2 depicts the theoretical concepts necessary to understand this dissertation. Firstly, we show notions of energy and power consumption. Then, how one can use the DVFS – a dynamic power management technique – to reduce the power consumed by a circuit. After that, we demonstrate a notion of parallel programming and how it works on the OpenMP framework. Finally, we study the scalability of parallel applications when applying DCT and DVFS.

Chapter 3 discusses the related work. We divide the chapter into three sections. First, we present those works that focus only on the optimization of the number of threads. Second, we show the researches that use only DVFS for optimization. Finally, we show studies that use both techniques to optimize parallel applications. Besides that, we highlight our contributions compared to the related work.

Chapter 4 shows the formal definition of the problem of optimizing parallel applications. Besides that, we give a short description of each algorithm that we use for our results comparison, which we divide between offline and online strategies.

Chapter 5 presents an alternative method, at static time, using a genetic algorithm to optimize parallel applications applying DVFS and DCT. First, we give the necessary background to understand the genetic algorithms, such as the main elements and operators. After, we show how we adapt it to our problem and the implementation bound to OpenMP. Finally, we show results comparing our tool to the usual way of executing parallel applications.

Chapter 6 presents the main contribution of this dissertation: Odin. Odin is a tool capable of automatically tuning the DCT and DVFS of an OpenMP application at run-time maintaining the software transparency. Besides that, we compare it to other techniques such as the framework using the genetic algorithm.

Chapter 7 presents the final considerations of this dissertation. It also discusses some points of improvement to our approach and promising future works.

#### **2 FUNDAMENTAL CONCEPTS**

This chapter presents the theoretical concepts necessary to understand the remainder of this work. First, we show the definition of energy and how it is related to power and time. Also, we explain what are the dynamic and static power consumption in an integrated circuit. Then, we introduce the Energy-Delay Product (EDP) metric, a formula that unifies performance and energy in a unique value. Secondly, the theory about parallel programming, models for exchange information between threads or processes, and the OpenMP interface. Finally, we dedicate a section to show how parallel application scales for both the number of threads and CPU frequency level.

## 2.1 Energy and Power Consumption

As mentioned in Chapter 1, the power consumption of the systems, both HPC and embedded devices, is growing up. Hence, it may imply more energy spent as can be seen in Equation 2.1 that gives the energy, in joules, consumed by a circuit.

$$Energy = \int P(t) \times dt \tag{2.1}$$

In Equation 2.1, P(t) is the power consumed at the instant of time t that is accumulated during a time interval. The **static** and **dynamic** power are the primary sources of power consumption in a Complementary Metal-Oxide-Semiconductor (CMOS) integrated circuit (KAXIRAS; MARTONOSI, 2008). We discuss each of them in the following subsections.

# 2.1.1 Dynamic Power

The power consumed mainly by the charge and discharge of the load capacitance when transistors switch is defined as dynamic power and given by Equation 2.2.

$$P_{dynamic} = C \times V^2 \times A \times f \tag{2.2}$$

Capacitance (C): shortly, aggregate the load capacitance and depends on both the capacitance of its transistors and the capacitance of its wires. Thus, the circuit designer

has a high influence on this component. For example, making smaller processor cores on-chip instead of a big one monolithic processor is likely to reduce wire lengths considerably, since most wires will interconnect units within a single core.

Supply Voltage (V): the main power source of the integrated circuit. Because of its quadratic influence on dynamic power, this presents excellent opportunities for power-aware design.

Activity Factor (*A*): the activity factor is a fraction between 0 and 1 that refers to how often wires transition from *high* to *low* and *low* to *high*. The clock signal, for example, has the activity factor of 1 as it is always switching between *low* and *high*.

Clock Frequency (f): has a direct impact on dynamic power. Besides that, the clock frequency maintains influence on the supply voltage because higher frequencies may require a higher supply voltage to the correct operation of the circuit. Therefore, combined with supply voltage it has a cubic impact on power consumption.

#### 2.1.2 Static Power

Dynamic power dissipation still represents the predominant factor in CMOS power consumption, but leakage energy has been increasingly prominent in recent technologies. Static power consumption is due to the imperfect essence of transistors that permits leakage currents (Equation 2.3). Thus, the integrated circuit is always consuming power even when it is not switching (KAXIRAS; MARTONOSI, 2008).

$$P_{static} = V \times I_{leak} \tag{2.3}$$

In Equation 2.3, V is the supply voltage and  $I_{leak}$  is the leakage current.

#### 2.1.3 Energy-Delay Product

At the same time that users want to maximize the performance of their applications, there are demands to reduce energy consumption. Embedded systems, for example, benefit from this by increasing the battery lifetime. While one can use DCT to optimize performance and energy in parallel applications, the DVFS aims to reduce power consumption and possibly decrease the energy spent – as energy depends on the execution time, this is not always achievable. Furthermore, to reach the maximum performance

using DVFS, we need to hold the frequency on the maximum level.

Thus, to optimize energy without a high degrading of the performance and vice versa, we use the Energy-Delay Product (EDP) as a metric for our work. The EDP is a metric that unifies energy and performance (delay) in a unique value as shown in equation 2.4 (GONZALEZ; HOROWITZ, 1996). Therefore, this metric transforms a multi-objective problem in a single objective form, helping the optimization procedure. Also, there are other metrics such as  $ED^2P$ , which give to performance more influence. Our tool can use it with minimal effort, but we focus our results only for EDP.

$$EDP = energy \times delay \tag{2.4}$$

## 2.1.4 Dynamic Voltage and Frequency Scaling for Power Management

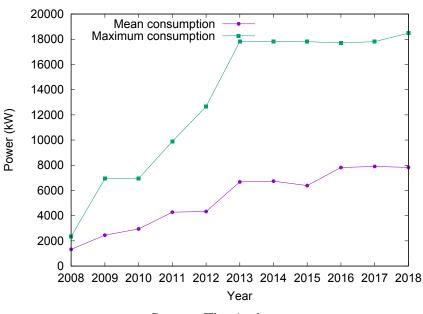

Dynamic voltage and frequency scaling is a widely used technique for reducing power/energy consumption. The frequency at which the circuit operates determines the voltage required for stable operation, so decreasing it we can also reduce the voltage. Figure 2.1 depicts an example of a DVFS system that a processor can use, where each point refers to an operating pair of voltage/frequency and the reduction of power consumption. Thus, a DVFS system can take advantage of the processor idleness to achieve cubic dynamic power reduction, since voltage has quadratic influence in dynamic power as shown in Equation 2.2, without performance impact.

According to Kaxiras and Martonosi (2008), there are three major levels of processor slackness in which DVFS decisions can be made:

- System-level based on system slack: at this level, the idleness of the whole system

determines the DVFS choices. In many cases, it considers the use of the CPU load

to make subsequent decisions, as the Linux Operating System does through the

ondemand governor (PALLIPADI; STARIKOVSKIY, 2006).

- Program- or program-phase-level based on instruction slack: the decisions are based on program phases behavior, for example, a DVFS system can exploit phases that present long-latency memory operations.

- 3. Hardware-level based on hardware slack: finally, there is an approach that goes below the program level, right to the hardware. It tries to exploit slack hidden in hardware operation.

In this dissertation, we focus on the program phase granularity (level 2), in which we choose a DVFS setting for each parallel region of the application, aiming for the EDP optimization of the entire execution. Therefore, we consider the exploitation of operating frequencies in a lower granularity than the approach using DVFS decisions level 1 without hardware modification (level 3), thus being possible to implement on most current processors.

Besides, although our system has the possibility of changing the frequency level for each physical core individually, in this work we are considering the frequency switching for the entire package. Considering that we need a system call (syscall) to change the CPU operating frequency at the application level for each core, which is an expensive task, we also implemented a special governor using a kernel module to reduce the overhead for the frequency switching process. It comprises a single syscall that changes the operating frequency of the whole package. With the module, we have diminished the cost from about 1 ms to approximately  $100~\mu s$  for each frequency changing (considering a processor with 24 cores). The user can insert or remove the governor dynamically on Linux, with no need to recompile the kernel. Therefore, the transparency for the application to be optimized is maintained.

## 2.2 Parallel Programming

Parallel programming is the process of dividing a set of tasks to be executed concurrently and, therefore, reducing the execution time of an application. It focuses on exploiting Thread-Level Parallelism (TLP) that is a high-level alternative way to exploit parallelism, in contrast with Instruction-Level Parallelism (ILP) that has significant limitations for some applications (JOUPPI; WALL, 1989).

The popularization of multicores in both desktops and embedded devices make the parallel programming a requirement to ensure high performance for taking advantage of the hardware resources. For example, we see parallel computing from mainstream applications such as a web browser and a text editor to scientific applications – e.g., fluid dynamics simulation.

Parallel applications require a method to exchange information between the threads or processes in run-time. There are two main models to implement it:

- Shared-memory: this model assumes that programs will be executed on one or more processors that share the available memory address space. Shared-memory programs are typically performed by multiple independent threads; the threads share data but may also have some additional, private data. Shared-memory approaches to parallel programming must provide, in addition to a normal range of instructions, a means for starting up threads, assigning work to them, and coordinating their accesses to shared data, including ensuring that certain operations are executed by only one thread at a time (CHAPMAN; JOST; PAS, 2007). OpenMP and PThreads are parallel programming interfaces that implement a shared-memory model.

- Message-passing: this model assumes that programs will be executed by one or more processes, each of which has its own private address space. Message-passing approaches must provide a mechanism to initiate and manage the participating processes, along with operations for sending and receiving messages, and possibly for performing specialized operations across data distributed among the different processes (CHAPMAN; JOST; PAS, 2007). The Message Passing Interface (MPI) is an example of standard that uses this model.

While PThreads and MPI present a set of routines libraries in which the programmer has to designate details of the parallel execution, OpenMP takes a form of additional

Figure 2.2: Example of parallel program using OpenMP.

```

#include <stdio.h>

#include <omp.h>

int main()

{

int i;

int a[10] = {1, 2, 3, 4, 5, 6, 7, 8, 9, 10};

#pragma omp parallel for

for (i = 0; i < 10; i++) {

a[i] = a[i] * 2;

}

/* Sequential region */

return 0;

}</pre>

```

Source: The Author

instructions to the compiler, which is expected to use them to generate the parallel code. Therefore, the use of OpenMP is usually more straightforward for the programmer.

#### **2.2.1 OpenMP**

OpenMP is a parallel programming interface for shared memory in C/C++ and FORTRAN that uses shared memory for communication between threads. It permits the user to parallelize its code only by using compilation directives. These directives inform the compiler of the regions for parallel execution and OpenMP takes care of the low-level steps, for example, thread creation and synchronization. Therefore, as already mentioned, it usually requires less effort to extract parallelism when compared to other APIs (e.g., PThreads and MPI), making it more appealing to software developers (S. et al., 2011). Figure 2.2 shows an example of a simple array processing using the directive *omp parallel for* to parallelizing the loop.

It supports the so-called fork-join programming model. Under this method, the process starts as a single thread, just like the sequential program. Whenever a thread finds an OpenMP parallel construct while it is executing the application, it creates a team of threads (this is the fork), becomes the master of the team, and cooperates with the other members of the team to execute the code dynamically enclosed by the construct. At the end of the construct, only the original thread, or master of the team, continues; all others

terminate (this is the join). The parallel region is the piece of code enclosed by a parallel construct (CHAPMAN; JOST; PAS, 2007).

Furthermore, OpenMP provides three ways for exploiting parallelism: parallel loops, sections, and tasks. Sections and tasks are only used in very particular cases: when the programmer must distribute the workload between threads in a similar way as PThreads, and when the application uses recursion (e.g. in sort algorithms). On the other hand, parallel loops are used to parallelize applications that work on multidimensional data structures (e.g arrays or grids), so the loop iterations (*for*) can be split into multithread executions. Therefore, parallel loops are by far the most used approach and all popular OpenMP benchmarks are implemented this way.

# 2.3 Scalability of Parallel Applications

In this section, we discuss how parallel applications scale under the number of threads and CPU frequency – although the latter is not exclusive to parallel applications, the parallelism can contribute to the lack of scalability. First, we show some bottlenecks that prevent or even worsen the outcomes of parallel applications when one increases the number of threads. Next, we explain that some applications will barely improve the performance as one increases the CPU frequency, so we can set a low DVFS setting to reduce energy consumption, and consequently improve the EDP result.

#### 2.3.1 Number of Threads

Not always selecting the maximum available number of cores to execute a parallel application will deliver the best results, since many aspects prevent linear improvements as one increases the number of threads. We discuss them in the following paragraphs.

**Issue-width saturation:** the SMT technology permits that two threads run simultaneously into the same physical core sharing functional units. However, the use of SMT when executing applications that present high Instruction-Level Parallelism (ILP) can lead to more competition for resources resulting in functional unit contention, consequently degrading performance (RAASCH; REINHARDT, 2003). Figure 2.3 presents the performance speedup relative to the sequential version and the number of idle cycles (average, represented by the bars, and total) as we increase the number of threads for the

Figure 2.3: Issue-width saturation 7.0 1.2 Avg idle cycles 6.0 \*Total idle cicles [dle Cycles x10<sup>12</sup> -Time 5.0 0.8 4.0 3.0 2.0 1.0 0.0 #Threads

Source: (LORENZON et al., 2018)

HotSpot (HS) application. As the benchmark executes with 13 threads or more, some threads will share the same physical core because the SMT is activated. After enabling the SMT, the average number of idle cycles increases by a small amount or stays constant, while the total number of idle cycles significantly increases, which prevents improvements in performance.

Off-chip bus saturation: when dealing with a massive amount of data, the application will end up being dependent on the main memory as the private caches will not have sufficient storage space. The problem is that the off-chip bus bandwidth is limited compared with the number of cores. Therefore a higher number of threads will increase the memory requests that can lead to saturation of this resource (JOAO et al., 2012). Figure 2.4 shows the Fast-Fourier Transform (FFT) execution as an example. As the number of threads increases, the execution time diminishes until the off-chip bus becomes completely saturated (100% of utilization). After this point (4 threads), increasing the concurrency will not improve the performance because the bus is slowly processing all the requested data.

**Data-synchronization saturation:** the threads in a parallel application sometimes need to communicate with each other. To ensure data synchronization and integrity is necessary a critical section at the end of a parallel region. Critical sections allow only one thread execution at a time, i.e., each thread runs sequentially in this stage. Therefore, the higher is the number of threads more time will need to execute the critical section that may end up in loss of benefits achieved by the parallel phase (SULEMAN; QURESHI; PATT, 2008). Figure 2.5 presents the execution time broken on the critical and parallel

Figure 2.4: Off-chip bus saturation 120% Off-chip bus utilization 100% 80% 60% 40% Off-chip 20% Time 0% 4 19 22 10 13 # Threads

Source: (LORENZON et al., 2018)

10 ■ Parallel Region □ Critical Region 8 **Execution Time** 4 2 0 3 5 7 9 13 15 17 19 21 23 11 # Threads

Figure 2.5: Data-synchronization saturation

Source: (LORENZON et al., 2018)

region for the benchmark N-Body (NB) for each DCT configuration. After four threads, the critical phase exceeds the parallel region, so the performance begins to worsen.

Besides that, the best DCT configuration to optimize energy or performance can be different as there is a trade-off between achieving higher speed splitting the workload in more threads and extra power consumption caused by more resources working.

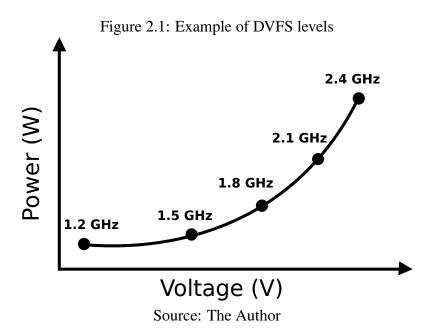

Figure 2.6 shows outcomes for time and energy normalized to the minimum parallelism (two) from one parallel region of the Block tri-diagonal solver (BT) benchmark running on a 24 cores system (24 hardware threads/12 physical cores). First, we can see that the region has poor scaling that will give unsatisfactory results running on the maximum number of threads. Besides that, while six threads ensure the optimum energy point, we need eight threads for the best result in performance.

Figure 2.6: Impact of the number of threads on the performance and energy.

## 2.3.2 CPU Frequency

As already described in Section 2.1, a DVFS system can take advantage of processor idleness and reduce the frequency level to decrease power consumption. For example, when an application makes many memory requests and has to wait for data from DRAM. In this case, increasing the processor frequency will not linearly improve the application performance.

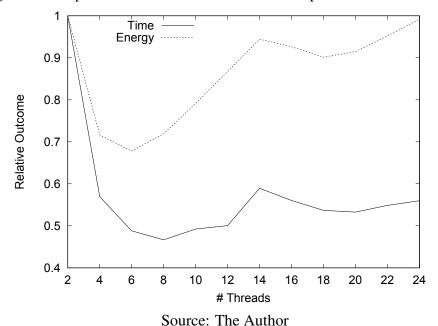

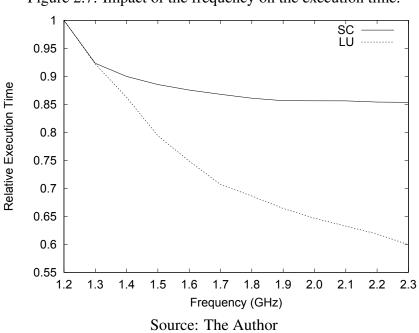

Figure 2.7 shows the impact of the frequency scaling in the execution time of two applications running in a system with 24 threads and 12 frequency levels. The x-axis represents each available DVFS configuration on the processor, and the y-axis gives the execution time relative to the lowest frequency. While the StreamCluster (SC) that is a memory-bound application, shows minimal performance improvement after a certain frequency level, the Lower-Upper gauss-seidel solver (LU), a CPU-bound benchmark, maintains a consistent decrease of execution time till the maximum frequency. Thus, applications like SC permits that we use DVFS to apply a low frequency reducing power consumption with minimal performance impact consequently optimizing the application EDP.

Figure 2.7: Impact of the frequency on the execution time.

#### **3 RELATED WORK**

We discuss the related work following the same order as listed in Table 3.1. We classify them into three categories: techniques that optimize the number of threads only; those that apply DVFS; and approaches that consider both. Works in each category are organized according to their adaptability:

- Offline: these works use an algorithm to learn the optimum or the near optimum configuration offline. After defining the best settings, the application loads it during the execution time. The drawbacks of this strategy are the need for training always that a characteristic of application or system changes, and the long learning time.

- **Hybrid:** these tools divide the adaptation process into two steps: offline and online phases. The former uses an algorithm with example cases, such as linear regression, to build a training a model. The latter uses the training model with dynamic data for online adaptation. Besides the long time needed for preparing the model, it also needs different training on each specific system. Moreover, in the same way as before, the cases used to train the model may miss some critical characteristics that can only appear at run-time (e.g., application input set and CPU load).

- Online: for these cases, the algorithm learns the configuration at run-time. They use some samples for training, find the best outcome and apply it to the next iterations. As to the disadvantages, there is an overhead caused during the learning step. Therefore, it needs many repetitions for a given target parallel region to overcome its cost.

Finally, we also use **transparency** for classifying the works. It is the capacity of adapting the application without code modification or instrumentation, that is, given the application binary, the tool can optimize it.

## 3.1 Adaptation of the Number of Threads

Thread Reinforcer (TR) (PUSUKURI; GUPTA; BHUYAN, 2011) works offline and involves the execution of the application binary multiple times for a short period with a different number of threads to find the appropriate configuration. Then, the application is fully re-executed with the number of threads previously defined. By executing the application binary already compiled, TR is a particular case that keeps binary compatibility.

Some approaches present some degree of adaptability, such as (JUNG et al., 2005), (CURTIS-MAURY et al., 2006), (CURTIS-MAURY et al., 2008), and (RAMAN et al., 2012). They are capable of changing the number of threads at runtime, although they need some previous offline analysis, instrumentation code, or a special compiler. Jung et al. (2005) present performance models for generating adaptive parallel code for SMT architectures. At compile-time, the preprocessor inserts performance estimation using a formula based on iterations, assignments, floating point operations, and function calls. Also, it injects instrumentation code using machine specific parameters for online analysis. At run-time, the master thread uses the analysis performed at compilation time to dynamically estimate whether it should enable the SMT in the core or not.

Curtis-Maury et al. (2006) propose a framework that has an off-line phase in which data from hardware event counters are collected to profile the parallel execution through a linear model to predict IPC. These trained models – one for each configuration target – are used at runtime to adapt the number of threads per processor and how many processors to use in each parallel region aiming to improve performance and energy consumption. Likewise, (CURTIS-MAURY et al., 2008) dynamically changes the number of threads and affinity of parallel regions that were identified by the programmer by using multivariate linear regression, which is trained off-line with performance counters. Also, the framework needs instrumentation in the target application.

In (RAMAN et al., 2012), the authors developed a particular compiler, Nona, that identifies parallelizable regions on a sequential code and applies multiple types of parallelism to each region. Also, it inserts profiling hooks for a run-time system to monitor its performance. The Parcae run-time system includes the Decima monitor and the Morta executor. The former can distinguish the time a task spends doing real computing and the overhead for communication. Finally, the latter can use the information from Decima to find the optimal or the near optimal parallelism configuration for the execution environment focusing on objectives such as minimize total execution time and energy consumption.

The following strategies that are online. In (SULEMAN; QURESHI; PATT, 2008), (PORTERFIELD et al., 2013), (LEE et al., 2010), (SRIDHARAN; GUPTA; SOHI, 2013), (SRIDHARAN; GUPTA; SOHI, 2014), (SHAFIK et al., 2015a), (LORENZON; SOUZA; BECK, 2017), and (LORENZON et al., 2018), the process of adjusting the concurrency level is totally at run-time.

Suleman et al. propose the FDT framework (SULEMAN; QURESHI; PATT,

2008). After code transformation of an application implemented with OpenMP, FDT samples portions of the application at run-time to estimate the application behavior, which is used to find the number of threads that saturates the parallel region performance so that the next iterations will run with fewer threads than the saturation point. During the training phase, it focuses on two performance bottlenecks: data-synchronization and bus bandwidth.

Porterfield et al. (2013) propose an adaptive run-time system that automatically adjusts the concurrency level based on online measurements of system resource usage. The framework extends Qthreads (a general purpose parallel library that is designed to support lightweight threading (WHEELER; MURPHY; THAIN, 2008)) and combines it with the running average power limit (RAPL) interface (HäHNEL et al., 2012) in the Intel architecture to build a scheduler that automates dynamic concurrency throttling. Thus, it will limit the level of parallelism in regions of code where power consumption is high and contention for a shared resource limits execution performance.

In Thread Tailor (LEE et al., 2010), a static software tool chain creates as many threads as can potentially be used by the architecture. At runtime, a Just-in-Time compiler takes a quick snapshot of the system state to determine how many free resources are available (e.g., number of available cores or free cache space) to apply thread throttling, generating code for that and redirecting the calls to increase system efficiency.

ParallelismDial (PD) (SRIDHARAN; GUPTA; SOHI, 2013) is a model that optimizes a program's execution efficiency by dynamically and continuously adapting the application parallelism to the execution conditions. To dynamically adjust software parallelism, PD firstly assesses the efficiency of the system using a proposed metric, Joules per instruction, that manifests effects in both instruction rate and energy expended. Also, it detects contention, variations in the program, and changes in the available resources. After these changes, it seeks to find and move the execution to the optimum degree of parallelism employing a heuristic based on the hill-climbing search algorithm. Finally, for continuous adaptation, PD periodically repeats the mentioned steps.

In (SRIDHARAN; GUPTA; SOHI, 2014), PD was extended to Varuna, which comprises an analytical engine which continuously monitors changes in the system using hardware performance counters to determine the optimum degree of parallelism; and a manager that regulates the execution to match the degree of parallelism previously defined. PD and Varuna comprise a monitor system that intercepts thread and task creation from PThreads, TBB, and Prometheus libraries, and create a pool of tasks to optimize

their degree of parallelism, creating a large number of fine-grained tasks, requiring more effort from the programmer.

Shafik et al. (2015a) propose an energy minimization model for OpenMP programs that involves code annotations that must be inserted in the code with specific performance requirements; which will be used by the run-time system to minimize energy.

LAANT (LORENZON; SOUZA; BECK, 2017) is a library that automatically adjusts the number of threads for optimizing the EDP of OpenMP applications. The code must be modified by the programmer to include additional function calls in each parallel region of interest. Besides that, it uses a finite state machine to implement a heuristic based on a hill-climbing algorithm.

All of these aforementioned works need code recompilation. Considering the case of LAANT, it was extended to Aurora (LORENZON et al., 2018), which can adapt the degree of TLP exploitation of OpenMP applications transparently. In order to achieve such level of transparency, the authors have implemented the search algorithm used by Aurora inside of the OpenMP library (libgomp), which is dynamically linked to the application at runtime. Therefore, any application can benefit from Aurora without modifications in the source code or recompilation.

## 3.2 CPU Frequency Level

Rossi et al. (2015) propose an offline approach using a multiple linear regression model based on DVFS and CPU usage that estimates the power consumption. It is implemented for different DVFS policies: performance (frequency is always at the maximum level), ondemand (frequency is adjusted according to the workload behavior), and powersaving (frequency is always at the minimum level). Thus, the programmer can use the predicted values to select the DVFS policy that provides the lowest power consumption.

In (HOTTA et al., 2006), the authors propose PowerWatch, a power-performance optimization model that adapts the processor frequency at run-time but relies on an off-line phase. In the approach, a parallel application is split into several regions by the programmer. Then, each region is executed with different processor frequencies during the off-line phase. Finally, the optimization algorithm determines the best processor operating frequency for each region and re-run the application with such frequency values.

Another hybrid approach is the Pack & Cap (COCHRAN et al., 2011), which manages the CPU voltage-frequency setting and the use of thread affinity (but do not

perform Thread Throttling) to optimize performance within a power budget. It consists of an offline phase where a large volume of data (performance, energy, temperature) are collected to train a multinomial logistic regression (MLR) classifier. Then, at runtime, the MLR classifier selects the optimal or the near optimal configuration to execute the rest of the application.

Next, we discuss run-time approaches, which do not need off-line analysis but need specific compilers/tools to enable the online adaptation.

DEP+BURST (AKRAM; SARTOR; EECKHOUT, 2016) is an online DVFS performance predictor to manage multithreaded applications that run on top of the Java virtual machine. It presents two key components, DEP and BURST. The former handles synchronization and inter-thread dependencies. It decomposes the execution time of a multithreaded application into epochs based on its synchronization activity identified by intercepting specific system calls used in multithread libraries. The latter identifies store operations that are on the application's critical path and predicts their impact on performance across frequency settings.

In (WU et al., 2006), the authors propose a dynamic compiler system that is a runtime software that compiles, changes and optimizes a program's instruction sequences. First, the framework selects frequently executed and long-running code regions to optimization such as loops and functions. After, it decides whether applying DVFS is beneficial for the candidate regions and determines the appropriate DVFS setting using hardware feedback information. Finally, for the regions where DVFS is useful, the tool inserts instructions at the entry point to start DVFS and at the exit point to restore the default configuration aiming to reduce energy consumption with a little performance impact.

Finally, we present online and transparent mechanisms to optimize the DVFS settings.

Hsu and Feng (2005) propose an automatic power-aware run-time system that adapts the CPU operating frequency to reduce energy consumption with minimal performance slowdown. The algorithm is an interval based scheduling that makes decisions at the beginning of time intervals of the same length, for example, every one second. The authors propose a model based on MIPS (Millions of Instruction Per Second) that associates the intensity of off-chip accesses to correlate the CPU frequency impact on the execution time.

Rizvandi et al. (2010) propose a maximum-minimum-frequency DVFS algorithm (MMF-DVFS). It uses a linear combination of the maximum and minimum processor

frequencies to reduce the energy consumption with minimal impact on the system's performance.

Ge et al. (2007) present the CPU Management Infra-Structure for Energy Reduction (CPU-MISER), a run-time DVFS scheduler for multicore-based power aware clusters. It consists of a monitor that collects performance events from the application using hardware counters and predicts the application's workload. Based on the predicted value, the DVFS scheduler determine the CPU frequency for the rest of the application.

In (MIFTAKHUTDINOV, 2014), the authors propose a performance predictor to control the CPU frequency level at runtime. The model measures the workload characteristics for each parallel region and estimates the performance at different CPU frequency levels. Then, when the region is re-executed, the CPU frequency is set to the level that offers the best performance.

Chen et al. (2016) also propose a model with the same purpose, but to predict the best CPU frequency level and voltage for multicore embedded systems aiming to reduce the energy consumption. In the approach, the user must define a given performance loss factor so the model can reduce the energy consumption accordingly.

## 3.3 CPU Frequency Level and Number of Threads

The aforementioned works apply either DVFS or Threads. More complete solutions that consider both are discussed here.

An offline approach is proposed by De Sensi (SENSI, 2016). It predicts the number of threads and CPU frequency level that offers the best performance and energy consumption for parallel applications. The idea is to execute the program using few configurations and then, predict the behavior of the other settings through multiple linear regression.

Hybrid (Offline+Online) approaches include (LI; MARTINEZ, 2006) and (LI et al., 2010). The former is divided into three phases: (*i*) the application is executed once for every combination (thread number and DVFS level), and energy and performance are collected; (*ii*) different optimization mechanisms are simulated with Matlab to find the combination that delivers the best result in energy under given performance restrictions (*ii*) At run-time, the approach uses the best combination found in phase *ii* to optimize the execution. In (LI et al., 2010), the authors propose a library for hybrid MPI/OpenMP applications by selecting the appropriate number of threads and CPU frequency to execute

each OpenMP region. The library has an off-line phase to train a model that will be used at runtime for each OpenMP region. The user has to instrument the applications with functions calls around each OpenMP region and selected MPI operations.

Finally, there are fully online approaches that are worth mentioning. They are (ALESSI et al., 2015), (SENSI; TORQUATI; DANELUTTO, 2016), (MARATHE et al., 2015), and (CHADHA; MAHLKE; NARAYANASAMY, 2012). We discuss them in the following paragraphs.

OpenMPE (ALESSI et al., 2015) is an extension designed for energy management of OpenMP applications, in which the programmers insert new directives in OpenMP code to indicate potential regions to save energy. For that, it requires a particular compiler and run-time system (from the Insieme project (ALESSI et al., 2015)) to recognize the directives at compilation time and apply the energy management during the application execution.

Nornir (SENSI; TORQUATI; DANELUTTO, 2016) is a runtime system that monitors the application execution and adjusts the resources configurations (DVFS, number of threads, and thread placement) in order to satisfy either performance or power consumption requirements. To use Nornir, the user has to install a system to manage the features provided by the OS (e.g. DVFS management and energy profiling), and instrument the parallel programming framework with Nornir functions.

Marathe et al. (2015) propose *Conductor*, a run-time system that dynamically selects the ideal number of threads and DVFS state to improve performance under a power constraint for hybrid applications (MPI + OpenMP). First the application is monitored in order to gauge its representative behavior; and then, a local search algorithm is applied to find and select the configuration to reduce power with minimal impact on execution time. For that, Conductor needs code modifications to insert functions.

LIMO (CHADHA; MAHLKE; NARAYANASAMY, 2012) is a dynamic system that monitors the application at run-time, being able to adapt the number of threads and DVFS accordingly. LIMO monitors the threads' progress aiming to disable cores when the thread is not making forward progress (e.g., in a synchronization function, blocking I/O call or is suspended) and, therefore, diminishing the power consumption. After disabling some cores, there is a space to increase the frequency on the active ones without exceeding a power budget. Although the work can make an online adaptation, this solution requires hardware modifications and special compiler support to determine the working set size of a thread, as well as additional OS support.

Table 3.1: Comparison of Odin with the related work

|                                            |          | nobs |         | daptabili |        |            | Transparen | cv                      |                      |

|--------------------------------------------|----------|------|---------|-----------|--------|------------|------------|-------------------------|----------------------|

| Proposal                                   |          |      |         |           |        | No special | No         | ř –                     | APIs                 |

|                                            | TLP      | DVFS | Offline | Hybrid    | Online | compilers/ | programmer | Binary<br>Compatibility |                      |

|                                            |          |      |         | -         |        | tools      | Influence  | Companionity            |                      |

| (PUSUKURI; GUPTA;                          | х        |      | v       |           |        |            | v          | X                       | OpenMP, PThreads     |

| BHUYAN, 2011)                              | X        |      | X       |           |        |            | X          | X                       | Openivir, Finiteaus  |

| (CURTIS-MAURY et al.,                      | x        |      |         | х         |        |            |            |                         | OpenMP               |

| 2008)                                      | , x      |      |         | Α         |        |            |            |                         | 1                    |

| (JUNG et al., 2005)                        | X        |      |         | X         |        |            | X          |                         | OpenMP-FORTRAN       |

| (CURTIS-MAURY et al.,                      | x        |      |         | X         |        |            | x          |                         | OpenMP-FORTRAN       |

| 2006)                                      | ^        |      |         | Λ         |        |            | Α          |                         | *                    |

| (RAMAN et al., 2012)                       | X        |      |         | X         |        |            | X          |                         | Sequential Code      |

| (LEE et al., 2010)                         | X        |      |         |           | X      |            |            |                         | PThreads, MPI        |

| (SRIDHARAN; GUPTA;                         | x        |      |         |           | x      | x          |            |                         | TBB, Prometheus      |

| SOHI, 2013)                                |          |      |         |           |        |            |            |                         | 155,11011001000      |

| (SRIDHARAN; GUPTA;                         | x        |      |         |           | X      | x          |            |                         | PThreads, TBB        |

| SOHI, 2014)                                |          |      |         |           |        |            |            |                         |                      |

| (SHAFIK et al., 2015a)                     | X        |      |         |           | X      | X          |            |                         | OpenMP               |

| (SHAFIK et al., 2015b)                     | X        |      |         |           | X      | X          |            |                         | OpenMP               |

| (LORENZON; SOUZA;                          | x        |      |         |           | x      | x          |            |                         | OpenMP               |

| BECK, 2017)                                |          |      |         |           |        | -          |            |                         |                      |

| (SULEMAN; QURESHI;                         | x        |      |         |           | x      |            | x          |                         | OpenMP               |

| PATT, 2008)                                |          |      |         |           |        |            |            |                         | 1                    |

| (PORTERFIELD et al.,                       | x        |      |         |           | x      |            | x          |                         | OpenMP               |

| 2013)                                      |          |      |         |           |        |            |            |                         | -                    |

| (LORENZON et al., 2018)                    | X        |      |         |           | X      | X          | X          | X                       | OpenMP               |

| (ROSSI et al., 2015)                       |          | X    | X       |           |        |            | X          | X                       | OpenMP, PThreads     |

| (HOTTA et al., 2006)                       |          | X    |         | X         |        |            |            |                         | OpenMP-FORTRAN       |

| (COCHRAN et al., 2011)                     |          | X    |         | X         |        | X          | X          | X                       | OpenMP, PThreads     |

| (AKRAM; SARTOR;                            |          | x    |         |           | x      |            |            |                         | Java Applications    |

| EECKHOUT, 2016)<br>(WU et al., 2006)       |          |      |         |           |        |            |            |                         | 0 (1 1               |

|                                            |          | X    |         |           | X      |            | X          |                         | Sequential code      |

| (HSU; FENG, 2005)                          |          | X    |         |           | X      |            | X          | X                       | Sequential, MPI      |

| (RIZVANDI et al., 2010)                    |          | X    |         |           | X      | X          | X          | X                       | Any                  |

| (GE et al., 2007)                          |          | X    |         |           | X      | X          | X          | X                       | OpenMP-FORTRAN       |

| (MIFTAKHUTDINOV,                           |          | x    |         |           | x      | x          | x          | x                       | OpenMP, PThreads     |

| 2014)<br>(CHEN et al., 2016)               |          |      |         |           |        |            |            |                         | O MD DThd-           |

|                                            |          | X    |         |           | X      | X          | X          | X                       | OpenMP, PThreads     |

| (SENSI, 2016)                              | X        | X    | X       |           |        |            | X          | X                       | OpenMP, PThreads     |

| (LI; MARTINEZ, 2006)                       | X        | X    |         | X         |        | X          |            |                         | OpenMP<br>MPI+OpenMP |

| (LI et al., 2010)                          | X        | X    |         | X         |        | X          |            |                         |                      |

| (ALESSI et al., 2015)<br>(SENSI; TORQUATI; | X        | X    |         |           | X      |            |            |                         | OpenMP               |

| (SENSI; TORQUATI; DANELUTTO, 2016)         | x        | X    |         |           | x      |            |            |                         | OpenMP, PThreads     |

| (MARATHE et al., 2015)                     | x        | X    |         |           | X      | X          |            |                         | MPI+OpenMP           |

| (CHADHA; MAHLKE;                           | <u> </u> | Α    |         |           |        | ^          |            |                         | 1711 1 Openivii      |

| NARAYANASAMY,                              | x        | x    |         |           | X      |            | x          |                         | OpenMP, PThreads     |

| 2012)                                      | ^        | A    |         |           | .      |            | "          |                         |                      |

| Odin                                       | х        | X    |         |           | X      | X          | X          | x                       | OpenMP               |

|                                            |          |      |         |           |        |            |            |                         |                      |

# **3.4 Our Contributions**

Table 3.1 compares Odin to previous works. The column *knobs* indicates whether the approach optimizes TLP, DVFS, or both. The column *adaptability* indicates when the optimization is performed. *Offline* approaches only predict the behavior of a given application and do not perform any sort of run-time adaptation. *Online* mechanisms adapt the application behavior at run-time without any off-line phase. *Hybrid* approaches adapt at run-time but rely on some sort of off-line analysis. The column *no special compiler/tools*

indicates the approaches that do not need any specific compiler or tool (i.e., use different tools from the traditional programming frameworks. The column *no programmer influence* contains the approaches that do not demand any changes in the source code by the software developer. Techniques with *Binary compatibility* can be used without any need for code recompilation at all: the existent binary code as is can be optimized. The column *API* shows the parallel libraries supported by each referred work.

As we will show in this work, only approaches that consider both Threads and Operating Frequency are capable of delivering the best results in EDP. As depicted in Table 3.1, none of them covers all the needed characteristics so it could be considered completely transparent and adaptive. On the other hand, Odin performs DCT and tunes the DVFS as the application executes with minimal overhead, without the need for any sort of off-line analysis. Besides being capable of adapting to the system and application at hand, it works with any C/C++ compiler and OpenMP. It means that the software developer does not need to make any changes in the source code or even recompile it. To enable Odin, the user only has set one environment variable in the Linux OS. Because of this high level of transparency, Odin is limited to OpenMP applications.

## 4 PROBLEM DEFINITION AND SEARCH STRATEGIES

In this chapter, we present a formal definition of the problem of optimizing parallel applications, which we use as motivation to develop the searches strategies. Then, we describe each search strategy that we use for results comparison.

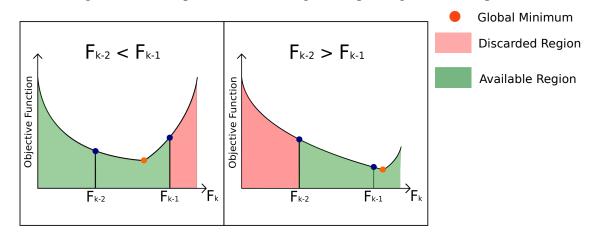

## **4.1 Problem Definition**