# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

RENÊ MORENO TIMBÓ

# A 130nm CMOS UHF Satellite Receiver Front-End for the Brazilian Environmental Data Collecting System

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microelectronics

Advisor: Prof. Dr. Hamilton Duarte Klimach

Porto Alegre May 2019 Timbó, Renê Moreno

A 130nm CMOS UHF Satellite Receiver Front-End for the Brazilian Environmental Data Collecting System / Renê Moreno Timbó. – Porto Alegre: PGMICRO da UFRGS, 2019.

102 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2019. Advisor: Hamilton Duarte Klimach.

1. RF Circuits. 2. Microelectronics. 3. Front-end. 4. Satellite. 5. SBCDA. 6. LNA. 7. Mixer. I. Klimach, Hamilton Duarte. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PGMICRO: Prof. Tiago Roberto Balen Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGMENTS

During the development of this thesis, I had the opportunity to meet incredible people in my way. Each of them somehow gave some contribution that helped me to finish this work.

First, I would like to thank my family, my parents João Parente Timbó and Denise de Deus Moreno Timbó, my brother Renan Moreno Timbó, my sister Renata Moreno Timbó and my brother-in-law Pablo Cassas and sister-in-law Shenna Araújo for supporting me whenever I need with a talk, advice or even with financial support.

I would like to thank my advisor Hamilton Duarte Klimach to give me the opportunity to obtain my master degree, for having patience with me and for guiding me through this whole process.

My friends and colleagues of NSCAD microeletrônica, Nelson Andrade, William Medeiros, Alonso Schmidt, Pedro Toledo, David Cordova, Helga Dornelas, Diogo Santana, Jhon Caicedo, Marcelo Negreiros, Jerson Guex, Thiago Nagel, Tatiana Costa and Luís Benitez that aid me technically and supported me in many moments during my trajectory.

To the NSCAD IT team, Márcia Silva and Felipe Formiga, for providing excellent support with Cadence, WicKeD and Keysight tools whenever I needed.

To the students of IC-Brazil training program that indirectly made some contribution to this work by making me study harder to teach them, to solve their problems or in some cases to propose partial solutions to this project.

To all students and professors of UFRGS Analog/RF GME group who contributes with discussions and suggestions during the meetings about this work. Also, to the friends of UFRGS LOGICS group.

To all professionals that work on administrative of Instituto de Informática and in the Microelectronics Post-Graduation Program.

To CNPq, CAPES, and LSITEC for financial support and MOSIS for the available PDK used in this work.

To all other people that directly or indirectly contributed to this work and was not mentioned.

## ABSTRACT

The Brazilian Environmental Data Collector System (SBCDA) has the objective to collect, by using satellites, data for environmental applications like meteorological forecast, pollution control, firefighting, and others. The SBCDA is composed of satellites, data collector platforms (DCP) that are distributed all over the country and a Control Center for data processing. By using more advanced technology nodes, it is expected even more integration of all components of the satellite, reducing the utilized total area and power consumption of the device as well. It is therefore proposed to design an RF receiver front-end for a transponder satellite to work at a UHF frequency of 401.635MHz with the technology of 130nm provided by IBM to accomplish this objective. It has a total gain of 39 dB, distributed between an LNA and a Mixer, 4.5 dB of NF and IIP3 of -32.5 dBm with 10.4 mW of power consumption.

Keywords: RF Circuits. Microelectronics. Front-end. Satellite. SBCDA. LNA. Mixer.

# UM *FRONT-END* DE UM RECEPTOR PARA SATÉLITE UHF NA TECNOLOGIA 130 NM CMOS PARA O SISTEMA BRASILEIRO DE COLETA DE DADOS AMBIENTAIS

## RESUMO

O Sistema Brasileiro de Coleta de Dados Ambientais (SBCDA) tem o objetivo de coletar, via satélite, dados para aplicações como previsão meterológica e climática, controle de poluição, combate a incêndios, entre outras. O SBCDA é composto por satélites, plata-formas de coleta de dados (PCD) ambientais distribuídas ao longo do país e de um Centro de controle de missão para processamento dos dados. Com a utilização de nós tecnológicos mais avançados, procura-se cada vez mais uma maior integração dos componentes, reduzindo a afea total utilizada, bem como o consumo total do dispositivo. É proposto, portanto, o projeto de um receptor do front-end RF para o transponder de um satélite na tecnologia de 130nm, fornecida pela IBM para realizar este objetivo. Ele fornece um total de 39 dB de ganho, distribuídos entre o LNA e o mixer, 4.5 dB de figura de ruído e um IIP3 de -32.5dBm consumindo 10.4mW de potência.

Palavras-chave: Circuitos RF, Microeletrônica, Front-End, Satélite, SBCDA, LNA, Mixer.

# LIST OF FIGURES

| Figure 1.1 Examples of application of Satellite images                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .13                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Number of DCP all over the years                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| Figure 1.3 Satellite with low inclination orbit for higher coverage in the country                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

| Figure 1.4 Example of a Data Collector Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| Figure 1.5 Data Collector Platforms distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |

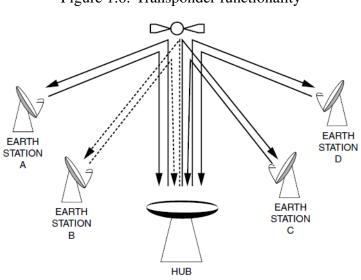

| Figure 1.6 Transponder functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .18                                                                                                                                             |

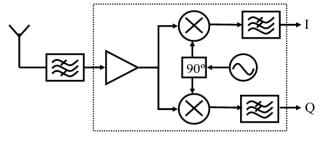

| Figure 2.1 Direct conversion architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .20                                                                                                                                             |

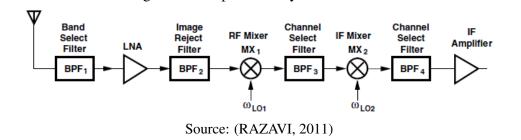

| Figure 2.2 Superheterodyne architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

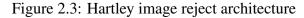

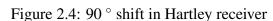

| Figure 2.3 Hartley image reject architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

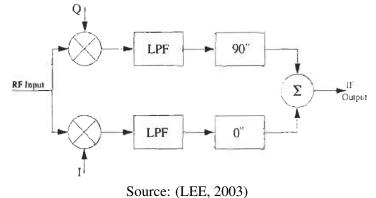

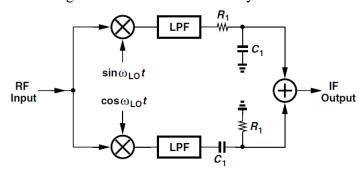

| Figure 2.4 90 ° shift in Hartley receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |

| Figure 2.5 Weaver image reject architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| Figure 2.6 Low IF image rejection architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

| Figure 2.7 Low IF homodyne architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

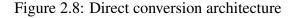

| Figure 2.8 Direct conversion architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |

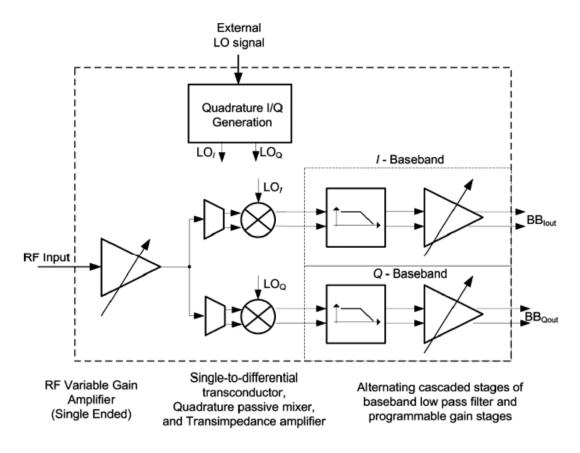

| Figure 3.1 Analog transponder architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26                                                                                                                                              |

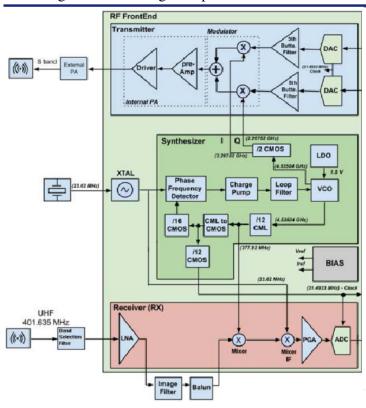

| Figure 3.2 Bit Error Rate for different phase deviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

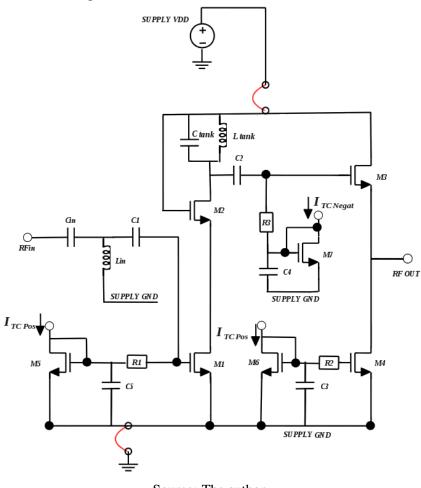

| Figure 4.1 Common source cascode LNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |

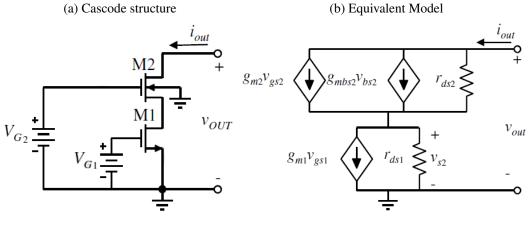

| Figure 4.2 Common Source Cascode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |

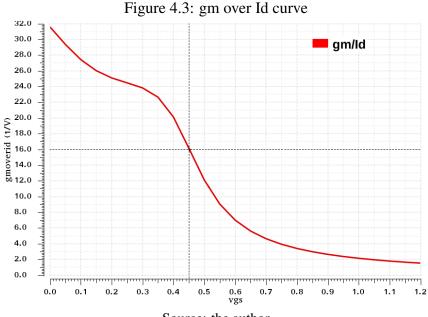

| Figure 4.3 gm over Id curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

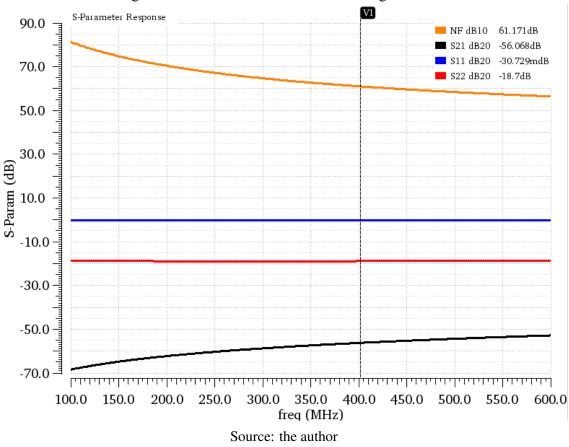

| Figure 4.4 LNA results without matching networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |

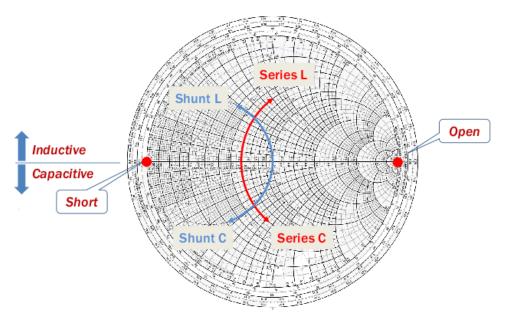

| Figure 4.5 Passive components behavior on Smith Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

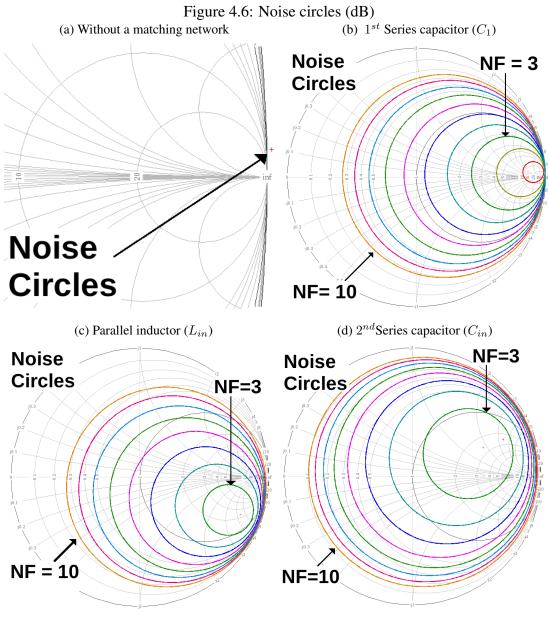

| Figure 4.6 Noise circles (dB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .39                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

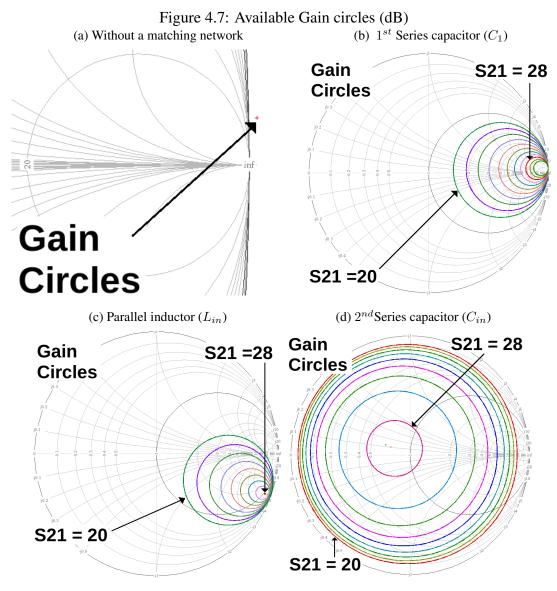

| Figure 4.7 Available Gain circles (dB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

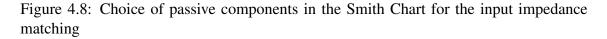

| Figure 4.7 Available Gain circles (dB)<br>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .40                                                                                                                                             |

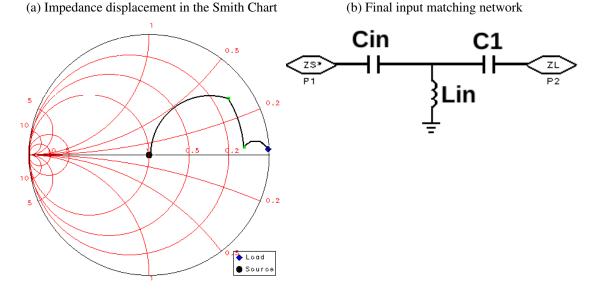

| <ul><li>Figure 4.7 Available Gain circles (dB).</li><li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .40<br>.41                                                                                                                                      |

| <ul><li>Figure 4.7 Available Gain circles (dB)</li><li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li><li>Figure 4.9 Input impedance after the inclusion of matching network</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .40<br>.41<br>.43                                                                                                                               |

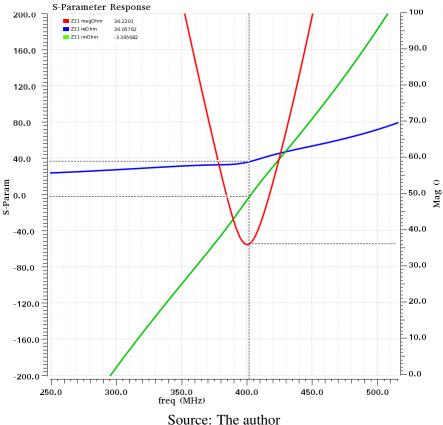

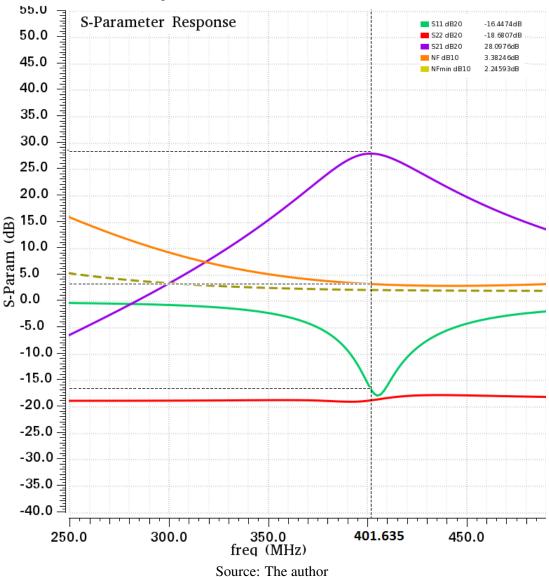

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .40<br>.41<br>.43<br>.44                                                                                                                        |

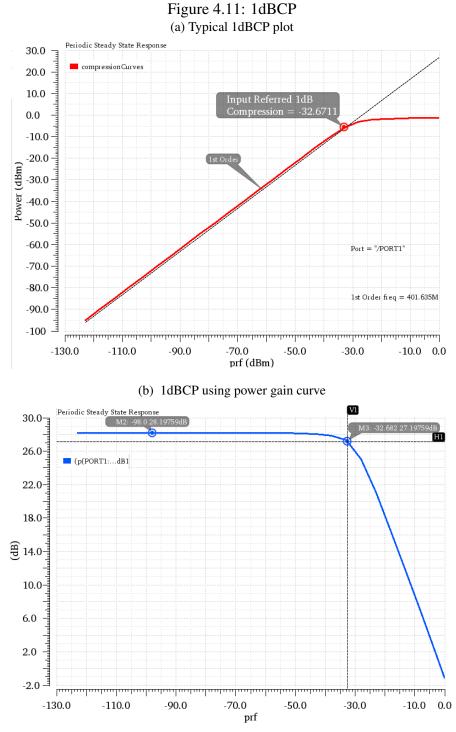

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .40<br>.41<br>.43<br>.44<br>.45                                                                                                                 |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .40<br>.41<br>.43<br>.44<br>.45<br>.46                                                                                                          |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47                                                                                                   |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47                                                                                            |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.48                                                                                     |

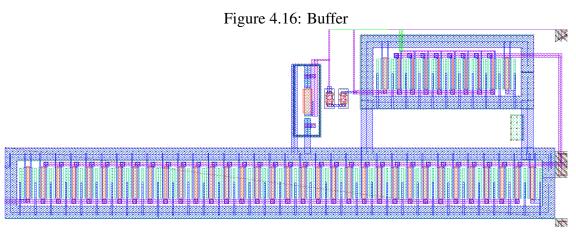

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.48<br>.49                                                                              |

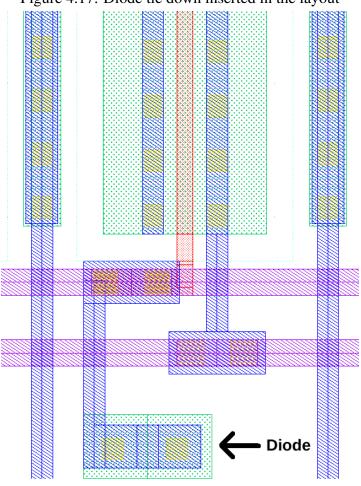

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> </ul>                                                                                                                                                                                                                                                                                    | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.47<br>.48<br>.49<br>.50                                                                |

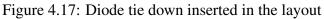

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> </ul>                                                                                                                                                                                                                                           | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.48<br>.49<br>.50<br>.51                                                                |

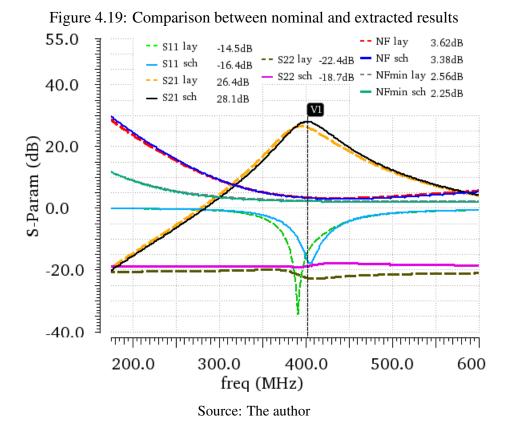

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.19 Comparison between nominal and extracted results</li> </ul>                                                                                                                                                                     | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52                                                         |

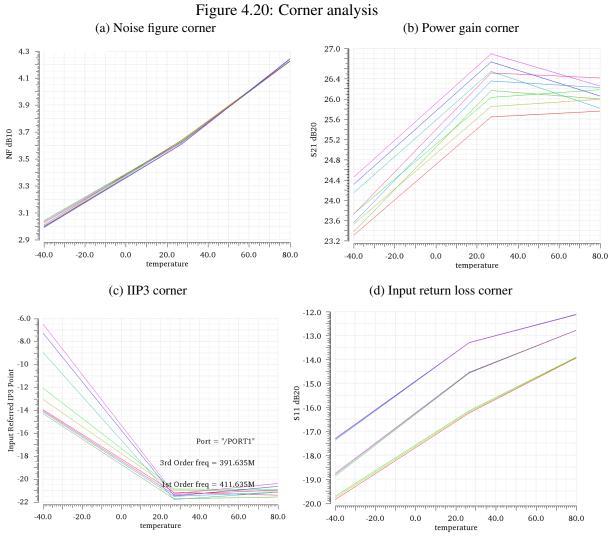

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.20 Corner analysis</li> </ul>                                                                                                                                                                                                      | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53                                           |

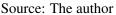

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.20 Corner analysis</li> <li>Figure 4.21 gm behavior with variation of temperature and VDC</li> </ul>                                                                                                                               | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.47<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53<br>.54                             |

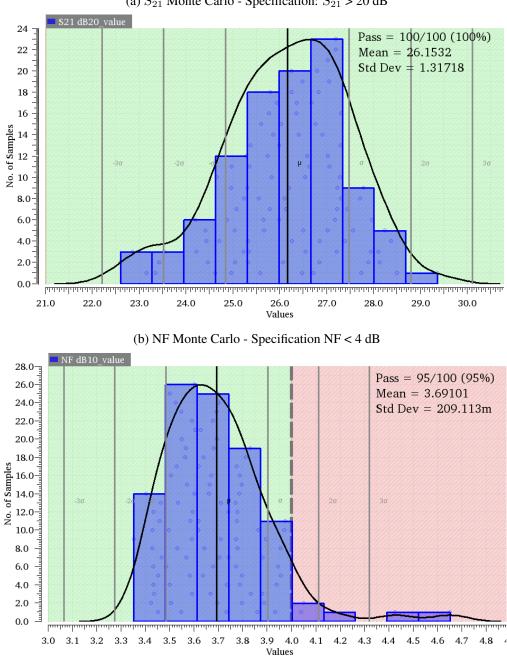

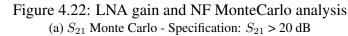

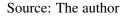

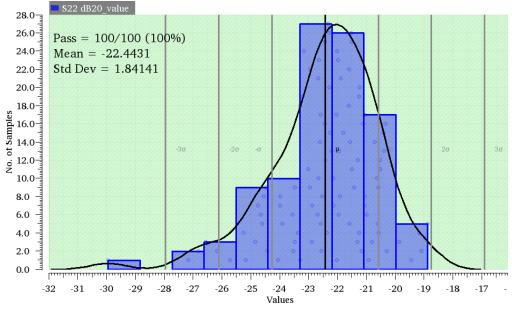

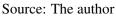

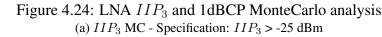

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.20 Corner analysis</li> <li>Figure 4.21 gm behavior with variation of temperature and VDC</li> <li>Figure 4.22 LNA gain and NF MonteCarlo analysis</li> </ul>                                                                      | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53<br>.54<br>.57                             |

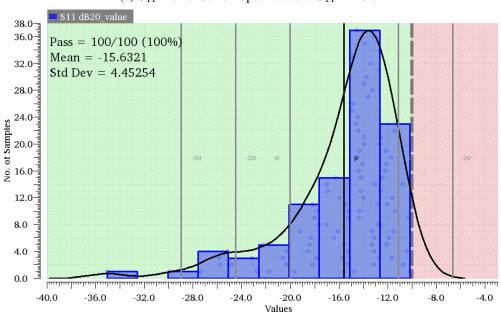

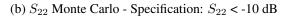

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.19 Comparison between nominal and extracted results</li> <li>Figure 4.21 gm behavior with variation of temperature and VDC</li> <li>Figure 4.23 LNA S<sub>11</sub> and S<sub>22</sub> MonteCarlo analysis</li> </ul>                                                                          | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53<br>.54<br>.57<br>.58                                    |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.20 Corner analysis</li> <li>Figure 4.21 gm behavior with variation of temperature and VDC</li> <li>Figure 4.22 LNA gain and NF MonteCarlo analysis</li> </ul>                                                                      | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53<br>.54<br>.57<br>.58                                    |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.19 Comparison between nominal and extracted results</li> <li>Figure 4.21 gm behavior with variation of temperature and VDC</li> <li>Figure 4.23 LNA S<sub>11</sub> and S<sub>22</sub> MonteCarlo analysis</li> </ul>                                                                          | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.47<br>.47<br>.47<br>.47<br>.47<br>.50<br>.51<br>.52<br>.53<br>.54<br>.57<br>.58<br>.59 |

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.10 Schematic nominal results</li> <li>Figure 4.11 1dBCP</li> <li>Figure 4.12 Intermodulation products</li> <li>Figure 4.13 Typical IIP3 plot</li> <li>Figure 4.14 IIP3</li> <li>Figure 4.15 Common source cascode structure</li> <li>Figure 4.16 Buffer</li> <li>Figure 4.17 Diode tie down inserted in the layout</li> <li>Figure 4.18 Final LNA structure</li> <li>Figure 4.20 Corner analysis</li> <li>Figure 4.21 gm behavior with variation of temperature and VDC</li> <li>Figure 4.23 LNA S<sub>11</sub> and S<sub>22</sub> MonteCarlo analysis</li> </ul> | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53<br>.54<br>.57<br>.58<br>.59<br>.61               |

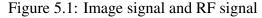

| <ul> <li>Figure 4.7 Available Gain circles (dB)</li> <li>Figure 4.8 Choice of passive components in the Smith Chart for the input impedance matching.</li> <li>Figure 4.9 Input impedance after the inclusion of matching network</li> <li>Figure 4.10 Schematic nominal results</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .40<br>.41<br>.43<br>.44<br>.45<br>.46<br>.47<br>.48<br>.49<br>.50<br>.51<br>.52<br>.53<br>.54<br>.57<br>.58<br>.59<br>.61<br>.64<br>.65        |

| Figure 5.5 The low-pass to Bandpass transformation                            | 66  |

|-------------------------------------------------------------------------------|-----|

| Figure 5.6 Butterworth bandpass filter                                        |     |

| Figure 5.7 Filter result                                                      | 68  |

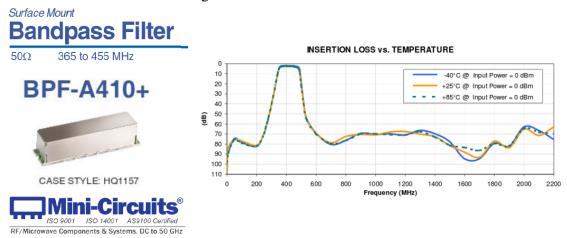

| Figure 5.8 Commercial filter                                                  | 68  |

| Figure 6.1 Mixer representation                                               | 70  |

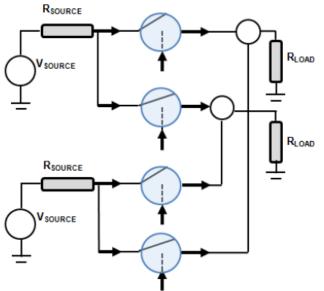

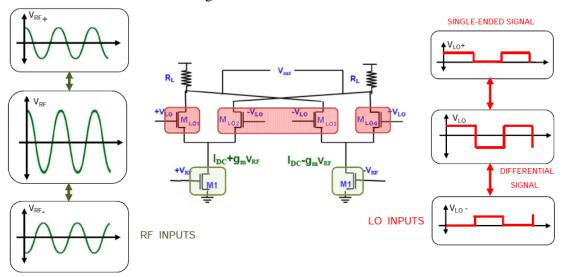

| Figure 6.2 Double balanced mixer                                              |     |

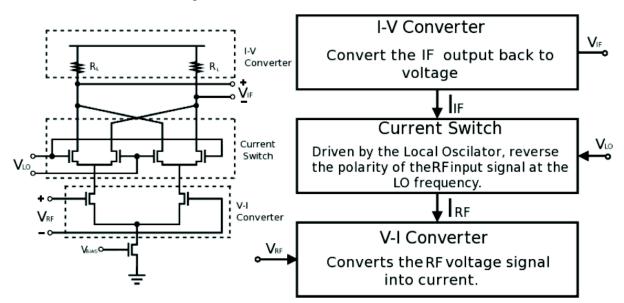

| Figure 6.3 Schematic of mixer                                                 |     |

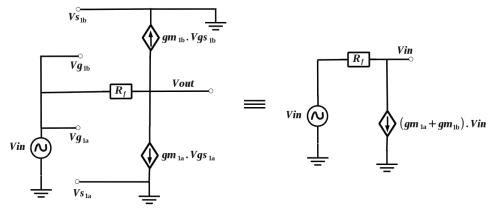

| Figure 6.4 Simplified small signal model for single-to-differential stage     |     |

| Figure 6.5 Basic Gilbert Cell                                                 |     |

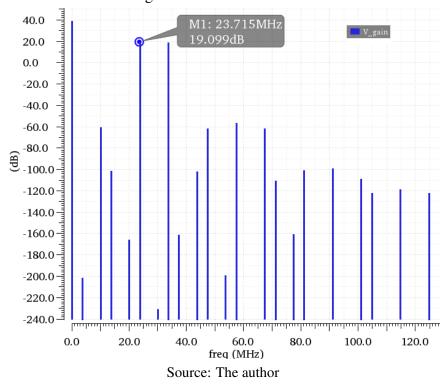

| Figure 6.6 Conversion Gain                                                    | 75  |

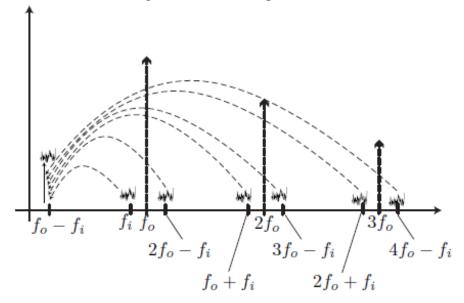

| Figure 6.7 Noise displacement                                                 | 76  |

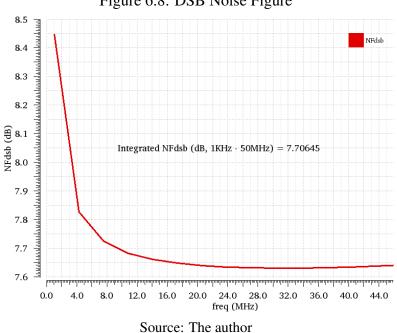

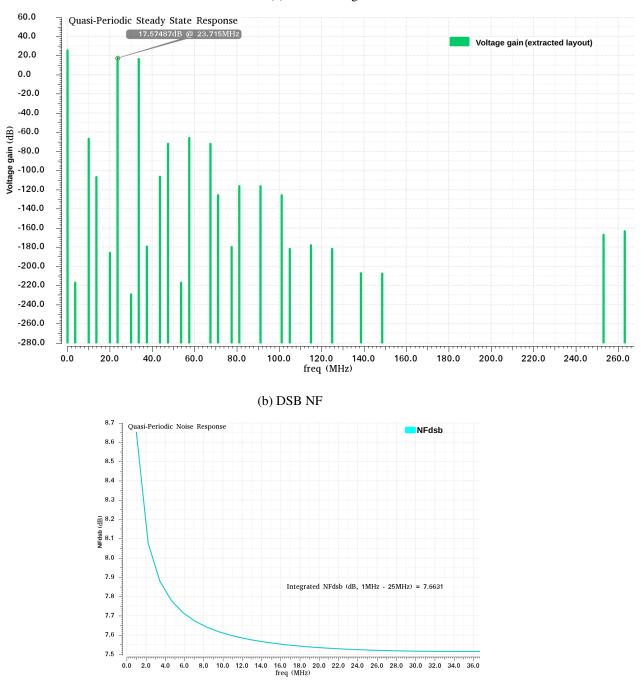

| Figure 6.8 DSB Noise Figure                                                   | 77  |

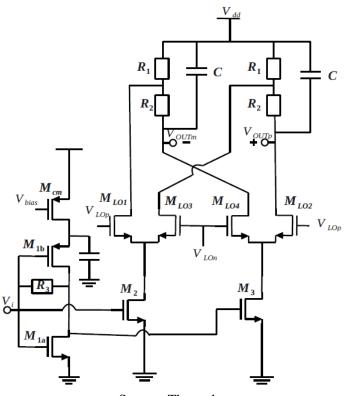

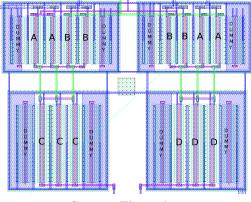

| Figure 6.9 Symmetric placement of LO switches(above) and transconductor(below |     |

|                                                                               |     |

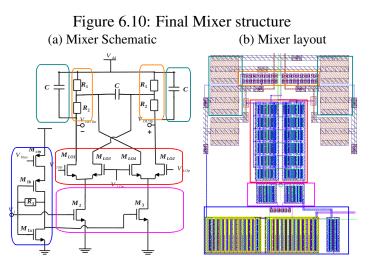

| Figure 6.10 Final Mixer structure                                             |     |

| Figure 6.11 Mixer Post-layout results                                         |     |

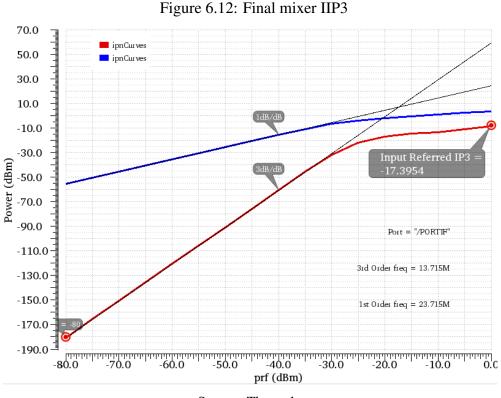

| Figure 6.12 Final mixer IIP3                                                  |     |

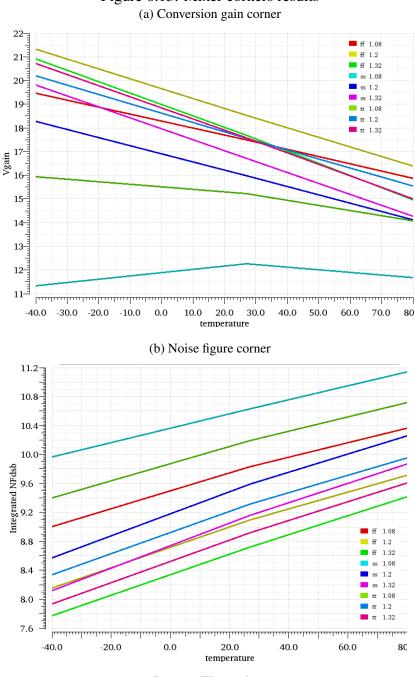

| Figure 6.13 Mixer corners results                                             |     |

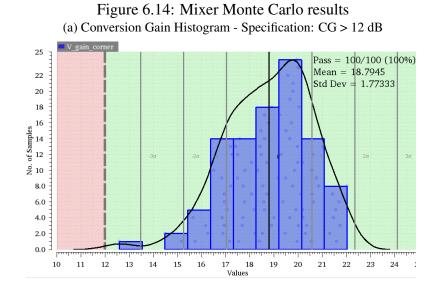

| Figure 6.14 Mixer Monte Carlo results                                         | 82  |

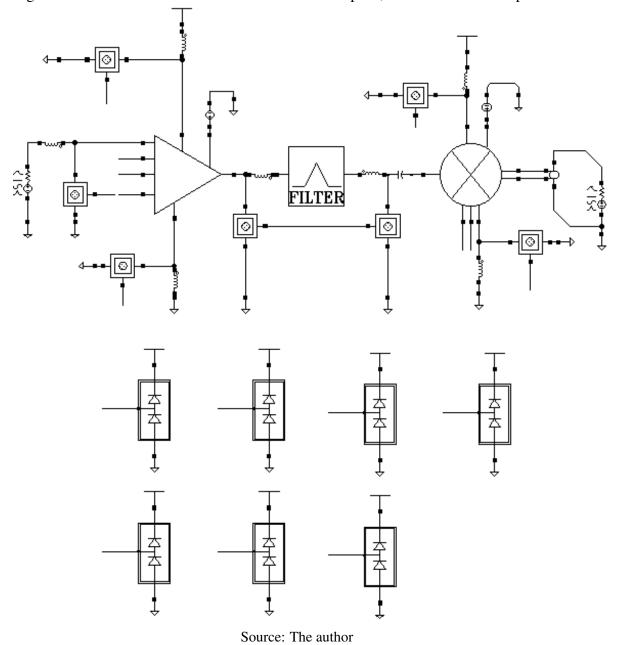

| Figure 7.1 Schematic of RF front end testbench with pads, bondwires and ESI   | )   |

| protection                                                                    |     |

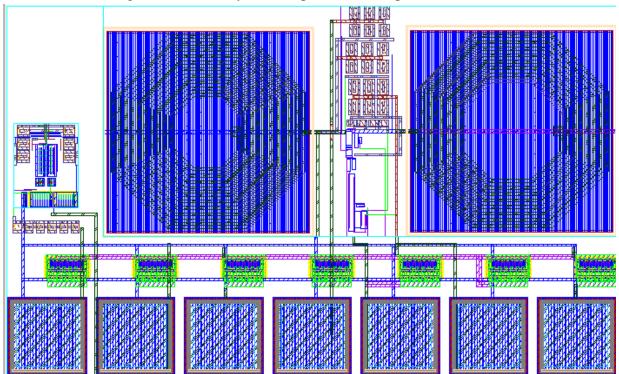

| Figure 7.2 Final layout with pads and ESD protection                          | 85  |

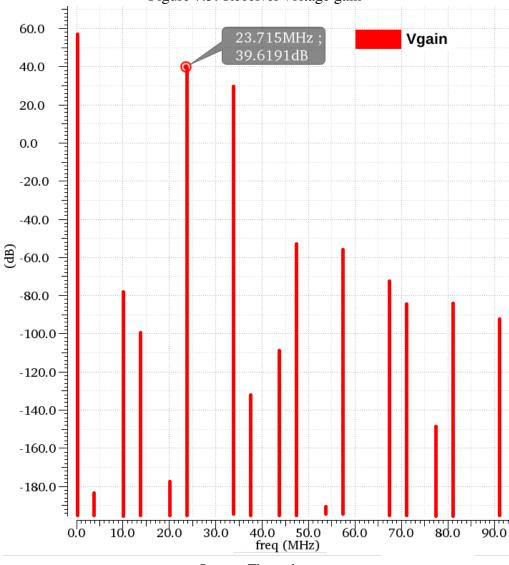

| Figure 7.3 Receiver voltage gain                                              |     |

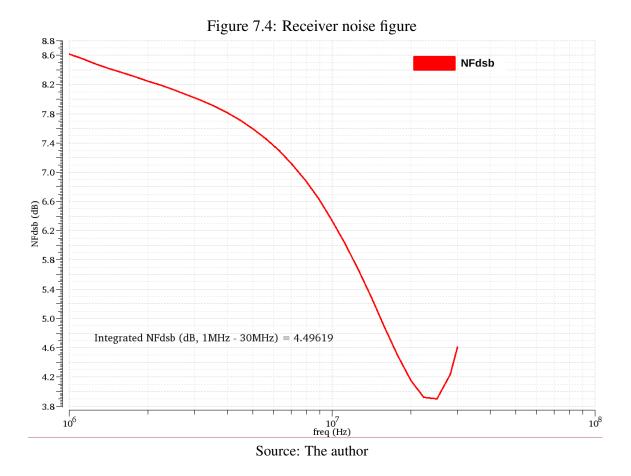

| Figure 7.4 Receiver noise figure                                              |     |

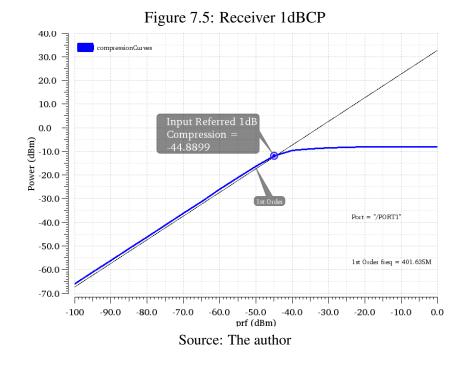

| Figure 7.5 Receiver 1dBCP.                                                    |     |

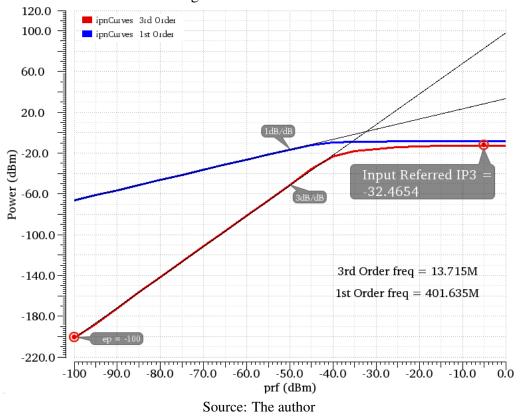

| Figure 7.6 Receiver IIP3                                                      |     |

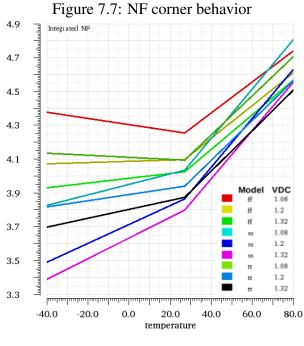

| Figure 7.7 NF corner behavior                                                 | 90  |

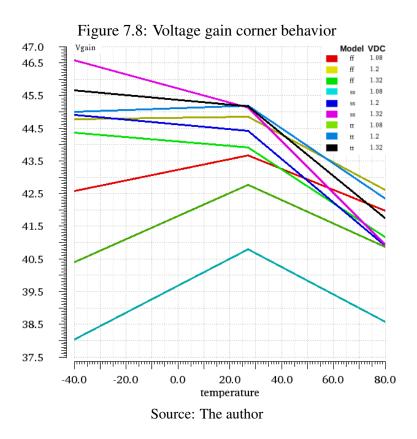

| Figure 7.8 Voltage gain corner behavior                                       | 90  |

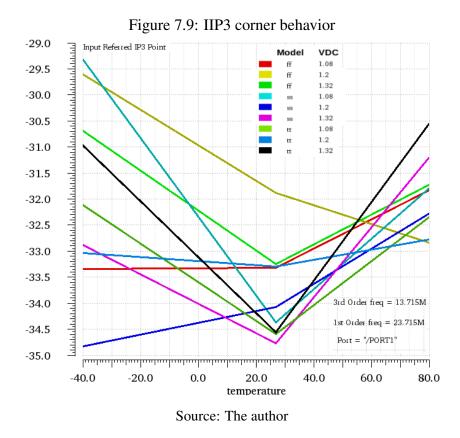

| Figure 7.9 IIP3 corner behavior                                               | 91  |

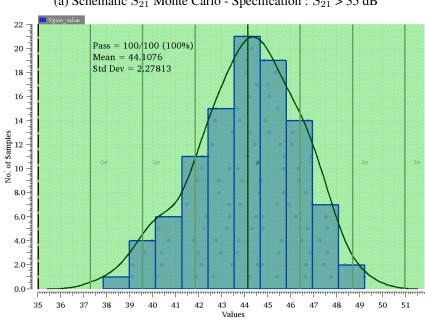

| Figure 7.10 Top-level gain MonteCarlo analysis                                | 92  |

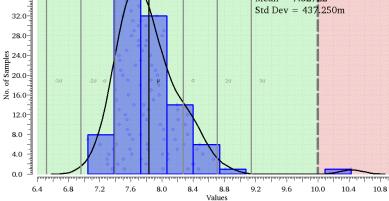

| Figure 7.11 Top-level NF MonteCarlo analysis                                  | 93  |

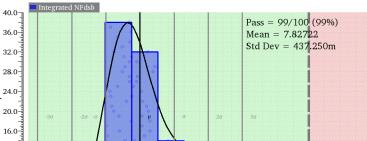

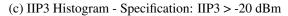

| Figure 7.12 Top-level <i>IIP</i> <sub>3</sub> MonteCarlo analysis             | 94  |

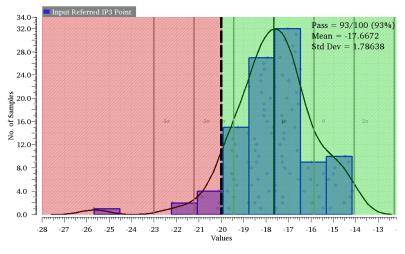

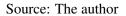

| Figure 8.1 Current Source with positive TC                                    | 97  |

| Figure A.1 Quadripole                                                         | 101 |

# LIST OF TABLES

| Table 1.1 | Orbit types                             | 15 |

|-----------|-----------------------------------------|----|

| Table 3.1 | Gain estimation for all receiver blocks |    |

| Table 3.2 | NF estimation for all receiver blocks   |    |

|           | Receiver specifications                 |    |

| Table 4.1 | LNA specifications                      |    |

| Table 4.2 | LNA Corner results                      | 55 |

|           | LNA Worst corner                        |    |

| Table 5.1 | Bandpass Filter specifications          | 61 |

|           | Bandpass Filter specifications          |    |

| Table 6.1 | Mixer specifications                    | 71 |

| Table 7.1 | Top-level corner results                |    |

| Table 7.2 | Top-Level MonteCarlo results            | 91 |

| Table 7.3 | Comparison of Published Receivers       | 95 |

|           |                                         |    |

# LIST OF ABBREVIATIONS AND ACRONYMS

| 1dBCP                                          | 1 dB Compression Point                                                                                                                                                         |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                                            | Analog-to-Digital Converter                                                                                                                                                    |

| ADS                                            | Advanced Design Software                                                                                                                                                       |

| AGC                                            | Available Gain Circles                                                                                                                                                         |

| ARGOS                                          | Advanced Research and Global Observation Satellite                                                                                                                             |

| BA                                             | Bahia                                                                                                                                                                          |

| BER                                            | Bit Error Rate                                                                                                                                                                 |

| BPSK                                           | Binary Phase Shift Keying                                                                                                                                                      |

| BW                                             | Bandwidth                                                                                                                                                                      |

| CBERS                                          | China Brazil Earth Resources Satellite                                                                                                                                         |

| CMOS                                           | Complementary Metal Oxide Semiconductor                                                                                                                                        |

| CONASAT                                        | Environmental Nano Satelite Constelation                                                                                                                                       |

| CTAT                                           | Complementary to the Absolute Temperature                                                                                                                                      |

|                                                |                                                                                                                                                                                |

| DC                                             | Direct Current                                                                                                                                                                 |

| DC<br>DCP                                      | Direct Current<br>Data Collector Platform                                                                                                                                      |

| -                                              |                                                                                                                                                                                |

| DCP                                            | Data Collector Platform                                                                                                                                                        |

| DCP<br>DSB                                     | Data Collector Platform<br>Double Side Band                                                                                                                                    |

| DCP<br>DSB<br>DSP                              | Data Collector Platform<br>Double Side Band<br>Digital Signal Processing                                                                                                       |

| DCP<br>DSB<br>DSP<br>ENOB                      | Data Collector Platform<br>Double Side Band<br>Digital Signal Processing<br>Effective Number Of Bits                                                                           |

| DCP<br>DSB<br>DSP<br>ENOB<br>ESD               | Data Collector Platform<br>Double Side Band<br>Digital Signal Processing<br>Effective Number Of Bits<br>Electrostatic Discharge                                                |

| DCP<br>DSB<br>DSP<br>ENOB<br>ESD<br>FoM        | Data Collector Platform<br>Double Side Band<br>Digital Signal Processing<br>Effective Number Of Bits<br>Electrostatic Discharge<br>Figure of Merit                             |

| DCP<br>DSB<br>DSP<br>ENOB<br>ESD<br>FoM<br>FSF | Data Collector Platform<br>Double Side Band<br>Digital Signal Processing<br>Effective Number Of Bits<br>Electrostatic Discharge<br>Figure of Merit<br>Frequency Scaling Factor |

| IBM                                                              | International Business Machines                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IF                                                               | Intermediary Frequency                                                                                                                                                                                                                                                                                                |

| IIP3                                                             | $3^{rd}$ order Input Intermodulation Products                                                                                                                                                                                                                                                                         |

| IM                                                               | Image Signal                                                                                                                                                                                                                                                                                                          |

| IM3                                                              | $3^{rd}$ order Intermodulation                                                                                                                                                                                                                                                                                        |

| INPE                                                             | National Institute of Spatial Researches                                                                                                                                                                                                                                                                              |

| INMET                                                            | National Institute of Meteorology                                                                                                                                                                                                                                                                                     |

| KHz                                                              | Kilo Hertz                                                                                                                                                                                                                                                                                                            |

| LNA                                                              | Low Noise Amplifier                                                                                                                                                                                                                                                                                                   |

| LEO                                                              | Low Earth Orbit                                                                                                                                                                                                                                                                                                       |

| LO                                                               | Local Oscillator                                                                                                                                                                                                                                                                                                      |

| MC                                                               | MonteCarlo                                                                                                                                                                                                                                                                                                            |

| MEO                                                              | Mid Earth Orbit                                                                                                                                                                                                                                                                                                       |

|                                                                  |                                                                                                                                                                                                                                                                                                                       |

| MHz                                                              | Mega Hertz                                                                                                                                                                                                                                                                                                            |

| MHz<br>MIM                                                       | Mega Hertz<br>Metal-Insulator-Metal capacitors                                                                                                                                                                                                                                                                        |

|                                                                  | -                                                                                                                                                                                                                                                                                                                     |

| MIM                                                              | Metal-Insulator-Metal capacitors                                                                                                                                                                                                                                                                                      |

| MIM<br>MOSFET                                                    | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor                                                                                                                                                                                                                                 |

| MIM<br>MOSFET<br>NF                                              | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure                                                                                                                                                                                                                 |

| MIM<br>MOSFET<br>NF<br>NMOS                                      | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure<br>N-type metal-oxide-semiconductor                                                                                                                                                                             |

| MIM<br>MOSFET<br>NF<br>NMOS<br>PAC                               | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure<br>N-type metal-oxide-semiconductor<br>Periodic Alternated Current                                                                                                                                              |

| MIM<br>MOSFET<br>NF<br>NMOS<br>PAC<br>PMOS                       | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure<br>N-type metal-oxide-semiconductor<br>Periodic Alternated Current<br>P-type metal-oxide-semiconductor                                                                                                          |

| MIM<br>MOSFET<br>NF<br>NMOS<br>PAC<br>PMOS<br>PSS                | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure<br>N-type metal-oxide-semiconductor<br>Periodic Alternated Current<br>P-type metal-oxide-semiconductor<br>Periodic Steady State                                                                                 |

| MIM<br>MOSFET<br>NF<br>NMOS<br>PAC<br>PMOS<br>PSS<br>PTAT        | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure<br>N-type metal-oxide-semiconductor<br>Periodic Alternated Current<br>P-type metal-oxide-semiconductor<br>Periodic Steady State<br>Proportional to the Absolute Temperature                                     |

| MIM<br>MOSFET<br>NF<br>NMOS<br>PAC<br>PMOS<br>PSS<br>PTAT<br>PVT | Metal-Insulator-Metal capacitors<br>Metal-Oxide-Semiconductor Field Effect Transistor<br>Noise Figure<br>N-type metal-oxide-semiconductor<br>Periodic Alternated Current<br>P-type metal-oxide-semiconductor<br>Periodic Steady State<br>Proportional to the Absolute Temperature<br>Process, Voltage and Temperature |

| RX    | Receiver                                      |

|-------|-----------------------------------------------|

| SBCDA | Brazilian Environmental Data Collector System |

| SC    | Santa Catarina                                |

| SCD-1 | Data Collector Satellite - 1                  |

| SINDA | Environmental Data Integrated System          |

| SNR   | Signal-to-Noise Ratio                         |

| TC    | Temperature Coefficient                       |

| UFRGS | Federal University of Rio Grande do Sul       |

| UHF   | Ultra High Frequency                          |

| VSWR  | Voltage Standing Wave Ratio                   |

|       |                                               |

# CONTENTS

| 1 INTRODUCTION                         |    |

|----------------------------------------|----|

| 1.1 SBCDA                              |    |

| 1.2 Transponder                        |    |

| 1.3 Thesis Organization                |    |

| 2 RECEIVER TOPOLOGIES AND STATE-OF-ART |    |

| 2.1 Receiver topologies                |    |

| 2.2 State-of-art                       |    |

| 3 SUPERHETERODYNE RECEIVER             |    |

| 3.1 Receiver specifications            |    |

| 3.1.1 Receiver Gain                    | 27 |

| 3.1.2 Noise Figure                     |    |

| 3.1.3 Linearity                        |    |

| 4 LOW NOISE AMPLIFIER                  |    |

| 4.1 Schematic project                  |    |

| 4.1.1 Common source Cascode            |    |

| 4.1.2 Output Matching Network          |    |

| 4.1.3 Input matching network           |    |

| 4.1.4 Nominal results                  |    |

| 4.2 Layout                             |    |

| 4.3 Post-layout simulations            |    |

| 4.4 Corners Analysis                   |    |

| 4.4.1 Temperature coefficient          |    |

| 4.5 MonteCarlo Analysis                |    |

| 4.6 Figure of Merit                    |    |

| 5 IMAGE REJECTION FILTER               |    |

| 6 MIXER                                |    |

| 6.1 Introduction                       |    |

| 6.2 Mixer topologies                   |    |

| 6.3 Schematic project                  |    |

| 6.4 Layout                             |    |

| 6.4.1 Post-layout results              |    |

| 6.5 Robustness Analysis                | 80 |

| 6.5.1 Monte carlo                      |    |

| 7 TOP-LEVEL SIMULATIONS                |    |

| 7.1 Nominal simulation                 |    |

| 7.2 Corner simulation                  |    |

| 7.3 Monte Carlo simulation             |    |

| 7.4 Receivers comparison               |    |

| 8 CONCLUSION                           |    |

| 8.1 Future Work                        |    |

| REFERENCES                             |    |

| APPENDIX A — SCATTERING PARAMETERS     |    |

### **1 INTRODUCTION**

It is an industry demand to produce innovations on existent products with the advance of technology. In general, the new structures to be proposed aim to miniaturize even more the electronic circuits, allowing a higher integration between them, improving its coupling efficiency and achieving better frequency response for a given passing band.

In the case of telecommunications systems, the development of a robust and reliable integrated system becomes essential to guarantee that all data or information is received and re-transmitted correctly. In this way, this work has as primary objective the development of a Radio-Frequency(RF) integrated front-end for Brazilian Environmental Data Collect System Satellite (SBCDA) using a 130 nm technology provided by IBM.

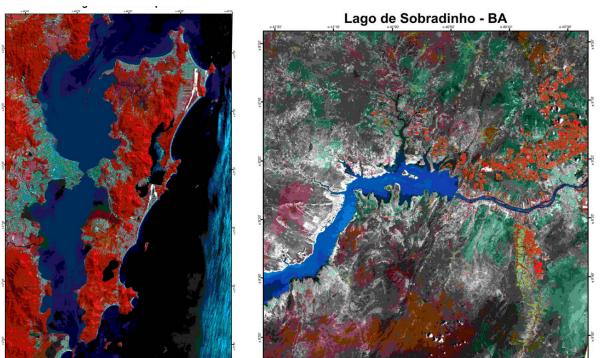

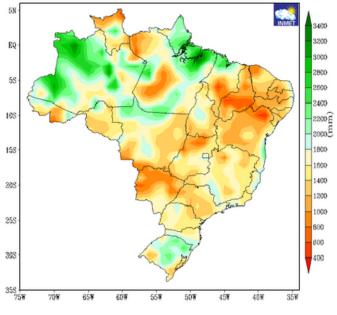

Figure 1.1: Examples of application of Satellite images (a) City growth of Florianópolis- SC (b) Hidrographic basin monitoring in Sobradinho-BA

Source: INPE

This system has the objective to collect data for applications like climatic and weather forecast, pollution control on cities, firefighting, oceanography, wildlife monitoring, cities growth, and others. Figure 1.1 (a) shows an example of the expansion of the city of Florianópolis - Santa Catarina (SC), marked in green, with the relief area or vegetation that has not yet been occupied, marked in red. Figure 1.1 (b) exemplifies a monitoring result of the São Francisco river, marked in blue, in the city of Sobradinho - Bahia (BA) which compounds an essential hydrographic basin in the Brazilian Northeast.

### 1.1 SBCDA

Initially, through a partnership between the governments of China and Brazil, it was launched the CBERS (China-Brazil Earth Resources Satellite) program to develop a satellite technology that could make feasible remote sensing and monitoring of large depopulated areas and with extensive agricultural and environmental potential that both countries have.

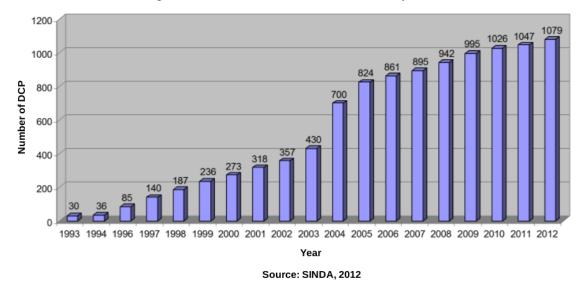

Figure 1.2: Number of DCP all over the years

On February of 1993, it was launched the first data collector satellite (SCD-1) to accomplish this objective and started to install some data collector platforms (DCP) in the country. Altogether six satellites have already been launched, due to the lifetime of each satellite, but all of them have the same final objective: the environmental data collection. (SCD-1..., 2018)

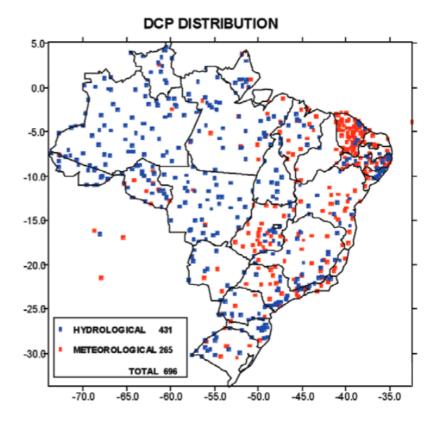

The DCPs might provide hydrological and meteorological information of the country. The number of installed DCPs is continually increasing, as showed in figure 1.2, but due to lack of maintenance, not all installed DCP's are active. Approximately 54% of the total number of DCPs are operating, and they divide themselves between hydrological ( $\approx$  43%) and meteorological ( $\approx$  38%) platforms. (LIMA; JOTHA; BIONDI, 2011)

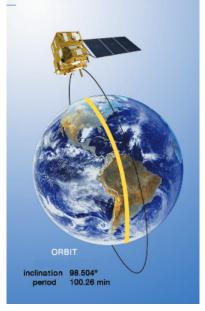

The satellites can operate on different orbits depending of their altitude (LEO -Low Earth Orbits, MEO - Mid Earth Orbits, GEO - Geostationary Earth Orbits, and HEO - High Earth Orbit). Table 1.1 shows that low Earth orbit satellites operate in the range of 150 Km to 900 Km of altitude, and suit better for weather/climatic applications using

| Table 1.1: Orbit types       |                                                     |                                      |                |             |

|------------------------------|-----------------------------------------------------|--------------------------------------|----------------|-------------|

| Orbit Type                   | Mission                                             | Altitude                             | Period         | Tilt        |

| LEO                          |                                                     |                                      |                |             |

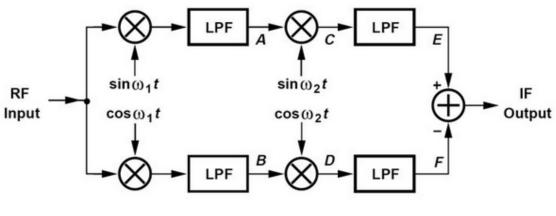

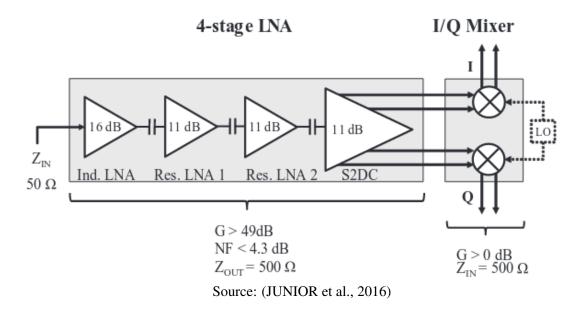

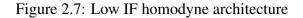

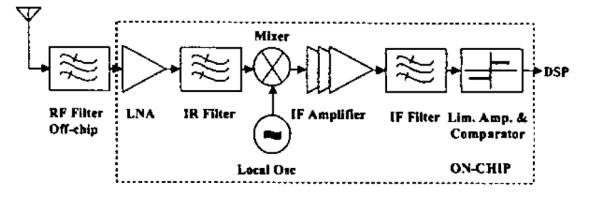

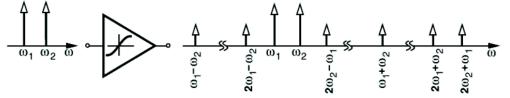

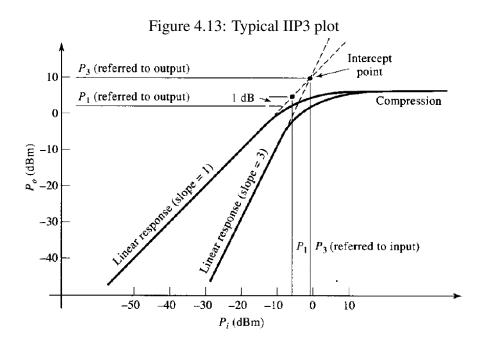

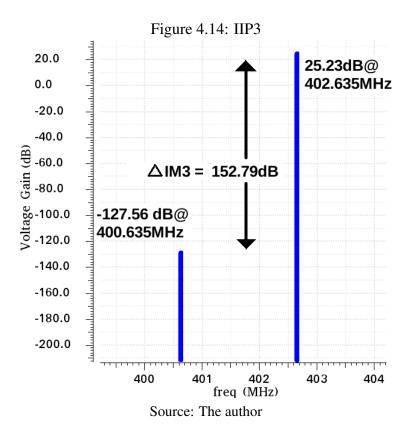

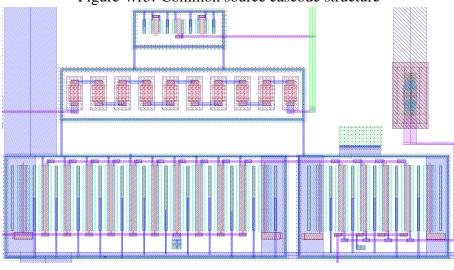

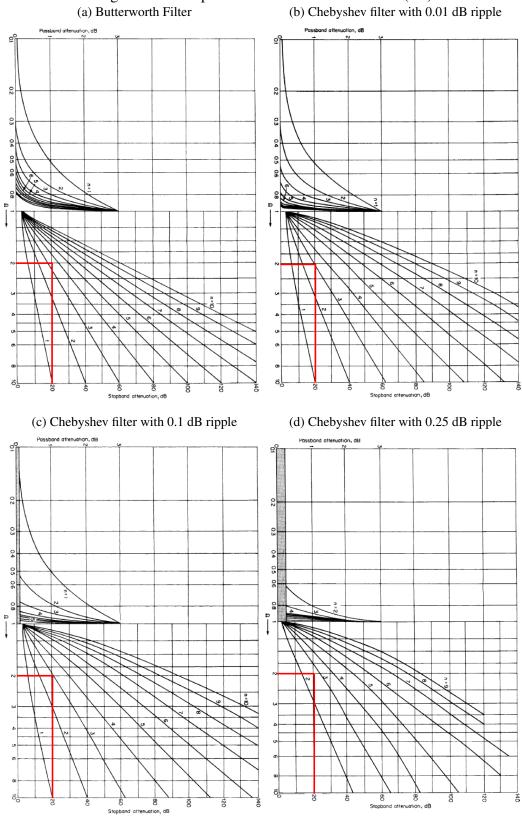

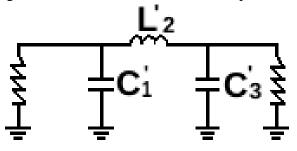

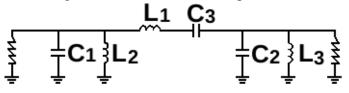

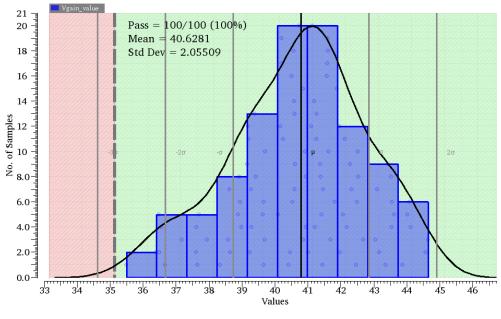

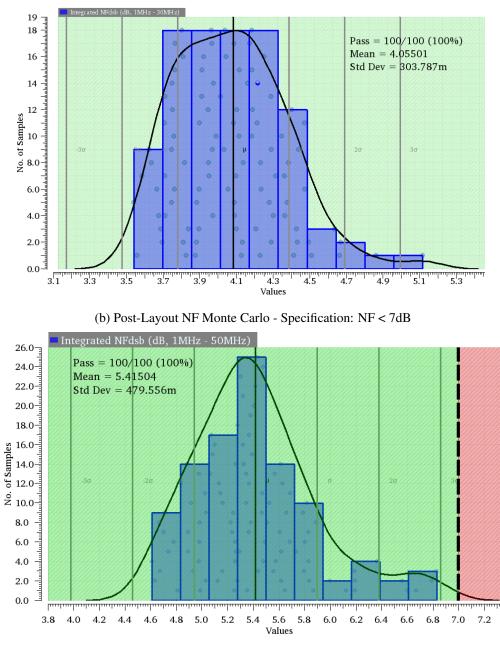

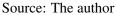

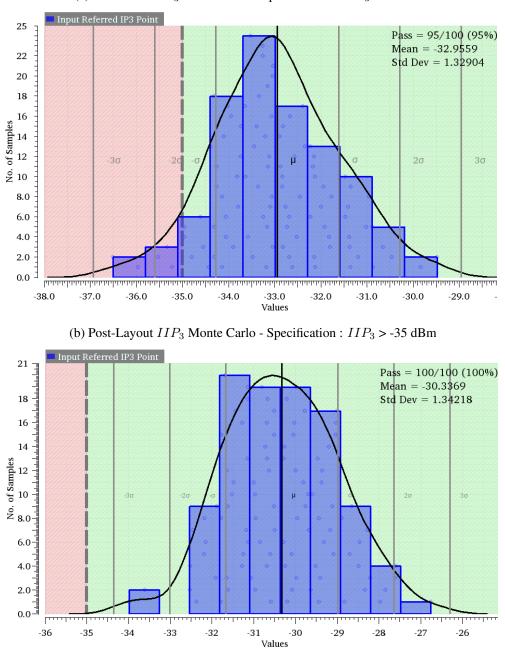

| Polar<br>sun-synchronous     | Remote sensing/<br>weather                          | 150-900 Km                           | 98-104<br>min  | 98°         |