# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

PEDRO HENRIQUE EXENBERGER BECKER

# Function Reuse on a Multi-Core VLIW Soft-Core Processor

Work presented in partial fulfillment of the requirements for the degree of Bachelor in Computer Engineering

Advisor: Prof. Dr. Antonio Carlos Schneider Beck Coadvisor: Anderson Luiz Sartor

Porto Alegre January 2018

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Graduação: Prof. Vladimir Pinheiro do Nascimento Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do Curso de Engenharia de Computação: Prof. Renato Ventura Henriques Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Navegar é preciso, viver não é preciso." — Fernando Pessoa

# ACKNOWLEDGMENTS

If I had to do this work without any help, I would probably need a couple more years and much patience to handle a very lonely and stressful life. Fortunately, I could count on great and supportive people to develop this work, whom I now want to acknowledge.

First of all, I would like to thank my parents, Raquel and Denis, for educating and supporting me ever since I recall. Also, for my advisor Antonio and his valuable guidance, and my colleagues from the Embedded Systems Laboratory of UFRGS, especially Anderson (my co-advisor) and Marcelo, whom I consulted incessantly. Furthermore, I would like to thank my classmates, whom I found to be a free and precious source of help. Finally, I would like to thank my lovely girlfriend Marina, for her every-day support and kindness.

# ABSTRACT

Modern processors contain several specific hardware modules and multiple cores to ensure performance on a wide range of applications. When a project needs a processor regarding time to market and architecture customization, FPGAs are often used as the implementation platform. However, for FPGA-based processors, those modules may not fit in the target device, because of FPGA's resource constraints, so their functionalities must be mapped into the much slower software domain. In the same way, we exploit the fact that logic-driven designs usually underuse available BRAMs, memory blocks embedded in FPGAs. As an alternative, we propose a low-cost hardware-based function reuse mechanism, which can optimize software execution. This is accomplished by saving the inputs and outputs of the most recurring functions in a BRAM-based reuse table, so they can be reused in the next function calls, skipping actual execution, and improving performance. The technique was implemented in HDL and was coupled to a 4-issue VLIW processor. As a case study, we optimized six applications that use a soft-float library to emulate a floating-point unit in software, achieving 1.23x of geomean speedup. The analysis was extended to a multi-core environment, which was done with a simulator built for this work, where we observed the benefits of sharing the reuse table among similar applications running with different inputs. Sharing the reuse table proven promising, for example, leading one application to 1.9x speedup instead of 1.25x if the reuse table was not shared. Also, we present how the mechanism can be easily enhanced, so function reuse embraces the concept of approximate computing, increasing the scenarios where its use is beneficial and achieving 1.52x speedup in single-core image filter application at the cost of output quality.

Keywords: FPGAs. Soft-core processors. Function reuse. Multi-core systems.

#### Reuso de Funções em Processadores Soft-Cores VLIW Multi-Núcleo

### **RESUMO**

Processadores modernos contém vários módulos específicos e multiplos núcleos para garantir desempenho em uma variedade de aplicações. Quando um projeto de processador depende de time-to-market e customização de arquitetura, FPGAS são frequentemente utilizados como a plataforma para a implementação. Entretando, para processadores baseados em FPGAs, esses módulos podem exceder a capacidade do dispositivo alvo, dadas as limitações de recursos dos FPGAs, de maneira que algumas funcionalidades precisam ser mapeadas para o domínio de software, mais lento. Da mesma forma, exploramos o fato de que projetos lógicos geralmente sub-utilizam a quantidade disponível de BRAMs, blocos de memória embarcados nos FPGAs. Como alternativa, propomos um mecanismo de reúso em hardware de baixo custo que pode otimizar a execução de programas. Isso é obtido ao salvarmos os parâmetros de entrada e valores de retorno de funções recorrentes, em uma tabela de reúso implementada em BRAM de maneira que as funções possam ser reutilizadas em chamadas futuras, evitando a sua reexecução, e acelerando a aplicação. A técnica foi implementada em linguagem de descrição de hardware e adicionada à um processador VLIW 4-issue. Como estudo de caso, otimizamos seis aplicações que usam uma biblioteca soft-float para simular uma unidade de ponto-flutuante em software, atingindo 1.23x de aceleração geométrica média. A análise foi estendida para um ambiente multinúcleo, o que foi feito com um simulador construído para este trabalho, onde observou-se os benefícios de compartilhar a tabela de reúso entre aplicações similares executando sobre dados diferentes. Compartilhar a tabela se mostrou promissor, por exemplo, levando uma das aplicações à ganhos de 1.9x em contra partida de 1.25x se a tabela não tivesse sido compartilhada. Além disso, apresentamos como o mecanismo pode ser facilmente melhorado, de maneira que o reúso de funções faça uso da computação aproximativa, aumentando o número de cenários onde o reúso de funções é benéfico e atingindo 1.52x de aceleração em uma aplicação de filtro de imagem, ao custo de qualidade.

**Palavras-chave:** FPGAs. Processadores soft-core. Reúso de funções. Sistemas multinúcleo.

# LIST OF ABBREVIATIONS AND ACRONYMS

- ALU Arithmetic and Logic Unit.

- ASIC Application Specific Integrated Circuit.

- **BRAM** Block Random Access Memories.

- CLB Configurable Logic Block.

- CPU Central Processing Unit.

- **DSP** Digital Signal Processing.

#### FORMOSA FunctiOn Reuse MulticOre SimulAtor.

- **FP** Floating-Point.

- **FPGA** Field-Programmable Gate Array.

- **FPU** Floating-Point Unit.

- FU Functional Unit.

- GPP General Purpose Processor.

- GPU Graphics Processing Unit.

- HDL Hardware Description Language.

- HLS High-Level Synthesis.

- **ILP** Instruction-Level Parallelism.

- **IO** Input/Output.

- **IOB** Input/Output Block.

- **IP** Intellectual Property.

- ISA Instruction-Set Architecture.

- LSB Least Significant Bit.

- LUT Look-Up Table.

- MPSoC Multiprocessor System on Chip.

- **RT** Reuse Table.

- RU Reuse Unit.

- **SMT** Simultaneous Multithreading.

- VLIW Very Long Instruction Word.

# LIST OF FIGURES

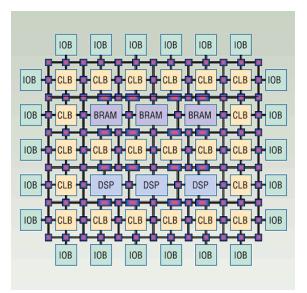

| Figure 2.1  | A typical FPGA Architecture.                                            | .14 |

|-------------|-------------------------------------------------------------------------|-----|

| Figure 2.2  | ILP Exploitation by VLIW and Superscalar Architectures.                 | .17 |

| Figure 2.3  | A four-core Intel i7 4770K processor.                                   | .18 |

| Figure 2.4  | Example of a Reusable Code Snippet                                      | .19 |

| Figure 2.5  | Example of a Reusable Function Result.                                  | .20 |

| Figure 2.6  | Example of a Reusable Function with Approximate Result                  | .21 |

| Figure 4.1  | A Reuse Table entry                                                     | .27 |

|             | The Functioning of the Function Reuse Unit.                             |     |

| Figure 4.3  | Organization of a 4-issue $\rho$ -VEX with a Reuse Unit                 | .28 |

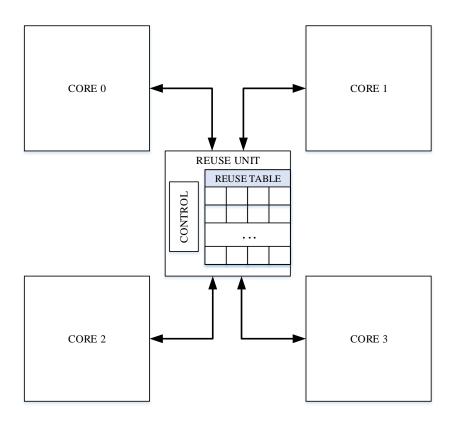

| Figure 4.4  | A Multi-Core Environment with a Shared Reuse Unit                       | .31 |

| Figure 4.5  | Example of a <i>Reuse Trace</i> from the Reuse Unit                     | .32 |

| Figure 4.6  | A Reuse Table entry that supports precise and approximate modes         | .36 |

| Figure 5.1  | Reusability of case study functions                                     | .39 |

| Figure 5.2  | Speedup for different Reuse Table sizes compared to the baseline        | .39 |

| Figure 5.3  | Speedup Scalability as the Reuse Table grows.                           | .40 |

| Figure 5.4  | Measuring Impacts of Sharing the Reuse Table from a Multi-core Scenario | .42 |

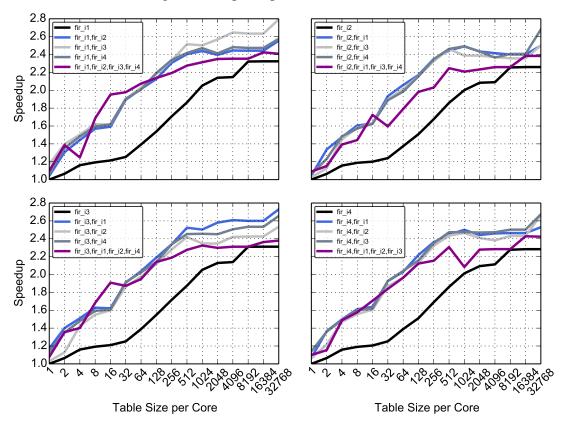

| Figure 5.5  | Speedup for the fir benchmark                                           | .44 |

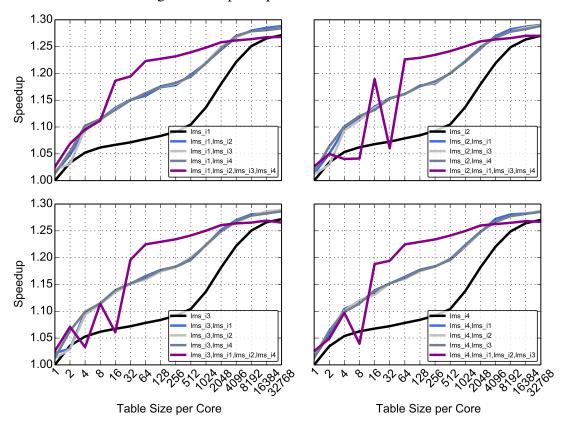

| Figure 5.6  | Speedup for the lms benchmark.                                          | .45 |

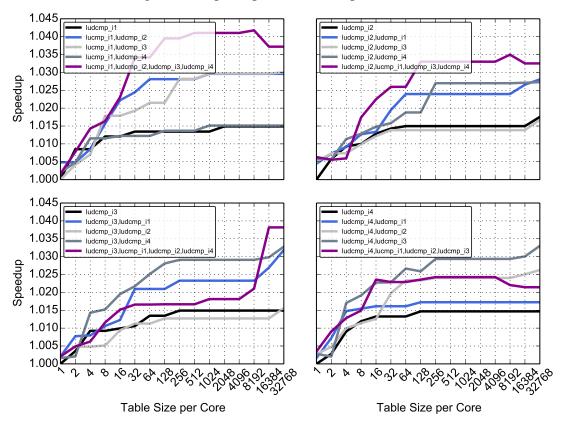

| Figure 5.7  | Speedup for the ludcmp benchmark.                                       | .46 |

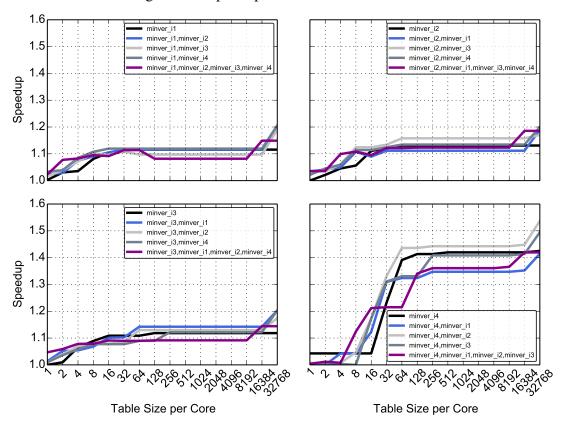

| Figure 5.8  | Speedup for the minver benchmark.                                       | .47 |

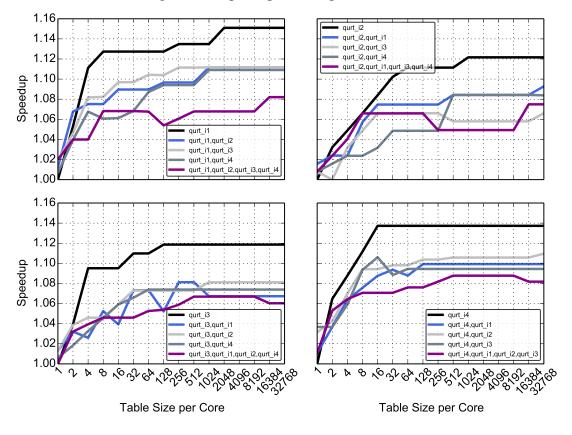

| Figure 5.9  | Speedup for the qurt benchmark                                          | .48 |

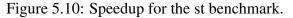

| Figure 5.10 | O Speedup for the st benchmark.                                         | .48 |

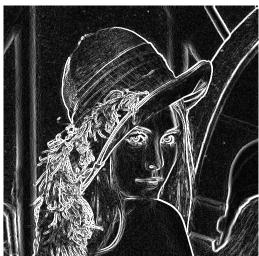

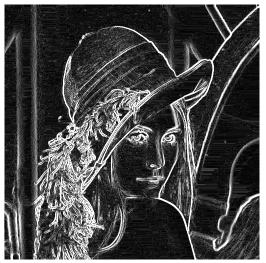

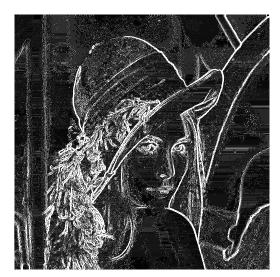

| Figure 5.1  | Speedup for approximate sobel image filter.                             | .50 |

| Figure 5.12 | 2 The approximate <i>sobel</i> filter dropping 4 Least Significant Bits | .51 |

|             |                                                                         |     |

# LIST OF TABLES

| Table 1.1 | Resource Utilization of Three Soft-Core Designs      | 12 |

|-----------|------------------------------------------------------|----|

| Table 5.1 | Investigated Simulation Scenarios for a Benchmark B  | 41 |

| Table 5.2 | Usage of Resources For Different Designs and Targets | 52 |

# CONTENTS

| 1 INTRODUCTION                                                        | 11 |

|-----------------------------------------------------------------------|----|

| 2 BACKGROUND                                                          | 14 |

| 2.1 Field-Programmable Gate Array                                     | 14 |

| 2.1.1 Block Random Access Memories                                    | 15 |

| 2.1.2 Soft-Core Processors                                            | 15 |

| 2.2 Modern Architectures                                              | 16 |

| 2.2.1 Very Long Instruction Word Processors                           | 16 |

| 2.2.2 Multi-Core Processors                                           | 18 |

| 2.2.3 Multiprocessor System on Chip                                   | 18 |

| 2.3 Reuse                                                             | 19 |

| 2.3.1 General Reuse                                                   | 19 |

| 2.3.2 Function Reuse                                                  |    |

| 2.3.3 Approximate Function Reuse                                      | 20 |

| 3 RELATED WORK                                                        | 22 |

| 3.1 Reuse in Single-Core Environments                                 | 22 |

| 3.2 Reuse in Multi-Core Environments                                  | 23 |

| 3.3 Approximate Reuse                                                 | 24 |

| 3.4 Work Contribuitions                                               |    |

| 4 IMPLEMENTATION AND METHODOLOGY                                      | 26 |

| 4.1 Baseline Processor                                                | 26 |

| 4.2 Implementing the Function Reuse Unit in a Single-Core             | 27 |

| 4.2.1 Reuse Mechanism                                                 |    |

| 4.3 Function Reuse in Multi-Core Environments                         | 30 |

| 4.3.1 Multi-Core Function Reuse Simulator                             | 32 |

| 4.4 Enhancing Function Reuse Possibilities with Approximate Computing | 34 |

| 4.4.1 Modifications to Support Approximate Reuse                      | 35 |

| 4.4.2 Modifying Software to Analyze Approximate Function Reuse        | 36 |

| 5 RESULTS                                                             | 37 |

| 5.1 Function Reuse in Single-Core Environments                        | 37 |

| 5.1.1 Experimental Methodology                                        | 37 |

| 5.1.2 Case Study - Floating-Point                                     | 37 |

| 5.1.3 Reusability                                                     | 38 |

| 5.1.4 Performance                                                     | 38 |

| 5.2 Function Reuse in Multi-Core Environments                         | 40 |

| 5.2.1 Experimental Methodology                                        | 40 |

| 5.2.2 Inputs Definition                                               | 43 |

| 5.2.3 Performance                                                     |    |

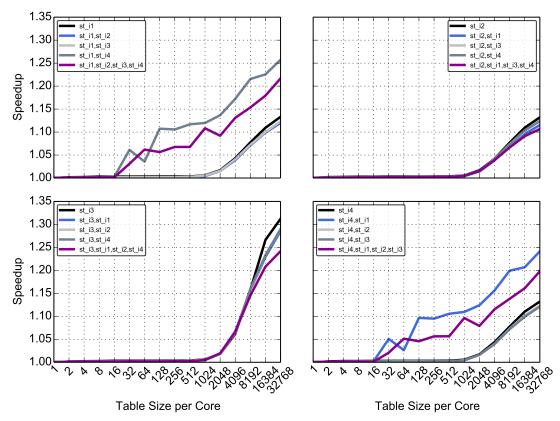

| 5.3 Using Approximate Computing to Function Reuse                     | 49 |

| 5.3.1 Experimental Methodology                                        |    |

| 5.3.2 Performance                                                     |    |

| 5.4 Resource Usage                                                    | 51 |

| 6 CONCLUSIONS AND FUTURE WORK                                         | 54 |

| 6.1 Conclusions                                                       | 54 |

| 6.2 Work Limitations                                                  |    |

| 6.3 Future Work                                                       | 55 |

| REFERENCES                                                            |    |

| APPENDIX A — PROJECT DESCRIPTION (TG1)                                | 61 |

# **1 INTRODUCTION**

The implementation of processors in Field-Programmable Gate Arrays (FPGAs), also known as soft-core processors, provides known benefits when designing a computational system. For example, the reprogrammability of FPGAs guarantees good time-tomarket, fast architecture customization and integration of hardware accelerators (either by writing new modules or using off-the-shelf components), as well as obsolescence mitigation since the hardware description can be easily ported to the latest FPGAs (FLETCHER, 2005). These processors have gained space in solutions to specific purpose problems: by using modules that can be configured at synthesis time, they combine performance gains in dedicated tasks with the ease of high-level programming for end users.

At the same time, nowadays systems require high performance for a wide range of applications, which increases the demand for logic resources. The use of multi-core processors, e.g., ARM Cortex-A53 (BOPPANA et al., 2015), together with dedicated hard-ware like Floating-Point Units (FPUs), security and cryptography modules, and coders / decoders for multimedia, are commonly adopted in any modern design, such as in Multi-processor Systems on Chip (MPSoCs) (WOLF; JERRAYA; MARTIN, 2008). However, FPGA designs require more area and energy compared to Application Specific Integrated Circuits (ASICs) (KUON; ROSE, 2007). Therefore, in many cases, the resources available in an FPGA will be the limiting factor. In case specialized hardware can't fit inside the FPGA, some of its features must be mapped into the software domain, which is significantly slower.

In addition, Block Random Access Memories (BRAMs) are often underutilized when implementing such complex logic driven designs in FPGAs. Table 1.1 shows the utilization of Look-Up Tables (LUTs), Registers and BRAMs of three soft-core processors (arranged in order of complexity) implemented in a Virtex-5 xc5vlx110t. As one can observe, for complex soft-core processors, such as the OpenSparc T1 (a single-issue, six-stage pipeline supporting up to four concurrent threads), BRAMs are not utilized in the same proportion as registers and LUTs. This comes from the observation that BRAMs usually present a limited number of ports (in most cases, 2 for reading and 1 for writing), which forbids many possible uses for them, such as the register file in multiple-issue processors, which need multiple read ports to properly feed all the available functional units (XILINX; INC, 2016). Hence, BRAMs are usually used only to implement moderate size caches, common in the scope of soft-cores running in embedded environments.

| Design       |     | % Slice Register | % BRAM |

|--------------|-----|------------------|--------|

| OpenRisc1200 | 5%  | 2%               | 7%     |

| Leon 3       | 27% | 16%              | 15%    |

| OpenSparc T1 | 88% | 56%              | 40%    |

Table 1.1: Resource Utilization of Three Soft-Core Designs

Considering this scenario, this work proposes a function reuse-based technique that leverages those idle BRAMs, resulting in a low-cost and generic hardware solution to speed up specific software parts without the need for implementing dedicated hard-ware components. Each time a function executes, its results are dynamically stored in a BRAM Reuse Table (RT) and, when the same function with the same input arguments is called again, the output of this function can be directly fetched from the RT, avoiding re-calculation and improving performance.

Additionally, considering the consolidation of multi-core environments, we extend our reuse concept within a soft-core multi-processor design, where it is possible to share the RT among cores. Thus, programs that are simultaneously running on the soft-core can all update the RT as they calculate function results, and fetch results calculated by other processes from the RT. Since multi-thread programs (or multiples instances of a program) run over the same code, we expect that they benefit from such arrangement, increasing the reuse possibilities. At the same time, the introduction of a shared RT is cheaper than if we would introduce a dedicated RT for each core, as we have a single and centralized (instead of replicated) control logic. By using this approach, we can accelerate multiple cores while proportionally reducing the impact of an RT in the FPGA design.

Going one step further, we also show that, by tuning how the BRAM RT is accessed, it is possible to gracefully switch, by using the same hardware structure, from precise to approximate reuse, which can significantly increase reuse rates and performance at the expense of output quality in some specific classes of applications. This reuse mechanism that uses BRAMs and is configurable for both precise and approximate modes can be easily used to optimize the execution of any given software library, avoiding its hardware implementation counterpart and resulting in significant savings in design time, LUTs and registers.

We evaluate the technique by implementing it in a complex 4-issue Very Long Instruction Word (VLIW) soft-core at Hardware Description Language (HDL). We investigate six applications that process a significant amount of Floating-Point (FP) operations in different scenarios, including one where implementing a hardware FPU prevents the addition of any new dedicated hardware because of the limited amount of resources available. In this case, we apply our idea to optimize a soft-float library that uses integer units to emulate double precision FP operations that would otherwise have to be implemented in hardware. Then, with software-based simulations, we consider the execution of multiple instances of each of these benchmarks, running with different inputs, sharing the RT to optimize the same soft-float library. Over this, we can analyze the space exploration benefits in performance and area when using the reuse mechanism in a thread-collaborative way. In addition, we evaluate an image processing filter software that tolerates a certain error level, so we can switch to the approximate mode to increase reuse rates and, therefore, improve performance at the cost of quality.

For the single-core scenario, we show that an average speedup of 1.23x in the precise case and 1.52x in the approximate one is achieved when considering an RT that fits in five different test targets. For targets with larger BRAMs, this number can be as high as 1.38x and 2.97x, respectively. Meanwhile, the usage of slice registers and slice LUTs by our reuse mechanism increases by 17% and 3% respectively, compared to 140% and 48% for an FPU or 11% and 13% for a dedicated sobel filter. It is important to note that our mechanism is generic, so its cost in registers and LUTs is fixed regardless the number of different applications that it can optimize. When considering a multi-core system with a shared RT, we present cases where improvement goes from 1.25x to 1.9x, keeping the total amount of BRAM used. When BRAM is also a scarce FPGA resource, we show that our multi-core reuse approach can equate the performance of the single-core using less BRAM.

The upcoming sections are organized as follows. We present background in Chapter 2. Related work about different reuse approaches is covered in Chapter 3. Chapter 4 discusses the Implementation and Methodology of the work. Results are presented and discussed in Section 5. Section 6 states Conclusions and Future Work.

# **2 BACKGROUND**

In the upcoming sections, we introduce some important concepts that support our study. They will be briefly defined together with its role in this work.

## 2.1 Field-Programmable Gate Array

FPGAs emerged as an intermediary solution between processors and ASICs, providing better control over the hardware implementation compared to processors, and more flexibility, testability, and time-to-market over ASIC. With its differentials, the FPGA market has reached about USD 6.36 billion by the year of 2015 with continuous growth expectation (Research Grand View, 2016). Thereby, this research is based on a technology that is already established and has a solid market.

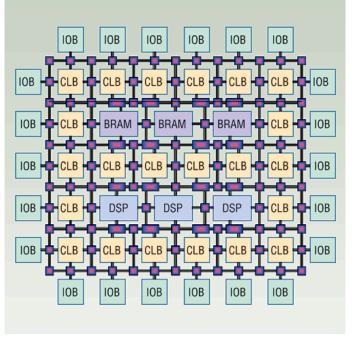

FPGAs gained market share with its uniqueness: the idea of a reconfigurable circuit. Figure 2.1 depicts a traditional FPGA architecture. It is an array of Configurable Logic Blocks (CLBs), routing channels, BRAMs and Digital Signal Processing (DSP) units. The reconfigurability is a result of the programmability of the CLBs and routing channels, as we present below.

A CLB is the fundamental component on the FPGA architecture. Inside each

Figure 2.1: A typical FPGA Architecture.

Source: (BUELL et al., 2007)

CLB, there are a set of small tables (LUTs). With these tables, the FPGA can implement logical functions over the CLB inputs (using the LUTs as a truth-table). Thus, combining many CLBs through the routing channels can lead to implementations of very complex logical functions. Moreover, the LUTs can be used as memory elements for small data amount. Since both CLB and routing channels are programmable, the circuit that an FPGA implements can be changed by reprogramming those components.

Aside CLBs and routing channels, FPGA also has Input/Output Blocks (IOBs), to connect the FPGA with the outside world, and embedded blocks. Traditional architectures contain both embedded DSPs units, to speed up costly operations that are implemented by cascades of truth-tables (e.g., multiplications), and BRAMs, which will be detailed in the following subsection. More details can be found in (SKLYAROV et al., 2014).

#### 2.1.1 Block Random Access Memories

BRAMs are embedded memory blocks used for storing large sets of data more efficiently than by LUTs, and are widely available in modern FPGAs. For example, the Xilinx 7 series FPGAs contain from 5 to 1880 dual-port BRAMs, depending on the model, each storing 36Kb of data. These blocks can be divided into two independent 18Kb BRAMs. In both cases, dual-port is assured, and each port is completely independent of another, sharing only the stored data (Xilinx Inc.; XILINX; INC, 2017).

These embedded blocks can also be configured in different associations (e.g., 32K 1-bit lines, 16K 2-bit lines, ..., 1K 32-bit lines, 512 64-bit lines), and can be interconnected to create wider and deeper memory structures (SKLYAROV et al., 2014). Finally, both read and write operations are synchronous, requiring an active clock edge.

As already mentioned since logic-driven designs, as soft-core processors, generally underuse available BRAMs (see Table 1.1), we propose to better occupy those components by implementing the RT for enhancing applications' performance.

# 2.1.2 Soft-Core Processors

A soft-core processor is a hardware description language model of a processor that can be customized and synthesized for an ASIC or FPGA target (TONG; ANDERSON; KHALID, 2006). In this study, however, we consider only FPGA-based soft-cores. FPGA-based soft-cores became popular as they bring advantages such as (i) architecture customization, since FPGA allows non-standard implementation, according to the design requirements; (ii) obsolescence mitigation, as the hardware description perpetuates while hardware technologies advance; (iii) cost reduction, considering that multiple components can be replaced with a single FPGA; and (iv) hardware acceleration, since specific algorithms can be easily implemented in hardware, for example, to achieve better performance (FLETCHER, 2005).

There is a variety of commercial and academic soft-core processors as a demonstration of its representativeness. Examples from the industry comprehend Xilinx *MicroBlaze* soft processor, an Intellectual Property (IP) for Xilinx FPGAs (KALE, 2016), the Altera Nios II (NIOS, 2009), and the open sourced hardware description of Sun's UltraSparc T1 and T2, which were released by the OpenSparc Project (PARULKAR et al., 2008). From academia, we highlight the  $\rho$ -VEX VLIW processor (WONG; Van As; BROWN, 2008) from Delft University of Technology.

# **2.2 Modern Architectures**

The required performance of computing devices has increased as technology advances. The transistor's scaling improved processors frequency, while the exploitation of Instruction-Level Parallelism (ILP) increased processors throughput. However, increased clock rates dissipate more power, which became a barrier. At the same time, the ILP exploitation in *superscalar* processors - where multiple independent instructions can be simultaneously executed every cycle - by deep pipelining and out-of-order execution, seems to have reached a plateau (DAS et al., 2008).

To overcome the above challenges and to guarantee computers ascendant performance, various solutions were proposed. We detail three solutions in the upcoming subsections, which are strongly related to this work: Very Long Instruction Word Processors, Multi-Core Processors, and Multiprocessor System on Chip.

# 2.2.1 Very Long Instruction Word Processors

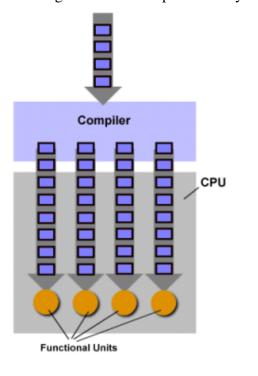

The extraction of ILP at execution time by *superscalar* processors enabled performance gains but introduced more hardware (and complexity) given the logic required to find parallel instructions (OLUKOTUN; HAMMOND, 2005) dynamically. As alternative to on-the-fly ILP exploitation, the VLIW processors were proposed (FISHER, 1983).

A VLIW processor contains multiple execution pipelines, the issue-slots, so that it can execute more than one instruction at a time (just like a superscalar). The advantage of using these processors is that the instruction parallelism is extracted by the compiler (see Figure 2.2). Thus, a VLIW processor can benefit from ILP while maintaining a simple microarchitecture. The parallel instructions are disposed inside a *very long instruction word*, in a set of independent instructions that can be executed concurrently without any concern by the processor. The arrangement of the instruction even maps each instruction with the issue-slot on which it will be executed.

Because of its simple organization alongside its ILP exploitation, the VLIW processors are powerful yet less resource-consuming in comparison to a complex superscalar. These factors make the VLIW a good architecture option for resource-constrained FPGAbased soft-core processors.

Dynamic Superscalar Instruction Scheduling

(a) A VLIW architecture. ILP is extracted by the compiler.

IW Instruction Scheduling

(b) A superscalar architecture. ILP is extracted by the hardware.

17

Source: (STOKES, 2000)

#### 2.2.2 Multi-Core Processors

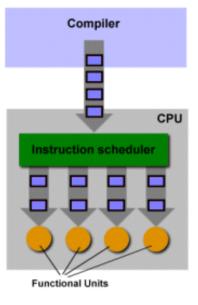

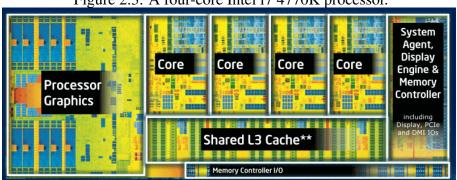

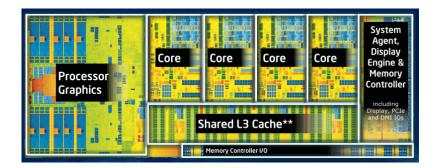

Optimizing a single core processor with pipeline, ILP exploitation and out-oforder execution became insufficient. Multi-core processors were proposed, observing that complex systems usually execute multiple tasks. Thus, in a multi-core environment, various tasks could be distributed among multiple processors, increasing the overall throughput of the system. Figure 2.3 presents a quad-core Intel i7 overview as example. Each core can execute independently of others and communicates by using the shared cache memory.

The first commercial multi-core processor was the IBM Power4 (TENDLER et al., 2002) released in 2001. After, other companies such as Intel, AMD, and Sun also turned to multi-core production (GEER, 2005). Ever since, multi-core designs became almost a standard for General Purpose Processors (GPPs), from Intel Pentium D up to the latest Intel i7 Series. Not enough, multi-core processors are highly used in nowadays embedded systems as smartphones (Van Berkel, 2009).

### 2.2.3 Multiprocessor System on Chip

Some computer tasks, like real-time video encoding, for example, execute a complex algorithm with very high throughput demand. In other cases, the constraints can be latency or power. When that occurs, using a GPP may not be the best option, either for performance or energy consumption, since a specialized hardware can meet the constraints more easily.

Let us consider the case of smartphones and tablets as an example. They are required to execute a broad range of concurrent tasks with minimum battery consump-

Figure 2.3: A four-core Intel i7 4770K processor.

Source: (LUDLOW, 2014)

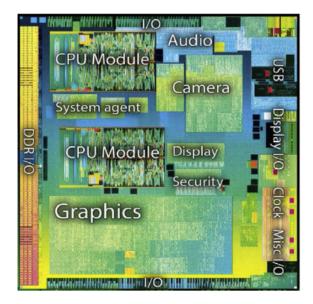

tion. For this reason, these devices have specific hardware modules in their main chip die working together with multiple processors to run the applications efficiently (JÓŹWIAK, 2017). This chip arrangement is known as MPSoCs. For example, the Snapdragon 835, used in newest smartphones, contains a quad-core Central Processing Unit (CPU) with dedicated hardware for processing audio, graphics, camera image, security, location, and several other specialized modules (QUALCOMM, 2017).

# 2.3 Reuse

Here we introduce the concept of reuse in the computing scope. A more detailed overview of techniques and approaches will be covered in the Chapter 3 (Related Work).

#### 2.3.1 General Reuse

Reuse of computation is based on the observation that deterministic execution where a set of inputs always leads to the same result - often repeats within programs. Reuse exploits this by saving input and result (output) values of those executions in a RT. The RT is searched when reentering a given snippet of execution, checking whether the current and the saved input values are the same. In case of a hit, the result (output value) from the RT is fetched faster than recomputing it.

For example, consider the hypothetical three-address code bellow:

Figure 2.4: Example of a Reusable Code Snippet

$$r.1 = r.6$$

$r.2 = 1 + r.1$

$r.3 = 1 + r.2$

#### Source: The Author

The inputs are the values which are read before are written; in the example, the register r.6 is the only input. The outputs are the written values, which will be read further, in the case r.1, r.2, r.3. Consider r.6 = 1 in a given execution. Therefore, after the code executes, r.1 = 1, r.2 = 2, r.3 = 3. Note that any eventual execution in which r.6 = 1 will imply in the same result in the outputs r.1, r.2, r.3. In this scenario, saving the input and output values for consulting in a new occurrence could skip execution of three

instructions.

#### **2.3.2 Function Reuse**

A particular case for reuse is when the evaluation of reuse occurs in the grain of functions. In this case, the function parameters are the inputs, and the values returned by functions are the outputs.

The following example illustrates a simple scenario where function reuse could be used:

Figure 2.5: Example of a Reusable Function Result.

$$a = sin(\pi)$$

$$\vdots$$

$$b = sin(\pi)$$

Source: The Author

In this case, the second execution of sin could be skipped, given a repetition of the inputs ( $\pi$  in this case). Naturally, in this simple case, the explicit re-operation of  $sin(\pi)$  could be avoided by better programming or even compiler optimization. Note, however, that in a more realistic situation the input parameters can, and often will, be variables, whose values are unknown at compile time and unpredictable by the programmer.

#### 2.3.3 Approximate Function Reuse

When applications tolerate some error level, approximate function reuse can take place. For example, observe the scenario in Figure 2.6. In this case, we have three calls to the function *sin*. If we consider the former function reuse, none of the calls could benefit from previous calculations to skip the functions executions since the inputs always differ. When we perform approximate reuse, we can consider that close values are good enough for the final computation, increasing reuse possibilities, at the cost of quality.

Therefore, we must decide how much error we can accept: in the example, we can be conservative considering  $\pi$  very close to 3.14, but not close enough to 3. Thus we could reuse in one case, with a small loss in quality in the value of *b*. Being more

$$a = sin(3.14)$$

$$\vdots$$

$$b = sin(\pi)$$

$$\vdots$$

$$c = sin(3)$$

Source: The Author

aggressive, we could consider  $\pi$  and 3.14 also very close to 3, hence, leading to one more reuse case (when calculating the value of *c*) but paying a higher cost in quality. In chapter 3, we present how different related works have implemented approximation to achieve a behavior like the one we discussed above.

# **3 RELATED WORK**

This chapter presents previous works that are somewhat aligned with the problem we try to solve. We divide the works in three groups: Reuse in Single-Core Environments, Reuse in Multi-Core Environments, and Approximate Reuse in order to facilitate the understanding of our contributions in each of these research subfields.

#### **3.1 Reuse in Single-Core Environments**

A variety of works has discussed reuse of computation (SASTRY; BODIK; SMITH, 2000). Implementations vary from software (where reuse is also known as *memoiza-tion* (HALL; MCNAMEE, 1997)) to hardware-based solutions and cover different granularities of code. Sodani and Sohi (1997) presented dynamic instruction reuse is with execution-driven simulation. The goal is to avoid re-execution of instructions in an out-of-order processor. Instructions' source registers are the inputs, and its result is the output. The scheme is enhanced with control of dependency links among instructions, providing reuse of a set of dependent instructions. Citron, Feitelson and Rudolph (1998) proposed the reuse of FP instructions only, focusing on multimedia applications. For each function unit that takes more than a cycle to execute (like an FP divider or multiplier), a MEMO-TABLE is used to store the results. Average speed up between 8% and 22% is achieved. Despite a hardware scheme being discussed, the results are taken from an instruction-level simulator.

Reuse of a set of instructions within a basic block is considered by Huang and Lilja (1999) and simulated using SimpleScalar (AUSTIN; LARSON; ERNST, 2002). The source operands (registers or memory) of each instruction inside a basic block are considered as part of the input. The values written to any register or memory location are considered as part of the output. Their work shows performance improvements of up to 14%. A similar system is proposed over trace level (a set of sequential basic blocks) by González, Tubella and Molina (1999). In this case, less reusability is found compared to instruction reuse, but more speedup is obtained since larger chunks of code are involved.

Kavi and Chen (2003) introduced the concept of dynamic function result reuse. In this case, only *pure* functions (global variables free, no I/O requirement, nor any change in the global state of the program) can be reused, so that the return value depends only on the function's input parameters. The authors verify the impact of (i) reuse buffer size; (ii) reuse buffer associativity; and (iii) amount of input parameters of functions. The study presented from 10% to 67% of reusability on a variety of applications, supporting the use of the function reuse concept. Finally, Suresh et al. (2015) implemented function reuse in the interface between programs and operating system. Their mechanism intercept calls to the dynamically linked math library by preloading a memoized version of it. This modified library verifies reusability and returns the respective output value by reuse when available (otherwise, the original math library is called to solve the function).

#### **3.2 Reuse in Multi-Core Environments**

Historically, when data value reuse was first proposed, research focused in (simulated) single-core environments for skipping snippets of execution. Very few works have extrapolated the analysis to multi-core/multi-thread scenarios.

Molina, Gonzdalez and Tubella (2002) propose the execution of a program with two virtual threads - similar to Simultaneous Multithreading (SMT) - where one speculates execution while the other uses a *Verification Engine* to quickly verify misspeculations to reduce the penalty of skipping execution by *prediction*.

Some works have put effort into avoiding reexecution of computation by thread synchronization. Long et al. (2010) propose to synchronize threads of an application in a form that execution of threads occurs by aligning identical instructions, synchronizing with a fetch priority mechanism. This is possible thanks to the code similarities among program's threads. By this, it is often possible to use a single fetch unit (since instructions are equal), and when instructions operand are also equal, execute multiple instructions together in a single thread, and applying the results to all threads. Speedup is expected, as highlighted by the authors, because the instruction window is easier to keep full, fewer instructions need to be executed, and fewer cache accesses must occur. Indeed, 1.15x speedup is achieved comparing to a two-thread traditional SMT processor, and 1.25x comparing with a four-thread SMT. The work by Mckeown, Balkind and Wentzlaff (2014) uses a similar approach. However, their solution also works with multi-threads from different programs, even though they show that this scenario is *not* the sweet spot for the technique usage.

# 3.3 Approximate Reuse

A few works have explored the concept of approximate function reuse under distinct names. Alvarez, Corbal and Valero (2005), present fuzzy memoization of FP instructions. Similarly to the work developed by Citron, Feitelson and Rudolph (1998), where only multiplication and division operations are saved in the table due to their high latency, and multimedia applications are used for evaluation. Approximation is achieved by dropping some Least Significant Bits (LSBs) from the input FP value's mantissa, causing close enough values to be grouped into the same table entry. The authors claim that 4x more energy can be saved by using fuzzy memoization compared to the precise reuse approach.

Work by Keramidas, Kokkala and Stamoulis (2015) presents the clumsy value cache, an instruction/block-level reuse technique targeting Graphics Processing Units (GPUs) fragment shaders. The authors investigate the potential of dropping input bits to increase instruction reuse rates and show that by doing so is the only viable way to implement block reuse. No speedup results are presented in the work, but the technique reduces the number of instructions executed, on average, by 13.5%. Sinha and Zhang (2016) use memoization to accelerate application-specific circuits synthesized for FPGA using High-Level Synthesis (HLS), and show that it can achieve 20% energy savings with less than 5% of area overhead.

#### **3.4 Work Contribuitions**

Our work is the first to consider reuse specifically targeted to FPGAs and softcores, taking into account their unique components, design constraints and intrinsic characteristics, such as the fact that BRAMs are usually underused. It can provide a generic solution for both precise and approximate computation either in single or multi-core environments, delivering a low-cost and flexible technique so the design requirements can be achieved with the FPGA at hand.

To the best of our knowledge, this is the first hardware implementation of such technique targeted towards soft-core processors. Through this, this work provides an in-depth analysis of the area/resources consumption of the mechanism and a level of accuracy that only actual implementations can provide. Our hardware implementation is free of any abstraction layers, leading to a solution independent of user space or operating systems, which are unavailable in bare metal designs. Additionally, we propose to cover reuse with a shared RT in a multi-core environment, which (to the best of our knowledge) was never proposed before not only for FPGA-based processors but also in GPPs.

By presenting function reuse in FPGA for soft-core processors, we open new possibilities for design space exploration and new tradeoffs for HW/SW co-design in such devices. For instance, low-price FPGAs may regain space in project decision, since our approach provides performance gains with low overhead in LUTs, occupying, instead, BRAMs that would otherwise be idle. Moreover, the multi-core analysis can update the knowledge of reusability in modern designs, and also explain the behavior of reuse when the RT is populated simultaneously from different applications.

#### **4 IMPLEMENTATION AND METHODOLOGY**

This chapter presents the addition of a function Reuse Unit (RU) to a singlecore VLIW processor, by VHDL implementation, to skip redundant function execution in single-thread programs; this is accomplished by using available BRAMs for storing the reuse information of functions. After, it details a multi-core reuse proposal to share a single centralized RU (and RT) among multiple cores, to improve reuse by leveraging inter-core likeness of code, and the simulator built to extract the results. Finally, we demonstrate the minor changes in the former hardware so we can enhance the RU with approximate reuse.

For the sake of clarity, we will explain each of this incremental steps in the sections below.

### 4.1 Baseline Processor

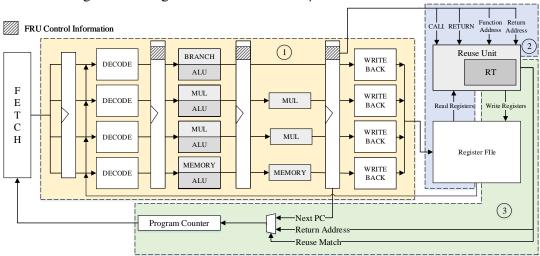

The techniques we propose are for the  $\rho$ -VEX VLIW soft-core processor (WONG; Van As; BROWN, 2008) compatible with the VEX Instruction-Set Architecture (ISA) (Hewlett-Packard Laboratories, 2009) and described in VHDL, even though there are no restrictions that would prevent its implementation to any other soft-core processor. It has a Load/Store Harvard architecture with a five-stage pipeline: *Fetch*, *Decode*, *Execute 1*, *Execute 2*, and *Write-back*. The issue-width (e.g., 2, 4, or 8), type and organization of functional units, and register file size can be configured during design time. Each pipelane may contain different Functional Units (FUs) from the following set: Arithmetic and Logic Unit (ALU) (always present), multiplier, memory, and branch units.

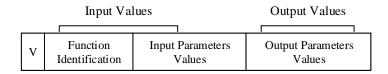

In this work, a  $\rho$ -VEX core is set as the default 4-issue version consisting of 4 ALUs, 2 multipliers, 1 memory unit, and 1 branch unit (as shown in Figure 4.3) and 8+8KB instruction and data caches. The VEX ISA defines that argument and return values for function calls are passed through registers *R3* to *R10*. If more than eight input or output registers are required, the memory is used. We consider only the first case (up to eight parameters) since we have found that the functions that do not fit in this case are not good for reuse: they are unlikely to be reused (many inputs to match) and lead to high latency to check/compare memory values.

| v | Function | Input Registers | Output Registers |

|---|----------|-----------------|------------------|

|   | Address  | Values          | Values           |

Figure 4.1: A Reuse Table entry.

Source: The Author

# 4.2 Implementing the Function Reuse Unit in a Single-Core

The proposed mechanism was implemented by modifying the  $\rho$ -VEX hardware description. An RU was attached to the processor and is composed of the following:

- *RT*: a direct mapped table implemented in BRAM that stores dynamic information of *reusable functions* (frequently executed, likely-to-be-reused pure functions defined at design time). Each entry (Figure 4.1) contains the function's address as well as the input and output contexts. Its size is defined at design time.

- *Functions Table*: a small (one entry per *reusable function*) and fully associative table with static information on the reusable functions. Each entry contains the function's address and the number of parameters of the function. This table is filled at *design* time by the designer.

- *Reuse mechanism*: implements the process of accessing the reuse table, which involves the index calculation (using a hash); checking whether the entry in the RT is valid or not; and reusing it, if it is the case.

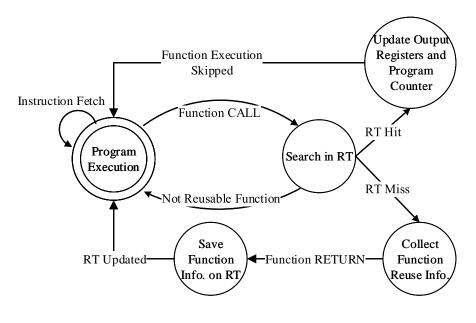

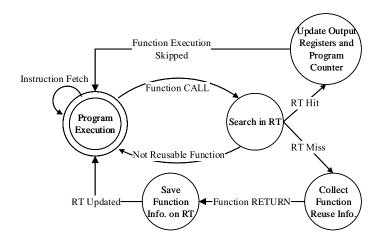

Figure 4.2 summarizes, through a finite state machine, the functioning of the RU along with a program execution. With the *Functions Table* filled (by the system's designer, as we explain soon), on every *CALL* instruction targeting such *reusable functions*, the mechanism verifies for a previous execution of it in the RT (and thus, for the result of such previous execution), updating the processor context if it finds it. When the current function result is not available in the RT, the scheme must wait for the function to end, so the outputs are available, and then store them in the RT for further lookups. Thereby, the RT is dynamically filled at run-time. As occurs in related works (see Chapter 3) the function reuse is a technique to be applied on *pure* functions, and therefore it must be explicit to the RU whenever a function is *pure* or not (so it can be reused). Actually, our implementation considers that the RU should work with a subset of the program's *pure* functions, named *reusable functions*, marked (stored at the *Functions Table*) to be reused by the system's designer in *design* time. Therefore, it is up to the designer to find *pure* functions and decide if they should or should not be reused.

Figure 4.2: The Functioning of the Function Reuse Unit.

Source: The Author

Next, detailed explanation of micro-architectural aspects is presented.

# 4.2.1 Reuse Mechanism

Figure 4.3 details the  $\rho$ -VEX organization integrated with the RU. Three phases are highlighted, and correspond to (1, yellow) how the RU collects reuse information, (2, blue) verifies and stores reuse information, (3, green) and applies reuse (if possible). Each phase works as follows:

Figure 4.3: Organization of a 4-issue  $\rho$ -VEX with a Reuse Unit.

Source: The Author

*Phase 1*: When the pipeline decodes a *call*, the function and return addresses proceed through the pipeline until reaching the RU, which checks in the *Functions Table* if the function was defined as *reusable*, and also the number of parameters of that function, preparing for phase (2). If the function is *not reusable*, the processor continues their regular operation.

*Phase 2*: In this phase, the current function's input parameters are collected by accessing the register file. With it, the RU generates a hash key by *XORing* every 16-bit of data in the current input context and function address, similarly to the approach in (SURESH et al., 2015). The resulting key's LSBs are used as the RT index to fetch a table entry, which contains the fields shown in Figure 4.1, accordingly with the RT size. In case the fetched entry is valid, the entry's function address and input parameters are compared with those of the current call. If the comparisons match, there is an RT hit and phase (3) starts.

Otherwise, a reuse miss happens if the valid bit of the current entry is not set or if the function address and inputs do not match. In these cases, the RU waits for the function to execute regularly (until the *return* instruction signaling). Then, with the input context and outputs captured from the register file, stores a new entry (if the valid bit was not set) or replace an entry in the RT (in case of data mismatch). Therefore, the RT is dynamically filled as the program executes.

*Phase 3*: A match was detected in the previous phase, so the result of the whole function is available in the fetched RT entry. Therefore, the RU writes it to the register file, skipping the actual execution, and notifies the reuse detection to the processor. Then, the instructions in the pipeline are flushed, and the return address (captured by the RU in phase (1)) is written to the program counter. Since reusability can be checked before the pipeline commits any instruction, no rollback mechanism is required.

In order to allow the RU to collect the inputs or the outputs of a function (available in registers *R3* to *R10*) while the processor is fetching instructions (and its operands), we added extra reading ports in the register file. Thereby, the RU and the processor can operate in parallel, and reuse misses cause no performance penalties. The number of additional ports can be tuned according to the target functions: the more parameters, the more ports are needed to ensure no pipeline stalls (in our implementation, four reading ports were added). As the register file and its ports are synthesized with FPGA's registers and LUTs, adding ports increase their usage, but only marginally as our results will show. As mentioned in phase (3), when the reuse is applied, the pipeline is flushed, and the result

of the function is written to the register file. The RU exploits the fact that these write ports would be idle due to the pipeline flush and uses them to perform this operation, which results in no additional write ports. In this arrangement, the RU takes only *four* cycles to apply the reuse: one cycle to collect the inputs, two cycles to access the RT and check for reusability, and one cycle to write back the function results. For more aggressive performance enhancement, a forwarding mechanism could anticipate data to compare input context. However, four cycles are already much less than the dozens/hundreds of cycles taken by functions commonly reused in related work, and avoiding the forwarding mechanism saves logic resources. Therefore, we did not implemented a forwarding-aware RU.

#### **4.3 Function Reuse in Multi-Core Environments**

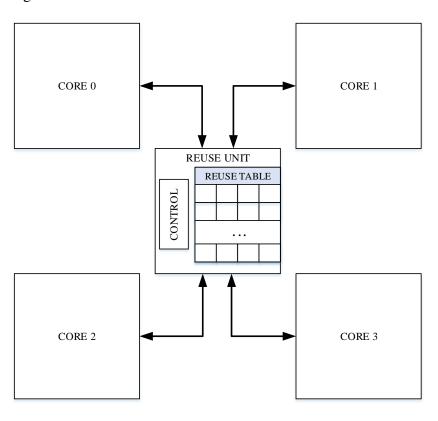

On a system with multiple cores, the straightforward approach for applying function reuse would be to attach a dedicated RU (and RT) for each core. However, as each application would have a dedicated RT running independently from the other cores, this would be like if we have multiple single-core reuse environments, which brings no novelty from the scientific analysis perspective. We, otherwise, propose to share the RT among cores, in order to possibly increase performance by benefiting from inter-core reuse, while amortizing resource usage since a single centralized RU would manage reuse instead of multiple, one-per-core, RUs. An overview of the idea is shown in Figure 4.4.

Our multi-core function reuse mechanism considers the following:

- Each core in the system is able to pass reuse-related information (as the functions and returns addresses) trough their pipelines (as occurs in the single-core case, see Figure 4.3), sending them to the centralized RU.

- The functioning of the RU is same as in single-core: it receives a function with its input context information, and fetch from (or update) the RT. Differences occur only in the interface with the system since now the RU needs to communicate with every system core. Therefore, all Inputs/Outputs (IOs) of the RU in Figure 4.3 should be multiplexed: information from pipeline as *call*, *return*, function address, return address; interface with register files; interface with fetch units. Thereby, no additional IOs ports in the RU are needed. The *decoding* of a CALL instruction in the pipelines can be used to control the access in the RU, multiplexing its IO to the

correspondent core in advance of the arrival of reuse information.

- Inter-core reuse is only possible if the functions to be reused have the same addresses in all programs instances. This is easily achieved by appropriate ordering the functions while writing programs, or when including libraries to compile a program. A specialized mechanism (such as a translate table) could be used to guarantee that same functions in different programs (with different addresses) are seen as the same by the RU, but we do not cover these mechanisms.

- Finally, when a core requests a reuse verification to the shared RU, the unit is locked for the 4 cycles it operates (for *reusable functions*), dropping any other requests during this time. If multiple requests occur in the same cycle, access grant is given to the smallest processor id that holds a *reusable function*. Cores that had dropped requests continue its regular execution. Note that each conflicting request could lead to a miss or hit in the RT, which means that dropping a request that would lead to a miss does not change the execution of the application. As future work, a queue will be implemented to handle all reuse requests.

Figure 4.4: A Multi-Core Environment with a Shared Reuse Unit.

Source: The Author

# 4.3.1 Multi-Core Function Reuse Simulator

To analyze the idea, we implement a simulator to handle function reuse in a multicore environment, based on function traces. For such, we added a log generator to the RU. Thereby, we can execute programs in  $\rho$ -VEX to generate a trace (we will call it *reuse trace*) of the *reusable functions* called. A brief example of a *reuse trace* is depicted in Figure 4.5, where each line contains the timestamp (execution cycle) of the call, the target function, the inputs, and the time (cycles) the function took to execute. As one can see, the trace is sorted in ascending order according to the timestamp. Although the *reuse traces* are generated by separated single-core executions, providing them to our simulator is all the necessary to analyze performance in the multi-core environment. Thus, we can use software analysis (instead of slower hardware simulation), to compute precisely the performance gains of sharing the RT. This is important because, as we shall present in the Results Chapter, the number of scenarios to be combined in multi-core testing increases quickly.

Here we introduce FunctiOn Reuse MulticOre SimulAtor (FORMOSA): the simulator we implemented to manage multiple *reuse traces* to act as a centralized RU, handling function reuse requests from multiple programs, and updating the centralized RT accordingly. For this, the simulator considers *reuse trace* as a faithful abstraction of a program execution. Although we have generated traces from our modified  $\rho$ -VEX, FORMOSA could be used to analyze function reuse in any generic environment, as long as the log files follow the pattern showed in Figure 4.5.

The high-level operation of the FORMOSA is presented in Algorithm 1, and is explained briefly next. To use the simulator, the log files (logs) and the table size ( $tbl_size$ ) must be given. FORMOSA executes until it consumes all lines from all logs. At each iteration, it consumes one line from each log and *chooses* the earliest request line (1. 2) by looking at the *tmstmp* field, saving it in the *chosen\_line* variable (1. 3). After, it checks whenever a reuse request will find the RU locked. It is done by simply check-

#### Figure 4.5: Example of a *Reuse Trace* from the Reuse Unit.

| <tmstmp></tmstmp> | <func_id></func_id> | <input1></input1> | <input2></input2> | <input3></input3> | <input4></input4> | <cycles></cycles> |

|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| 420               | 00011D30            | 40000000          | 00000000          | 40240000          | 00000000          | 345               |

| 554               | 000104E0            | 3FC99999          | 99999999A         | 3FC99999          | 99999999A         | 123               |

| 636               | 0000EF80            | 3FC99999          | 99999999A         | 3FC99999          | 99999999A         | 78                |

| 773               | 000103C0            | 40000000          | 00000000          | 3FA47AE1          | 47AE147C          | 129               |

Algorithm 1 The FORMOSA's Algorithm.

```

Require: log files (logs), table size (tbl_size).

RU \ CYCLES \leftarrow 4

1: while there are lines to be analyzed in logs do

chosen\_loq \leftarrow findSmallestTimestamp(logs)

2:

chosen\_line \leftarrow readLineFromLog(chosen\_loq)

3:

4:

foreach log in logs where log \neq chosen\_log do

log\_line \leftarrow readLineFromLog(log)

5:

if log_line.tmstmp < chosen_line.tmstmp + RU_CYCLES then

6:

7:

FoundRTLocked[log_idx] += 1

8:

else

rollbackLogFile(loq)

9:

end if

10:

end for

11:

tbl_pos \leftarrow hash (tbl_size, chosen_line.Func_ID, chosen_line.Inputs)

12:

RT\_entry \leftarrow RT(tbl\_pos)

13:

if chosen_line.Func_ID = RT_entry.Func_ID

14:

and chosen line. Inputs = RT entry. Inputs then

SavedCycles[chosen_log_idx] += chosen_line.Cycles - RU_CYCLES

15:

updateLogTimestamps(chosen_log,SavedCycles)

16:

17:

else

updateRT(tbl_pos, chosen_line.Func_ID, chosen_line.Inputs)

18:

end if

19:

20: end while

```

ing if the remaining lines of the current iteration contain a timestamp that is in the range from  $chosen\_line.tmstmp$  up to 4 more cycles (l. 6), which are the cycles that the RU is locked. For all log lines that found the RT locked, the reuse verification (which could or could not lead to reuse) is missed and counted so that one can analyze accessing conflicts later (l. 7). Logs where timestamps were ahead of  $chosen\_line.tmstmp + 4$  have their handlers rolled-back (l. 9), since they can be the next *earliest timestamp* and must be reevaluated in the following iteration.

Finally, the RU can use the *chosen\_line* to attempt reuse in the same way it occurs in the single-thread scenario. It generates the hash key to get the position  $(tbl_pos)$  to lookup in the RT (l. 12). Then, the RT is consulted, returning a  $RT_entry$  (l. 13). Function addresses  $(FUNC_IDs$  in the algorithm) and inputs are compared to check for a reuse match. When reuse is successful (l. 15), FORMOSA accumulates the number of cycles that were skipped (given by the number of cycles spent when the function was computed, less the four cycles to apply reuse). This is used later to observe performance gains over baselines. Also, the saved cycles are diminished from upcoming timestamps of the current *chosen\_log* (l. 16), since in a reuse hit would cause upcoming calls to occur earlier. If reuse fails, the RT is updated with *chosen\_line* data in the *tbl\_pos* (l. 18).

Note that FORMOSA does not require the output values in the *reuse traces*, since it does not execute any program (and therefore does not update any processor context). Thus, we save simulation memory by ignoring output values. The FORMOSA final results are the total saved cycles of each application (in its own core). Therefore, one has to know the number of cycles of the baseline, which is trivial, to infer metrics such as speedup. Finally, if the *reusable functions* are guaranteed to be *pure*, function reuse is also guaranteed to be safe and correct.

To validate the simulator, we have tested it with small sized traces, checking results manually. Especially, conflicts in border values of time (for locking the RU) were verified. Also, the simulator has the same results as the VHDL implementation (from the previous chapter) for the cases where a *single* trace is provided.

# 4.4 Enhancing Function Reuse Possibilities with Approximate Computing

Although previous work (and ours, as we discuss later) shows that reuse can achieve speedup, some classes of applications hardly benefit from function reuse. This occurs because the input space can be very extensive, reducing chances to match previous calculations. At the same time, many of them can tolerate some error in their outputs, being convenient for approximate computing. Classical examples are image filters, video encoders, and neural networks (HAN; ORSHANSKY, 2013; ESMAEILZADEH et al., 2012).

In this section, we present how our function reuse mechanism could embrace the approximate concept, with *approximate reuse*, leveraging reusability in the aforementioned scenarios. Also, we show how it could be used alongside with the *precise reuse*, with marginal changes in the former hardware. This is achieved by dropping some LSBs from the inputs, so similar/close values are hashed to the same positions in the hash function. Thus, we enhance reuse possibilities, increasing the number of scenarios where it can be useful. Although we discuss the minor changes to implement it in hardware, we did not implement it on VHDL, but instead, investigated approximate function reuse in a single-core scenario by simulating and estimating the behavior of applications, as discussed in the Results chapter.

Next, we highlight the necessary additions to the reuse mechanism. Since modifications for *approximate reuse* do not change the overall multi-core reuse arrangement, we simplify the explanation considering a single-core environment.

# 4.4.1 Modifications to Support Approximate Reuse

Below we detail the modifications required so a hardware RU supports *approximate reuse*:

- The *Functions Table* (which formerly stored the *reusable function's* addresses and quantity of inputs) must indicate, for each function, if it is to be *approximately* or *precisely* reused. If *approximately*, it must indicate how many LSBs should be dropped from the inputs for generating the hash key and tuning the performance/output quality trade-off. This is, as in the former case, up to the designer to set up at *design* time.

- When reusing *approximately*, the RU has to drop the inputs' LSBs before generating the hash key, to group close values. This is easily done in hardware by *ignoring* wires. The LSBs of the hash key itself still index the RT, while the full hash key is used as a *tag* in approximate mode.

- The RT entries can now contain data in two different structures (see Figure 4.6), accordingly with the reuse mode (precise or approximate). In precise mode, all inputs are stored. In approximate mode, only the *tag* is stored. The tag is stored in a sub-part of the former entries, and thus, no change in the RT entries width have to be made.

- When attempting precise reuse, input values are compared. Otherwise, when attempting approximate reuse, the *tag* is used. Therefore, comparing a tag uses a subset of the hardware that compares precise inputs.

- A few multiplexers must be included to control, based on the current reuse mode, when to compare the inputs or the tag; when to ignore LSBs of the inputs to calculate the hash key; and when to store the inputs or the tag in an RT entry.

As we described, it is possible to enhance function reuse with approximate reuse with marginal addition in control logic and *Functions Table*. Thereby, it is possible to have a generic RU that can switch between precise and approximate reuse easily.

| Precise              |   | Function            | Input Registers | Output Registers           |

|----------------------|---|---------------------|-----------------|----------------------------|

| Reuse                |   | Address             | Values          | Values                     |

| Approximate<br>Reuse | v | Function<br>Address | Tag             | Output Registers<br>Values |

Figure 4.6: A Reuse Table entry that supports precise and approximate modes.

Compared Fields to Reuse

Source: The Author

## 4.4.2 Modifying Software to Analyze Approximate Function Reuse

To measure the potential of approximate function reuse to improve performance, we have changed the original program/application we want to analyze for one which counts functions calls, how many times it repeats, and the number of table hits. This is done considering the same replacement policy and hash function that we propose to exist in hardware (including the dropping of LSBs). In time, the benchmark modification is based on the work of Brandalero et al. (2017). This modified version is executed on a regular Linux machine. This was needed because approximate benchmarks (as the one we use in Chapter 5) commonly consider image or video processing, requiring system calls to access files, and specific libraries not supported by the  $\rho$ -VEX platform. At the same time, we have implemented a pure C code of the respective kernel under analysis, hard-coding the inputs (like an image) in the source so we have a version that can run in  $\rho$ -VEX.

With the pure C version of the program, we have an estimation of the number of cycles that the benchmark and the function we want to approximately reuse demand on  $\rho$ -VEX. Likewise, with the modified benchmark application running on a regular Linux machine, we collect the number of reuse hits according to with the number of LSBs we chose to drop. With the number of cycles of the benchmark, the function we want to reuse, and the reuse hits, we can analyze performance improvement.

#### **5 RESULTS**

In this chapter, we explain the evaluation methods and present the results of each aforementioned function reuse technique. For performance results, which we introduce first, we follow the same order of previous chapters: first, we debate (*precise*) function reuse in single-core environments, then in multi-core environments and finally the potential of using approximate function reuse. After, we summarize area/resources usage analysis over the covered techniques.

#### **5.1 Function Reuse in Single-Core Environments**

#### 5.1.1 Experimental Methodology

We performed cycle-accurate simulations of the processor execution using Mentor Graphics Modelsim 10. We evaluated the speedup of six benchmarks, five from the WCET benchmark suite (GUSTAFSSON et al., 2010): *lms, ludcmp, minver, qurt, st*; and one from the Powerstone suite (SCOTT et al., 1998): *fir*. To measure performance, we compared the execution cycles of the benchmarks on  $\rho$ -VEX with and without the RU, experimenting with RT sizes varying from one to 32K lines. We could use cycles as reliable performance metric since we do not change the critical path, and thus maintained the clock frequency. The final state (registers and memory values) of the enhanced processor was compared to the final state of the baseline, to ensure programs still executed correctly after our modifications. The benchmarks were compiled with LLVM (LATTNER; ADVE, 2004) with the back end modified to support the VEX ISA (JOST; NAZAR; CARRO, 2016), and *-O3* flag.

#### 5.1.2 Case Study - Floating-Point

As a case study, we optimized the standard soft-float library (HAUSER, 2002) which emulates FP operations using integer hardware - applying reuse over some of its functions. The soft-float is a library traditionally used to support FP operations in systems where no FP ALUs are available, or when FP is not supported by the ISA (the case for VEX ISA of  $\rho$ -VEX). It conforms to the IEEE Standard for Floating-Point Arithmetic, and is available, for example, in the LLVM (used here) and in the gcc compiler. We considered the four basic operations (add, sub, mult, div) in double FP precision of the soft-float library as the *reusable functions*. The consideration is based on the profiling of applications, which showed that those functions are commonly called. As the soft-float library was statically linked at compile time, we could consult the assembly of the code to get the addresses of the functions, and the amount of input and output registers used, assigning it to the *Functions Table* on our VHDL description.

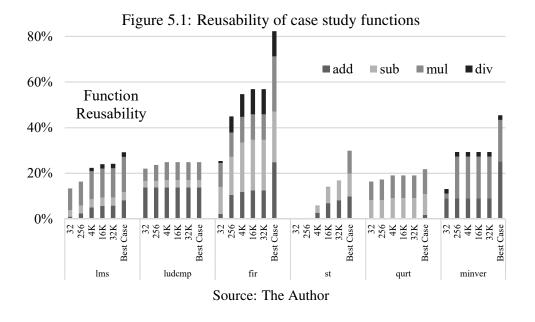

#### 5.1.3 Reusability

Figure 5.1 presents the reusability of the case study functions, which will influence the performance gains. Grouped by benchmarks, each column depicts the stacked RT hit rate for *add*, *sub*, *mul*, and *div* functions, according to the number of RT lines (*x-axis*). Naturally, reusability increases with the RT size, since more reuse information is available, so a match attempt succeeds. A *Best Case* scenario was also included, presenting results for a hypothetical RT that behaves like an infinite and perfect collection that stores all entries without replacements. This best case indicates how good are the table sizes and the chosen hash function. Cases with significant reusability of *div* (e.g., *fir*) and *mul* (e.g., *lms* and *minver*) have more potential for improving performance, since these operations generally take longer than *add* or *sub*. Although reusability does not guarantee performance gains (for instance, if a function is called only a few times or if it is extremely fast), it gives the intuition of the space exploration for when we further look upon performance speedups.

For these benchmarks, reusability can vary from almost none (*st* with 32 lines) to more than 80% (*fir* in the *best case*), while in overall, the functions reusability can sum up to more than 20% in all benchmarks, when using a sufficiently large table. In addition, *mul* was the most reused function, while *div* was the least one.

### 5.1.4 Performance

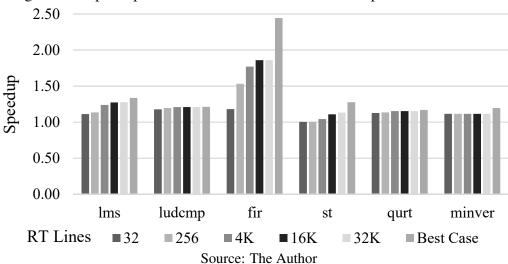

Fig. 5.2 depicts the speedup for different RT sizes, also grouped by benchmark. For the largest RT tested (32K lines) significant speedups are achieved: in *ludcmp* (1.21x), *lms* (1.28x) and *fir* (1.86x); and even in the worst cases (*minver*, 1.12x and *st*, 1.13x).

When the RT is reduced to only 32 lines, five out of six benchmarks still improve by more than 1.1x (the only exception is *st*, given its small reuse rates). Also, for most benchmarks, note how a 16K or even a 4K-line RT already places the improvements in performance near to the theoretical maximum (the *best case*) of the technique. Comparing to a 4K-line RT, for example, the best case brings no improvement in *ludcmp*, and increases *qurt* and *lms* performance only marginally, by 2% and 7%, respectively. This fact highlights function arguments very often repeat during execution and present limited variability. The exception is *fir*, in which the reuse rates increase significantly with larger table sizes. In the best case, its performance improves by 2.44x compared to the baseline (and 67% more than the 4K-line RT).

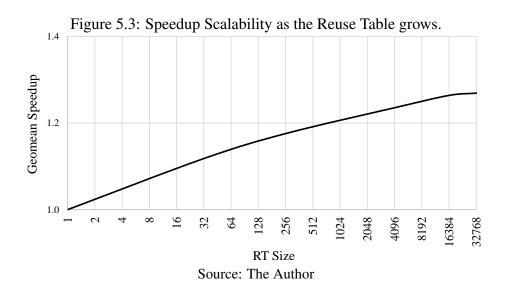

Finally, we can observe the speedup scalability as the RT grows. Figure 5.3

Figure 5.2: Speedup for different Reuse Table sizes compared to the baseline.

presents a comparison among the RT depth (in  $\log_2$  horizontal axis) and the correspondent geometric mean speedup achieved (in the vertical axis). It elucidates that, in some cases, we can achieve considerable gains in performance with low resource overhead, as will be shown later. For example, a 32-line RT can provide a speedup of 1.12x over the baseline, while it can reach 1.18x of improvements with 256 lines. A 4K-line RT, which fits in all five tested FPGAs (which will be discussed later) can reach 1.23x speedup. Therefore, even resource-limited FPGAs can benefit from applying the proposed mechanism. When it comes to high-end FPGAs, the available BRAMs can be used to increase even more the RT size and consequently get closer to the maximum speedup possible for applications with high reusability rates (e.g., *fir*).

### **5.2 Function Reuse in Multi-Core Environments**

#### 5.2.1 Experimental Methodology

The  $\rho$ -VEX processor, in which our work is strongly based on, has several limitations for running real-life benchmarks: e.g., it runs with no operating systems and therefore cannot call any traditional system function like for file and memory handling. More importantly, it cannot run parallel programs, which would be appreciable to this work. Although we could generate *reuse traces* by modifying other simulators that support parallel applications (as long as it respects the *reuse trace* format presented in Figure 4.5), we would be changing the simulation platform, and thereby affecting the results analysis, which is specially inadequate to compare the multi-core results with single-core results, presented previously. Moreover, we want to keep the  $\rho$ -VEX as the platform since it provides reliable results in area.

We have constrained our multi-core test setup to multiple programs running the same kernel, but with different inputs - as it is not possible to run pure parallel applications in  $\rho$ -VEX- maintaining our benchmarks set (fir, lms, ludcmp, minver, qurt, st) and the reusable functions (add, sub, mul, div, in double FP). The baseline continues to be the system without function reuse. For each benchmark *B*, *four* versions, with different inputs *i* were created:  $B_{i1}, B_{i2}, B_{i3}, B_{i4}$ . We generated the *reuse trace* for each of these versions, which were combined among each other to feed FORMOSA with all possible versions combinations of benchmarks (see Table 5.1), and get speedup results.

To examine the benefits of using a shared RT we always compare scenarios where the total BRAM per configuration is maintained, in other words, we preserve the RT size

| Scenario                                               | Description                                          | RT Size as Seen by the Applications                                     |  |  |  |  |

|--------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| B_i1                                                   | <i>B_i</i> 1 running with a dedicated RT             | $B_i1$ sees an RT with size $S$ .                                       |  |  |  |  |

| B_i2                                                   | <i>B_i</i> 2 running with a dedicated RT             | $B_{i2}$ sees an RT with size S.                                        |  |  |  |  |

| B_i3                                                   | <i>B_i</i> 3 running with a dedicated RT             | $B_i3$ sees an RT with size S.                                          |  |  |  |  |

| B_i4                                                   | <i>B_i</i> 4 running with a dedicated RT             | $B_{i4}$ sees an RT with size S.                                        |  |  |  |  |

| B_i1, B_i2                                             | <i>B_i</i> 1 and <i>B_i</i> 2 sharing the RT         | $B_i1$ and $B_i2$ see a shared RT with size $2 * S$ .                   |  |  |  |  |

| B_i1, B_i3                                             | <i>B_i</i> 1 and <i>B_i</i> 3 sharing the RT         | $B_{i1}$ and $B_{i3}$ see a shared RT with size $2 * S$ .               |  |  |  |  |

| B_i1, B_i4                                             | <i>B_i</i> 1 and <i>B_i</i> 4 sharing the RT         | $B_i1$ and $B_i4$ see a shared RT with size $2 * S$ .                   |  |  |  |  |

| B_i2, B_i3                                             | <i>B_i</i> 2 and <i>B_i</i> 3 sharing the RT         | $B_i2$ and $B_i3$ see a shared RT with size $2 * S$ .                   |  |  |  |  |

| B_i2, B_i4                                             | <i>B_i</i> 2 and <i>B_i</i> 4 sharing the RT         | $B_i2$ and $B_i4$ see a shared RT with size $2 * S$ .                   |  |  |  |  |

| B_i3, B_i4                                             | <i>B_i</i> 3 and <i>B_i</i> 4 sharing the RT         | $B_i3$ and $B_i4$ see a shared RT with size $2 * S$ .                   |  |  |  |  |

| <i>B_i</i> 1, <i>B_i</i> 2, <i>B_i</i> 3, <i>B_i</i> 4 | $B_i1, B_i2,$<br>$B_i3$ and $B_i4$<br>sharing the RT | $B_i1$ , $B_i2$ , $B_i3$ and $B_i4$ see a shared RT with size $4 * S$ . |  |  |  |  |

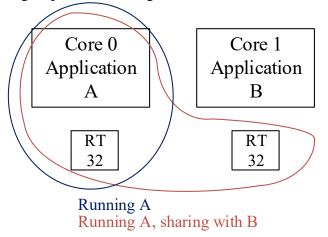

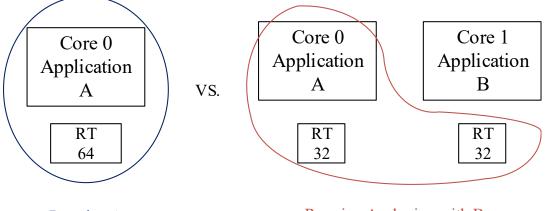

per core, as we show in Figure 5.4. When we share the RT, an application will see a larger table, which does not mean that we have used more BRAM. Instead, the application can simply access a table from another core which formerly was not possible. If we share the RT in a dual-core, applications will see an RT two times larger. If we share the RT in a quad-core, applications will see an RT four times larger. As we can have single, dual, or quad-core sharing scenarios, results are always presented in relation to the table size per core, which is maintained regardless the number of total cores.

Figure 5.4: Measuring Impacts of Sharing the Reuse Table from a Multi-core Scenario.

(a) Maintaining the size per core, 32 lines in this case, explicits the benefits of sharing the RT. This is the approach we use in our performance analysis.

Running A

Running A, sharing with B

(b) Maintaining the total size, 64 lines in this case, is not a fair comparison since it compares two different configurations: sing-core and dual-core. We do not want to pay the cost of more cores, but instead, demonstrate how we could benefit from sharing the RT in a former multi-core scenario.

Source: The Author

### **5.2.2 Inputs Definition**