# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

JOÃO PAULO CARDOSO DE LIMA

# PIM-gem5: a system simulator for Processing-in-Memory design space exploration

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Advisor: Prof. Dr. Luigi Carro

Porto Alegre March 2019 Lima, João Paulo Cardoso de

PIM-gem5: a system simulator for Processing-in-Memory design space exploration / João Paulo Cardoso de Lima. – Porto Alegre: PPGC da UFRGS, 2019.

87 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2019. Advisor: Luigi Carro.

1. Processing-in-memory. 2. System simulator. 3. 3D-stacked memory. 4. . I. Carro, Luigi. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. João Luiz Dihl Comba Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"A very large part of space-time must be investigated, if reliable results are to be obtained." — ALAN TURING

# ACKNOWLEDGMENTS

I want to thank and dedicate this thesis to every person who has been involved in my academic life. First, I would want to give special thanks to Professor Luigi Carro for his guidance and words of motivation and inspiration. I want to convey my gratitude to Paulo and Rafael for the discussions and cooperation in many works. Finally, I would like to thank all my beloved relatives and friends, who have been so supportive along the way of my academic journey.

## ABSTRACT

Processing-in-Memory (PIM) has been recently revisited to address the issues of memory and power wall, mainly due to the maturity of 3D-stacking manufacturing technology and the increasing demand for bandwidth and parallel access in emerging data-centric applications. Recent studies have shown a wide variety of processing mechanisms to be placed in the logic layer of 3D-stacked memories, not to mention the already available 3D-stacked DRAMs, such as Micron's Hybrid Memory Cube (HMC). Most of the studies in PIM architectures use the HMC as target memory, since its logic layer is suitable for placing processing logic in the memory device. Nevertheless, the lack of tools for rapid prototyping can be a limiting factor to explore new architectures, mainly when computer architectures aim to simulate system integration. In this document, we present a PIM support for the broadly adopted gem5 simulator and a methodology for prototyping PIM accelerators. Using the proposed simulator, computer architects can model a full environment and address open problems in the PIM research field. Also, we present two case studies of a fixed-function and a programmable logic PIM placed alongside each vault controller, and we highlight the generic points of our implementation which can be used to the exploit efficiency of new PIM accelerators.

Keywords: Processing-in-memory. System simulator. 3D-stacked memory. .

# PIM-gem5: um simulador de sistemas para exploração de espaço de projeto em arquiteturas de processamento em memória

## **RESUMO**

O conceito de Processamento em Memória (PIM) está sendo revisitado recentemente para tratar de problemas relacionados ao gargalo de memória e energia dos sistemas computacionais atuais. A retomada à pesquisa em PIM deve-se principalmente à maturidade da tecnologia de fabricação de circuitos 3D e à crescente demanda por banda de memória e acesso paralelo em novas aplicações que são centradas em dados. Para conciliar aceleração e eficiência energética em aplicações emergentes, estudos recentes investigaram diferentes projetos de circuitos digitais de processamento para a camada lógica de memórias 3D, sem mencionar as memórias em produção como o Hybrid Memory Cube (HMC) da Micron, que integram camadas de circuitos lógicos e DRAM por vias de alta velocidade. A maioria dos estudos em arquiteturas PIM usa o HMC como memória alvo, já que sua camada lógica é adequada para inserir lógica de processamento no dispositivo de memória. No entanto, a falta de ferramentas para prototipagem rápida pode ser um fator limitante para explorar novas arquiteturas, principalmente quando estas arquiteturas necessitam simular a integração de sistemas para avaliar e testar alguma solução em nível de sistema. Neste documento é apresentado um suporte para o simulador gem5 que permite a simulação de novos projetos e uma metodologia para prototipagem de aceleradores PIM. Usando o simulador proposto é possível modelar um ambiente completo e abordar problemas em aberto no campo de pesquisa de PIM. Além disso, dois estudos de caso de arquiteturas PIM são apresentados: um projeto do tipo função fixa e outro de lógica programável, e destacam-se os pontos genéricos da implementação do simulador que podem ser utilizados para a exploração de eficiência de novos aceleradores PIM.

Palavras-chave: Processamento em memória, Simulador de sistema, memórias 3D.

# LIST OF ABBREVIATIONS AND ACRONYMS

- ALU Arithmetic and Logic Unit

- AVX Advanced Vector Extensions

- BPO Bounded-Operand Processing-in-Memory Operation

- CAS Column Access Strobe

- CGRA Coarse-Grain Reconfigurable Array

- CISC Complex Instruction Set Computer

- CPO Compound PIM Operation

- CPU Central Processing Unit

- DDR Double-Data Rate

- DLP Data-level Parallelism

- DRAM Dynamic Random Access Memory

- EDP Energy Delay Product

- FCFS First-Come-First-Served

- FPGA Field Programmable Gate Array

- FPU Floating Point Unit

- FR-FCFSFirst-Ready First-Come-First-Served

- FSM Finite-State Machine

- FU Functional Unit

- GPU Graphics Processing Unit

- HBM High Bandwidth Memory

- HMC Hybrid Memory Cube

- ILP Instruction-level Parallelism

- ISA Instruction Set Architecture

- LSU Load-Store Unit

## LPDDR Low-Power Double-Data Rate

- NDP Near-Data Processing

- OoO Out-of-Order

- OS Operating System

- PCE Pointer-Chasing Engine

- PIM Processing-in-Memory

- RAS Row Access Strobe

- RISC Reduced Instruction Set Computer

- RMW Read-Modify-Write

- RTL Register-tranfer Level

- RVU Reconfigurable Vector Unit

- SerDes Serializer-Deserializer

- SIMD Single Instruction Multiple Data

- SSE Streaming Single Instruction Multiple Data Extensions

- TLB Translation Lookaside Buffer

- TSV Through-Silicon Via

- VPU Vector Processing Unit

# LIST OF FIGURES

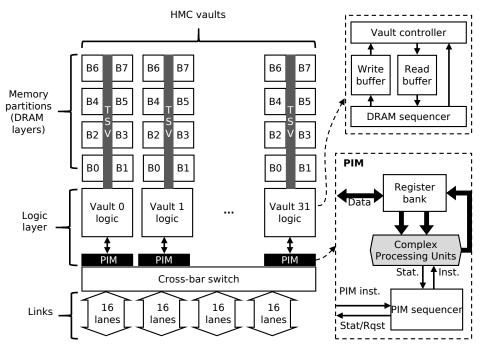

| Figure 2.1 HMC overview                                                            | 22   |

|------------------------------------------------------------------------------------|------|

| Figure 2.2 Three behaviors of master/slave protocol employed in the gem5 simulato  | r.26 |

| Figure 4.1 An example of system integration: a PIM-enabled stacked memory con-     |      |

| nected to a Chip Multiprocessor (CMP) via serial links in a 2.5D package           | 32   |

| Figure 4.2 HMC model broke down into serial link, crossbar switch and vault con-   |      |

| troller objects                                                                    | 33   |

| Figure 4.3 Address map fields 256 Byte maximum block size and 8GB                  |      |

| Figure 4.4 Crossbar switch model broke down into ports, buffers and switching laye |      |

| Figure 4.5 Crossbar switch model broke down into ports, buffers and switching laye |      |

| Figure 4.6 Vault controller broke down into queues, bank control, PIM FSM, DRAM    |      |

| commands and DRAM organization (layers and banks)                                  |      |

| Figure 4.7 Different position to place logic near memory                           |      |

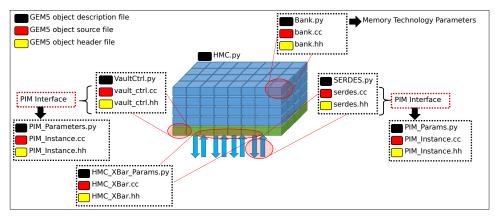

| Figure 4.8 Overview of source files used to implement fixed-function PIM logics    |      |

| in the gem5 simulator                                                              | 41   |

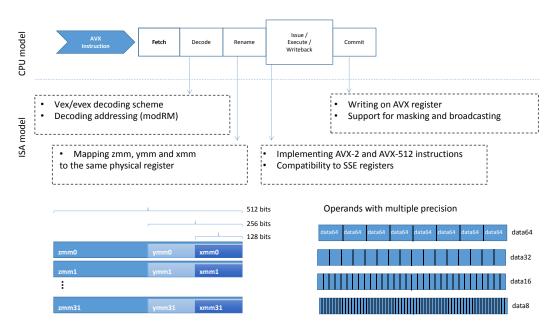

| Figure 4.9 Main modifications to include AVX-512                                   |      |

| Figure 4.10 Example of PIM instructions                                            |      |

| Figure 4.11 Example of hybrid code mixing X86 and PIM ISA                          |      |

| Figure 4.12 Flow of a PIM instruction in host CPU and memory system                |      |

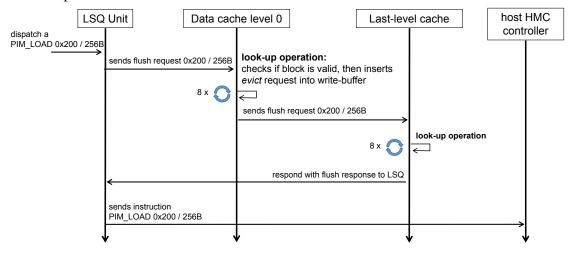

| Figure 4.13 Sequence diagram depicting the interaction between LSQ unit and        |      |

| cache model to provide data coherence for PIM instructions                         | 48   |

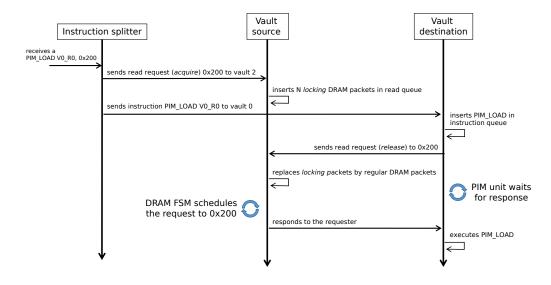

| Figure 4.14 Sequence diagram depicting the interaction between vault controllers   |      |

| and the instruction splitter in a PIM_load instruction                             | 50   |

|                                                                                    |      |

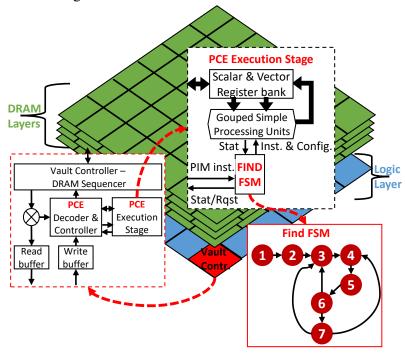

| Figure 5.1 Overview of the PCE mechanism                                           | 53   |

| Figure 5.2 Overview of the RVU architecture                                        |      |

| Figure 5.3 Setup mechanism used for all experiments with fixed-function PIM        | 55   |

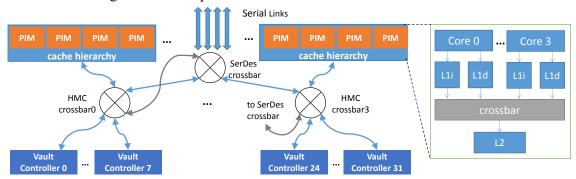

| Figure 5.4 Setup mechanism for PIM multi-core simulation                           | 57   |

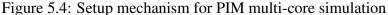

| Figure 6.1 Aggregate vault bandwidth for linear access pattern                     | 61   |

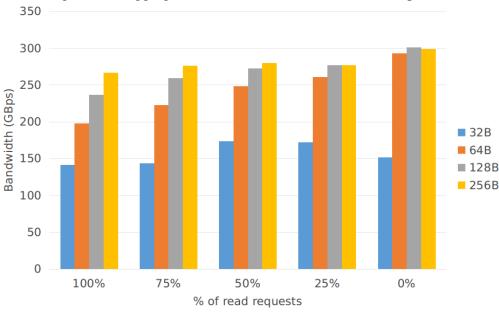

| Figure 6.2 Aggregate vault bandwidth for random access pattern                     | 62   |

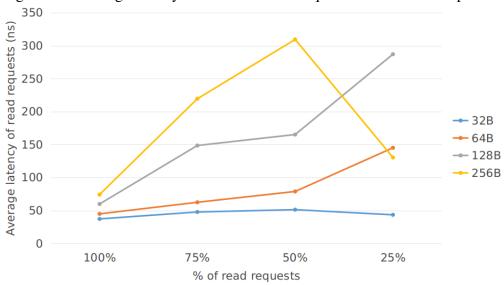

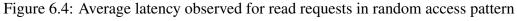

| Figure 6.3 Average latency observed for read requests in linear access pattern     | 63   |

| Figure 6.4 Average latency observed for read requests in random access pattern     | 63   |

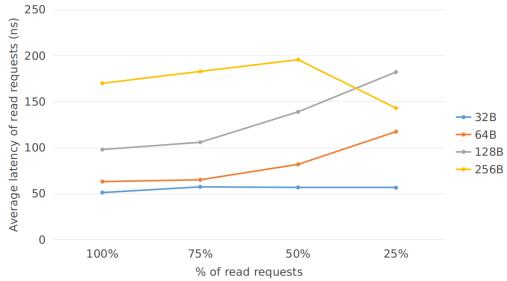

| Figure 6.5 Performance comparison between 16 in-order cores and single OoO         |      |

| core systems                                                                       | 64   |

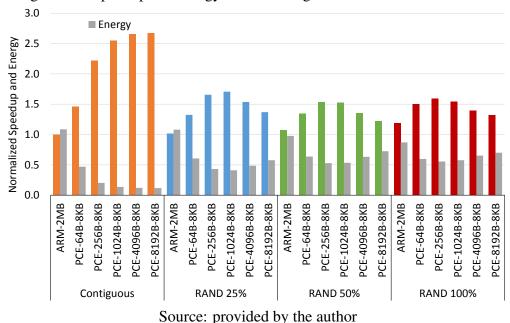

| Figure 6.6 Speedup and energy for traversing a linked list with 100k nodes         | 65   |

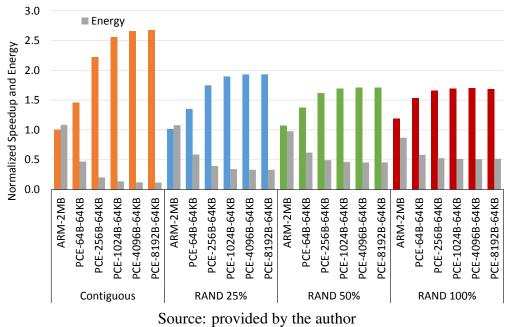

| Figure 6.7 Performance and energy for traversing a linked list with 100k nodes -   |      |

| PCE using 64kB of registers                                                        | 66   |

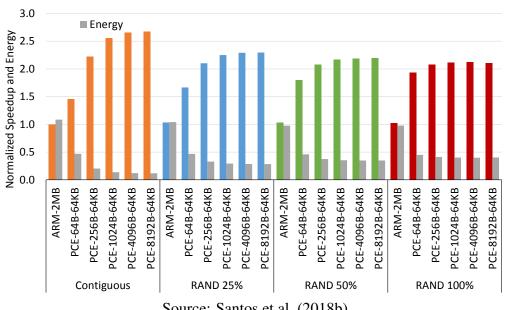

| Figure 6.8 Performance and energy consumption for traversing a linked list with    |      |

| 1M nodes                                                                           | 66   |

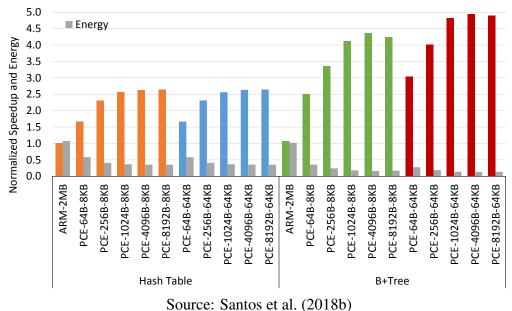

| Figure 6.9 Performance and energy consumption for traversing a hash table with     |      |

| 1.5M nodes and a b+tree with 3M nodes                                              | 67   |

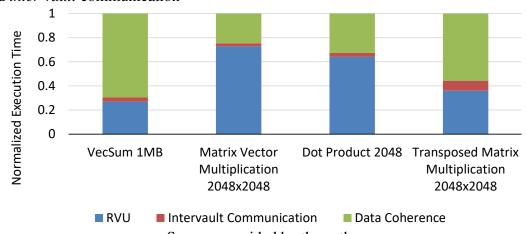

| Figure 6.10 Execution time of common kernels to illustrate the costs of cache co-  |      |

| herence and <i>inter-vault</i> communication                                       |      |

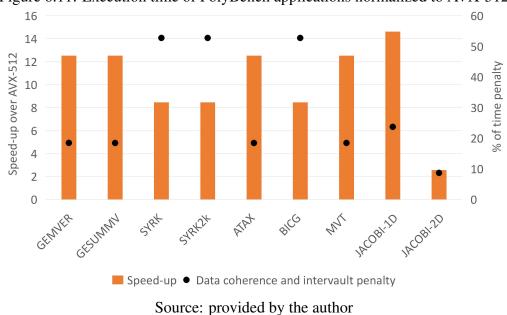

| Figure 6.11 Execution time of PolyBench applications normalized to AVX-512         | 70   |

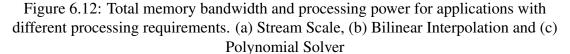

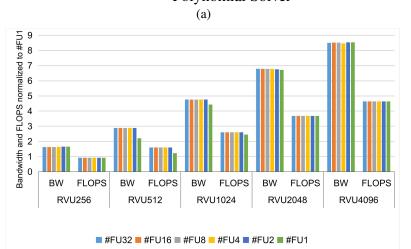

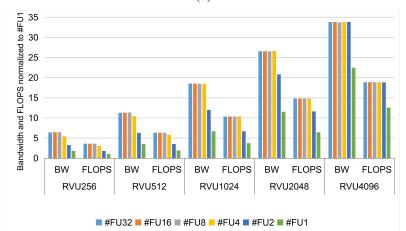

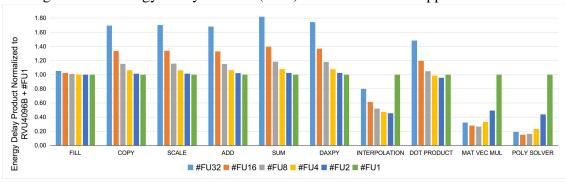

| Figure 6.12 Total memory bandwidth and processing power for applications with      |      |

| different processing requirements. (a) Stream Scale, (b) Bilinear Interpolation    |      |

| and (c) Polynomial Solver                                                          | 72   |

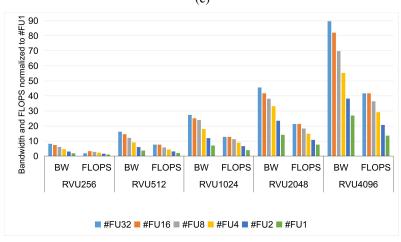

| Figure 6.13 Speedup and energy consumption in three applications. (a) and (b)  |    |

|--------------------------------------------------------------------------------|----|

| Stream Scale, (c) and (d) Bilinear Interpolation, and (e) and (f) Polynomial   |    |

| Solver Equation                                                                | 74 |

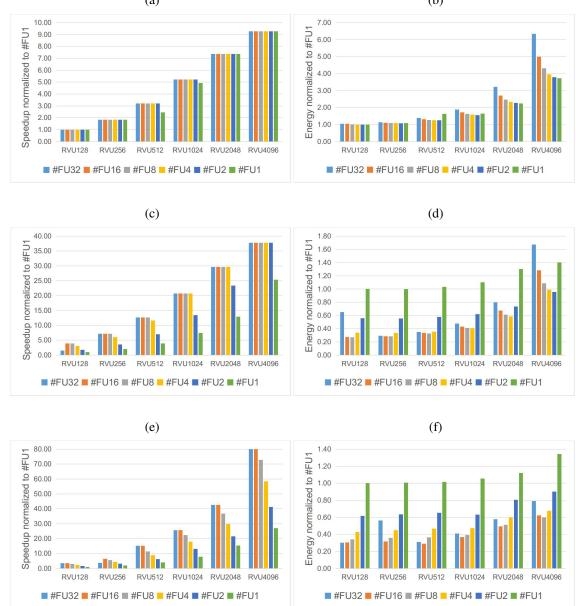

| Figure 6.14 Energy Delay Product (EDP) results for several application kernels | 75 |

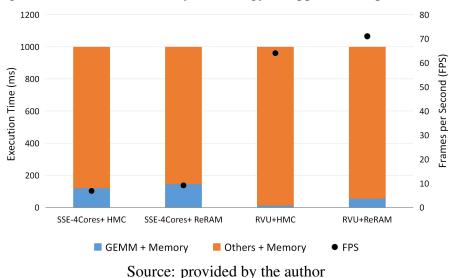

| Figure 6.15 Effect of memory technology on application's performance           | 75 |

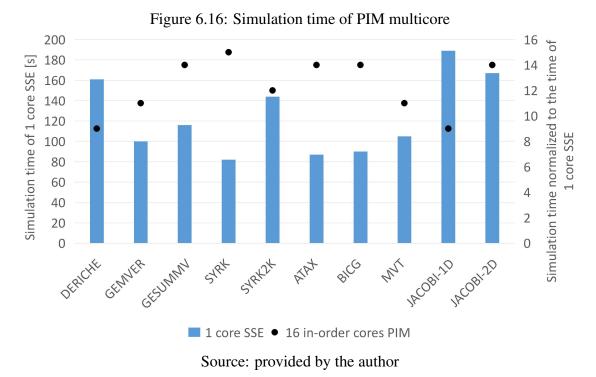

| Figure 6.16 Simulation time of PIM multicore                                   | 76 |

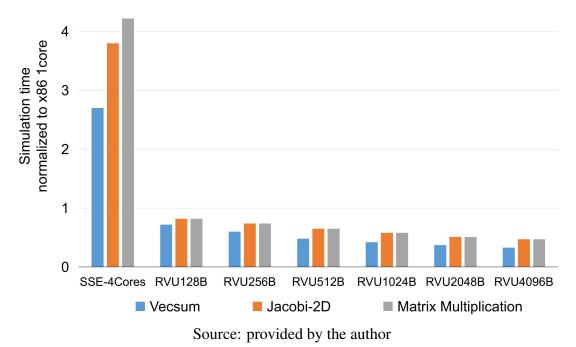

| Figure 6.17 Simulation time of RVU cores                                       | 77 |

# LIST OF TABLES

| Table 3.1 | Summary of features                                                                                                     | .30 |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.1 | List of parameterized items in the serial link and crossbar switch model                                                | .37 |

| Table 5.2 | HMC configuration<br>Baseline and Design system configuration of PCE<br>Baseline and Design system configuration of RVU | .58 |

| Table 6.1 | Estimate of development efforts                                                                                         | .77 |

# CONTENTS

| 1 IN7 | <b>FRODUCTION</b> 1                               | 14 |

|-------|---------------------------------------------------|----|

| 1.1 ( | Current problem                                   | 15 |

| 1.2 N | Notivation                                        | 16 |

| 1.3 ( | Dbjectives1                                       | 16 |

| 1.4 ( | Contributions                                     | 17 |

| 1.5 I | Document organization                             | 17 |

| 2 BA  | CKGROUND                                          | 19 |

| 2.1 3 | BD high-density DRAMs                             | 19 |

| 2.1.1 | HMC architecture                                  | 20 |

| 2.2 P | Processing-in-Memory                              | 21 |

| 2.2.1 | History                                           | 22 |

| 2.2.2 | Taxonomy of PIM logic                             | 24 |

| 2.3 S | System simulation basics                          | 25 |

| 3 RE  | LATED WORK                                        | 27 |

| 3.1 N | Memory modeling tools and simulators              | 27 |

| 3.2 S | Simulating a PIM-based architecture               | 28 |

|       | System-level challenges for PIM adoption          |    |

| 4 SIN | MULATOR SUPPORT FOR PIM ARCHITECTURES             | 32 |

|       | HMC modeling                                      |    |

| 4.1.1 | Address mapping                                   | 33 |

| 4.1.2 | High-speed serial links                           | 34 |

| 4.1.3 | Switch interconnection                            | 36 |

| 4.1.4 | Vault controller                                  | 37 |

| 4.2 P | PIM logic modeling                                | 39 |

| 4.2.1 | NDP and PIM with fully-programmable cores         | 39 |

|       | Fixed-function and Functional Unit-centered PIM   |    |

|       | Power and energy                                  |    |

| 4.3 H | Host interface and system integration4            | 42 |

|       | ISA extension                                     |    |

|       | ISA extension - PIM                               |    |

|       | Offloading PIM instructions                       |    |

| 4.3.4 | Cache coherence                                   | 47 |

| 4.3.5 | Data coherence inside HMC                         | 49 |

| 5 CA  | SE STUDIES, METHODS AND MATERIALS                 | 51 |

|       | Pointer-Chasing Engine                            |    |

|       | Reconfigurable Vector Unit                        |    |

|       | Experimental setup                                |    |

|       | HMC architecture setup                            |    |

|       | PIM multi-core setup                              |    |

|       | Fixed-function PIM for pointer-chasing operations |    |

|       | Reconfigurable Vector Unit                        |    |

|       | SULTS AND DISCUSSION                              |    |

|       | HMC validation                                    |    |

|       | PIM multi-core                                    |    |

|       | Fixed-function PIM for pointer-chasing operations |    |

|       | Reconfigurable Vector Unit                        |    |

|       | Evaluation of mechanisms to support RVU           |    |

| 6.4.2 | Design space exploration on RVU                   | 70 |

| 6.5 Applicability to emergent memory technologies | 73 |

|---------------------------------------------------|----|

| 6.6 Simulation time and development efforts       |    |

| 7 CONCLUSIONS AND FUTURE WORK                     |    |

| 7.1 Future Work                                   |    |

| 7.2 Published Papers                              |    |

| REFERENCES                                        |    |

## **1 INTRODUCTION**

Over the past decades, microprocessor performance has improved, and the energy cost per operation has decreased by many orders of magnitude, which have been resulted from equal efforts made in technology scaling and micro-architectural research (DANOWITZ et al., 2012; HU; STOW; XIE, 2018). However, as technology scaling slows down and we come to effectively notice the end of Moore's Law, the current process of manufacturing technology becomes more difficult and less beneficial to scale and shrink (KISH, 2002; TRACK; FORBES; STRAWN, 2017). To make matters worse, the scaling trends of off-chip memory bandwidth, which has historically been known as the major bottleneck of traditional architectures, are not as promising as the trends of on-chip computing capability.

As the traditional 2D manufacturing process could not diminish the performance gap between processor power and memory bandwidth, emerging die-stacking technologies have caught the attention of the memory industry to mitigate the effect of the bandwidth wall. By stacking several memory dies on top of each other and connecting them through dense vias, the 3D integration enabled high-bandwidth and high-capacity memory systems (HU; STOW; XIE, 2018). Although modern high-speed links and 2.5D designs have been used to deliver improved off-chip bandwidth, they still provide a lower bandwidth between the core die and the DRAM stacks (HASSAN et al., 2016), not to mention that energy consumption remains as a bottleneck to the overall system (HADIDI et al., 2017).

Due to constraints compelled by the end of Dennard scaling (DENNARD et al., 1974; ESMAEILZADEH et al., 2013), computer architects are required to come up with new designs to extract performance in order to provide more speed-up and consumes less energy. A viable approach to achieve such computing capacity consists of avoiding data movements by performing computation where the data resides, which is the main purpose of Processing-in-Memory (PIM) and Near-Data Processing (NDP) concept (SIEGL; BUCHTY; BEREKOVIC, 2016).

The main idea behind developing a PIM approach was to eliminate or at least to lower the memory wall (STANLEY-MARBELL; CABEZAS; LUIJTEN, 2011), the bandwidth wall (KAGI; GOODMAN; BURGER, 1996) and the power wall (POLLACK, 1999) gaps created by bringing data to be processed into the main processor. However, the insertion of 2D-integrated PIM brought some implications and problems that were not completely solved and, thus, corroborated as the main reasons for a not widely PIM adoption. Only with the advent of 3D-stacking technologies, which enabled new opportunities for integration of distinct technology process, that PIM research was revived.

## 1.1 Current problem

3D-stacking PIM presents a massive change to the current hardware architecture design and, consequently, reveals new challenges in how applications can extract enormous acceleration. Researches have historically relied on software simulators to enable architectural studies and evaluate their impact on benchmarks and real-life applications. The primary goal of such simulators is to allow design space exploration of PIM architectures and, in some cases, serve as a virtual prototype that enables earlier software design. Some simulators used in previous PIM architectural researches include: gem5 (BINKERT et al., 2011) PimSim (XU et al., 2018), Clapps (OLIVEIRA et al., 2017a), SiNuca (ALVES et al., 2015) and zsim (SANCHEZ; KOZYRAKIS, 2013) and other inhouse simulators (AHN et al., 2015).

However, most of these simulators struggle to deliver generic models for implementing PIM logic and a complete simulation platform encompassing both microarchitectural and system-level aspects. One of the essential requisites for PIM acceptance is easy programmability and system support, which may include code offloading, data coherence, virtual address translation, and other issues depending on the type of PIM logic. There is an increasing need for architectural and system-level approaches to solve these issues. Thus, the lack of tools for rapid prototyping can be a limiting factor to explore new solutions for PIM architectures, mainly when one wants to simulate full-system integration.

Many studies have relied on analytical models or separate simulators for evaluating their PIM designs (DRUMOND et al., 2017; ALVES et al., 2016). Nonetheless, analytical models do not provide important design metrics, and trace-based simulation is not as accurate as a real memory model driving the CPU model. Although this can be useful for a proof of concept, it can also be limiting for a proper design space exploration and also for serving as a virtual prototype, which requires more accurate simulations.

On the other hand, some of the more recent works have used highly accurate models in their experiments (OLIVEIRA et al., 2017a; LLOYD; GOKHALE, 2018), which yields useful statistics for a hardware-focused analysis. Although this approach can also provide rapid prototyping, the System-C models experience high simulation time, and most of the hardware-related metrics may not be useful for system-level evaluation.

#### **1.2 Motivation**

Despite all advances related to different types of PIM architectures, some issues are still major concerns to enable the adoption of PIM at the system-level. Problems associated with the programming model, data mapping, runtime scheduling support, granularity of PIM scheduling and applicability to emerging memory technologies are just some of them (GHOSE et al., 2018a). The increasing interest in evaluating how PIM architecture can affect the entire compute-stack is essential not only to enable GPPs and GPUs to use PIM capabilities, but also to allow in-memory accelerators.

The primary goal of such system-level exploration is to allow designers to identify memory and PIM logic characteristics that affect the efficiency of PIM execution. For instance, one can evaluate the trade-off between the number of PIM engines and memory bandwidth, or affinity of PIM engine and data location. However, many optimizations can only be made at execution time and, then, must be made by a system mechanism to avoid increasing the energy of PIM computation.

The complex interactions between the CPUs, Input/Output devices, memory system, and PIM logic are captured by using full-system simulation. As few previous simulators cannot provide a complete environment for the system and architectural PIM research, there are open questions not only for evaluating the benefits of more accurate models, but also for investigating novel interactions between system-level and PIM capabilities. Likewise, virtual prototypes are essential to the industry, since they provide high-speed functional software models of physical hardware, enabling concurrent hardware and software development. Thus, a complete simulation environment can also serve as a virtual prototype.

## **1.3 Objectives**

The main goal of this dissertation is to provide system-level information, which is translated into statistics, for different types of PIM logic. As much work has been done in system simulation, the first challenge consists of providing support for PIM simulation, which includes different programming and execution models, as well as correct models of memory system and system integration. Secondly, as the nature of PIM can widely vary, generic PIM mechanisms become the second challenge of this work. It is expected to allow the development of system-level solutions which apply to a wide variety of PIM architectures. Finally, the last challenge resides on demonstrating the ability to use the simulator to perform design space exploration in novel PIM proposals.

## **1.4 Contributions**

In this document, PIM-gem5, a PIM support for the broadly adopted gem5 simulator (BINKERT et al., 2011) and a methodology for prototyping PIM accelerators is presented. By using the PIM support described in this work, computer architects can model a full environment and address open issues on PIM research, such as connection to host processors, offloading mechanisms, Instruction Set Architecture (ISA) modifications, data coherence protocols, and address translation methods, just to list some of them.

The validation of the simulator includes two case studies of PIM logic placed alongside each vault controller of HMC, and we highlight the generic points of our implementation which can be used to exploit the efficiency of new PIM accelerators. Using the proposed implementation, we show the potential for energy reduction and performance improvement of different applications when compared to traditional architectures. Also, we demonstrate how any processor available in the gem5 platform can be simulated in a PIM fashion.

#### **1.5 Document organization**

This thesis is structured as follows: an overview of 3D-stacked memories and the research field of Processing-in-Memory is presented in Chapter 2. In Chapter 3, we present the recent developments on modeling and simulation tools, as well as system-level challenges that prevent PIM architectures to be broadly adopted.

Then, the implementation of the support for PIM simulation in gem5 is reported in Chapter 4, which is broken down into details of memory and PIM instance modeling, system integration, and host interface. Two case studies of PIM architectures are described in Chapter 5, which captures the potential of PIM-gem5 to simulate different PIM types. In Chapter 5.3 we present the experimental setup used to validate the memory modeling and evaluate the performance of the case studies. Then, in Chapter 6, we present the main results of the HMC and case studies simulation. Finally, some considerations about this thesis and opportunities for future works are discussed in Chapter 7.

## **2 BACKGROUND**

As the Dynamic Random Access Memory (DRAM) has been a de facto standard for main memory, some basic concepts of recent development on memory systems based on DRAM, which includes high-performance interfaces for 3D-stacked DRAM, are presented. Next, an overview of the research field on PIM architectures and taxonomy is described, as well as basic notions of simulation platforms for enabling the design and exploration of computer-system architecture.

#### 2.1 3D high-density DRAMs

3D high-density memories rely on multiple stacked DRAM dies to provide high bandwidth and capacity to meet the demand of today's system workloads. Most of the today's major memory manufacturers develop 3D-DRAMs, such as Samsung's DDR4, Tezzaron's DiRAM4, AMD and Hynix's High Bandwidth Memory (HBM) and Micron's Hybrid Memory Cube (HMC). Due to the limitation of parallelism and bandwidth of Double Data Rate (DDR) interfaces for high-performance computing, different industry leaders have gathered efforts to propose high-performance RAM interface for throughsilicon vias (TSV)-based stacked DRAM memories.

Although significant changes can be seen in these new interfaces over planar DRAM devices, 3D high-density memories use the same basic DRAM circuitry, array organization, and DRAM operations. For details of DRAM technology and devices, we refer the interested readers to (JACOB; NG; WANG, 2010; HANSSON et al., 2014; KIM, 2016; GHOSE et al., 2018b).

The HBM and HMC interfaces are the most prominent specification in the present time. For instance, the HBM is a JEDEC's standard composed of four DRAM dies and one single logic die at the bottom. Each DRAM die consists of 2 channels, where each channel has 1 Gb density with a 128-bit data interface and 8 independent banks (STAN-DARD, 2013; LEE et al., 2014). The logic die is divided in PHY, which is responsible for interfacing DRAM and memory controller, TSV arrays, and a direct access port for testing. HBM communicates with memory controller through a 2.5D interposer, which has 1024-bit. The available bandwidth with an 8-channel read operation is 128 GBps at 1.2V.

## 2.1.1 HMC architecture

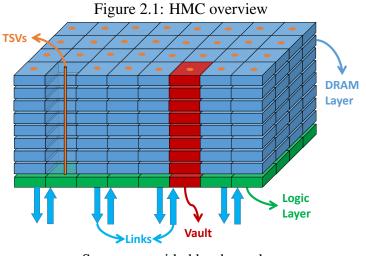

As described in the last specification (CONSORTIUM et al., 2015), the HMC is a package containing either four or eight DRAM die and one logic die stacked together and connected by TSV, as shown in Figure 2.1. Within each cube, the memory is organized vertically into *vaults*, which consist of a group of corresponding memory portions from different DRAM dies combined with a *vault* controller within the logic die, as shown in the red region of Figure 2.1. Each HMC contains 16 or 32 *vaults* depending on the version and each *vault* controller is functionally independent to operate upon 16 memory banks in the eight DRAM layers configuration. The available bandwidth from all *vaults* is up to 320 GBps and is accessible through multiple serial links, each with a default of 16 input lanes and 16 output lanes for full duplex operation. All in-band communication across a link is packetized and there is no specific timing associated with memory requests, since *vaults* may reorder their internal requests to optimize bandwidths and reduce average latency.

A request packet includes an address field of 34 bits for internal memory addressing (vault, bank and DRAM address) within the HMC. The address mapping is based on the maximum memory block size (32B, 64B, 128B OR 256B) chosen in the address map mode register. This mapping algorithm is reffered to as low interleave, and forces sequential addressing to be spread accross different vaults and then across different banks within a vault, thus avoiding bank conflict. The user can select a specific address mapping scheme to optimize the bandwidth based on the characteristics of the request address stream.

Some of the benefits of the HMC over the traditional DRAM modules can be summarized as:

**Capacity:** one of the advantages of the HMC architecture resides on the capacity and density problem of current DRAM devices. Due to the difficult of scaling DRAM cells, DRAM density have slowed in recent years. With stacked DRAM dies, a single cube can contain a multiple of 4 or 8 times the storage in the same package footprint as a single DRAM device. Even improvements in traditional devices, such as DDR4 standard, has 3D stacking extension to increase density without increasing pin count.

**Parallelism and Aggregated Bandwidth:** the high bandwidth of HMC is achieved by combining dense TSV (thousands of TSVs in each cube) and transferring at a high frequency. In addition to the TSVs, each cube has several high speed serialized links to provide high-bandwidth to off-chip processors. Since each *vault* is operated independently, each one with one or more banks, there is a high level of parallelism inside of a cube. Each *vault* is practically equivalent to DDRx channels. With 16 or 32 vaults per cube, the *vault-parallelism* adds an order of magnitude within a single package. As vertical stacking allows a greater number of banks per vault, bank-level parallelism also increases the bandwidth within each vault.

**Energy Efficiency:** by reducing the length and capacitance of the connections between the memory controller and the DRAM devices with short TSV bus, the HMC is more efficient than traditional DDRx memories. The first measurements of HMC indicates 3.7 pJ/bit for the DRAM layers and 6.78 pJ/bit for the logic layer, while existing DDR3 modules spend 65 pJ/bit (JEDDELOH; KEETH, 2012). In a design space exploration, Weis et al. (2011) demonstrate that 3D-stacked memories like HMC can be 15x more efficient than an equivalent LPDDR from Micron. Current estimations considering the DRAM process scaling were not available in the literature.

**Interface Abstraction:** Differently from DDRx systems, a CPU must use a general protocol to communicate with the cube or a topology of cubes that decouple memory controller functions from CPU. The CPU sends read and write commands, instead of traditional RAS and CAS commands, that are converted into device-specific commands within the *vault* controller. This effectively hides the natural silicon variations and bank conflicts within the cube and way from the host CPU. The DRAM can be optimized on a vault-basis without exposing the change to the CPU. (SCHMIDT; FRÖNING; BRÜN-ING, 2016; JEDDELOH; KEETH, 2012).

**Near-Memory computation:** as presented in the specification (Hybrid Memory Cube Consortium, 2013b), the logic die of HMC not only plays a role as vault controller, but also supports a set of atomic operation instructions. These instructions operate on 16-bytes memory operands and writes the result back to the DRAM arrays following a read-modify-write sequence.

# 2.2 Processing-in-Memory

Modern applications, such as data analytics, pattern recognition and bioinformatics, can benefit from PIM since they present poor temporal locality and can use in-memory computing instead of passing the data back and forth through the memory hierarchy (ZHU et al., 2013; SIEGL; BUCHTY; BEREKOVIC, 2016).

Source: provided by the author

## 2.2.1 History

The concept of PIM as presented today appeared in the 90s, where the main idea behind developing a PIM approach was to eliminate or at least to lower both the memory wall (STANLEY-MARBELL; CABEZAS; LUIJTEN, 2011), the bandwidth wall (KAGI; GOODMAN; BURGER, 1996) and the power wall (POLLACK, 1999) gaps. The first studies on 2D-integrated PIM brought some implications and problems that were not completely solved and, thus, corroborated as the main reasons for not having 2D-integrated PIM largely adopted. Only with the advent of 3D-stacking technologies, which enabled new opportunities for integration of distinct technology process, and also with the arising of data-intensive workloads that the PIM research field was revived and leveraged.

In the past decades, several attempts were made to include processing logic in different locations of the memory system. The main contributions are listed below and classified according to the location where processing units were placed:

**Processing in the DRAM Module or Memory Controller:** some recent works have examined how to process near the memory, but not within the DRAM chip, to leverage conventional DRAM modules or memory controllers (SESHADRI et al., 2015; ASGHARI-MOGHADDAM et al., 2016; HASHEMI et al., 2016). This approach was proposed mainly to reduce the cost of PIM manufacturing, as DRAM chip remains unmodified and it avoids the use of still costly 3D-stacking technology. However, it may suffer from challenges in programmability and consistent PIM interface to tackle the problems of address translation and cache coherence challenges. Moreover, the efficiency of PIM execution in this approach is limited, since it cannot take advantage of internal

memory bandwidth as in-DRAM chip mechanisms and 3D-stacked accelerators do.

Processing in 3D-stacked Memory: meanwhile, several works (KLEINER; KUHN; WEBER, 1995; LIU et al., 2005) studied the possibility of stacking memory dies and interconnecting them through very small vias, granting the emerging of 3D-stacked processingin-memory approach. Moreover, the evolution of Through-Silicon-Via (TSV) technique (DAVIS et al., 2005; SAKUMA et al., 2008) solved some problems present on previous versions of 3D-stacked memory like thermal dissipation influences making feasible the production and exploitation of stacked memories as done by the HMC (Hybrid Memory Cube Consortium, 2013a) and HBM (STANDARD, 2013) products. Consequently, since 2013 3D-stacked PIMs have regained focus with different projects approaches, varying from multicore systems placed into the logic layer as in (PUGSLEY et al., 2014; AHN et al., 2016; AZARKHISH et al., 2016; DRUMOND et al., 2017; SCR-BAK et al., 2017), alternative cores (NAIR et al., 2015; KERSEY; KIM; YALAMAN-CHILI, 2017), Single Instruction Multiple Data (SIMD) units (SANTOS et al., 2017; OLIVEIRA et al., 2017b), Graphics Processor Units (GPUs) (ZHANG et al., 2014; PAT-TNAIK et al., 2016) to Coarse-Grain Reconfigurable Arrays (GAO; KOZYRAKIS, 2016; FARMAHINI-FARAHANI et al., 2015a). Despite all advances related to 3D-stacked memory PIM, some issues are still major concerns in the recent 3D-PIM architectures such as how to perform offloading of instructions from the host processor to the PIM unit, data coherence among host processor and PIM units.

**Processing within the memory chip or memory array:** several recent works have investigated how to perform memory and arithmetic operations directly within the memory chip and also the memory array. These works take advantage of architectural properties of memory circuits and add bulk operations to them as new functionality to the memory chip. They can significantly improve computational efficiency and do not require 3D integration, although they still face the same challenges of processing in 3D-stacked memory. Most of the mechanisms in the literature following this concept rely on the bulk copy, data initialization (SESHADRI et al., 2013), bulk bitwise operations (SESHADRI et al., 2017; LI et al., 2016; KANG et al., 2017; ANGIZI; HE; FAN, 2018), and simple arithmetic operation (SHAFIEE et al., 2016; CHI et al., 2016) in different memory technologies.

Despite all advances related to 3D-stacked and in-DRAM PIM, some issues are still major concerns, such as how to perform offloading of instructions from the host processor to the PIM unit, cache coherence and interconnection communication network between host processor and PIM, and also between PIM units.

## 2.2.2 Taxonomy of PIM logic

Regarding execution model, two main classes of processing units are identified by Loh et al. (2013): Fully programmable PIM and Fixed-function PIM.

- Fully programmable PIM: This class comprises full or simplified processors which fetch, decode and execute instructions from code offloaded to the PIM accelerator. Since existing core processors are used as PIM units, existing compilers can be used without any change. On the other hand, it generally requires programmer's efforts to manage the communication between host processors and PIM, and also requires the use of external libraries such as OpenMP and MPI (FANG et al., 2012; DRUMOND et al., 2017; NAIR et al., 2015).

- **Fixed-function PIM:** This class provides pre-defined simple FUs, or fixed operations based on existing memory access instructions. An extension of *LOAD* and *STORE* instruction could encode PIM operations directly in the opcode or as a special prefix in case of General Purpose Processors' ISA. Fixed-function PIM operations can be divided into Bounded-operand PIM Operation (BPO) and Compound PIM Operation (CPO). BPO comprises a single operation or a limited set of operations on single or multiple data (e.g., add and multiply-accumulate), while CPO includes a dynamic number of operations and arbitrary number of memory locations.

The authors do not limit their classification as the only one possible. In fact, they acknowledge that fixed-function can be more complex than the examples shown in their position paper. The exploration of fixed-function PIMs can lead to partially programmable designs, although they cannot be classified as fully programmable PIM since they do not present a mechanism for fetching instructions, translating virtual addresses, and other mechanisms present in fully programmable cores. In addition, there are several challenges regarding system-level decisions and compiler tools in fixed-function PIMs, since a new ISA organization, a different virtual memory translation, and data coherence mechanism, and other requirements may be expected.

In recent 3D-stacked PIM, most of the studies consider a logic layer organized into *vaults* similar to the one available on HMC devices, where simple processing units are placed within each *vault* to minimize communication costs (Hybrid Memory Cube Consortium, 2013a). Also, in recent PIM architectures based on HMC architecture (AHN et al., 2016; SANTOS et al., 2017), each processing unit is placed next to its home *vault* router to reduce routing complexity and improve performance. Regarding communication costs, *fully programmable* PIM usually requires a complex memory hierarchy. Inside the *vault*, area and power dissipation are critical constraints that can lead to performance limitations (ECKERT; JAYASENA; LOH, 2014; ZHU et al., 2016; LIMA et al., 2018). In this case, communication between different cores across different *vaults* tends to harm performance, and/or require more attention from the PIM programmer (AHN et al., 2016).

#### 2.3 System simulation basics

Before diving into the implementation of the PIM support in gem5, some details regarding simulation mode, accuracy of simulation and interfaces for connecting models have to explained.

Although cycle-based models can be easily portable to different simulation frameworks, as they do not depend on any specific event semantics, a huge penalty is paid on simulation speed. Event-based models, instead, are only updated when part of the model has to be changed and, then, it skips ahead to the next event. The simulation speed is increased by orders of magnitude. Even though event-based models are tied to a particular simulation platform, many models created on it can also be applied to any discrete event simulator. The gem5 simulator (BINKERT et al., 2011) was chosen as basis of this work due to mature event-based models.

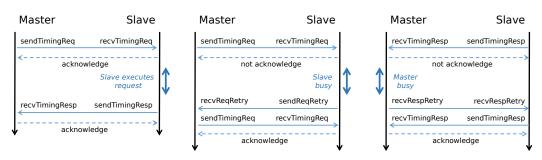

Apart from this level of abstraction, which is suitable for system simulation, gem5 enables three more modes. These simulation modes are closely coupled with the master/slave port interface, which are the most basic, rigid interface protocol in the simulator to implement communication between CPU models and memory system models. As summarized in Figure 2.2, the master/slave protocol allows four sequences of message exchanging in which the request/response is straightforwardly transmitted, or either the slave or master module denies the request/response when busy. These ports implement three different memory system modes: timing, atomic and functional. The timing mode is used to provided correct simulation results dynamic behavior since it makes use of events. Atomic and functional modes, instead, are used in special circumstances that do not require accurate results of the memory system, such as in fast-forwarding simulations and loading binary from the host to the simulated system's memory.

Figure 2.2: Three behaviors of master/slave protocol employed in the gem5 simulator

Source: provided by the author

In addition to hardware simulation modes, gem5 enables architects to use two modes with different system-level accuracy. The full system mode simulates not only the hardware, but also system details similar to emulators like QEMU<sup>1</sup> and hypervisors. This allows gem5 to execute unmodified OS binaries and investigate the impact of operating system, Input/Output devices and other low-level details Likewise, a less accurate system model is supported in the system emulation mode. This mode restricts gem5 to use only basic OS syscalls, which are imitated, rather than executed from the OS binaries. This mode does not require any OS kernel, device drivers, disk image or interaction with the OS.

The models are generally integrated in full-system simulation to form a complete architectural-exploration framework. For more details, we refer the readers to gem5 tutorial and documentation (LOWE-POWER, 2017; LOWE-POWER, 2019; BINKERT et al., 2011).

### **3 RELATED WORK**

This chapter presents the recent development of tools for exploring memory and processing-in-memory design space, as well as system-level challenges that prevent PIM architectures to be broadly adopted.

### 3.1 Memory modeling tools and simulators

When it comes to DRAM design space and architectural research, the tools are divided into DRAM bank/chip modeling and DRAM controller simulation tools. Developed by HP Labs, CACTI (CHEN et al., 2012) is one of the most cited tools for DRAM modeling. CACTI produces as output energy and timing parameters, and also an estimation of performance and power for future DRAMs, but it is not suitable for exploring advanced DRAM architectures or devices (WEIS et al., 2017). DRAMSpec (WEIS et al., 2017), in turn, generates datasheet timing and current parameters, as well as it provides support for novel memory devices, such as HMC. The authors claim that their tool enables to explore DRAM design space and key parameters very fast with enough accuracy. Also, the estimation tool is seamlessly integrated into gem5 (BINKERT et al., 2011).

The second type of tools features the DRAM controller simulation driven by previously collected memory-access patterns or by a simulated processor. Some examples of planar DRAM simulators include: DRAMSim2 (ROSENFELD; COOPER-BALIS; JACOB, 2011), Ramulator (KIM; YANG; MUTLU, 2016), DRAMSys (JUNG; WEIS; WEHN, 2015). DRAMsim2 provides a cycle-accurate simulation of DRAM using Verilog descriptions. Although current research efforts try to abstract from low-level accuracy to speed-up simulation time, DRAMsim2 is still a largely adopted tool. Ramulator offers an abstract C++-based simulation which part of the model needs to be clocked at a specific point in time. DRAMSys leverages transactional-level modeling to provide rapid simulation in conjunction with approximated timing to enable characterization of new DRAM subsystems and even allows the evaluation of 3D-stacked memories.

While previous mentioned simulators were focused on planar memories, recent simulators have been focusing on enabling 3D-stacked models, which includes HMC-Sim (LEIDEL; CHEN, 2016), CasHMC (JEON; CHUNG, 2017), Clapps (OLIVEIRA et al., 2017a) and gem5's simple HMC model (AZARKHISH et al., 2015). HMC-Sim provides cycle-accurate memory simulation for any of the supported HMC 1.0 and 2.0 configura-

tions. Though, the approach taken to implement HMC instructions harms scalability for future PIM extension and also the interoperability between different host operating systems. CasHMC is a C++ simulator that implements most of the HMC resources, as packet error detection, link flow control, and HMC instructions. The drawbacks of this tool are due to its offline simulation, which only uses an external memory trace as input and the lack of PIM extension. Clapps (OLIVEIRA et al., 2017a) is a cycle-accurate trace-driven HMC simulator that includes the HMC commands and a generic interface for custom PIM logic. As this tool is built on System-C library, it can be integrated into other simulation platforms such as gem5.

A previous attempt of modeling HMC architecture on gem5 was made by Azarkhish et al. (2015), and their contribution was added to gem5's repository. However, their experiments did not achieve the vault bandwidth reported by Micron due to mistakes in the memory interleaving. In fact, each vault controller received a single contiguous memory range of 256 MB, preventing the cube to exploit both vault-level and bank-level parallelism in sequential request streams. In addition to that mistake, this model of HMC had three modes of interconnection, but all modes presented distortions to the HMC specification. These issues are related to an incorrect behavior on the address range assigned to each serial link, either limiting each link to a specific memory range or adding extra latency to provide complete memory range to all links.

## 3.2 Simulating a PIM-based architecture

Most of the recent PIM works focus on fully-programmable cores, which are generally simulated by adjusting constraints of 3D integrated circuits in existing simulators and by taking advantage of existing execution models and compilers. For example, zsim (SANCHEZ; KOZYRAKIS, 2013) is a fast and scalable simulator that supports thousand of core simulation, including PIM models (GAO; AYERS; KOZYRAKIS, 2015; GAO et al., 2017; SONG et al., 2018). As the full-system support is compromised to enable scalability, zsim provides a collection of lightweight user-level virtualization to ease execution of unmodified benchmarks. SiNuca (ALVES et al., 2015) is an accurate and validated simulator focused on Non-Uniform Cache Architectures (NUCA) simulation, which was also used in the previous PIM studies (ALVES et al., 2016; SANTOS et al., 2017). Though, this tool requires traces generated on a real machine without the influence of Operating System or other processes. Some past studies that consider a reconfigurable logic in-memory generally extend existing simulators. For instance, the CGRA model of (FARMAHINI-FARAHANI et al., 2015a) placed near commodity DRAM devices is simulated in the gem5 simulator (BINKERT et al., 2011), and the reconfigurable (GAO; KOZYRAKIS, 2016) is built on zsim (SANCHEZ; KOZYRAKIS, 2013).

On the other hand, fixed-function in-memory processing, which includes the HMC and the works of (AHN et al., 2015; GAO; SHEN; ZHUO, 2018; NAI et al., 2017; OLIVEIRA et al., 2017a), relies on a more varied design methodology which generally includes custom or in-house tools. Although there exist numerous PIM simulators, they still lack dealing with many challenges and difficulties in the PIM simulation. The first issue resides on the necessity of coupling a significant number of different tools to represent a whole computing system and its respective modules. In (XU et al., 2018), the authors presented a PIM simulator that relies on the integration of three memory simulators to provide interconnection and description of CPU architectures.

Likewise, in (YANG; HOU; HE, 2019) is presented a PIM architecture for Internetof-Things applications which relies on the integration of one simulator for simulating both PIM and host processing elements and a tool for estimating power consumption. Coupling several simulators to represent the desired computing system incurs drawbacks to the design life-cycle, making this simulation approach prohibitive. When considering different simulation environments, the architectural designers must have complete and in-depth knowledge about the simulators features, which in turn demands time-consuming tasks. Also, since the involved simulators may have different accuracy levels, system modeling patterns, and technological constraint representations, the result of the simulation might not present the desired precision.

Although (YANG; HOU; HE, 2019) utilizes the same architectural simulator for all the hardware components, different simulation accuracy level components are instantiated to compose the whole system. Thus, the simulation approach followed by (YANG; HOU; HE, 2019) not only needs a particular synchronization mechanism but also does not reflect a real scenario where the host processor is represented by an event-detailed processor description and the PIM elements are described only with atomic and no-delayed operations.

Meanwhile, other simulators require the generation of trace files as input to feed them. The main drawbacks inherit from the trace-based simulation approach are the necessity of previous execution of the target applications in a real machine and the gathering of relevant information such as executed instructions and data access addresses. Although (XU et al., 2018) and (OLIVEIRA et al., 2017a) are built over architectural cycle-accurate simulators, the PIM modeling and measurements are done by analyzing memory traces gathered during the simulation.

To summarize the main aspects desirable for PIM simulation tools, we gathered some features from the related simulators in Table 3.1. The cells marked as "-" indicate that the feature is provided, but the behavior is not correct, which is the case of many HMC models in current gem5-based tools. According to the characteristics listed in this table, PIM-gem5 is the only one to support full-system simulations, accurate HMC models and system-level mechanisms for PIM designs.

| Simulator                | Processor    | HMC          | System-level                 | PIM          | Full-system  |

|--------------------------|--------------|--------------|------------------------------|--------------|--------------|

|                          | sim          | model        | support for PIM <sup>1</sup> | extension    | support      |

| HMC-Sim (LEIDEL;         | Х            | Х            | Х                            | $\checkmark$ | Х            |

| CHEN, 2016)              |              |              |                              |              |              |

| CasHMC (JEON;            | Х            | $\checkmark$ | Х                            | $\checkmark$ | Х            |

| CHUNG, 2017)             |              |              |                              |              |              |

| Clapps (OLIVEIRA et      | Х            | $\checkmark$ | Х                            | $\checkmark$ | Х            |

| al., 2017a)              |              |              |                              |              |              |

| Zsim (SANCHEZ;           | $\checkmark$ | $\checkmark$ | Х                            | Х            | Х            |

| KOZYRAKIS, 2013)         |              |              |                              |              |              |

| SiNuca (ALVES et al.,    | Х            | $\checkmark$ | Х                            | $\checkmark$ | Х            |

| 2015)                    |              |              |                              |              |              |

| PimSim (XU et al., 2018) | $\checkmark$ | Х            | Х                            | $\checkmark$ | $\checkmark$ |

| gem5's simple HMC        | $\checkmark$ | -            | Х                            | $\checkmark$ | $\checkmark$ |

| (AZARKHISH et al.,       |              |              |                              |              |              |

| 2015)                    |              |              |                              |              |              |

| (YANG; HOU; HE,          | $\checkmark$ | -            | $\checkmark$                 | $\checkmark$ | $\checkmark$ |

| 2019)                    |              |              |                              |              |              |

| PIM-gem5                 | $\checkmark$ | $\checkmark$ | $\checkmark$                 | $\checkmark$ | $\checkmark$ |

Table 3.1: Summary of features

Source: Provided by the author

## 3.3 System-level challenges for PIM adoption

Data-copy between PIM and host cores is a frequent challenge to be faced since most of PIMs share their embedded memory in a regular storage mode. The investi-

<sup>&</sup>lt;sup>1</sup>We consider if there is any available mechanisms for PIM offloading, virtual address translation, data coherence and so on.

gation of the cache coherence problem is restricted mainly to three alternatives: noncacheable data, fine-grain, and coarse-grain coherence. The use of non-cacheable memory region forces the host CPU to directly read data from memory (AHN et al., 2016; NAI; KIM, 2015; FARMAHINI-FARAHANI et al., 2015b), while the fine-grain solution uses traditional coherence protocols and flushes data back to the memory when needed (BOROUMAND et al., 2017). Other works use coarse-grain coherence or coarse-grain locks to prevent the host core to access data being used in PIM (AHN et al., 2015; HSIEH et al., 2016a; SESHADRI et al., 2013; SESHADRI et al., 2015). Another concern on PIM system-level infrastructure is the virtual address translation. For instance, IMPICA (HSIEH et al., 2016b) proposes in-memory support for address translation and pointer chasing operation, and DIPTA (GOKHALE; LLOYD; HAJAS, 2015) avoids traditional page frame translation and stores translation information next to the data to eliminate translation overhead in near-memory architectures.

The PIM concept introduces new challenges in how programmers will interact with in-memory processing logic. The discussion about programming model involves how much control the CPU has over the PIM and the type of integration of PIM instruction using compiler-based methods and libraries. Recent works that tackle the problem of deciding between host and PIM instructions (AHN et al., 2015; HSIEH et al., 2016a). The PIM-enabled instruction (PEI) (AHN et al., 2015) consists of an ISA extension for PIM operations and a data locality-aware mechanism to decide whether instructions should be executed on the host CPU or PIM. Unlike PEI, the work of (HSIEH et al., 2016a) proposes a compiler-based mechanism to transparently offload instructions to PIM and also map data based on the code offloaded.

Another open issue in PIM research resides on determining the ideal place to store data and the ideal allocation of the workload to the in-memory compute units. Besides, (HSIEH et al., 2016a) that provides a programmer-transparent mapping of data and PIM instructions, the work of (SURA et al., 2015) hides memory latency by combining programming language features, compiler techniques, and operating system interfaces to map data and optimize data access. Nonetheless, there are still many opportunities for optimizations that take advantage of memory architecture properties, such as vault and banks location, to decide where data should be mapped.

#### **4 SIMULATOR SUPPORT FOR PIM ARCHITECTURES**

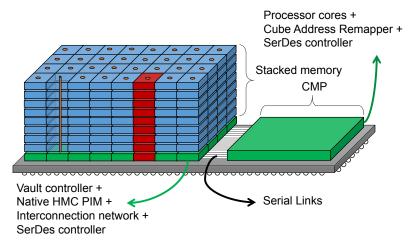

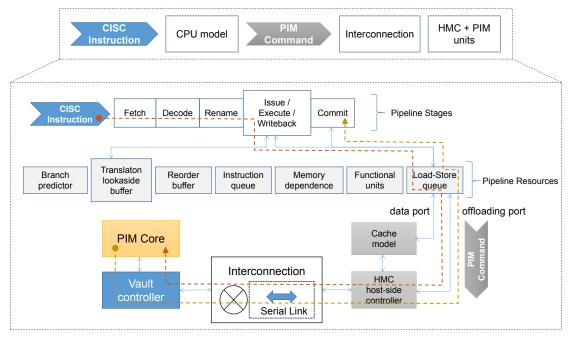

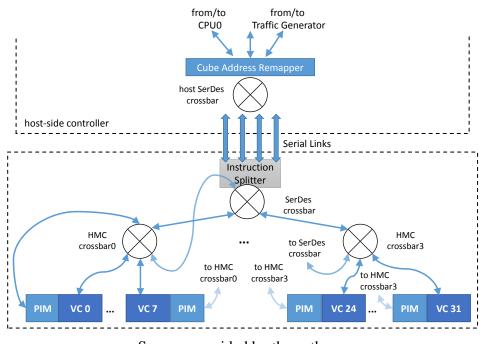

This section presents the implementation of reusable models for PIM architectural research in the gem5 simulator. The elements described here include system and hard-ware abstractions applicable to a wide variety of PIM styles. The following subsections report many decisions related to modeling accurately 3D-stacked memories, offloading mechanism, interconnection, PIM logic, and energy model. We divided the presentation into three major blocks: HMC modeling, PIM logic modeling, and, finally, host interface and system integration. An overview of the system integration that we intend to represent using these three blocks is shown in Figure 4.1.

Figure 4.1: An example of system integration: a PIM-enabled stacked memory connected to a Chip Multiprocessor (CMP) via serial links in a 2.5D package

Source: provided by the author

### 4.1 HMC modeling

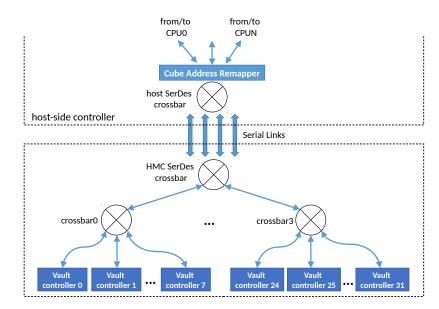

To model the HMC and also enable the extension for future PIM studies based on HMC, the specification (Hybrid Memory Cube Consortium, 2013b), related papers (JED-DELOH; KEETH, 2012; PAWLOWSKI, 2011; WEIS et al., 2011; HADIDI et al., 2017; HADIDI et al., 2018; HANSSON et al., 2014) and recent proposals of PIM interfaces were studied (AHN et al., 2015; SANTOS et al., 2017; OLIVEIRA et al., 2017a). The HMC is composed of three major blocks: the high-speed serial links (SerDes), switching interconnection and the vault controller. An overview of the objects that compose the HMC model is shown in Figure 4.2, and they are described in the following subsections. However, before diving into the challenges of implementing and extending the three ma-

jor hardware components of HMC, we focus on the difficulties found to represent the HMC interleaving correctly.

Figure 4.2: HMC model broke down into serial link, crossbar switch and vault controller objects

Source: provided by the author

### 4.1.1 Address mapping

To correctly represent the HMC in the gem5 simulator, we had to make significant changes in the memory mapping mechanism to provide vault-level parallelism and suitable interconnection latencies in the way that it is specified in Hybrid Memory Cube Consortium (2013a). The first challenge is associated with the correct implementation of memory interleaving, which was already misinterpreted in a previous study presented in Subsection 3.1.

As aforementioned in Subsection 2.1.1, the maximum memory block size dictates the pattern of memory ranges addressed by a vault in the low-interleave mapping algorithm. In the gem5 model, these address ranges are given either by a single address range or a range list. Each vault controller receives a range list where the range addresses are spaced at regular intervals, which depends on the number of vaults and the configured block size.

The default approach provided by gem5's source code is heavy to simulate and cannot scale for ordinary memory sizes. This happens because, in a device of 8 GB, it can represent up to 1M entries of address range to form an aggregate range of a single vault

controller. Thus, iterating over a 1M entries to find the address range makes this choice prohibitive in terms of memory usage and simulation time. Then, a different interleaving mode is needed, and we provide the *Cube Address Remapper* to correctly forward requests from the serial link to the vault controllers.

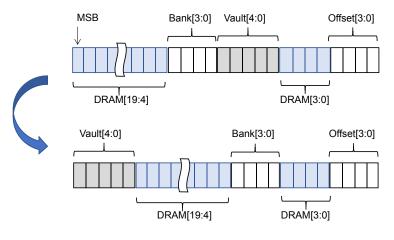

Figure 4.3: Address map fields 256 Byte maximum block size and 8GB

Source: provided by the author

The *Cube Address Remapper* is intended to be implemented in the host-side HMC controller, and it enables modules within the HMC to forward packets using contiguous ranges seamlessly. This module moves the bits responsible for the vault addressing (*Vault*[0:4]) to the most significant part of the address as shown in Figure 4.3. By rearranging the address of memory packets before they are forwarded in the cube, we provide the so-called low-interleaved mode without extra overhead in simulation. Thus, for the purpose of ease the simulation, each vault controller receives a single address range and the components within a cube (serial links and switching interconnection) can correctly forward the packets using a reduced list of address ranges. The bitfields presented in Figure 4.3, with the exception of *Vault*[0:4], are used to address the memory within a vault. *DRAM*[4:19] bits are used to address the row, *Bank*[4:19] bits address the bank, *DRAM*[0:3] bits, if applicable, are used to address the block of a given bank *b* and row *r*, and *Offset*[0:3] bits to address unaligned requests.

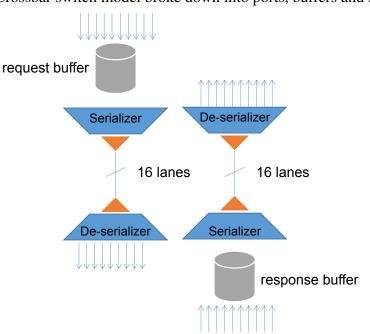

### 4.1.2 High-speed serial links

All HMC I/O is implemented as multiple serialized, full duplex links. Each serial link is composed of SerDes lanes, e.g., 16 input lanes and 16 output lanes by default, that carry system commands and data. Other SerDes configurations are also possible,

such as half-width and quarter-width setups. All in-band communication across a link is packetized, and a packet specifies single, complete operations. There is no specific time associated with each memory requests, and responses are generally returned in a different order than requests are made since there are multiple independent vaults answering requests.

Each serial link is composed of buffered slave and master ports. In timing mode accesses, an event on the master port side is responsible for handling a transmission list, i.e. packets in the request buffer. Likewise, the slave port side has a buffer for the responses not yet sent. In addition to that, the master port presents a simple traffic control by marking outstanding packets in the response buffer. By tracking outstanding responses, it is possible to maintain a maximum number of packets inside the cube and prevent data contention.

Table 4.1 shows the parameterized items of this model. These parameters are mostly related to static latencies, bandwidth and number of buffer entries. As the serial link object inherits the address range of memory and routing objects, the four links receive the address range of an HMC crossbar switch. To provide a full address range across all serial links, we added a crossbar switch to forward the requests coming from four serial links to one of the four internal crossbar switches with limited address ranges.

Figure 4.4: Crossbar switch model broke down into ports, buffers and switching layers

Source: provided by the author

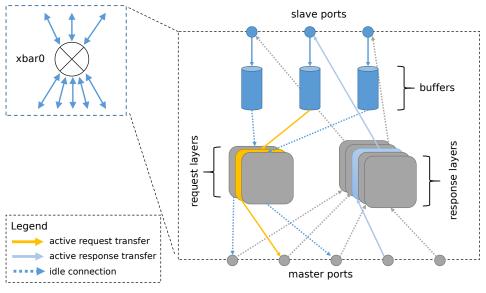

## 4.1.3 Switch interconnection

The implementation of the interconnection network between serial links and vault controller is an open discussion. Although some past works have analyzed the impact of a Network on Chip on real hardware (HADIDI et al., 2017; HADIDI et al., 2018), this issue generally does not receive much attention, since different interconnection networks can provide the maximum bandwidth. On the other hand, the first announcement of HMC in the Hot Chips Symposium made by Jeddeloh and Keeth (2012) considers a crossbar switch as an alternative, which we have followed in this work.

A crossbar switch is an example of implementation of how the aggregate bandwidth from all vaults is made accessible to the Input/Output links. This portion of HMC is responsible for data routing and data buffering between Input/Output links and vaults, which is implemented by non-coherent buffered crossbar model. A detailed representation of this crossbar model is shown in Figure 4.5.

Source: provided by the author

Each link is associated with eight local vaults that form a quadrant. Accesses from a link to a local quadrant may have lower latency than accesses coming from a link of a distinct quadrant. Bit fields within the vault address designate both the specific quadrant and the vaults within that quadrant. Each internal crossbar is associated with eight local vaults, and the transfer of requests from its corresponding serial link has reduced latency. This behavior models the four quadrants present in HMC. We use four crossbar switches to simulate the quadrants specified in (Hybrid Memory Cube Consortium, 2013b). In Table 4.1 we present the parameterized items of our crossbar switching model. These parameters are mostly related to latencies, bandwidth and number of buffer entries.

| Model           | Parameter                | Description                                         |

|-----------------|--------------------------|-----------------------------------------------------|

| Serial Link     | Lane width               | Number of parallel lanes inside the serial (Bytes)  |

|                 | Link speed               | Speed of each parallel lane inside the (GBps)       |

|                 | Request buffer size      | Number of requests to buffer                        |

|                 | Response buffer size     | Number of responses to buffer                       |

|                 | Total controller latency | Static latency experienced by every packet (ns)     |

| Crossbar switch | Width                    | Data width (Bytes)                                  |

|                 | Clock frequency          | Fixed clock frequency of all operations             |

|                 | Request buffer size      | Number of requests to buffer                        |

|                 | Response buffer size     | Number of responses to buffer                       |

|                 | Frontend latency         | Static latency experienced by every packet          |

|                 |                          | regardless if the bus is busy or can transmit       |

|                 | Forward latency          | Static latency to forward a packet                  |

|                 | Response latency         | Static latency to transmit a packet in the response |

|                 |                          | direction                                           |

Table 4.1: List of parameterized items in the serial link and crossbar switch model

Source: provided by the author

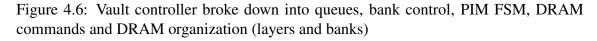

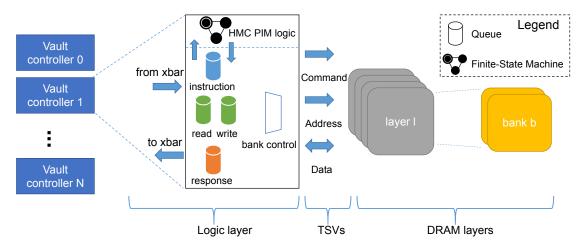

# 4.1.4 Vault controller

In this section, the mechanism and behavior of a memory controller targeted for HMC and PIM architectures are described. Our model of *vault controller* is based on the generic DRAM controller proposed by Hansson et al. (2014). Their fast, event-based model captures the behavior of modern DRAM devices, which can model either DIMM modules or can easily be adapted to model other DRAM interfaces such as Wide-IO (KIM et al., 2012), HBM (STANDARD, 2013) and HMC (CONSORTIUM et al., 2015).

As shown in Figure 4.6, the controller splits write and read queues for incoming requests and a shared queue for responses. The DRAM organization is captured by determining parameters such as bus width, page size, burst length, number of banks, ranks, and devices. Likewise, DRAM operations are modeled after event-based state machines that take DRAM timings as parameters. The controller model captures a subset of the DRAM bank state changes, along with data bus occupancy, refresh events, and data response events. For more details of the DRAM finite state machine, we refer the readers to Hansson et al. (2014).

*Scheduling*: The memory controller schedules read and write requests observing the DRAM timings and bank state machines with the goal of maximizing the efficiency

and exploiting the maximum bandwidth. Two levels of scheduling are provided. The first is related to read/write switching policy. The controller handles requests from read queue as the default state and implements a write drain mode as described in Narancic (2012). A parameterized threshold is used for forcefully changing the DRAM state from read to write queue, and a minimum number of writes to switch back to read queue. The second level of scheduling selects the request from either read or write queue as demanded by the first scheduling level, and it is tightly coupled to the row buffer policy. Two simple scheduling algorithms are available: First-Come-First-Served (FCFS) and First-Ready-FCFS (FR-FCFS) (RIXNER et al., 2000). Also, two basic row-buffer policies, namely closed and opened page, and two variations, namely adaptive closed and adaptative opened page, are provided.

The controller model uses the transaction-level gem5 port interface presented in Section 2.3. The flow control is made by monitoring queue size when receiving a packet or after a response event. The model has two timing parameters to capture the static frontend and backend latency of a memory controller. The frontend latency represents the pipeline stages and complexity of the controller design. The backend parameter captures the PHY and IO latency, thus allowing us to study the impact of different memory interconnection, e.g., Package-on-Package, Dual Inline Memory Module and Through Silicon Vias;

*PIM logic interface*: A PIM unit can be connected to arbitrary locations in the memory system, e.g., behind a crossbar switch, attached to a dedicated port of the memory controller, behind the row buffer, etc. To model such different locations, we provide an interface to connect PIM logic using dedicated slave and master ports to the memory controller. By using them, one can model the placement of PIM units inside a vault to take advantage of reduced communication costs. The specific location can be imitated by adjusting the timing parameters. In turn, to model PIM units externally to a vault, the implementation is straightforward since crossbar switch models are readily available.

Regarding modeling specifics characteristics of HMC, we modeled the layers as ranks that share the same TSV connection in burst operations. The baseline address mapping of HMC is  $RoBaVaOf^1$ . As the *Cube Address Remapper* rearranges the address as depicted in Figure 4.3, the address mapping had to be changed to *VaRoBaOf* to keep the bank-level parallelism.

Transactional operations, such as the read-modify-write (RMW) commands in HMC and the instructions presented in Section 5.2, require changes to the scheduling al-

<sup>&</sup>lt;sup>1</sup>With Ro, Ba, Va and Of denoting row, bank, vault and offset, respectively, and going from MSB to LSB.

gorithm to keep data consistency. Instead of handling the requests strictly following one of the scheduling algorithms mentioned above, the memory controller must also check flags and timestamps of requests to the same address in the read and write queue. The changes made to both scheduling algorithms, FCFS and FR-FCFS, are responsible for skipping requests to the same address or overlapping address of an in-flight transactional request, then postponing ordinary requests till the transactional one has been finished. More details of transactional requests are presented in Section 4.3.5, which describes two concurrency models for lock-release and RMW requests that apply to different types of PIM commands.

Source: provided by the author

# 4.2 PIM logic modeling

As described in Section 2.2.2, the current taxonomy of PIM architecture is divided into two classes which have different requirements when modeling and simulating them.

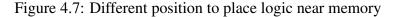

# 4.2.1 NDP and PIM with fully-programmable cores

First, fully-programmable PIM can be simulated in gem5 by adjusting parameters to represent TSV interconnection and by taking advantage of existing CPU models and compilers. In general, in-order CPUs are used as PIM logic since area and power are primary constraints for the logic layer of 3D-stacked DRAM memories (PUGSLEY et al., 2014; AHN et al., 2016; SCRBAK et al., 2017; DRUMOND et al., 2017). Regarding

software support for code generation and optimization, traditional tools for parallel programming can be applied, such as the m5thread library in syscall emulation mode, and unmodified pthread, OpenMP or other libraries, which can only be used in full-system mode.

In the present form, this work provides a correct and validated model of HMC to be used in fully-programmable PIM research. Since many CPU and ISA models are readily available in gem5, one can concentrate efforts in proposing novel techniques and tools for improving performance based on the application's characteristics and also for dealing with thermal constraints, to list some open problems. As the HMC model is solved and tested, the modeling of NDP/PIM architectures becomes straightforward. One of the decision resides on where to place ports of existing CPUs into the memory system. Figure 4.7 demonstrates different positions to place the processor cores inside or close to HMC.

Source: provided by the author

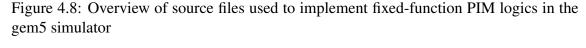

# 4.2.2 Fixed-function and Functional Unit-centered PIM

On the other hand, fixed-function PIM not always relies on existing models or hardware descriptions. Thus, modeling the behavior of a specialized processing unit is probably the first step. Figure 4.8 presents an overview of the source files used to describe the behavior and parameters of PIM instances and HMC model. Each module is defined by at least three files: the description file, where the parameterized values are exposed to the Gem5 simulation engine in Python, and source file and header file, where the behavior of the module is written in C++. To build the models related to fixed-function and FU-centered PIM, an architect must start by defining the communication protocol, datapath, and control unit. To couple processing units to a vault controller or to a crossbar switch, a PIM instance must implement the PIM interface (master/slave ports) to be able to receive memory packets that encapsulate PIM commands and data.

The PIM instance must implement a command queue and a decoder for the packets containing a PIM instruction. The datapath and control unit must follow one of the approaches to the event-based simulation: either by updating the model on a cycle-by-cycle basis or based only on meaningful events. The behavior of a PIM instance is arbitrary and can be implemented using a myriad of elements, such as pipeline stage and different issues (e.g., Load Store Unit, Arithmetic and Logic Unit (ALU), and Floating Point Unit). Statistics, such as busy cycles and the total of instructions ALU accesses, are optional, though they are valuable for energy consumption estimation.

Two models were created to evaluate the benefits of PIM in different classes of applications, which will be described in more details in Section 5. Before that, we present the basic support in host CPU (offloading, virtual address translation, data coherence).

Source: provided by the author

## 4.2.3 Power and energy

Originally, gem5 integrates McPAT (LI et al., 2009) and CACTI (CHEN et al., 2012) for area and power modeling of chip multiprocessors, which can still be used for power estimation of PIM with existing programmable cores. However, fixed-function designs need more details of the synthesis as input to an analytical model of the power consumption. Thus, we can offer a similar estimation by using results backed on the synthesis of RTL models and the statistics obtained during application execution. For complete results, the analytical model takes statistics, power models and design constraints to estimate the energy consumption of PIM cores. Statistics such as idle and busy cycles, number of floating point, integer and logic operations, just to list some of them, are mul-

tiplied by the static and dynamic power of each corresponding module of the processing core to give an estimate of the energy consumption.

## 4.3 Host interface and system integration

Several related works propose PIM architectures based on fine-grain offloading of PIM instructions, that is, PIM instructions are emitted one by one from a host CPU to the PIM logic. In fact, the native instructions of HMC already use a similar mechanism. In computer modules such as Micron's FPGA card AC-510, the PIM commands are generated in the FPGA's logic and transmitted to the HMC device following the protocol specified in Consortium et al. (2015). Unlike this FPGA board, new PIM proposals have to find a suitable mechanism to perform the communication between host and accelerator (AZARKHISH et al., 2015) or create new ones.