#### THESE

présentée par

# Cláudio Fernando RESIN GEYER

pour obtenir le titre de DOCTEUR

# de l'UNIVERSITE JOSEPH FOURIER - GRENOBLE I

(arrêté ministériel du 5 juillet 1984)

Spécialité: INFORMATIQUE

# UNE CONTRIBUTION A L'ETUDE DU PARALLELISME OU EN PROLOG SUR DES MACHINES SANS MEMOIRE COMMUNE

Date de soutenance: 29 octobre 1991.

Composition du Jury:

Yves CHIARAMELLA

Président

Yves BEKKERS

Rapporteurs

Gilles BERGER-SABBATEL

Phillipe JORRAND

Examinateurs

Laurent TRILLING

Jacques BRIAT

Thèse préparée au sein du Laboratoire de Génig informatique

INSTITUTO DE INFORMÁTICA

BIBLIOTECA

Linguageus de Profrancea - 500 Linguageus: Perofrancea PROLOG Magninas paralelas Paralelismo OU

UFRGS

INSTITUTO DA HINDOMATICA

BIDITOTECA

Nº CHAMADA

681.32.06 PROLOG (043) 5825

G 397C

ORIGEM: D DATA:

21/01/93 Ct\$ 200.000,00

FUNDO: FORN::

II II

# Remerciements

Je tiens à remercier

Yves Chiaramella, directeur du Laboratoire de Génie Informatique (LGI), de me faire l'honneur de présider le jury de cette thèse.

Jacques Briat, maître de conférences à l'Université Joseph Fourier, qui m'a accepté dans son équipe (Flop) et qui a bien dirigé mon travail. Qu'il soit également remercié pour ses conseils et ses critiques lors de la rédaction de ce document.

Yves Bekkers, directeur de recherche INRIA, et Gilles Berger-Sabbatel, chargé de recherches CNRS, d'avoir bien voulu juger ce travail.

Philippe Jorrand, directeur du Laboratoire d'Informatique Fondamentale et d'Intelligence Artificielle, et Laurent Trilling, professeur à l'Université Joseph Fourier, qui ont accepté de participer du jury de cette thèse.

Jacques Mossière, directeur de l'ENSIMAG, de m'avoir invité à travailler au sein de son laboratoire.

Mon camarade et collègue Michel Favre, dont la coopération lors du développement du projet Opera a toujours été amicale et fructueuse.

Tous les membres de l'équipe Flop et de l'équipe Sympa, au LGI; en particulier Philippe Waille qui m'a initié à la connaissance de la machine Tnode, et Jacques Eudes et Miguel Santana qui ont participé au développement des logiciels de base de cette machine.

Thadeu Botteri-Corso, pour m'avoir lancé dans le domaine du parallélisme et aux langages déclaratifs.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Sistema de Biblioteca da UFRGS

5825

GEYER, CLAUDIO FERNANDO RESIN

UNE CONTRIBUTION A L'ETUDE DU PARALLELISME OU EN PROLOG SUR DES MACHINES SANS MEMOIRE 681.32.06PROLOG(043) G397C

INF 1993/60195-0 1993/04/05

# Résumé

Cette thèse est consacrée à l'étude de l'implantation du parallélisme OU en Prolog sur des machines sans mémoire commune. Nous présentons le modèle multi-séquentiel OU Opera, implanté par compilation (machine abstraite de Warren - WAM), en préservant la sémantique de Prolog. Les deux problèmes principaux d'un tel système, la gestion de contextes multiples et l'ordonnancement, sont détaillés. La gestion des contextes multiples s'effectue par copie incrémentale, en parallèle au calcul. Pour que ceci reste efficace et cohérent, le traitement des variables conditionnelles a été inclus dans la WAM. Notre méthode introduit une nouvelle pile pour ces variables dont l'initialisation, la liaison et la déliaison ont été modifiées. Le coût des opérations séquentielles de la WAM est constant et indépendant du nombre de processus. Nous proposons encore une méthode simple et efficace pour la réalisation de la coupure.

Un prototype Opera a été implanté sur un réseau de Transputers. Dans ce prototype, l'ordonnancement a été résolu par une méthode basée sur des heuristiques d'évaluation de charge. Cet ordonnancement est mis en œuvre par une architecture centralisée où un processus ordonnanceur unique régule la charge des autres processus. L'ordonnanceur utilise une représentation approximative de l'état du système. La partie séquentielle du prototype Opera constitue l'un des systèmes Prolog les plus efficaces existant actuellement sur le Transputer. Ses gains de performance en parallèle sont aussi effectifs.

Mots-clés: Opera: Ou Parallélisme Et Régulation Adaptative, Prolog, parallélisme OU multi-séquentiel, Prolog parallèle basé sur la WAM, implantation sur machine parallèle sans mémoire commune, gestion des contextes multiples, copie incrémentale, ordonnancement, coupure en parallèle.

# Abstract

This thesis is dedicated to the study of the implementation of Or-parallel Prolog over distributed memory machines. The Opera Or multi-sequential model is presented. It uses compiling techniques (Warren Abstract Machine) and preserves the Prolog semantics. Multi-environment management and scheduling, the two major problems of Opera, are described. Multi-environment management is realized by incremental copying, in parallel to the computation. The treatment of conditional variables is included in the WAM, in order to allow an efficient and coherent cooperation. Our method introduces a new pile for these variables, initialization, binding and unbinding of which are adapted. The cost of WAM sequential operations is constant and independent of the number of processes. We also propose a simple and efficient method for implementing cut in parallel.

An Opera prototype has been implemented over a Transputer array. In the current prototype, scheduling is resolved by heuristics of load evaluation. This scheduling is centralized, a unique process balancing the load of the other Prolog workers, and using an approximate representation of the state of the system. The Opera prototype is one of the most efficient Prolog implementations on the Transputer, and reaches effective speed-ups in parallel.

**Key-words:** Opera: Or Parallelism and Adaptable Balancing, Prolog, Or multisequential parallelism, based-WAM parallel Prolog, implementation over distributed parallel machine, multi-environment management, incremental copy, scheduling, parallel cut.

# Table des Matières

| 1. Chapitre 1                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------|

| 1.1. Le Thème                                                                                                       |

| 1.2. Justification                                                                                                  |

| 1.3. Contexte Mondial                                                                                               |

| 1.4. Le Contexte Local                                                                                              |

| 1.5. Contribution de l'Auteur                                                                                       |

| 1.6. La Structure de la Thèse                                                                                       |

| 2. Chapitre 2                                                                                                       |

| 2.1. Prolog en un Exemple                                                                                           |

| 2.2. Programmation Logique                                                                                          |

| 2.2.1 Syntaxe                                                                                                       |

| 2.2.2. La sémantique déclarative                                                                                    |

| 2.2.3. La résolution SLD                                                                                            |

| 2.2.4. Interprétation Procédurale                                                                                   |

| 2.3. Prolog                                                                                                         |

| 2.3.1. Prolog Pur                                                                                                   |

| 2.3.2. La Coupure                                                                                                   |

| 2.3.3. La Négation                                                                                                  |

| 2.3.4. Les Prédicats à Effet de Bord                                                                                |

| 2.4. Les Machines Abstraites pour Prolog                                                                            |

| 2.4.1. L'organisation de la Mémoire et le Retour-Arrière                                                            |

| 2.4.2. Les Variables: Représentation et Etats                                                                       |

| 2.4.3. La Pile Traînée                                                                                              |

| 2.5. Parallélisme en Programmation Logique                                                                          |

| 2.5.1. Les Sources de Parallélisme                                                                                  |

| 2.5.1. Des bources de l'aranterisme 2.5.2. Parallélisme Explicite et Implicite 35                                   |

| 2.5.2. Parallélisme Explicite et Implicite       35         2.5.3. Modèles Théoriques et Multi-Séquentiels       36 |

| 2.5.4. Le Parallélisme OU                                                                                           |

| 2.5.5. Le Parallélisme ET                                                                                           |

| 2.5.6. Le Parallélisme ET/OU                                                                                        |

| 2.5.7. Les Langages Logiques Gardés                                                                                 |

| 2.6. Conclusions                                                                                                    |

| 3. Chapitre 3                                                                                                       |

| 3.1. Les Principes                                                                                                  |

| 3.2. La Condition d'Existence du Parallélisme OU                                                                    |

| 3.3. La Gestion des Contextes Multiples                                                                             |

| 3.3.1. La Gestion de la Mémoire                                                                                     |

| 3.3.2. Le Maintien de la Cohérence des Sections Communes                                                            |

| 3.4. La Copie des Sections Communes                                                                                 |

| 3.4.1. La Copie Simple de Piles                                                                                     |

| 3.4.2. La Copie avec Datation                                                                                       |

| 3.5. Le Partage des Sections Communes                                                                               |

| 3.5.1. Le Tableau de Liaisons                                                                                       |

| 3.5.2. Les Liaisons Privilégiées                                                                                    |

| 3.5.3. Les Tables d'Adressage Associatif                                                                            |

| 3.5.4. La Liste de Liaisons et l'Historique                                                                         |

| 3.5.5. La Fermeture d'Environnements                                                                                |

| 3.6. L'Ordonnancement 51                                                                                            |

| 3.6.1. Les Conditions Minimales du Parallélisme Efficace                                                            |

| 3.6.2. La Régulation de la Charge                                                                                   |

| 3.6.3. Quelques Méthodes de Régulation de Charge                                                                    |

| 3.7. Les Opérateurs Séquentiels de Prolog                                                                           |

| 3.7. Les Operateurs acquemiers de Fronce                                                                            |

| 3.7.1.1.a Coupure 57                                               |

|--------------------------------------------------------------------|

| 3.7.1. La Coupure                                                  |

| 2.9 Les Bénérales de Bold                                          |

| 3.8. Les Résultats                                                 |

| 3.9. Conclusions                                                   |

| 4. Chapitre 4                                                      |

| 4.1 Le Projet                                                      |

| 4.1.1. Objectifs et Choix Initiaux                                 |

| 4.1.2. Hypothèses de Travail                                       |

| 4.1.3. Décisions Techniques Importantes                            |

| 4.1.3. Decisions recriniques importantes                           |

| 4.1.4. Résumé des Caractéristiques Principales                     |

| 4.2. Les Constituants Séquentiel et Parallèle                      |

| 4.2.1. La partie Séquentielle                                      |

| 4.2.1.1. Le Langage                                                |

| 4.2.1.2. Compilation et Machine Abstraite                          |

| 4.2.1.3. Les Optimisations d'Opera (TWAM)67                        |

| 4.2.2 Le Modèle Opera 67                                           |

| 4.2.2. Le Modèle Opera                                             |

| 4.2.2.1. Schema de Cooperation Paranete                            |

| 4.2.1.2. Le Problème de la Gestion des Contextes Multiples 67      |

| 4.3. La Gestion de Contextes Multiples                             |

| 4.3.1. Principes                                                   |

| 4.3.1.1. Méthode Naïve                                             |

| 4.3.1.2. Copie Incrémentale                                        |

| 4.3.1.3. Objectif d'une Implantation                               |

| 4.3.2. Problèmes                                                   |

| 4.3.2.1. Liaison et Copie Incrémentale71                           |

| 4.3.2.2. Gestion de la Mémoire et la Pile de Variables             |

| 4.3.2.3. Liaison Superficielle/Liaison Profonde                    |

| 4.3.2.4. Variable Conditionnelle/Inconditionnelle                  |

| 4.3.2.5. Gestion des Points de Choix et la Pile Locale             |

|                                                                    |

| 4.3.2.6. Bilan                                                     |

| 4.3.3. La Méthode Pile de Variables Plus Datation (VD)75           |

| 4.3.3.1. Organisation de la Mémoire                                |

| 4.3.3.2. Allocation et Initialisation de Variables                 |

| 4.3.3.3. Liaison et Déréférencement                                |

| 4.3.3.4. Déliaison Séquentielle                                    |

| 4.3.3.5. Récupération de l'Espace dans les Piles de Variables      |

| 79                                                                 |

| 4.3.3.6. Datation                                                  |

| 4.3.3.7. Installation de Tâches                                    |

| 4.3.3.7. Installation de Taches                                    |

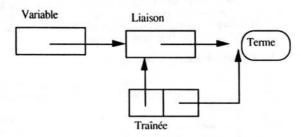

| 4.3.4. La Méthode Pile de Variables et Traînée plus Valeur (VV) 81 |

| 4.3.4.1. Organisation de la Mémoire                                |

| 4.3.4.2. Traitement des Variables                                  |

| 4.3.4.3. Installation de Tâches                                    |

| 4.3.5. Bilan Datation ou Traînée plus Valeur (VD/VV)               |

| 4.3.6. Contrôle des Points de Choix Communs                        |

| 4.3.6.1. Enregistrement des Liaisons de la Dernière Branche 86     |

| 4.3.6.2. Maintien des Points de Choix Communs                      |

| 4.3.7. Cohérence des Données                                       |

| 4.3.7.1. Les Sources d'Incohérence                                 |

| 4.3.7.2. Les Remèdes                                               |

|                                                                    |

| 4.4. La Coupure                                                    |

| 4.4.1. Le Problème                                                 |

| 4.4.2. Les Principes de la Méthode Opera94                         |

| 4.4.3. Registres de la TWAM94                                      |

| 4.4.4. Instructions de la TWAM et Compilation                      |

| 4.4.5. La Synchronisation avec l'Exportation                       |

| 4.4.6. Autres Méthodes96                                           |

| 4.5 L'ordonnancement des Tâches                                    |

| 4.5.1. Classification selon la Charge                                               | 98  |

|-------------------------------------------------------------------------------------|-----|

| 4.5.2. Evaluation de la Charge                                                      | 98  |

| 4.5.3. Conditions Minimales du Parallélisme                                         | 99  |

| 4.5.4. Dégulation de Charge                                                         | 00  |

| 4.5.4. Régulation de Charge 4.6. L'architecture du Logiciel: Processus et Protocole | 22  |

| 4.6. L'architecture du Logiciei: Processus et Protocole                             | 00  |

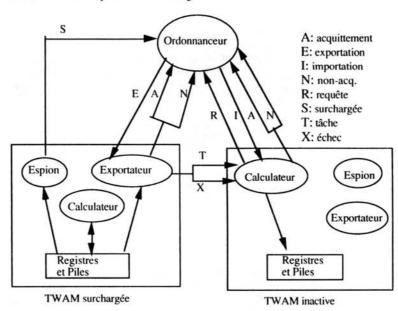

| 4.6.1. Organisation en Processus                                                    | 00  |

| 4.6.2. L'Ördonnanceur                                                               | 02  |

| 4.6.3. L'Espion                                                                     | 03  |

| 4.6.4. Le Calculateur                                                               | 04  |

| 4.6.5. L'Exportateur                                                                | 104 |

| 4.7. Conclusions                                                                    | 04  |

|                                                                                     |     |

| 5. Chapitre 5                                                                       | 07  |

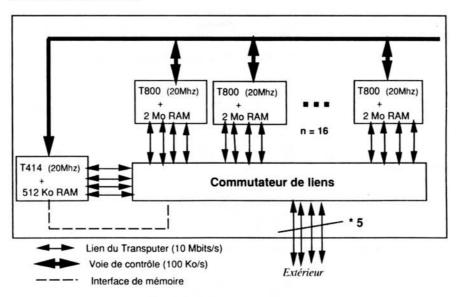

| 5.1. Le Supernode                                                                   | 07  |

| 5.2. Le Placement de l'Architecture Opera sur le Supernode                          | 10  |

| 5.3. L'adaptation du Modèle Opera au Supernode1                                     | 11  |

| 5.3.1. La Gestion des Contextes Multiples                                           | 12  |

| 5.3.2. L'ordonnancement                                                             | 13  |

| 5.3.3. Le Format des Messages inter Processus                                       | 13  |

| 5.4. Les Programmes de Test                                                         | 14  |

| 5.4. Les Programmes de Test                                                         | 14  |

| 5.5. Les Résultats en Séquentiel                                                    | 13  |

| 5.6. Les Résultats en Parallèle                                                     | 13  |

| 5.7. Le Logiciel de Développement                                                   | 16  |

| 5.8. Conclusions                                                                    | 17  |

| 6. Chapitre 61                                                                      | 19  |

| 6.1. Résumé                                                                         | 10  |

| 6.1.1. Prolog et Parallélisme                                                       | 10  |

| 6.1.1. Prolog et Parallelisme                                                       | 119 |

| 6.1.2. Le Modèle OU Multi-séquentiel                                                | 19  |

| 6.1.3. Gain d'Efficacitél                                                           | 20  |

| 6.1.4. Le Modèle Opera1                                                             | 20  |

| 6.1.5. Le Prototype Opera                                                           | 22  |

| 6.2. Le Problème de la Mémoire et de la Complétude                                  | 122 |

| 6.3. Opera: Critiques et Perspectives                                               | 123 |

| A. Annexe A1                                                                        | 25  |

| A. Alliexe A.                                                                       | 25  |

| A.1. Modules                                                                        | 23  |

| A.2. Les Prédicats Prédéfinis1                                                      | 25  |

| A.3. La Coupure                                                                     | 127 |

| R Appeve R                                                                          | 29  |

| B.1. Les Eléments de Base de la Machine Abstraite (WAM)                             | 20  |

| B.1.1. Les Termes de la WAM                                                         | 20  |

| B.1.2. L'organisation de la Mémoire                                                 | 120 |

| B.1.2. L organisation de la Memoire                                                 | 130 |

| B.1.3. Les Registres                                                                |     |

| B.1.4. Les Instructions                                                             |     |

| B.2. La Compilation vers la WAM                                                     | 131 |

| B.2.1. La Compilation de Prédicats1                                                 | 131 |

| B 2.2. La Compilation de Clauses                                                    | 134 |

| B.2.3. Résumé de l'Exécution d'un Prédicat                                          | 134 |

| B.3. Les Optimisations de la WAM                                                    | 135 |

| B.3.1. Occurrences de Variables                                                     | 125 |

| B.3.1. Occurrences de Variables                                                     | 133 |

| B.3.2. Optimisation d Appel Terminal                                                | 133 |

| B.3.2. Optimisation d'Appel Terminal                                                | 36  |

| B.3.4. Globalisation de Variables Locales                                           | 136 |

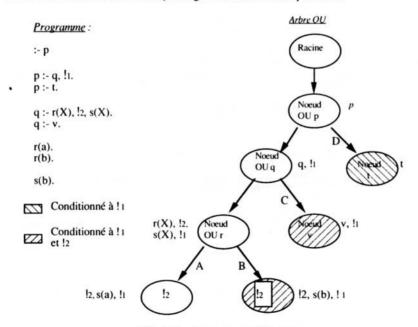

| B.4. Un Exemple                                                                     | 136 |

| B.4. Un Exemple                                                                     | 137 |

| B.5.1. Les Termes                                                                   | 137 |

| B.5.2. Listes                                                                       | 138 |

| B.5.3. La Disjonction                                                               | 138 |

| B.5.5. La Disjoint follon                                                           | 130 |

| B.5.5. La Coupure                                         | 139 |

|-----------------------------------------------------------|-----|

| B.5.6. Indexation                                         | 139 |

| C. Annexe C                                               |     |

| C.1. Introduction                                         | 141 |

| C.2. Implantation                                         |     |

| C.2.1. Le mécanisme de coupure de la WAM                  | 143 |

| C.2.2. La Compilation de la Coupure                       | 144 |

| C.2.2.1. Principe de Compilation                          | 144 |

| C.2.2.2. Coupure Locale                                   | 144 |

| C.2.2.3. Coupure Globale                                  | 145 |

| C.2.2.4. Coexistence de la Double Sémantique de la Coupur | e   |

|                                                           |     |

| C.3. Extensions                                           |     |

| C.3.1. Le Snip (Arity_Prolog)                             | 147 |

| C.3.2. La Coupure Faible                                  | 147 |

| C.3.2.1. Objectif                                         |     |

| C.3.2.2. Réalisation                                      | 148 |

| C.3.2.3. Coupure Faible Locale/Globale                    | 150 |

| C.3.2.4. Coexistence des Coupures Fortes/Faibles          | 150 |

| C.4. Conclusion                                           | 150 |

| D. Annexe D                                               | 151 |

| D.1. Nouvelles Instructions                               | 151 |

| D.2. Instructions Modifiées                               |     |

|                                                           |     |

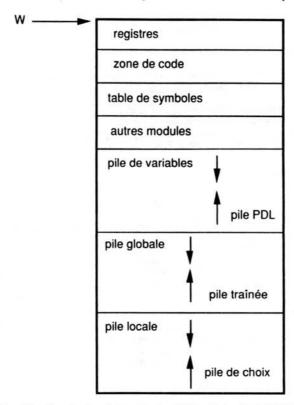

| E. 1. Les Langages et les Logiciels de Développement      | 155 |

| E.2. Les Modules                                          | 155 |

| E.3. La Structure de la Mémoire                           | 155 |

| E.4. Les Registres                                        | 156 |

| E.5. Les Données                                          |     |

| E.6. Les Instructions de la TWAM                          |     |

| E.7. Le Module d'Initialisation (init)                    |     |

| E.8. Les Prédicats Pré-Définis (builtin)                  | 158 |

| E.9. Les Exceptions et la Mise au Point (debug)           | 158 |

| E.10. L'appel des Routines                                | 159 |

| Bibliographie:                                            | 161 |

| Bioliographic                                             |     |

# Liste des Figures

| Fig. 2.1 - Programme exemple de la résolution SLD               | 24 |

|-----------------------------------------------------------------|----|

| Fig. 2.2 - Arbre OU fini                                        | 27 |

| Fig. 2.3 - Arbre OU infini                                      | 28 |

| Fig. 2.4 - Mémoire simplifiée d'une MAP                         | 33 |

| Fig. 2.5 - Graphe d'états d'une variable                        |    |

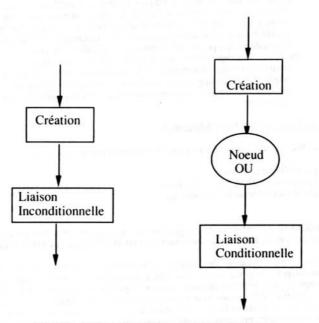

| Fig. 2.6 - Liaisons inconditionnelle et conditionnelle          | 35 |

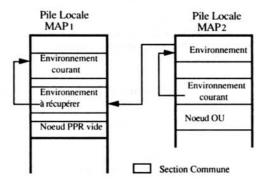

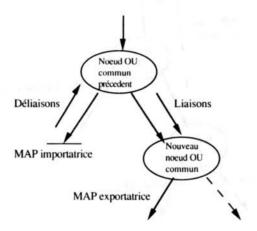

| Fig. 3.1 - Récupération d'environnement commun                  | 44 |

| Fig. 3.2 - Récupération totale de la section commune            | 45 |

| Fig. 3.3 - Liaisons multiples (a)                               |    |

| Fig. 3.4 - Liaisons multiples (b)                               |    |

| Fig. 3.5 - Datation                                             |    |

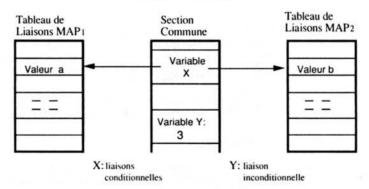

| Fig. 3.6 - Tableau de liaisons                                  |    |

| Fig. 3.7 - Installation avec tableau de liaisons                | 49 |

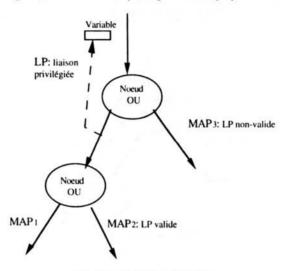

| Fig. 3.8 - Liaison privilégiée                                  |    |

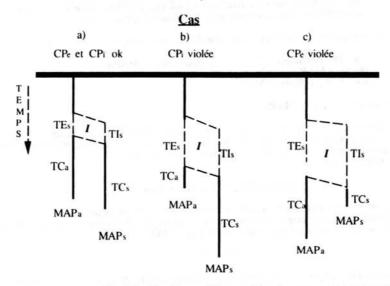

| Fig. 3.9 - Cas des conditions minimales                         |    |

| Fig. 3.10 - Coupure conditionnée                                |    |

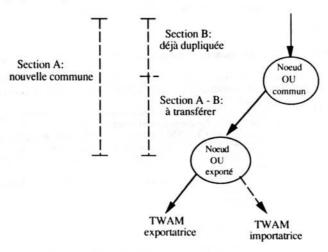

| Fig. 4.1 - Sections communes                                    |    |

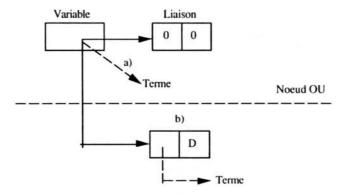

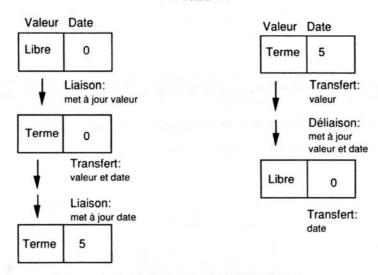

| Fig. 4.2 - Liaison avec pile de variables et datation           | 78 |

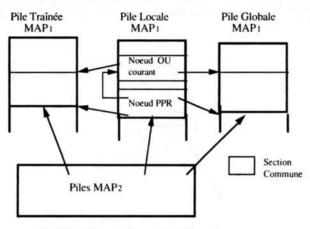

| Fig. 4.3 - Schéma de l'installation VD                          | 80 |

| Fig. 4.4 - Liaison conditionnelle dans la méthode VV            | 82 |

| Fig. 4.5 - Points de choix communs                              | 83 |

| Fig. 4.6 - Schéma de la méthode VV                              | 84 |

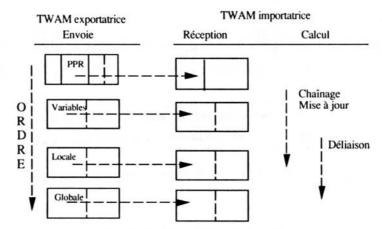

| Fig. 4.7 - Destruction de section commune                       | 85 |

| Fig. 4.8 - Règles d'ordonnancement                              | 86 |

| Fig. 4.9 - Transfert de liaison incohérente                     | 90 |

| Fig. 4.10 - Transfert de liaison cohérente                      |    |

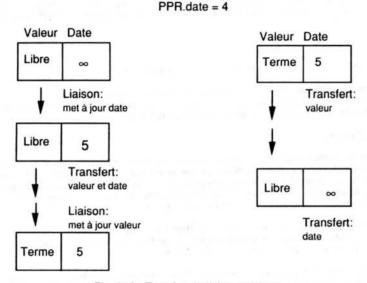

| Fig. 4.11 - Inhibition totale et inhibition partielle           |    |

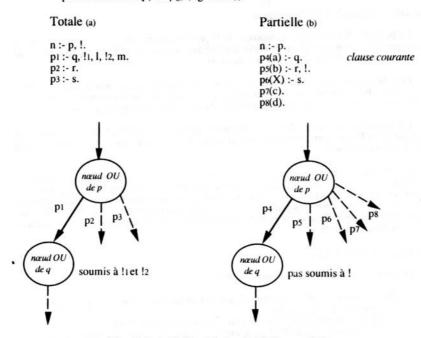

| Fig. 4.12 - Coupure globale dans une disjonction                | 94 |

| Fig. 4.13 - Exécution de la coupure en parallèle                |    |

| Fig. 4.14 - Organisation en processus d'Opera                   |    |

| Fig. 5.1 - Configuration du Tnode à 16 Transputers              |    |

| Fig. B.1 - Code TWAM pour sous-but et clause                    |    |

| Fig. B.2 - Etat des piles et des registres                      |    |

| Fig. E.1 - Organisation de la mémoire de l'émulation de la TWAM |    |

# Liste des Tables

| Table 3.1 - Résultats de Aurora, Muse et PEPSys | 60 |

|-------------------------------------------------|----|

| Table 5.1 - Résultats en séquentiel             |    |

| Table 5.2 - Les résultats sur le Tnode          |    |

# 1. Chapitre 1 Introduction

#### 1.1. Le Thème

Le thème général de cette thèse est l'étude et l'évaluation de l'implantation du langage Prolog sur des architectures parallèles. Pendant ce travail nous avons restreint notre recherche au parallélisme OU implicite, implanté sur des machines avec un haut degré de parallélisme et sans mémoire commune.

#### 1.2. Justification

Parmi les principaux buts de la recherche en Génie Informatique se trouvent:

- la recherche de puissance;

- la facilité de programmation.

# a) La difficile maîtrise du parallélisme

Dans la recherche de puissance, le parallélisme a toujours été considéré comme une bonne voie de recherche. Cet intérêt a produit de nouvelles architectures de machines offrant un excellent rapport prix/performance, comme par exemple: Sequent, Alliant, Butterfly, Encore, Intel Hypercube et autres ([HER 86c], [DUN 90]).

Ces architectures revendiquent deux avantages sur l'architecture séquentielle:

- une façon de contourner les limites technologiques actuelles;

- une augmentation de performance pour une augmentation correspondante de prix.

Ce dernier point est dû à la régularité de l'architecture, permettant l'ajout aisé de processeurs.

L'utilisation effective de ces machines est cependant limitée du fait de l'absence de logiciel de base et de langage de programmation appropriés. Cette inadéquation provient de ce que systèmes ou langages sont de simples adaptations de ceux utilisés sur les machines classiques. L'utilisation "à bon escient" du parallélisme est donc intégralement à la charge du programmeur. Cette tâche délicate entraîne des coûts de développement trop importants.

# b) Le problème de l'efficacité de la programmation logique

Si l'on s'intéresse à la facilité de programmation, le langage Prolog est un bon candidat dans un certain nombre de domaines:

- traitement des langages formels ou naturels;

- expression de gros problèmes combinatoires;

- systèmes experts;

- prototypage rapide.

Son utilisation comme langage "à tout faire" en informatique bute sur un problème d'efficacité. En [REI 88] et [PAA 88] des études montrent un facteur de 1 à 10 entre les temps d'exécution de Prolog et ceux des langages C ou Pascal. Plusieurs techniques d'optimisation ont contribué à diminuer ce facteur, mais la différence persiste. La source de cette inefficacité provient de sa nature "applicative" ou "non-séquentielle" qui rend son exécution (et sa compilation) délicate.

# c) La programmation logique parallèle

Ainsi, nous voici face à un double problème:

les machines parallèles existent et sont viables, mais leur emploi est limité par l'absence de langages de programmation parallèle;

Prolog est un bon langage de programmation, mais son utilisation est limitée par son inefficacité séquentielle.

Toutefois, la nature "non-séquentielle" de Prolog se traduit par la présence de multiples opportunités de parallélisation. En conséquence un programme Prolog pourrait être exécuté de façon parallèle faisant ainsi:

- de Prolog, une solution à la maîtrise du parallélisme;

- du parallélisme, un remède à l'inefficacité séquentielle de Prolog.

C'est l'objectif de notre travail, comme de celui de beaucoup d'autres équipes.

# 1.3. Contexte Mondial

Divers centres de recherche travaillent actuellement dans le même domaine, c.a.d. la programmation logique et le parallélisme. Certains d'entre eux examinent plutôt les modèles d'architecture, d'autres préfèrent les questions relatives au langage. Certains privilégient un type spécifique de parallélisme (les types sont présentés dans le chapitre 2). Plusieurs défendent des modifications dans la définition classique de Prolog, parfois en introduisant des mécanismes de contrôle explicite du parallélisme, parfois en proposant un nouveau langage.

Entre les différents projets qui, isolément ou comme partie importante d'un projet plus général, recherchent des solutions aux problèmes posés par l'implantation parallèle d'un langage de programmation logique, nous pouvons citer:

- le projet GIGALIPS [LUS 88] qui concerne principalement les centres de recherche suivants:

- Argonne National Laboratory, USA:

- University of Manchester, Angleterre;

- Swedish Institut of Computer Science, Suède.

- le projet "Fifth Generation Computer Project" qui est conduit par l'ICOT Research Center, au Japon [KUR 88];

- le projet PEPSys, Parallel ECRC Prolog System, en développement depuis 1985 à l'ECRC (European Computer-Industry Research Center), en Allemagne [BAR 88].

#### 1.4. Le Contexte Local

Les travaux et les résultats de cette thèse font partie du projet Opera, conduit par l'équipe Flop, du Laboratoire de Génie Informatique. Ce laboratoire fait partie de l'IMAG (Institut de l'Informatique et Mathématiques Appliquées de Grenoble), groupement de laboratoires communs à l'INPG (Institut National Polytechnique de Grenoble) et à l'UJF (Université Joseph Fourier).

Les recherches de l'équipe Flop se concentrent sur la programmation logique, les systèmes d'exploitation et les outils de développement, principalement dans le cadre du parallélisme.

Le projet Opera ([BRI 90a], [BRI 90b], [BRI 91]) est l'implantation de Prolog pur sur le Supernode, une machine parallèle sans mémoire commune. Actuellement, dans une première phase du projet, seul le parallélisme du type OU a été étudié. Dans cette phase, les tâches suivantes ont été réalisées par les membres de l'équipe Flop:

- la définition du modèle d'exécution;

- la définition de la machine abstraite pour la compilation de Prolog;

- la définition et l'implantation des outils de base pour le développement:

- un assembleur du transputer, processeur du Supernode;

- un éditeur de liens:

- un chargeur et metteur au point pour les cartes à transputer;

- un compilateur C pour le transputer avec des extensions pour le parallélisme:

- les bibliothèques de fonctions C;

- un serveur pour le Supernode: chargeur, communication, entrée/sortie.

- l'adaptation d'un compilateur Prolog à la machine abstraite d'Opera;

- l'implantation (émulation) de la machine abstraite sur le transputer;

- l'implantation d'un premier prototype d'Opera sur le Tnode, la version bas de gamme du Supernode.

#### 1.5. Contribution de l'Auteur

Au moment où l'auteur a commencé son travail de thèse, le projet Opera avait déjà débuté. Divers choix avaient été faits:

- la définition du type de parallélisme à étudier dans la première phase;

- le choix de la machine parallèle;

et diverses tâches étaient en cours:

- la définition du modèle d'exécution;

- la définition de la machine abstraite pour l'implantation de Prolog.

L'auteur a participé à la définition du modèle d'exécution et de la machine abstraite, à l'adaptation d'un compilateur Prolog à la nouvelle machine abstraite, à l'implantation de l'émulation de cette machine, et à l'implantation d'Opera sur la machine parallèle cible.

#### 1.6. La Structure de la Thèse

Le deuxième chapitre consiste en:

- une présentation succinte du modèle de la programmation logique, ainsi que du langage Prolog;

- une introduction au parallélisme en programmation logique: sources, types et modèles.

Dans le chapitre trois, le modèle OU multi-séquentiel de parallélisme en Prolog est étudié de façon plus approfondie. Ceci se justifie par le fait que le système Opera, sujet de cette thèse, est un exemple de ce modèle. Nous décrivons les principes de ce modèle, et nous abordons les problèmes principaux de son implantation, ainsi que les solutions les plus remarquables trouvées dans la littérature. Une attention spéciale est donnée à la régulation de charge, un problème crucial dans le cas du modèle multi-séquentiel OU.

Le chapitre quatre est le cœur de cette thèse. Il se traduit par une description détaillée du système Opera, qui comprend:

- les caractéristiques principales du projet Opera: objectifs initiaux et choix de base:

- les principes du système Opera, et les problèmes principaux à résoudre dans une implantation;

- une étude de la gestion des contextes multiples, en proposant deux méthodes pour son traitement;

- une méthode efficace pour l'implantation de la coupure en parallèle;

- la régulation de charge, ici abordée du point de vue des caractéristiques du système Opera;

- l'architecture du logiciel Opera, en présentant les processus et le protocole de messages.

Il faut remarquer une caractéristique initiale du projet Opera: nous avons décidé de privilégier les architectures sans mémoire commune. Ceci affecte fortement certains aspects du système Opera, comme la gestion des contextes multiples et la régulation de charge.

Un résumé de l'implantation d'un prototype d'Opera, sur une classe particulière de machines sans mémoire commune (le Supernode), se trouve dans le chapitre 5. Les premiers résultats de sa performance y sont présentées.

La thèse se termine par les conclusions que nous avons pu tirer de ces études, et de l'implantation du parallélisme OU multi-séquentiel sur une machine sans mémoire commune.

# 2. Chapitre 2

# Programmation Logique, Prolog et Parallélisme

Ce chapitre comprend deux parties. La première partie est une définition succincte du modèle de programmation logique ainsi que du langage Prolog, lequel en est la concrétisation principale. Nous pensons que ceci est nécessaire pour deux raisons:

proposer à un lecteur qui ne connaît ni l'un ni l'autre, un minimum de concepts nécessaires à la compréhension du texte qui suit;

bien préciser les concepts que nous lions aux expressions les plus souvent utilisées dans ce texte.

Outre ces raisons, cette partie permettra de préciser, dans la suite, les limites et les possibilités de Prolog par rapport à la programmation logique.

La deuxième partie est une introduction au parallélisme en Prolog: sources, types et modèles.

# 2.1. Prolog en un Exemple

Cette section introduit Prolog par un exemple simple.

La construction la plus simple en Prolog est le fait. Un fait est une affirmation, ou relation, qui est toujours vraie. Quelques exemples sont présentés, accompagnés de leur sens en langue naturelle:

| pere(jacques, marie).          | Jacques est le père de Marie |  |

|--------------------------------|------------------------------|--|

| age(marie, 4).                 | Marie a 4 ans.               |  |

| profession(jacques, dentiste). | Jacques est dentiste.        |  |

Un programme peut contenir un ensemble de faits du même type, ce qui correspond à une base de données.

L'utilisateur peut demander si un fait particulier est "vrai" ou "faux", c.a.d. s'il existe dans la base de données du programme. Cette demande s'exprime par un **but**. Par exemple, étant donné les faits ci-dessous,

```

pere(jacques, marie).

pere(jacques, philippe).

pere(philippe, jean).

```

et le but suivant,

```

:- pere(jacques, philippe). Jacques est-il le père de philippe?

```

l'exécution de ce programme Prolog répond OUI.

L'exécution répond NON pour le but

```

:- pere(jacques, martine).

```

L'utilisateur peut encore demander quels sont tous les enfants de Jacques en utilisant une variable (une variable commence par une majuscule), *Enfant* dans le but ci-dessous:

:- pere(jacques, Enfant). De quel enfant, Jacques est-il le père?

L'exécution du programme répond:

Enfant = marie; Enfant = philippe;

Le deuxième type de construction en Prolog est la règle. Celle-là permet de résoudre des problèmes plus complexes que le précédent. Une règle comporte deux parties: la tête et le corps. La tête est vraie si le corps est vrai. La tête a le même format qu'un fait, et le corps est une série de buts. Le programme précédent peut être augmenté par la règle suivante qui exprime la relation de parenté (l'une entre les possibles) entre un grand-père et son petit-enfant:

grandpere(GrandPere, PetitEnfant):pere(GrandPere, Pere),

pere(Pere, PetitEnfant).

Par cette règle, un *PetitEnfant* est le petit-enfant d'un *GrandPere*, si celui-là est le père d'un *Pere* et si celui-ci est le père du *PetitEnfant*. *GrandPere*, *PetitEnfant* et *Pere* sont des variables.

On peut proposer le but

:- grandpere(jacques, PetitEnfantJacques).

qui correspond à "Est-ce que Jacques a des petits-enfants?", et auquel Prolog répond affirmativement:

PetitEnfantJacques = jean;

Finalement, Prolog offre la récurrence, qui permet d'exprimer des programmes plus complexes. Par exemple, au programme précédent on peut ajouter les deux règles suivantes, exprimant la relation d'ascendance entre deux personnes:

ascendance(Ascendant, Descendant): pere(Ascendant, Descendant):

ascendance(Ascendant, Descendant): pere(Ascendant, AscendantPlusProche),

ascendance(AscendantPlusProche, Descendant).

Par ces règles, deux personnes ont une relation d'ascendance si soit l'Ascendant est le père du Descendant (première règle), soit l'Ascendant est le père d'un AscendantPlusproche, et celui-ci est un ascendant du Descendant. Au but ci-dessous

:- ascendance(AscendantsJean, jean).

Prolog répond:

AscendantsJean = philippe; AscendantsJean = jacques;

Il est important d'observer que, en Prolog, on peut exprimer une fonction par une relation (règle), et qu'on peut l'exécuter de plusieurs façons. Ainsi, pour la fonction grandpère(personne), dont la valeur est le grand-père d'une personne, et exprimée par la règle grandpere(GrandPere, PetitFils), trois exécutions sont possibles:

au sens classique: on demande les résultats (valeurs) à partir des arguments d'entrée: par exemple, le but grandpere(GrandPere, jean);

- à l'envers: on demande les arguments d'entrée à partir des résultats: par

exemple, le but grandpere(jacques, PetitEnfantJacques);

comme test: les arguments et les résultats sont fournis, et on demande une vérification de la relation entre eux: par exemple, le but grandpere(jacques, jean).

Ainsi, un même programme permet de résoudre des problèmes différents.

# 2.2. Programmation Logique

La programmation logique est un modèle de programmation dérivé de la logique de prédicats du premier ordre. Celle-ci est l'un des formalismes utilisés en logique pour la représentation et le traitement d'axiomes et de propositions dans le domaine scientifique en général.

Les divers concepts utilisés en programmation logique seront présentés par la logique des clauses de Horn, une sous-partie de la logique de prédicats du premier ordre.

Une description formelle et détaillée de la programmation logique est présentée dans le texte de Lloyd ([LLO 88]). Les chapitres initiaux de [STE 86] et le chapitre 10 de [CLO 85] contiennent des introductions plus simples. Parmi les références sur la définition et les caractéristiques les plus importantes de la programmation logique, les articles [KOW 74] et [KOW 83] peuvent être cités, le premier étant considéré comme l'acte fondateur de la programmation logique.

#### 2.2.1. Syntaxe

En général les auteurs utilisent une syntaxe bien proche de celle utilisée par la logique des prédicats du premier ordre. Afin de rendre ce texte moins long, nous utilisons une simplification de la syntaxe de C-Prolog, lequel est l'une des implantations les plus populaires de Prolog. Cette syntaxe est utilisée dans notre implantation de Prolog, à quelques exceptions près.

#### Variables:

Les variables représentent des objets arbitraires et s'écrivent comme des suites alphanumériques, qui commencent soit par une lettre majuscule soit par un sous-tiret (\_).

Exemples: X, Y, Pere, GrandPere.

#### Constantes:

Une constante représente un objet distinct, tel qu'un entier ou un atome. Les entiers sont représentés de la façon usuelle. Les atomes sont représentés par des suites alphanumériques qui commencent par une lettre minuscule.

Exemples de entiers: 0, 1, 34, 2409, -56.

Exemples d'atomes: table, jacques, françoise.

#### Termes:

Un terme est:

- soit une variable:

- soit une constante:

soit une expression, dite terme fonctionnel (ou composé ou structuré), de la forme f(t<sub>1</sub>, t<sub>2</sub>, ..., t<sub>n</sub>) où f est un symbole fonctionnel (représenté par une suite alphanumérique qui commence par une lettre minuscule), les sous-termes t<sub>i</sub> sont des termes (définition récurrente), et n est l'arité du terme (nombre de sous-termes).

Exemple de termes structurés: liste(a, 3, X).

Les constantes sont aussi définies comme termes fonctionnels d'arité zéro.

# Formule atomique:

Une formule atomique est une expression de la forme  $p(t_1, t_2, ..., tm)$  où p est un symbole de prédicat à m positions (arité), et les  $t_i$  sont des termes. Le symbole de prédicat s'écrit comme une suite alphanumérique, débutant par une minuscule.

Exemples: pere(jacques, marcel), mere(marie, X).

#### Formule:

Une formule est soit une formule atomique soit une des expressions suivantes (à droite dans la liste ci-dessous) où F et G sont des formules:

| - négation:                   | not(F)  |

|-------------------------------|---------|

| - disjonction:                | F; G    |

| - conjonction:                | F, G    |

| - G implique F:               | F :- G  |

| - équivalence:                | F <-> G |

| - quantificateur universel:   | ∀x F    |

| - quantificateur existentiel: | ∃x F    |

#### Littéral:

Un littéral est soit une formule atomique soit sa négation.

# Clause de programme1:

Une clause de programme (clause dans la suite) est une formule de la forme

$$A := B_1, B_2, ..., B_n$$

où A est une formule atomique et les  $B_i$  sont des littéraux et toutes les variables de la clause sont quantifiées universellement  $(\forall)$ . A est la **tête** de la clause et la conjonction des  $B_i$  est le **corps**.

#### Exemple:

$$grandPere(X, Y) :- pere(X, Z), pere(Z, Y).$$

<sup>&</sup>lt;sup>1</sup>Dans les clauses de Horn (but inclus), les sous-buts doivent être des formules atomiques.

Une clause unitaire, dénommée aussi fait, est une clause dont le corps est vide (n est égal à zéro), le symbole :- étant omis.

Exemple: pere(jacques, marcel).

Les clauses dont le corps n'est pas vide (n est égal ou supérieur à 1) sont dénommées **règles**.

# But de programme:

Un but est une formule de la forme

où chaque  $B_i$  est un littéral dénommé sous-but et toutes les variables sont quantifiées de façon existentielle.

#### Prédicat:

Un prédicat est défini par un ensemble fini de clauses de programme dont la tête contient le même symbole de prédicat avec la même arité.

# Exemple:

```

ancetre(X, Y):- parent(X, Y).

ancetre(X, Y):- parent(X, Z), ancetre(Z, Y).

```

# Programme:

Un programme est un ensemble fini de prédicats.

### 2.2.2. La sémantique déclarative

La sémantique d'un programme logique admet plusieurs définitions ([EMD 76]): déclarative, procédurale et dénotationelle. Cette section est une présentation informelle de la sémantique déclarative.

Les concepts de base de la sémantique déclarative, utilisée dans la programmation logique, sont l'interprétation et les modèles de Herbrand ([LLO 88], [STE 86]). Voici quelques définitions, nécessaires pour la suite:

Règle

$$(\forall X_i (A :- B_1, B_2, ..., B_n))$$

:

Pour toutes les valeurs de  $X_i$ , A est vrai si  $B_1$ ,  $B_2$ , ..., et  $B_n$  sont vrais. Pour prouver A, il est suffisant de prouver  $B_1$ ,  $B_2$ , ...,  $B_n$ . Si A est faux au moins l'un des  $B_i$  est faux. Si l'un des  $B_i$  est faux A peut être faux ou vrai.

# Fait $(\forall X_i (A))$ :

Pour toutes les valeurs de  $X_i$  A est toujours vrai.

#### Programme:

Un programme est la spécification formelle d'une théorie dans un certain domaine. Les règles et les faits du programme représentent cette théorie.

But

$$((\exists X_i \ B_1, \ B_2, \ ..., \ B_n) \ ou \ (\forall X_i :- B_1, \ B_2, \ ..., \ B_n))$$

:

Existe-t-il des valeurs de  $X_i$  pour lesquelles  $B_1, B_2, ...,$  et  $B_i$  sont vrais? Si le but ne contient pas de variables: est-ce que  $B_1, B_2, ..., B_n$  sont vrais?

#### Clause vide:

Une clause vide est une contradiction.

# Interpréteur d'un langage logique:

Etant donnés un programme et un but, l'interpréteur du langage logique doit essayer de vérifier la satisfaisabilité du but par rapport au programme. La résolution SLD, décrite dans la section suivante, est à la base d'un tel interpréteur.

#### 2.2.3. La résolution SLD

La résolution SLD est une méthode de déduction d'assertions à partir d'axiomes exprimés sous la forme de clauses de Horn. Les trois lettres de SLD ont le sens suivant:

- D: la méthode est applicable aux clauses définies (de Horn);

- L: la méthode est linéaire, c.a.d. à chaque pas une seule formule est conservée;

- S: la méthode utilise des règles de sélection (choix) de formules.

Elle a été décrite, pour la première fois, par Kowalski ([KOW 74]). Désormais la résolution SLD est à la base du modèle d'exécution de la programmation logique. Elle est une simplification du principe de résolution proposé par Robinson ([ROB 65]) pour les clauses dans la forme normale, dont il est très difficile d'extraire une implantation efficace à cause d'un espace de recherche extrêmement vaste.

La résolution SLD utilise la technique de preuve par réfutation: pour démontrer qu'un but G est une conséquence d'un programme P, il est prouvé que la négation du but et le programme sont contradictoires. Dans le cas de la résolution SLD la négation de G est ajoutée au programme et, à partir de ce nouvel ensemble de clauses, on essaie de déduire la clause vide. L'avantage de la preuve par réfutation, dans le cas où G est une conséquence de P, est la certitude d'obtenir la clause vide en un nombre fini de pas à condition qu'un "bon choix" de clause soit fait (ce point sera revu par la suite). Par contre, en appliquant une méthode de déduction qui essaye de dériver G à partir de P, il est plus difficile dans le cas général de trouver le "bon chemin" (qui vérifie G en un nombre fini de pas), même si G est une conséquence de P.

Le programme et le but de la fig. 2.1 ([LLO 88]) seront utilisés pour illustrer les définitions présentées dans la suite.

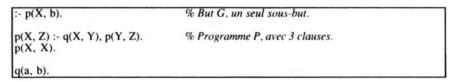

Fig. 2.1 - Programme exemple de la résolution SLD

La résolution SLD utilise une opération complexe et spécifique, nommée unification, laquelle applique deux opérations plus simples: la substitution et l'exemplarisation. Ces trois opérations correspondent aux notions suivantes:

#### Substitution:

Une substitution est un ensemble fini de la forme  $\{v_1/t_1, v_2/t_2, ..., v_n/t_n\}$  où  $v_i$  est une variable,  $t_i$  est un terme,  $v_i$  est différent de  $v_j$  pour tout i différent de j. Par exemple,  $\{X/a, Y/b\}$  est une substitution pour les variables de la première clause de P (voir fig.2.1)

#### Exemplarisation (instantiation):

Etant donnés une substitution q et un littéral L, l'exemplarisation Lq est le nouveau littéral produit par le remplacement de chaque référence à  $v_i$  dans L par  $t_i$  si  $t_i/v_i$  appartient à q. D'une façon informelle l'exemplarisation est l'application d'une substitution q à un littéral L. Lq est un exemplaire de L. L'application de  $\{X/a, Y/b\}$  au littéral q(X, Y), p(Y, Z) produit q(a, b), p(b, Z) (voir fig.2.1).

#### Unification:

Etant donnés deux littéraux,  $L_1$  et  $L_2$ , une substitution  $\theta$  est un **unificateur** de  $L_1$  et de  $L_2$  si  $L_1\theta = L_2\theta$ . Un littéral  $L_1$  est **plus général** qu'un autre littéral  $L_2$  si  $L_2$  est un exemplaire de  $L_1$ . On peut dire qu'il existe une substitution  $\theta_a$  telle que  $L_2 = L_1\theta_a$ . L'unificateur le plus général de deux littéraux  $L_1$  et  $L_2$  est une substitution  $\theta$  telle que  $L_1\theta = L_2\theta$  et que pour tout autre unificateur  $\alpha$  de  $L_1$  et  $L_2$  il est possible de trouver une substitution  $\beta$  telle que  $L_1\alpha = (L_1\theta)\beta$  (ou  $L_2\alpha = (L_2\theta)\beta$ ).

Un algorithme d'unification de deux littéraux  $L_1$  et  $L_2$  produit l'unificateur le plus général de  $L_1$  et de  $L_2$  s'il existe, ou, dans le cas contraire, indique cette inexistence, c.a.d. un échec. L'algorithme d'unification doit éviter un cas particulier de substitution: pour  $\theta = \{v_1/t_1, v_2/t_2, ..., v_n/t_n\}$  il n'existe pas d'occurrence de la variable  $v_i$  dans  $t_i$ . Ce contrôle s'appelle vérification d'occurrence (occurs-check). Dans l'exemple de la fig. 2,1 l'unificateur le plus général de p(X, b) et p(X, Z) est  $\{Z/b\}$ .

Il est maintenant possible de détailler la méthode de la résolution SLD.

#### Dérivation SLD:

A: Etant donnés un programme P, composé par les clauses C<sub>1</sub>, C<sub>2</sub>, ..., C<sub>n</sub>, et un but G, composé par les sous-buts SG<sub>1</sub>, SG<sub>2</sub>, ..., SG<sub>m</sub>. k est initialisé à 0. Le but G est copié en R<sub>k</sub> appelé résolvante.

- B: Un sous-but SG<sub>i</sub> de R<sub>k</sub> est choisi. Une clause C<sub>j</sub> est aussi choisie parmi les clauses du sous-ensemble SP, constitué de clauses dont la tête s'unifie avec SG<sub>i</sub>. Toutes les variables de C<sub>j</sub> sont renommées de façon à ce que aucune variable de C<sub>j</sub> n'apparaisse dans R<sub>k</sub>. L'algorithme d'unification est appliqué à SG<sub>i</sub> et à la tête de C<sub>j</sub>, en produisant l'unificateur θ<sub>k</sub>. Une nouvelle résolvante R<sub>k+1</sub> est produite, à partir de R<sub>k</sub>, en remplaçant SG<sub>i</sub> par le corps de C<sub>j</sub> et par l'application de θ<sub>k</sub>, k est incrémenté. L'étape B est répétée.

#### La dérivation ci-dessus peut avoir trois résultats:

- succès: R<sub>k</sub> est vide. Dans ce cas une réfutation SLD a été trouvée, c.a.d. la satisfaisabilité du but G a été vérifiée;

- échec: SP est vide;

- boucle infinie: à chaque itération ni R<sub>k</sub> ni SP sont vides.

Un exemple de dérivation SLD avec succès, pour la fig. 2.1, contient les étapes suivantes:

- choix du sous-but (un seul) p(X, b);

- choix de la clause  $p(X_1, Z_1)$ :-  $q(X_1, Y_1)$ ,  $p(Y_1, Z_1)$ . (les indices indiquent le renommage des variables);

- $\theta_0$  est  $\{Z_1/b\}$ ;

- $R_1$  est  $q(X_1, Y_1), p(Y_1, b)$ .;

- unification de  $q(X_1, Y_1)$  et q(a, b), en produisant  $R_2 = p(b, b)$ . et  $\{X_1/a, Y_1/b\}$ :

- unification de p(b, b). et  $p(X_3, X_3)$  (deuxième clause de p/2) en produisant  $R_3$  = vide, ce qui correspond à un succès ou à la preuve de p(X, b).

Dans chaque itération deux choix sont faits: celui du sous-but  $SG_i$  et celui de la clause  $C_j$ . Le premier, appelé **règle d'évaluation**, n'affecte pas le résultat. Si un succès est produit pour un ordre donné d'exécution des sous-buts, il est possible de produire le même succès pour tous les autres ordres. Ceci est parfois appelé l'indépendance de la règle d'évaluation ([LLO 88]): on peut fixer la règle d'évaluation a priori. En outre, tous les sous-buts doivent être exécutés afin de produire un succès.

Par contre, le choix de la clause, ou règle de sélection, est important. Selon la règle de sélection, on peut, pour un même programme et un même but, produire l'un quelconque des trois résultats (succès, échec, boucle infinie). Une seule clause est suffisante afin de produire un succès, à condition d'effectuer le "bon choix". La difficulté provient du fait que le "bon choix" n'est pas évident, car il est indécidable.

En considérant que l'utilisateur s'intéresse aux (au moins une) réfutations et que le "bon choix" de la clause n'est pas évident, il faut prévoir une stratégie (règle) de recherche en cas d'échec:

- quel sous-but précédent (déjà unifié) choisir?;

- quelle nouvelle clause choisir (re-application de la règle de sélection, en éliminant la clause qui a échouée)?

Cette action est nommée **retour-arrière** dans les stratégies séquentielles. La combinaison d'une règle d'évaluation et d'une stratégie de recherche (règle de sélection incluse) est nommée **procédure de réfutation SLD** ([LLO 88]). Il faut observer que, pour un programme et un but et en considérant toutes les clauses, certaines règles d'évaluation produisent des boucles infinies (en plus des succès et des échecs), pendant que d'autres n'en produisent pas. La règle de sélection devient donc importante, parce qu'on ne trouve pas certains succès si les boucles ne sont pas détectées. Des exemples de procédures de réfutation SLD sont présentés plus loin (voir les figures 2.2 et 2.3), en utilisant la représentation en arbre OU.

Il est prouvé que le but G est en contradiction avec le programme P si, en fixant une règle d'évaluation, tous les choix de clauses (toutes les dérivations SLD) amènent à des échecs. La négation de Prolog, ou **négation par échec**, définie dans la suite, applique le même procédé.

#### Notion d'arbre ET/OU:

La résolution SLD peut être représentée par un arbre composé de nœuds ET et OU et de feuilles Echec et Succès. Chaque nœud ET correspond à une sélection de sous-but et contient la résolvante courante. La racine contient le but originel et est un nœud ET. Chaque branche ET (qui part d'un nœud ET) correspond au choix d'un sous-but. A la pointe d'une branche ET il peut y avoir:

- une feuille Echec: il n'y a pas de clause qui puisse être unifiée avec le sousbut;

- un nœud OU: il groupe toutes les clauses qui peuvent être unifiées avec le sous-but respectif.

Chaque nœud OU correspond à une sélection de clause et contient le sous-but choisi précédemment. Chaque branche OU correspond au choix d'une clause dont la tête sera unifiée avec son sous-but. A la pointe d'une branche OU il peut y avoir:

- succès: la clause respective est un fait et la résolvante courante contient un seul sous-but;

- un nœud ET: il contient la nouvelle résolvante où le sous-but du nœud OU précédent a été remplacé par le corps de la clause respective.

La satisfaisabilité du but originel est prouvée s'il y a au moins une feuille Succès. La satisfaisabilité du but originel ne peut pas être prouvée s'il n'y a pas de feuilles Succès.

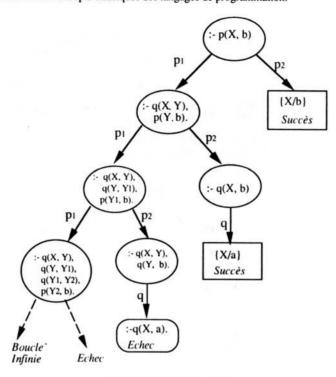

Fig. 2.2 - Arbre OU fini

Etant donné que la règle d'évaluation n'affecte pas les résultats, on peut maintenir une seule branche par nœud ET. En général les nœuds ET sont omis soit en figeant une règle d'évaluation soit en annotant le sous-but choisi dans chaque nœud OU. L'arbre ET/OU se transforme en un arbre OU.

Les figures 2.2 et 2.3 sont des exemples de représentations en arbre OU de deux différentes procédures de réfutation SLD, appliquées au programme de la fig. 2.1. La première utilise une règle d'évaluation qui choisit toujours le sous-but le plus à gauche. Cet arbre ne possède pas de boucles infinies. La règle d'évaluation de la fig. 2.3 choisit toujours le sous-but le plus à droite, en produisant des boucles infinies. Les deux possèdent le même nombre de succès.

# 2.2.4. Interprétation Procédurale

L'interprétation procédurale ([KOW 74], [KOW 79]) est une analogie entre la résolution SLD et les concepts classiques des langages de programmation.

Fig. 2.3 - Arbre OU infini

Les points principaux de cette analogie sont:

# Procédure:

Une procédure est l'ensemble des clauses d'un programme, dont les têtes ont le même symbole de prédicat et la même arité. Le nom de la procédure est formé par symbole/arité. Chaque clause est une définition (alternative) de la procédure. Le corps d'une définition est composé exclusivement d'appels de procédures.

# Appel de procédure:

Chaque littéral du corps d'une clause et du but est un appel de procédure.

# Arguments:

Les arguments d'un appel sont tous les termes de chaque littéral.

# Unification:

L'unification est interprétée comme une seule opération qui englobe:

- passage de paramètres: une variable de la tête de la clause est unifiée à un sous-terme (constant ou non) d'un argument;

- retour de résultats: une variable d'un argument est unifiée à un sous-terme (constant ou non) de la tête de la clause.

# Exécution du programme:

La solution d'un problème G (but) par un programme P passe par l'exécution de chaque sous-but  $G_i$  de G. Pour exécuter chaque  $G_i$  il est nécessaire de résoudre tous les sous-buts  $B_j$  d'une clause dont la tête s'unifie avec le sous-but  $G_i$ . L'interprétation procédurale impose la contrainte suivante: pour exécuter le sous-but  $G_{i+1}$  d'un but  $G_i$ , il ne doit plus rester de sous-buts  $B_j$  non-exécutés du sous-but  $G_i$  précédemment choisi. L'exécution d'un sous-but,  $G_i$  ou  $B_i$ , s'achève si la clause avec laquelle il est unifié possède un corps vide.

# Représentation en arbre OU:

Chaque nœud OU représente la liste d'appels à exécuter, en explicitant le premier (règle d'évaluation). Chaque branche correspond à une définition de procédure dont le nom concorde avec l'appel. Une feuille de succès indique une solution au problème initial. Une feuille d'échec est une alternative de calcul qui ne produit pas de solution.

# 2.3. Prolog

Cette section présente le langage Prolog. Nous essayons de mettre en évidence les différences par rapport au modèle de la programmation logique, et les caractéristiques qui posent des problèmes pour une implantation parallèle.

#### 2.3.1. Prolog Pur

Le langage Prolog (PROgrammation en LOGique) est une concrétisation du modèle de programmation logique décrit dans les sections précédentes. Prolog a été défini par A. Colmerauer au début des années 70. Les études de Colmerauer portaient sur les langues naturelles (grammaires, traduction automatique), et un langage adapté à ce type de problème fut défini et réalisé ([COL 72]). Ce langage fut définitivement fondé avec la rencontre avec les travaux de Kowalski sur la logique ([COH 88], [VAN 86]).

L'exécution d'un programme Prolog "pur" est conforme à une mise en œuvre de la résolution SLD, appliquée à un ensemble de clauses et un but initial. Cette mise en œuvre, ou procédure de réfutation SLD, est définie par les règles suivantes :

- R1: la règle d'évaluation choisit toujours, et seulement, le premier sous-but à gauche;

- R2: la règle de sélection a deux parties:

- Prolog choisit toujours la première clause, dans l'ordre d'écriture, unifiable avec le sous-but choisi;

- après un succès ou un échec, l'exécution reprend le nœud OU le plus récent, contenant encore des clauses non exécutées. La prochaine clause de ce nœud est choisie.

R3: dans la nouvelle résolvante le corps de la clause est mis à gauche, c.a.d. la clause sélectionnée sera exécutée avant les autres sous-buts de la résolvante antérieure.

Les règles R1 et R3 coupent tous les sous-arbres dérivés d'un nœud ET de l'arbre ET/OU, à l'exception d'une branche, celle qui correspond au premier sous-but à gauche de la résolvante. Ceci permet la transformation de l'arbre ET/OU en un arbre OU. Le deuxième point de la règle R2 correspond au concept de retour-arrière. Toutes ces règles correspondent à un parcours en profondeur d'abord (R1 et R3) et de gauche à droite (R2) de l'arbre OU. Le parcours en profondeur d'abord équivaut à l'interprétation procédurale.

Cette stratégie, en séquentiel, ne produit pas toutes les solutions (succès) dans les cas de programmes dont l'arbre OU contient des branches infinies. Cependant elle est simple et elle consomme peu de mémoire. Elle contraste avec la stratégie en largeur d'abord, où on essaye d'avancer "en parallèle" toutes les branches de l'arbre OU. Cette deuxième stratégie évite les impasses que sont les arbres infinies pour la stratégie en profondeur. Par contre, elle exige un espace en mémoire plus grand, et son contrôle est plus complexe.

Il est possible de résoudre divers problèmes académiques avec Prolog, réduit à la logique de clauses de Horn. Cependant, pour la programmation d'applications réelles, il a été nécessaire d'introduire des prédicats prédéfinis (calcul arithmétique, entrée/sortie, ...) dans le langage. Plusieurs d'entre eux ne peuvent pas recevoir une interprétation purement logique. Dans les prochaines sections quelques-uns de ces prédicats seront analysés, en particulier ceux dont la sémantique et/ou l'implantation sont affectées par le parallélisme.

# 2.3.2. La Coupure

L'exécution d'un prédicat Prolog effectue une recherche exhaustive et produit en général diverses solutions. Si pour chaque valeur d'un argument d'appel, une seule solution est possible, un tel prédicat est déterministe. Une fois la solution trouvée, il est inutile de continuer à en chercher d'autres (suppression de calculs inutiles, qui produisent des échecs). Parfois, pour des prédicats non-déterministes, il n'est pas utile de chercher d'autres solutions après qu'une première ait été trouvée. Dans le but de réduire le temps et la mémoire nécessaires à la recherche de ces solutions inutiles ou inexistantes, un prédicat prédéfini, nommé coupure (représenté par !), a été introduit.

La sémantique de la coupure est la suivante: étant donné une clause  $C_i$  d'un prédicat p de la forme

$$A_1 \dots$$

$A_i := B_1, \dots, B_j, !, B_{j+1}, \dots, B_k$  % clause  $C_i$

$A_{i+1} \dots$

$A_n$

l'exécution de ! coupe toutes les alternatives restantes parmi celles créées à partir de l'appel du prédicat p, c.a.d. les clauses qui suivent  $C_i$  ( $A_{i+1}$  à  $A_n$ ) dans la définition de p et les alternatives créées par l'exécution de  $B_1$  à  $B_i$ .

Certains emplois de la coupure n'affectent pas la lecture déclarative (purement logique) de chaque clause. Ce type d'emploi est nommé coupure verte. Son seul objectif est l'efficacité: éviter la recherche d'autres solutions valides ou d'échecs. Si la coupure est enlevée le programme produit les résultats corrects. L'exemple classique est le prédicat maximum/3 qui retourne le maximum de deux nombres. La coupure !1 est verte parce que la deuxième clause peut être lue de façon déclarative.

```

\max \operatorname{imum}(X, Y, X) := X \ge Y, !_1. \\

\operatorname{maximum}(X, Y, Y) := X < Y, !_2.

```

Par contre, dans d'autres emplois, nommés coupure **rouge**, la seule lecture possible est celle définie par l'ordre de déclaration de clauses. En général cette restriction est due à l'omission des conditions qui valident les clauses suivantes à la coupure. Elles ne doivent être exécutées que si la clause qui contient la coupure échoue avant la coupure. Si la coupure est enlevée et la clause n'échoue pas, les clauses suivantes produiront des solutions invalides. La coupure  $!_1$  de maximum/3 devient rouge, si la condition X < Y de la deuxième clause est enlevée.

```

\begin{aligned} & \text{maximum}(X, Y, X) :- X \ge Y, !_1. \\ & \text{maximum}(X, Y, Y). \end{aligned}

```

#### 2.3.3. La Négation

Le modèle de programmation logique décrit dans les sections précédentes ne comporte pas la négation. Les faits négatifs sont simplement omis. Par exemple, dans le cas du programme exemple de la première section, il n'est pas possible de déclarer, en utilisant le prédicat pere/2, que jean n'est pas le père de marie.

La solution adoptée pour l'expression de la négation est le concept de **négation par échec**. La négation d'un but est vrai s'il n'est pas possible de prouver le but. Dans le cas des faits, si le but-fait n'est pas déclaré dans le programme, alors la négation de ce but est vrai.

Dans le contexte de la résolution SLD, étant donné un but not(B), la solution ci-dessus implique un parcours de toutes les alternatives du but B afin de vérifier qu'il n'existe aucune solution. A ce moment not(B) est considéré vrai, not(B) est éliminé de la résolvante et aucune substitution pourvue par B n'est conservée. La négation par échec ne peut être utilisée que lorsque l'arbre de recherche du but nié ne possède pas de boucles infinies. En effet, la présence d'une seule branche infinie implique la non-terminaison de la négation.

Notons que la notion de négation par l'échec ne correspond pas exactement à la négation logique. Par exemple, la solution du but

:- not(p(X)), q(X).

et des faits:

p(a). p(b). q(c).

est dépendant de l'ordre de choix du sous-but:

- échec si not(p(X)) est sélectionné avant q(X): p(a) est une solution à p(X) donc not(p(X)) est faux;

- succès si q(X) est sélectionné avant not(p(X)): le sous-but p(c) n'a pas de solution.

Par contre, le choix de clauses n'affecte pas les solutions parce que toutes les clauses doivent être examinées pour confirmer la négation.

L'implantation classique de la négation est réalisée au moyen de la coupure. Le prédicat (prédéfini dans le langage) not/1 peut se décrire par:

not(p) :- p, !, fail. not(p).

Si p est prouvé, la deuxième clause de not/l et les autres alternatives de p sont coupées et not/l retourne un échec. Si toutes les alternatives de p échouent not/l retourne un succès par la deuxième clause. La coupure de la première clause est rouge parce que la lecture déclarative de la deuxième clause n'a pas de sens.

Des travaux, ayant comme but la recherche de la négation sure, ont été réalisés ([NAI 86], [BEK 90]). Une solution possible est de différer l'exécution du *not* jusqu'à ce que son argument soit clos.

# 2.3.4. Les Prédicats à Effet de Bord

La plupart des implantations de Prolog offrent divers prédicats prédéfinis qui provoquent des effets de bord. Parmi ceux-ci les principaux sont:

- entrée/sortie: par exemple, read/1, write/1;

- modifications dynamiques des programmes par inclusion/exclusion de clauses: par exemple, assert/1, retract/1;

- les "bases de données" ou table de termes à accès par clef.

En général, l'utilisation correcte de ces prédicats est dépendante des règles de sélection de Prolog. Si par exemple la position des appels de ces prédicats dans une clause est modifiée il est probable que le programme produira d'autres résultats. Le même phénomène peut se produire si l'ordre d'exécution des clauses est changé. Un exemple très simple est la lecture d'un terme, suivie de son écriture:

..., read(X), ..., write(X), ...

# 2.4. Les Machines Abstraites pour Prolog

Depuis le premier compilateur Prolog ([WAR 77]), les travaux sur l'amélioration de la compilation du langage ont conduit à la définition d'une machine abstraite de référence: la WAM, du nom de son créateur Warren ([WAR 83]). Bien que d'autres propositions de machines pour Prolog existent ([CLO 85], [CHA 86], [BEK 86]), la WAM est la machine la plus utilisée pour la compilation. Nous allons décrire les éléments et mécanismes principaux de cette machine séquentielle, qui sont nécessaires pour la compréhension des problèmes posés par la conception d'une machine abstraite parallèle.

Une machine abstraite Prolog (MAP) de type WAM est en général définie par un ensemble de types de données, un ensemble de registres, un ensemble d'instructions et une organisation de la mémoire. Dans la suite, l'organisation de la mémoire et la représentation des variables, ainsi que leurs relations avec le retour-arrière, seront examinées. Pour plus de détails sur la compilation ou sur les instructions, le lecteur peut consulter l'annexe B. Des références sur la WAM sont: [WAR 83], [GAB 85], [BOI 88], [AIT 90].

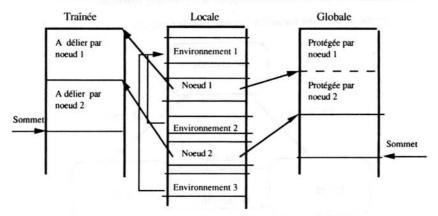

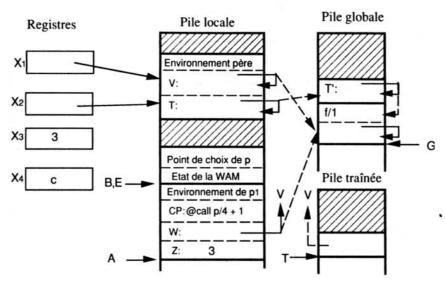

# 2.4.1. L'organisation de la Mémoire et le Retour-Arrière

La mémoire est organisée en 3 piles (conforme le schéma simplifié de la figure 2.4):

- la pile locale: utilisée pour le contrôle des appels de prédicats et du retourarrière, et pour l'allocation des variables locales à une clause;

- la pile globale: utilisée pour la création des termes structurés;

- la pile traînée: utilisée pour la mise à jour des variables, lors du retourarrière.

La pile locale contient deux types de structures de données:

- les environnements: un environnement contient les variables locales d'une clause en exécution;

- les nœuds OU: un nœud OU (ou point de choix) contient une sauvegarde de l'état de la machine, permettant le retour-arrière vers des clauses inexplorées.

Fig. 2.4 - Mémoire simplifiée d'une MAP

L'environnement correspond à la notion de bloc d'activation de procédure dans la compilation des langages classiques. Il contient entre autres les informations nécessaires au retour à la clause appelante: prochain sous-but et pointeur vers son environnement (chaînage dynamique). Il est alloué au début de l'exécution de la clause, la taille étant déterminée par le nombre de variables de la clause. A la fin de l'exécution de la clause, il est libéré. L'environnement sert à renommer les variables d'une clause (ce qui est nécessaire dans la résolution SLD).

Un nœud OU est créé si le prédicat appelé par un sous-but est non-déterministe (plusieurs clauses). Les divers nœuds OU sont empilés. Le plus récent est utilisé en cas d'échec (retourarrière), de façon à restaurer l'état de la machine pour l'exécution de la prochaine clause du prédicat. Un nœud OU est détruit (libéré), si cette prochaine clause est la dernière clause du prédicat. Un nœud OU protège automatiquement les environnements nécessaires au retourarrière, du fait que les deux structures sont allouées dans la même pile physique. L'espace d'un environnement ne peut pas être réutilisé (après la fin de la clause), si un nœud OU a été créé pendant son exécution. En outre, un nouvel environnement est toujours alloué au sommet de la pile. L'environnement protégé par un nœud OU n'est récupéré que lors d'un retour-arrière à un nœud OU plus ancien. Ce mécanisme de protection et de récupération de mémoire, ainsi que les mécanismes équivalents des piles globale et traînée, exigent la sauvegarde des sommets des piles dans les nœuds OU (état de la machine).

Les termes structurés, nécessaires à l'exécution du programme, sont construits dans la pile globale. L'espace alloué n'est récupéré que lors d'un retour-arrière à un nœud OU, créé avant le terme, c.a.d. en cas d'échec ou de recherche d'une autre solution.

Le rôle de la pile traînée sera examinée après la présentation de l'implantation des variables.

#### 2.4.2. Les Variables: Représentation et Etats

Une variable logique est représentée par une cellule de mémoire, dans la pile locale, si elle est locale à une clause, ou dans la pile globale, si elle est un sous-terme d'un terme structuré.

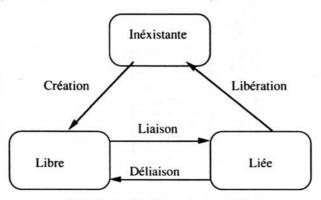

L'initialisation de la cellule (à la première référence) la met à **libre** ("valeur inconnue"). Après substitution, la variable reprend une valeur. Cette substitution est représentée par un pointeur vers le terme qui représente la valeur de la variable. Cette opération est nommée **affectation** ou **liaison**. Certaines variables peuvent être créées avant un nœud OU et affectées par une substitution après ce nœud. En cas de retour-arrière à ce nœud, ces affectations doivent être défaites sans détruire les variables. Cette opération est nommée **déliaison**.

Le graphe d'états d'une variable est montré dans la figure 2.5.

Fig. 2.5 - Graphe d'états d'une variable

Les liaisons **conditionnelles**, ou **inconditionnelles**, (fig. 2.6) sont celles qui sont, ou ne sont pas, séparées de la création de la variable par la création d'un nœud OU. Une liaison inconditionnelle n'est jamais défaite.

#### 2.4.3. La Pile Traînée

Les déliaisons peuvent être effectuées à partir d'un enregistrement de chaque liaison conditionnelle. En général ces enregistrements sont maintenus dans une pile nommée pile traînée. Lors d'un retour-arrière vers un nœud OU, cette pile est parcourue entre le sommet actuel et le sommet au moment de la création du nœud OU. Toutes les variables enregistrées dans cette partie de la pile sont déliées.

#### 2.5. Parallélisme en Programmation Logique

Dans cette section, nous présentons brièvement les différentes sources et types de parallélisme en programmation logique, les différentes approches pour la définition d'un langage de programmation logique parallèle et les problèmes posés par l'exploitation de ces sources de parallélisme, ainsi que des solutions simplificatrices.

# 2.5.1. Les Sources de Parallélisme

Les sources potentielles de parallélisme dans l'exécution d'un programme logique sont:

- le parallélisme OU: l'exécution en parallèle des clauses d'un prédicat;

- le parallélisme ET: l'exécution en parallèle des sous-buts d'une clause ou d'un but;