# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# VÍCTOR EDUARDO MARTÍNEZ ABAUNZA

# Performance Optimization of Geophysics Stencils on HPC Architectures

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor:

Prof. Dr. Philippe Olivier Alexandre Navaux Advisor during Ph.D. internship: Dr. Fabrice Dupros

#### **CIP** — **CATALOGING-IN-PUBLICATION**

Martínez Abaunza, Víctor Eduardo

Performance Optimization of Geophysics Stencils on HPC Architectures / Víctor Eduardo Martínez Abaunza. – Porto Alegre: PPGC da UFRGS, 2018.

129 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2018. Advisor: Philippe Olivier Alexandre Navaux; Advisor during Ph.D. internship: Fabrice Dupros.

I. Navaux, Philippe Olivier Alexandre. II. Dupros, Fabrice. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof. João Luiz Dihl Comba

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

«(El cabalista que ofició de numen a la vasta criatura apodó Golem; estas verdades las refiere Scholem en un docto lugar de su volumen.)» EL GOLEM — J. L. BORGES

# **ACKNOWLEDGMENT**

# I want to thank to:

My family, you are the reason

My friends, they become my family

My advisers, they become my friends

My colleagues, they become my advisers

and all the people that support me...

You know who you are.

Víctor

#### **ABSTRACT**

Wave modeling is a crucial tool in geophysics, for efficient strong motion analysis, risk mitigation and oil & gas exploration. Due to its simplicity and numerical efficiency, the finite-difference method is one of the standard techniques implemented to solve the wave propagation equations. This kind of applications is known as stencils because they consist in a pattern that replicates the same computation on a multi-dimensional domain. High Performance Computing is required to solve this class of problems, as a consequence of a large number of grid points involved in three-dimensional simulations of the underground. The performance optimization of stencil computations is a challenge and strongly depends on the underlying architecture.

In this context, this work was directed toward a twofold aim. Firstly, we have led our research on multicore architectures and we have analyzed the standard OpenMP implementation of numerical kernels from the 3D heat transfer model (a 7-point Jacobi stencil) and the Ondes3D code (a full-fledged application developed by the French Geological Survey). We have considered two well-known implementations (naïve, and space blocking) to find correlations between parameters from the input configuration at runtime and the computing performance; thus, we have proposed a Machine Learning-based approach to evaluate, to predict, and to improve the performance of these stencil models on the underlying architecture. We have also used an acoustic wave propagation model provided by the *Petrobras* company and we have predicted the performance with high accuracy on multicore architectures. Secondly, we have oriented our research on heterogeneous architectures, we have analyzed the standard implementation for seismic wave propagation model in CUDA, to find which factors affect the performance; then, we have proposed a task-based implementation to improve the performance, according to the runtime configuration set (scheduling algorithm, size, and number of tasks), and we have compared the performance obtained with the classical CPU or GPU only versions with the results obtained on heterogeneous architectures.

**Keywords:** HPC. Machine Learning. Multicore. Heterogeneous Architectures. Stencil Computations. Performance Simulation. Performance improvement.

# Optimização de Desempenho de Estênceis Geofísicos sobre Arquiteturas HPC

#### **RESUMO**

A simulação de propagação de onda é uma ferramenta crucial na pesquisa de geofísica (para análise eficiente dos terremotos, mitigação de riscos e a exploração de petróleo e gáz). Devido à sua simplicidade e sua eficiência numérica, o método de diferenças finitas é uma das técnicas implementadas para resolver as equações da propagação das ondas. Estas aplicações são conhecidas como estênceis porque consistem num padrão que replica a mesma computação num domínio multidimensional de dados. A Computação de Alto Desempenho é requerida para solucionar este tipo de problemas, como consequência do grande número de pontos envolvidos nas simulações tridimensionais do subsolo. A optimização do desempenho dos estênceis é um desafio e depende do arquitetura usada. Neste contexto, focamos nosso trabalho em duas partes. Primeiro, desenvolvemos nossa pesquisa nas arquiteturas multicore; analisamos a implementação padrão em OpenMP dos modelos numéricos da transferência de calor (um estêncil Jacobi de 7 pontos), e o aplicativo Ondes3D (um simulador sísmico desenvolvido pela Bureau de Recherches Géologiques et Minières); usamos dois algoritmos conhecidos (nativo, e bloqueio espacial) para encontrar correlações entre os parâmetros da configuração de entrada, na execução, e o desempenho computacional; depois, propusemos um modelo baseado no Aprendizado de Máquina para avaliar, predizer e melhorar o desempenho dos modelos estênceis na arquitetura usada; também usamos um modelo de propagação da onda acústica fornecido pela empresa *Petrobras*; e predizemos o desempenho com uma alta precisão (até 99%) nas arquiteturas multicore. Segundo, orientamos nossa pesquisa nas arquiteturas heterogêneas, analisamos uma implementação padrão do modelo de propagação de ondas em CUDA, para encontrar os fatores que afetam o desempenho quando o número de aceleradores é aumentado; então, propusemos uma implementação baseada em tarefas para amelhorar o desempenho, de acordo com um conjunto de configuração no tempo de execução (algoritmo de escalonamento, tamanho e número de tarefas), e comparamos o desempenho obtido com as versões de só CPU ou só GPU e o impacto no desempenho das arquiteturas heterogêneas; nossos resultados demostram um speedup significativo (até ×25) em comparação com a melhor implementação disponível para arquiteturas multicore.

**Palavras-chave:** HPC, aprendizado de máquina, multicore, arquiteturas heterogêneas, computação de estênceis, simulação de desempenho, ganho de desempenho.

#### LIST OF ABBREVIATIONS AND ACRONYMS

ANOVA Analysis of Variance

APU Accelerated Processing Architecture

BRGM French Geological Survey

CM Cache Misses

CPU Central Processing Unit

CUDA Compute Unified Device Architecture

DAG Directed Acyclic Graph

DMA Direct Memory Access

DRAM Dynamic Random Access Memory

DP Data Parallelism

FDM Finite Difference Method

EDP Energy Delay Product

FPGA Field Programmable Gate Arrays

GPU Graphics Processing Unit

HC Heterogeneous Computing

HCS Heterogeneous Computing System

HT HyperThreading

HPC High Performance Computing

ILP Instruction Level Parallelism

ISA Instruction-Set Architectures

LLC Last Level Cache

LU Lower Upper Decomposition

MIPS Microprocessors with Interlocked Pipeline Stages

ML Machine Learning

MLP Memory Level Parallelism

MPI Message Passing Interface

MSE Mean Squared Error

NUMA Non-Uniform Memory Access

PCIe Peripheral Component Interconnect Express

PTX Parallel Thread Execution

PU Processing Unit

RISC Reduced Instruction Set Computer

RMSE Root Mean Square Error

S2S Source-to-source

SCHP Single-Chip Heterogeneous Processor

SIMD Single Instruction Multiple Data

SM Streaming Multiprocessors

SMP Symmetric Multi-Processing

SMT Simultaneous Multithreading

SoC System-on-a-Chip

SVM Support Vector Machine

TLB Translation Lookaside Buffer

TLP Thread-level Parallelism

# LIST OF FIGURES

| Figure 2.1 Example of the Roofline model for an Intel Xeon (Clovertown) multi-         |      |

|----------------------------------------------------------------------------------------|------|

| core architecture                                                                      | 32   |

| Figure 2.2 Architeture of Viking multicore machine presented in Table 2.1              | 33   |

| Figure 3.1 Size of 7-point Jacobi stencil and its neighbor points.                     | 36   |

| Figure 3.2 Size of seismic stencil to calculate velocity and stress components         | 39   |

| Figure 3.3 Size of acoustic wave propagation stencil and its neighbor points           | 40   |

| Figure 3.4 Representation of solution by thread, for naive and space tiling algorithms | s.42 |

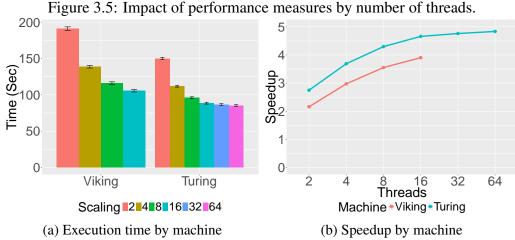

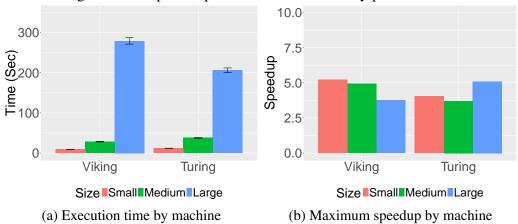

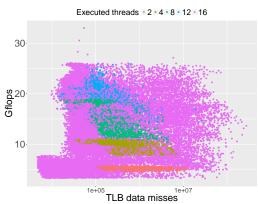

| Figure 3.5 Impact of performance measures by number of threads                         | 44   |

| Figure 3.6 Impact of performance measures by problem size.                             | 45   |

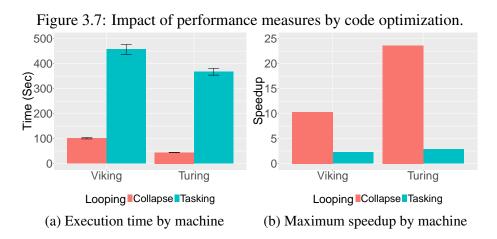

| Figure 3.7 Impact of performance measures by code optimization                         |      |

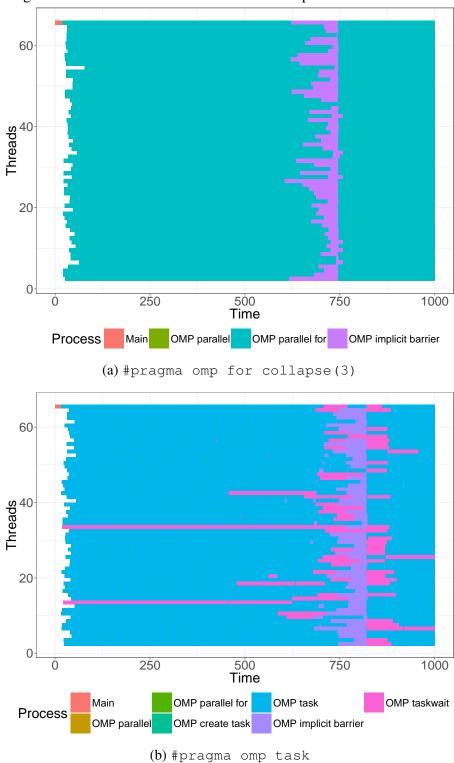

| Figure 3.8 Traces of one-time iteration for 7-point stencil execution                  | 46   |

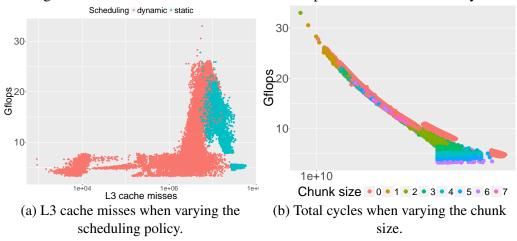

| Figure 3.9 Impact of performance measures by scheduling policy                         | 48   |

| Figure 3.10 Impact of performance measures by scheduling and chunk size on Tur-        | 40   |

| ing machine.                                                                           |      |

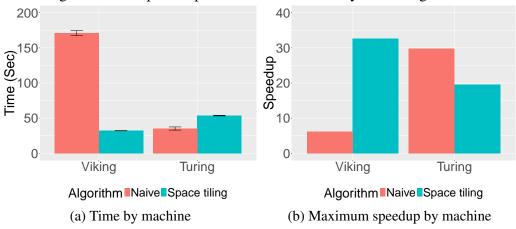

| Figure 3.11 Impact of performance measures by stencil algorithm                        |      |

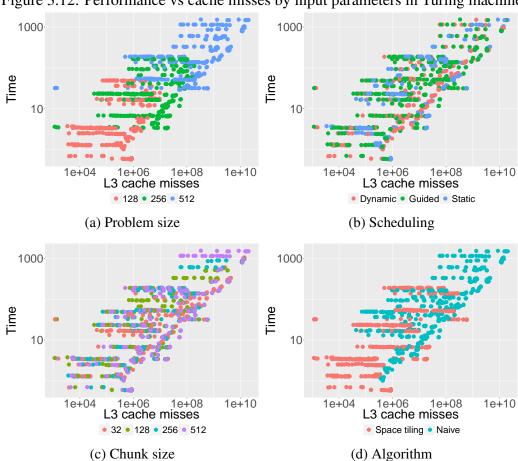

| Figure 3.12 Performance vs cache misses by input parameters in Turing machine          |      |

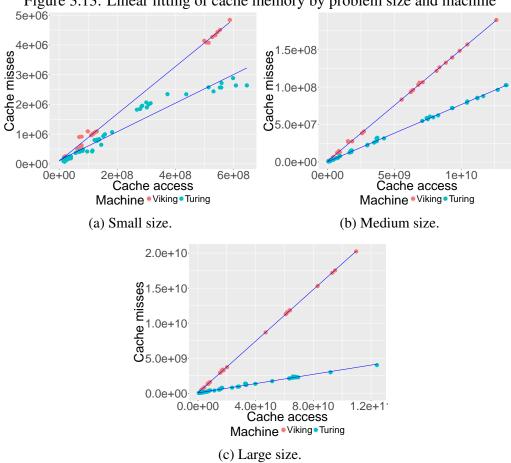

| Figure 3.13 Linear fitting of cache memory by problem size and machine                 |      |

| Figure 3.14 Exponential fitting for problem size                                       | 52   |

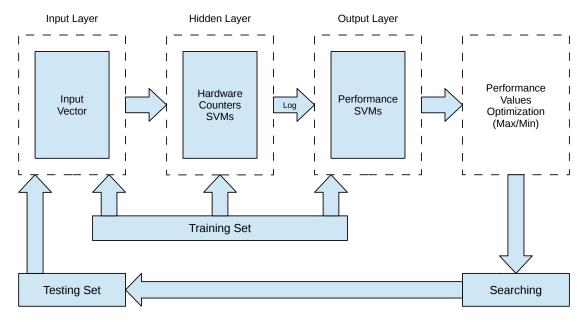

| Figure 4.1 Flowchart of General Model for Performance Prediction of Geophysics         |      |

| Stencils based on Machine Learning (Golem)                                             | 56   |

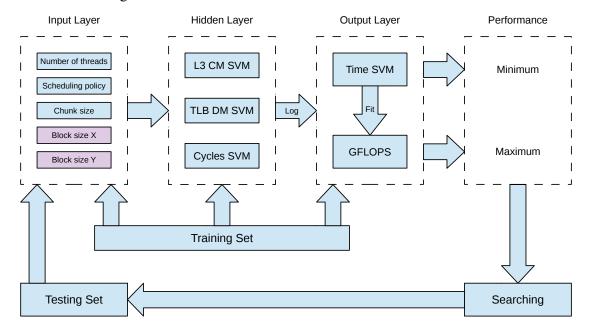

| Figure 4.2 Flowchart of Golem on multicore architectures.                              | 58   |

| Figure 4.3 Hardware counter behavior of 7-point Jacobi on Node Cryo                    | 61   |

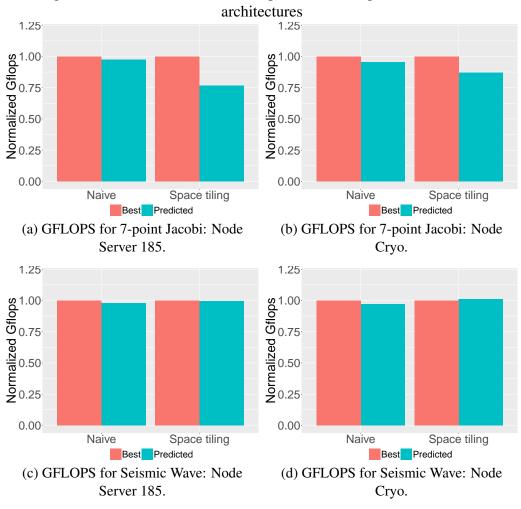

| Figure 4.4 Normalized performance comparison between predicted results from            |      |

| the ML-algorithm and results from the best performance experimens on mul-              |      |

| ticore architectures                                                                   | 64   |

| Figure 4.5 Flowchart of Golem on manycore architectures                                | 65   |

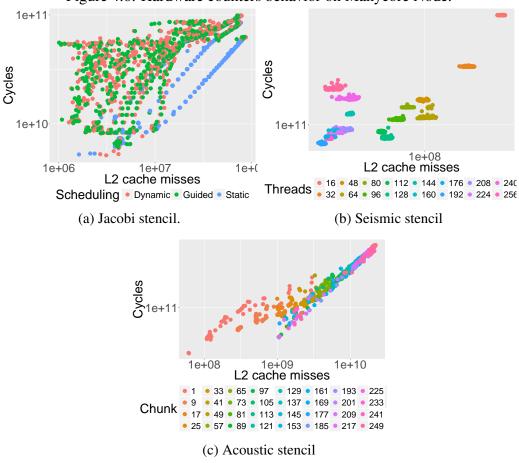

| Figure 4.6 Hardware counters behavior on Manycore Node.                                | 68   |

| Figure 4.7 Normalized performance comparison between predicted results from            |      |

| the ML-algorithm and results from the best performance experimens on many-             |      |

| core architectures.                                                                    | 70   |

| Figure 5.1 Block diagram of a NVIDIA GPU SM.                                           | 74   |

| Figure 5.2 Representation of a grid with the thread blocks.                            |      |

| Figure 5.3 Representation of memory hierarchy for threads, blocks and grids            |      |

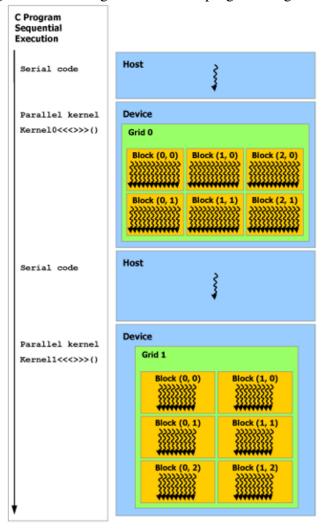

| Figure 5.4 Heterogeneous CUDA programming model.                                       |      |

| Figure 5.5 Architecture of the Fermi SM.                                               |      |

| Figure 5.6 Architecture of the Kepler SM.                                              |      |

| Figure 5.7 Architecture of the Maxwell SM                                              |      |

| Figure 5.8 Architecture of the Pascal SM.                                              |      |

| Figure 5.9 Architecture of Tegra machine presented in Table 5.1.                       |      |

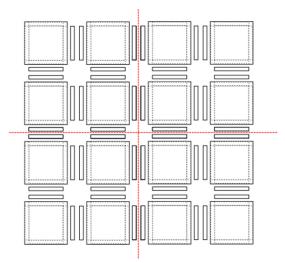

| Figure 6.1 Tiling division of 3D data domain, each slice is computed by the GPU        | 87   |

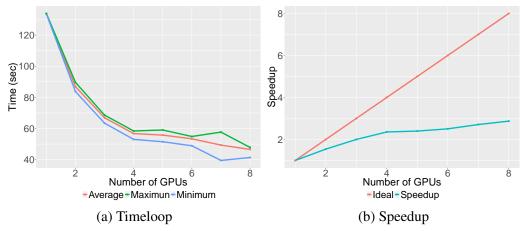

| Figure 6.2 Timeloop and speedup measures of Ondes 3D application when increas-         |      |

| ing the number of GPUs.                                                                | 88   |

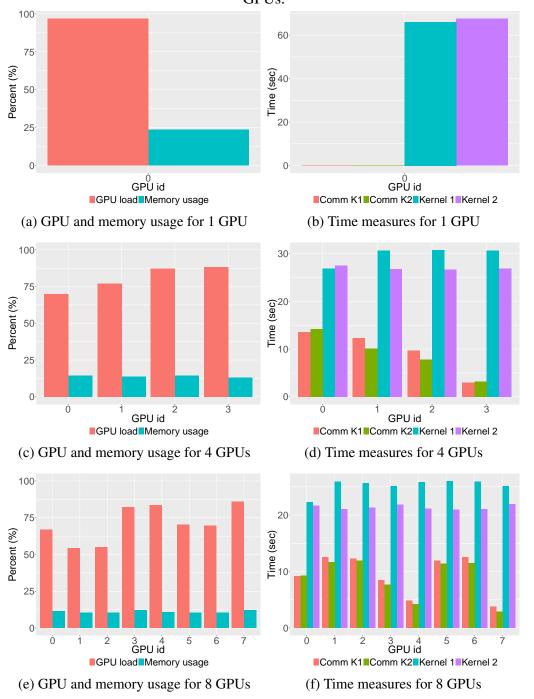

| Figure 6.3 Kernel execution and communication time of Ondes 3D application             |      |

| when increasing the number of GPUs.                                                    | 89   |

| Figure 6.4 Measures (time, load and memory consumption) of Ondes 3D on a clus-      |     |

|-------------------------------------------------------------------------------------|-----|

| ter of GPUs.                                                                        | 90  |

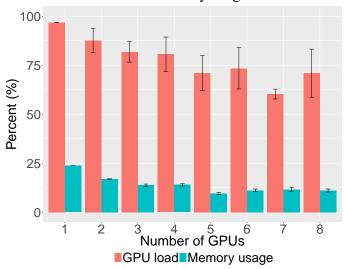

| Figure 6.5 Statistical estimators (average and standard deviation) of Ondes 3D for  |     |

| GPU load and memory usage.                                                          | 91  |

| Figure 7.1 Grid of blocks including inner grid-points corresponding to the physical |     |

| domain and outer ghosts zones                                                       | 96  |

| Figure 7.2 Tasks dependency on a grid of 3×3 blocks                                 | 97  |

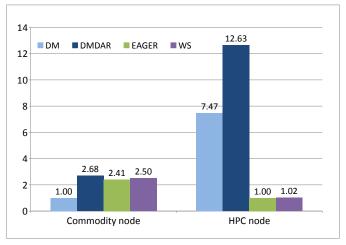

| Figure 7.3 Impact of the scheduling algorithms for experiments on heterogeneous     |     |

| platforms. Relative speedup over the worst situation on each platform               | 99  |

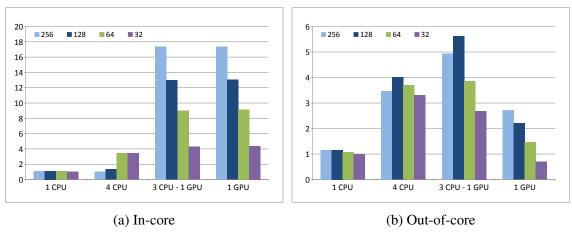

| Figure 7.4 Impact of the granularity on the efficiency of seismic wave modeling on  |     |

| GPUs+CPUs.                                                                          | 100 |

| Figure 7.5 Speedup on the HPC node (in-core dataset) over multicore execution       | 102 |

| Figure 7.6 Speedup for out-of-core dataset when running on the HPC node over        |     |

| multicore execution.                                                                | 103 |

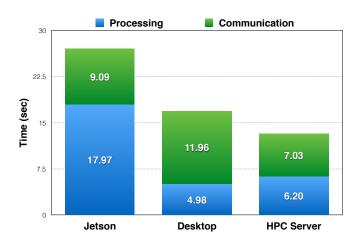

| Figure 7.7 Comparison of Time-to-solution metrics for Tegra K1 (Jetson), Guane-     |     |

| 1 (HPC server) and BRGM node (Desktop platform).                                    | 105 |

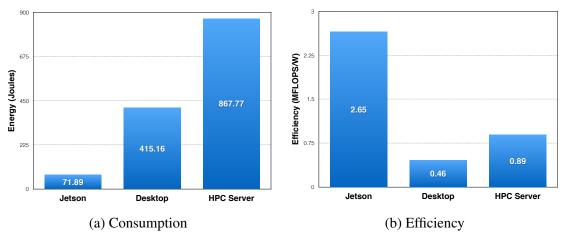

| Figure 7.8 Energy measures for the earthquake modeling on three heterogeneous       |     |

| architectures.                                                                      | 106 |

|                                                                                     |     |

# LIST OF TABLES

| Table 2.1 Configurations of multicore machines.                                      | 33   |

|--------------------------------------------------------------------------------------|------|

| Table 3.1 Measures for the parameters of input vector.                               | 43   |

| Table 3.2 Correlation coefficient of cache access vs cache misses                    | 51   |

| Table 3.3 RMSE, SD and R-SQUARE of cache fitting                                     | 52   |

| Table 3.4 RMSE, SD and R-SQUARE of exponential fitting                               | 53   |

| Table 4.1 Parameters of input vector for each algorithm.                             | 58   |

| Table 4.2 Optimizations set for multicore architectures                              | 59   |

| Table 4.3 <i>p-value</i> of one-way ANOVA for the GFLOPS variable in the naive algo- |      |

| rithm experiments.                                                                   | 60   |

| Table 4.4 <i>p-value</i> of two-way ANOVA for the seismic wave kernel                | 60   |

| Table 4.5 p-value of one-way and two-way ANOVA for the GFLOPS variable in            |      |

| Space tiling algorithm experiments.                                                  | 61   |

| Table 4.6 Total number of experiments.                                               | 62   |

| Table 4.7 RMSE and R-square for predicted values of the 7-point Jacobi and the       |      |

| Seismic Wave kernels.                                                                | 63   |

| Table 4.8 Available configurations for optimization procedure                        | 66   |

| Table 4.9 <i>p-value</i> of one-way ANOVA for the manycore architecture              | 66   |

| Table 4.10 <i>p-value</i> of two-way ANOVA for the seismic wave kernel               | 67   |

| Table 4.11 Number of experiments                                                     | 69   |

| Table 4.12 Statistical estimators of our prediction model                            | 69   |

| Table 5.1 Heterogeneous architecture configurations.                                 | 84   |

| Table 7.1 Memory consumption, number of blocks and number of parallel task for       |      |

| the simulated scenarios                                                              |      |

| Table 7.2 Speedup on the commodity-based hardware configuration (in-core dataset)    |      |

| over multicore execution                                                             | .101 |

| Table 7.3 Speedup on the commodity-based configuration (out-of-core dataset) over    |      |

| multicore execution                                                                  | .102 |

| Table 7.4 List of runtime parameters that affect the performance of task-based im-   |      |

| plementation on heterogeneous architectures                                          | .104 |

# **CONTENTS**

| 1 INTRODUCTION                                          | 14 |

|---------------------------------------------------------|----|

| 1.1 Research issues                                     | 15 |

| 1.1.1 Exploiting multicore architectures                | 15 |

| 1.1.2 Machine Learning approaches on HPC platforms      | 16 |

| 1.1.3 Heterogeneous architectures                       | 16 |

| 1.1.4 Research context                                  | 17 |

| 1.2 Objectives and contributions                        | 18 |

| 1.3 Outline                                             |    |

| 2 MULTICORE ARCHITECTURES AND PROGRAMMING MODELS        | 24 |

| 2.1 Parallelism                                         | 24 |

| 2.2 Multicore architectures                             | 25 |

| 2.2.1 Manycore architectures                            |    |

| 2.3 Programming models on HPC architectures             | 26 |

| 2.3.1 Message Passing Interface                         |    |

| 2.3.2 Shared-Memory programming                         | 27 |

| 2.3.3 Impact of compilers                               | 29 |

| 2.4 Performance evaluation                              | 31 |

| 2.4.1 Hardware performance counters                     | 31 |

| 2.4.2 Roofline model                                    |    |

| 2.5 Target machines                                     | 33 |

| 2.6 Concluding remarks                                  | 34 |

| 3 NUMERICAL BACKGROUND: GEOPHYSICAL KERNELS ON MULTI-   |    |

| CORE PLATFORMS                                          | 35 |

| 3.1 Stencil applications                                |    |

| 3.1.1 7-point Jacobi stencil                            | 36 |

| 3.1.2 Seismic wave propagation stencil                  |    |

| 3.1.3 Acoustic wave propagation stencil                 | 40 |

| 3.2 Standard implementations of numerical stencil       |    |

| 3.2.1 Naïve                                             |    |

| 3.2.2 Space Tiling                                      | 41 |

| 3.3 Performance charaterization of numerical stencils   | 42 |

| 3.3.1 Scalability                                       | 44 |

| 3.4 Concluding remarks                                  | 53 |

| 4 MACHINE LEARNING STRATEGY FOR PERFORMANCE IMPROVE-    |    |

| MENT ON MULTICORE ARCHITECTURES                         | 54 |

| 4.1 Performance improvement by Machine Learning models  | 54 |

| 4.2 General model for performance prediction            |    |

| 4.2.1 Architecture of geophysics prediction model       |    |

| 4.2.2 Performance prediction on multicore architectures |    |

| 4.2.3 Performance prediction on manycore architectures  |    |

| 4.3 Concluding remarks                                  |    |

| 5 HETEROGENEOUS ARCHITECTURES AND PROGRAMMING MODEL     |    |

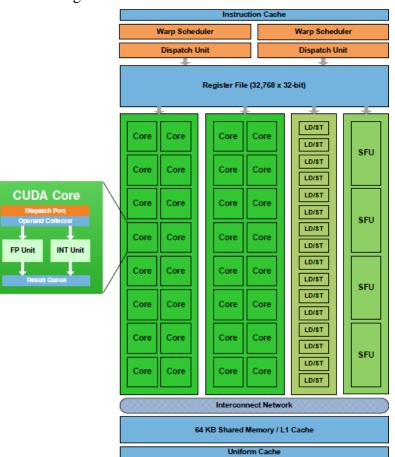

| 5.1 Streaming Multiprocessors                           |    |

| 5.2 Programming models on heterogeneous architectures   |    |

| 5.2.1 OpenCL programming model                          |    |

| 5.3 Evolution of NVIDIA GPU Architectures               |    |

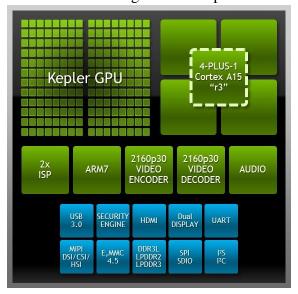

| 5.4 Assymetric low power architectures                  |    |

| 5.5 Target machines                                     |    |

| 5.6 Concluding remarks                                                        | 84   |

|-------------------------------------------------------------------------------|------|

| 6 NUMERICAL IMPLEMENTATION OF GEOPHYSICS STENCILS ON                          |      |

| HETEROGENEOUS PLATFORMS                                                       | 86   |

| 6.1 Setup and Performance Measurement                                         | 87   |

| 6.2 Elapsed Time                                                              | 88   |

| 6.3 GPU Load and Memory Usage                                                 | 91   |

| 6.4 Concluding Remarks                                                        |      |

| 7 TASK-BASED APPROACH FOR PERFORMANCE IMPROVEMENT ON                          |      |

| HETEROGENEOUS PLATFORMS                                                       | 93   |

| 7.1 Runtime systems for task-based programming                                | 93   |

| 7.2 StarPU runtime system                                                     |      |

| 7.3 Elastodynamics over runtime system                                        |      |

| 7.4 Experiments                                                               |      |

| 7.4.1 Scheduling strategies                                                   |      |

| 7.4.2 Size of the block                                                       |      |

| 7.4.3 In-core dataset                                                         | .100 |

| 7.4.4 Out-of-core dataset                                                     | .101 |

| 7.5 Summary of runtime parameters                                             | .103 |

| 7.6 Task-based implementation for energy efficiency                           | .104 |

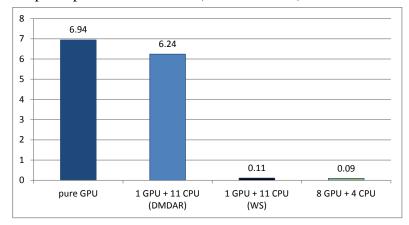

| 7.6.1 Computing time                                                          |      |

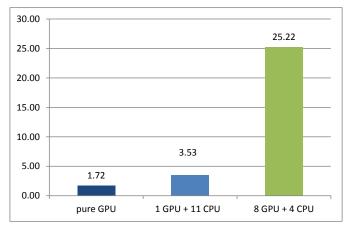

| 7.6.2 Energy efficiency                                                       |      |

| 7.7 Concluding remarks                                                        | .107 |

| 8 RELATED WORK                                                                |      |

| 8.1 Perfomance improvement of stencil applications on multicore architectures | .109 |

| 8.2 Advanced optimizations, low-level and auto-tuning strategies              |      |

| 8.3 Machine Learning approaches                                               |      |

| 8.4 Heterogeneous computing                                                   |      |

| 9 CONCLUSION AND PERSPECTIVES                                                 |      |

| 9.1 Contributions                                                             | .117 |

| 9.2 Future Work                                                               | .118 |

| REFERENCES                                                                    | .120 |

#### 1 INTRODUCTION

The behavior of scientific applications related to High Performance Computing (HPC) depends on many factors (non-uniform memory access, vectorization, compiler optimizations, memory policies, scheduling algorithms, etc.) that may severely influence the performance. At the hardware level, the complexity of available computing nodes is increasing, this includes several levels of hierarchical memories and more heterogeneous cores. At the software level, there are currently several programming models to exploit the architecture (shared memory, message passing, parallel tasks, etc.). These evolutions lead to redesign the code of scientific applications to obtain the best performance for a specific architecture with a specific programming model (BUCHTY et al., 2012; MITTAL; VETTER, 2015).

Examples of HPC applications are the stencil-based applications (a nearest-neighbor pattern replicated in a data domain), which are used to solve many problems related to Partial Differential Equations (PDE), the heart of many problems in areas as diverse as electromagnetics, fluid dynamics or geophysics. This is particularly true in the case of three-dimensional waves propagation in complex media, it is still one of the main challenges in geophysics and the Finite-Difference Method (FDM) is a standard technique implemented to solve these equations (MOCZO; ROBERTSSON; EISNER, 2007; DATTA et al., 2008; NGUYEN et al., 2010).

Additionally, this class of modeling heavily relies on parallel architectures in order to tackle large scale geometries including a detailed description of the physics. Last decade, significant efforts have been devoted towards efficient implementation of the FDM on emerging architectures. These contributions have demonstrated their efficiency leading to robust scientific applications (DATTA et al., 2009; MICHÉA; KOMATITSCH, 2010).

Although a large literature on the optimization of stencil numerical kernels is available, predicting and optimizing its performance remains a challenge, because many input parameters are involved and affect the performance. In terms of computational efficiency, one of the main difficulties is to deal with the disadvantageous ratio between the limited pointwise computation and the intensive memory access required, leading to a memory-bound situation (DUPROS et al., 2008; DUPROS; DO; AOCHI, 2013).

#### 1.1 Research issues

This thesis focuses on the performance optimization of stencil applications on HPC architectures. We consider classical geophysics numerical stencils that lie at the heart of earthquake modeling, and 3D underground imaging for the oil and gas industry.

# 1.1.1 Exploiting multicore architectures

In addition to the challenge of geophysical modeling and the mathematical problems behind seismic and acoustic wave propagation modeling, one major challenge is to leverage the various levels of parallelism involved. HPC is actually facing key challenges on both the hardware and the software sides. Machines are reaching several millions of cores and the scalability of the applications could become a bottleneck. As reported in several recent research papers (ROTEN et al., 2016; TSUBOI et al., 2016; BREUER; HEINECKE; BADER, 2016), various geophysical applications show the variability of scaling up to thousands of cores. Indeed, regardless of the numerical method involved (Finite-Difference, Finite-Elements or Spectral-Elements), such applications benefit from the limited amount of point-to-point communications between neighboring subdomains.

Traditional methods to improve the performance of computing architectures were to increase the clock frequency, add high-speed, on-chip cache, and to optimize instructions. Nowadays, companies have turned to offer parallel machines, these architectures include several processing units on smaller chips to provide several executions of instructions in the same cycle (BLAKE; DRESLINSKI; MUDGE, 2009). Numerical implementations are focused on automatic parallelization of stencil codes (SPAZIER; CHRIST-GAU; SCHNOR, 2016), analysis of the stencil performance on shared memory systems by compiler optimizations (ZHU et al., 2015), and to apply computational optimizations that scale the performance over cores and vector units (GAN et al., 2014). At the shared-memory level, efficient exploitation of the growing number of computing cores available remains a challenge.

#### 1.1.2 Machine Learning approaches on HPC platforms

Application tuning represents one methodology to improve the performance on HPC architectures. In this case, several parameters such as machine architecture, domain decomposition, compiler flags, scheduling or load balancing algorithms are considered to achieve the best performance. Unfortunately, this approach lead to the exploration of a huge set of parameters, thus limiting its interest in complex platforms. Finding the optimal value for each parameter requires to search on a large configuration set, and several heuristics or frameworks have been proposed to speed up the process of finding the best configuration in various contexts (DATTA et al., 2010; CHRISTEN; SCHENK; BURKHART, 2011; TANG et al., 2011; MIJAKOVIC; FIRBACH; GERNDT, 2016).

At this point, Machine Learning (ML) is a methodology for optimization that could be applied to find patterns on a large set of input parameters. Recently, ML algorithms have been used on HPC systems under different situations and for various workloads such as threads mapping and memory accesses (CASTRO; GÓES; MÉHAUT, 2014), I/O scheduling (BOITO et al., 2016; LI et al., 2017), or performance improvement (GANAPATHI, 2009). Building a suitable ML-based performance model for geophysics numerical kernels remains a challenge, because the accuracy of current models don't achieve the target behavior. In this sense, a model may allow us to predict, to simulate and to optimize the performance behavior on HPC architectures with a limited amount of experiments.

#### 1.1.3 Heterogeneous architectures

The importance of Heterogeneous Computing (HC) comes from the fact that a large fraction of main Top500 and Green500 lists of supercomputers use processors with both CPUs and coprocessors (TOP500, 2017; GREEN500, 2017). The different architectures and programming models on heterogeneous architectures also present several challenges in achieving optimal performance. HC approaches have also been referred to as collaborative, hybrid, co-operative or synergistic execution, co-processing, divide and conquer approach and others (MITTAL; VETTER, 2015). In this work, we consider heterogeneous architectures where they are built with CPUs, as main processors, and accelerated by GPU devices. Early graphics processors were special-purpose accelerators suitable only for applications related to graphics, image processing, and video

coding. Current GPUs are general-purpose (also known as GPGPU) and programmable, massively parallel processors (LINDHOLM et al., 2008).

In this sense, an approach called task-based parallelism is a data-oriented programming model used at high-level on heterogeneous architectures, the main idea is to build a task dependence graph, to create a queue of tasks with data directionality and to schedule the tasks into all available processors. Task parallelism allows the creation of multiple threads of control (processes or tasks) that can synchronize and communicate in arbitrary ways (HASSEN; BAL; JACOBS, 1998). Several runtime systems have been designed for programming and running applications on heterogeneous platforms, frameworks such as *StarPU* (AUGONNET et al., 2011), *G-Charm* (VASUDEVAN; VADHIYAR; KALÉ, 2013) or *PaRSEC* (BOSILCA et al., 2013a) have a growing impact in the scientific community. Nevertheless, the performance gains expected from the use of such runtime systems come at a price. The challenge is to decouple as much as possible the algorithms and the knowledge of the underlying architecture (STOJANOVIC et al., 2012), this situation is rather challenging for heterogeneous platforms and one of the main problems is to deal with the costly memory transfers (KRAKIWSKY; TURNER; OKONIEWSKI, 2004).

#### 1.1.4 Research context

This research is conducted in the context of joint collaborations between the *Institute of Informatics of the Federal University of Rio Grande do Sul (INF-UFRGS)* and the *French Geological Survey (BRGM), Carnot Institute*, under the *High Performance Computing for Geophysics Applications project (HPC-GA)* funded by the *FP7-PEOPLE*, grant agreement number 295217. Research has also received funding from the *EU H2020 Programme* and from *MCTI/RNP-Brazil* under the *High Performance Computing for Energy Project (HPC4E)*, grant agreement 689772, and the *Iberian-American Network for High Performance Computing (RICAP)*, partially funded by the *Ibero-American Program of Science and Technology for Development (CYTED)*, Ref. 517RT0529. This research was also accomplished in the context of the *International Laboratory in High Performance and Ambient Informatics (LICIA)*.

At UFRGS, the research has been developed in the *Parallel and Distributed Processing Group (GPPD)*. This work has been granted by *Coordination for the Improvement of Higher Education Personnel (CAPES)*, *National Council for Scientific and Technological Development (CNPq)*, *Fundação de Amparo à Pesquisa do Estado do Rio Grande do*

Sul (FAPERGS), and Petrobras company.

It was also supported by *Intel Corporation* under the *Modern Code Project*. For computer time, this research partly used the resources of *Colfax Research Cluster*. Some experiments presented in this thesis were carried out using the *GridUIS-2* experimental testbed, being developed under the *Universidad Industrial de Santander High Performance and Scientific Computing Centre* (SC3UIS), development action with support from *Vicerrectoría de Investigación y Extensión (VIE-UIS)* and several UIS research groups as well as other funding bodies (<a href="http://www.sc3.uis.edu.co">http://www.sc3.uis.edu.co</a>).

#### 1.2 Objectives and contributions

The main objective of this research is to increase the performance of stencil computations from geophysics models. Many work has been guided in two alternatives: improvement of architectural features or improvement of algorithms and implementations in specific programming models; the first alternative is out of the scope of this research and second alternative limits the performance for each implementation on the underlying architecture. Thus, we research into a third alternative that has been recently used: how to tune the application by finding an optimal input set from a configuration set of runtime parameters. Then, our hypothesis is: **finding the optimal parameters from a input configuration set improve the performance of stencil applications**. Considering our objective and hypothesis, the steps are:

- To define which parameters from a configuration set, at runtime level, affect the performance of stencil computations;

- On multicore architectures, to optimize the performance of stencil computations by finding the optimal input configuration set based on an ML approach; and

- On heterogeneous architectures, to exploit the computing power by searching for an optimal runtime configuration set that uses all available processing units.

First, and according to our objectives, we contribute to the analysis and characterization of stencil computations performance on both multicore and heterogeneous architectures, they are composed by CPUs and Graphics Processing Units (GPU). On heterogeneous architectures, several high-level parameters such as data size, memory capability,

scheduling algorithms and the number of processing units have been considered. This contribution was part of *HPC-GA project*, the preliminary results were published in:

Víctor Martínez, David Michéa, Olivier Aumage, Fabrice Dupros, and Philippe Navaux. "Hybrid CPU-GPU Computing for a Finite-Difference Numerical Seismic Kernel: First Results with StarPU". In: *High Performance Computing for Geophysics Applications, Workshop (HPC-GA)*. Oral presentation. October, 2014. Grenoble, France.

On multicore architectures, we studied the influence of several input and runtime configurations with respect to classical algorithm implementations. This contribution was part of *HPC4E project*, the results have been presented in the Latin American High Performance Computing Conference (CARLA 2016) and in the Workshop de Processamento Paralelo e Distribuído (WSPPD 2016):

- Víctor Martinez, Philippe Navaux, Fabrice Dupros, Hideo Aochi, and Márcio Castro. "Stencil-based applications tuning for multi-core architectures". In: *Latin American High Performance Computing Conference (CARLA 2016)*. Oral presentation. August, 2016. Ciudad de México, México. Available in: <a href="https://hpc4e.eu/sites/default/files/files/presentations/Paper\_Victor.pdf">https://hpc4e.eu/sites/default/files/files/presentations/Paper\_Victor.pdf</a>.

- Víctor Martinez, Philippe Navaux, Fabrice Dupros, Hideo Aochi, and Márcio Castro. "Tuning space optimization for stencil-based applications on multi-core". In: *XIV Workshop de Processamento Paralelo e Distribuído (WSPPD)*. Oral presentation. September, 2016. Porto Alegre, Brazil. Available in: <a href="http://www.inf.ufrgs.br/gppd/wsppd/2016/">http://www.inf.ufrgs.br/gppd/wsppd/2016/</a>.

Second, we introduce a Machine Learning (ML) model to predict and to optimize the performance of stencil computations on multicore architectures. The key idea is to provide adaptability of the input parameters, a training execution set is used in a learning process until the model is available to reach the best performance. The final model could be integrated into auto-tuning frameworks to find the best configuration for a given stencil application. This contribution was part of *HPC4E project*, the *Modern Code Project* and the *Petrobras 2016/00133-9 project*, the results are available in the proceedings of International Conference on Computational Science (ICCS 2017) published in *Procedia Computer Science*, proceedings of the Latin American High Performance Computing Conference (CARLA 2017) published in *Communications in Computer and*

*Information Science*, proceedings of 18° Escola Regional de Alto Desempenho do Estado do Rio Grande do Sul (ERAD/RS), and has been published at HPC4E: High Performance Computing for Energy Workshop along with The Eighth International Conference on Smart Grids, Green Communications and IT Energy-aware Technologies (ENERGY 2018):

- Víctor Martínez, Fabrice Dupros, Márcio Castro and Philippe Navaux. "Performance Improvement of Stencil Computations for Multi-core Architectures based on Machine Learning". In: *International Conference on Computational Science (ICCS)* Zürich, Switzerland: Procedia Computer Science, 2017, V. 108, pp. 305–314. DOI:10.1016/j.procs.2017.05.164. Available in: <a href="https://www.sciencedirect.com/science/article/pii/S1877050917307408">https://www.sciencedirect.com/science/article/pii/S1877050917307408</a>>. Qualis: A1.

- Víctor Martínez, Matheus Serpa, Fabrice Dupros, Edson L. Padoin, and Philippe Navaux. "Performance Prediction of Acoustic Wave Numerical Kernel on Intel Xeon Phi Processor". In: *In: Mocskos E., Nesmachnow S. (eds) High Performance Computing. (CARLA 2017). Communications in Computer and Information Science*, vol 796, pp. 101–110. Springer, Cham. Buenos Aires, Argentine. DOI:10.1007/978-3-319-73353-1\_7. Available in: <a href="https://link.springer.com/chapter/10.1007/978-3-319-73353-1\_7">https://link.springer.com/chapter/10.1007/978-3-319-73353-1\_7</a>. Qualis: B4.

- Víctor Martínez, and Philippe Navaux. "Performance Prediction of Stencil Applications on Accelerator Architectures". In: 18° Escola Regional de Alto Desempenho do Estado do Rio Grande do Sul (ERAD/RS), 2018. Available in: <a href="http://www.inf.ufrgs.br/erad2018/anais/FPG/179903.pdf">http://www.inf.ufrgs.br/erad2018/anais/FPG/179903.pdf</a>>.

- Víctor Martínez, Matheus Serpa, Philippe Navaux, Edson L. Padoin, and Jairo Panetta. "Performance Prediction of Geophysics Numerical Kernels on Accelerator Architectures". Contribution presented at HPC4E: High Performance Computing for Energy Workshop along with The Eighth International Conference on Smart Grids, Green Communications and IT Energy-aware Technologies (ENERGY 2018). Qualis: B5.

Finally, the third contribution of this work is the introduction of a task-based implementation of the elastodynamics equation for heterogeneous architectures. This contribution on heterogeneous architectures use the maximum number of available processing units and have been demonstrated a better performance than standard implementations.

This contribution was part of *HPC-GA project*, the results were published in the proceedings of 27<sup>th</sup> International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD 2015):

Víctor Martínez, David Michéa, Fabrice Dupros, Olivier Aumage, Samuel Thibault, Hideo Aochi, and Philippe Navaux. "Towards Seismic Wave Modeling on Heterogeneous Many-Core Architectures Using Task-Based Runtime System". In: 27th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD 2015). Florianópolis, Brazil: IEEE Computer Society, 2015, pp. 1–8. DOI: 10.1109/SBAC-PAD.2015.33. Available in: <a href="https://ieeexplore.ieee.org/document/7379827/">https://ieeexplore.ieee.org/document/7379827/</a>. Qualis: B1.

This contribution for heterogeneous architectures has been extended to the analysis of the energy consumption. A low-power many-core heterogeneous architecture was used as an alternative to solve the seismic model with a better energy efficiency. Our solution makes a better usage of the available resources (CPU and GPU cores) with a significant reduction of the energy consumption and communication cost. This contribution was a joined work with *SC3UIS*, the results were presented in the Latin American High Performance Computing Conference (CARLA 2015) and in the Workshop de Processamento Paralelo e Distribuído (WSPPD 2015):

- Víctor Martínez, John García, Carlos Barrios, Fabrice Dupros, Hideo Aochi, and Philippe Navaux. "Task-based Programming on Low-power Nvidia Jetson TK1 Manycore Architecture: Application to Earthquake Modelling". In: *Latin American High Performance Computing Conference (CARLA 2015)*. Oral presentation. August, 2015. Petrópolis, Brazil.

- John García, Víctor Martínez, Philippe Navaux, and Carlos Barrios. eGPU for Monitoring Performance and Power Consumption on Multi-GPUs. In: XIII Workshop de Processamento Paralelo e Distribuído (WSPPD). Oral presentation. August, 2015. Porto Alegre, Brazil. Available in: <a href="http://inf.ufrgs.br/gppd/wsppd/">http://inf.ufrgs.br/gppd/wsppd/</a> 2015/papers/footer/WSPPD\_2015\_paper\_13.pdf>

## 1.3 Outline

We divided this document into two parts. The First Part focuses on performance improvement of stencil applications on multicore architectures, and is organized as fol-

#### lows:

- Chapter 2 reviews the fundamental concepts involved in this work. We present the architectural features of multicore systems and the common parallel programming models;

- Chapter 3 describes the numerical background for the geophysics numerical kernels, and we characterize the performance of classical implementations on multicore architectures;

- Chapter 4 focuses on the use of ML to predict and to optimize the performance of geophysics numerical kernels on multicore and many-core architectures.

The Second Part is focused on performance improvement of a geophysics numerical stencil on heterogeneous architectures, and corresponds with following chapters:

- Chapter 5 reviews the basic features of heterogeneous architectures and common programming models;

- Chapter 6 presents the standard implementation of a seismic wave propagation stencil on heterogeneous architectures;

- Chapter 7 details the task-based implementation and compare the performance obtained with the classical CPU or GPU only versions.

Finally, we present the related works and the conclusion of this research in following chapters:

- Chapter 8 presents the related works;

- Chapter 9 concludes this document, and presents the perspectives.

#### 2 MULTICORE ARCHITECTURES AND PROGRAMMING MODELS

We start the first part of this document with this chapter. We present a background of the HPC platforms and the programming models. Traditional methods to improve the performance of computing architectures were to increase the clock frequency, add high-speed, on-chip cache. These methods worked until physical issues limited the processor manufacturing. Nowadays, companies have turned to offer parallel machines, these architectures includes on processors several processing units to provide multiple executions of instructions in the same cycle. The performance improvement is achieved by replicating the processing units, adding additional processing instructions, improving communication between the cores, and the calculations are solved simultaneously, in parallel. In this context, Moore's law (BLAKE; DRESLINSKI; MUDGE, 2009) has also driven a constant increase in parallelism and performance.

#### 2.1 Parallelism

Parallelism is considered for several levels, in (BUCHTY et al., 2012) the authors present six levels: (1) *Instruction Level Parallelism* (ILP) provides techniques to parallel processing at runtime, (2) *Data Parallelism* (DP) exploited mainly by Single Instruction Multiple Data (SIMD) processing, (3) *Hardware-Supported Multithreading* performs a thread level parallelism (TLP) with simultaneous multithreading (SMT) or HyperThreading (HT), when the inactive resources could be used to execute instructions from another thread, (4) *Core-Level Parallelism* builds a homogeneous multicore processor with strong coupling of cores, (5) *Socket-Level Parallelism* uses various processing devices (CPUs, GPUs, FPGAs, etc.), and finally (6) *Node Level Parallelism* is provided with a set of nodes connected by specific network topologies.

Performance optimization of parallel architectures is mainly related to adding more and more processing units, and applications need to be adapted to a wide range of platforms. Most common parallel architectures are the general-purpose multicore employing a low number of heavy-weight and highly complex cores, and multilevel cache hierarchies (i.e., private L1 and L2 caches and a shared L3 cache), as the memory access time depends on the memory location relative to the processor, each core is addressed to access its own private local memory, these architectures evolved to Non-Uniform Memory Access (NUMA) machines.

#### 2.2 Multicore architectures

Architectural features on parallel architectures can be improved in two ways: First, multiple pipelines can be added to fetch and issue more instructions in parallel, creating a superscalar processing element; second, by increasing the number of stages, thus reducing the logic per stage. These improvements are successful for in-order processing elements. On the other hand, out-of-order architecture gains as much single thread performance as possible by dynamic scheduling to keep the pipelines full. This kind of optimization is implemented on multicore machines.

Multicore architectures can be classified according to their attributes: the application domain, the power/performance ratio, the class of processing elements, the memory system, and accelerators/integrated peripherals (SHUKLA; MURTHY; CHANDE, 2015). The application domain has two classes of processing: data processing dominated and control dominated; digital signal processors (DSPs) are the example for data processing-dominated applications and control-dominated applications include devices for file compression, decompression, and network processing. Power/Performance relation is also an important goal for multicore processors, power consumption has become a concern for computers.

At the architectural level, the memory system was a rather simple component, consisting of a few levels to feed the single processor with a data and instructions private cache. In multicores, the caches are just one part of the memory system, the other components include the consistency model, cache coherence support, and the intrachip interconnect. A consistency model defines how the memory operations may be reordered when the code is executing.

Caches have increased importance in multicore processors. They give a fast local memory to work with processing elements. The amount of cache required depends on the application. Bigger caches are better for performance but show diminishing returns as caches sizes grow. The number of cache levels has been increasing as processing elements get faster and become more numerous. The L1 cache is accessed on every instruction cycle as part of the instruction pipeline and is broken into separate instruction and data caches, and it is usually rather small, fast, and private to each processing element. The L2 cache can be private for each core or shared between cores. L3 is a shared cache for all processing elements and reduced delays in multi-threaded environments.

## 2.2.1 Manycore architectures

In this work, we consider the Xeon Phi processor as a special case of multicore architectures. The Knights Landing (KNL) is the code name for the second-generation Intel Xeon Phi family. It is a many-core architecture that delivers massive thread parallelism, data parallelism, and memory bandwidth in a CPU form factor for high throughput workloads. It is a standard, standalone processor that can boot an off-the-shelf operating system.

The KNL brings two types of memory: multichannel DRAM (MCDRAM) and double data rate (DDR) memory. MCDRAM is a high bandwidth and low capacity (up to 16GB) memory comprising eight devices (2 GBytes each) integrated on-package and connected to the KNL die via a proprietary on-package I/O. All eight MCDRAM devices together provide an aggregate Stream triad benchmark bandwidth of more than 450 GBytes per second. KNL has six DDR4 channels running up to 2,400 MHz, with three channels on each of two memory controllers, providing an aggregate bandwidth of more than 90 GBps. Each channel can support at most one memory DIMM. The total DDR memory capacity supported is up to 384 GBytes.

KNL has three memory modes and can be configured as *Cache* mode to work as a third level cache; in *Flat* mode, both the MCDRAM memory and the DDR memory act as regular memory and are mapped into the same system address space as a distinct NUMA node (allocatable memory); and the *Hybrid* mode, the MCDRAM is partitioned such that either a half or a quarter of the MCDRAM is used as cache, and the rest is used as flat memory (SODANI et al., 2016).

#### 2.3 Programming models on HPC architectures

According to the evolution of HPC architectures, the programming models also have been developed to exploit the processing capability. They mainly involved the following aspects: how to send data in a network of processors and how to share and process data from the main memory between several cores. Parallel programming models are usually based on three fields: message passing, shared memory, and data-parallel. The first provides a high level of controlling architecture mapping and forces the programmer to detailed partitioning and orchestration. The second has standardized programming environments such as OpenMP for targeting compiler-exploitable TLP. The third, well-known

examples are the Compute Unified Device Architecture (CUDA) and the Open Computing Language (OpenCL), the first standard for kernel invocation on multiple heterogeneous systems (NVIDIA, 2016; INC., 2018). CUDA and heterogeneous architectures will be discussed in Chapter 5

# 2.3.1 Message Passing Interface

The Message Passing Interface (MPI) is the most common programming model for parallel machines with distributed memory and has been used widely in parallel and distributed computing systems. The basic content of MPI is point-to-point communication between processes and collective communications.

The point-to-point message-passing routines form the core of the MPI standard, the basic operations being *send* and *receive*. They allow messages to be sent between pairs of processes, with message selectivity based explicitly on message tag and source process, and implicitly on communication context. MPI defines a group as an ordered set of process identifiers, each of which is assigned a numerical rank, between zero and the size of the group. The identifier is used to send/receive data between processors.

Collective communications are provided where all processes in a group are involved in a collective operation. A collective function is called, in a group synchronization, when it is necessary; although this is not mandated and some implementations may not synchronize. These collective communications allow processing activities as broadcasting or data reducing. (CLARKE; GLENDINNING; HEMPEL, 1994)

# 2.3.2 Shared-Memory programming

In a shared-memory system, every processor has direct access to the memory of every other processor, meaning each one can load or store any shared address. The programmer also can declare data variables as privates to the processor. With shared-memory, the processes can exchange data more quickly than by MPI by using a designated area of memory. The data can be made directly accessible to all processes without having to use the communications (DAGUM; MENON, 1998).

Because of the ability to directly access memory throughout the system (with minimum latency and no explicit address mapping), combined with fast shared-memory locks,

OpenMP is used to implement the shared-memory applications. At its most elemental level, OpenMP is a set of compiler directives and runtime library routines that extend Fortran, C and C++ languages to express shared-memory parallelism. Program execution begins as a single process. This initial process executes serially and can set up the problem in a standard sequential manner until encounter a parallel construct defined by the directive #pragma omp parallel. The runtime forms a team of one or more threads and creates the data environment for each team member.

# Parallel looping

The shared-memory model in OpenMP makes possible to parallelize at loop level without decomposing the data structures. The construct is #pragma omp for. The inner iterations from loops are executed by several threads. A parallel construct by itself creates a Single Program Multiple Data (SPMD) program, each thread redundantly executes the same code on different areas from shared data. Usually, there are many more iterations in a loop than the number of threads. Thus, a scheduling policy is necessary to assign the loop iterations to the threads.

OpenMP scheduling can be defined in runtime by the OMP\_SCHEDULE environment variable, this variable is a string formatted by two parameters: scheduling policy and chunk size. Four different loop scheduling policies can be provided to OpenMP: *Static* divide the loop into equal-sized chunks; *Dynamic* uses the internal work queue to give a chunk-sized block of loop iterations to each thread; *Guided* is similar to dynamic, but the chunk size starts off large and decreases to better handle load imbalance between iterations; and *Auto*, when the decision regarding scheduling is delegated to the compiler. The optional parameter (chunk), when specified, must be a positive integer and defines how many loop iterations will be assigned to each thread at a time (INTEL, 2014).

#### Parallel tasking

Tasks in OpenMP are code blocks that the compiler wraps up and makes available to be executed in parallel threads. The construct is #pragma omp task. Teams of threads are created and tasks can be executed in arbitrary order, one per thread. They are synchronized by the master thread using a barrier, to check when all tasks are completed.

When a thread encounters the task construct, it may execute the task immediately or delay its execution. If delayed, the task is located in a pool of tasks associated with

the current parallel region. All threads in a team will take tasks out of the pool and execute them until the pool is empty. A thread that executes a task might be different from the thread that originally encountered it. At some point, if the list of delayed tasks is too long, the runtime may stop the task generating, and switches all threads to execute already generated tasks

# 2.3.3 Impact of compilers

Compilers are very important in performance optimization. To handle the multicore architectures and to parallelize a program, the compiler must perform three tasks: first, it analyzes the program to determine the dependencies between instructions; second, it performs ILP optimizations which remove dependencies between instructions; third, it reorders the instructions, a process known as code scheduling. For memory accesses, it is also useful to know if two or more instructions read the same memory location (HWU et al., 1995).

Optimization in compiling is a process where the control and data flows are analyzed and may transform the order of instructions to satisfy performance requirements. There are two common compilers for multicore architectures: the GNU Compiler Collection (GCC) is an integrated distribution of compilers for many programming languages (C, C++, Objective-C, Objective-C++, Java, Fortran, Ada, and Go) (STALLMAN; COMMUNITY, 2017), and the Intel C++ Compiler (ICC) (INTEL, 2018) to compile and generate applications that can run on the Intel® 64 and IA-32 architectures (available to Linux, Windows an MacOS).

The compilers support several optimization levels to control compiling time, memory usage, speed and code scaling at runtime. But finding optimal performance is quite difficult because to expand compiler options creates a large set. For example, to evaluate the compiler optimizations (-O1, -O2, and -O3 flags) of six parallel codes (implemented in sequential, Pthreads, C++11, OpenMP, Cilk Plus, and TBB) on two different multicore architectures (Intel Xeon and AMD Opteron) used a total of 240 performance combinations (MACHADO et al., 2017).

Additionally to OpenMP, there are some approaches to exploit the multicore architectures based on compiler directives. First, *OpenCL* is an open standard that provides a common language, programming interfaces, and hardware abstraction for developing applications in HPC environments. The environment consists of a host CPU and any at-

tached accelerator device. OpenCL offers classic compilation and linking features, and it also supports runtime compilation that allows the execution of kernels on devices unavailable when applications were developed. Runtime compilation in OpenCL allows an application to be independent of instruction sets of devices.

Second, the *OpenACC* approach is also represented by a set of compiler directives. OpenACC is a nonprofit corporation founded by four companies: CAPS Enterprise, CRAY Inc., the Portland Group Inc., and NVIDIA. Their objective was to create a cross-platform API that would easily allow acceleration of applications on manycore and multicore processors using directives. OpenACC API-enabled compilers and runtimes hide concerns about the initialization of accelerators, or data and program transfer between the host and the accelerator, inside the programming model. This allows the programmer to provide additional information to the compilers, including locality of data to an accelerator and mapping of loops onto an accelerator (CANTIELLO; MARTINO; MOSCATO, 2014).

#### Source-to-source transformation

Recent alternatives to support compilers and model programming for multicore architectures are the source-to-source (S2S) transformers. They convert a program source written in a given language to a new version in the same language or in a different one, and are conceived mainly with one or more of the following objectives: to transform a sequential version of code into a parallel version for a target architecture, to transform a parallel source code written with a particular paradigm (i.e., OpenMP) to a different language (i.e., OpenCL), to apply source code optimization on regions of code (i.e., loopnests) in order to take advantage of hardware features or to improve data locality.

The process of transformation of code generally is not a priori fixed, but it can be driven in several ways: by users who can annotate code regions they want to transform, by analyzing dependences on data inside loop nests, or by the size of the data involved. There are systems that produce multiple versions of the translated code with software probes that can select among them at runtime, depending on the architecture performance, these are known as auto-tuning systems. One example of this is the BOAST framework (CRONSIOE; VIDEAU; MARANGOZOVA-MARTIN, 2013)

#### 2.4 Performance evaluation

To exploit the parallelism, HPC applications must be programmed to considerably reduce the overhead between the processors. Because of the high cost involved in hardware implementation or software simulation of HPC architectures, a performance evaluation needs to be carried out through analytic techniques. A mathematical model to analyze the performance makes it possible to study the efficiency in terms of various design parameters used as inputs to a performance model. And it is necessary to take a general approach, independent of the application (BHUYAN; YANG; AGRAWAL, 1989).

In computer systems, performance evaluation is a fundamental phase. The most direct method of performance evaluation is by the executing applications, collecting the output, and observing the system performance by analyzing the output. Another method of performance evaluation is when the architecture is not available, this method helps to predict the requirements at previous stages of application execution (KUMAR; BAL-AMURUGAN, 2017). Furthermore, characterizing and predicting the performance of applications at runtime on multicore architectures help to design best performing configurations and to optimize the execution of applications on new systems. To build linear models to predict the performance in different chips is useful to characterize the performance of common HPC applications (ROSALES et al., 2017).

# 2.4.1 Hardware performance counters

Knowing the status on multicore architectures, when they are running the applications, allows to improve the performance. In this sense, the hardware performance counters exist as a small set of registers that counts the occurrences of specific signals related to the processor functions (cache misses, cycles, branch instructions, FLOPS, etc.). Monitoring these events facilitates correlation between the structure of code and the efficiency of that code to the underlying architecture.

In this work, we use a common library to access the registers from hardware counters called the *Performance Application Programming Interface (PAPI)*. It provides two interfaces to the underlying counter hardware: a high-level interface for the acquisition of measurements, it provides the ability to start, stop and read the counters for a specified list of events, and a low-level interface that deals with hardware events in groups called EventSets. An EventSet consists of countable events that the user can count as

part of a group, it can reflect how the counters are most frequently used, such as taking simultaneous measurements of different hardware events (MUCCI et al., 1999).

#### 2.4.2 Roofline model

The Roofline model (WILLIAMS; WATERMAN; PATTERSON, 2009) is a performance model used for kernel computations and combines together the floating-point performance, the operational intensity, and memory performance in a 2D graph. The peak floating-point performance can be found through hardware specifications or microbenchmarks. The operational intensity means the operations per byte of DRAM traffic, defining total bytes accessed as those bytes that go to the main memory after they have been filtered by the cache hierarchy.

The graph is on a log-log scale. The y-axis is the floating-point performance. The x-axis is the operational intensity. The Roofline model provides several upper bound to performance that gives this model its name, the horizontal lines represent the parallel optimizations (TLP, ILP, SIMD, and floating-point balance) and diagonal lines represent the peak memory bandwidth and related optimizations (restructure loops for unit stride accesses, memory affinity, and software prefetching). An example of the Roofline model for an Intel Xeon multicore architecture is illustrated in Figure 2.1. The red vertical dashed lines indicate the operational intensity for different kernels (7-point stencil, Lattice-Boltzmann MagnetoHydro-Dynamics, and 3D the Fast Fourier Transform), the X marks the performance achieved for each kernel. As we can see, the different kind of applications and the parallelism level achieve different performance.

Source: (WILLIAMS; WATERMAN; PATTERSON, 2009)

# 2.5 Target machines

Compiler

gcc 4.6.4

Characteristics of multicore architectures used in this research are described in Table 2.1. Although these machines are quite different in terms of the number of cores and memory size, the processor architecture is similar: a multicore chip with a memory hierarchy of several levels of cache. They are located at BRGM (France) and at Informatics Institute of UFRGS (Brazil).

Hostname Viking (UFRGS) Cryo (BRGM) Server 185 (BRGM) Turing (UFRGS) KNL (UFRGS) Xeon E5530 Xeon E5-2650 Processor Xeon E5-4650 Xeon X7550 Xeon Phi 7520 2.70 Clock (GHz) 2.40 2.00 2.00 1.40 4 8 Physical cores 8 8 68 Sockets 2 2 4 4 1 Threads 16 16 32 64 272 Cache (MB) L3 (8) L3 (20) L3 (20) L3 (18) L2 (34)

gcc 5.4.0

gcc 4.6.4

icc 18.0.1

gcc 5.4.0

Table 2.1: Configurations of multicore machines.

Topology of *Viking* node is presented in Figure 2.2 and is a typical multicore machine. Each core runs two threads simultaneously (TLP) by the HyperThreading technology, and the memory hierarchy is easily exposed: the data and instruction L1 private caches for each core, it continues with an L2 private cache, also for each core, and the last level cache (L3) is a shared memory for all cores in the same socket.

Machine (24GB total) NUMANode P#0 (12GB) NUMANode P#1 (12GB) Package P#1 Package P#0 L3 (8192KB) L3 (8192KB) L2 (256KB) L1d (32KB) L1i (32KB) Core P#0 Core P#1 Core P#2 Core P#3 Core P#0 Core P#1 Core P#2 Core P#3 PU P#0 PU P#2 PU P#4 PU P#6 PU P#1 PU P#3 PU P#5 PU P#7 PU P#8 PU P#10 PU P#12 PU P#14 PU P#9 PU P#11 PU P#13 PU P#15

Figure 2.2: Architeture of Viking multicore machine presented in Table 2.1.

Source: The author

# 2.6 Concluding remarks

In this chapter we presented the basis of common multicore architectures and how they are evolved in complex systems with many components, and how there is a constant increase in parallelism. In this context, programming models have to take into account the particular characteristics of different architectures to improve the performance. Thus, programming of hardware devices and scalability of software need to be optimized to reach the theoretically available performance.

With the rising of multicore architectures for several application domains, it is important to understand the common characteristics among all platforms (processing elements, memory hierarchy, and power/performance rates). However, as long as there is no convergence towards unified programming approaches applicable to a variety of different architectures, efforts into general solutions are a challenge. The solution for performance improvement is frequently one particular application for one detailed architecture. Moreover, although current compilers can deal with parallelism, freeing the programmer from the task of parallelizing and orchestrating is quite difficult to obtain the optimal processing, much of the responsibility is still put on the programmer.

Trending of current efforts may be focused on multicore aware algorithms, multicore enabled libraries, and multicore capable tools. The goal is not to design isolated solutions for particular configurations but to develop methodologies and concepts that apply to a wide range of problem classes and architectures. It is important for multicore systems to be able to satisfy the different computing requirements of a large fraction of users with multicore resources. To predict and to improve the performance on these systems depend on the underling architecture.

The research is necessary for exploring new models of performance optimization that are well adapted to the prerequisites of hardware and programming models. The approach of hardware aware computing is trying to find a balance between programmer capabilities from best performing implementations and the compiler based optimizations. Currently, restructuring of algorithms is needed to optimize the performance and to minimize the execution time.

# 3 NUMERICAL BACKGROUND: GEOPHYSICAL KERNELS ON MULTICORE PLATFORMS

In this chapter, we present the geophysics numerical models. Because of its simplicity, the Finite-Difference Method (FDM) is widely used to design the geophysics models, when discretizing Partial Differential Equations (PDE). From the numerical analysis point of view, the FDM computational procedure consists in using the neighboring points in horizontal, vertical or diagonal directions to calculate the current point.

## 3.1 Stencil applications

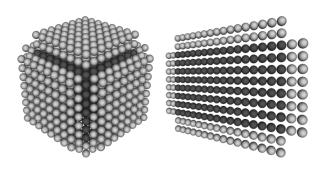

In the case of a 3D Cartesian grid, the computational procedure consists in using the neighboring points in the north-south, east-west and forward-backward directions to evaluate the current grid point. The stencil sweep can be expressed as iterative time domain (represented by the first loop controlled by  $n\_times$  variable), and a triply nested parallel loop presented in Algorithm 1. The algorithm then moves to the next point applying the same stencil computation until the entire spatial grid have been traversed, and the time domain is completed. The number of points used in each direction depends on the order of the approximation and is of great importance for the overall performance.

# Algorithm 1: Pseudocode for stencil algorithms

```

1: for t = 1 to n\_times do

compute in parallel

2:

for i = 1 to SIZE\_X\_direction do

3:

for j = 1 to SIZE\_Y\_direction do

4:

for k = 1 to SIZE\_Z\_direction do

5:

compute stencil(3D tile)

6:

7:

end for

8:

end for

end for

9:

10: end for

```

# 3.1.1 7-point Jacobi stencil

The 7-point Jacobi stencil is a reference example of numerical kernel used in various context in order to evaluate the impact of advanced reformulation or the impact of the underlying architecture. This numerical kernel can be described as a proxy of complex stencils like those corresponding to geophysical applications. A review can be found in (DATTA et al., 2010). This stencil model also corresponds to the standard discretization of the elliptic 3D Heat equation 3.1.

$$B_{i,j,k} = \alpha A_{i,j,k} + \beta (A_{i-1,j,k} + A_{i,j-1,k} + A_{i,j,k-1} + A_{i+1,j,k} + A_{i,j+1,k} + A_{i,j,k+1})$$

(3.1)

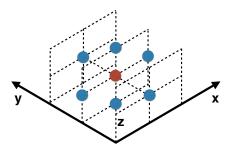

Representation of stencil size is presented in Figure 3.1. Calculation of this numerical equation needs 7 values, one from current point plus 6 from neighbor points (one previous and one next on 3D axes).

Figure 3.1: Size of 7-point Jacobi stencil and its neighbor points.

Source: (NGUYEN et al., 2010)

A standard metric available to characterize a stencil kernel is the Arithmetic Intensity (AI) that can be defined as the ratio between the floating point operations and the memory transfers. In the case of the Seven-point Jacobi kernel, the lower-bound of the arithmetic intensity is 0.18. A synthetic pseudo-code of this kernel could be found in Algorithm 2.

Algorithm 2: Pseudo-code for the Seven-point Jacobi stencil.

$$\begin{array}{l} \text{for } i = 1 \text{ to } N_x \text{ do} \\ \\ \text{for } j = 1 \text{ to } N_y \text{ do} \\ \\ \text{for } k = 1 \text{ to } N_z \text{ do} \\ \\ X^{n+1}(i,j,k) = X^n(i,j,k) + X^n(i,j,k+1) + X^n(i,j,k-1) \\ \\ + X^n(i,j+1,k) + X^n(i,j-1,k) \\ \\ + X^n(i+1,j,k) + X^n(i-1,j,k) \\ \\ \text{end for} \end{array}$$

end for

end for

### 3.1.2 Seismic wave propagation stencil

Evaluation of damages occurred during strong ground motion is critical for urban planning. The seismic wave equation waves radiated from an earthquake are often simulated under the assumption of an elastic medium although the waves attenuate due to some anelasticity. If it considers a 3D isotropic elastic medium, the seismic wave equation is given by equation 3.2:

$$\rho \frac{\partial v_i}{\partial t} = \frac{\partial \sigma_{ij}}{\partial j} + F_i \tag{3.2}$$

The discretization of previous equation using a finite-difference method gives the following system of equations:

$$\begin{cases}

\rho \frac{\partial}{\partial t} v_x &= \frac{\partial}{\partial x} \sigma_{xx} + \frac{\partial}{\partial y} \sigma_{xy} + \frac{\partial}{\partial z} \sigma_{xz} + f_x \\

\rho \frac{\partial}{\partial t} v_y &= \frac{\partial}{\partial x} \sigma_{yx} + \frac{\partial}{\partial y} \sigma_{yy} + \frac{\partial}{\partial z} \sigma_{yz} + f_y \\

\rho \frac{\partial}{\partial t} v_z &= \frac{\partial}{\partial x} \sigma_{zx} + \frac{\partial}{\partial y} \sigma_{zy} + \frac{\partial}{\partial z} \sigma_{zz} + f_z

\end{cases}$$

(3.3)

Additionally, the constitutive relation in the case of an isotropic medium is presented in equation 3.4.

$$\frac{\partial \sigma_{ij}}{\partial t} = \lambda \delta_{ij} \left( \frac{\partial v_x}{\partial x} + \frac{\partial v_y}{\partial y} + \frac{\partial v_z}{\partial z} \right) + \mu \left( \frac{\partial v_i}{\partial j} + \frac{\partial v_j}{\partial i} \right)$$

(3.4)

$$\begin{cases}

\frac{\partial}{\partial t}\sigma_{xx} &= \lambda \left( \frac{\partial}{\partial x}v_x + \frac{\partial}{\partial y}v_y + \frac{\partial}{\partial z}v_z \right) + 2\mu \frac{\partial}{\partial x}v_x \\

\frac{\partial}{\partial t}\sigma_{yy} &= \lambda \left( \frac{\partial}{\partial x}v_x + \frac{\partial}{\partial y}v_y + \frac{\partial}{\partial z}v_z \right) + 2\mu \frac{\partial}{\partial y}v_y \\

\frac{\partial}{\partial t}\sigma_{zz} &= \lambda \left( \frac{\partial}{\partial x}v_x + \frac{\partial}{\partial y}v_y + \frac{\partial}{\partial z}v_z \right) + 2\mu \frac{\partial}{\partial z}v_z \\

\frac{\partial}{\partial t}\sigma_{xy} &= \mu \left( \frac{\partial}{\partial y}v_x + \frac{\partial}{\partial x}v_y \right) \\

\frac{\partial}{\partial t}\sigma_{xz} &= \mu \left( \frac{\partial}{\partial z}v_x + \frac{\partial}{\partial x}v_z \right) \\

\frac{\partial}{\partial t}\sigma_{yz} &= \mu \left( \frac{\partial}{\partial z}v_y + \frac{\partial}{\partial y}v_z \right)

\end{cases}$$

(3.5)

In the previous equations 3.3 and 3.5, v and  $\sigma$  represent the velocity and the stress field respectively and f denotes a known external source force. The medium is characterized by the elastic (Lamé) parameters  $\lambda$  and  $\mu$  and  $\rho$  is the density. A time derivative is denoted by  $\frac{\partial}{\partial t}$  and a spatial derivative with respect to the i-th direction is represented by  $\frac{\partial}{\partial i}$ . The Kronecker symbol  $\delta_{ij}$  is equal to 1 if i=j and zero otherwise. Exponents i,j,k indicate the spatial direction with  $\sigma^{ijk}=\sigma(i\Delta s,j\Delta s,k\Delta s)$ ,  $\Delta s$  corresponds to the space step and  $\Delta t$  to the time step.

Due to its simplicity, the finite-difference method is widely used to compute the propagation of seismic waves. The numerical kernel under study relies on the classical 4-th order in space and second-order in time approximation (VIRIEUX, 1986; MOCZO; ROBERTSSON; EISNER, 2007). Considering the classical 4-th order in space and second-order in time approximation, the stencil applied for the computation of the velocity component in the x-direction is given by equation 3.6. The same numerical scheme is used to compute the stress components.

$$v_{x}^{(l+\frac{1}{2})jk} \left( l + \frac{1}{2} \right) = v_{x}^{\left( i + \frac{1}{2} \right)jk} \left( i - \frac{1}{2} \right) + a_{1} F_{x}^{\left( i + \frac{1}{2} \right)jk}$$

$$+ a_{2} \left[ \frac{\sigma_{xx}^{(i+1)jk} - \sigma_{xx}^{ijk}}{\Delta x} + \frac{\sigma_{xy}^{\left( i + \frac{1}{2} \right)\left( j + \frac{1}{2} \right)k} - \sigma_{xy}^{\left( i + \frac{1}{2} \right)\left( j - \frac{1}{2} \right)k}}{\Delta y} + \frac{\sigma_{xz}^{\left( i + \frac{1}{2} \right)j\left( k + \frac{1}{2} \right) - \sigma_{xz}^{\left( i + \frac{1}{2} \right)j\left( k - \frac{1}{2} \right)}}{\Delta z} \right]$$

$$- a_{3} \left[ \frac{\sigma_{xx}^{(i+2)jk} - \sigma_{xx}^{(i-1)jk}}{\Delta x} + \frac{\sigma_{xy}^{\left( i + \frac{1}{2} \right)\left( j + \frac{3}{2} \right)k} - \sigma_{xy}^{\left( i + \frac{1}{2} \right)\left( j - \frac{3}{2} \right)k}}{\Delta y} + \frac{\sigma_{xz}^{\left( i + \frac{1}{2} \right)j\left( k + \frac{3}{2} \right) - \sigma_{xz}^{\left( i + \frac{1}{2} \right)j\left( k - \frac{3}{2} \right)}}{\Delta z} \right]$$

$$(3.6)$$

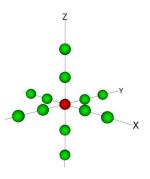

Figure 3.2 illustrates the size of the seismic stencil. In this case, the stencil needs 13 values, one from current point plus 12 from neighbor points (2 previous and 2 next on 3D axes).

Figure 3.2: Size of seismic stencil to calculate velocity and stress components.

Source: (MICHÉA; KOMATITSCH, 2010)