#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### KATHOLIEKE UNIVERSITEIT LEUVEN ARENBERG DOCTORAL SCHOOL FACULTY OF ENGINEERING SCIENCE

# Design of Wideband CMOS Building Block Circuits for Receivers from 0.5 up to 4 GHz

### Filipe DIAS BAUMGRATZ

Examination committee: Prof. dr. T. Balen, Chair (UFRGS) Prof. dr. S. Bampi, Supervisor (UFRGS) Prof. dr. ir. F. Tavernier, Supervisor (KU Leuven) Prof. dr. ir. M. Steyaert, Supervisor (KU Leuven) Prof. dr. ir. S. Pollin (KU Leuven) Prof. dr. H. Klimach (UFGRS) Prof. dr. A. Mariano (UFPR) Dr. ir. M. Borremans (Huawei Ltd.)

Dissertation presented in partial fulfillment of the requirements for the degrees of PhD in Microelectronics (UFRGS) and Doctor of Engineering Science (PhD): Electrical Engineering (KU Leuven) Baumgratz, Filipe Dias

Design of Wideband CMOS Building Block Circuits for Receivers from 0.5 up to 4 GHz / Filipe Dias Baumgratz. -2018.

150 f.

Orientadores: Sergio Bampi, Filip Tavernier.

Coorientador: Michiel Steyaert.

Tese (Doutorado) – Universidade Federal do Rio Grande do Sul, Instituto de Informática, Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2018.

1. wideband receivers. 2. discrete-time receivers. 3. low-noise amplifiers. 4. passive mixers. 5. discrete-time filters. I. Bampi, Sergio, orient. II. Tavernier, Filip, orient. III. Steyaert, Michiel, coorient. IV. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Oppermann

Vice-Reitora: Profa. Jane Tutikian

Pro-Reitor de Pos-Gradução: Prof. Celso Giannetti Loureiro Chaves

Diretora do Instituto de Informática: Profa. Carla Maria Dal Sasso Freitas

Coordenadora da Pós-Graduação em Microeletrônica: Profa. Fernanda Gusmão de Lima Kastensmidt

Bibliotecária - Chefe: Beatriz Haro

# Preface

This PhD had been a long and winding road. Hence, first and foremost, I would like to thank God for granting me the strength to complete this task. Also, I would like to thank my wife, Cíntia, my brother, Thiago, and my parents, Leila and Carlos, for the patience and support throughout all those years. I am grateful to Laura and Cecília for hosting Cíntia and me in their home on multiple occasions.

I am genuinely thankful to my supervisors, prof. Sergio Bampi and prof. Filip Tavernier, for the guidance, support, and motivation. Prof. Bampi, thank you for supporting my two internships abroad and my joint-degree (even though they delayed my PhD). Prof. Tavernier, thank you for helping me with all the paperwork at KU Leuven.

I am also thankful to the other members of the examination committee, prof. Michiel Steyaert, prof. Sofie Pollin, prof. Hamilton Klimach, prof. André Mariano and Marc Borremans. Their valuable comments have helped me to significantly improve my thesis manuscript.

Also, I would like to thank Prof. Carlos Saavedra from Queen's University. Prof. Saavedra not only gave me the opportunity to have my first tapeout in 2014 but also guided through it.

I am thankful to my friends and colleagues in Brazil, Canada, and Belgium for the fruitful discussions, help, and friendship. Paramartha, Jan and Umut, thank you for all the help at MICAS and for being such great officemates. Sandro, thank you for introducing me to discrete-time filters, and for the support with the design of my discrete-time receiver. Hao Li, thank you for testing my first chip. Oscar, thank you for the climbing partnership and technical discussions. Dedecca, thank you for the Dutch translation of my thesis abstract. Pedro, Paulo, Diogo, Arthur L., Arthur C., Alonso, David, Israel, Helga, Gabriel, Bortolon, Guilherme (Gnomo), Baris, Thanos, Laura, Nicolas, Alexander, Marco, Elisa, Wouter, Anthony, Sebastián, Jorge, Dileep, Luciano, Mahdi, Sean and Jeet, thank you all for the funny discussions, the barbecues, the drinking, etc...

I am grateful to CAPES, CNPq, FAPERGS, ELAP, and MICAS for the financial support.

Filipe Dias Baumgratz May 2018

### Abstract

This thesis has been focused on the design of wideband circuits for multi-band/multistandard receivers. Three projects have been developed during this Ph.D. and are presented in this thesis: the required specifications of a wideband spectrum-sensing receiver, two versions of a 130 nm CMOS wideband low-noise variable gain amplifier, and a 40 nm CMOS wideband high-IF receiver.

The specifications of the spectrum-sensing receiver aim for the detection of three wideband signals WRAN, WiMax, and LTE. These are the principal wideband signals within the band from 50 MHz to 4 GHz, which has been selected because it was very crowded but with plenty of underused spaces. After the definition of the receiver specifications, the block-level specifications have also been calculated and verified through behavioral model simulations. The specifications have shown that a multistandard receiver must cope with a large range of signal power, which motivated the design the low-noise variable gain amplifier (LNVGA).

The purpose of the LNVGA is to allow for the reception of both strong and weak signals by either reducing their signal power to values that do not compress the following blocks, like the mixer, or increasing it so that the noise figure is reduced, which increases the receiver sensitivity. The two fabricated LNVGAs achieve a gain tuning range up to 45 dB within a bandwidth of 3 GHz in addition to a NF as low as 3.4 dB. In contrast to other published VGAs, the proposed LNVGAs are the only ones that achieve a large gain tuning range in combination with a reasonably low NF. The large gain tuning range has been obtained thanks to the proposed low imbalance active balun. Both LNVGAs have been designed in 130 nm CMOS for a 1.2 V supply.

The final design is a 40 nm CMOS wideband high-IF receiver. Due to the evolution of CMOS technology, receivers with a higher IF and without external components are feasible in CMOS nodes below 65 nm. The main advantage of those high-IF receivers is their robustness to DC offsets, flicker noise, and even-order distortion. The two main contributions of this design are the LTNA and the modified bandpass switched-capacitor filter (SC-BPF). The LNTA uses a dual noise cancellation, which ensures a

low noise figure. Since both the mixer and the SC-BPF are passive, the LTNA needs an output impedance higher than the input impedance of the following blocks. Hence, a folded-cascode has been merged into the LNTA to increase its output impedance. The original SC-BPF has been modified by adding cross-connected transconductors at the in-phase (I) and quadrature (Q) inputs. These cross-connected transconductors not only boost but also allow for a variation of the Q-factor of the SC-BPF with a minimum increase of power consumption and design complexity. The highest voltage gain achieved by the receiver is 30 dB. While operating at the maximum gain, the receiver noise figure is 3.3 dB. The highest IIP3 is -2.5 dBm, and the IIP2 is as high as 35 dBm. The receiver and clock generation circuitry drain together 25 mA from a 0.9 V power supply. In comparison to the state-of-the-art, our receiver has the smallest area in addition to the reduced power consumption, and it targets the largest RF band.

# Resumo

#### Projeto CMOS de circuitos banda larga para receptores de 0.5 à 4 GHz

O foco desta tese de doutorado é o projeto de circuitos integrados banda larga para receptores que atedem múltiplas bandas e padrões. Durante este doutorado, três projetos foram desenvolvidos e são apresentados nesta tese: a especificação de um receptor banda-larga para sensoriamento de espectro, duas versões do projeto de um amplificador de ganho variável e baixo ruído, fabricado em 130 nm CMOS, e o projeto de um receptor *high-IF* banda larga, fabricado em 40 nm CMOS.

As especificações do receptor de sensoriamento espectral visam a detecção de três sinais de banda larga: WRAN, WiMax e LTE. Estes são os principais sinais de banda larga dentro da banda de 50 MHz à 4 GHz. A band em questão, foi selecionada por estar, concomitantemente, superlotada e subutilizada. Após a definição das especificações do receptor, as especificações em nível de bloco também foram calculadas e verificadas através de simulações com modelos comportamentais dos circuitos. As especificações mostram que o receptor deve suportar sinais com diversos níveis de potência, o que motivou o projeto do amplificador de ganho variável de baixo ruído (LNVGA).

O objetivo do LNVGA é permitir a recepção de sinais fortes e fracos. Seja atenuando o sinal, de modo a evitar a sua compressão nos blocos subsequentes, como o mixer, ou amplificando-o, de modo a reduzir a figura de ruído do sistema, o que aumenta a sua sensibilidade. Os LNVGAs fabricados são capazes de ajustar o ganho em até 45 dB em uma banda de 3 GHz. Além disso, foi observada uma figura de ruído de até 3.4 dB. Em contraste com outros VGAs publicados, os LNVGAs propostos conseguem combinar grande capacidade de ajuste de ganho com uma figura de ruído satisfatoriamente baixa. Esta grande capacidade de se ajustar o ganho deve-se, parcialmente, ao *balun* ativo proposto neste projeto. Ambos os LNVGAs foram projetados em 130 nm CMOS com uma tensão de alimentação de 1.2 V.

O projeto final é um receptor *high-IF* banda larga em 40 nm CMOS. Devido à evolução da tecnologia CMOS, receptores *high-IF* sem componentes externos são viáveis em nós

abaixo de 65 nm. A principal vantagem destes receptores é a sua robustez, à DC-offset, ruído *flicker* e distorções de ordem par. As duas principais contribuições neste projeto são o transcondutor de baixo ruído (LTNA) e a modificação no filtro passa banda à capacitor chaveado (SC-BPF). O LNTA usa duplo cancelamento de ruído, garantindo uma baixa figura de ruído. Sendo o mixer e o SC-BPF passivos, a impedância de saída do LNTA deve ser maior que a impedância de entrada desses blocos. Deste modo, incorporou-se um folded-cascode ao LNTA para aumentar a sua impedância de saída. O SC-BPF original foi modificado adicionando-se um par cruzado de transcondutores as entradas em fase (I) e em quadratura (Q). Estes transcondutores permitem o aumento do valor do fator de qualidade (Q-factor) do SC-BPF e, até mesmo, o seu controle, isso com um aumento mínimo no consumo de energia e na complexidade do projeto. O maior ganho de tensão alcançado pelo receptor é de 30 dB. Operando com o ganho máximo, figura de ruído do receptor é de 3.3 dB. O IIP3 mais alto em 1 GHz é -2.5 dBm, e o IIP2 máximo é de 35 dBm. O receptor e o gerador de clock drenam 25 mA de uma fonte de 0.9 V. Em comparação com o estado da arte, o nosso receptor tem a menor área. Além disso, o consumo de energia é pequeno e buscamos operar numa banda mais ampla de entrada de RF.

## Beknopte samenvatting

Dit proefschrift is gericht op het ontwerpen van breedbandige circuits voor multiband/multi-standaard ontvangers. Drie projecten zijn ontwikkeld en worden beschreven in dit proefschrift: de vereiste specificaties van een breedbandige spectrum-detecterende ontvanger, twee versies van een 130 nm CMOS breedbandige lage-ruis versterker met variable versterking, en een 40 nm CMOS breedbandige hoog-IF ontvanger.

De specificaties van de spectrum-detecterende ontvanger zijn gericht op de detectie van drie breed-bandige signalen, namelijk WRAN, WiMax en LTE. Dit zijn de belangrijkste breedbandige signalen in de frequentieband van 50 MHz tot 4 GHz, een druk bezette band, maar met veel vrij beschikba-re ruimte. Na de definitie van de ontvanger specificaties, zijn de specificaties op blokniveau ook berekend en geverifieerd door gedragsmodel simulaties. De specificaties hebben aangetoond dat een multi-standaard ontvanger moet kunnen omgaan met een groot bereik in signaalvermogen, wat een motivatie is voor het ontwerp van de lage-ruis versterker met variabele versterking (LNVGA).

Het doel van de LNVGA is om de ontvangst van zowel sterke als zwakke signalen mogelijk te ma-ken, door ofwel signaalvermogen te verlagen tot waardes die niet tot compressie resulteren in de volgende blokken, zoals de mixer, of deze te verhogen zodat het ruisgetal wordt verminderd, wat een positief effect heeft op de gevoeligheid van de ontvanger. De twee gefabriceerde LNVGA's maken het mogelijk om de versterking aan te passen over een bereik van 45 dB, in een bandbreedte van 3 GHz, en met een ruisgetal van slechts 3,4 dB. In tegenstelling tot eerder gepubliceerde VGA's, zijn de voorgestelde LNVGA's de enige die een groot versterkingsbereik realiseren, in combinatie met een behoorlijk laag ruisgetal. Het grote versterkingsbereik is gerealiseerd dankzij de voorgestel-de actieve balun met lage onbalans. Beide LNVGA's zijn ontworpen in 130 nm CMOS voor een 1,2 V voedingsspanning.

Het laatste ontwerp is een 40 nm CMOS breedbandige hoog-IF ontvanger. Vanwege de schaling van CMOS technologieën, zijn ontvangers met een hoge IF en zonder externe componenten moge-lijk geworden voor CMOS technologieën onder 65 nm.

Het grote voordeel van deze hoog-IF ont-vangers is hun robuustheid ten opzichte van DC-verschuivingen, flikkerruis en even-orde vervor-ming. De twee belangrijkste bijdragen van dit ontwerp zijn de lage-ruis transimpedantie versterker (LNTA) en de aangepaste geschakelde-condensator banddoorlaat filter (SC-BPF). De LNTA maakt gebruik van een dubbele ruisonderdrukking, die zorgt voor een laag ruisgetal. Omdat zowel de mixer als de SC-BPF passief zijn, heeft de LNTA een uitgangsimpedantie nodig die hoger is dan de ingangsimpedantie van de volgende blokken. Vandaar dat een folded-cascode structuur gebruikt is in de LNTA om de uitgangsimpedantie te verhogen. De oorspronkelijke SC-BPF is aangepast door het toevoegen van kruisgekoppelde transconductors aan zowel de in-fase (I) als de kwadratuur-fase (Q) ingangen. Deze kruisgekoppelde transconductors verhogen niet alleen de Q-factor, maar maken ook een variatie mogelijk in de Q-factor van de SC-BPF met een minimale toename van het energieverbruik en complexiteit van het ontwerp. De grootste spanningsversterking van de ontvanger is 30 dB. Met deze maximale versterking is het ruisgetal van de ontvanger 3,3 dB. De hoogste IIP3 is 2,5 dBm en de IIP2 is 35 dBm. De ontvanger, inclusief klokgeneratie, verbruikt 25 mA van een 0,9 V voedingsspanning. In vergelijking met de state-of-the-art, heeft deze ontvanger de kleinste oppervlakte, een laag energieverbruik, en de grootste RF bandbreedte.

# List of Abbreviations

| Notation<br>2G | <b>Description</b><br>Second generation mobile communication systems. |

|----------------|-----------------------------------------------------------------------|

| 3G             | Third generation mobile communication systems.                        |

| 4G             | Fourth generation mobile communication systems.                       |

| 5G             | Fifth generation mobile communication systems.                        |

| AC             | Alternate current.                                                    |

| ADC            | Analog-to-digital converter.                                          |

| ATSC           | Advanced television systems committee.                                |

| AWG            | Arbitrary wave generator.                                             |

| BER            | Bit-error-rate.                                                       |

| BPF            | Bandpass filter.                                                      |

| BR             | Bit-rate.                                                             |

|                |                                                                       |

| CLK            | Clock.                                                                |

| CMOS           | Complementare metal oxide semiconductor.                              |

| CR             | Cognitive Radio.                                                      |

| CS             | Charge-sharing.                                                       |

| DAB            | Digital audio broadcasting.                                           |

| DC             | Direct current.                                                       |

| DCS1800        | Digital Cellular System at 1.8 GHz.                                   |

| DMB            | Digital multimedia broadcasting.                                      |

| DSA            | Dynamic spectrum access.                                              |

| DSP            | Digital signal processing.                                            |

| DT             | Discrete-time.                                                        |

| DUT            | Dispositive under test.                                               |

| DVB            | Digital video broadcasting.                                           |

|                |                                                                       |

| Notation | Description                                 |

|----------|---------------------------------------------|

| FCC      | American federal communications commission. |

| FFT      | Fast fourier transform.                     |

| FPLL     | Frequency-Phase locked loop.                |

| FSV      | Full-scale voltage.                         |

| GM-cells | Transconductor cells.                       |

| GPS      | Global positioning system.                  |

| GSM850   | Global System for Mobile communications at  |

|          | 850 MHz.                                    |

| GSM900   | Global System for Mobile communications at  |

|          | 900 MHz.                                    |

| Ι        | In-phase.                                   |

| IF       | Intermediate frequency.                     |

| IIP2     | Input second-order intercept point.         |

| IIP3     | Input third-order intercept point.          |

| IIR      | Infinite impulse response.                  |

| IM2      | Second-order intermodultion.                |

| IM3      | Third-order intermodulation.                |

| IP1dB    | Input 1 dB compression point.               |

| IRR      | Image rejection ratio.                      |

| LNA      | Low-noise amplifier.                        |

| LNTA     | Low noise transconductance amplifier.       |

| LNVGA    | Low-noise variable-gain amplifier.          |

| LO       | Local oscillator.                           |

| LTE      | Long-Term Evolution - 4G.                   |

| LIL      |                                             |

| MI       | Moderate inversion.                         |

| NEB      | Noise equivalent bandwidth.                 |

| NF       | Noise figure.                               |

| NMOS     | N-channel MOSFET.                           |

| OFDIA    |                                             |

| OFDM     | Orthogonal frequency division multiplexing. |

| PAPR     | Peak-to-average power ratio.                |

| PCS1900  | Personal communications service at 1.9 GHz. |

| PMOS     | P-channel MOSFET.                           |

| PSG      | Power signal generator.                     |

| Notation | Description                                                    |

|----------|----------------------------------------------------------------|

| Q        | Quadrature.                                                    |

| Q-factor | Quality-factor.                                                |

| RF       | Radio frequency.                                               |

| RX       | Receiver.                                                      |

| S11      | The reflection coefficient of the input.                       |

| SAW      | Surface acoustic wave.                                         |

| SCC      | Shared spectrum company.                                       |

| SDR      | Software defined radio.                                        |

| SI       | Strong inversion.                                              |

| SNR      | Signal-to-noise ratio.                                         |

| SPI      | Serial peripheral interface.                                   |

| SS       | Spectrum access.                                               |

| TF       | Transfer function.                                             |

| TIA      | Transimpedance amplifier.                                      |

| UHF      | Ultra high frequency radio for television broadcast-<br>ing.   |

| VDD      | Voltage supply.                                                |

| VGA      | Variable-gain amplifier.                                       |

| VVA      | Variable-voltage attenuator.                                   |

| WI       | Weak inversion.                                                |

| WiFi     | WLAN - IEEE 802.11.                                            |

| WiMax    | Worldwide interoperability for microwave access - IEEE 802.16. |

| WLAN     | Wireless local area network.                                   |

| WPAN     | Wireless personal area network.                                |

| WRAN     | Wireless regional area network - IEEE 802.22.                  |

# Contents

| At  | ostrad | ct                                                                | iii  |

|-----|--------|-------------------------------------------------------------------|------|

| Re  | esumo  | ο                                                                 | v    |

| Be  | eknop  | ote samenvatting                                                  | vii  |

| Lis | st of  | Abbreviations                                                     | xi   |

| Co  | onten  | ts                                                                | xiii |

| Lis | st of  | Figures ×                                                         | vii  |

| Lis | st of  | Tables x                                                          | ×iii |

| 1   | Intr   | oduction                                                          | 1    |

|     | 1.1    | Motivation                                                        | 1    |

|     | 1.2    | Wideband receivers for multi-band and multi-standard applications | 2    |

|     | 1.3    | Outline of this thesis                                            | 5    |

| 2   | A S    | pectrum-Sensing Receiver specification                            | 7    |

|     | 2.1    | Introduction                                                      | 7    |

|     | 2.2    | The cognitive radio today                                         | 9    |

| 4 |     | eband High-IF Receiver Using a Modified Charge-Sharing                  |    |

|---|-----|-------------------------------------------------------------------------|----|

|   | 3.7 | Conclusion of the chapter                                               | 62 |

|   | 3.6 | Measurement Results                                                     | 53 |

|   | 3.5 | Monte Carlo simulation results                                          | 52 |

|   | 3.4 | Simulation Results                                                      | 48 |

|   |     | 3.3.5 Measurement Buffer                                                | 47 |

|   |     | 3.3.4 Linearity                                                         | 45 |

|   |     | 3.3.3 Voltage Gain                                                      | 43 |

|   |     | 3.3.2 Noise Figure                                                      | 39 |

|   |     | 3.3.1 Input Matching                                                    | 39 |

|   | 3.3 | Design of the proposed LNVGA                                            | 34 |

|   | 3.2 | Previous wideband VGAs                                                  | 30 |

|   | 3.1 | Introduction                                                            | 29 |

| 3 | AW  | /ideband Low Noise Variable Gain Amplifier in 130 nm CMOS               | 29 |

|   | 2.7 | Conclusion of the chapter                                               | 25 |

|   | 2.6 | Budget of the SS receiver specification                                 | 24 |

|   | 2.5 | This specification and the state-of-art of spectrum sensing receivers . | 22 |

|   | 2.4 | Receiver architectures                                                  | 17 |

|   |     | 2.3.6 Gain                                                              | 17 |

|   |     | 2.3.5 Linearity                                                         | 14 |

|   |     | 2.3.4 Noise Figure                                                      | 13 |

|   |     | 2.3.3 Sensitivity                                                       | 12 |

|   |     | 2.3.2 Signal-to-noise ratio                                             | 11 |

|   |     | 2.3.1 Frequency band                                                    | 11 |

|   | 2.3 | The receiver specification                                              | 10 |

|    | 4.1    | Introduction                                                           | 63 |

|----|--------|------------------------------------------------------------------------|----|

|    | 4.2    | Overview of the state-of-the-art                                       | 65 |

|    | 4.3    | High-IF receiver architecture                                          | 69 |

|    | 4.4    | LNTA                                                                   | 72 |

|    | 4.5    | First filtering stage                                                  | 75 |

|    |        | 4.5.1 Mixer                                                            | 77 |

|    |        | 4.5.2 First-order Bandpass Filter                                      | 80 |

|    | 4.6    | Second filtering stage                                                 | 84 |

|    |        | 4.6.1 GM-Cells                                                         | 84 |

|    |        | 4.6.2 Modified Second-order Bandpass filter                            | 85 |

|    | 4.7    | Image rejection ratio                                                  | 90 |

|    | 4.8    | Clock Generation                                                       | 91 |

|    | 4.9    | Receiver Measurement Setup                                             | 93 |

|    | 4.10   | Receiver Measurement Results                                           | 96 |

|    | 4.11   | Conclusion of the chapter                                              | 04 |

| 5  | Con    | clusions and Future Work 1                                             | 07 |

|    | 5.1    | General conclusions                                                    | 07 |

|    | 5.2    | The achivements of the thesis                                          | 08 |

|    | 5.3    | Future work                                                            | 09 |

| Α  | Cons   | siderations regarding the gain reduction in the high-IF receiver $f 1$ | 11 |

| Bi | bliogr | aphy 1                                                                 | 15 |

# **List of Figures**

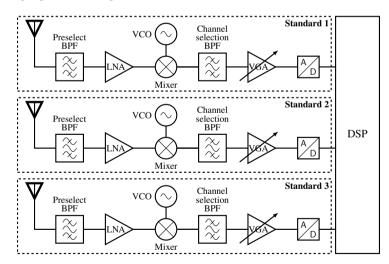

| 1.1 | Multi-band/multi-standard receiver using multiple receivers [44, 77]                                                             | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Multi-band/multi-standard receiver using multiple RF front-ends and sharing the baseband [44, 77].                               | 3  |

| 1.3 | Multi-band/multi-standard receiver using a single receiver [44, 77]                                                              | 4  |

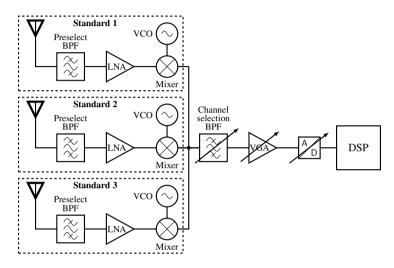

| 2.1 | The spectrum occupation in New York and Chicago [67, 68]                                                                         | 8  |

| 2.2 | (a) The Cognitive cicle and (b) CR operation [2].                                                                                | 9  |

| 2.3 | Maximum allowed output power and RF band of the communication standards considered in the specification [47, 46, 32, 33, 31, 45] | 10 |

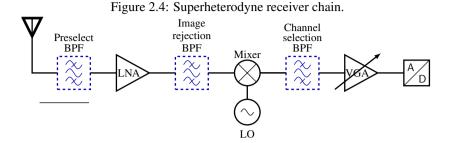

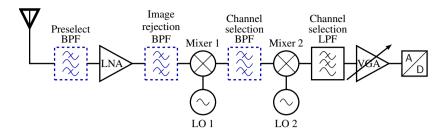

| 2.4 | Superheterodyne receiver chain                                                                                                   | 18 |

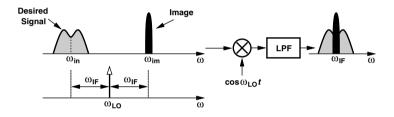

| 2.5 | The image problem [80]                                                                                                           | 18 |

| 2.6 | Dual IF Superheterodyne receiver chain                                                                                           | 19 |

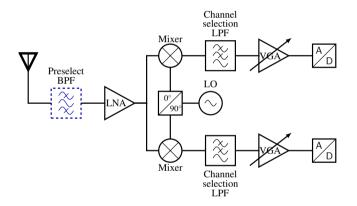

| 2.7 | Zero-IF receiver chain.                                                                                                          | 19 |

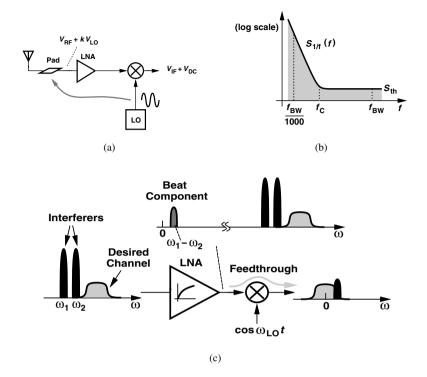

| 2.8 | (a) DC offset, (b) spectrum of flicker noise, and (c) the effect of even-<br>order distortion components [80]                    | 21 |

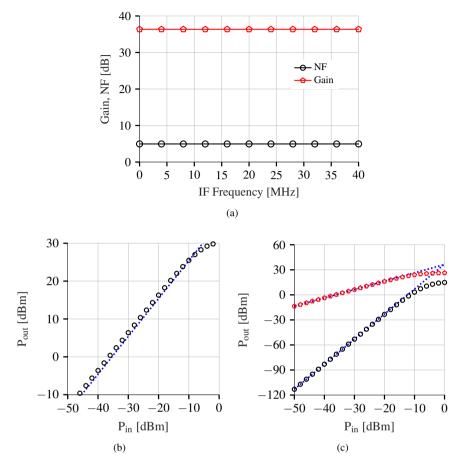

| 2.9 | Behavioral simulation results of (a) voltage gain and NF, (b) IP1dB, and (c) IIP3                                                | 26 |

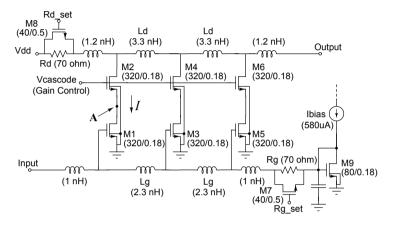

| 3.1 | 3-stage distributed VGA proposed in [102]                                                                                        | 31 |

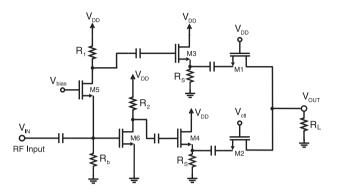

| 3.2 | VGA proposed in [82] that uses phase cancellation.                                                                               | 32 |

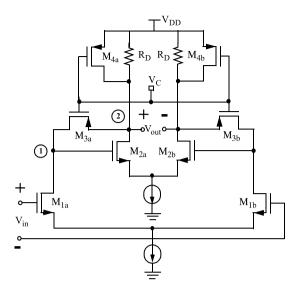

| 3.3 | Cherry-Hooper VGA proposed in [98]                                                                                               | 33 |

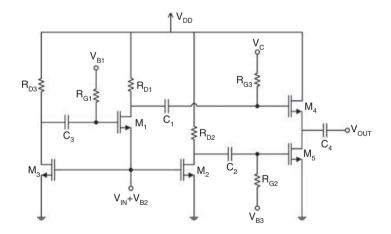

| 3.4  | VGA proposed in [27]                                                                                                                                      | 33 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

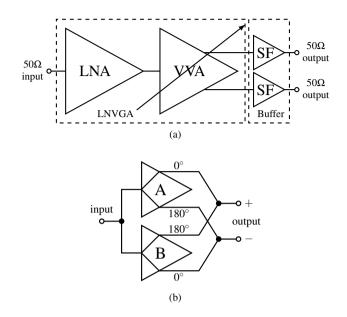

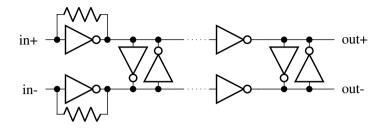

| 3.5  | (a) Block diagram of the VGA circuit and the measurement buffer. (b) VVA composed by two baluns                                                           | 35 |

| 3.6  | The schematics of the LNVGA I                                                                                                                             | 37 |

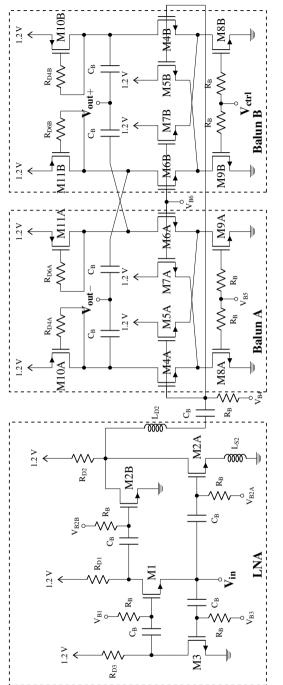

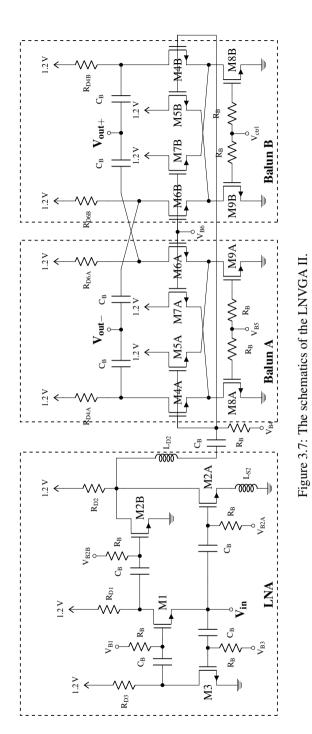

| 3.7  | The schematics of the LNVGA II.                                                                                                                           | 38 |

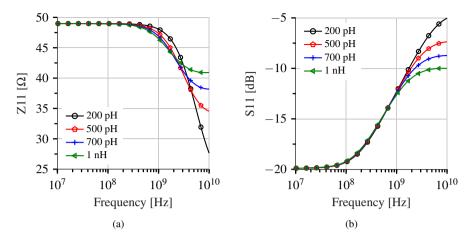

| 3.8  | The calculated (a) input impedance and (b) S11 of the LNVGA. $\ . \ .$                                                                                    | 40 |

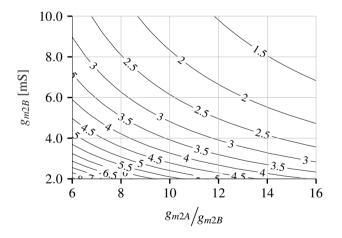

| 3.9  | LNA NF calculated for different values of $g_{m2A}/g_{m2B}$ , at $\gamma = 4/3$ [53], $\alpha = 0.8$ [53]                                                 | 41 |

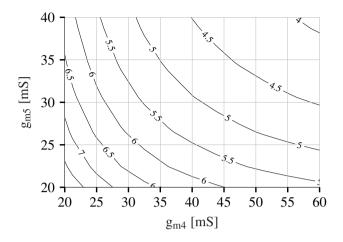

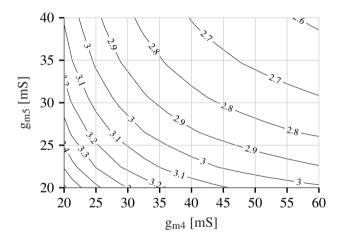

| 3.10 | LNVGA NF calculated for the LNVGA I                                                                                                                       | 43 |

| 3.11 | LNVGA NF calculated for the LNVGA II                                                                                                                      | 43 |

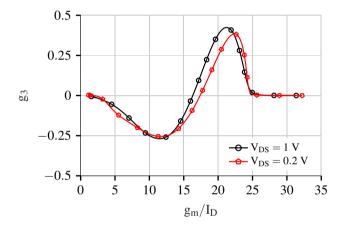

| 3.12 | Simulated $g_3$ for a single NMOS transistor with L=120 nm                                                                                                | 46 |

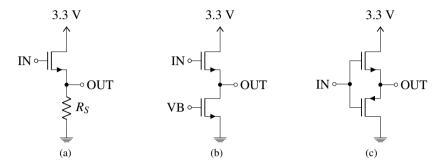

| 3.13 | The measurement buffers using (a) source followers with a passive load, (b) source follower with an active load, and (c) class AB source followers.       | 48 |

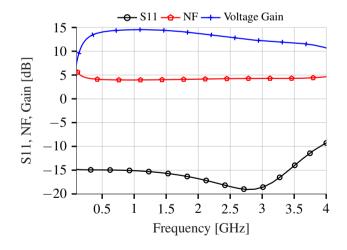

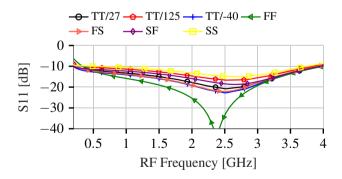

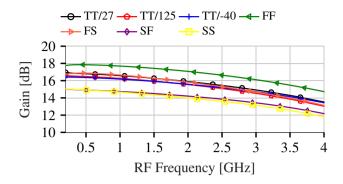

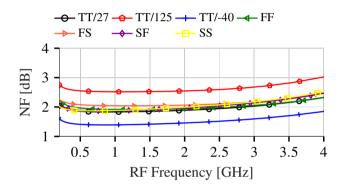

| 3.14 | S11, NF, and Voltage Gain post-layout simulation results of the LNVGA I.                                                                                  | 48 |

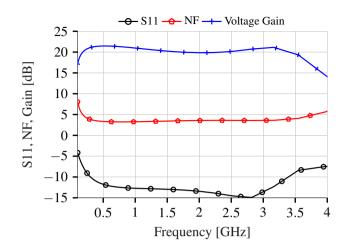

| 3.15 | S11, NF, and Voltage Gain post-layout simulation results of the LNVGA II.                                                                                 | 49 |

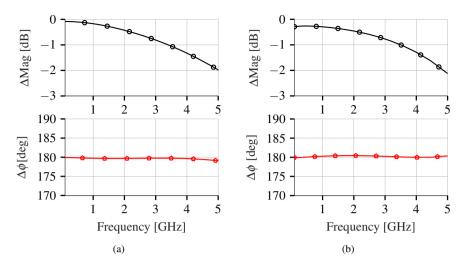

| 3.16 | Magnitude and phase imbalance post-layout simulation results of the (a) LNVGA I and (b) LNVGA II                                                          | 50 |

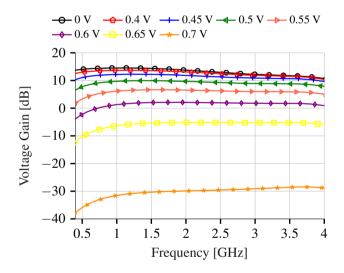

| 3.17 | Voltage gain post-layout simulation results of the LNVGA I, where each curve uses a different $V_{CTRL}$ .                                                | 50 |

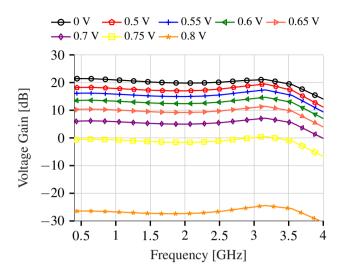

| 3.18 | Voltage gain post-layout simulation results of the LNVGA II, where each curve uses a different $V_{CTRL}$ .                                               | 51 |

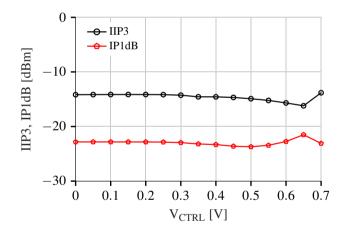

| 3.19 | IP1dB and IIP3 post-layout simulation results of the LNVGA I at 1 GHz, using different values of <i>V</i> <sub>CTRL</sub>                                 | 51 |

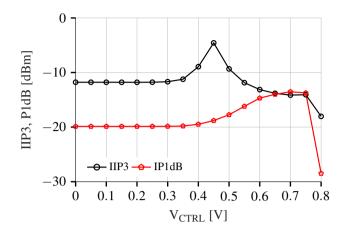

| 3.20 | IP1dB and IIP3 post-layout simulation results of the LNVGA II at 1 GHz, using different values of <i>V</i> <sub>CTRL</sub>                                | 52 |

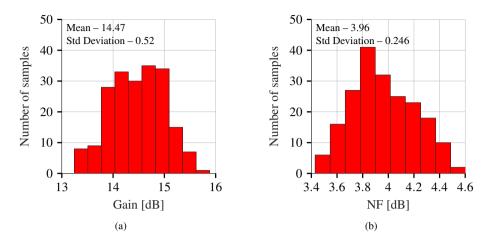

| 3.21 | Post-layout Monte Carlo (process variation) simulation results of the LNVGA I for 200 samples: (a) Voltage gain and (b) noise figure                      | 53 |

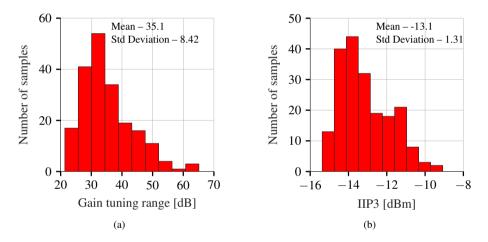

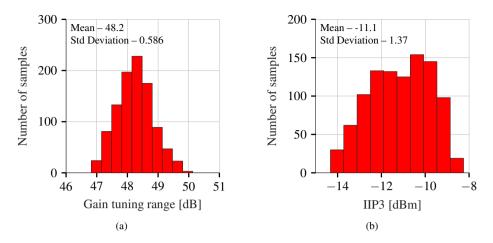

| 3.22 | Post-layout Monte Carlo (process variation) simulation results of the LNVGA I for 200 samples: (a) Gain tuning range and (b) third-order intercept point. | 53 |

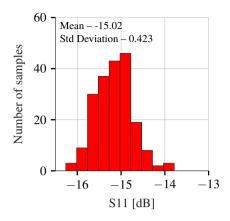

| 3.23 | Post-layout Monte Carlo (process variation) simulation results of the LNVGA I for 200 samples: Input match.                                                 | 54 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

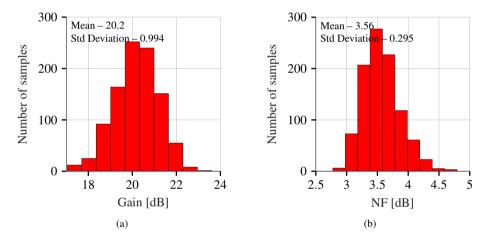

| 3.24 | Post-layout Monte Carlo (process variation) simulation results of the LNVGA II for 1000 samples: (a) Voltage gain and (b) noise figure                      | 54 |

| 3.25 | Post-layout Monte Carlo (process variation) simulation results of the LNVGA II for 1000 samples: (a) Gain tuning range and (b) third-order intercept point. | 55 |

| 3.26 | Post-layout Monte Carlo (process variation) simulation results of the LNVGA II for 1000 samples: Input match                                                | 55 |

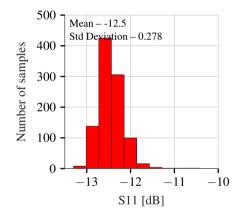

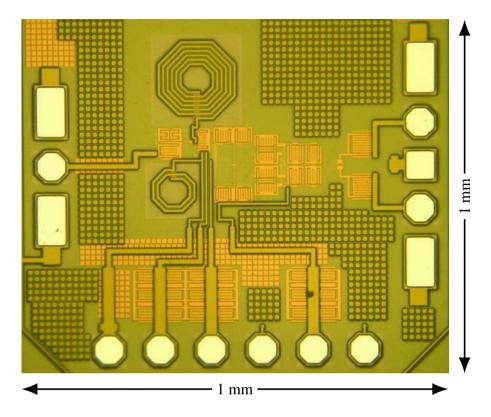

| 3.27 | Chip photograph of the LNVGA I                                                                                                                              | 56 |

| 3.28 | Chip photograph of the LNVGA II.                                                                                                                            | 57 |

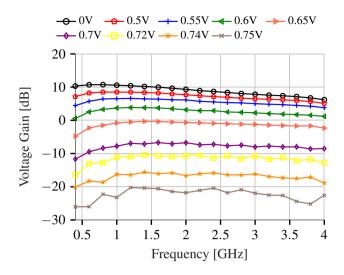

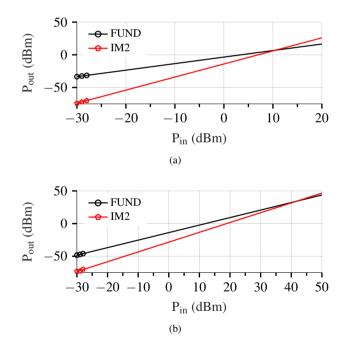

| 3.29 | Voltage gain variation with $V_{CTRL}$ across the entire band of the LNVGA I.                                                                               | 58 |

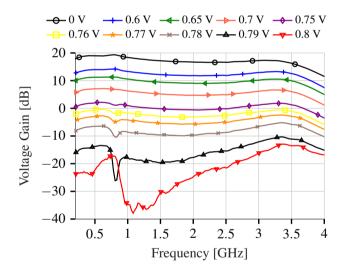

| 3.30 | Voltage gain variation with V <sub>CTRL</sub> across the entire band of the LNVGA II.                                                                       | 58 |

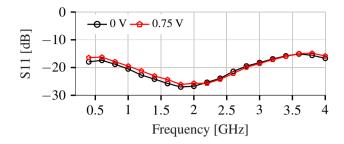

| 3.31 | S11 results at maximum gain and minimum gain of the LNVGA I. $\ . \ .$                                                                                      | 59 |

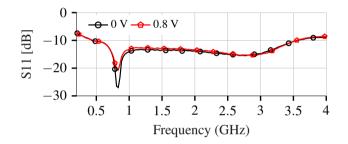

| 3.32 | S11 results at maximum gain and minimum gain of the LNVGA II                                                                                                | 59 |

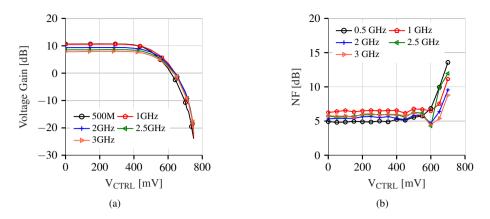

| 3.33 | The variation of the (a) voltage gain and (c) NF of the LNVGA I                                                                                             | 60 |

| 3.34 | The variation of the (a) voltage gain and (b) NF of the LNVGA II. $\ . \ .$                                                                                 | 60 |

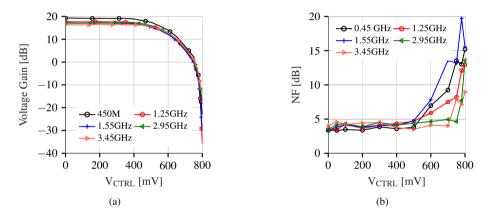

| 3.35 | The IIP3 and IP1dB variation within the gain levels of the LNVGA I.                                                                                         | 61 |

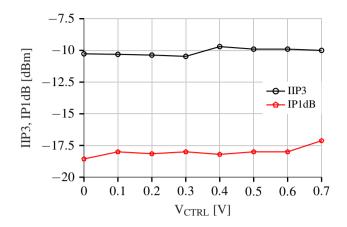

| 3.36 | The (a) maximum and (b) minimum IIP2 results of the LNVGA I                                                                                                 | 61 |

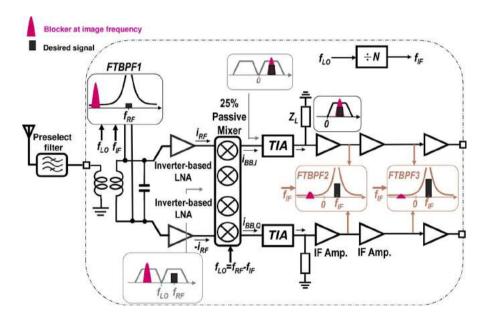

| 4.1  | High-IF receiver proposed in [71].                                                                                                                          | 65 |

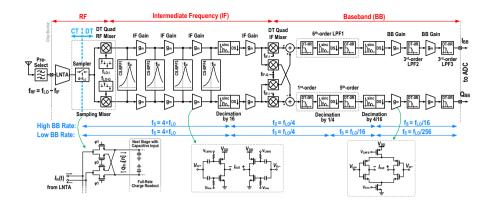

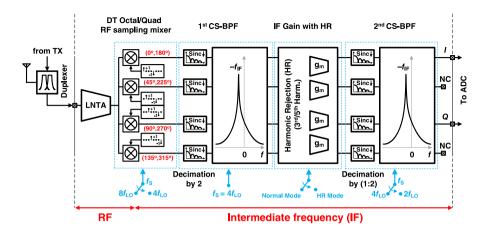

| 4.2  | High-IF receiver proposed in [88].                                                                                                                          | 67 |

| 4.3  | High-IF receiver proposed in [63].                                                                                                                          | 68 |

| 4.4  | High-IF receiver proposed in [56].                                                                                                                          | 69 |

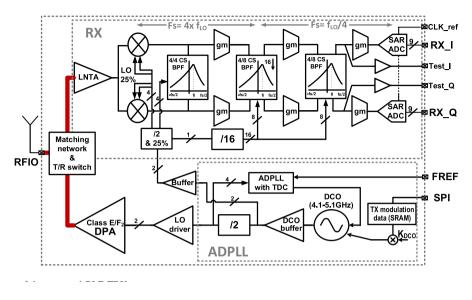

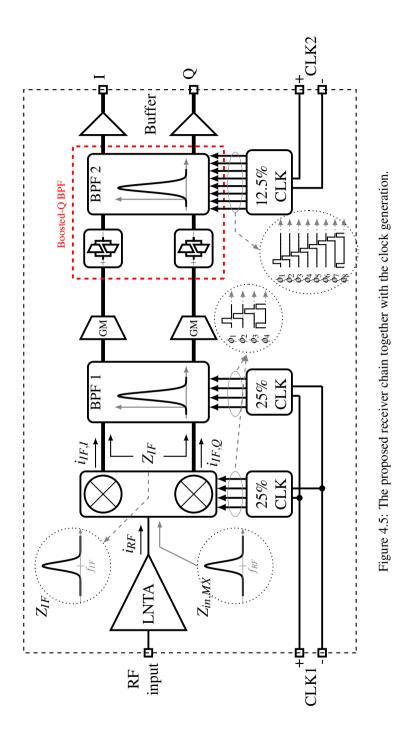

| 4.5  | The proposed receiver chain together with the clock generation. $\ldots$                                                                                    | 71 |

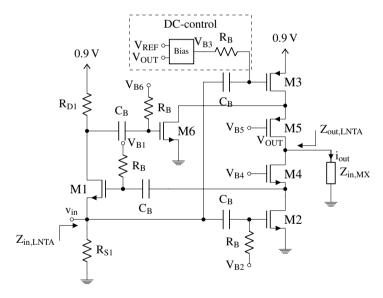

| 4.6  | The proposed LNTA topology.                                                                                                                                 | 72 |

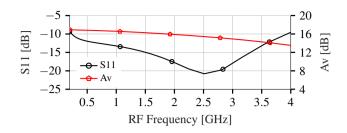

| 4.7  | The voltage gain and input reflection coefficient simulation results                                                                                        | 76 |

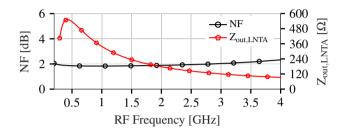

| 4.8  | The output impedance and noise figure simulation results                                                                                                    | 76 |

| 4.9  | LNTA post-layout results of S11                                                                                         | 76 |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

| 4.10 | LNTA post-layout results of voltage gain.                                                                               | 77 |

| 4.11 | LNTA post-layout results of NF.                                                                                         | 77 |

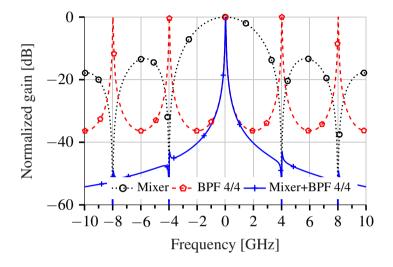

| 4.12 | Transfer Function of the mixer and BPF when $f_s = 4GHz$                                                                | 78 |

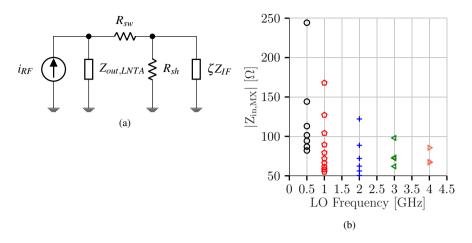

| 4.13 | (a) The passive mixer electrical model [5]. (b) The variation of the input impedance of the mixer with the LO frequency | 79 |

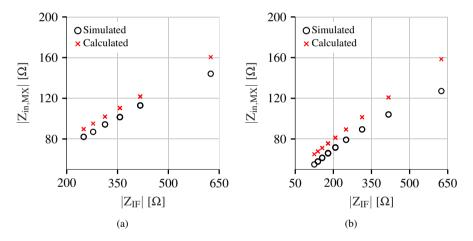

| 4.14 | The comparison of the calculated and simulated input impedance of the mixer at (a) 500 MHz and (b) 1 GHz                | 79 |

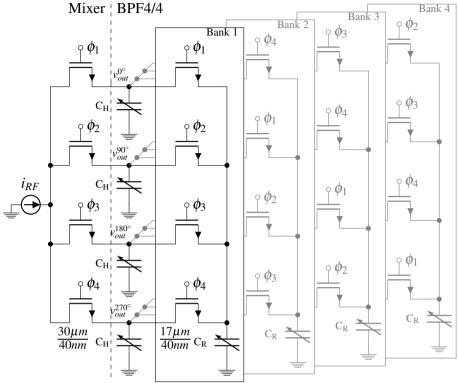

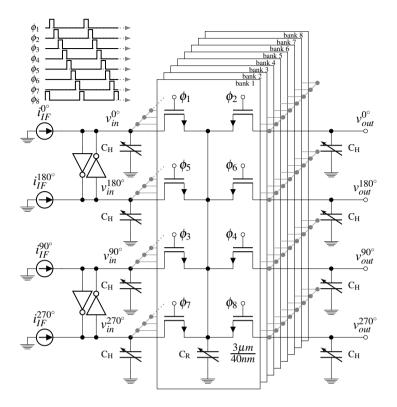

| 4.15 | Schematic of the passive mixer and the BPF 4/4                                                                          | 81 |

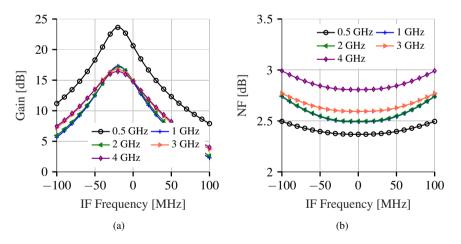

| 4.16 | (a) Voltage gain and (b) noise figure post-layout simulation results of combined LNTA, mixer and first filtering stage  | 83 |

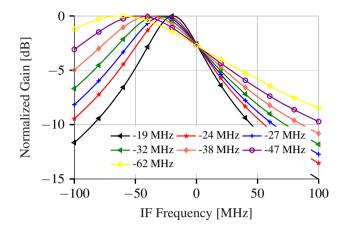

| 4.17 | Normalized transfer function sweeping the central frequency, which is shown at the legend.                              | 84 |

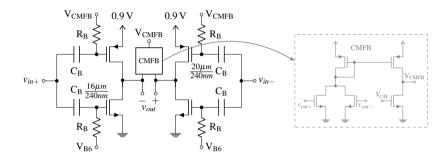

| 4.18 | The GM-cell.                                                                                                            | 85 |

| 4.19 | The BPF 4/8 modified circuit with implemented cross-connected transconductors.                                          | 86 |

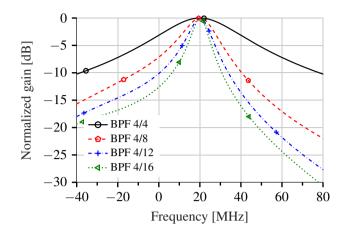

| 4.20 | Transfer function of the BPF 4/4, 4/8, 4/12, 4/16                                                                       | 87 |

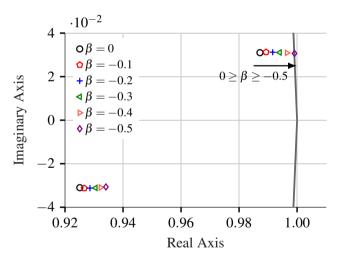

| 4.21 | Pole-zero mapping of the modified BPF 4/8 TF                                                                            | 88 |

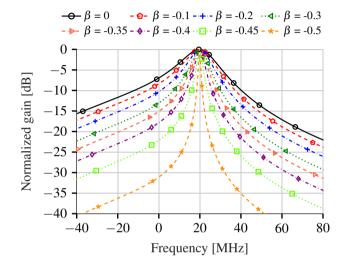

| 4.22 | Transfer function of the modified BPF 4/8, where $\beta$ is the cross-<br>connection gain                               | 89 |

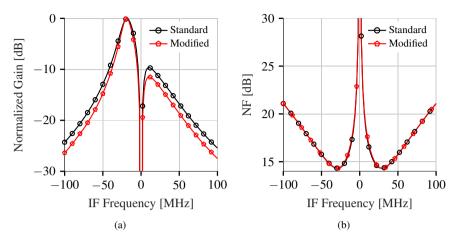

| 4.23 | (a) Normalized gain and (b) Noise figure of the standard and modified BPF 4/8 with $ \beta  = 0.2$ .                    | 90 |

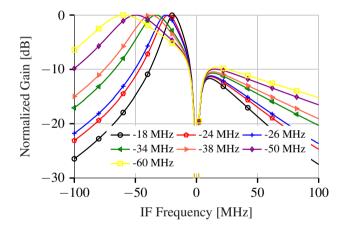

| 4.24 | Normalized transfer function of the modified BPF 4/8 sweeping the central frequency, which is shown at the legend.      | 90 |

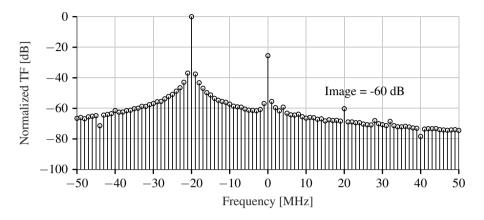

| 4.25 | Normalized transfer function.                                                                                           | 91 |

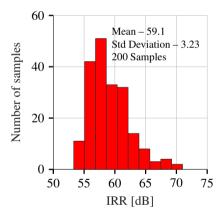

| 4.26 | IRR Monte Carlo (process variation) simulation results of the receiver.                                                 | 91 |

| 4.27 | The delay line, which converts the input sinusoidal wave to a square wave.                                              | 92 |

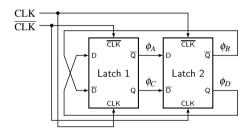

| 4.28 | The Frequency divider-by-2.                                                                                             | 92 |

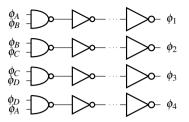

| 4.29 | The logic circuit that creates the 25% non-overlaping clock                                                             | 93 |

| 4.30 | (a) The latch and (b) the tristate inverter with a transmission gate $93$                                                                                                                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

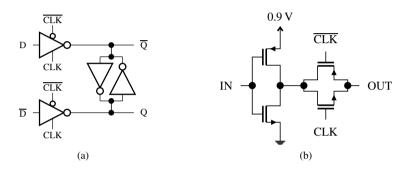

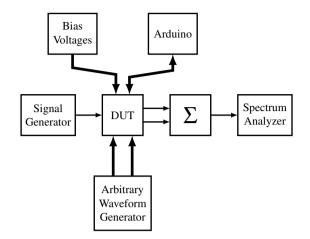

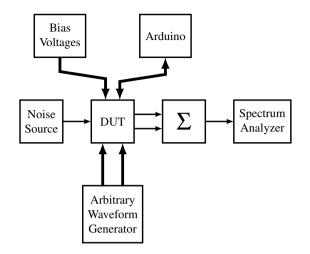

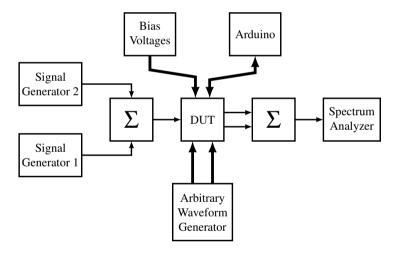

| 4.31 | Gain measurement setup                                                                                                                                                                             |

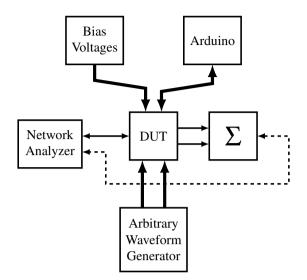

| 4.32 | Noise figure measurement setup                                                                                                                                                                     |

| 4.33 | IIP3/IIP2 measurement setup                                                                                                                                                                        |

| 4.34 | S-parameters measurement setup                                                                                                                                                                     |

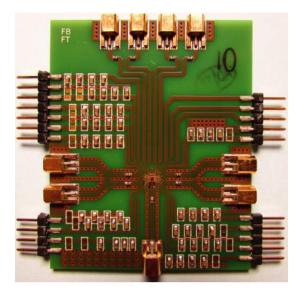

| 4.35 | Measurement PCB                                                                                                                                                                                    |

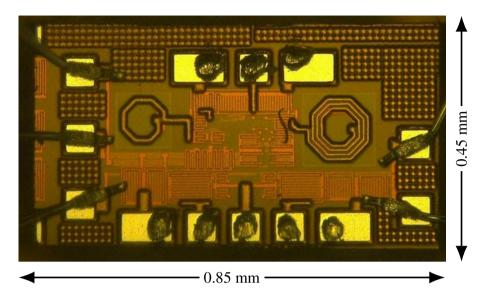

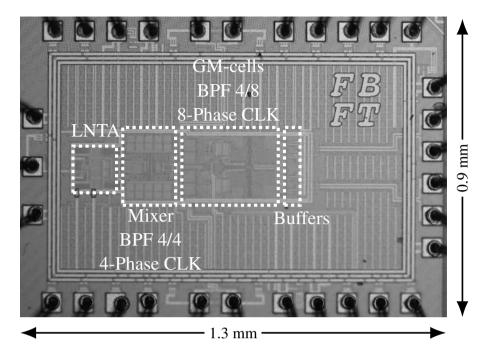

| 4.36 | Chip photograph                                                                                                                                                                                    |

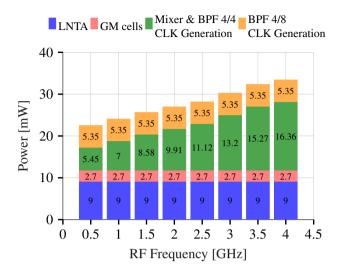

| 4.37 | Power budget                                                                                                                                                                                       |

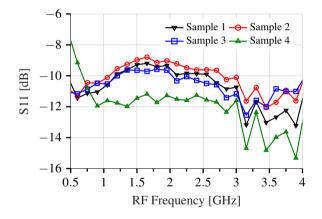

| 4.38 | S11 measurement results from four samples                                                                                                                                                          |

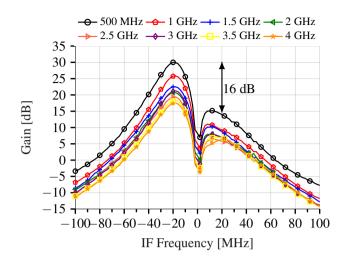

| 4.39 | Gain measured at the I path at different RF frequencies, the legend shows the LO frequency in which the measurement has been performed.100                                                         |

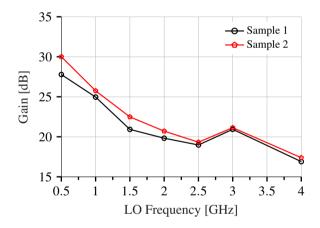

| 4.40 | Gain measurement results at the central frequency while the LO frequency is swept from 0.5 to 4 GHz                                                                                                |

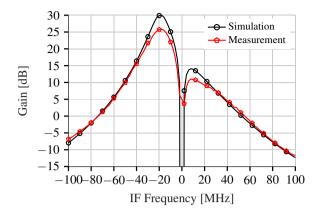

| 4.41 | Gain simulation results versus measurement results                                                                                                                                                 |

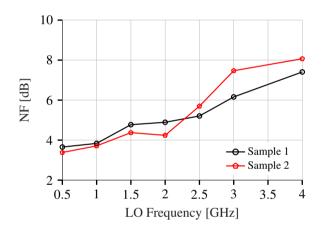

| 4.42 | Noise Figure measurement results at the central frequency while the LO frequency is swept from 0.5 to 4 GHz                                                                                        |

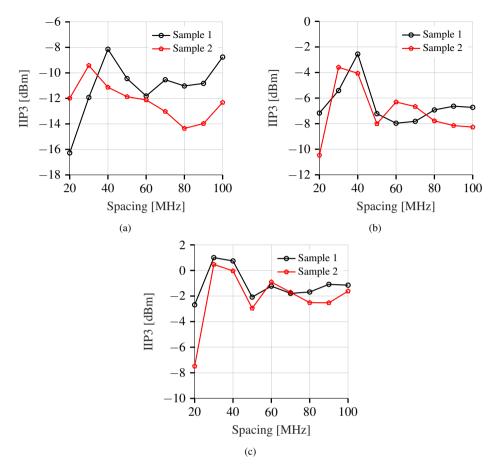

| 4.43 | The IIP3 measurement results at (a) 500 MHz, (b) 1 GHz, and (c) 2 GHz.102 $$                                                                                                                       |

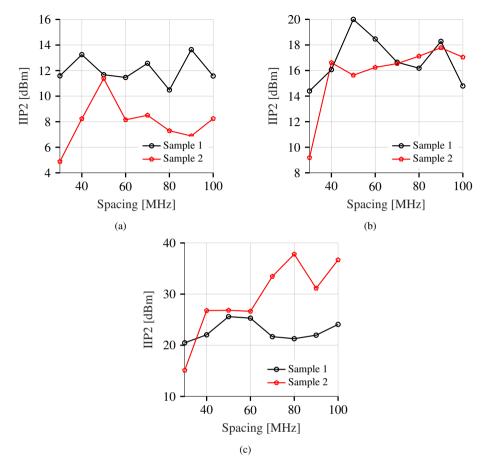

| 4.44 | The IIP2 measurement results at (a) 500 MHz, (b) 1 GHz, and (c) 2 GHz.103                                                                                                                          |

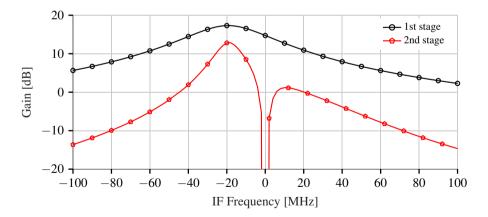

| A.1  | Post-layout simulation results of the first and second stages 111                                                                                                                                  |

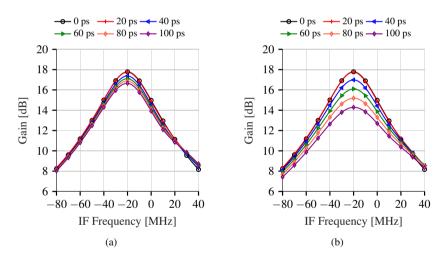

| A.2  | The gain drop when (a) the clock phase $\phi_1$ of the mixer is shifted forward, and (b) the clock phase $\phi_1$ of both the mixer and CS-BPF 4/4 are shifted forward                             |

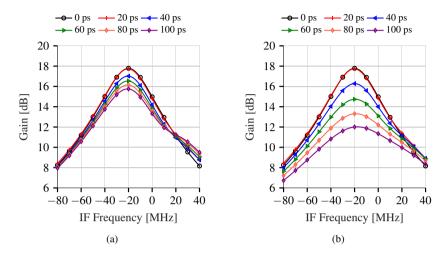

| A.3  | The gain drop when (a) the clock phases $\phi_1$ and $\phi_3$ of the mixer are shifted forward, and (b) the clock phase $\phi_1$ and $\phi_3$ of both the mixer and CS-BPF 4/4 are shifted forward |

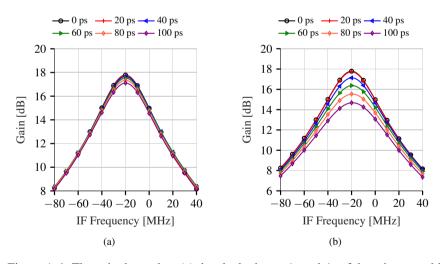

| A.4  | The gain drop when (a) the clock phases $\phi_1$ and $\phi_2$ of the mixer are shifted forward, and (b) the clock phase $\phi_1$ and $\phi_2$ of both the mixer and CS-BPF 4/4 are shifted forward |

| A.5  | The gain drop when the clock amplitude is reduced                                                                                                                                                  |

# List of Tables

| 2.1  | SNR values and sensing time for different sensing techniques [47]      | 12  |

|------|------------------------------------------------------------------------|-----|

| 2.2  | Path loss exponents for different environments [79]                    | 13  |

| 2.3  | SS receiver minimum received signal for WRAN, WiMax and LTE detection. | 13  |

| 2.4  | WRAN, WiMax, and LTE IP1dB for a spectrum-sensing receiver             | 15  |

| 2.5  | Estimated SS Receiver IIP3 requirements due to IM interference in dBm. | 16  |

| 2.6  | Estimated SS Receiver IIP2 requirements due to IM interference in dBm. | 16  |

| 2.7  | Maximum and minimum receiver power gain $(A_p)$                        | 17  |

| 2.8  | Spectrum-sensing receiver specification                                | 22  |

| 2.9  | Performance of state-of-art SS receivers                               | 23  |

| 2.10 | Budget of the specification                                            | 25  |

| 3.1  | LNVGA I transistors parameters                                         | 47  |

| 3.2  | LNVGA II transistors parameters.                                       | 47  |

| 3.3  | Simulation results of the LNVGAs                                       | 52  |

| 3.4  | LNVGA results in comparison with prior works.                          | 56  |

| 4.1  | LNTA sizing parameters.                                                | 75  |

| 4.2  | Receiver performance summary and comparison with other HIF receivers.  | 104 |

### Chapter 1

### Introduction

### 1.1 Motivation

The importance of wireless communication in our daily life has drastically increased over the last three decades thanks to the popularization of notebooks, tablets, and smartphones. The latter is, in fact, the main responsible for this wireless explosion. The number of cell phone subscriptions worldwide has risen by 133% over the last 10 years. In 2017, there were 7.7 billion subscriptions, whereas there were only 3.3 billion in 2007 [49]. In fact, there are already more subscriptions worldwide than people, with 1.03 subscription per person [49]. Moreover, 66.7% of the Earth population owns a cell phone, of those 54% owns a smartphone [40]. In addition to the number of users, the volume of data transferred is also rapidly increasing year by year. In order to attend this scenario of growing, new communication standards are emerging, and old standards are being expanded.

Conversely to an old cell phone that only connects with the base station, new wireless devices connect with many other devices, using a variety of wireless communication standards. For example, a modern smartphone supports the cellular (2G, 3G, 4G, etc.), WLAN (802.11a/b/g/n), WPAN (Bluetooth, Zigbee, etc.), broadcasting (DAB, DVB, DMB, etc.), and positioning (GPS) communication standards [44, 77]. Each of those standards is allocated within a band of the spectrum, which might differ from country to country. In addition to multiple bands, the wireless device must attend multiple specifications since each communication standard has an entirely different specification. Thus, the transceiver required for those applications must be not only portable but also multi-band and multi-standard.

The transceiver can be divided into three main parts: the receiver, the transmitter, and

the frequency synthesizer. The receiver and transmitter are responsible for receiving and transmitting the information, respectively, while the frequency synthesizer generates the clock frequencies needed within the radio transceiver for mixing with the incoming RF signal and also for mixing and converting to the ouput transmitter frequency RF band the outgoing baseband signal. The focus of this thesis are the blocks of the receiver; consequently, the discussion will be focused on the receiver hereafter.

### 1.2 Wideband receivers for multi-band and multistandard applications

A receiver is usually composed of a low-noise amplifier (LNA), one or more RF mixers, filters for the band and channel selections, a baseband variable-gain amplifier (VGA), and the analog-to-digital converter (ADC). The LNA is the first block of the receiver chain; thus, it must provide the impedance match with the antenna and reduce the noise figure of the entire system. The mixer down-converts the income signal to low frequencies so that it can be processed by the ADC. Both the band and the channel are selected using either a lowpass or a bandpass filter. Those filters can be either passive or active. The baseband VGA controls the gain of the receiver so that the signal delivered to the ADC does not have a significant variation in amplitude, and stays within the dynamic range and full-scale range acceptable for the ADC. Finally, the ADC converts the analog signal to the digital domain.

Figure 1.1: Multi-band/multi-standard receiver using multiple receivers [44, 77].

The most straightforward implementation of a multi-band/multi-standard receiver is one chip or, alternatively, one entire block in the receiver chip, per communication standard, like presented in figure 1.1. Since only the receiver block that is working is turned on, this approach can be very power efficient. Nevertheless, it requires multiple chips, or at least multiple blocks in a larger chip, which is not efficient from both the area and the design perspectives since each chip needs be designed individually. On top of that, every time a new communication standard is created the chip needs to be replaced.

Figure 1.2: Multi-band/multi-standard receiver using multiple RF front-ends and sharing the baseband [44, 77].

Figure 1.2 shows a more efficient approach and the most common one [44]. It shares the baseband circuits, while the RF front-end circuits are replicated one per standard. In this case, since both the channel selection filter and the ADC must cope with all the communication standards, the blocks must be able to adjust their parameters to the communication standard in use. Although more complex than the first approach, this option reduces chip area, which reduces the overall cost, eventually. The inclusion of new communication standards or the modification of an old one still requires the replacement of the chip.

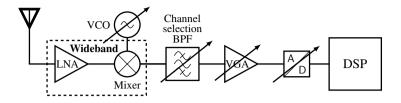

Another possible multi-band/multi-standard receiver is shown in figure 1.3, in which all the blocks are shared and can be adjusted to different communication standards. This block diagram is an example of software-defined radio (SDR). In order to share the RF front-end circuits, these circuits must be designed either with a tunable band or a wide band. The former changes its central frequency accordingly to the band in use, while the latter covers all the bands of interest. Although both approaches are possible, the

Figure 1.3: Multi-band/multi-standard receiver using a single receiver [44, 77].

research focus has been on SAW-less wideband receivers for SDR due to the pressure for cost reduction and universality of new wireless devices [65, 81, 61]. Currently, wideband RF techniques are the main direction for the design of multi-band/multi-standard receivers [61].

A SAW-less wideband receiver must have a low noise figure (NF), a high second and third order linearity, a high resilience to blockers, a wideband impedance match, and minimum external components, which poses a significant challenge to the RF circuits designers [61, 63, 15]. Indeed, blockers are the most significant threat to a SAW-less receiver since, without RF pre-filtering, a strong signal (e.g., 0 dBm) goes directly into the receiver desensitizing it, which deteriorates the receiver sensitivity. Also, the low supply voltage of new CMOS technologies aggravates the problem.

The wideband receivers can be divided into two groups: the ones with LNA [81, 71, 15, 93, 89, 63] and the ones without LNA (i.e., mixer first topology) [6, 73, 4, 60, 74, 58]. The mixer first receivers show a higher resilience to blockers than the LNA receivers. However, they are unable to achieve a low NF except for [73, 74, 58], which deliver a low NF but at the cost of a large area and high power consumption. On the other hand, the LNA receivers can achieve a very low NF with reasonable power consumption, but their 0 dBm blocker NF is 10 dB larger than that of the mixer first receivers [63].

So far, both approaches can achieve high performance but also have issues to solve. Even though it is not yet possible to surely state which is the best topology for wideband receivers, there are four techniques [61] presented in the previously cited works that will be probably part of them. Firstly, the noise canceling technique [17], which has been initially proposed to reduce the noise of LNAs and extrapolated to the receiver level in [73, 74]. This first technique has proven to be a sound technique to achieve a low NF within a wide band. Secondly, the N-path filtering [36], which was proposed in the 60's, has been successfully applied to design on-chip bandpass filters [96, 37, 71, 89, 64, 63]. Eventually, even high quality-factor (Q-factor) bandpass filters are achievable with N-path filtering [71]. Thirdly, the N-path passive mixer has been extensively used in previous designs. In fact, only [60] still uses an active mixer. Despite the lack of gain, the passive mixer under hard switching can have a low NF in addition to be an extremely linear circuit [5]. Finally, harmonic recombination has proven to be an

efficient way to reduce the intermodulation products. It must be applied in combination with the N-path mixing since it needs multiple paths with a different phase shift. Those paths are weighted and added in such way that the harmonics are canceled [81].

Due to the high importance of wideband blocks to those multi-band/multi-standard receivers, this thesis focuses on the design of such blocks. Although the projects developed in this thesis were done for two different CMOS technologies, and are not directly integrated all in the same silicon die for cost reasons. They are all aligned with multi-band/multi-standard applications.

#### **1.3** Outline of this thesis

This thesis is structured as follows. Chapter 2 presents the first project, which aims at the specification of a wideband receiver for spectrum sensing of cognitive radio (CR). This work was part of the Cognitive Radio Project developed at the Federal University of Rio Grande do Sul (UFRGS), in which the purpose was the application of CR in a band wider than the one specified in the standard IEEE 802.22. Several masters and Ph.D. students were involved in this project, and this specification was used as a guideline in some of their designs [95, 23]. The CR design project at UFRGS was discontinued in late 2013, and silicon implementations for its modules were only in part finalized in 130nm CMOS, due to the complete absence of commercial interest (and financial support) for CR application. Nevertheless, this specification gives an overview of the challenges of RF wideband circuit design.

In the following chapters, the focus is moved to the circuit design of wideband blocks. In chapter 3, the design of two low-noise variable-gain amplifiers (LNVGA) in 130 nm CMOS are presented and discussed. The advantage of having a variable gain in the first stage of the receiver is to avoid signal compression. Whenever a strong signal arrives at the receiver, it can be attenuated, preventing the compression of the following blocks. This feature is particularly useful in a multi-standard application since there could be a considerable power variation between standards.

In chapter 4, the design of a discrete-time (DT) high-IF receiver in 40 nm CMOS is presented and discussed. This last design, encompassing an low-noise transconductance amplifier (LNTA), a mixer, and the band selection filtering, takes advantage of the CMOS technology evolution which allows for high-speed switches. Hence, the mixer and filters are designed with switched-capacitors circuit techniques, which enhance the performance of the passive mixer selected for the front-end and allow for the design of integrated charge-sharing (CS) bandpass filters (BPF), i.e., N-path filtering.

Finally, chapter 5 concludes this thesis, summarizes the main contributions, and proposes future work.

### Chapter 2

# A Spectrum-Sensing Receiver specification

### 2.1 Introduction

At the beginning of the 2000's, the spectrum scarcity became the central concern since the spectrum is a limited resource and the demand for wireless services were sharply rising [30, 24].

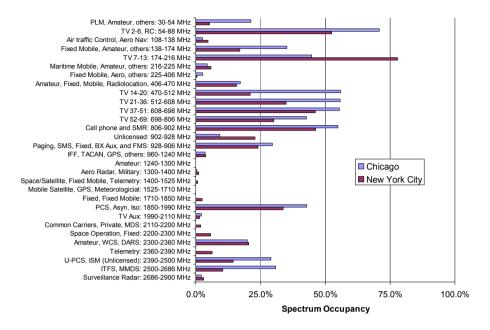

In 2002, the American Federal Communications Commission (FCC) made a limited measurement of spectrum use in certain USA urban areas, allowing for a partial view of the real spectrum usage [30]. During 2004 and 2005, the Shared Spectrum Company (SCC) did measurements of spectrum usage in several USA cities such as New York and Chicago [67, 68]. These measurements, which are presented in figure 2.1, show that the spectrum utilization was well below 100% of the sampled time. Those reports conclude that the problem is not only the congestion of the spectrum but its potentially poor usage too.

As a solution to that problem, the deployment of dynamic spectrum access (DSA) networks have been proposed, which opportunistically use the licensed spectrum without interfering with the licensed signals. This kind of system, however, is only feasible for radios that are aware of their surroundings and highly configurable such as the cognitive radio (CR) since it needs to change the operation parameters continuously [2].

The CR is a radio that can change the transmission and reception parameters based on the interaction with the environment in which it operates [21]. Hence, it must be able

Figure 2.1: The spectrum occupation in New York and Chicago [67, 68].

to sense the spectrum information from its surrounding environment and to operate at several frequencies with different transmission standards [43, 87, 50, 2, 18].

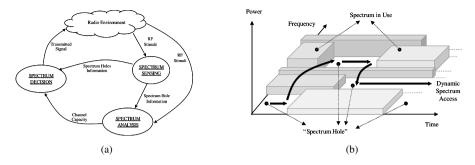

The operation is divided into the spectrum sensing, analysis, and decision like is presented in figure 2.2a. First, the CR evaluates the spectrum. Second, it analyzes the data collected in the previous phase. Finally, it selects the operation parameters according to the spectral characteristics and user requirements.

The CR classifies the regions of the spectrum in either vacant or occupied. It is imperative that the CR operates only in the vacant regions. Thus, it updates this classification continuously. Also, this process must be fast and precise to avoid interference with other users. As soon as the primary user appears in the band in use by the CR, the CR must quickly tune itself to another spectrum region to avoid interference as shown in Fig 2.2b [43, 2].

The spectrum sensing (SS) receiver is a key block for the CR since it is responsible for the spectrum classification. The SS is called as digital when only the digital signal processing (DSP) does the channel classification. On the other hand, when the analog front-end partially or entirely does the classification, the SS is called analog.

The main difference between the SS and the primary receiver (i.e., the one used

Figure 2.2: (a) The Cognitive cicle and (b) CR operation [2].

for actual communication) is their resilience to signal corruption. In contrast to the primary receiver, the SS receiver can still perform its detection task despite some signal corruption, so the requirements of noise and linearity are relaxed for the SS receiver. In fact, the acceptable signal-to-noise ratio (SNR) of the SS receiver is limited by the detection time and the coverage region, whereas the SNR of the primary receiver is limited by the bit-error-rate (BER).

### 2.2 The cognitive radio today

The cognitive radio (CR) drew a lot of attention during the last decade thanks to its exciting proposal of dynamically accessing the spectrum. In 2011, the first standard enabling CR deployment was published by IEEE. The IEEE 802.22 (WRAN) [47] has proposed the utilization of CR in the analog TV band to provide broadband wireless access in low population density areas, covering large regional distances (wider than typical cellular base-stations coverage), which are typically rural areas. However, this standard has never attracted the vital commercial interest and, eventually, the high-speed wireless communications standards for cell phones have reached those rural regions.

In late 2014, the WRAN working group initiated a project to broaden the spectrum sharing beyond TV bands [99]. In spite of that last effort, the research interest in circuits for CR faded. In the end, it was overshadowed by the research on SDR, which is similar to the CR but for the spectrum awareness. Although there is still some research related to the IEEE 802.22 and CR, the most recent publications are related to the MAC layer [42, 12].

Regarding spectrum sensing receivers, there are also few publications in the last 5 years. The most recent ones are [55, 52, 7].

### 2.3 The receiver specification

The specification of the SS receiver was part of the cognitive radio project at UFRGS, which aimed for the application of cognitive radio into a broader band than that of the IEEE 802.22. Until 2012, the cognitive radio application was limited to the analog TV bands. However, there was plenty of poorly used spectrum besides the TV band in which the CR could be explored [38].

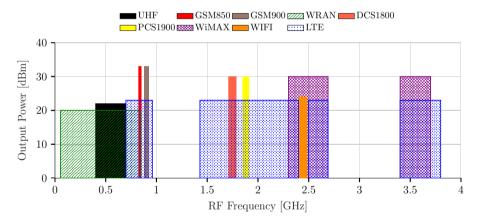

Therefore, the RF band has been extended up to 3.8 GHz. With the extension of the RF band to the span of 50MHz to 3.8GHz, this radio would be able to cover the spectrum region with the best propagation conditions. Since the purpose is also a multi-standard receiver, three communication standards have been selected to be detected, WRAN (Wireless rural area network) [47], WiMax (IEEE 802.16) [46], and LTE [32]. We have considered other communication standards within this band as interferers. Among all the possible interferers, we have selected for the calculation the UHF wireless microphone [33], GSM850 [31], GSM900 [31], PCS1900 [31], DCS1800 [31], and WiFi [45] signals. Since those signal came all from portable devices, they ought to be most common interferers. Figure 2.3 shows a representation of the spectrum considered for the considered communication standards.

Figure 2.3: Maximum allowed output power and RF band of the communication standards considered in the specification [47, 46, 32, 33, 31, 45].

### 2.3.1 Frequency band

The frequency band of this SS receiver has to cover the standards WRAN, WiMax, and LTE, which are the signals to be detected. The WRAN band stretches from 54 to 842 MHz. In contrast, the WiMax and LTE bands are not composed of one single frequency band, several narrow frequency bands. The frequency bands that belong to the WiMax standard are located between 2.3 GHz and 11 GHz, while those of the LTE standard are located between 699 MHz and 3.8 GHz.

The spectrum sharing is a worthwhile feature within the crowded regions of the spectrum which is below 4 GHz. Although there are WiMax bands up to 11 GHz, it is not necessary to share the spectrum at frequencies above 4 GHz since this part of the spectrum is far from crowded. Moreover, the spectrum-sensing receiver needs to cover a wide band so that the possibility of finding a free frequency range for opportunistic CR operation is boosted. Thus, the design frequency band spans from 54 MHz up to 3.8 GHz.

### 2.3.2 Signal-to-noise ratio

The SNR is the comparison of the desired signal and the background noise that is given by [80]

$$SNR_{out} = \frac{E_b}{N_0} \cdot \frac{BR}{NEB},$$

(2.1)

where  $E_b/N_0$ , BR, and NEB stand for the energy per information bit over noise powerspectral-density, the bit-rate in bps, and the noise-equivalent-bandwidth respectively. The ratio  $E_b/N_0$  is proportional to the bit error rate (BER) and the type of signal modulation specified in the standard, the BR is close to the conversion rate of the analog-to-digital converter (ADC), and the NEB is equal to the channel bandwidth. Hence, improving the SNR also improves the BER. In contrast, when the receiver aims for the signal detection instead of the signal reception, the SNR is defined by the probabilities of detection and false alarm. The detection event is the correct classification of an occupied channel. Meanwhile, the false alarm event is the wrong classification of either a vacant or an occupied channel [51].

The relation of those probabilities and the SNR depends on the detection technique used by the SS receiver to classify the channels as vacant or occupied. The relationship between some detection methods and SNR have been presented in [47], and it is presented in table 2.1.

The detection methods are divided into two classes: the blind methods, which do not depend on specific signal features, and specific methods, which do rely on specific

signal features. The blind methods are the first three in table 2.1, whereas the others are specific techniques.

The blind methods of sensing are faster but less accurate than the specific ones. For example, the multi-resolution sensing method detects a signal in 0.1 ms, but it requires a -3 dB SNR. On the other hand, the FFT-based pilot detects a signal in 5 ms, but it does the detection with a -18 dB SNR. Since the methodologies of signal detection are not the focus of this work, we are just going to select the SNR values within table 2.1. Furthermore, the various sensing techniques are not going to be discussed here.

| Sensing Techniques   | Max. SNR<br>[dB] | Min. Sensing time<br>[ms] | Min. SNR<br>[dB] | Max. Sensing time<br>[ms] |

|----------------------|------------------|---------------------------|------------------|---------------------------|

| Energy               | -11              | 0.2                       | -18              | 5                         |

| Eigenvalue           | -10.5            | 4                         | -15.8            | 32                        |

| Multi-resolution     | -3.19            | 0.1                       | -24.47           | 16                        |

| Field-sync           | -6               | 24.2                      | -12              | 24.2                      |

| Segment-sync         | -7               | 4.06                      | -13              | 92.5                      |

| FFT-based pilot      | -18              | 5                         | -24.5            | 50                        |

| Dual FPLL pilot      | -12.42           | 50                        | -14.88           | 75                        |

| Spectral correlation | -7               | 0.333                     | -29              | 10                        |

| ATSC cyclostationary | -21              | 19.03                     | -31              | 19.03                     |

Table 2.1: SNR values and sensing time for different sensing techniques [47].

### 2.3.3 Sensitivity

Sensitivity is the minimum signal power that a receiver detects with acceptable quality, which means the SNR needs to be sufficiently large so that the ADC correctly converts the analog signal.

Apart from the WRAN standard, the communication standards do not specify the sensitivity for spectrum-sensing since spectrum-sharing is not allowed. Therefore, this information is estimated based on the transmitted power, cell radius, and frequency band. The log-distance path loss model [79] gives a reasonable estimation of the received signal power. This model is estimated by

$$P_{RX} = P_{TX} - 20\log\left(\frac{4\pi f d_0}{c}\right) + n \, 10\log\left(\frac{d_0}{d}\right),\tag{2.2}$$

where  $P_{RX}$ ,  $P_{TX}$ , f, c, n,  $d_0$ , and d are the received signal power, the transmitted signal power, the frequency, the light speed, the path loss exponent, the reference distance, and the separation from the transmitter to the receiver respectively.

The minimum  $P_{RX}$  is equivalent to the receiver sensitivity. The value of *n* defines the environment where the transmission/reception takes place. For instance, *n* has values from 2.7 and 3.5 in urban areas, while *n* is 2 in free space. Table 2.2 shows the values of *n* for different environments. The transmitter was considered at the center of the cell. Hence, the separation of transmitter and receiver sets the coverage radius of the spectrum-sensing. Table 2.3 shows the minimum received signal power that has been calculated using 2.2 in addition to the information mentioned above.

Table 2.2: Path loss exponents for different environments [79].

| Environment                        | n              |

|------------------------------------|----------------|

| Free space                         | 2              |

| Urban area cellular radio          | $2.7\sim 3.5$  |

| Shadowed urban area cellular radio | $3\sim 5$      |

| In building line-of-sight          | $1.6 \sim 1.8$ |

| Obstructed in building             | $4\sim 6$      |

| Obstructed in factories            | $2\sim 3$      |

Table 2.3: SS receiver minimum received signal for WRAN, WiMax and LTE detection.

|       | $P_{TX}$ [dBm] | d [km] | n | f [GHz] | $P_{RX,min}$ [dBm] |

|-------|----------------|--------|---|---------|--------------------|

| WRAN  | 20 [47]        | 2      | 3 | 0.862   | -110               |

| WiMax | 30 [46]        | 1.5    | 3 | 3.7     | -109               |

| LTE   | 23 [32]        | 1      | 3 | 3.8     | -111               |

### 2.3.4 Noise Figure

The Noise Figure (NF) that is the representation of the noise factor (F) in dB quantifies the noise added by the circuit to the signal. F is given by

$$F = \frac{SNR_{in}}{SNR_{out}},\tag{2.3}$$

where  $SNR_{in}$  and  $SNR_{out}$  are SNR at the input and output respectively. The relation between a receiver sensitivity and its NF is given by

$$P_{RX,min} = 10\log\left(kTB\right) + SNR_{out} + NF,$$

(2.4)

where  $P_{RX,min}$  is the receiver sensitivity, k is the Boltzmann constant, T is the absolute temperature, and B is the channel bandwidth in Hz.

The eq. (2.4) shows that as the SNR increases either a lower NF is needed or the coverage area (i.e. the distance of the RX to the transmitter) has to be reduced. On the other hand, the reduction of the SNR slows down the detection since the signal is buried in noise. The first alternative forces the designer to reduce the system linearity to improve the NF, whereas the second one may cause harmful interference to the primary users since the detection will not be fast enough. Therefore, the minimum SNR is -20 dB that relaxes the NF requirement.

The WRAN standard proposes a 50 MHz channel for the spectrum sensing operation. Thus, this value has been used in calculations further in this section on SS.

The NF required for each one of the wireless system signals has been calculated using eq. (2.4) and the considerations mentioned above. The receiver NFs are 6.9 dB, 7.8 dB, and 6 dB for the standards WRAN, WiMax, and LTE respectively. These values are replaced in the Friis equation,

$$F = 1 + (F_1 - 1) + \frac{(F_2 - 1)}{A_{p1}} + \dots + \frac{(F_m - 1)}{A_{p1} \dots A_{p(m-1)}},$$

(2.5)

where  $F_n$  is the noise factor for each stage and  $A_{Pn}$  is their respective available power gain, so the NF specification for each block of the circuit is calculated.

### 2.3.5 Linearity

The circuit linearity is defined by the interferers present inside the band and by the power of the received signal. The interferers may harm the incoming signal due to intermodulation, cross modulation, and desensitization. Meanwhile, the power of the received signal may create gain compression or desensitization.

There are three most common methods to evaluate the system linearity: the 1 dB input compression point (IP1dB), the input third-order intercept point (IIP3), and the input second-order intercept point (IIP2).

The IP1dB is the input power at which the gain drops by 1 dB, and it detects gain compression and desensitization. Indeed, both gain compression and desensitization saturate the receiver, but their causes are different. The former is the consequence of a strong incoming signal, while the latter is the result of a strong blocker at frequencies close to that of the incoming desired signal.

The gain compression is a major problem whenever the modulation scheme contains information in the amplitude since this information will be distorted when the receiver is saturated. The desensitization, on the other hand, is an issue regardless of the modulation scheme. Even with a small input signal, the blocker saturates the receiver that reduces the gain. Consequently, the SNR at the receiver output is lowered, which becomes a critical issue for the receiver.

Since the receiver is a nonlinear system, any two signals that are applied to the system create components at frequencies that are not harmonics of those input frequencies. These components are the intermodulation (IM) products. Whenever one of these IM products falls onto the reception channel, it corrupts the incoming signal.

The consequence of IM in the reception is evaluated with the intercept point, which is the point in which the intermodulation (IM) product is equal to the fundamental tone. In the case of the second-order IM product (IM2) and third-order IM product (IM3), those points are named IIP2 and IIP3 respectively.

The selected signals, WRAN, WiMax, and LTE, use orthogonal frequency division multiplexing (OFDM), which is a popular scheme for wideband communication. Due to the subcarriers interaction, the OFDM shows a significant amplitude variation. Thus, the calculation of IP1dB needs to take into account the signal peak-to-average power ratio (PAPR). The PAPR of signals with a large number of subcarriers is [26]

$$PAPR \le 2\ln(N), \tag{2.6}$$

where N is the number of subcarriers. Therefore, IP1dB is

$$IP1dB = P_{RX,max} + PAPR_{[dB]}, \qquad (2.7)$$

where  $P_{RX,max}$  is the maximum signal power in dBm that the receiver can detect. Table 2.4 shows the calculated IP1dB for the receiver.

|       | Ν    | PAPR (dB) | P <sub>RX,max</sub> (dBm) | IP1dB (dBm) |

|-------|------|-----------|---------------------------|-------------|

| WRAN  | 2048 | 11.8      | -41.8 [14]                | -29.7       |

| WiMax | 256  | 10.44     | -30 [46]                  | -19.5       |

| LTE   | 1200 | 11.8      | -25 [32]                  | -13.2       |

Table 2.4: WRAN, WiMax, and LTE IP1dB for a spectrum-sensing receiver.

Due to the extended bandwidth of the receiver this thesis is focusing on, the interferers enter into the system without any filtering. Thus, the IM products created by those interferers can severely harm the incoming signal. The IIP2 and IIP3 are calculated by

$$IIP2 = 2P_{int} - IM2 \tag{2.8}$$

and

$$IIP3 = \frac{3P_{int} - IM3}{2} \tag{2.9}$$

respectively, where  $P_{int}$  is the interferer power at the receiver input. The IM2 and IM3 have been set to the receiver total integrated noise [80],

$$IM3 = IM2 = 10\log(kTB) + NF.$$

(2.10)

The power of each interferer has been estimated using (2.2). Like in section 2.3.3, the *n* is set to 3. The separation interferer-receiver has been set to 15 meters for all interferers apart from WRAN interferer, which has been set to 30 meters. The calculated IIP3 and IIP2 are presented in table 2.5 and table 2.6 respectively.

WRAN WiMax LTE UHF **GSM850 GSM900** WiFi WRAN -1.1 -22.5 -17.5 -14.7-4.2 -5.7 -38 WiMax -1.6 -22.9 -17.8-15 -4.63 -6.2 -38.8 -21.9 -5.2 LTE -0.6 -16.9 -14.1 -3.7 -23.2

Table 2.5: Estimated SS Receiver IIP3 requirements due to IM interference in dBm.

Table 2.6: Estimated SS Receiver IIP2 requirements due to IM interference in dBm.

|       | WRAN | WiMax | LTE | UHF  | GSM850 | GSM900 | WiFi  |

|-------|------|-------|-----|------|--------|--------|-------|

| WRAN  | 28.5 | 0     | 6.7 | 10.5 | 24.4   | 22.4   | -20.7 |

| Wimax | 27.6 | -0.8  | 5.8 | 9.55 | 23.5   | 21.5   | -21.6 |

| LTE   | 29.6 | 1.1   | 7.8 | 11.5 | 25.5   | 23.4   | -0.5  |

The most demanding values of IP1dB, IIP2, and IIP3 for the 3 standards considered are -13.2, 29.6, and -0.6 dBm respectively. The IIP3 is the most severe linearity requirement since the system is wideband. Hence, there are a lot of pairs of interferers that can generate IM products that fall onto the channel.

The intercept point (IIPn) of each block of the receiver has been calculated with the cascade equation

$$\frac{1}{HPn^2} \approx \frac{1}{HPn_1^2} + \frac{A_{p1}^2}{HPn_2^2} + \dots + \frac{A_{p1}^2 \dots A_{p(m-1)}^2}{HPn_m^2}.$$

(2.11)

Also, the IP1dB of each block has been calculated with the same equation but replacing IIPn for the IP1dB.

### 2.3.6 Gain