# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# JEFERSON JOSÉ BAQUETA

# **Evaluation of using MIGFET Devices in Digital Integrated Circuit Design**

Dissertation presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Renato Perez Ribas Advisor.

# CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Baqueta, Jeferson José

Evaluation of using MIGFET Devices in Digital Integrated Circuit Design / Jeferson José Baqueta. – 2017.

113 f.:il.

Adivisor: Renato Perez Ribas;

Dissertation (Master) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2017.

1. Digital Circuits. 2. Emerging Technologies 3. MIGFET 4. Adders 5. Cell libraries 6. Nanotechnology I. Ribas, Renato Perez. III. Evaluation of using MIGFET Devices in Digital Integrated Circuit Design.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Prof. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretor do Instituto de Informática: Prof. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: João Luiz Dihl Comba

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **ACKNOWLEDGEMENTS**

Gostaria de agradecer primeiramente a minha a minha mãe, Roseni, e ao meu pai Anito, por todo o apoio que recebi durante esses dois anos de mestrado. Cheguei até aqui devido ao incentivo que recebi de vocês.

Agradeço a minha namorada Aline que esteve ao meu lado durante todo o mestrado, agradeço pelo companheirismo, compreensão e principalmente por estar sempre disposta a me ouvir e me incentivar nas horas difíceis.

Quero agradecer também a todos os colegas do Logics pela paciência e por toda a ajuda que me ofereceram durante esses dois últimos anos. Irei lembrar de cada um e levarei comigo todos os conhecimentos recebidos de vocês.

Gostaria de agradecer ao meu orientador o Professor Renato Perez Ribas pela paciência, compreensão e amizade, o que com certeza fez toda a diferença para o desenvolvimento desse trabalho.

E finalmente, agradeço a todos que diretamente ou indiretamente contribuíram para mais essa conquista.

## Avaliação do Uso de Dispositivos MIGFET no Projeto de Circuitos Integrados Digitais

#### **RESUMO**

A diminuição das dimensões do transistor MOS tem sido a principal estratégia adotada para alcançar otimizações de desempenho na fabricação de circuitos integrados. Contudo, reduzir as dimensões dos transistores tem se tornado uma tarefa cada vez mais difícil de ser alcançada. Nesse contexto, vários esforços estão sendo feitos para encontrar dispositivos alternativos que permitam futuros avanços em relação à capacidade computacional. Entre as mais promissoras tecnologias emergentes estão os transistores de efeito de campo com múltiplos e independentes gates (MIGFETs). MIGFETs são dispositivos controlados por mais que um terminal de controle permitindo que funções Booleanas com mais de uma variável sejam implementadas por um único dispositivo. Redes de chaves construídas com dispositivos MIGFET tendem a ser mais compactas do que as redes de chaves tradicionais. No entanto existe um compromisso em relação a redução no número de chaves, devido à maior capacidade lógica, e um maior tamanho e pior desempenho do dispositivo. Neste trabalho, pretendemos explorar tal balanceamento no sentido de avaliar os impactos do uso de MIGFETs na construção de circuitos integrados digitais. Dessa forma, alguns critérios de avaliação são apresentados no sentido de analisar área e atraso de circuitos construídos a partir de dispositivos MIGFET, onde cada transistor é representado por um modelo RC. Em particular, tal avaliação de área e desempenho é aplicada no projeto de circuitos somadores binários específicos (metodologia full-custom). Além do mais, bibliotecas de células construídas a partir de dispositivos MIGFET são utilizadas na síntese automática de circuitos de referência através da metodologia standard-cell. Através dos experimentos, é possível terse uma ideia, mesmo que inicial e pessimista, do quanto o layout de um dado MIGFET pode ser maior do que um single-gate FinFET e ainda apresentar redução na área do circuito devido à compactação lógica.

**Palavras-chave**: Circuitos digitais, tecnologias emergentes, MIGFET, somadores, bibliotecas de células, nanotecnologia.

## **Evaluation of using MIGFET Devices in Digital Integrated Circuit Design**

### **ABSTRACT**

The scaling of MOS transistor has been the main manufacturing strategy for improving integrated circuit (IC) performance. However, as the device dimensions shrink, the scaling becomes harder to be achieved. In this context, much effort has been done in order to develop alternative devices that may allow further progress in computation capability. Among the promising emerging technologies is the multiple independent-gate field effect transistors (MIGFETs). MIGFETs are switch-based devices, which allow more logic capability in a single device. In general, switch networks built through MIGFET devices tend to be more compact than the traditional switch networks. However, there is a tradeoff between the number of logic switches merged and the area and performance of a given MIGFET. Thus, we aim to explore such a tradeoff in order to evaluate the MIGFET impacts in the building digital integrated circuits. To achieve this goal, in this work, we present an area and performance evaluation based on digital circuit built using MIGFET devices, where each MIGFET is represented through RC modelling. In particular, such an evaluation is applied on full-custom design of binary adder circuits and on standard-cell design flow targeting in a set of benchmark circuits. Through the experiments, it is possible have an insight, even superficial and pessimist, about how big can be the layout of a given MIGFET than the single-gate FinFET and still show a reduction in the final circuit area due to the logic compaction.

**Keywords**: Digital circuits, emerging technologies, MIGFET, adders, cell libraries, nanotechnology.

# LIST OF FIGURES

| Figure 1: Transistor structures: (a) traditional MOSFET, (b) FinFET and (c) silicon nanowire FET. Source: (ZHANG, 2016)                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Boolean equivalences used to group functions in classes. Source: (HINSBERGER; KOLLA, 1998)                                                                                                                    |

| Figure 3: Logic switch representations: (a) direct or NMOS, and (b) complementary or PMOS 27 Figure 4: Switch networks: (a) series association $f = (x_0 \cdot x_1)$ , (b) parallel association $f = (x_0 + x_1)$ , and |

| (c) arrangement corresponding to the function $f = tx_4 + ((x_1 \cdot x_2) \cdot (tx_0 + tx_3))$ 28                                                                                                                     |

| Figure 5: NSP logic switch associations: (a) Delta, and (b) Wye. Source: (SHANNON, 1938)                                                                                                                                |

| branch-based, (b) factored form, and (c) NSP                                                                                                                                                                            |

| representation for $!f$                                                                                                                                                                                                 |

| (b) representation for !f30                                                                                                                                                                                             |

| Figure 9: Generic <i>n</i> -inputs CMOS logic gate                                                                                                                                                                      |

| Figure 10: Examples of static CMOS logic gates: (a) inverter, (b) NAND2, (c) NOR2, and (d) or-and (OA)                                                                                                                  |

| Figure 11: Example of RC network32                                                                                                                                                                                      |

| Figure 12: SG-FinFET: (a) physical structure, (b) direct or N-type symbol, and (c) complementary or                                                                                                                     |

| P-type symbol33                                                                                                                                                                                                         |

| Figure 13: MIGFET logic switch behavior.                                                                                                                                                                                |

| Figure 14: IG-FinFET: (a) physical structure, (b) N-type IG-FinFET-HV <sub>th</sub> symbol, (c) N-type IG-                                                                                                              |

| $FinFET-LV_{th}\ symbol,\ (d)\ P-type\ IG-FinFET-LV_{th}\ symbol\ and\ (e)\ P-type\ IG-FinFET-HV_{th}\ symbol\ 35$                                                                                                      |

| Figure 15: DG-SiNWFET and possible configurations: (a) physical structure, (b) N-type device, (c) P-                                                                                                                    |

| type device and (d) XNOR operation                                                                                                                                                                                      |

| Figure 16: Signal degradation in SiNWFET: (a) degradation of signal in the N-type and P-type                                                                                                                            |

| transistor, and (b) logic gate using transmission gate structure to restore the output signal                                                                                                                           |

| Figure 17: TIG-SiNWFET and possible configurations (a) physical structure (b) GAMBLE operation,                                                                                                                         |

| (c) N-type device, (d) P-type device, (e) series nFET, (f) series pFET, and (h) XNOR configuration. 38 Figure 18: Signal degradation in TIG-SiNWFET: (a) degradation of signal in N-type and P-type                     |

| transistors, and (b) logic gate using transmission gate structure to restore the output signal39                                                                                                                        |

| Figure 19: TIG-FGMOSFET and possible configurations: (a) physical structure (b) MAJ3 operation,                                                                                                                         |

| (c) N-type device, (d) P-type device. Source: (DAVILA-SALDIVAR, et al., 2014)40                                                                                                                                         |

| Figure 20: Switch networks corresponding to equation (13): (a) SG devices, (b) IG-FinFET, (c) TIG-                                                                                                                      |

| FGMOSFET, (d) DG-SiNWFET, and (e) TIG-SiNWFET42                                                                                                                                                                         |

| Figure 21: Defactorization technique: (a) original network and (b) defactored one                                                                                                                                       |

| Figure 22 Series and parallel defactorizations: (a) switch network obtained from                                                                                                                                        |

| $f = x_0 + (x_1 \cdot x_2 \cdot x_3 \cdot x_4)$ , and (b) switch network obtained from $f = x_0 \cdot (x_1 + x_2 + x_3 + x_4)$ Source:                                                                                  |

| (POSSANI et al., 2016)                                                                                                                                                                                                  |

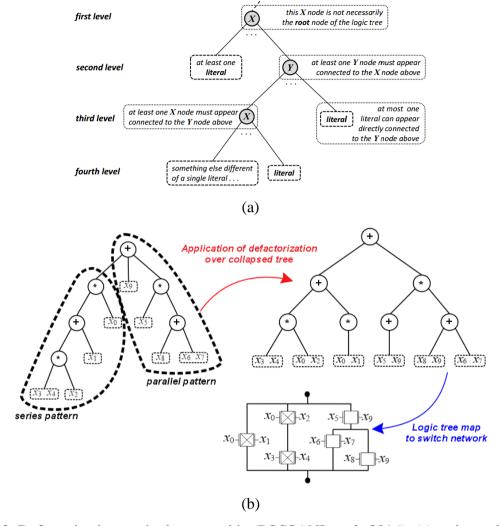

| Figure 23: Defactorization method proposed in (POSSANI et al., 2016): (a) series and parallel                                                                                                                           |

| patterns, and (b) use of defactorization technique over the logic expression                                                                                                                                            |

| $f = x_0 \cdot (x_1 + (x_2 + x_3 + x_4)) + x_5 \cdot (x_6 + x_7 + x_8) + x_9$ . Source: (POSSANI et al., 2016)45                                                                                                        |

| Figure 24: Logic gate implementation for $f = (x_0 \cdot x_1 \cdot ! x_2) + (x_1 \cdot x_2 \cdot ! x_3) + (x_0 \cdot x_2 \cdot ! x_3)$ using TIG-                                                                       |

| FGMOSFET, where $f_M = (x_0 \cdot x_1) + (x_0 \cdot x_2) + (x_1 \cdot x_2)$ . Source: (AMARÚ <i>et al.</i> , 2015)47                                                                                                    |

| Figure 25: Direct relationship between BBDD node and transistor network composed by DG-                                                                                                                                 |

| SiNWFET. Source: (GAILLARDON et al., 2014)                                                                                                                                                                              |

| Figure 26: Transistor layout: (a) MOSFET, and (b) FinFET and SiNWFET51                                                                                                                                                  |

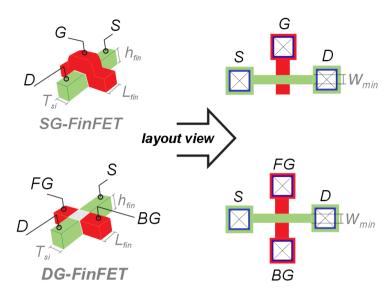

| Figure 27: Dimension parameters for SG-FinFET and DG-FinFET and layout representation                                                                                                                                   |

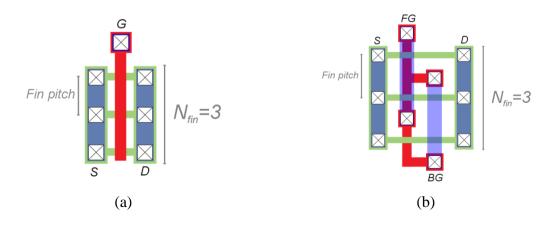

| Figure 28: Layouts for FinFFT devices with N equals to 3: (a) SG-FinFFT and (b) IG-FinFFT 53                                                                                                                            |

| Figure 29: Example of application of folding technique on two-finger FinFETs: (a) SG-FinFET (b) DG-FinFET                                                                                                       |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

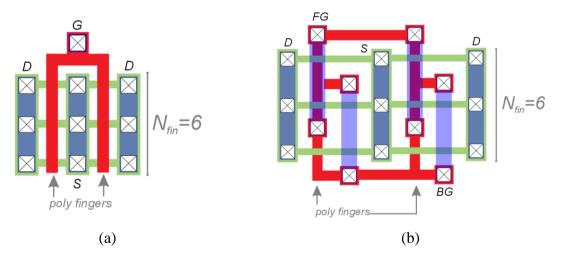

| Figure 30: Physical dimensions for DG-SiNWFET and TIG-SiNWFET, and layout representation                                                                                                                        |        |

| considering minimum W                                                                                                                                                                                           |        |

| Figure 31: Layouts of SiNWFETs with N <sub>SiNW</sub> equals to 3: (a) DG-SiNWFET, and (b) TIG-SiNV                                                                                                             | WFET.  |

| Figure 32: Example of application of folding technique on two-finger SiNWFET devices: (a) DesiNWFET, and (b) TIG-SiNWFET                                                                                        | G-     |

| Figure 33: Examples of DSD for DG-SiNWFET devices: (a) NAND2 gate layout, and (b) possi                                                                                                                         | ble    |

| layouts for XOR2 gate. Source: (BOBBA <i>et al.</i> , 2015)                                                                                                                                                     |        |

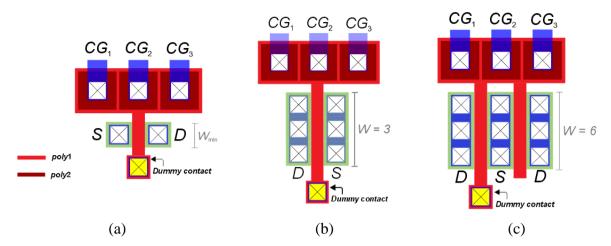

| Figure 35: Layouts for TIG-FGMOSFET transistors: (a) TIG-FGMOSFET with W <sub>min</sub> , (b) TIG-                                                                                                              | 39     |

| •                                                                                                                                                                                                               | 60     |

| FGMOSFET with W equals to 3, and (c) folding transistor technique                                                                                                                                               |        |

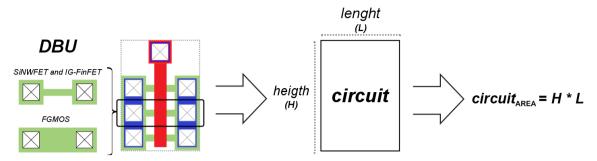

| Figure 36: Circuit area estimation.                                                                                                                                                                             |        |

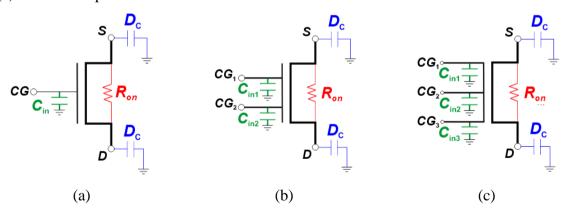

| Figure 37: Transistor models: (a) 1-control gate, (b) 2-control gate, and (c) 3-control gate                                                                                                                    |        |

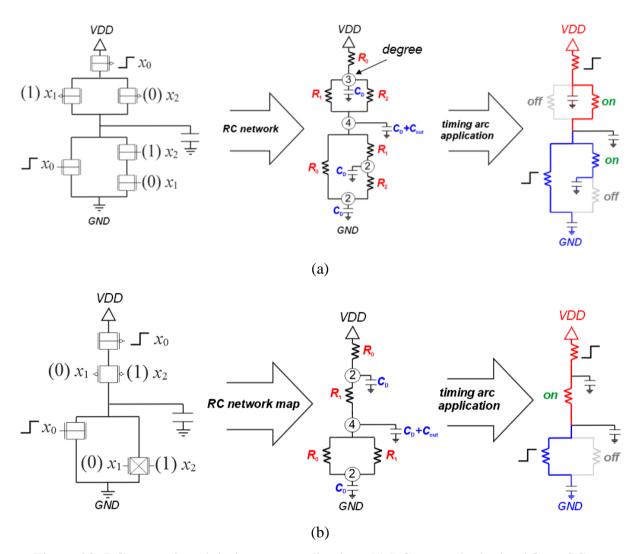

| Figure 38: RC network and timing arcs application: (a) RC network obtained from SG-FinFET                                                                                                                       | -      |

| gate, and (b) RC network obtained from IG-FinFET logic gate                                                                                                                                                     |        |

| Figure 39: Electric behavior of a transistor model based on Elmore delay modeling                                                                                                                               |        |

| Figure 40: Circuit representation for application of STA.                                                                                                                                                       |        |

| Figure 41: Logic gate implementations using IG-FinFET devices: (a) inverter using IG-FinFET in FGV, (b) inverter using IG-FinFET-HV <sub>th</sub> in SIA, (c) inverter using IG-FinFET-LV <sub>th</sub> in FGV, |        |

| inverter using IG-FinFET-LV <sub>th</sub> in SIA, (e) NOR2 logic gate implemented from IG-FinFET-LV <sub>th</sub>                                                                                               |        |

| FGV, and (f) NOR2 logic gate implemented from IG-FinFET-LV <sub>th</sub> in SIA                                                                                                                                 |        |

| Figure 42: Logic gate implementations using TIG-FGMOSFET devices: (a) inverter gate in FG                                                                                                                       |        |

| inverter gate in SIA, (c) NOR2 gate in FGV, and (d) NOR2 gate in SIA                                                                                                                                            |        |

| Figure 43: Ripple-carry adder block diagram                                                                                                                                                                     |        |

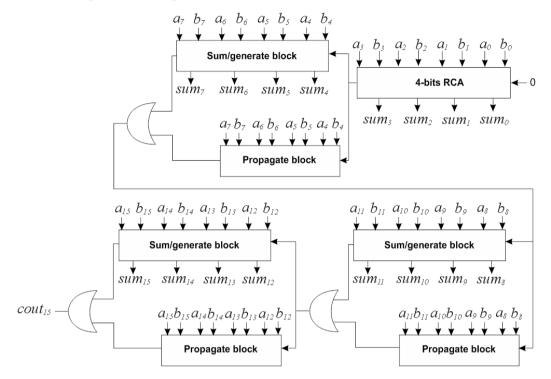

| Figure 44: 4-bits Carry Select Adder block (CSelB).                                                                                                                                                             |        |

| Figure 45: 16-bits CSelA implemented through 4-bits CSelB                                                                                                                                                       |        |

| Figure 46: 4-bits Carry Skip Adder block (CSkipB)                                                                                                                                                               |        |

| Figure 47: 16-bits CSkipA implemented using 4-bits CSkipB                                                                                                                                                       |        |

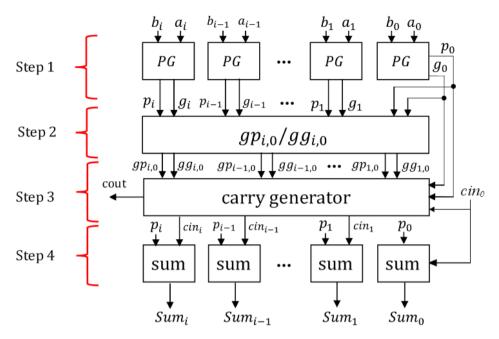

| Figure 48: Basic block used to build parallel-prefix adder and carry lookahead adder                                                                                                                            |        |

| Figure 49: PPA structure: (a) generate-propagate operator, and (b) Brent-Kung arrangements for                                                                                                                  |        |

| bits                                                                                                                                                                                                            |        |

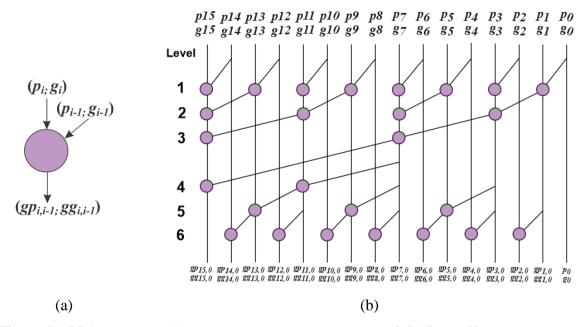

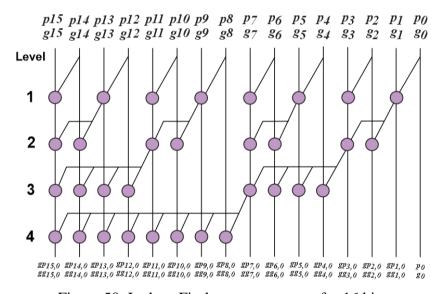

| Figure 50: Ladner-Fischer arrangements for 16 bits                                                                                                                                                              |        |

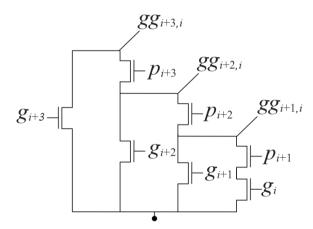

| Figure 51: Manchester carry chain transistor network for group generate signals from indexes 0                                                                                                                  | to 3.  |

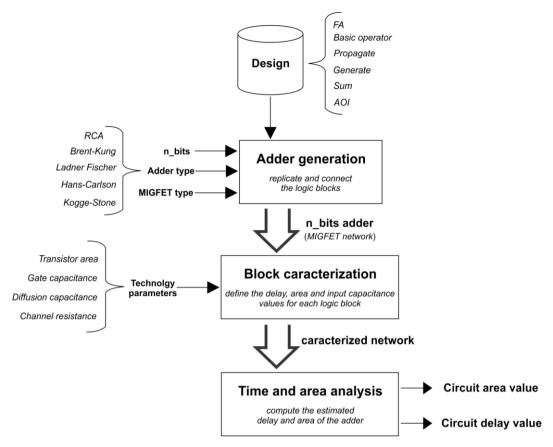

| Figure 52: Design flow applied to estimate the delay and area of the adder circuits evaluated                                                                                                                   |        |

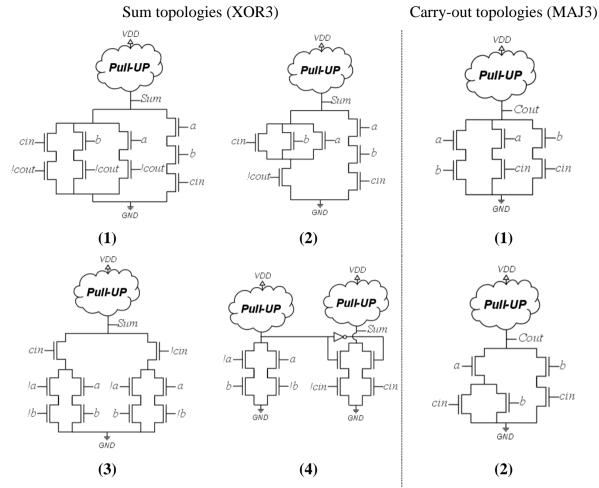

| Figure 53: Topologies of XOR3 gate (sum signal) and MAJ3 gate (carry-out signal)                                                                                                                                | 86     |

| Figure 54: FA designs chosen for each MIGFET technology: (a) IG-FinFET, (b) DG-SiNWFET                                                                                                                          | ', (c) |

| TIG-SiNWFET and (d) TIG-FGMOSFET                                                                                                                                                                                | 90     |

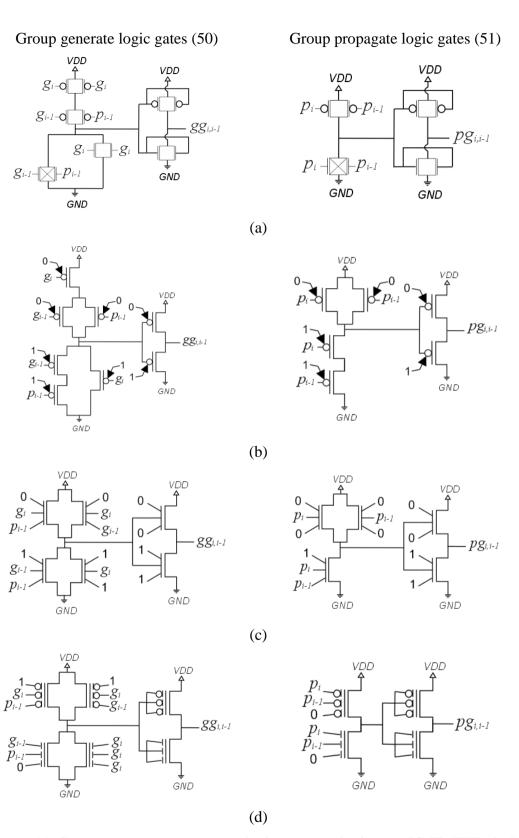

| Figure 55: Generate-propagate operator logic gate topologies: (a) IG-FinFET, (b) DG-SiNWFE                                                                                                                      | Γ, (c) |

| TIG-SiNWFET and (d) TIG-FGMOSFET                                                                                                                                                                                |        |

| Figure 56: Technology mapping stages                                                                                                                                                                            |        |

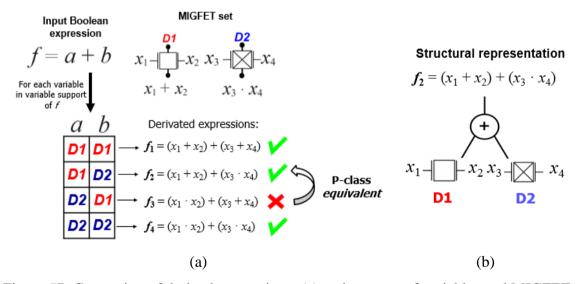

| Figure 57: Generation of derived expressions: (a) assignments of variables and MIGFETs, and (                                                                                                                   |        |

| structural representation of a derived expression.                                                                                                                                                              |        |

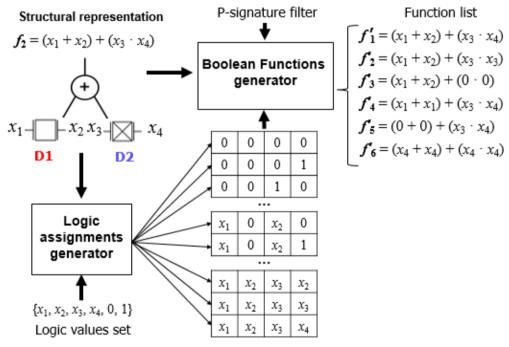

| Figure 58: Generation of all possible Boolean function from a given derivate expression                                                                                                                         |        |

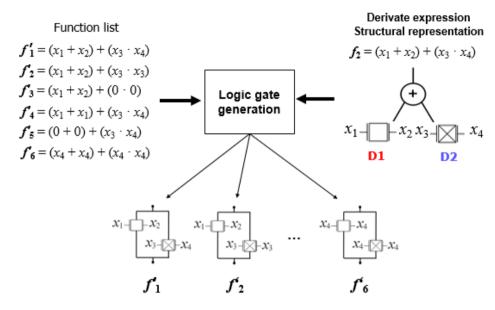

| Figure 59: Generation of switch networks from a given derivate expression                                                                                                                                       |        |

| Figure 60: Logic gate built through of the proposed logic gate generator method                                                                                                                                 |        |

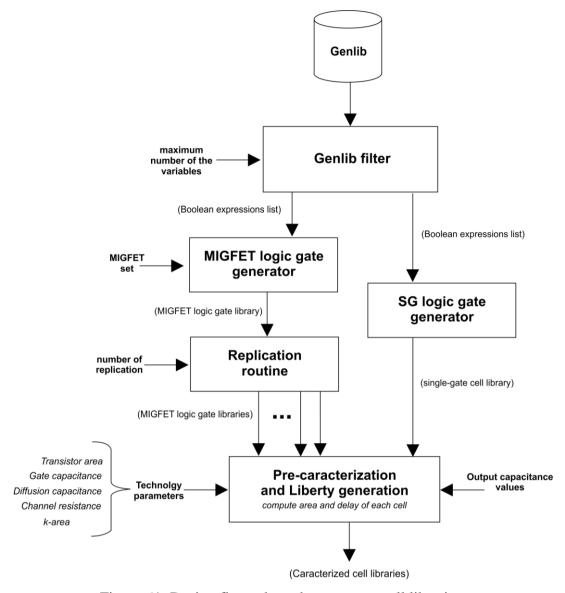

| Figure 61: Design flow adopted to generate cell libraries                                                                                                                                                       | 108    |

# LIST OF TABLES

| Table 1: Fictitious design rules adopted here for different MIGFET technologies                                                                                                          | 50 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2: Estimated area values, in nm <sup>2</sup> , for different MIGFET with DBU from 1 to 66                                                                                          | 51 |

| Table 3: Values for area increasing factors, $\lambda$ and $\Phi$ , for different MIGFET technologies6                                                                                   | 52 |

| Table 4: Estimated area and delay values for inverter and NOR2 logic gates implemented through IG                                                                                        | j- |

| FinFET and TIG-FGMOSFET, normalized in relation to respective SG device of each MIGFET                                                                                                   |    |

| technology                                                                                                                                                                               | 73 |

| Table 5: Estimated area and delay values for FA topologies using IG-FinFET according to Figure 53.                                                                                       |    |

| Table 6: Estimated area and delay values for FA topologies using DG-SiNWFET according to Figure 53                                                                                       | e  |

| Table 7: Estimated area and delay values for FA topologies using TIG-SiNWFET according to Figur 53                                                                                       | e  |

| Table 8: Estimated area and delay values for FA topologies using TIG-FGMOSFET according to Figure 53                                                                                     | 39 |

| Table 9: The best XOR3 and MAJ3 gates for each MIGFET according to Figure 53                                                                                                             | 39 |

| Table 10: Area and delay estimated for RCA implemented through the MIGFET devices, normalized                                                                                            | l  |

| in relation to respective SG device of each MIGFET technology.                                                                                                                           | 91 |

| Table 11: Gate sizing application on 8-bits RCA implemented using TIG-SiNWFET, area and delay values are normalized in relation to SG-SiNWFET                                            |    |

| Table 12: Estimated area and delay values for 64-bits PPA implementations considering each MIGFET technologies, area value is normalized in respect to BK PPA area, while delay value is |    |

| normalized in respect to LF PPA delay                                                                                                                                                    | 95 |

| Table 13: Estimated area and delay values for 64-bits LF PAA, normalized in relation to SG version                                                                                       |    |

| the 64-bits LF PAA for each MIGFET technology                                                                                                                                            | 96 |

| Table 14: Tradeoff between area and delay values for 64-bits RCA and 64-bits LF PAA, delay and                                                                                           |    |

| area values are normalized in relation to 64-bits RCA                                                                                                                                    |    |

| Table 15: Direct and complementary MIGFET switches10                                                                                                                                     | )4 |

| Table 16: Maximum device area per MIGFET technology considering the benchmark circuits, the                                                                                              |    |

| values are normalized in relation to mapped circuit using SG devices10                                                                                                                   |    |

| Table 17: Logic cells used in the mapped circuits11                                                                                                                                      | 10 |

## LIST OF ABREVIATIONS AND ACRONYMS

AIG And Inverter Graph

BBDD Biconditional binary decision diagram

CMOS Complementary Metal-Oxide-Semiconductor

DG-SiNWFET Double gate

FET Field effect transistor

IG-FinFET Independent-gate FinFET

ISOP Irredundant sum-of-product

MIG Majority inverter graph

MIGFET Multiple-independent gate field effect transistor

MOSFET Metal oxide semiconductor field effect transistor

POS Product-of-sums

SOP Sum-of-products

SIA Single-input assignment

SFV Short fixed version

SG Single-gate

STA Static timing analysis

RC Resistance-capacitor

TIG-FGMOSFET Tiple-independent gate floating gate MOSFET

TIG-SiNWFET Triple-independent gate silicon nanowire FET

# **SUMMARY**

| ACKNO          | WLEDGEMENTS                                                                                                                                               | 11 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| RESUM          | O                                                                                                                                                         | 12 |

| LIST OI        | F FIGURES                                                                                                                                                 | 14 |

| 1 INTROI       | DUCTION                                                                                                                                                   | 20 |

| 1.1 Motivation |                                                                                                                                                           | 21 |

| 1.2 Object     | ive                                                                                                                                                       | 22 |

| 1.3 Text of    | rganization                                                                                                                                               | 23 |

| 2 BACKG        | ROUND                                                                                                                                                     | 24 |

| 2.1 Boolea     | n function                                                                                                                                                | 24 |

| 2.2 Rooles     | n expressions                                                                                                                                             | 24 |

| 2.2.1          | SOP and POS expressions                                                                                                                                   |    |

| 2.2.2          |                                                                                                                                                           |    |

| 2.2.3          |                                                                                                                                                           |    |

| 2.3 Boolea     | n difference                                                                                                                                              | 26 |

| 2.4 Classes    | s of Boolean functions                                                                                                                                    | 26 |

| 2.5 Switch     | networks                                                                                                                                                  | 27 |

| 2.6 Static     | CMOS logic gate                                                                                                                                           | 30 |

| 2.6 Elmor      | e delay method                                                                                                                                            | 32 |

| 3 SWITCI       | ISOP expression Factored form  In difference  Is of Boolean functions  In networks  CMOS logic gate  In delay method  H-BASED DEVICES  -gate logic switch | 33 |

| 3.1 Single-    | gate logic switch                                                                                                                                         | 33 |

| 3.2 Multin     | ole-gates logic switches                                                                                                                                  | 33 |

| 3.2.1          | IG-FINFET                                                                                                                                                 |    |

| 3.2.2          | DG-SINWFET                                                                                                                                                |    |

| 3.2.3          | TIG-SINWFET                                                                                                                                               |    |

| 3.2.4          | TIG-FGMOSFET                                                                                                                                              |    |

| 3.3 New cl     | nallenges for MIGFET                                                                                                                                      | 41 |

| 3.3.1          | Methods for MIGFET-based network generation                                                                                                               |    |

| 4 PHYSIC       | CAL AND ELETRICAL ISSUES                                                                                                                                  | 49 |

| 4.1 MOS a      | and emerging transistor layouts                                                                                                                           | 50 |

| 4.1 FINFE      | T layout                                                                                                                                                  | 51 |

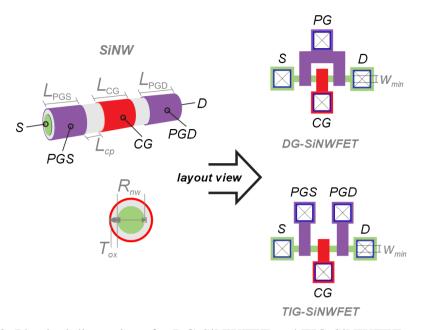

| 4.2 SINWFET layout        |                                            | 54  |

|---------------------------|--------------------------------------------|-----|

|                           |                                            | 58  |

| 4.4 Evalua                | 4.4 Evaluation of MIGFET area              |     |

| 4.5 RC modeling of MIGFET |                                            |     |

| 4.5.1                     | RC modeling                                | 63  |

| 4.5.2                     | RC modelling of IG-FinFET                  |     |

| 4.5.3                     | RC modelling of TIG-SiNWFET and DG-SiNWFET | 65  |

|                           | analysis of MIGFET logic gates             |     |

| 4.6.1                     | Elmore delay analysis of logic gates       |     |

| 4.6.2                     | Static timing analysis                     | 69  |

| 4.6.3                     | Discussions and considerations             | 71  |

| 5 BINARY                  | Y ADDERS DESIGN                            | 74  |

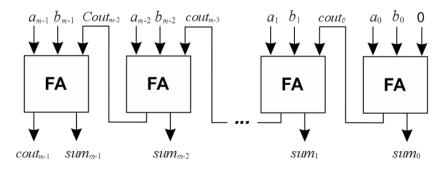

| 5.1 Ripple-carry adder    |                                            | 74  |

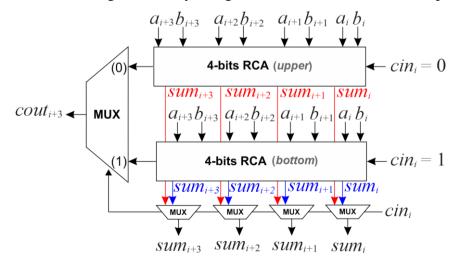

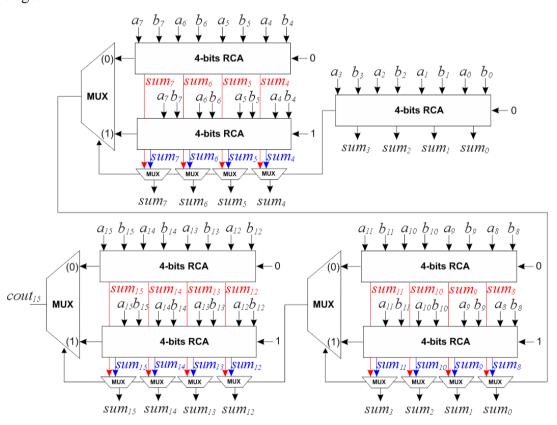

| 5.2 Carry-select adder    |                                            | 75  |

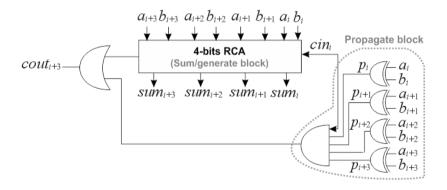

| 5.3 Carry-skip adder      |                                            | 77  |

| 5.4 Parallo               | el-prefix adder                            | 79  |

| 5.5 Carry                 | -lookahead adder                           | 82  |

| 5.6 Binary                | adder design evaluation                    | 83  |

| 5.6.1                     | Evaluation methodology                     | 83  |

| 5.6.2                     | Ripple-Carry Adder design                  |     |

| 5.6.3                     | Gate sizing approach                       |     |

| 5.6.4                     | Parallel-Prefixed Adder design             |     |

| 6 MIGFE                   | T cell library and ASIC design             | 98  |

| 6.1 Techno                | ology mapping                              | 98  |

| 6.2 Librar                | y generator                                | 100 |

| 6.3 Bench                 | mark circuit synthesis                     | 106 |

| 6.3.1                     | Evaluation methodology                     |     |

| 6.3.2                     | Experimental results                       |     |

| CONCLU                    | SIONS                                      | 112 |

| DEFER                     | ENGES                                      | 444 |

| KEFEK                     | ENCES                                      | 114 |

### 1 INTRODUCTION

The miniaturization (scaling) of MOS transistor has been the key of semiconductor success in the last 30 years. Along these years, more compact and faster circuits have been manufactured as a result of the increasing high density of transistors in a single chip. However, with the current physical dimensions of MOS transistor reaching atomics dimensions of silicon (Si), several studies have indicated that MOS transistor scaling is reaching its limit (FRANK *et al.*, 2001) and (HAENSCH, 2006). In general, the main consequence of such a scaling approach is the fact that smaller devices tend to be more susceptible to electrical effects and parasitic elements. In this sense, several improvements have been performed over the MOSFET structure in order to maintain similar device performance while scaling down.

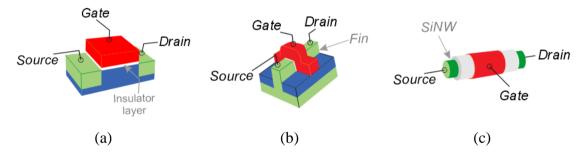

For instance, traditionally, SiO<sub>2</sub> has been adopted as the main insulator material in the manufacturing of MOS transistors, as depicted in Figure 1(a). In this context, according to the downscaling of transistor, the SiO<sub>2</sub> layer has become thinner. Such dimension reductions in the SiO<sub>2</sub> layer are needed in order to keep electrostatic control over the transistor channel. However, gate tunneling current increases as SiO<sub>2</sub> layer reduce, so impacting in the leakage current (GHANI *et al.*, 2000). In particular, it has been indicated the use of insulator materials with higher dielectric constant (k) such as HfO<sub>2</sub> (RIBES *et al.*, 2005) for technology nodes under of 45 nm in order to reduce the leakage current.

Another consequence of the downscaling of MOS transistor is the impact of the gate material on the electrostatic control of the inversion transistor channel. In general, polycrystalline silicon has been adopted to build the transistor gate. The polysilicon gate suffers from high resistance and depletion effects (YEO *et al.*, 2002). In depletion effect, the depleted region in the polysilicon tends to behave as an additional gate oxide that increases the oxide thickness layer and reduces the electrostatic control of the transistor channel. Such effects are more severe according to the technology node adopted in manufacturing. For instance, for technology node under 45 nm, the metal gate has replaced the polysilicon gate in order to reduce the gate resistance and to eliminate the depletion effects (ZHANG, 2016).

According to (ZHANG, 2016), the MOSFET inversion channel from the 22 nm node technology is quite short than the traditional MOSFET structure cannot provide sufficient electrostatic control of transistor channel. Alternative devices have been proposed and studied in order to keep the continuous downscaling strategy. Among the most promising device

structures, there are the silicon-on-insulator FET (SOI FET) (GNANI *et al.*, 2012), the fully depleted (FD) SOI FET (FD-SOI FET) (DOYLE *et al.*, 2003), the ultra-thin body and buried oxide FD SOI (UTBB-FD SOI) (NOEL *et al.*, 2011), the FinFET (ROSTAMI; MOHANRAM, 2011), and the gate-all-around (GAA) nanowires (ZHANG *et al.*, 2017).

In particular, the physical structure of FinFET and GAA devices tend to increase the electrostatic integrity and the scalability of transistor (RIEL *et al.*, 2014), because, in FinFET and GAA transistor structures, the control gate overlaps the transistor channel over more than one dimension (KUHN, 2012). As seen in Figure 1(b), notice that in the FinFET structure the gate overlaps the transistor channel over the sides and the top (BHOJ; JHA, 2013). On the other hand, in GAA structure, the gate surrounds transistor channel over all sides. According to (ZHANG, 2016), silicon nanowires (SiNW) are a further improvement on the MOSFET structure since the SiNWFET, illustrated in Figure 1(c), can provide significant improvements on the electrostatic control.

Figure 1: Transistor structures: (a) traditional MOSFET, (b) FinFET and (c) silicon nanowire FET. Source: (ZHANG, 2016).

## 1.1 Motivation

The adoption of a new technology impacts significantly in the manner as the integrated circuits (IC) are designed. In general, according to a given technology, different logic paradigms are possible. The logic paradigms define the way as the information is represented and handled through of a given technology (HAENSCH, 2006). In this context, much effort has been done in order to develop alternative methods to improve the digital circuit design based on emerging technologies. In such efforts, it is included modifications in the standard methods up to the creation of new algorithms and data structure (AMARÚ; GAILLARDON; DE MICHELI, 2014), (AMARÚ, GAILLARDON; DE MICHELI, 2016), (POSSANI *et al.*, 2016) and (ROSTAMI; MOHANRAM, 2011).

For instance, in CMOS technology the most basic logic element is the logic switch (POSSANI *et al.*, 2016). By combining several switches into a network, different Boolean

functions can be performed. Therefore, the optimization of switch networks is an important task to improve IC performance (POSSANI *et al.*, 2016). On the other hand, when multiple-independent-gate FETs (MIGFET) are adopted, more complex Boolean functions can be implemented through a single switch (AMARÚ *et al.*, 2015). Consequently, the optimal transistor arrangements considering MIGFET devices may be different when compared to conventional CMOS implementations.

## 1.2 Objective

Our goal is evaluated the impacts of using of MIGFET devices in digital IC design considering the tradeoff between improvements obtained at logic level and physical cost penalties. In particular, at logic level, MIGFETs can be used to merge logic switch arrangements in order to build more compact and efficient circuits. According to (POSSANI et al., 2016), (DATTA et al., 2007), (CHIANG et al., 2006) and (ROSTAMI; MOHANRAM, 2011) it is expected that the reduction in transistor count at logic level compensates the area overhead provided by extra contacts needed for connecting the transistor gates. However, at physical level, the cost of more complex switches tends to penalize the area and signal delay propagation of the target circuit.

In this work, we performed two experiments considering a specific set of MIGFET devices. In the first one, we implement two distinct binary adder architectures, the ripple carry adder (RCA) and parallel prefix adder (PPA). The main goal is to evaluate if binary adder circuits can be optimized through the adoption of MIGFETs considering the tradeoff between logic optimizations and physical penalties. In the second experiment, we developed specific library cells to map a set of digital benchmark circuits in order to evaluate how the commercial tools treat the logic synthesis considering the MIGFET devices. Moreover, in this experiment, we aim to determine an area limit for each MIGFET device that ensures the improvements obtained at logic level.

## 1.3 Text organization

Chapter 2 presents the basic background needed for understanding the experiments and discussions performed in this work. Among the concepts presented are Boolean expression, logic switch, switch network and the building of static CMOS logic gate.

Chapter 3 offers an overview about MIGFET devices taken into account in this work, discussing the logic behavior of each transistor. In particular, in this chapter, we also aim to demonstrate the new possibilities and the challenges raised from using MIGFETs in building digital integrated circuits.

Chapter 4 presents some MIGFET layouts elaborated through fictitious design rules. In particular, the MIGFET layouts are used to extract some physical characteristic in order to create the RC modelling of devices.

Chapter 5 presents the binary adder architectures implementations discussed in this work. The estimated area and delay results for binary adders implementations are provided.

Chapter 6 presents the method used to build MIGFET libraries and discusses the logic mapping performed considering these libraries.

Finally, the Chapter 7 outlines the conclusions and final considerations of this work.

### 2 BACKGROUND

In this chapter, some definitions and basic notation are introduced. These concepts are helpful for understanding the present work.

#### 2.1 Boolean function

An *n*-input Boolean function f(X), defined by the variable support set  $X = \{x_0, ..., x_{n-1}\}$ , can be represented as follows:

$$f(X): B^n \to B \tag{1}$$

where B =  $\{0, 1\}$ . A Boolean variable is defined in the domain of the function, and can assume the logic values 0 or 1, typically 0 = false and 1 = true. Moreover, a variable can be represented in positive or negative polarity. The positive polarity indicates the direct use of the variable, whereas the negative polarity indicate the use of the complemented (or negated) variable. An instance of a variable in its positive or negative polarity is called literal. The literals  $x_0$  and  $x_1$  are examples of positive literals. whereas  $x_0$  and  $x_1$  are negative literals.

## 2.2 Boolean expressions

A simple way to represent a Boolean function is using Boolean expression. A Boolean expression can be defined recursively as a constant (0 or 1), a variable (in positive or negative polarity), a product, a sum or a complement of Boolean expressions. In this work, the product operator is denoted as AND (•), the sum operator is denoted as OR (+) and the complement is denoted as NOT (! or  $\bar{\ }$ ).

### 2.2.1 SOP and POS expressions

A sum-of-product (SOP) is a Boolean expression representation where a given Boolean function is expressed as a sum of product terms of l literals, called *minterms*. On the other hand, a product-of-sum (POS) expression of a given Boolean function is expressed through a product of sum terms of l literals, called *maxterms* (DE MICHELI, 1994). The following Boolean expression:

$$f = (x_0 \cdot x_1 \cdot x_2) + (x_3 \cdot x_4) \tag{2}$$

is an example of SOP, whereas the following Boolean expression:

$$f = (x_0 + x_1 + x_2) \cdot (x_3 + x_4) \tag{3}$$

is an example of POS. Notice that both SOP and POS expressions represent two-level forms. In this approach, a given expression can be directly implemented through a circuit of logic depth equals to two.

## 2.2.2 ISOP expression

A cube (or product term) is a cube implicant of a given Boolean function f, if each assignment that makes this product to be evaluated to 1 also evaluates f to 1 (MURGAI; BRAYTON; SANGIOVANNI, 2012). In turn, a prime implicant of a given Boolean function f is a cube implicant such that removing any literal from such a cube results in a new cube that does not imply f. On the other hand, an irredundant sum-of-products (ISOP) expression is a SOP where each product term is prime implicant that cannot be removed without changing the Boolean function behavior by the expression.

#### 2.2.3 Factored form

A factored form can be defined as a literal, a product, or a sum of factored forms (BRAYTON, 1987). The factored form is also defined as multi-level logic form. In multi-level logic, the Boolean expressions can have unbounded number of levels. However, not all multi-level expression are factored forms. For instance, the following expression:

$$f = !(!x_0 \cdot (!x_1 \cdot x_2)) \tag{4}$$

is described as a multi-level form but not a factored form. In turn, the Boolean expression presented in sequence:

$$f = !x_0 \cdot (!x_1 \cdot x_2) \tag{5}$$

is a factored form and also a multi-level form. According to (GOLUMBIC; MINTZ, 1999), the objective of factorization methods is to represent a Boolean function in a logically equivalent factored form but with a minimum number of literal. For instance, the following Boolean expression:

$$f = (x_0 \cdot x_2) + (x_1 \cdot x_2) + (x_2 \cdot x_3 \cdot x_4) \tag{6}$$

can be factored into an equivalent form, such as follow:

$$f = x_2 (x_0 + x_1 + (x_3 \cdot x_4)) \tag{7}$$

Notice that, this factored expression is optimum in the number of literals, where literals count reduced from seven to five.

### 2.3 Boolean difference

Given a Boolean function  $f(x_0, x_1, ..., x_{n-1})$  the cofactor operation consist of assigning a logic constant value  $c_i \in \{0, 1\}$  to an input variable  $x_i \in \{x_0, x_1, ..., x_{n-1}\}$ . Such operation is denoted  $f_{X_i} = c_i$  (BOOLE, 1854). Thus, the positive cofactor of f with respect to variable  $x_i$  is denoted  $f_{X_i} = f(x_0, x_1, ..., x_i = 1, ..., x_{n-1})$ . On the other hand, the negative cofactor of f with respect to variable  $x_i$  is  $f(x_i) = f(x_0, x_1, ..., x_i) = 0, ..., x_{n-1}$  (DE MICHELI, 1994). This way, the Boolean difference with regard to a variable  $x_i$  of a given Boolean function f is defined as the exclusive sum of its cofactors, as follows:

$$\frac{\partial f}{\partial x_i} = f \overline{x_i} \oplus f x_i \tag{8}$$

### 2.4 Classes of Boolean functions

Boolean functions can be classified into classes of functions. In general, Boolean functions can be grouped considering the complementation (negation) of its inputs (x), the permutation of its inputs (y) and/or inversion (negation) of its outputs (z), as shown in Figure 2. In particular, P-class represents the set of equivalent Boolean functions obtained by permuting the inputs (HINSBERGER; KOLLA, 1998).

Figure 2: Boolean equivalences used to group functions in classes. Source: (HINSBERGER; KOLLA, 1998).

### 2.5 Switch networks

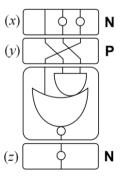

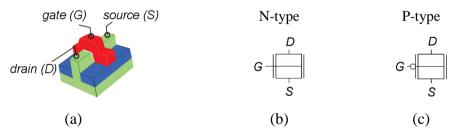

A logic switch can be represented through a device composed of one control terminal, gate (G), and two contact terminals, source (S) and drain (D). The control terminal determines if there is a connection between the contact terminals. Moreover, a logic switch can be classified as direct or complementary according to the polarity of the control terminal activation. In the direct logic switch the contact terminals are connected only when the logic value 1 is applied to the control terminal. In contrast, the complementary switch presents the connection between the terminal contacts only when the logic value 0 is defined in the control terminal.

In CMOS technology, the direct and complementary logic switches are represented by NMOS and PMOS transistors, respectively. Such devices implements 1-input Boolean function, *i.e.*, f(x) = x or f(x) = !x (POSSANI *et al.*, 2016). For convenience, in this work, devices or switches that presents such a logic behavior are named as single-gate (SG) one. Moreover, the definition of logic switch will be later extended to devices with more than one control terminals. Notice that the direct and complementary logic switches in CMOS technology are depicted in Figure 3.

Figure 3: Logic switch representations: (a) direct or NMOS, and (b) complementary or PMOS.

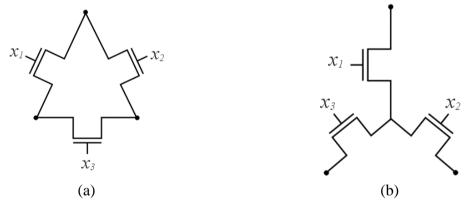

Traditionally, switch networks are built through the arrangement of direct and/or complementary SG logic switches. In this way, a Boolean function can be represented through a switch network by defining the arrangement of logic switches that connects two external terminals (T1 and T2) of the logic network (POSSANI *et al.*, 2016). The most trivial logic switch arrangements are *series* and *parallel* associations. A series association  $(x_0 \cdot x_1)$  is shown in Figure 4(a), whereas a parallel association  $(x_0 + x_1)$  is shown in Figure 4(b). An arbitrary Boolean function can be implemented through a switch network, as illustrated in Figure 4(c).

Figure 4: Switch networks: (a) series association  $f = (x_0 \cdot x_1)$ , (b) parallel association  $f = (x_0 + x_1)$ , and (c) arrangement corresponding to the function  $f = !x_4 + ((x_1 \cdot x_2) \cdot (!x_0 + x_3))$

In general, switch networks can be divided in series-parallel (SP) and non-series-parallel (NSP) networks. An SP switch network is composed by only series or/and parallel associations of logic switches. In turn, an NSP switch network, besides series and parallel associations, the logic switches can be associated through Delta or Wye logic arrangements (SHANNON, 1938), as shown in Figure 5.

Figure 5: NSP logic switch associations: (a) Delta, and (b) Wye. Source: (SHANNON, 1938).

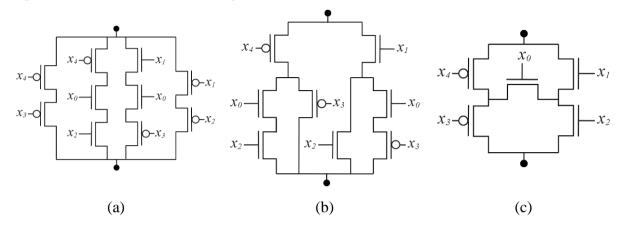

In general, NSP switch networks are more compact than SP ones. For instance, all switch networks presented in Figure 6 correspond to the following Boolean function:

$$f = (!x_4 \cdot !x_3) + (!x_4 \cdot x_0 \cdot x_2) + (x_1 \cdot x_2) + (x_1 \cdot x_0 \cdot !x_3)$$

(9)

In Figure 6(a), the switch network is obtained directly from a SOP expression. In Figure 6(b), the switch network is implemented from a factored form expression and, in Figure 6(c), such Boolean function is represented through an NSP switch network. The switch network shown in Figure 6(a) presents a network configuration known as *branch-based*. In this type of network, only arrangements of logic switches associated in series are used to connect the external terminals of the switch network (PIGUET, 1998). Notice that, among all possible

switch network representations shown in Figure 6, the NSP network is the most compact representation in the number of logic switches.

Figure 6: Switch networks corresponding to  $f = (!x_4 \cdot !x_3) + (!x_4 \cdot x_0 \cdot x_2) + (x_1 \cdot x_2) + (x_1 \cdot x_0 \cdot !x_3)$ : (a) branch-based, (b) factored form, and (c) NSP.

In the literature, the switch network generation methods are divided into factored-form-oriented methods and graph-oriented methods. In the methods based on factored form expressions, the switch network is built directly from a Boolean expression. In such approach, it is only possible to generate SP switch networks (BRAYTON, 1987), (MARTINS *et al.*, 2010), and (GOLUMBIC; MINTZ; ROTICS, 2008). In turn, in switch network generation methods based on graph structures, a given Boolean function is initially represented through a graph that can be later optimized and translated to a switch network. In such an approach, each edge of the graph represents a logic switch. This technique allows the generation of SP and NSP switch networks (ZHU; ABD-EL-BARR, 1993), (DA ROSA, MARQUES *et al.*, 2007), (KAGARIS; HANIOTAKIS, 2007), and (POSSANI *et al.*, 2016).

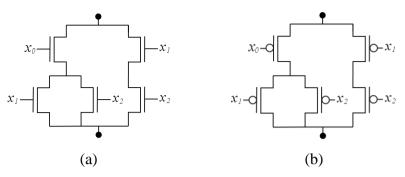

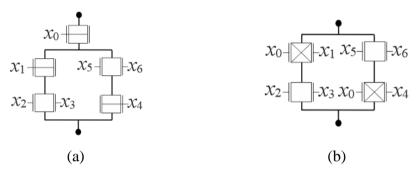

Another quite important property regarding to switch networks is the concept of complementarity. A given switch network is said logically complementary to another when only one of them is connecting respective contact terminals for a given configuration of the input vector. In turn, a given switch network is topologically complementary to another if such logic switch implements the dual plan of the other switch network (UEHARA; VANCLEEMPUT, 1979). In Figure 7, it is presented two switch networks that are logically complementary but are not topologically complementary. In turn, in Figure 8 it is shown two switch networks that are topologically complementary.

Figure 7: Logically complementary switch networks: (a)  $f = (x_0 \cdot x_1) + (x_0 \cdot x_2) + (x_1 \cdot x_2)$  and (b) representation for f.

Figure 8: Topologically complementarity switch networks (a) representation for  $f = x_0 + (x_1 \cdot x_2)$ , and (b) representation for !f.

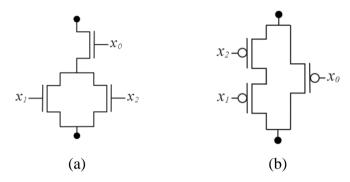

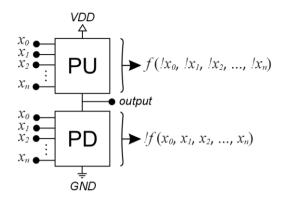

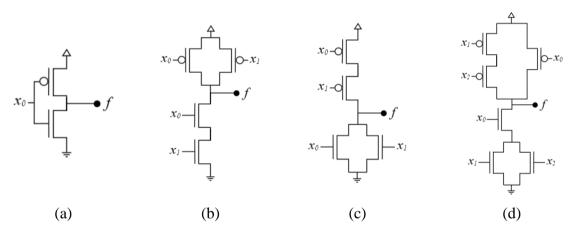

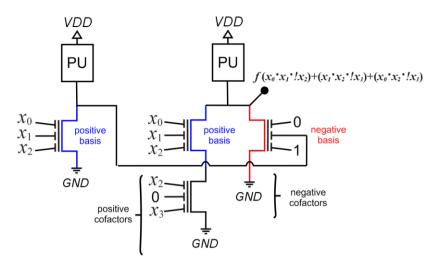

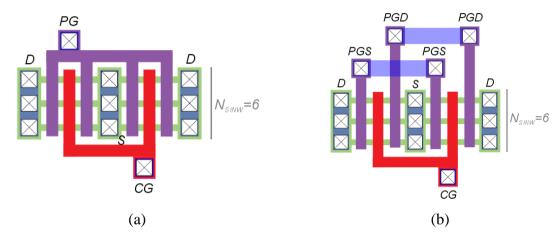

## 2.6 Static CMOS logic gate

In conventional static CMOS logic topology, a logic gate is built through two complementary plans, called pull-up plan (PU) and pull-down plan (PD). The structure of the CMOS logic gate is illustrated in Figure 9. Notice that the PU plan is used to connect the output terminal to the constant logic value 1 (VDD terminal), while the PD plan is used to connect the output terminal to constant logic value 0 (GND terminal). This way, when the output of the gate logic is evaluated as 1, there is a logic path across the PU plan that connects the VDD terminal to output terminal. Otherwise, it exist a logic path across the PD plan that connects the output terminal to GND terminal. Notice that, in this context, a given Boolean function f is implemented in PD plan, whereas its complement is implemented in PU plan, such as it is shown in Figure 9.

Figure 9: Generic *n*-inputs CMOS logic gate.

The PU plan is implemented through a switch network built exclusively by PMOS transistors. Additionally, the PD plan is implemented through a switch network comprising only NMOS transistors. Some static CMOS logic gates are shown in Figure 10. Notice that, to ensure the complementarity between the PU and PD plans, the switch network implemented in PU plan can be obtained through the dual switch network implemented in PD plan.

Figure 10: Examples of static CMOS logic gates: (a) inverter, (b) NAND2, (c) NOR2, and (d) or-and (OA).

In general, the static CMOS logic gates present low power dissipation when compared to others CMOS logic topology and families, since PU and PD plans are complementary, so only one of them is *on* (RABAEY; CHANDRAKASAN; NIKOLIC, 2002). Moreover, the static CMOS logic topology presents high noise margin since due to the complementary structure, a static logic path restores the correct logic state in the presence of noise. Furthermore, the static CMOS topology presents a high robustness against power voltage downscaling (ANIS; ALLAM; ELMASRY, 2002). However, CMOS logic gates requires 2*n* transistors to implements an *n*-input Boolean function. Moreover, the load capacitance is quite significant since each input signal drives at least two devices per logic gate (RABAEY; CHANDRAKASAN; NIKOLIC, 2002).

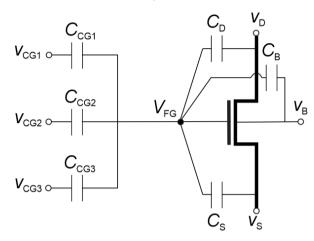

## 2.6 Elmore delay method

The Elmore delay modeling is used to obtain an approximated delay for a given input circuit (ELMORE, 1948). In general, the results obtained through Elmore delay method are not very accurate since the slope of input signal is not taken into account. However, reducing the Elmore delay tends to lead to a delay reduction in real circuit.

In the Elmore delay method, the evaluated circuit is modelled through resistive (R) and capacitive (C) elements in an RC network. This way, the circuit is represented through resistor and capacitance associations. Additionally, the estimated delay for a given RC network can be computed as follows (CONG; KWOK-SHING, 1995):

$$D = \sum_{i=0}^{all\_nodes} Ri * Ci$$

(10)

where  $R_i$  represents the resistance between the source node and the node i, whereas  $C_i$  represents the capacitance at the node i. In order to exemplify the application of Elmore delay method, in Figure 11, it is illustrated an RC network implemented from a series association of resistors. In this case, the delay (D) of the circuit can be computed as follows:

$$D = C_{1} * R_{1} + C_{2} * (R_{1} + R_{2}) + \dots C_{i} * (R_{1} + R_{2} + \dots + R_{i})$$

$$R_{1} \qquad R_{2} \qquad R_{3} \qquad R_{i}$$

$$C_{1} \qquad C_{2} \qquad C_{3} \qquad C_{i} \qquad C_{i}$$

$$C_{1} \qquad C_{2} \qquad C_{3} \qquad C_{i}$$

$$C_{1} \qquad C_{2} \qquad C_{3} \qquad C_{i}$$

$$C_{1} \qquad C_{2} \qquad C_{3} \qquad C_{4}$$

$$C_{1} \qquad C_{2} \qquad C_{3} \qquad C_{4}$$

Figure 11: Example of RC network.

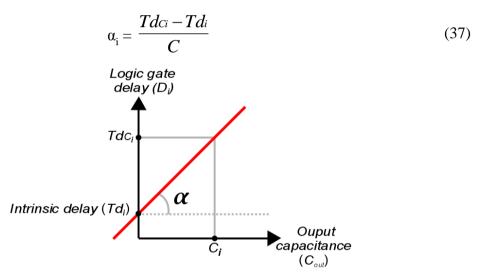

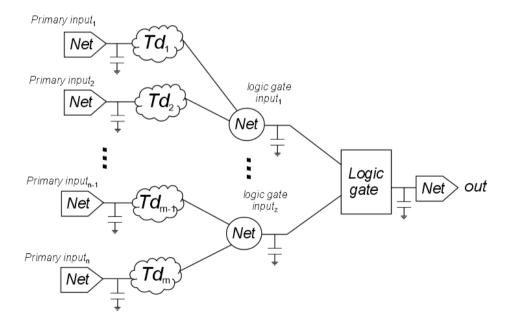

The Elmore delay model corresponds to the linear delay modeling (LDM) to compute the signal delay propagation across logic gates. In such a situation, the estimated delay value of a given logic gate is defined as a linear function in respect to its output capacitance (JU; HANDSCHIN; KARLSSON, 1996). However, the propagation of a given signal in a logic gate do not varies linearly with its output capacitance. Such a variation depends also on the input signal slope. Moreover, the resistances associated to the wires used to connect distinct logic gates tend to be more significant when the technology node is scaled down. In this sense, the non-linear delay model (NLDM), composite current source model (CCSM) (SYNOPSYS, 2017) and effective current source model (ECSM) (CADENCE, 2017) present more accurate results (MARTINS *et al.*, 2015).

### 3 SWITCH-BASED DEVICES

In this chapter, the multiple-independent-gate field effect transistors (MIGFETs) are introduced. Similar to traditional MOSFET transistor, MIGFETs can be adopted in the construction of switch networks. However, due to higher logic capability of MIGFETs, the traditional methods for switch network generation may not be the most indicated for these transistors. In this sense, we discussed the main challenges and possibilities regarding to switch network generation taking into account a particular set of MIGFETs. The concepts presented herein are helpful for the understanding of experiments performed in this work.

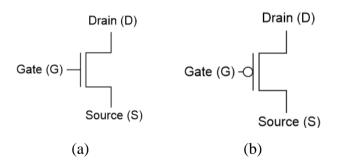

## 3.1 Single-gate logic switch

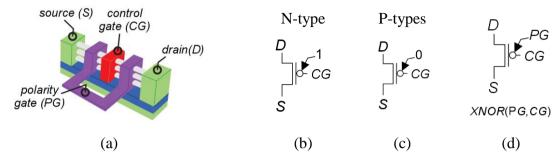

In FinFET technology (ROSTAMI; MOHANRAM, 2011), the direct and complementary logic switches can be represented through of the shorted-gate FinFET, also referenced as single-gate (SG) FinFET. This device is a transistor controlled by a single gate. Similar to traditional MOSFET device, SG-FinFET can only implement 1-input Boolean function. Its physical structure consists of a thin silicon body wrapped by gate electrodes (CUI *et al.*, 2014), such as illustrated in Figure 12(a). Similarly to MOSFET devices, SG-FinFET can be manufactured in N-type and P-type versions. Therefore, SG-FinFET device corresponds to direct logic switch (N-type) or complementary logic switch (P-type). In Figure 12(b) and in Figure 12(c), the notations for N-type and P-type SG-FinFET logic switches are represented, respectively.

Figure 12: SG-FinFET: (a) physical structure, (b) direct or N-type symbol, and (c) complementary or P-type symbol.

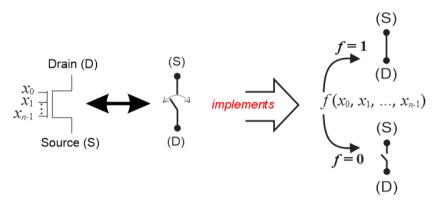

## 3.2 Multiple-gates logic switches

Multiple-independent-gate field effect transistors (MIGFET) allow more logic capability into a single device. In particular, a MIGFET logic switch can implement logic functions with more than one variable into a single device, as illustrated in Figure 13. Thus,

the switch networks implemented using MIGFET tend to be more compact in the number of logic switches when compared to traditional SG approaches (AMARÚ *et al.*, 2015). However, the circuit area and the signal delay propagated through the devices tend to be larger than in circuits based on SG devices (ALIOTO, 2011). Indeed, there is a tradeoff between the increased logic capability of a given MIGFET and its area/performance cost. Consequently, the optimal MIGFET-based network arrangements may be different from conventional static CMOS implementations (POSSANI *et al.*, 2016).

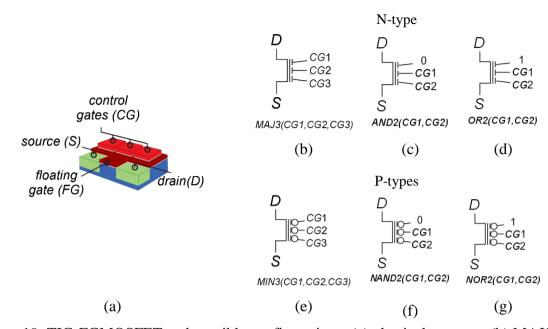

Figure 13: MIGFET logic switch behavior.

MIGFET devices have demonstrated a great potential for digital integrated circuit design. Several works have explored the use of such a kind of devices to improve mainly area and power consumption of digital ICs (AMARÚ *et al.*, 2015), (CHIANG, *et al.*, 2005), (BENJAMAA; MOHANRAM; DE MICHELI, 2011), (HSIEH, *et al.*, 2012) and (BHOJ; JHA, 2013). Among the most the promising MIGFET alternatives discussed in the literature are the independent-gate FinFET (IG-FinFET) (RIEL *et al.*, 2014), the double-gate silicon nanowire FET (DG-SiNWFET) (AMARÚ; GAILLARDON; DE MICHELI, 2013), the triple independent-gate silicon nanowire FET (TIG-SiNWFET) (ZHANG *et al.*, 2017) and the triple independent-gate floating-gate MOS transistor (FGMOSFET) (SHIBATA; OHMI, 1992). Hereafter, the physical structure, graphic representation and logic behavior those MIGFETs are presented.

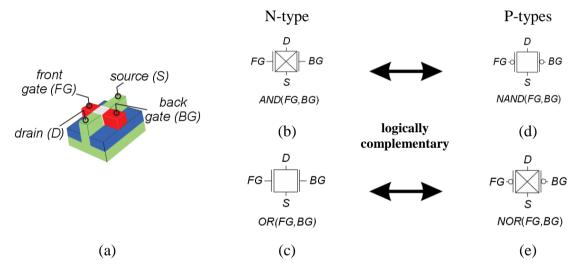

#### 3.2.1 IG-FINFET

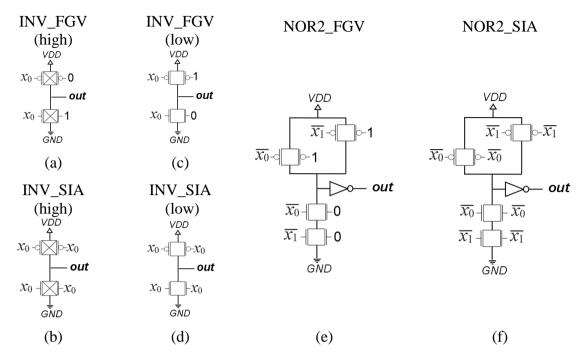

IG-FinFET is a transistor controlled by two independent gates, the front gate (FG) and the back gate (BG), as shown in Figure 14(a). Such a device implements 2-input (AND2) or 2-input OR (OR2) operation, which can be associated to series and parallel arrangements of two SG-transistors, respectively. AND2 and OR2 configuration are shown in Figure 14(b), and in Figure 14(c), respectively. The OR2 operation is performed through IG-FinFET-LV<sub>th</sub>.

In such case, if at least one of the independent gates is active, the transistor is turned on (ROSTAMI; MOHANRAM, 2011). On the other hand, the AND2 operation is obtained by using IG-FinFET-HV<sub>th</sub>, in which, both control gates must be active to create the conducting transistor channel (ROSTAMI; MOHANRAM, 2011).

Both IG-FinFET-LV<sub>th</sub> and IG-FinFET-HV<sub>th</sub> admits P-type and N-type versions. All the possible variations those devices are shown in Figure 14. Notice that the P-type IG-FinFET-LV<sub>th</sub> implements a 2-input NAND (NAND2) operation, which can be related to two P-type SG-transistor associated in parallel. In turn, the P-type IG-FinFET-HV<sub>th</sub> implements the 2-input NOR (NOR2) operation, which can be related to two P-type SG-transistors associated in series. NAND2 and NOR2 configurations are shown in Figure 14(d) and in Figure 14(e), respectively.

Figure 14: IG-FinFET: (a) physical structure, (b) N-type IG-FinFET-HV $_{th}$  symbol, (c) N-type IG-FinFET-LV $_{th}$  symbol, (d) P-type IG-FinFET-HV $_{th}$  symbol and (e) P-type IG-FinFET-HV $_{th}$  symbol.

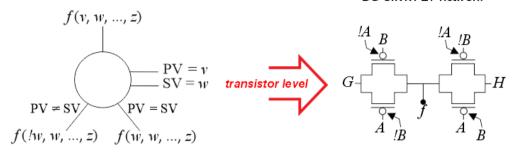

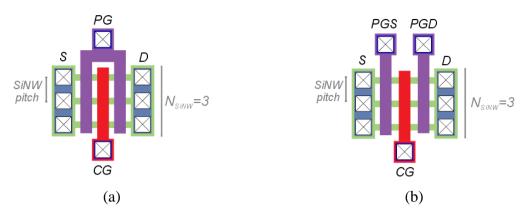

### 3.2.2 DG-SINWFET

DG-SiNWFET, as shown in Figure 15(a), is an ambipolar transistor. Therefore, the polarity (N-type or P-type) of the device is configurable via back gate, called polarity-gate (PG) (AMARÚ; GAILLARDON; DE MICHELI, 2013). If the signal on the PG is 0 the device acts as a P-type transistor, whereas if this signal is 1 the device acts as an N-type transistor. N-type and P-type configurations are shown in Figure 15(b) and in Figure 15(c), respectively. The other devices gate in DG-SiNWFET is the control-gate (CG), which defines the connectivity between the source and drain terminals. Such a device implements a 2-input exclusive-NOR (XNOR2) operation, as illustrated in Figure 15(d). Thus, a DG-SiNWFET can represent the arrangement of SG-transistors that corresponds to a XNOR2 Boolean function.

However, due to the signal electrical degradation, it is necessary to use two devices to build the XNOR2 logic gate (DE MARCHI *et al.*, 2012).

Figure 15: DG-SiNWFET and possible configurations: (a) physical structure, (b) N-type device, (c) P-type device and (d) XNOR operation.

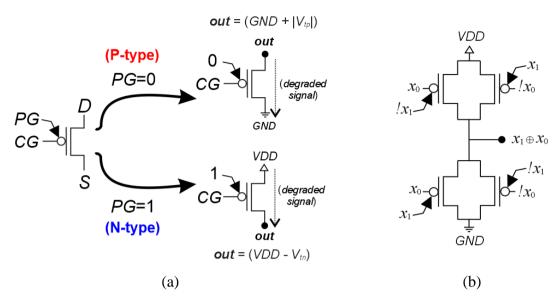

Similar to MOSFET device, the N-type DG-SiNWFET conduces a weak logic value 1, and the P-type DG-SiNWFET conduces a weak logic value 0. In this context, according to polarization of the DG-SiNWFET, its use can cause degradation of the electrical signal that pass through the transistor. Notice that, for the P-type transistor, presented in Figure 16(a), the logic value that passes through the transistor is at least GND+|Vtp|, where the Vtp is defined as the threshold value of P-type transistor. In turn, in N-type transistor, presented in Figure 16(a), the output value is at most VDD-Vtn, where Vtn is the threshold value of the N-type transistor. For both situations, the output signal is degraded due to the polarization of the device. In order to guarantee the correct output signal, the transmission gate configuration is needed. In this structure, P-type and N-type devices are used in parallel to ensure that one of the two transistors restores the electrical signal level in all cases (BEN-JAMAA; MOHANRAM; DE MICHELI, 2011). In Figure 16(b), a 2-input exclusive-OR2 (XOR2) logic gate illustrates the use of transmission gate approach. Notice that, in both the PU and PD plans, the transistors are duplicated in order to ensure the correct output signal level.

Figure 16: Signal degradation in SiNWFET: (a) degradation of signal in the N-type and P-type transistor, and (b) logic gate using transmission gate structure to restore the output signal.

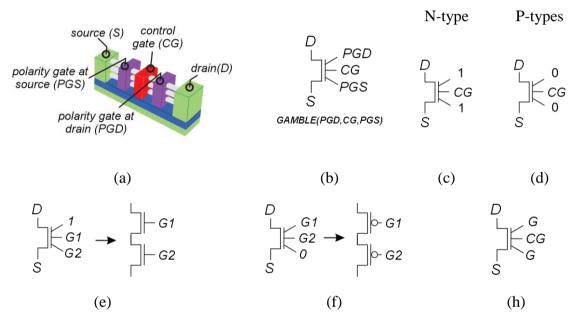

## 3.2.3 TIG-SINWFET

TIG-SiNWFET is an ambipolar device controlled by three independent gates: the control gate (CG), the polarity gate at source (PGS) and the polarity gate at drain (PGD) (ZHANG *et al.*, 2017). The physical structure of TIG-SiNWFET is depicted in Figure 17(a). The connection between drain and source terminals exists only when all three independent-gate present the same signal value (AMARÚ *et al.*, 2015). Therefore, the logic behavior of this device corresponds to the gamble function, in the following:

$$f = (x_0 \cdot x_1 \cdot x_2) + (!x_0 \cdot !x_1 \cdot !x_2)$$

(12)

Notice that, in this case, the transistor is on if the same logic level is applied to CG, PGS and PGD. Otherwise, the transistor is off. Similar to DG-SiNWFET, TIG-SiNWFET can be configured to act as an N-type or a P-type device according to its polarization (ZHANG *et al.*, 2017). A P-type device can be obtained by fixing PGS and PGD in 0. In this case, the transistor is on only when the CG assumes the logic value 0. In turn, an N-type device can be obtained by fixing PGS and PGD in 1. This way, the device is active only when the logic value 1 is applied to CG. N-type and P-type devices are shown in Figure 17(c) and in Figure 17(d), respectively.

Two others possible configurations for TIG-SiNWFET are the series SG transistors merging (ZHANG *et al.*, 2017). In this context, when only the PGD is fixed to 1, TIG-SiNWFET acts as an N-type device allowing the implementation of AND2 operation, as shown in Figure 17(e). On the other hand, when only the PGS is fixed to 0, it is possible to

obtain a P-type device that allows the implementation of NOR2 operation, as illustrated in Figure 17(f).

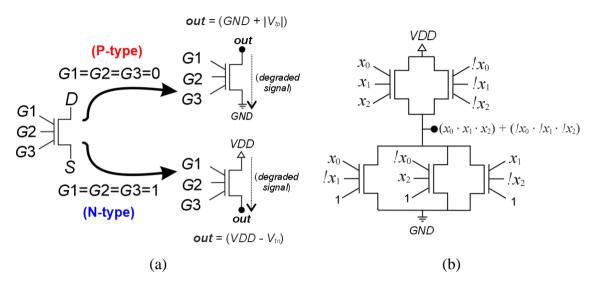

Additionally, TIG-SiNWFET can acts as DG-SiNWFET by applying the same logic level to PGS and PGD, as shown in Figure 17(h) (ZHANG; GAILLARDON; DE MICHELI, 2013). However, as discussed previously, this configuration may present degradation of the electrical signal that flows across the transistor. Similarly, the signal degradation problem may occur in gamble configuration, as illustrated in Figure 18(a). In both cases, the transmission gate structure may be adopted to ensure the correct signal. Figure 18(b) shows a logic gate that implements the gamble function using TIG-SiNWFET. Notice that the transmission gate structure is used in PU plan to ensure the correct signal transmission.

Figure 17: TIG-SiNWFET and possible configurations (a) physical structure (b) GAMBLE operation, (c) N-type device, (d) P-type device, (e) series nFET, (f) series pFET, and (h) XNOR configuration.

Figure 18: Signal degradation in TIG-SiNWFET: (a) degradation of signal in N-type and P-type transistors, and (b) logic gate using transmission gate structure to restore the output signal.

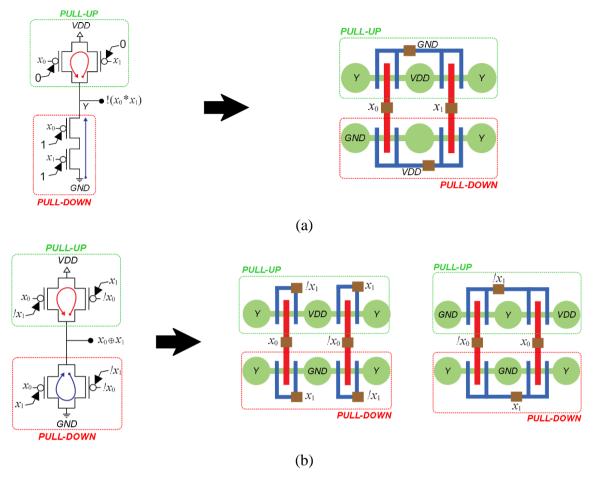

### 3.2.4 TIG-FGMOSFET

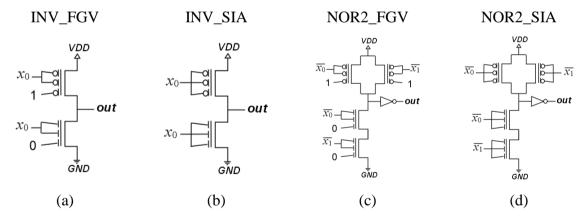

The last device considered in this work is the TIG-FGMOSFET, which is a transistor electrically controlled by a floating-gate, as shown in Figure 19(a). A general FGMOSFET transistor has *i*-inputs that are capacitively coupled to the floating gate (SHIBATA; OHMI, 1992). Such a device allows the computation of threshold logic functions (NEUTZLING *et al.*, 2015). However, in general case, the number of inputs of the device increases according to the number and weight assigned to input variables of the target threshold function. In this work, it is adopted a kind of TIG-FGMOSFET transistor similar to the one presented in (AMARÚ *et al.*, 2015).

The N-type version of TIG-FGMOS implements a 3-input majority (MAJ3) operation, as illustrated Figure 19(b). In this sense, such a transistor is only activated when at least two of its inputs are 1. Additionally, the N-type TIG-FGMOSFET can be configured to implement AND2 and OR2 operations. The AND2 configuration is attained by fixing one of the inputs to 0 value, as illustrated in Figure 19(c). In turn, the OR2 configuration is possible by fixing one input to 1 value, as shown in Figure 19(d). On the other hand, a P-type TIG-FGMOSFET implements a 3-input minority (MIN3) operation, as illustrated in Figure 19(e). Therefore, this device is active only when at least two inputs are 0. Moreover, the P-type device can implements the NAND2 operation by fixing one input to 0 value. Additionally, the NOR2 operation is implemented also through P-type transistor but by fixing one input to 1 value. The NAND2 and NOR2 configurations are depicted in Figure 19(f) and in Figure 19(g), respectively.

Figure 19: TIG-FGMOSFET and possible configurations: (a) physical structure (b) MAJ3 operation, (c) N-type device, (d) P-type device. Source: (DAVILA-SALDIVAR, *et al.*, 2014).

## 3.3 New challenges for MIGFET

As discussed before, MIGFET have the ability to implement into a single device ninput Boolean functions, such as AND2, OR2, MAJ3, XNOR2, among others. Thus, the

adoption of MIGFETs to design digital integrated circuits introduces new logic paradigms and

challenges that must be considered in order to obtain optimized solutions. For instance, the

most conventional SG transistor network generation methods explore the unitary relationship

between a literal and a logic switch. However, for MIGFET devices, such a relationship may

not be the best alternative, since more than one literal can be mapped into a single transistor

(POSSANI et al., 2016).

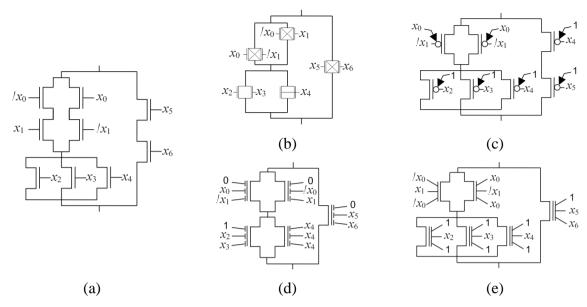

In order to exemplify this concept, it is shown in Figure 20(a) a switch network that implements the following Boolean function:

$$f = ((x_0 \oplus x_1) \cdot (x_2 + x_3 + x_4)) + x_5 \cdot x_6 \tag{13}$$

Notice that nine SG logic switches are needed to implement such a switch network. In this case, each literal of the logic expression is mapped directly to a logic switch. In turn, in Figure 20(b)-(e), MIGFET switches are used to build alternative networks for the logic equation (13). In all these cases, the SG switch merging performed by using MIGFET devices results in more compact network when compared to conventional single gate switch based implementation. Notice also that the number of switch merging performed through a given MIGFET depends on the target Boolean function and the type of MIGFET used to generate the switch network. For instance, the most compact network implementations for logic equation (13) are reached through TIG-FGMOSFET and IG-FinFET switches, since series and parallel switch merging are better exploited through these MIGFETs. In this case, each switch network comprises only five logic switches. In contrast, the switch networks obtained through DG-SiNWFET and TIG-SiNWFET comprise seven and six switches, respectively. In the case of DG-SiNWFET, only XOR2 merges can be explored, whereas TIG-SiNWFET allows performing series and XOR2 switch merges.

Figure 20: Switch networks corresponding to equation (13): (a) SG devices, (b) IG-FinFET, (c) TIG-FGMOSFET, (d) DG-SiNWFET, and (e) TIG-SiNWFET.

As demonstrated in the example above, at logic level, MIGFETs can be used to minimize the number of logic switches in a given network, so resulting in a more compact circuit (POSSANI *et al.*, 2016). However, at physical level, MIGFET devices tend to be penalized due to extra contact gates, as will be discussed in Chapter 4 (AMARÚ *et al.*, 2015). However, it is expected that the transistor merging performed at logic level compensates the additional area and delay costs when using MIGFET devices (ROSTAMI; MOHANRAM, 2011), (DATTA *et al.*, 2007) and (CHIANG *et al.*, 2006).

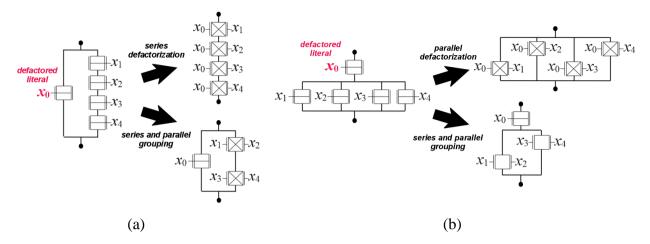

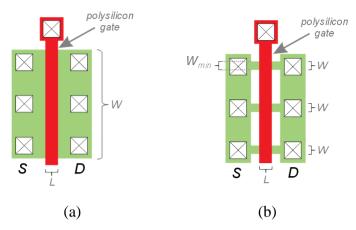

## 3.3.1 Methods for MIGFET-based network generation