## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

MATHEUS SCHUH

## Porting of an avionics ARINC 653 compliant RTOS

Monografia apresentada como requisito parcial para a obtenção do grau de Bacharel em Engenharia de Computação.

Trabalho realizado na École nationale supérieure d'informatique et de mathématiques appliquées de Grenoble (ENSIMAG) dentro do acordo de dupladiplomação UFRGS – Grenoble INP.

Orientador: Prof. Dr. Alexandre da Silva Carissimi (INF/UFRGS)

Co-Orientador: Prof. Dr. Matthieu Moy (ENSIMAG/INP)

#### CIP – Catalogação na Publicação

```

Schuh, Matheus

Porting of an avionics ARINC 653 compliant RTOS /

Matheus Schuh. -- 2016.

72 f.

Orientador: Alexandre da Silva Carissimi.

Trabalho de conclusão de curso (Graduação) --

Universidade Federal do Rio Grande do Sul, Escola de

Engenharia, Curso de Engenharia de Computação, Porto

Alegre, BR-RS, 2016.

1. Sistemas embarcados. 2. ARINC 653. 3.

Arquiteturas paralelas. 4. Sistemas operacionais de

tempo real. 5. Manycore. I. da Silva Carissimi,

Alexandre, orient. II. Título.

```

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Prof. Jane Fraga Tutikian Pró-Reitor de Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do Curso de Engenharia de Computação: Prof. Raul Fernando Weber Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## Porte de um RTOS Aviônico baseado na norma ARINC 653

Matheus Schuh<sup>1</sup>, Alexandre Carissimi<sup>1</sup>, Matthieu Moy<sup>2</sup>

<sup>1</sup>Instituto de Informática – Universidade Federal do Rio Grande do Sul (UFRGS) Caixa Postal 15.064 – 91.501-970 – Porto Alegre – RS – Brazil

<sup>2</sup>École nationale supérieure d'informatique et mathématiques appliquées (ENSIMAG) Institut polytechnique de Grenoble (Grenoble INP), France.

{mschuh,asc}@inf.ufrgs.br, Matthieu.Moy@grenoble-inp.fr

#### 1. Introdução

Kalray é uma empresa pioneira na concepção de processadores *many-core*. Seu último lançamento, o Multi-Purpose Processor Array (MPPA<sup>®</sup>) Bostan conta com 288 núcleos programáveis em C/C++ com interfaces de Entrada/Saída (E/S) de alta velocidade. Essas características asseguram alto desempenho com baixo consumo (entre 10W e 20W) e resposta em tempo real.

Inúmeras aplicações podem se beneficiar de tais particularidades e, entre elas, estão os sistemas utilizados na indústria aviônica. O MPPA<sup>®</sup> oferece previsibilidade temporal, i.e. capacidade de calcular deterministicamente quanto tempo uma operação levará, e particionamento espacial, i.e. garantia de não-interferência entre espaços de memórias através de isolamento físico. Esses aspectos são cruciais para sistemas aeronáuticos.

Este resumo estendido irá apresentar o trabalho de porte de um Real-Time Operating System (RTOS) para a arquitetura do processador MPPA<sup>®</sup> Bostan. O documento está dividido em 6 seções, incluindo esta introdução. Na seção 2 é exposto o contexto e a motivação do projeto. Na seção 3 há uma análise de mercado, da metodologia de desenvolvimento de aplicações aeronáuticas e das soluções existentes em termos de sistemas operacionais (SOs). A seção 4 aborda os detalhes de implementação mais importantes e, por fim, na seção 5 os resultados do trabalho são mostrados seguidos pela conclusão na seção 6.

## 2. Contexto e Motivação

A Kalray foi fundada em 2008 por antigos funcionários da STMicroelectronics que possuíam experiência no desenvolvimento de arquiteturas paralelas e que acreditavam fortemente em seu potencial futuro. É uma empresa do tipo *fabless*<sup>1</sup>, contando com uma equipe de hardware completa que realiza desde a concepção até a verificação de funcionalidade do processador.

Além do projeto de hardware, a empresa fornece também soluções de software visando integrar e explorar a capacidade de seu produto físico, entregando um pacote completo de acordo com as necessidade de cada cliente. Atualmente, os principais nichos de mercado atingidos são centros de processamento de dados (encriptação, compactação) e a indústria automobilística (processamento de imagem para veículos autônomos).

<sup>&</sup>lt;sup>1</sup>Empresa que realiza o *design* de um circuito, externalizando sua produção.

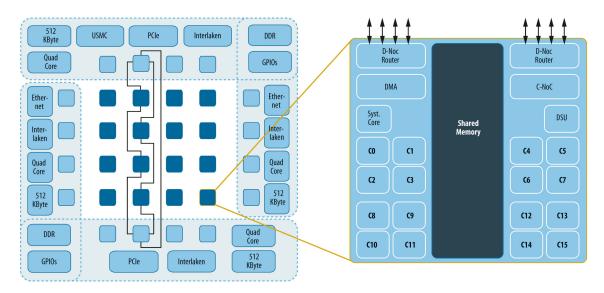

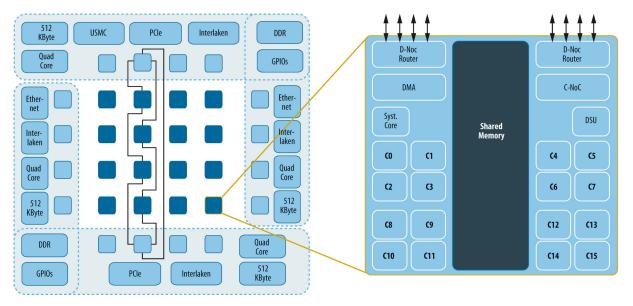

A arquitetura do MPPA<sup>®</sup> Bostan é composta por 288 núcleos de 32, ou 64 bits, que recebem instruções do tipo *Very Long Instruction Word (VLIW)*. Desses núcleos, 256 são para uso geral e 32 para gestão de recursos. Os núcleos são ainda subdivididos em 16 clusters de cálculo com 2MB de *Shared MEMory (SMEM)* e 2 clusters de E/S com 1MB de SMEM e 2GB de *Double Data Rate (DDR)* para uso geral.

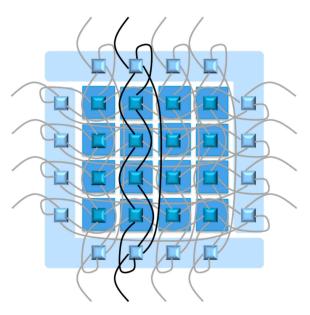

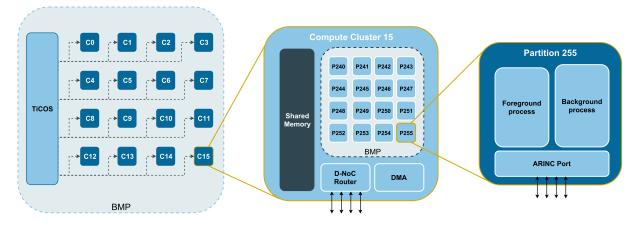

A comunicação interna no processador é realizada através de um *Network on Chip* (*NoC*) temporalmente previsível e eficiente. A comunicação externa é garantida através de interfaces de E/S dos tipos *Peripheral Component Interconnect (PCI)* e Ethernet. Uma visão geral da arquitetura do processador é apresentada na figura 1.

Figura 1. Visão geral do MPPA® Bostan com detalhe para um cluster de cálculo

O projeto, por estar inserido em um contexto aviônico, tem requisitos de um sistema crítico, onde falhas ou mal funcionamento podem representar mortes ou lesões e grande custo por perda de equipamento. Portanto, tanto o hardware, quanto o software, devem oferecer disponibilidade temporal, confiabilidade de execução, segurança contra falhas e proteção contra intrusões.

As características arquiteturais, previamente mencionadas, asseguram o MPPA<sup>®</sup> como um processador pronto para a computação crítica. Três aspectos são essenciais para isso:

- Computação determinística: duas operações realizadas sobre os mesmos dados de entrada terão a mesma sequência de instruções, executadas na mesma ordem.

- Tempos de resposta restritos: duas operações realizadas sobre os mesmos dados de entrada levarão o mesmo tempo.

- *Worst-Case Execution Time (WCET)*: capacidade de calcular o pior caso temporal de um sistema somando os piores casos individuais de seus componentes.

Além disso, elementos de hardware que tem efeito histórico, como a *cache*, podem ser desativados para evitar alterações temporais entre execuções. Ainda, a organização arquitetural do MPPA<sup>®</sup> em *clusters* permite a replicação de operações, disponibilizando redundância em caso de falhas.

Somando com o nível de criticalidade presente no hardware, a motivação principal do projeto vem da busca da indústria aeronáutica por um sistema que exponha uma camada de software com uma *Application Programming Interface (API)* padronizada, capacidade de particionamento temporal e espacial e que possa passar por um processo de certificação. Dessa maneira, o porte de um RTOS, que já atende os requisitos previamente citados, será feito para capacitar o MPPA<sup>®</sup> em termos de hardware e software para receber aplicações aviônicas que seguem a norma ARINC 653.

Na próxima seção explora-se em detalhe as exigências da camada de software revisitando como elas eram atingidas em sistemas aeronáuticos antigos e como deseja-se garanti-las atualmente.

#### 3. Embasamento técnico

#### 3.1. Metodologias de Desenvolvimento

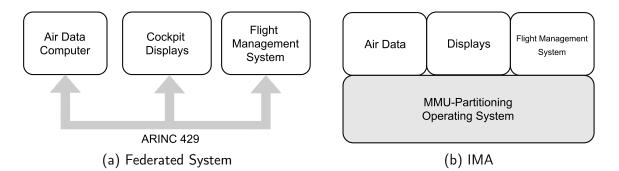

Tradicionalmente a indústria aeronáutica utiliza uma metodologia denominada *Federated* para a concepção dos sistemas eletrônicos das aeronaves. Essa metodologia é baseada em unidades independentes e construídas especificamente para uma aplicação, e.g. controle do *display* da cabine de pilotagem. Tais unidades se comunicam através de um barramento que segue a norma *Avionics Application Standard Software Interface (ARINC)* 429 visando garantir a não-interferência e requisitos temporais do sistema.

Algumas desvantagens da metodologia *Federated* são: subutilização de recursos, visto que as unidades são especializadas e, possivelmente, carregam elementos que poderiam ser reaproveitados em outras partes do sistema; e o processo de certificação é realizado no sistema como um todo, sendo necessária a recertificação a cada troca ou adição de unidade.

Visando suprir tais deficiências a metodologia *Integrated Modular Avionics (IMA)* surgiu. Ela utiliza como base um SO onde partições de aplicação são executadas (equivalentes às unidades *Federated*). Uma partição é, portanto, um contêiner para uma aplicação, podendo abrigar múltiplos processos, porém, preservando a capacidade de isolamento temporal e espacial (em memória) entre os processos e outras partições. As aplicações aeronáuticas, e.g. controle do *display* da cabine, são assim construídas obtendo maior portabilidade e modularidade. A portabilidade vem do fato de que, como o SO é construído segundo uma norma específica, as aplicações desenvolvidas utilizando um sistema podem ser facilmente portadas para outro que segue a mesma norma. A modularidade vem do isolamento entre as partições

Essa modularidade permite que aplicações com diferentes níveis de criticidade sejam executadas em paralelo no mesmo sistema. Como consequência, todo o sistema pode ser implementado em um único *chip*, ao contrário de múltiplos sistemas eletrônicos integrados, existe uma grande economia em peso e em consumo energético. O processo de certificação, entretanto, é ligeiramente mais complicado, pois, o SO deve seguir estritamente as normas de concepção, bem como as aplicações. Uma vez que o longo processo de certificação, tanto para o sistema, quanto para as aplicações é concluído, os mesmo podem ser substituídos por outros sistemas e aplicações que também possuam certificação, sem necessidade de recertificação.

## 3.2. A norma ARINC 653

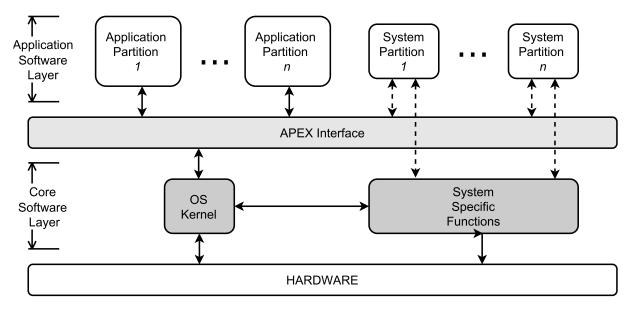

Com o desenvolvimento e a consolidação do conceito IMA, a necessidade de uma norma para estruturar o SO responsável por gerenciar todo o sistema era iminente. A norma ARINC 653 surgiu com o objetivo de preencher tal lacuna. Essa norma especifica basicamente dois aspectos do SO: sua interface e seus componentes.

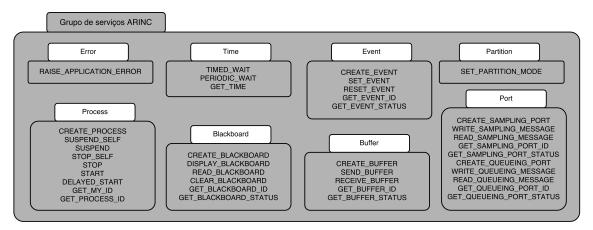

A interface define como será a comunicação entre aplicações e o SO. Essa interface foi denominada de APplication/EXecutive (APEX), e é uma lista de funções para a gestão de partições, processos, tempo, memória e comunicação. Os componentes definem as estruturas básicas necessárias no SO para que ele seja capaz de fornecer a interface APEX, entre elas um escalonador customizável, possibilidade de comunicação intra e inter partições e gestão de recursos de hardware como memória e frequência.

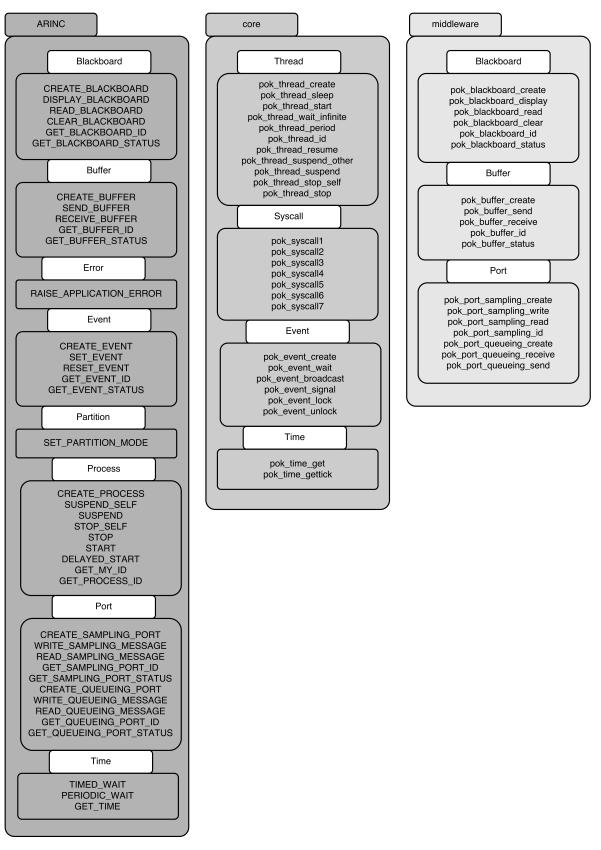

A interface APEX é resumida e agrupada nos chamados grupos de serviço ARINC. Funções semelhantes compõem o mesmo grupo e essa organização auxilia tanto na implementação quanto nos testes de um SO baseado na norma ARINC 653.

Figura 2. Grupo de serviços ARINC e suas funções

## **3.3. TiCOS**

Uma análise dos SOs disponíveis no mercado foi feita para a definição de qual deles seria de fato portado para o processador MPPA<sup>®</sup>. Os aspectos mais relevantes foram ter código aberto, haver possibilidade de contato com os desenvolvedores e respeito estrito da norma ARINC 653.

O Time-Composable Real-Time Operating System (TiCOS) foi escolhido por satisfazer os aspectos citados anteriormente. Além disso, o TiCOS tem boa documentação, está disponível publicamente e possui colaboradores ativos. O TiCOS foi resultado da tese de doutorado de Andrea Baldovin e baseado em outro sistema chamado de POK. Sua implementação original é voltada para a arquitetura PowerPC da IBM que é *single-core*. Além disso, a adoção do TiCOS também foi uma recomendação de parceiros externos da Kalray neste projeto.

## 4. Implementação

## 4.1. Objetivo

Como citado, o TiCOS tem sua implementação original voltada para a arquitetura *single-core* PowerPC da IBM. O código é composto principalmente por C e *assembly* específico

da Instruction Set Architecture (ISA) PowerPC.

O objetivo deste trabalho é portar o TiCOS para a arquitetura MPPA<sup>®</sup> da Kalray, preservando o aspecto *single-core* do núcleo (*kernel*) do SO em um primeiro momento. A linguagem C para o código foi mantida graças ao suporte prévio do ambiente de software do processador. A maior mudança vem da alteração do código *assembly*, específico para a arquitetura MPPA<sup>®</sup>, e o uso de uma camada de virtualização que será apresentada nas próximas seções, o mOS.

#### 4.2. Arquitetura

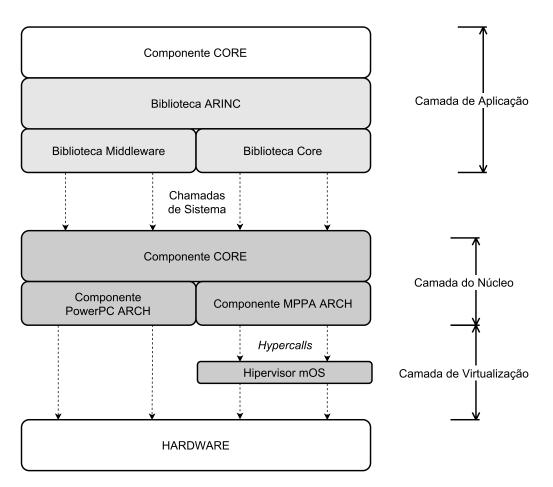

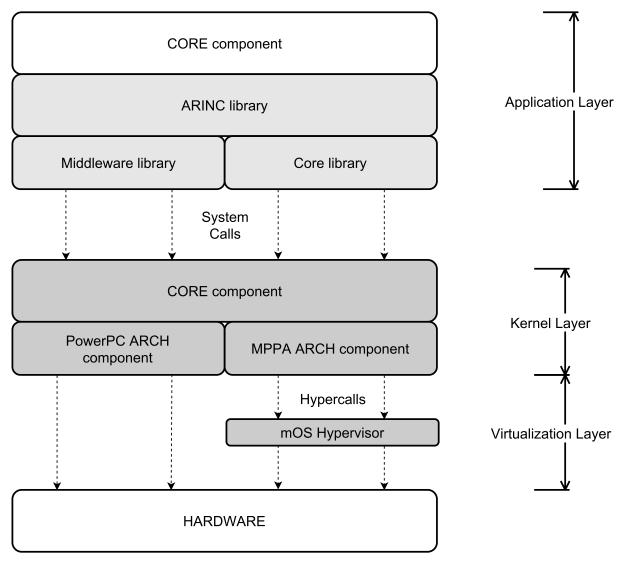

A arquitetura do TiCOS é dividida em duas camadas: aplicação e núcleo. A camada de aplicação é formada por um componente *core* que expõe ao usuário as funcionalidades do sistema e se apoia nas bibliotecas ARINC (contém as interfaces da APEX segundo a norma), *middleware* (responsável por tratar os serviços de comunicação) e *core* (responsável por tratar os demais serviços, e.g. criação de *threads*, controle de tempo). A comunicação entre a camada de aplicação (que é executada em nível de usuário) e o núcleo (executado originalmente em modo privilegiado) é feita através de chamadas de sistema.

A camada do núcleo é formada também por um componente *core* que é o ponto de entrada das chamadas de sistema e se comunica com o componente dependente da arquitetura (na implementação original denominado PowerPC *arch*). Esse último componente é o responsável pelo acesso aos recursos de hardware através de instruções específicas do processador.

O porte para uma nova arquitetura deve, em teoria, modificar apenas o último componente mencionado. Dessa maneira, um componente MPPA<sup>®</sup> *arch* foi adicionado e, entre a camada do núcleo e o hardware, foi introduzida a camada de virtualização composta pelo mOS. A figura 3 mostra a visão global da arquitetura do TiCOS.

## 4.3. O Hipervisor mOS

A Kalray optou por encapsular todo seu ambiente de software com um hipervisor que nada mais é do que uma camada virtual entre o hardware e qualquer aplicação, até mesmo um SO de terceiros.

O hipervisor mOS é um exonúcleo, um tipo específico de núcleo de SO extremamente minimalista e pequeno. Esse conceito foi introduzido pelo grupo de sistemas operacionais paralelos e distribuídos do MIT, em 1994. Uma de suas principais características é não forçar abstrações de hardware para as próximas camadas de software, construindo um *kernel* com poucas funcionalidades mas que entrega maior flexibilidade às aplicações. Um exonúcleo deve primordialmente garantir proteção, através da virtualização, e multiplexação de recursos de hardware.

Qualquer aplicação, ou SO, que utiliza um hipervisor é, portanto, considerada uma biblioteca, ou um SO hóspede, já que são executados em nível de usuário. Algumas características particulares do mOS da Kalray são: tamanho reduzido (apenas 32KB), presença de uma estrutura, denominada *scoreboard*, que armazena o estado virtual do sistema e uso de *hypercalls* que são chamadas de sistema com pré e pós processamento de dados.

Figura 3. Visão arquitetural do TiCOS com o componente MPPA®

## 4.4. Metodologia de Desenvolvimento

Para este projeto a mesma metodologia de implementação foi utilizada para cada nova funcionalidade prevista pelo sistema original. Ela é descrita abaixo:

- 1. Análise do código do TiCOS e das estruturas presentes no processador PowerPC;

- 2. Estudo de estruturas equivalentes no processador MPPA<sup>®</sup>;

- 3. Identificação de funções existentes no hipervisor mOS que explorem essas estruturas;

- 4. Utilização da API do mOS ou implementação da funcionalidade.

As próximas seções apresentam detalhes de implementação e das estruturas de suporte de hardware presentes no processador, mostrando os principais pontos de interesse em um trabalho de porte de um SO.

## 4.5. Suporte de Arquitetura

O TiCOS necessita de alguns recursos de hardware comuns e presentes na maioria dos processadores para seu funcionamento. O primeiro deles, usado no isolamento temporal entre partições, é um registrador para o controle do tempo global do sistema juntamente com um registrador decrementador. O isolamento temporal garante que apenas uma partição estará em execução no sistema em um determinado *slot* de tempo. O

MPPA<sup>®</sup> possui uma estrutura no *scoreboard* que mantém um *timestamp* global e virtualiza o registrador físico decrementador de 64 bits. A API do mOS fornece acesso a ambos.

O segundo recurso é a definição de um contexto do estado arquitetural dos registradores para seu armazenamento e restauração. O MPPA<sup>®</sup> possui 64 registradores para uso geral e 50 registradores para funções específicas. A definição dos registradores importantes para o contexto foi feita em uma struct em C e macros *assembly* são utilizadas para salvar e restaurar o contexto.

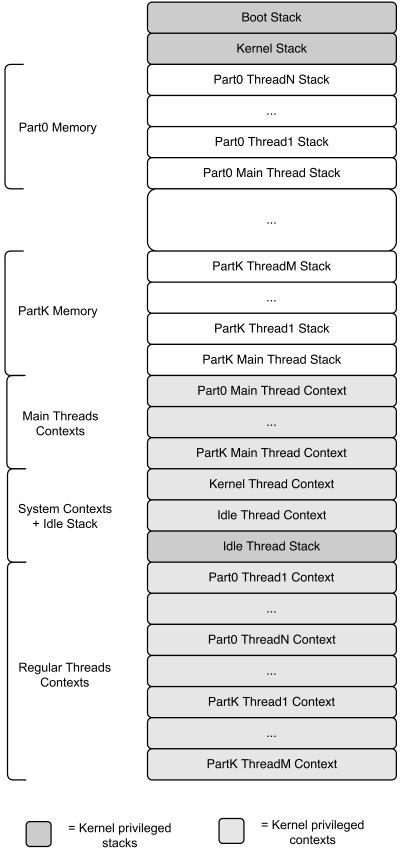

O terceiro recurso é a gestão de memória através de uma *Memory Management Unit (MMU)* para o particionamento espacial. Embora o MPPA<sup>®</sup> possua tal suporte em hardware, ele é limitado, seu uso é complexo e desencorajado pelos desenvolvedores. A solução arquitetada foi separar a compilação do núcleo e das partições em endereços fixos, i.e. código absoluto, sem amarração dinâmica com a MMU. O ligador então se encarrega de empacotá-los em um objeto único (multibinário).

#### 4.6. Casos especiais

Além das estruturas de hardware citadas, o TiCOS requer suporte extra de software em alguns casos especiais. Quanto ao primeiro dos casos, o sistema original foi concebido para ser *standalone*, i.e. não depender de nenhuma biblioteca externa para sua compilação. Assim sendo, o processo de compilação do sistema é feito usando a opção --nodefaultlibs do gcc. Para suprir a ausência de algumas funcionalidades básicas foi necessária uma implementação minimal da libC, bem como sua compilação e posterior ligação com o restante do sistema. Funções como putchar e exit foram escritas usando chamadas de sistema próprias do MPPA<sup>®</sup>. Rotinas aritméticas de baixo nível como \_\_divdf3, \_\_modis3, \_\_umodis3, divmodsi4 foram reaproveitadas de outros módulos já presentes no ambiente de software da Kalray.

O segundo caso vem da atrelação entre as chamadas de sistema e a ISA em questão, necessitando de um trabalho de porte tanto na instrução *assembly* utilizada, quanto no tratador das chamadas. É um trabalho vital para o funcionamento do sistema, visto que os serviços ARINC que necessitam acessar funcionalidades do núcleo do sistema terminam em chamadas de sistema.

Na ISA do MPPA<sup>®</sup> a instrução *assembly* é a scall. Ao ser executada, ela é interceptada pelo mOS, que redireciona o fluxo da aplicação para o tratador de chamadas de sistema. O tratador é responsável por salvar o contexto de execução, trocar as pilhas entre partição e núcleo e chamar as próximas funções do sistema que irão completar o fluxo de execução. O registro do tratador de chamadas de sistema é feito no *scoreboard* do mOS durante a inicialização do sistema.

O terceiro caso trata do suporte aos dois tipos de troca de contexto presentes no sistema original: dirigidas por interrupção e explícitas. Para isso, além de um registrador decrementador e de *timestamp*, é requerido o conhecimento do sistema de interrupções da arquitetura e o registro de um tratador, semelhante ao de chamadas de sistema.

A troca de contexto dirigida por interrupção ocorre no momento em que o registrador decrementador atinge zero e levanta uma interrupção, que interrompe o fluxo normal de execução do processador. Essa interrupção é então interceptada pelo mOS e redirecionada para o tratador que se encarregará da troca de contexto. Esse é um tipo de escalonamento preemptivo de partições. O registro de tal tratador também é feito no scoreboard do mOS durante a inicialização do sistema.

A troca de contexto explícita ocorre quando uma partição decide esperar pelo próximo período de execução ou por um evento. A partição faz uma chamada de sistema que invoca o escalonador, que por sua vez retira a atual partição da execução. Esse é um tipo de escalonamento cooperativo, porém que ainda respeita o aspecto tempo real, visto que a próxima partição só será executada quando o *slot* de tempo reservada a ela começar.

#### 5. Resultados obtidos

Antes de apresentar os resultados é importante mencionar o processo de validação utilizado e as dificuldades encontradas. Idealmente, ao desenvolver qualquer software visa-se isolar suas camadas e funções para posteriormente criar testes unitários. Mesmo com a arquitetura modular do TiCOS (seção 4.2), a utilização de testes unitários não foi possível, pela vinculação entre as camadas de núcleo e de partições de aplicação em único objeto.

Resta então como vetor de teste aplicações que serão compiladas e executadas juntamente com o TiCOS. As aplicações de teste tem duas origens: códigos exemplo fornecidos juntamente com o sistema original e códigos obtidos através de um gerador automático que tem como entrada arquivos XML.

Os códigos exemplo possuíam os estímulos necessários para avaliar a maioria dos grupos de serviço ARINC. Não estavam incluídos testes para os grupos EVENT, BLACKBOARD, BUFFER e PORT. Ainda, o sistema não estava sendo testado em termos de escalabilidade, isto é, o exemplo que mais estressava o TiCOS em gestão temporal e espacial possuía 3 partições com 1 processo cada.

Assim, um gerador automático de código foi usado para complementar os casos de teste. Foram criadas aplicações para estimular os serviços EVENT e PORT e aplicações com 4 partições e 1 ou 2 processos cada. O gerador foi necessário, pois o código do núcleo e das partições é parametrizável através de arquivos do tipo deployment.h e deployment.c que possuem diretivas de compilação e são de difícil alteração manual. Esses arquivos, além de *templates* para o código fonte das aplicações, são automaticamente criados pelo gerador com arquivos xml como entrada, que descrevem de maneira declarativa as partições, processos e comportamento esperado de uma aplicação.

Os critérios de avaliação para a execução dos testes foram:

- Funcionais, i.e. se a execução da aplicação está em conformidade com seu código fonte. Para isso uma análise visual baseada em mensagens de *debug* foi utilizada;

- Estruturais, i.e. estado arquitetural dos registradores durante a execução de serviços ARINC que podem modificá-los;

- Temporais, i.e. estado dos registradores de *timestamp* e de decremento em momentos chave da execução, como a troca de contexto.

Cada uma das aplicações teste explorava um ou mais conjunto de serviços ARINC fornecido pelo sistema, visando-o testar na sua integridade. A execução foi feita primeiramente em simulação *Instruction Set Simulator (ISS)*, que é mais rápida e facilita testes com funções de E/S. Posteriormente a execução foi feita em hardware, buscando avaliar os registradores físicos e aspectos temporais através do uso do gdb, o que não está com-

pletamente modelado na simulação. Após ou durante a execução os critérios de avaliação foram então aplicados para validar ou reprovar o teste.

Os resultados dos testes são apresentados na tabela 1. As células da tabela que apresentam o símbolo  $\checkmark$  evidenciam que o grupo de serviço ARINC correspondente foi validado através de uma aplicação executada com o TiCOS, em simulação, ou em hardware (dependendo da coluna), segundo os critérios previamente citados. As células que apresentam o símbolo  $\varkappa$  evidenciam que o grupo de serviço não foi testado. Em especial os grupos *blackboard* e *buffer*, que fornecem comunicação intra partição, não foram testados em nenhuma das aplicações executadas.

| Grupo de serviço ARINC | Simulação | Hardware |

|------------------------|-----------|----------|

| ERROR                  | 1         | 1        |

| TIME                   | 1         | 1        |

| PARTITION              | 1         | 1        |

| PROCESS                | 1         | 1        |

| EVENT                  | 1         | 1        |

| BLACKBOARD             | ×         | X        |

| BUFFER                 | ×         | X        |

| PORT                   | 1         | ✓        |

Tabela 1. Resultados da validação em simulação e hardware

O produto final é o RTOS TiCOS portado com sucesso para a arquitetura MPPA<sup>®</sup>, com exceção de dois grupos de serviço que não possuíam alta prioridade no projeto segundo a especificação da Kalray. Além disso melhorias no processo de compilação foram feitas, para que todos exemplos presentes no diretório do sistema pudessem ser compilados de uma só vez e posteriormente executados através de comandos simples no MPPA<sup>®</sup>.

## 6. Conclusão

Os resultados da validação apontam que o porte do TiCOS foi feito com sucesso para o MPPA<sup>®</sup>. Esse trabalho foi de extrema importância na construção de uma prova de conceito da arquitetura para aplicações aviônicas e ressaltou suas características de criticidade e tempo real.

O projeto de porte de um SO é um ótimo tópico, pois incentiva a análise de código de terceiros, requer profundo conhecimento em C e *assembly* e familiaridade com a arquitetura para a qual o sistema está sendo portado. O uso do mOS como hipervisor trouxe acessibilidade aos recursos de hardware de maneira fácil, acelerando a curva de aprendizado e a realização de algumas tarefas. Entretanto, sua obrigatoriedade acarreta na perda da flexibilidade presente em sistemas *bare-metal*.

Como já dito anteriormente, o porte teve um aspecto *single-core* onde o núcleo e as partições são executados no mesmo *core*, isolados temporalmente e dispostos na SMEM em endereços fixos. Entretanto, um isolamento espacial garantido por estruturas de hardware é necessário para um processo de certificação. Trabalhos futuros podem explorar a MMU do MPPA<sup>®</sup> para obter tal característica.

No intuito de explorar a capacidade de processamento do MPPA<sup>®</sup> um porte a nível de *cluster* pode ser realizado, ainda em fase de estudo. A primeira proposta foi do

tipo Asymmetric multiprocessing (AMP), com o núcleo sendo executado em um *core* e as partições aplicações em *cores* distintos do mesmo *cluster*. Um porte a nível do MPPA<sup>®</sup> completo também está em estudo. Nesse caso, o núcleo seria executado em um *cluster* de E/S e as aplicações em cores distintos de *clusters* distintos, sendo o NoC responsável pela comunicação entre partições.

Grenoble INP – ENSIMAG École Nationale Supérieure d'Informatique et de Mathématiques Appliquées

# Final Study Project Report

Undertaken at Kalray

# Porting of an avionics ARINC653 compliant RTOS

Matheus SCHUH 3A – SLE

22 February 2016 - 22 July 2016

Kalray SA 445 Rue Lavoisier 38330 Montbonnot Saint Martin Internship responsible Benoît de DINECHIN School Tutor Matthieu MOY

# Acknowledgements

I would like first to thank **Kalray** for offering me the opportunity to undertake my internship at the Montbonnot site, for welcoming me in its facilities and for giving me all the required material to accomplish my tasks.

I thank particularly **Benoît de Dinechin** for offering me this internship, for trusting me in the accomplishment of the given tasks and for supporting me in fullfilling them.

I am also grateful to **Matthieu Moy** for accepting to be the tutor of this project, for the advices given and the revisions of the report.

I also thank **Pierre Guironnet de Massas** and **Samuel Jones** for their constant support in all OS, MPPA<sup>®</sup> architecture and general doubts that came up throughout the internship. Finally, I would like to thank all the **Core Software Team members** for receiving me during these 5 months, for helping me in doubts and difficulties and also for their kindness and patience with eventual french communication problems.

# Abstract

The avionics industry has a huge interest in improving their systems through better performance and lower power consumption while maintaining the safety requirements. Kalray's processor comes in handy and is able to meet these needs with a proper software environment.

The work presented in this document is focused on porting a Real-Time Operating System (RTOS) to Kalray's processor. This OS provides resource management and a programming interface that respects the ARINC 653 avionics standard.

The port was successfully accomplished as the majority of the examples are functional on simulation and on hardware. Even though, it is still a work in progress as some ARINC services are not completely working and optimizations exploiting the processor architecture can be made.

**Keywords:** Kalray, MPPA, ARINC653, embedded systems, C, assembly, processor, many-core, APEX, RTOS, TiCOS, POK.

# Résumé

L'industrie avionique porte un grand intérêt à l'amélioration de leurs systèmes en ce qui concerne la performance et la consommation énérgétique, tout en respect les contraintes de sûreté. Le processeur Kalray permet de répondre à ces besoins par son environnement logiciel standard.

Ce document présente le travail de portage d'un système d'exploitation temps-réel (RTOS) au processeur de Kalray. Cet OS assure la gestion des ressources et une interface de programmation qui respecte la norme avionique ARINC 653.

Le portage a été accompli avec succès, vu que la plupart des exemples sont fonctionnels en simulation et en matériel. De toute façon, cela est encore un travail en progrès, car certains services ARINC ne marchent pas et des optimisations qui exploitent l'architecture du processeur peuvent toujours être faites.

**Mot-clés:** Kalray, MPPA, ARINC653, systèmes embarqués, C, assembleur, processeur, many-core, APEX, RTOS, TiCOS, POK.

# Contents

| Ac | knowledgments                                                                                                                                                                                                                   | 1                                      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| AŁ | stract                                                                                                                                                                                                                          | 2                                      |

| Ré | sumé                                                                                                                                                                                                                            | 3                                      |

| Gl | ssary                                                                                                                                                                                                                           | 7                                      |

| 1  | Introduction                                                                                                                                                                                                                    | 8                                      |

| 2  | Context2.1The company2.2The site2.3The team                                                                                                                                                                                     | 9                                      |

| 3  | The internship project         3.1       The MPPA processor         3.1.1       Global Architecture         3.1.2       The k1b VLIW core         3.2       Motivation         3.3       Objectives                             | 11<br>12<br>14                         |

| 4  | Technical aspects         4.1       Time-Critical Computing on the MPPA                                                                                                                                                         | 16<br>16<br>17<br>17<br>17             |

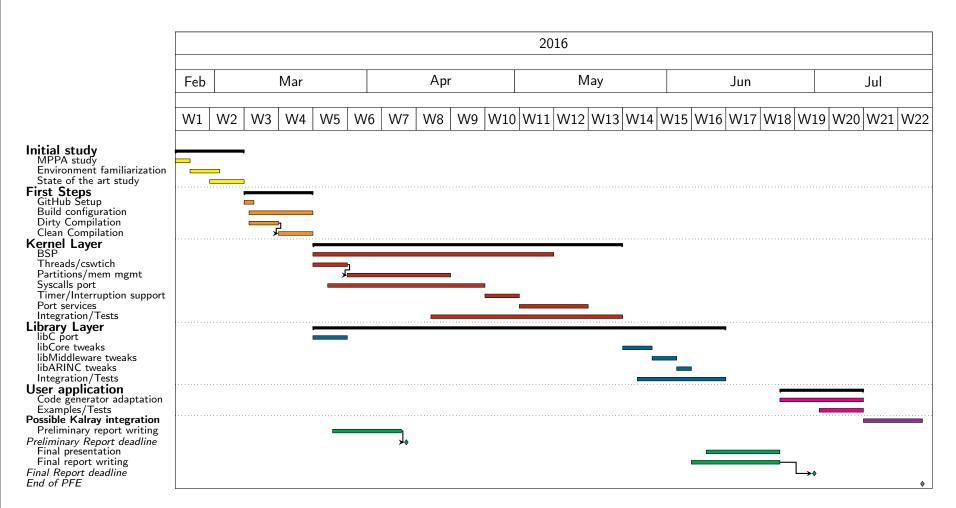

| 5  | Solution undertaken         5.1 OS choice         5.2 mOS         5.3 Porting steps         5.3.1 Kernel Layer         5.3.2 Library Layer         5.3.3 Build chain         5.4 Employed tools         5.5 Evaluation protocol | 22<br>23<br>23<br>24<br>24<br>24<br>26 |

| 6  | Implementation         6.1       Architectural modifications         6.1.1       Clock         6.1.2       Thread context         6.1.3       Memory management         6.2       Core modifications                            | 27<br>28<br>30                         |

|                  | 6.3<br>6.4<br>6.5               | LibC implementation       3         Library modifications       3         6.4.1 System Calls Implementation       3         Context Switch       3         6.5.1 Interrupt-driven context switching       3 | 33<br>33<br>34<br>34<br>35<br>35<br>37 |  |

|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| 7                | Obta                            | ained results                                                                                                                                                                                               | 39                                     |  |

|                  | 7.1                             | Validation                                                                                                                                                                                                  | 39                                     |  |

|                  | 7.2                             | Simulation                                                                                                                                                                                                  | 40                                     |  |

|                  | 7.3                             | Hardware                                                                                                                                                                                                    | 40                                     |  |

|                  | 7.4                             | Final Product                                                                                                                                                                                               | 41                                     |  |

|                  | 7.5                             | Future work                                                                                                                                                                                                 | 41                                     |  |

| 8                | -                               |                                                                                                                                                                                                             | 13                                     |  |

|                  | 8.1                             |                                                                                                                                                                                                             | 43                                     |  |

|                  | 8.2                             |                                                                                                                                                                                                             | 44                                     |  |

|                  | 8.3                             |                                                                                                                                                                                                             | 45                                     |  |

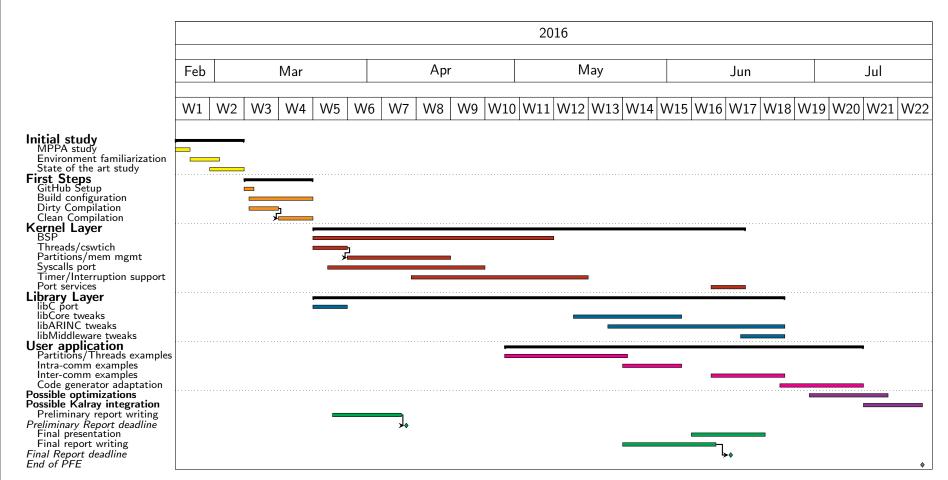

|                  | 8.4                             | Final planning analysis                                                                                                                                                                                     | 46                                     |  |

| 9                | Inte                            | rnship appraisal 4                                                                                                                                                                                          | 17                                     |  |

| 10 Conclusion 48 |                                 |                                                                                                                                                                                                             |                                        |  |

| Re               | feren                           | ices 4                                                                                                                                                                                                      | 19                                     |  |

| Α                | MP                              | PA additional content 5                                                                                                                                                                                     | 50                                     |  |

| В                | <b>TiC</b><br>B.1<br>B.2<br>B.3 | Listings                                                                                                                                                                                                    | 52<br>52<br>54<br>57                   |  |

# List of Figures

| 1  | Two Kalray MPPA <sup>®</sup> -256 processors in a board $\ldots$                                                                                               | 9  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Multi-Purpose Processor Array (MPPA®)2-256 Bostan Overview with a Com-                                                                                         |    |

|    | pute Cluster (CC) zoomed view                                                                                                                                  | 11 |

| 3  | $MPPA^{®}  NoC in detail \ldots \ldots$ | 12 |

| 4  | Kalray k1b pipeline                                                                                                                                            | 13 |

| 5  | Diagram exposing the differences between federated and IMA systems                                                                                             | 18 |

| 6  | Generic structure of an Avionics Application Standard Software Interface (AR-                                                                                  |    |

|    | INC) 653 compliant system                                                                                                                                      | 18 |

| 7  | ARINC 653 Part 4 proposed implementation on the $MPPA^{\mathbb{R}}$                                                                                            | 19 |

| 8  | TiCOS high level architecture with $MPPA^{\mathbb{R}}$ entity $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                               | 21 |

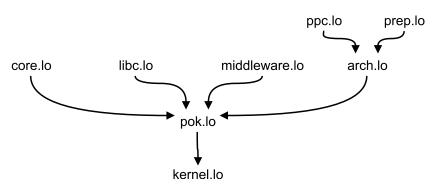

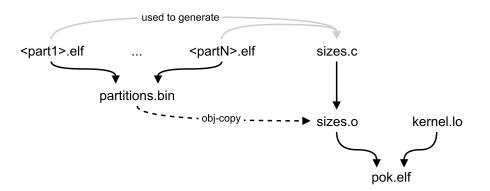

| 9  | Visualization of the kernel build process and its compilation objects                                                                                          | 24 |

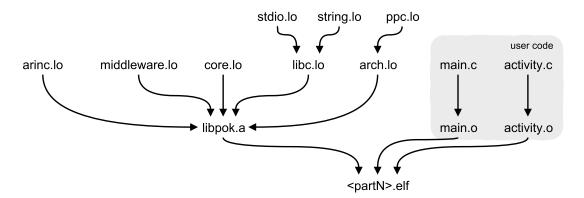

| 10 | Visualization of a partitionN build process and its compilation objects                                                                                        | 25 |

| 11 | Visualization of a partitionN build process and its compilation objects                                                                                        | 25 |

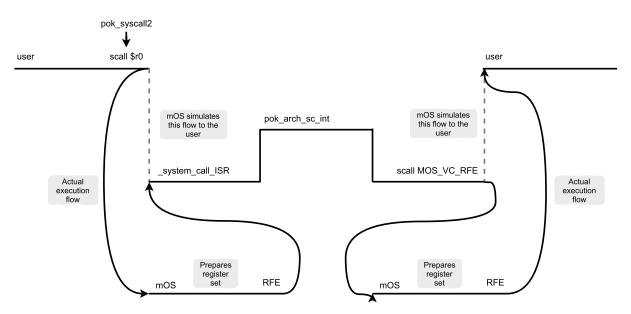

| 12 | System call execution flow with mOS interference                      | 35 |

|----|-----------------------------------------------------------------------|----|

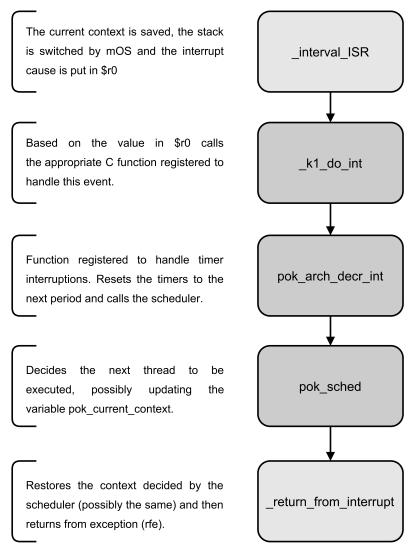

| 13 | Interruption execution flow                                           | 37 |

| 14 | GPRs and GPR pairs with their respective usage convention             | 50 |

| 15 | SFRs and their respective functions                                   | 51 |

| 16 | Structure of the ARINC 653 Part 1 library layer for user applications | 54 |

| 17 | Structure of the ARINC 653 Part 4 library layer for user applications | 55 |

| 18 | TiCOS memory map                                                      | 56 |

# List of source codes

| 1  | C structures representing the $MPPA^{\mathbb{R}}$ context. | 29 |

|----|------------------------------------------------------------|----|

| 2  | Kernel linker script snippet                               | 30 |

| 3  | System entry point                                         | 31 |

| 4  | Partition linker script template                           | 33 |

| 5  | $MPPA^{\mathbb{R}}$ system call implementation             | 34 |

| 6  | $MPPA^{\mathbb{R}}$ context switch                         | 37 |

| 7  | $MPPA^{\mathbb{R}}$ system call handler                    | 52 |

| 8  | $MPPA^{\mathbb{R}}$ interrupt handler                      | 53 |

| 9  | part1/activity.c                                           | 57 |

| 10 | part1/main.c                                               | 57 |

| 11 | arinc653-part1 example execution                           | 58 |

# Glossary

ALU Arithmetic and Logic Unit APEX APplication/EXecutive API Application Programming Interface ARINC Avionics Application Standard Software Interface ASIC Application Specific Integrated Circuit

**BCU** Branch and Control Unit **BMP** Bound Multi-Processing **BSP** Board Support Package

C-NoC Control NoC CC Compute Cluster CPU Central Processing Unit

D-NoC Data NoC DDR Double Data Rate DSU Debug System Unit

**ELF** Executable and Linking Format

FIFO First in, First out FPGA Field Programmable Gate Array FPU Floating-Point Unit

**GNU** Recursive acronym for GNU's Not Unix **GPR** General Purpose Register **GPU** Graphics Processing Unit

HAL Hardware Abstraction Layer

I/O Input/OutputIMA Integrated Modular AvionicsIOC I/O Cluster

**ISA** Instruction Set Architecture **ISS** Instruction Set Simulator

JTAG Join Action Group

LRU Least Recently Used LSU Load/Store Unit

MAU Multiply-Accumulate Unit MMU Memory Management Unit MPPA<sup>®</sup> Multi-Purpose Processor Array

NoC Network on Chip

**OS** Operating System

PCI Peripheral Component Interconnect PE Processing Element

RM Resource Manager RR Round-Robin RTC Real Time Controller RTOS Real-Time Operating System

**SFR** Special Function Register **SMEM** Shared MEMory

TiCOS Time Composable Operating System

VHDL VHSIC Hardware Description language

**VHSIC** Very High Speed Integrated Circuit **VLIW** Very Long Instruction Word

WCET Worst-Case Execution Time

# 1 Introduction

Kalray is a pioneer company in the development of many-core processor architectures. Its latest processor release, the MPPA<sup>®</sup>2-256 Bostan, with 288 C/C++ programmable cores, provides a performance level similar to ASICs and high speed Input/Output (I/O) interfaces. These characteristics allow the so-called supercomputing on a chip with low power consumption and real-time response.

The applications that can benefit from such an architecture are the most varied: data centers, encryption acceleration and multimedia processing are some examples. Besides from these parallel intensive tasks, the avionics industry is particularly interested in the time predictability and space partitioning provided by the processor. The goal of the internship is to use the aforementioned features in order to port a RTOS compliant with the ARINC 653 specification to the Kalray's MPPA<sup>®</sup>. Thanks to this Operating System (OS) interface, clients may port modular avionics software to the MPPA<sup>®</sup> processor.

This document will begin by exposing an overview of the company and the work team. Then the internship's subject will be presented in detail: final goal, problematic, restrictions and work to be done. Furthermore, a technical section will follow containing the possible analysed solutions, a description of the alternative chosen and an evaluation mechanism of the developed product. Implementation and results sections are placed next, showing the work accomplished until this moment. Finally, a planning with the progress, a personal appraisal and a conclusion will be attached.

# 2 Context

## 2.1 The company

Kalray is an organization created in 2008 by Joël Monnier, former vice president of *STMicroelectronics*. It is specialized in the design of many-core processors targeting mainly the embedded computing market (a photo of such processor can be seen in figure 1). As many semiconductor companies nowadays, it is identified as fabless<sup>1</sup>, having its processors production done in Taiwan.

More than 50 people are currently working in Kalray's offices. They are spread throughout Paris (financial headquarters), Montbonnot-Saint-Martin (near Grenoble), Tokyo (Japan) and recently Los Altos (USA) in the *Silicon Valley*.

Figure 1: Two Kalray MPPA®-256 processors in a board

## 2.2 The site

The Kalray Montbonnot-Saint-Martin site groups the most part of the company's workforce. It is situated in a region called Inovallée<sup>2</sup> that incubates more than 380 companies and laboratories. This privileged location has allowed multiple collaborative projects and the creation of a joint laboratory with the CEA, employing more than 30 engineers.

There are two main teams in the site:

- Hardware: the logical and physical design of the processor is done by this team, which is subdivided in:

- Backend: in charge of the placement and routing process, in order to obtain a functional and optimized circuit layout. This design will finally be printed out on masks<sup>3</sup>.

- Frontend: responsible for the architecture design and the hardware description of the processor, written in VHSIC Hardware Description language (VHDL). A part of this team implements the VHDL code in a Field Programmable Gate Array (FPGA), providing a quick prototype interface to be used in internal projects.

<sup>&</sup>lt;sup>1</sup>Company that externalizes the production process, being responsible only for a product's conception.

<sup>&</sup>lt;sup>2</sup>A science park between Meylan and Montbonnot-Saint-Martin created in 1971 with the purpose of shorting the distances between industry and laboratories. Similar in concept with the *Silicon Valley*.

$<sup>^{3}</sup>$ A plate with transparencies that allow the light to pass in a defined pattern. In a chip production this is used in the photolitography process, engraving a layout on a silicon wafer.

- Core Software: all the software tools used to program the MPPA<sup>®</sup> are done by this team, which has two main work branches:

- Core Development: creation of Kalray versions of GNU tools, such as k1-gcc, k1-gdb and k1-objdump. Deployment tools such as a Instruction Set Simulator (ISS)<sup>4</sup> and a hardware runner<sup>5</sup> are also developed and maintained by this branch.

- Core Applications: creation of programs that demonstrate the processor abilities and performance. OS and libraries (such as the well known *libc*) are developed and ported by this branch.

Even though Kalray has been in the market for 8 years, the startup atmosphere remains. The communication and interaction between teams are extremely easy and the work dynamics is flexible. That means one person is not tied down to a group, being allowed to work in multiple projects at the same time.

## 2.3 The team

The Core Software team is lead by Céline Barraud and sums up to 20 engineers working, as already mentioned, with all the problematics linked to the MPPA<sup>®</sup> software environment.

My internship tutor is Benoît Dupont de Dinechin, who occupies the post of Chief Technology Officer, having more than 20 years of expertise in software engineering, processor design and compiler tools. As he is frequently busy with managing decisions, daily basic questions are addressed to Pierre Guironnet de Massas who possesses a deep knowledge of the Kalray environment and the process of porting an OS, specifically its kernel.

Both of these mentors work inside this team and the internship follow-up is done through a weekly email containing the tasks accomplished in the period and the goals to attain for the next week. This helps them verify the quality of the work and if a specific task may be blocking the progression.

<sup>&</sup>lt;sup>4</sup>A simulation model that imitates a processor by reading instructions, executing them and maintaining a virtual state of such hardware.

<sup>&</sup>lt;sup>5</sup>A tool that runs a given binary in a hardware system, in our case the MPPA® with its k1-jtag-runner.

# 3 The internship project

## 3.1 The MPPA processor

MPPA®2-256 Bostan is Kalray's latest processor. It implements a 32-bit/64-bit Very Long Instruction Word (VLIW)<sup>6</sup> core named k1b. The frequency of operation can vary between 4000MHz and 600MHz, which gives a power consumption variation between 10W and 20W. Its peak floating-point performances are 634 GFLOPS and 316 GFLOPS for single and double precision respectively.

In the following sub-subsections some important aspects of the processor will be detailed, as they are required for further comprehension of the document.

## 3.1.1 Global Architecture

Inside the processor there are 288 cores divided in 16 *Compute Clusters* and 2 *I/O Clusters* (*IOCs*) (an overview can be seen in figure 2).

Each CC is composed of 16 Processing Element (PE) cores and 1 Resource Manager (RM) core, all sharing a local Shared MEMory (SMEM) of 2 MB. The communication between CCs is achieved using the Network on Chip (NoC).

Each IOC is composed of 8 RM cores with multiple I/O interfaces (PCIe, Ethernet) and an external Double Data Rate (DDR) memory that normally can be accessed only by these cores.

Figure 2: MPPA<sup>®</sup>2-256 Bostan Overview with a CC zoomed view

The processor was conceived originally to perform parallel calculation (for image and video processing) with high performance and low power consumption, overcoming in these terms a Graphics Processing Unit (GPU). Throughout the years, many other possibilities have appeared: cryptography, data storage, self-driving cars, real-time systems, etc.

Isolating the DDR access and limiting the CC communication to the NoC interface are important features for these applications. It makes the  $\mathsf{MPPA}^{\texttt{R}}$  more energy-efficient and

<sup>&</sup>lt;sup>6</sup>Processor architecture capable of executing multiple instructions at the same time as long as they are not dependant.

prevents unexpected timing interferences between the clusters. Another great advantage is that the programming environment remains a C/C++ standard with no proprietary language learning requirements.

**NoC** The MPPA<sup>®</sup> contains a dual NoC that allows communication and synchronization between the clusters. It is composed of a Data NoC (D-NoC) designed for heavier data traffic, capable of remote writing and a Control NoC (C-NoC) which supports fast synchronization barriers.

The topology is based on a 2D torus<sup>7</sup> augmented with direct links between IOC nodes and NoC extension links to other MPPA<sup>®</sup> processors or an external FPGA. The two NoCs are identical concerning the bidirectional links, router arbitration, the topology and the route encoding, differing at their interfaces and by the size of First in, First out (FIFO) queues. The MPPA<sup>®</sup> NoC totalizes 32 nodes, one per CC and 8 per IOC (c.f. figure 3).

An important aspect for time-criticality is the NoC latency. The D-NoC which is dedicated to streaming data transfers (possible biggest delays) has been designed to operate with guaranteed services, thanks to nonblocking routers and flow regulation at source code. The routers multiplex flows originating from different directions, each with its own

Figure 3: MPPA<sup>®</sup> NoC in detail

FIFO buffer, allowing interference on a node only if they share a link to the next one. In addition, a Round-Robin (RR) arbitration is done between the packets in these FIFOs.

All these features induce a minimal amount of perturbation on the data flow and have allowed Kalray to develop a linear programming formulation to compute the application minimal bandwidth requirements, absence of FIFO queue overflow in the routers and fairness of bandwidth allocation between the different flows.

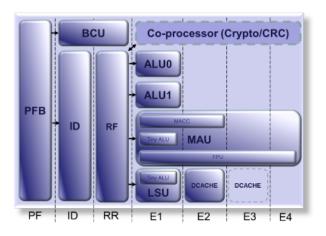

## 3.1.2 The k1b VLIW core

The Kalray k1b core implements the previously mentioned 32-bit/64-bit VLIW architecture with a 7-stage instruction pipeline<sup>8</sup>. This allows the execution of bundles<sup>9</sup> containing up to 5 instructions.

The core also features two Arithmetic and Logic Units (ALUs), a Multiply-Accumulate Unit (MAU) combined with a Floating-Point Unit (FPU), a Load/Store Unit (LSU), and a Branch and Control Unit (BCU). Another important aspect to be mentioned is the endianess<sup>10</sup> of the architecture: *byte-addressable bit-little-endian*, meaning that it is legal to access bytes of a word and that the bit 0 of any data is always the least significant bit.

<sup>&</sup>lt;sup>7</sup>Network topology to connect processing nodes in a computer system

<sup>&</sup>lt;sup>8</sup>Hardware resource that splits the execution of an instruction into multiple steps, allowing parallelism and faster Central Processing Unit (CPU) throughput

<sup>&</sup>lt;sup>9</sup>Group of instructions that can be executed in parallel

<sup>&</sup>lt;sup>10</sup>Order of the bytes in a computer memory stored word. Usually big-endian or little-endian.

**Pipeline** An overview of k1b core pipeline can be seen in figure 4. The 7 stages are explained as follows:

Figure 4: Kalray k1b pipeline

- **PF** (Prefetch): pre-load instructions to the core

- ID (Instruction Decode): fetch, align, decode and dispatch an instruction

- RR (Register read): read the necessary operands for an instruction

- E1, E2, E3, E4: execution stages; all executions begin in E1; results of instructions finished before E4 are available for bypassing

All the functional units, such as the ALU or the LSU, have their own internal pipeline structure that can be seen with more details in [1] and are out of the scope of this document.

**Registers** The MPPA<sup>®</sup> provides three types of register files:

- R: 64 General Purpose Registers (32-bit)

- P: 32 General Purpose Register pairs (64-bit)

- S: 64 Special Function Registers (32-bit)

General Purpose Registers (GPRs) can be used to store all data types that fit within their width: integers, addresses, boolean conditions, single or double precision floating-point. Special Function Registers (SFRs) are used for program and system control and as status registers. An introductory overview of the registers and their functions can be seen in figures 14 and 15. For further information please refer to [1].

**MPPA**<sup>®</sup> **Instruction Set Architecture (ISA)** As already mentioned, the MPPA<sup>®</sup> implements a VLIW core, leading to a very particular instruction set, completely different from the standard x86 ISA.

Due to the pipeline and parallel operation units, these instructions are regrouped into bundles in which they are encoded in ordered words called syllables. In assembly language a valid bundle is, therefore, an ordered subsequence of:

BCU ALUO ALU1 MAU LSU ;;

Following the MPPA<sup>®</sup> assembly rules, each instruction is separated from the next by an end of line. Two semicolons ";;" mark the end of a bundle. In the above listing the acronyms represent instructions that can be executed in the respective unit. For example, the BCU could be replaced by an IGOTO, the ALU could be replaced by an ADD, and so on. For further details of the ISA and valid bundle operations please refer to [1].

## 3.2 Motivation

The MPPA<sup>®</sup> has, as shown, a unique architecture. Managing all of its features and being able to write complex programs in bare-metal<sup>11</sup> is rather challenging. To solve this problem, the services provided by an OS are of great help.

Kalray software engineers have already ported multiple OSs to the MPPA<sup>®</sup> such as RTEMS and even Linux. They have also developed their own simplified systems called  $\mu$ task<sup>12</sup> and simpleOS<sup>13</sup>. Third-party OSs have also been ported by partner companies such as eMCOS by the japanese eSOL and ERIKA Enterprise by Evidence Srl.

Even though the last two mentioned ports are from RTOSs, none of them have been projected exclusively for the avionics market. Therefore, they do not necessarily respect the ARINC653 specification, leading to the following problems when providing such non-compliant OS to avionics costumers:

- The general purpose APplication/EXecutive (APEX)<sup>14</sup> interface for application software is not available and the development will have to be done using a different API. This may cause compatibility issues with older programs and a productivity decrease due to the learning curve of a new API.

- The concept of partition may not be implemented, leading to applications that are not spatially and temporally isolated.

- The final software produced has the same (or a lower) level of certification than the OS, leading to usage restriction.

This problematic has brought up the urge of an RTOS available for the MPPA<sup>®</sup> that is compliant with the ARINC653 specification, and preferentially open-source. The defence and avionics market may then have their attention drawn to the possibilities offered by Kalray's processor. Of course the process of porting an OS to a new architecture is not easy and many aspects must be analysed before the implementation, particularly:

• Different ISA, forcing the rewriting of assembly parts of the kernel

<sup>&</sup>lt;sup>11</sup>A computer running without an OS.

<sup>&</sup>lt;sup>12</sup>Thread support functions with an Application Programming Interface (API) mirroring the classic POSIX pthread implementation.

$<sup>^{13}\</sup>text{Quite similar to }\mu\text{task}$  but also providing scheduling primitives between threads.

<sup>&</sup>lt;sup>14</sup>A special type of API defined by ARINC 653 specification. More details can be seen in section 4.2.1.

- The boot, initial steps and core configuration must be adapted but remain similar

- Memory map changes with new peripherals

- Possible optimizations can be made with a new ISA and they should be made

## 3.3 Objectives

The final goal of the internship is to obtain an ARINC 653 OS on the MPPA<sup>®</sup> Compute Clusters, starting from an open-source single-core implementation. The main tasks to be accomplished can be listed as follows:

- 1. Analyse and choose an ARINC 653 compliant OS which will be then ported

- 2. Translate or re-implement the architecture dependant kernel files

- 3. Adjust the remaining kernel core files for the MPPA<sup>®</sup> architecture

- 4. Adjust the OS libraries as the underlying modifications may have consequences for them

- 5. Optimize the system (single-core to many-core perspective change)

- 6. Simplify the system as the Part 4 is a subset of the original ARINC 653 standard

The tasks 5 and 6 are optional and may be executed depending on the remaining time after a single-core port has been successfully accomplished. A more detailed technical view of the tasks can be seen in section 5.3, while a planning using a Gantt chart can be seen in section 8.

Concerning the quality and robustness of the final result, it should meet the criteria specified in section 5.5, which can be summarized in: having a functional system; respecting the ARINC 653 standard, performance and timing requirements; and being integrated in Kalray's repository. These criteria are based on the ultimate objective of the internship: an opensource RTOS that can be exploited by avionics costumers and used to develop applications using Kalray's environment.

## 4 Technical aspects

## 4.1 Time-Critical Computing on the MPPA

Time-Critical applications are defined as the association of time constraints with information manipulation activities such as acquisition, processing, transport, storage, coordination and delivery [2]. Meeting time constraints requires having a suitable computing model of an application and a computing platform whose OS or run-time software, architecture and implementation support at least the following properties:

- *Deterministic computations*: given the same system environment, inputs and event timing, computation results should be the same.

- *Deterministic and predictable response times*: given the same system environment; inputs and event timing, computation output should take the same predictable time.

- *Composable execution and communication lines*: updates of the system functionality should have commensurable effects on timing properties.

The main issue with many-core platforms and time-critical applications is ensuring timeliness<sup>15</sup> of computation and communication, given the logical (e.g. code critical sections) or physical interference (e.g. memory hierarchy) of tasks that execute concurrently [3].

## 4.1.1 MPPA general architecture features for Time-Critical Applications

The astuteness to ensure that the MPPA<sup>®</sup> is suitable for these type of applications is to, first of all, guarantee the timing constraints at the core and CC level, then combine the multiple clusters and finally connect them to external interfaces through the NoC and synchronisation capabilities.

This is possible because the core architecture makes timing analysis more precise than on classical multicore devices with shared caches (c.f. 4.1.2), while the NoC communication can be configured to meet certain limits on the rate and latency of data transfers (c.f. 3.1.1).

## 4.1.2 MPPA core architecture features for Time-Critical Applications

The VLIW architecture of MPPA<sup>®</sup>'s core was implemented with the elimination of timing anomalies<sup>16</sup> in mind. The following properties assure their absence:

- All memory access instructions exist in cache and uncached variants.

- Instruction and data caches implement the Least Recently Used (LRU) replacement policy.

- Data caches are write-through / write-around and are complemented with a write buffer

- The effects of possible hazards or stalls in instruction/execution pipeline are only transient for time-critical applications

- There is no branch prediction

<sup>&</sup>lt;sup>15</sup>The state of being punctual, having time precision

<sup>&</sup>lt;sup>16</sup>Situation where a local worst-case execution time does not contribute to the global worst-case [4].

• There is no hardware support for branch prediction or out-of-order execution, which could lead to non-deterministic or data-dependent timing.

Consequently, the Kalray VLIW core can be classified as fully time-compositional, i.e. with no timing anomalies. An accurate static timing analysis can thus be done at the core level using predictable and composable execution times, following local worst-cases.

## 4.1.3 MPPA practical usage in Time-Critical Applications

Some examples of applications that can benefit from the aforementioned  $\mathsf{MPPA}^{\texttt{R}}$  features are:

**Control-Command Applications** High safety and security requirements, typical in avionics, transports, medical or industrial domains. The software is written in a model-based programming that generates C code which can be deployed locally in different CC without hardware or software interference between them (except for planned global interactions).

**Mixed-Criticality Applications** Composed by individual programs with different criticality requirements (hard real-time, soft real-time, streaming or interactive). The goal of such applications is to increase the system utilisation, taking advantage of underused hardware resources and allocating them to less critical programs. The spatial partitioning between the cores and natural boundaries provided by the CC help the deployment of this kind of application. Moreover, there is hardware support for fast barrier synchronizations across cores that allows advanced mixed-criticality execution techniques.

Latency Constrained Application High performance with deterministic or even real-time execution requirements that can only be met by parallel processing. Typical classes of such applications include: computer vision applied to self-driving vehicles, industrial robotics and online processing of large-scale physical instrumentation. The MPPA® architecture provides high performance Ethernet (10 Gb/s), PCIe (Gen3) and Interlaken (10 Gb/s) directly connected to the NoC that guarantees timing services. Furthermore, parallel execution patterns can have its worst-case execution time easily calculated when running inside a CC.

## 4.2 State of the Art

## 4.2.1 ARINC 653 standard specification

Aviation industry has been transitioning from the classical federated<sup>17</sup> structure to Integrated Modular Avionics (IMA). This new concept allows avionic subsystems to be grouped inside a limited (or even unique) set of processing units, managed by a dedicated RTOS. As long as the OS provides a proper API and meets the safety requirements, IMA has several advantages over a federated structure: excellent software re-use, portability and modularity, reducing costs of a re-certification process. Nevertheless, as IMA is still a modern methodology, it has a higher complexity of design and certification.

The ARINC 653 standard is closely connected to the IMA concept. Developed by aviation experts to provide "the baseline environment for application software used within IMA and

$<sup>^{17}\</sup>mbox{Avionic subsystems with a dedicated microprocessing unit for each functionality, communicating through ARINC standard 429 (c.f. figure 5a)$

Figure 5: Diagram exposing the differences between federated and IMA systems

traditional ARINC 700-series avionics". Its primary objective is to define a general purpose APEX interface between the OS and application software. The specification includes interface requirements between application software and OS and a list of services that allow application software to control scheduling, communication and status of processing.

Figure 6: Generic structure of an ARINC 653 compliant system

The key concept behind the ARINC 653 specification is the **partition**. It is nothing more than a container for an application assuring that its execution is both spatially and temporally isolated. Partitions are divided in two types: applications partitions and system partitions. The former executes avionics applications and exchanges data with the system through the APEX interface. The latter is optional and may provide services not available in the regular APEX, such as device drives or fault management.

**ARINC 653 Part 1** Initial version of the ARINC 653 standard, published October, 2003 [5] after several drafts and modifications. Defines the core aspects and required services, particularly:

- Time and space partitioning

- APEX interface, of which the main components are:

- partition management,

- process management,

- time management,

- memory management,

- inter-partition communication,

- intra-partition communication,

- health monitoring.

The whole set of ARINC services is a heavy task to implement and requires a complex system to support it. Therefore, simplifications have been suggested and a supplement to the standard was created.

**ARINC 653 Part 4 on the MPPA** A supplement of the ARINC 653 standard, released June, 2012 [6] prepared to support controllers and relatively simple avionics. It is a subset of services specified in ARINC 653 Part 1, simplifying the interface. In the subset services, partition scheduling is restricted to only one partition time window within the partition's period. Process management uses a dual-process model with at most two processes within a partition.

The internship reported in this document is part of the CAPACITES project which determines that the OS ported to the MPPA<sup>®</sup> should be compliant at least with the ARINC 653 Part 4. Moreover, the specification states that the application partitions should execute on CCs, while the system partitions, if there is any, will run on IOCs.

As the Part 4 profile prescribes, application partitions only have two processes, a periodic foreground process and an aperiodic background process. As a result, there is no need to implement the intra-partition communication and synchronization objects such as blackboards, events and semaphores. Inter-partition communication and synchronization is provided by message queuing and message sampling, which will be supported by the NoC (c.f. paragraph 3.1.1) interfaces of the MPPA<sup>®</sup>.

The final proposition is then to run one ARINC 653 Part 4 partition per PE core in the CCs, in a configuration known as Bound Multi-Processing (BMP). This type of configuration allows the developer to bind any process (partition) and all of its associated threads (processes) to a specific core while using a common OS across all cores. An illustration of this proposition can be seen in figure 7.

Figure 7: ARINC 653 Part 4 proposed implementation on the MPPA®

#### 4.2.2 Available compliant OS

In this sub-subsection possible OS options for the porting process will be presented. A brief introduction of each system is given, the decision, however, is postponed to the section 5.1 where proper justification concerning the choice is provided.

**TiCOS** TiCOS is a time-composable real-time operating system developed within the framework of the PROARTIS project supporting the ARINC653 software specification and originally targeting the PPC<sup>18</sup> architecture. TiCOS is based on POK, a light weight operating system implementing the ARINC653 standard and distributed under the BSD license.

Its source code is publicly available, along with documentation and some introductory examples at the following link:

https://github.com/UPD-RTS/TiCOS

**INRIA AOSTE OS** Open-source implementation of an RTOS with ARINC 653 personality based on the aforementioned POK OS. Developed by the team AOSTE, hosted by the INRIA laboratory, that conducts research mainly on real-time embedded systems.

Its creation was motivated by the deficiencies of POK and also to obtain practical systems to be tested in AOSTE's framework of Worst-Case Execution Time (WCET). It is not publicly available so the usage of this RTOS requires the collaboration of INRIA in providing its source code, documentation and support.

$<sup>^{18}\</sup>mbox{PowerPC},$  a ISA created by the 1991 Apple-IBM-Motorola alliance.

# 5 Solution undertaken

## 5.1 OS choice

The OS chosen to be ported was TiCOS. Its public availability, relative stability (been in development for 4 years) and proximity between the internship tutor B. Dinechin and its developers were the main points taken in account for the decision. A GitHub repository was created for this project inside the same organization (UPD-RTS) as the original version. More details in subsection 5.4.

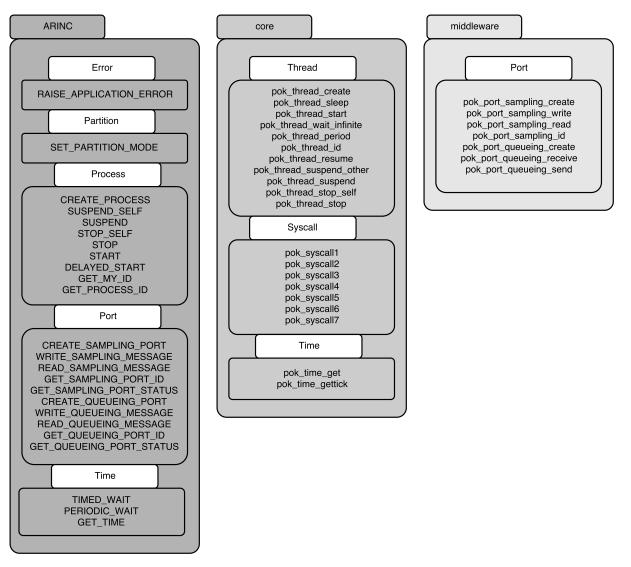

The high level architecture of TiCOS can be seen in figure 8. There are two main layers: kernel layer and application layer. The first is responsible for implementing the OS services, while the latter is composed by the user application, the ARINC library layer, the core library layer and finally the middleware library layer. The libraries services are implemented through system calls to functions inside the kernel layer.

Figure 8: TiCOS high level architecture with MPPA<sup>®</sup> entity

Normally this mechanism would make the system start executing in supervisor (privileged) mode and call the proper kernel functions. The MPPA<sup>®</sup> port of TiCOS will embed in its arch component (as we can see in figure 8) a virtualization layer containing an exokernel hypervisor

called mOS. This system will be detailed in the next subsection, but in this case its main influence is that the OS will always be in user mode and the kernel functions will end up calling mOS that runs in supervisor mode.

## 5.2 mOS

Kalray's Hypervisor, called mOS, is a lightweight exokernel that provides two main services: processor and I/O virtualization, and strong hardware partitioning.

The exokernel concept was introduced by the MIT Parallel and Distributed Operating Systems group in 1994. Its principle is to force as few hardware abstractions as possible to further software layers, constructing a kernel that does apparently nothing and gives freedom to applications. An exokernel is supposed to be tiny and only ensure protection and multiplexing of resources, in opposition to microkernels and monolithic kernels that perform way more tasks and provide high-level abstractions.

mOS essential characteristics are:

- 1. All the services commonly provided by operating systems are delayed to the user-space execution level. As an example, it provides neither a scheduler, a memory allocator nor virtual memory support. Moreover, its implementation is fully static and lock free.

- 2. Its sole role is to ensure proper usage of the underlying hardware, control and manage access rights and ownership.

- 3. It has a very limited memory footprint (32 KB).

- 4. It allows the implementation of any complex system services in user-space. As an example, a user-space operating system may implement fully custom virtual memory support.

A key feature that eases the port of an OS is the virtualization layer provided by the hypervisor that exposes a symmetric 16 core CC (instead of an asymmetric 16PE + 1RM) with direct access to the NoC (hides also the RM interface in order to use the NoC). It also provides a virtualized view of the k1 processor core, modifying its architectural states and behaviour.

An OS that runs with mOS support is called guestOS or libOS due to its user-space status. The interface between such system and the hypervisor is composed of hypercalls, asynchronous remote services and a shared memory region called scoreboard.

**Scoreboard** A structure that allows both mOS and a potential libOS to read and write information. It is composed of a set of architectural registers corresponding to the processor core, NoC, memory management, etc. They are possibly organized in their own sub-scoreboard and are updated asynchronously or synchronously by the hypervisor. There is a scoreboard per CC shared by all the cores of the partition.

**Hypercalls** Mostly related to updates of the architectural state of the virtual core. They are divided in fast, regular and slow types, according to register use and efficiency. An exhaustive list is provided in the internal documentation and is out of the scope of this document.

**Asynchronous remote services** They are important because in the MPPA<sup>®</sup> processor some services, mainly related to the NoC interface configuration, cannot be issued directly by the PE. These requests are packaged by the hypervisor in helpers, which sends them to the RM, waits for the response and raises an event when the request is ready.

The last important aspect concerning the hypervisor is the partition setup. It relies on a *binary descriptor* that allows static hardware resource allocation for an application. It also allows the application to configure its initial MMU setup. Finally, it contains the address of the scoreboard within the user binary and the application entry point. Currently, the hypervisor, user application and binary descriptor are packaged together in one ELF file and loaded into the cluster SMEM as a single unit.

## 5.3 Porting steps

This section will describe more in depth the services and functionalities implemented on each of the previously presented TiCOS layers. It may be seen as a guideline or checklist for the development covered in section 6. The document presents the port of an RTOS originally targeting a mono-core system and, therefore, a single-core port is the first natural stage (c.f. subsection 3.3). Nonetheless, optimizations for a many-core architecture and simplifications regarding the ARINC 653 Part 4 specification are suggested at certain moments.

## 5.3.1 Kernel Layer

The kernel of TiCOS is made of three main components: an architectural dependant part (called *arch component*) and two architectural independent parts (called *core component* and *middleware component*).