# Low Latency Izhikevich's Simple Neuron Model on FPGA

#### Vitor Bandeira, Advisors: Guilherme Bontorin e Ricardo Reis

### Abstract

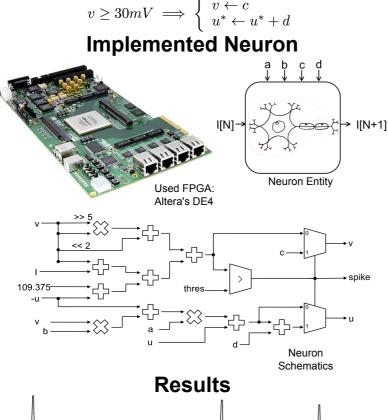

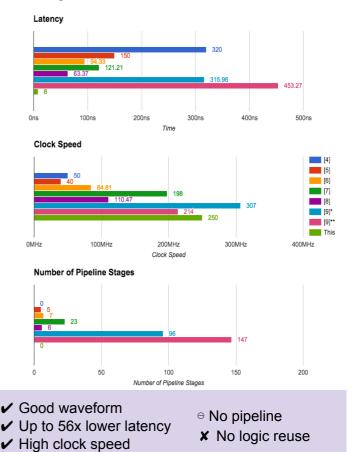

The Izhikevich Simple Model (ISM) for neural activity presents a good compromise between waveform quality and computational cost. FPGAs (Field-Programmable Gate Array) are powerful, flexible, and inexpensive digital hardware that can implement such a model. We present an implementation on FPGA of the ISM whose latency is up to 56 times smaller than the ones in the literature.

Modified Equations of ISM <sup>[1,2,3]</sup>  $h\frac{dv}{dt} = \frac{1}{2}v^2 + 4v = 100.275$

$$\frac{du}{dt} = \frac{1}{32}v^2 + 4v + 109.375 - u^* + I^*$$

$$h\frac{du}{dt} = a^*(b^*v - u^*)$$

This data was obtained from the FPGA running our implementation through the SignalTap II tool in Quartus II® Software.

E. M. Izhikevich, "Simple model of spiking neurons," IEEE, vol. 14, pp. 1569–1572, 2003.

A. Cassidy and A. Andreou, "Dynamical digital silicon neurons," in Biomedical Circuits and Systems

[2] A. Cassidy and A. Andreou, "Dynamical digital silicon neurons," in Biomedical Circuits and Systems Conference, 2008. BioCAS 2008. IEEE, Nov 2008, pp. 289–292.

[3] M.Ambroise, T. Levi, Y.Bornat, and S. Saighi, "Biorealistic Spiking Neural Network on FPGA," in Information Sciences and Systems (CISS), 2013 47th Annual Conference on, March 2013, pp. 1–6.

[4] A. Cassidy, S. Denham, P. Kanold, and A. Andreou, "FPGA Based Silicon Spiking Neural Array," in

[5] A. Cassidy and A. Andreou, "Dynamical digital silicon neurons," in Biomedical Circuits and Systems Conference, 2007. BIOCAS 2007. IEEE, Nov 2007, pp. 75–78.

[5] A. Cassidy and A. Andreou, "Dynamical digital silicon neurons," in Biomedical Circuits and Systems Conference, 2008. BioCAS 2008. IEEE, Nov 2008, pp. 289–292.

UFRGS UFRGS AGO DE INFORMÁTICA AGO DE INFORMATICA AGO DE INFORMÁTICA A

# **Comparison with the Literature**

# Conclusions

Our implementation is best suited for hybrid networks systems and presents a fair performance for artificial-only networks. The low latency of the circuit will allow us to reuse the same neuron multiple times.

[6] M. Ambroise, T. Levi, Y. Bornat, and S. Saighi, "Biorealistic spiking neural network on fpga," in Information Sciences and Systems (CISS), 2013 47th Annual Conference on, March 2013, pp. 1–6. [7] K. L. Rice, M. Bhuiyan, T. Taha, C. N. Vutsinas, and M. Smith, "Fpga implementation of izhikevich spiking neural networks for character recognition," in *Reconfigurable Computing and FPGAs, 2009. ReConFig '09. International Conference on*, Dec 2009, pp. 451–456.

[8] K. Cheung, S. Schultz, and P. Leong, "A parallel spiking neural network simulator," in *Field-Programmable Technology, 2009. FPT 2009. International Conference on*, Dec 2009, pp. 247–254.

[9] D. B. Thomas and W. Luk, "Fpga accelerated simulation of biologically plausible spiking neural networks." in *FCCM*, K. L. Pocek and D. A. Buell, Eds. IEEE Computer Society, 2009, pp. 45–52.

#### Universidade Federal do Rio Grande do Sul Instituto de Informática

Av. Bento Gonçalves, 9500 - Campus do Vale. Bloco IV CP 15064, 91501-970- Porto Alegre-Brazil

Contact: {vvbandeira,reis}@inf.ufrgs.br

Salão de Iniciação Científica - October 19-23, 2015 - Porto Alegre, Brazil