## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

## CLÁUDIO MACHADO DINIZ

Dedicated and Reconfigurable Hardware Accelerators for High Efficiency Video Coding Standard

Tese apresentada como requisito parcial para a obtenção do grau de Doutor em Ciência da Computação.

Orientador: Prof. Dr. Sergio Bampi

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Diniz, Cláudio Machado

Dedicated and Reconfigurable Hardware Accelerators for High Efficiency Video Coding Standard / Cláudio Machado Diniz. – 2015. 141 f.

Orientador: Sergio Bampi.

Tese (Doutorado) — Universidade Federal do Rio Grande do Sul, Instituto de Informática, Programa de Pós-Graduação em Computação. Porto Alegre, BR — RS, 2015.

1. HEVC. 2. Hardware Accelerator 3. Video Coding Architecture. 4. Reconfigurable Architectures. I. Bampi, Sergio, orient. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

This thesis is dedicated to my wife, Cilene, and to my mother, Eliane.

Dedico esta tese à minha noiva, Cilene, e à minha mãe, Eliane.

Ich sage euch: man muss noch Chaos in sich haben, um einen tanzenden Stern gebären zu können. Ich sage euch: ihr habt noch Chaos in euch.

Friedrich Nietzsche

#### **AGRADECIMENTOS**

O melhor deste longo e intenso período de estudos de doutorado foi conviver com uma quantidade grande, e sempre crescente, de pessoas incríveis. Gostaria de agradecer, de coração, a essas pessoas especiais que me ajudaram, das mais diversas formas, no desenvolvimento deste trabalho, e que, de certa forma, também possam compartilhar comigo a alegria de ter conquistado mais esta etapa.

Quero agradecer de coração à minha noiva, Cilene, por seu apoio e amor incondicional. Por sempre me dar força e incentivo em todas minhas ações e decisões, mesmo que elas significassem a nossa distância física por longos períodos (como foi durante o estágio na Alemanha). Pela compreensão quando eu estava distante por causa do trabalho. Pelo seu sorriso e aquela tentativa de me deixar mais feliz em momentos difíceis. Por sempre compartilhar comigo também dos momentos felizes. Faltam-me até palavras para tudo que tenho a agradecê-la. Eu te amo, Cilene.

Quero agradecer de coração à minha mãe, Eliane, que me transmitiu todos os valores e a educação que carrego sempre comigo. Diante de todas as dificuldades que passamos, ela esteve sempre forte e determinada em seguir em frente e contribuir para minha formação. Agradeço pelas palavras de apoio, que me ajudaram a recuperar a autoconfiança. Agradeço a ela por ser uma mãe maravilhosa e uma profissional na qual eu tento me espelhar, um exemplo de responsabilidade e honestidade.

Agradeço ao meu irmão, Fernando, pela convivência durante os anos em que moramos juntos e pela amizade de sempre. Quero agradecer também aos meus sogros, Carmen e Cilon, pela amizade e por toda ajuda ao longo destes anos.

Agradeço ao meu orientador, professor Sergio Bampi, por ter primeiramente confiado no meu potencial e me aceitado no seu grupo de pesquisa. Agradeço por toda sua orientação, ensinamentos, e ajuda, sejam elas técnicas ou pessoais. Agradeço pelas oportunidades que me foram proporcionadas, as quais foram muito enriquecedoras para minha formação como pesquisador e como pessoa.

Agradeço aos professores Altamiro Susin e Luciano Agostini, por terem escrito, em duas ocasiões, cartas de recomendação nas minhas duas tentativas em ingressar no doutorado em Computação da Universidade Federal do Rio Grande do Sul (UFRGS).

Agradeço a todos os colegas e amigos do meu grupo de pesquisa da UFRGS, conhecido informalmente como "lab 215", pela amizade e por todas as discussões

técnicas e não técnicas. Agradeço em especial aos colegas Bruno Zatt, Guilherme Corrêa, Eduarda Monteiro, Daniel Palomino, Felipe Sampaio, Mateus Grellert, Leonardo Soares, André Rosa, Bruno Vizzotto, Roger Porto, Fábio Ramos, Vagner Rosa, Débora Matos, Leandro Max, Kleber Stangherlin e Fábio Walter. Agradeço também a todos os alunos de graduação que passaram no grupo de pesquisa como bolsistas de iniciação científica ou para desenvolver trabalho de conclusão de curso. Agradeço em especial ao Felipe Dalcin e Filipe Posteral, cujos trabalhos de conclusão eu tive a oportunidade de co-orientar, e que contribuíram para o desenvolvimento desta tese.

Agradeço aos amigos e colegas que conheci (ou reencontrei) no curto período em que trabalhei na empresa CEITEC S.A em 2012. Agradeço em especial aos colegas do meu time, Fábio Ramos, Marcos Hervé, Frederico Moller, Daniel Ferrão, Marcelo Moraes, Janaína Costa, e meu chefe, Murugappan Ramaswami, pelos ensinamentos sobre projeto de circuitos digitais.

Durante o estágio na Alemanha, em 2013, pude conviver também com pessoas incríveis. Agradeço ao professor Jörg Henkel, por ter me recebido no Chair for Embedded Systems do Karlsruhe Institute of Technology (KIT), em Karlsruhe, e por ter me proporcionado um excelente ambiente de trabalho para meu estágio de doutoradosanduíche em 2013. Aprendi muito sobre como pesquisar durante o estágio no CES/KIT. Agradeço, em especial, ao Dr. Muhammad Shafique, que me orientou e discutiu comigo os trabalhos de pesquisa que realizei durante o estágio e mesmo os demais trabalhos iniciados depois do estágio. Não é por acaso que praticamente todos os artigos que foram produzidos nesta tese tem o prof. Henkel e o Dr. Shafique como co-autores.

Agradeço a todo esforço realizado pelo colega e amigo Bruno Zatt que, juntamente com o Dr. Shafique, deu início ao processo de cooperação científica entre nosso grupo da UFRGS e o grupo do CES/KIT. Este processo de cooperação iniciado resultou em uma cooperação bilateral formal, financiada pela CAPES, que me apoiou com uma bolsa de estudos de um ano na Alemanha.

Agradeço aos amigos José Azambuja e Georg Hasenpflug, pela excelente convivência diária no ano em que morei em Karlsruhe. Especialmente o José me ajudou muito na mudança para esta nova cidade e país, conseguindo um quarto no apartamento em que morava, me orientando nos primeiros passos no novo país, entre outras coisas.

Gostaria de agradecer às visitas da minha noiva Cilene, da minha mãe Eliane, da minha tia Hilda, e de meu amigo Felipe Sampaio. Elas tornaram meus dias mais agradáveis, diante da saudade que eu sentia dos familiares e amigos do Brasil naquele momento. Agradeço ainda aos amigos Oliver Longhi, Mateus Grellert, José Amendola, Daniel Palomino, Arthur Veiga, Luiza Biasoto, Gabriel Marchesan e família, Philip Porter e Abelardo Gonzalez, pela amizade e companhia em Karlsruhe. Agradeço também aos meus colegas do CES/KIT, especialmente Muhammad Usman Khan, Farzad Samie Ghahfarokhi, Fazal Hameed e Daniel Palomino, pela amizade e conversas diárias.

Agradeço aos professores da Universidade Católica de Pelotas (UCPel), Eduardo Costa, Sergio Almeida, Leandro Zafalon, Wemerson Parreira, Adenauer Yamin e Monica Matzenauer, que pude conhecer ou reencontrar em 2014, quando comecei a trabalhar na UCPel. Especialmente o professor Eduardo Costa me deu grande apoio para que eu pudesse focar na escrita de artigos e no término desta tese. Agradeço também ao professor Mateus Beck Fonseca, da Universidade Federal de Pelotas (UFPel), com quem tive a oportunidade de começar um trabalho ainda em 2014 que resultou em uma contribuição para esta tese, e que me auxiliou na parte experimental do projeto de circuitos digitais.

Agradeço a todos os professores e funcionário do Programa de Pós-Graduação em Computação e do Instituto de Informática da UFRGS, que propiciaram um excelente ambiente para pesquisa.

Agradeço aos órgãos de fomento, CNPq e CAPES, por apoiarem meus estudos através da concessão de bolsas de estudo no país e no exterior, respectivamente.

Por fim, agradeço a todos familiares e amigos que não foram citados nominalmente.

A todos, meu muito obrigado!

#### ACKNOWLEDGEMENTS

The best thing of this long and intense period of Ph.D. studies was to meet a large (and always growing) set of incredible people. I would like to thank those special people that helped me, in many different ways, in the development of this work. I hope they can share with me the joy of achieving this step.

I would like to thank my wife, Cilene, for her support and unconditional love. For always support and encourage all my actions and decisions, even if they mean our long distance for long periods (which was the case during the internship in Germany). For her understanding when I was distant because of work. For her smile and that effort to make me happier in difficult moments. For always share with me also the moments of joy. I can't thank you enough for everything you have done. I love you, Cilene.

I would like to thank my mother, Eliane, who transmitted all the human values and education that I carry with me. In the face of all the difficulties we went through, she was always strong and determined to move forward and contribute to my education. I thank for all the words of support, which helped me to recover my self-assurance. I thank her for being a wonderful mother and also a professional that I try to look up to, an example of responsibility and honesty.

I thank my brother, Fernando, for being my roommate during some years in Porto Alegre and for his friendship. I would like to thank also my mother-in-law and father-in-law, Carmen e Cilon, for their friendship and all the help during those years.

I thank my advisor, professor Sergio Bampi, for trusting in my potential and accepting me in his research group. I thank for all the guidance, teaching, and the technical and personal help. I thank for all the opportunities he provided me. They were very enriching for me as researcher and person.

I thank to the professors Altamiro Susin and Luciano Agostini, for writing, in two occasions, recommendation letters in my two attempts to join the Ph.D. program in Computer Science at the Federal University of Rio Grande do Sul (UFRGS).

I thank all my colleagues and friends of my research group in UFRGS, informally known as "lab 215", for the friendship and for all the technical and non-technical discussions. I thank in particular the colleagues Bruno Zatt, Guilherme Corrêa, Eduarda Monteiro, Daniel Palomino, Felipe Sampaio, Mateus Grellert, Leonardo Soares, André Rosa, Bruno Vizzotto, Roger Porto, Fábio Ramos, Vagner Rosa, Débora

Matos, Leandro Max, Kleber Stangherlin and Fábio Walter. I also thank all the undergraduate students that worked in the research group, in special Felipe Dalcin and Felipe Posteral, whose final undergraduate works I had the opportunity to co-advise, and which contributed to the development of this thesis.

I thank all the friends and colleagues that I met in the short period I worked in CEITEC S.A company in 2012. I thank in particular the colleagues of my team, Fábio Ramos, Marcos Hervé, Frederico Moller, Daniel Ferrão, Marcelo Moraes, Janaína Costa, and my boss, Murugappan Ramaswami, for teaching me valuable things about digital circuit design.

During my internship in Germany, in 2013, I also had the opportunity to meet incredible people. I thank to the professor Jörg Henkel, for receiving me in the Chair for Embedded Systems of the Karlsruhe Institute of Technology (KIT), in Karlsruhe, and for providing me an excellent work office for my internship. I learned a lot how to research during my internship in CES/KIT. I would like to thank, in particular, Dr. Muhammad Shafique, who guided me and discussed with the research projects that I realized during the internship and even the works that began after the internship. It is no coincidence that prof. Henkel and Dr. Shafique are co-authors in most papers that have been produced in this thesis.

I thank all the effort realized by my colleague and friend Bruno Zatt that, along with Dr. Shafique, began the scientific cooperation process between our research group at UFRGS and the CES/KIT research group. This cooperation process resulted in a formal bilateral scientific cooperation agreement, funded by CAPES, which supported me with an one-year research scholarship in Germany.

I thank to my friends José Azambuja and Georg Hasenpflug, for the daily friendship during the year that we were roommates in Karlsruhe. In particular, José helped me a lot in my change for this new city and country, getting a room for me in the apartment he lived that time, helping me in the first steps in Germany, and other things. I would like to thank the visits of my wife Cilene, my mother Eliane, my aunt Hilda, and my friend Felipe Sampaio. I missed my family and friends that time, and those visits make my days more enjoyable. I thank my friends Oliver Longhi, Mateus Grellert, José Amendola, Daniel Palomino, Arthur Veiga, Luiza Biasoto, Gabriel Marchesan e família, Philip Porter and Abelardo Gonzalez, for the friendship in Karlsruhe. I also thank my colleagues from CES/KIT, in particular Muhammad Usman

Khan, Farzad Samie Ghahfarokhi, Fazal Hameed and Daniel Palomino, for the friendship and daily discussions.

I thank the professors from Catholic University of Pelotas (UCPel), Eduardo Costa, Sergio Almeida, Leandro Zafalon, Wemerson Parreira, Adenauer Yamin and Monica Matzenauer, which I met in 2014 when I started working in this university. In particular, professor Eduardo Costa gave me a lot of support so I could focus in writing papers and finishing my thesis. I also thank professor Mateus Beck Fonseca, from the Federal University of Pelotas (UFPel), with whom I had the opportunity to start a work in 2014 that resulted in a contribution of this thesis. He also helped me in the experimental part of digital circuit design.

I thank all the professors and staff of Graduate Program in Computer Science and the Informatics Institute of UFRGS, which provided an excellent environment for research.

I thank the funding agencies, CNPq and CAPES, for supporting my studies through research scholarships in Brazil and in Germany, respectively.

Finally, I thank all my relatives and friends that were not nominally mentioned. To all, thank you very much!

#### **ABSTRACT**

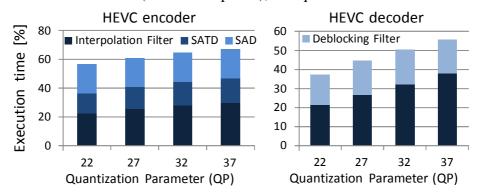

The demand for ultra-high resolution video (beyond 1920x1080 pixels) led to the need of developing new and more efficient video coding standards to provide high compression efficiency. The High Efficiency Video Coding (HEVC) standard, published in 2013, reaches double compression efficiency (or 50% reduction in size of coded video) compared to the most efficient video coding standard at that time, and most used in the market, the H.264/AVC (Advanced Video Coding) standard. HEVC reaches this result at the cost of high computational effort of the tools included in the encoder and decoder. The increased computational effort of HEVC standard and the power limitations of current silicon fabrication technologies makes it essential to develop hardware accelerators for compute-intensive computational kernels of HEVC application. Hardware accelerators provide higher performance and energy efficiency than general purpose processors for specific applications. An HEVC application analysis conducted in this work identified the most compute-intensive kernels of HEVC, namely the Fractional-pixel Interpolation Filter, the Deblocking Filter and the Sum of Absolute Differences calculation. A run-time analysis on Interpolation Filter indicates a great potential of power/energy saving by adapting the hardware accelerator to the varying workload. This thesis introduces new contributions in the field of dedicated and reconfigurable hardware accelerators for HEVC standard. Dedicated hardware accelerators for the Fractional Pixel Interpolation Filter, the Deblocking Filter and the Sum of Absolute Differences calculation are herein proposed, designed and evaluated. The interpolation filter hardware architecture achieves throughput similar to the state of the art, while reducing hardware area by 50%. Our deblocking filter hardware architecture also achieves similar throughput compared to state of the art with a 5X to 6X reduction in gate count and 3X reduction in power dissipation. The thesis also does a new comparative analysis of Sum of Absolute Differences processing elements, in which various architecture design alternatives with different area, performance and power results were introduced. A novel reconfigurable interpolation filter hardware architecture for HEVC standard was developed, and it provides 57% design-time area reduction and run-time power/energy adaptation in a picture-by-picture basis, compared to the state-of-the-art. Additionally a run-time accelerator binding scheme is proposed for tile-based mixed-grained reconfigurable architectures, which

reduces the communication overhead, compared to first-fit strategy with datapath reusing scheme, by up to 44% (23% on average) for different number of tiles and internal tile organizations. This run-time accelerator binding scheme is aware of the underlying architecture to bind datapaths in an efficient way, to avoid and minimize inter-tile communications. The new dedicated and reconfigurable hardware accelerators and techniques proposed in this thesis enable next-generation video coding standard implementations beyond HEVC with improved area, performance, and power efficiency.

Keywords: HEVC, Hardware Accelerator, Video Coding Architecture, Reconfigurable Architectures.

# Aceleradores Dedicados e Reconfiguráveis para o Padrão High Efficiency Video Coding (HEVC)

#### **RESUMO**

A demanda por vídeos de resolução ultra-alta (além de 1920x1080 pontos) levou à necessidade de desenvolvimento de padrões de codificação de vídeo novos e mais eficientes para prover alta eficiência de compressão. O novo padrão High Efficiency Video Coding (HEVC), publicado em 2013, atinge o dobro da eficiência de compressão (ou 50% de redução no tamanho do vídeo codificado) comparado com o padrão mais eficiente até então, e mais utilizado no mercado, o padrão H.264/AVC (Advanced Video Coding). O HEVC atinge este resultado ao custo de uma elevação da complexidade computacional das ferramentas inseridas no codificador e decodificador. O aumento do esforço computacional do padrão HEVC e as limitações de potência das tecnologias de fabricação em silício atuais tornam essencial o desenvolvimento de aceleradores de hardware para partes importantes da aplicação do HEVC. Aceleradores de hardware fornecem maior desempenho e eficiência energética para aplicações específicas que os processadores de propósito geral. Uma análise da aplicação do HEVC realizada neste trabalho identificou as partes mais importantes do HEVC do ponto de vista do esforço computacional, a saber, o Filtro de Interpolação de Ponto Fracionário, o Filtro de Deblocagem e o cálculo da Soma das Diferenças Absolutas. Uma análise de tempo de execução do Filtro de Interpolação indica um grande potencial de economia de potência/energia pela adaptação do acelerador de hardware à carga de trabalho variável. Esta tese introduz novas contribuições no tema de aceleradores dedicados e reconfiguráveis para o padrão HEVC. Aceleradores de hardware dedicados para o Filtro de Interpolação de Pixel Fracionário, para o Filtro de Deblocagem, e para o cálculo da Soma das Diferenças Absolutas, são propostos, projetados e avaliados nesta tese. A arquitetura de hardware proposta para o filtro de interpolação atinge taxa de processamento similar ao estado da arte, enquanto reduz a área do hardware para este bloco em 50%. A arquitetura de hardware proposta para o filtro de deblocagem também atinge taxa de processamento similar ao estado da arte com uma redução de 5X a 6X na contagem de gates e uma redução de 3X na dissipação de potência. A nova análise comparativa proposta para os elementos de processamento do cálculo da Soma das Diferenças Absolutas introduz diversas alternativas de projeto de arquitetura com

diferentes resultados de área, desempenho e potência. A nova arquitetura reconfigurável para o filtro de interpolação do padrão HEVC fornece 57% de redução de área em tempo de projeto e adaptação da potência/energia em tempo-real a cada imagem processada, o que ainda não é suportado pelas arquiteturas do estado da arte para o filtro de interpolação. Adicionalmente, a tese propõe um novo esquema de alocação de aceleradores em tempo-real para arquiteturas reconfiguráveis baseadas em tiles de processamento e de grão-misto, o que reduz em 44% (23% em média) o "overhead" de comunicação comparado com uma estratégia first-fit com reuso de datapaths, para números diferentes de tiles e organizações internas de tile. Este esquema de alocação leva em conta a arquitetura interna para alocar aceleradores de uma maneira mais eficiente, evitando e minimizando a comunicação entre tiles. Os aceleradores e técnicas dedicadas e reconfiguráveis propostos nesta tese proporcionam implementações de codificadores de vídeo de nova geração, além do HEVC, com melhor área, desempenho e eficiência em potência.

Palavras-Chave: HEVC, Acelerador de Hardware, Arquitetura para Codificação de Vídeo, Arquiteturas Reconfiguráveis.

## LIST OF FIGURES

| Figure 2.1 – Abstract system diagram of video encoder                                    | . 37 |

|------------------------------------------------------------------------------------------|------|

| Figure 2.2 – System diagram of video encoder                                             |      |

| Figure 2.3 – System diagram of video decoder                                             |      |

| Figure 2.4 – Motion estimation process                                                   |      |

| Figure 2.5 – Temporal picture coding structure using Random Access configuration         |      |

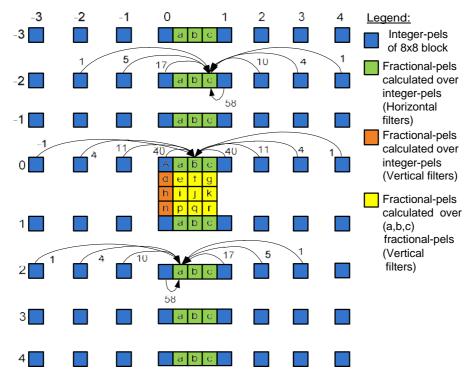

| Figure 2.6 – Luma fractional pixel positions for a 8x8 luma integer pixel block          |      |

| Figure 2.7 – Boundary of a 4x4 block (blocks P and Q)                                    |      |

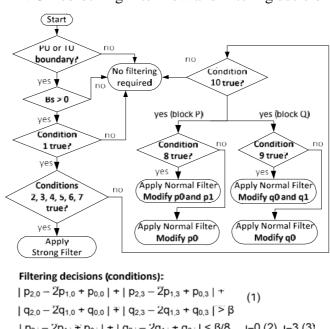

| Figure 2.8 – HEVC Deblocking filter flow and filtering decision equations                |      |

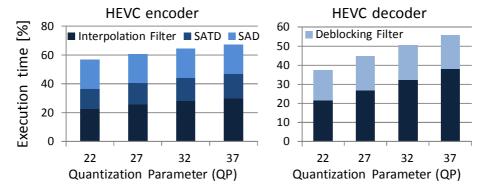

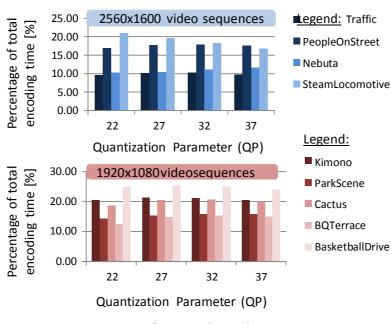

| Figure 3.1 – Contribution of different HEVC coding tools (in percentage) to the total    |      |

| execution time. Video sequence: "People on Street" (2560x1600 pixels), 150 pictures      |      |

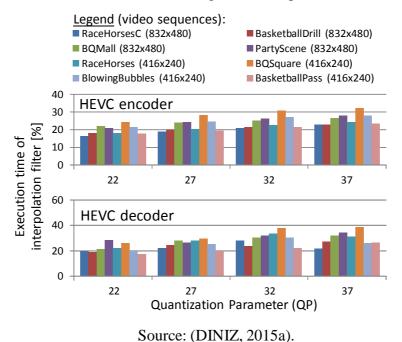

| Figure 3.2 – Contribution of Interpolation Filter (in percentage) to the total execution |      |

| time of HEVC encoder and decoder for eight video sequences and four QP values            |      |

| Figure 3.3 – Contribution of Deblocking Filter (in percentage) to the total execution    |      |

| time of HEVC decoder for nine video sequences and four QP values                         | . 56 |

| Figure 3.4 – Contribution of Sum of Absolute Differences (in percentage) to the total    |      |

| execution time for various nine video sequences and four QP values                       |      |

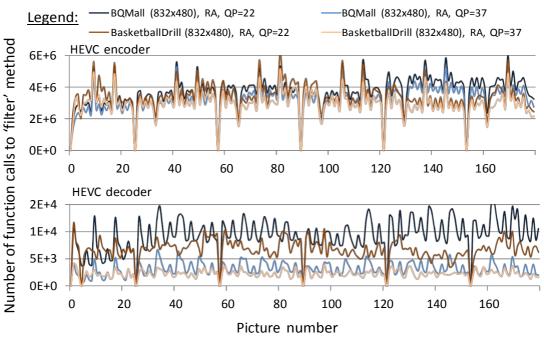

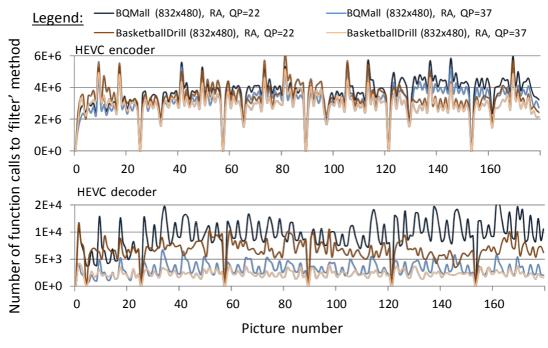

| Figure 3.5 – Number of calls per picture to the interpolation filter basic method        |      |

| Figure 4.1 – Methodology to design optimized hardware accelerators                       |      |

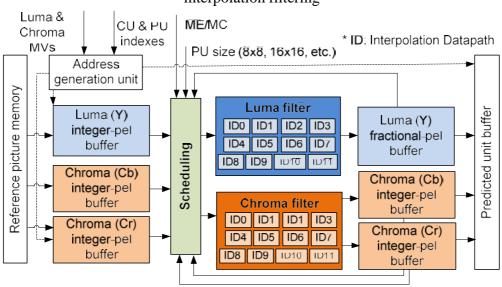

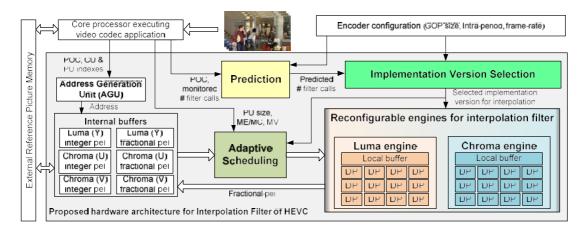

| Figure 4.2 – System diagram of the proposed hardware architecture for HEVC               |      |

| interpolation filtering                                                                  | . 60 |

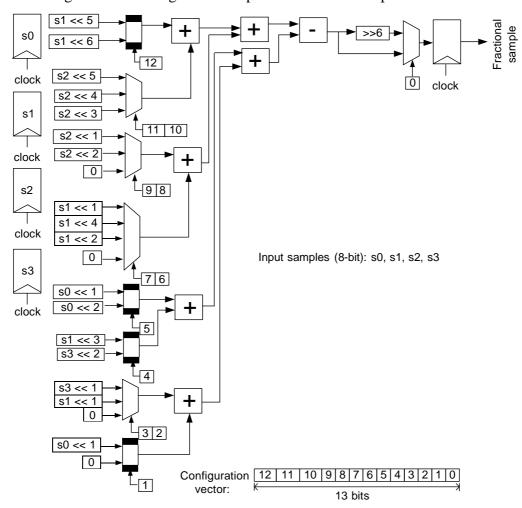

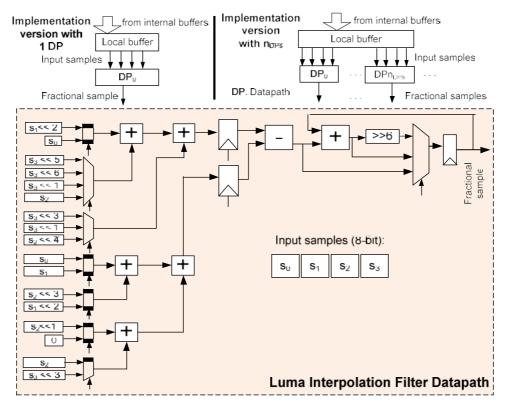

| Figure 4.3 – Configurable datapath for luma interpolation filter                         |      |

| Figure 4.4 – Configurable datapath for chroma interpolation filter                       |      |

| Figure 4.5 – Interpolation filter scheduling                                             |      |

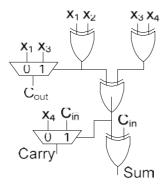

| Figure 4.6 – Internal structure of 4-2 adder compressor                                  |      |

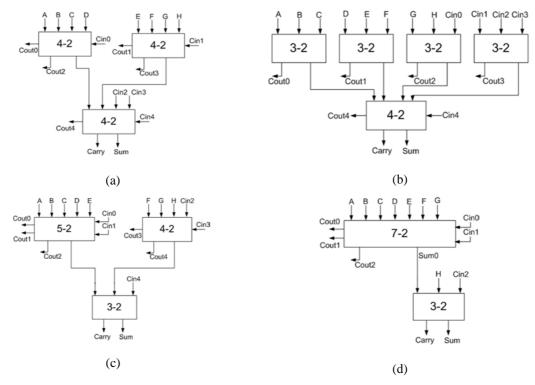

| Figure 4.7 – Hierarchical 8-2 adder compressor using internal structures based on        |      |

| (a) 4-2; (b) 3-2 and 4-2; (c) 5-2, 4-2 and 3-2; (d) 7-2 and 3-2                          |      |

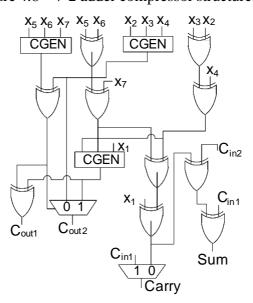

| Figure 4.8 – 7-2 adder compressor structure.                                             |      |

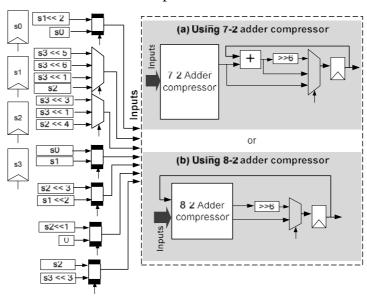

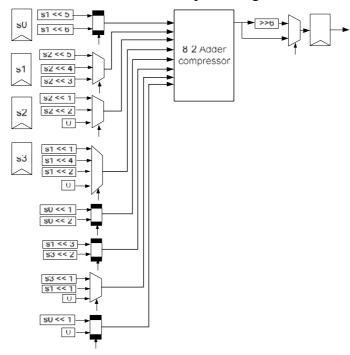

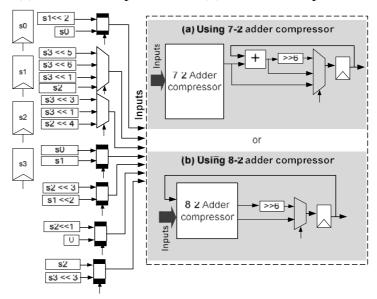

| Figure 4.9 – Modified luma filter datapath using (a) 7-2 adder compressor; (b) 8-2 ad    |      |

| compressor                                                                               |      |

| Figure 4.10 – Modified chroma filter datapath using 8-2 adder compressor                 |      |

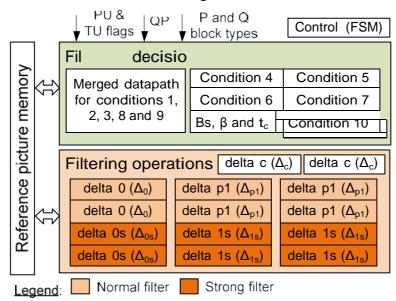

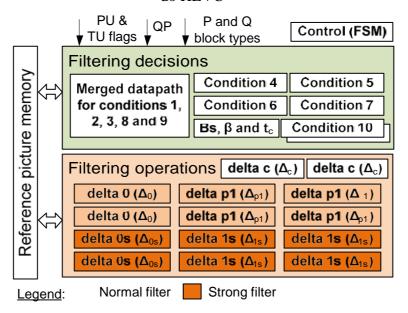

| Figure 4.11 – System diagram of the proposed hardware architecture for HEVC              | . 07 |

| deblocking filter                                                                        | 71   |

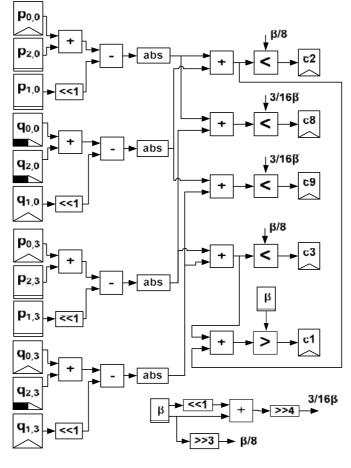

| Figure 4.12 – Merged datapath for conditions 1, 2, 3, 8 and 9                            |      |

| Figure 4.13 – Datapaths for conditions 4, 5, 6, 7 and 10                                 |      |

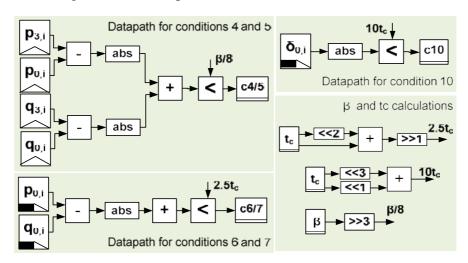

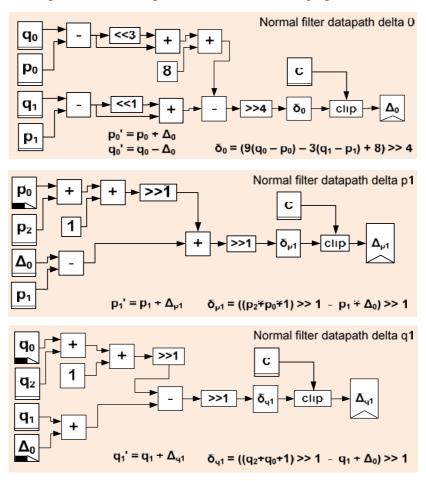

| Figure 4.14 – Datapaths for normal filtering operations                                  |      |

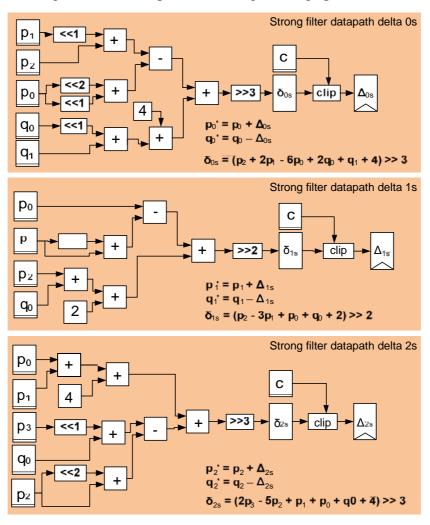

| Figure 4.15 – Datapaths for strong filtering operations                                  |      |

| Figure 4.16 – Datapath for chroma filtering operation                                    |      |

| Figure 4.17 – State diagram of the Finite State Machine                                  |      |

| Figure 4.18 – Processing schedule of normal filter (worst case)                          |      |

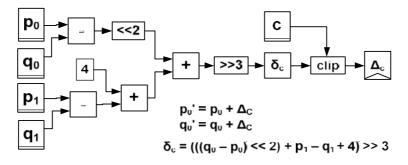

| Figure 4.19 – A Motion Estimation (ME) architecture diagram and the Sum of Absol         |      |

| Differences (SAD) architecture                                                           |      |

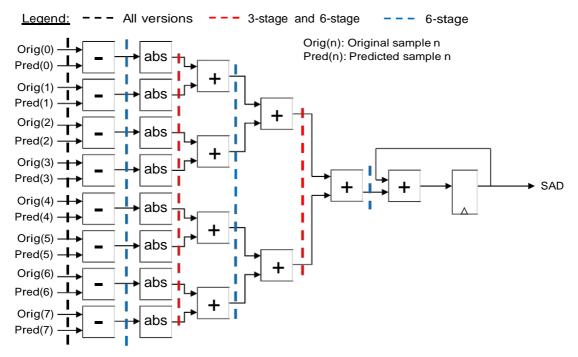

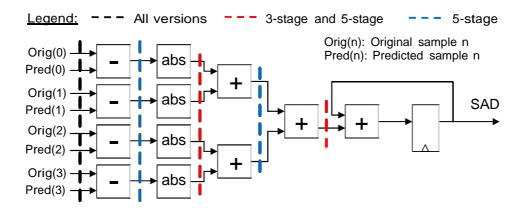

| Figure 4.20 – SAD Processing Element (PE) alternatives with 4-input samples              |      |

| Figure 4.21 – SAD Processing Element (PE) alternatives with 8-input samples              |      |

| Figure 4.22 – SAD Processing Element (PE) alternatives with 16-input samples             |      |

| Figure 5.1 – Proposed reconfigurable hardware architecture for Interpolation Filter of   |      |

| HEVC                                                                                     |      |

| 11L / C                                                                                  | . 00 |

| Figure 5.2 – Correlation of the number of interpolation filter calls considering GOP       |

|--------------------------------------------------------------------------------------------|

| sizes equal to (a) 8, (b) 16, and (c) 4                                                    |

| Figure 5.3 – Architectural template of the reconfigurable engines. Luma and chroma         |

| datapaths are shown in section 4.2. Luma datapath is shown here as an example 89           |

| Figure 5.4 – Pseudo-code of the adaptive scheduling scheme (for luma engine) 92            |

| Figure 5.5 – Pseudo-code of the schedule function                                          |

| Figure $5.6$ – Example of scheduling for $S(p,g) = 6$ and $PU_width = 8$                   |

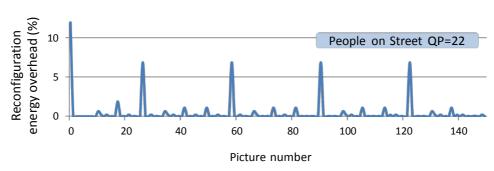

| Figure 5.7 – Reconfiguration energy overhead (%)                                           |

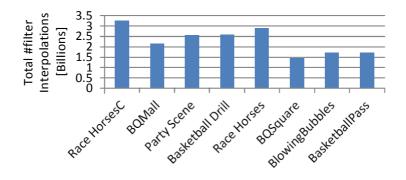

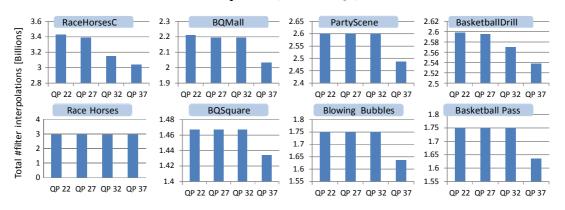

| Figure 5.8 – Number of total filter interpolations of our architecture for the set of test |

| video sequences (averaged over QPs)                                                        |

| Figure 5.9 – Number of total filter interpolations of our architecture for each video      |

| sequence (for each QP)                                                                     |

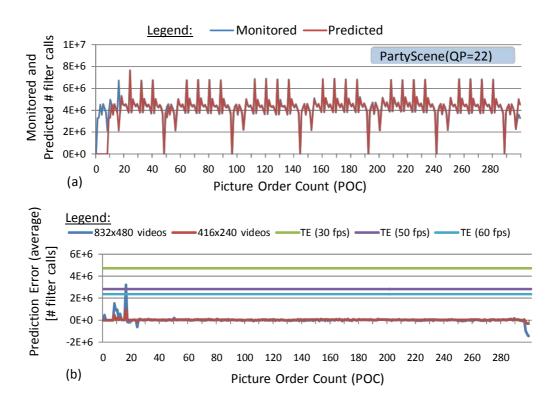

| Figure 5.10 – (a) Monitored and predicted number of filter calls; (b) Prediction error for |

| 832x480 and 416x240 video sequences                                                        |

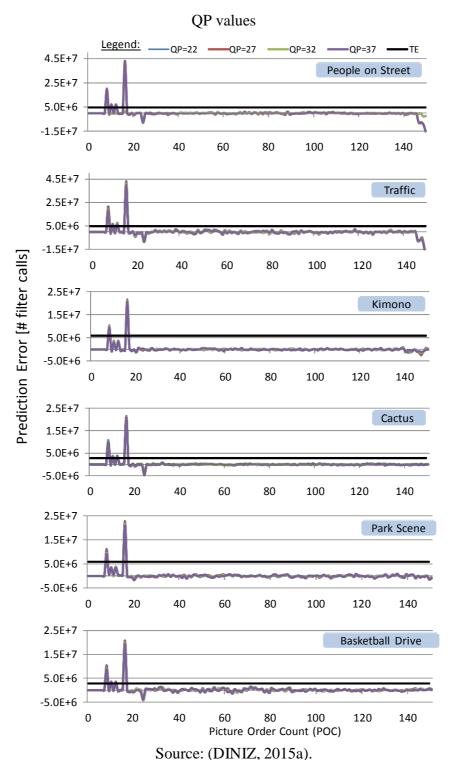

| Figure 5.11 – Prediction error for 2560x1600 and 1920x1080 videos, considering four        |

| QP values                                                                                  |

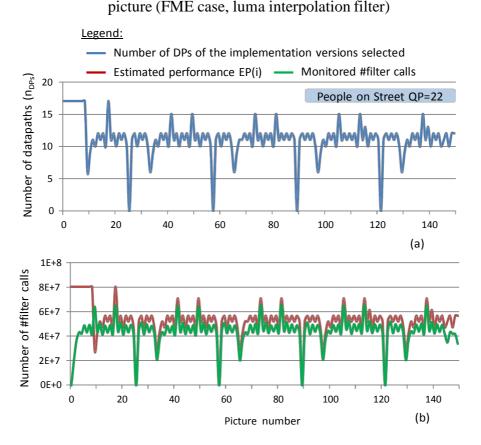

| Figure 5.12 – Implementation version selection results: (a) Number of DPs of               |

| implementation versions selected; (b) Comparison of Estimated Performance (EP) of          |

| implementation version selected and the monitored number of filter calls for each          |

| picture (FME case, luma interpolation filter)                                              |

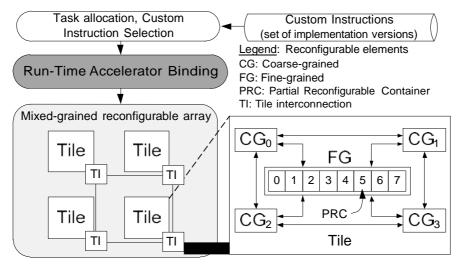

| Figure 6.1 – Abstract System Overview: Our proposed run-time accelerator binding           |

| module integrated within the tile-based mixed-grained reconfigurable architecture 100      |

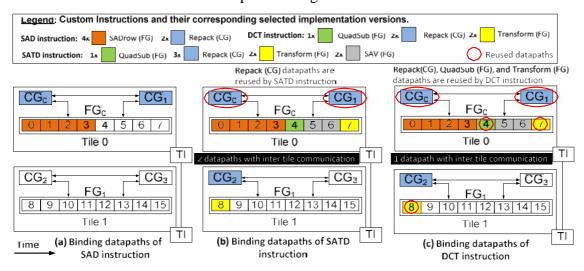

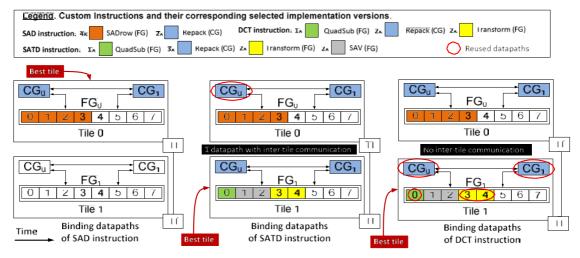

| Figure 6.2 – Example of binding three custom instructions using first-fit strategy with    |

| datapath reusing scheme                                                                    |

| Figure 6.3 – Pseudo-code of our run-time accelerator binding sheme                         |

| Figure 6.4 – Example of binding three custom instructions using our run-time               |

| accelerator binding scheme                                                                 |

| Figure 6.4 – Number of datapaths with inter-tile communication for 2 tiles                 |

| Figure 6.5 – Communication overhead for different tile internal organizations 113          |

# LIST OF TABLES

| Table 2.1 – Comparison of H.264/AVC and HEVC coding tools                                       |

|-------------------------------------------------------------------------------------------------|

| Table 2.2 – 7-tap and 8-tap luma and 4-tap chroma filter coefficients                           |

| Table 2.3 – Derivation of threshold variables $\beta$ and $t_c$ for each QP                     |

| Table 3.1 – Video sequences used for analysis and evaluation                                    |

| Table 4.1 – Luma coefficient multiplications replaced by add/shift operations 61                |

| Table 4.2 – Synthesis results and comparisons to the state of the art hardware                  |

| implementation of the interpolation filter                                                      |

| Table 4.3 – Synthesis results for the Interpolation Datapaths                                   |

| Table 4.4 – Synthesis results of the deblocking filter architecture for FPGA and ASIC77         |

| Table 4.5 – Comparisons to the state of the art hardware implementations of the                 |

| deblocking filter                                                                               |

| Table 4.6 – Architectural parameters of the different SAD PE alternatives                       |

| Table 4.7 – Synthesis results and comparison of the different SAD PE alternatives 83            |

| Table 5.1 – Synthesis results of the proposed hardware architecture for the worst-case          |

| throughput constraint (i.e., 2560x1600 @ 30 fps). Consider max(n <sub>DPs</sub> )=1794          |

| Table 5.2 – Synthesis results of six implementation versions for luma and chroma                |

| hardware acceleration engines                                                                   |

| Table 5.3 – Comparisons with state of the art hardware architectures for fractional-pixel       |

| interpolation filter                                                                            |

| Table 5.4 – Worst-case dynamic power (mW) <sup>1</sup> comparison with state of the art for the |

| same throughput                                                                                 |

| Table 5.5 – Comparison with non-reconfigurable design                                           |

|                                                                                                 |

#### LIST OF ABREVIATIONS AND ACRONYMS

AGU Address Generation Unit

ALU Arithmetic Logic Unit

ASIC Application Specific Integrated Circuit

AVC Advanced Video Coding

B Bi-predictive

BD-PSNR Bjontegaard Delta Peak Signal-to-Noise Ratio

BD-Rate Bjontegaard Delta Rate

BRAM Block Random Access Memory

CABAC Context-Adaptive Binary Arithmetic Coding

CAVLC Context-Adaptive Variable Length Coding

Cb Chrominance Blue

CCD Charge Coupled Devices

CG Coarse-grained

CLB Configurable Logic Block

CMOS Complementary metal-oxide-semiconductor

CODEC COder/DECoder

Cr Chrominance Red

CTU Coding Tree Unit

CU Coding Unit

DCT Discrete Cosine Transform

DF Deblocking Filter

DC Direct Current

MOS Metal Oxide Semiconductor

DP Datapath

DST Discrete Sine Transform

DVD Digital Versatile Disk

EP Estimated Performance

EXOR Exclusive OR FG Fine-grained

FME Fractional Motion Estimation FPGA Field-Programmable Gate Array

FSM Finite State Machine

GB Gigabytes

GOP Group of Pictures

GPB Generalized P and B

HD High Definition

HEVC High Efficiency Video Coding

HM HEVC Test Model

ID Interpolation Datapath

IME Integer Motion Estimation

IP Intra-Period

IQ Inverse Quantization

ISO International Organization for Standardization

IT Inverse Transforms

ITU International Telecommunication Union

JCT-VC Joint Collaborative Team on Video Coding

JVT Joint Video Team

LD Low Delay

LUT Look-Up Table

MC Motion Compensation

MD Manhattan Distance

ME Motion Estimation

MNFC Monitored Number of Filter Calls

MOS Mean Opinion Score

MPEG Motion Picture Experts Group

MSE Mean-Squared Error

MV Motion Vector

NRE Non-Recurring Engineering

P Predictive

PDP Power Delay Product

PE Processing Element

PNFC Predicted Number of Filter Calls

POC Picture Order Count

PRR Partial Run-Time Reconfiguration

PSNR Peak Signal-to-Noise Ratio

PU Prediction Unit

Q Quantization

QFHD Quad Full High Definition

QP Quantization Parameter

QVGA Quarter Video Graphics Array

RA Random Access

RAM Random Access Memory

RCA Ripple-Carry Adders

RGB Red, Green, and Blue

RTL Register Transfer Level

SAD Sum of Absolute Differences

SAO Sample Adaptive Offset

SATD Sum of Absolute Transformed Differences

SD Standard Definition

SoC Systems-on-Chip

T Transforms

TU Transform Unit

VCEG Video Coding Experts Group

VGA Video Graphics Array

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

WPP Wavefront Parallel Processing

WQVGA Wide Quarter Video Graphics Array

WVGA Wide Video Graphics Array

Y Luminance

YCbCr Luminance, Chrominance Blue, Chrominance Red

# TABLE OF CONTENTS

| ABS   | TRACT                                                                | 15 |

|-------|----------------------------------------------------------------------|----|

|       | UMO                                                                  |    |

|       | OF FIGURES                                                           |    |

|       | OF TABLES                                                            |    |

|       | OF ABREVIATIONS AND ACRONYMS                                         |    |

|       | NTRODUCTION                                                          |    |

| 1.1   | Motivation and Problem Definition                                    |    |

| 1.2   | Thesis Contribution.                                                 |    |

| 1.3   |                                                                      |    |

| 2 E   | BACKGROUND AND RELATED WORK                                          |    |

| 2.1   | Digital Video Capture, Representation, and Video Quality             |    |

| 2.1   | 1.1 Digital Video Capture                                            |    |

| 2.1   | 1.2 Color Spaces and Color Sub-sampling                              |    |

| 2.1   | 1.3 Video Quality Metrics                                            |    |

| 2.2   | Video Coding Background                                              |    |

|       | 2.1 Brief History of Video Coding Standardization                    |    |

| 2.2   | 2.2 Video CODEC                                                      |    |

|       | 2.2.2.1 Motion Estimation (ME)                                       | 39 |

|       | 2.2.2.2 Deblocking Filter (DF)                                       |    |

|       | 2.3 Temporal picture structure                                       |    |

| 2.3   | Overview of the High Efficiency Video Coding (HEVC) Standard         | 42 |

|       | 3.1 Fractional-pixel Interpolation Filter                            |    |

| 2.3   | 3.2 Deblocking Filter (DF)                                           |    |

| 2.3   | 3.3 HEVC reference software and common test conditions               | 47 |

| 2.4   | Reconfigurable Computing Background                                  | 47 |

| 2.5   |                                                                      | 49 |

| 2.6   | Related Work                                                         |    |

| 2.6   | 6.1 Chips and Hardware Accelerators for Video Encoding and Decoding  | 50 |

| 2.6   | Hardware Architectures for Interpolation Filter                      |    |

| 2.6   | Hardware Architectures for Deblocking Filter                         |    |

| 2.6   | Hardware Architectures for Sum of Absolute Differences               |    |

| 2.6   | Accelerator Binding on Reconfigurable Architectures                  | 52 |

| 3 F   | HIGH EFFICIENCY VIDEO CODING APPLICATION ANALYSIS                    | 53 |

| 3.1   | HEVC Application Profiling                                           | 53 |

| 3.1   | 1.1 Experimental Test Conditions                                     | 53 |

| 3.1   | 1.2 Analysis of HEVC application with an ultra-high resolution video |    |

| seque |                                                                      |    |

| 3.1   | 1.3 Analysis of the Interpolation Filter                             | 55 |

| 3.1   | 1.4 Analysis of the Deblocking Filter                                | 55 |

| 3.1   | 1.5 Analysis of the Sum of Absolute Differences (SAD) Calculation    | 56 |

| 3.1   | 1.6 Summary of HEVC application analysis                             | 56 |

| 3.2   | Run-time Analysis of HEVC Application                                | 57 |

| 4 I   | DEDICATED HARDWARE ACCELERATORS                                      | 59 |

| 4.1   | Methodology to Design Hardware Accelerators                          | 59 |

| 4.2   | Hardware Architecture for Fractional Pixel Interpolation Filter of   |    |

| HEVC  | 60                                                                   |    |

| 4.2          | .1 Lui             | ma Interpolation Filter Datapath                                 | 61   |

|--------------|--------------------|------------------------------------------------------------------|------|

| 4.2          |                    | roma Interpolation Filter Datapath                               |      |

| 4.2          |                    | neduling                                                         |      |

| 4.2          | .4 Res             | sults and Evaluation                                             | 65   |

| 4.3          | Hardwa             | are Architecture for Fractional Pixel Interpolation Filter using |      |

| Adder C      | Compress           | sors                                                             | . 65 |

| 4.3          | .1 Ad              | der Compressors Background                                       | 66   |

| 4.3          | .2 Enl             | hancing our Fractional Pixel Interpolation Filter Hardware       |      |

| Archi        |                    | ith Efficient Adder Compressors                                  |      |

| 4.3          |                    | sults and Discussion                                             |      |

| 4.4          | Hardwa             | are Architecture for Deblocking Filter of HEVC                   | . 70 |

| 4.4          |                    | tering Decisions Datapaths                                       |      |

| 4.4          | .2 Filt            | tering Operations Datapaths                                      | 73   |

| 4.4          | .3 Co              | ntrol Unit                                                       | 76   |

| 4.4          | .4 Res             | sults and Evaluation                                             | . 77 |

| 4.5          | Hardwa             | are Architecture for Sum of Absolute Differences (SAD)           | . 79 |

| 4.5          | .1 Ex <sub>1</sub> | ploiting Different Versions of Parallel SAD Processing Elements  | . 80 |

| 4.5          |                    | sults and Evaluation                                             | 83   |

|              |                    | IGURABLE HARDWARE ARCHITECTURE FOR                               |      |

| FRACT!       | ONAL-I             | PIXEL INTERPOLATION OF HEVC                                      | . 85 |

| 5.1          | Adaptiv            | e Prediction of Interpolation Filter Calls                       | . 86 |

| 5.1          | .1 An              | alytical Observations                                            | 86   |

| 5.1          | .2 Pre             | ediction Design                                                  | 88   |

| 5.2          | Reconfi            | gurable Hardware Engines for Interpolation Filter                | . 89 |

| 5.3          | Implem             | entation Version Selection                                       | . 90 |

| 5.4          | Adaptiv            | e Scheduling                                                     | . 91 |

| 5.5          | Results            | and Evaluation                                                   | 93   |

| 5.5          | .1 Fai             | rness of comparison                                              | 93   |

| 5.5          | .2 Syr             | nthesis Results                                                  | 93   |

| 5.5          | .3 Dis             | scussion on Reconfiguration Latency                              | 95   |

| 5.5          | .4 Dis             | scussion on Reconfiguration Energy                               | 96   |

| 5.5          | .5 Co              | mparison with State of the Art                                   | . 97 |

| 5.5          | .6 Per             | formance Results for Different Video Sequences                   | . 99 |

| 5.5          |                    | aluation of Prediction Results                                   |      |

| 5.5          | .8 Eva             | aluation of Run-time Implementation Version Selection            | 103  |

| 5.5          | .9 Co              | mparison with a Non-Reconfigurable Implementation                | 104  |

| 6 R          | UN-TIM             | E ACCELERATOR BINDING INTO RECONFIGURABLE                        |      |

| <b>ARCHI</b> | TECTU              | RES                                                              | 105  |

| 6.1          | Overvie            | ew of Tile-based Reconfigurable Architecture                     | 105  |

| 6.2          |                    | ional Analysis1                                                  |      |

| 6.3          | Run-tim            | ne Accelerator Binding Scheme                                    | 108  |

| 6.3          | .1 Pro             | bblem Formulation                                                | 108  |

| 6.3          | .2 Ru              | n-time Accelerator Binding Scheme                                | 108  |

| 6.3          | .3 Ch              | oosing the Best Tile to Bind a Custom Instruction                | 109  |

| 6.3          |                    | nding into Tiles with Low Communication Cost                     |      |

| 6.3          |                    | nding Datapaths inside a Tile                                    |      |

| 6.3          |                    | Example of Our Binding Scheme                                    |      |

| 6.4          | Results            | and Evaluation                                                   | 111  |

| 6.4          | .1 Ex <sub>1</sub> | perimental Setup                                                 | 111  |

| 6.4.2   | Evaluation of inter-tile communications                    | 112 |

|---------|------------------------------------------------------------|-----|

| 6.4.3   | Evaluation of communication overhead for many tiles        | 112 |

| 7 CON   | CLUSIONS AND FUTURE WORK                                   | 115 |

| 7.1 Fut | ture Work                                                  | 116 |

| 7.2 Puł | olished Papers by the Author                               | 117 |

|         | Journal Paper                                              |     |

| 7.2.2   | Conference and Symposia Papers                             | 117 |

|         | NCES                                                       |     |

| APPEND  | IX A <extended abstract="" in="" portuguese=""></extended> | 129 |

|         |                                                            |     |

#### 1 INTRODUCTION

Nowadays, there are many devices in the market capable of digital video recording and displaying, such as digital (smart) televisions, desktop and laptop computers, tablets, smartphones, videogame consoles, camcorders, security cameras, etc. These devices enable a variety of digital video applications, such as video streaming, broadcast digital television, videoconferencing, digital cinema, video surveillance, etc. Two on-demand digital video streaming services over the Internet, namely YouTube and Netflix, became increasingly popular in the last years. YouTube is the largest video repository and video broadcast service in the Internet, with 80 hours of video uploaded per minute by the users and millions of views per day (KOKARAM, 2013). Netflix is subscription-based streaming video service that delivers movies and TV series. Netflix achieved the mark of 50 million subscribers in the second quarter of 2014 (FORBES, 2014). It is predicted that video traffic over the Internet will be 79% of all consumer Internet traffic in 2018 (CISCO, 2014).

To deal with video storing and transmitting over the Internet (and other communication networks), video compression is essential. Here is an example of why video compression is important: a raw (uncompressed) video lasting 10 minute with 720x480 pixel resolution (Standard Definition - SD) represented with 24 bits per pixel (8 bit for each color channel, using three color channels) and with 30 frames per second (fps) require 19 Gigabytes (GB) to be stored or transmitted over the Internet. The same 10-minute raw video with 1920x1080 pixels resolution (Full-HD resolution) requires 112 GB. The same video in the new Sony 4K video resolution format (4096x2160 pixels), used in the 2014 FIFA World Cup, requires 477 GB. It is not viable to deal with such amount of data of raw video sequences using the recent storing and communication technologies.

Video coding is the process of compressing and decompressing digital video. In other words, video coding is the process of converting digital video into a format suitable for transmission or storage. The number of bits to represent encoded video is reduced compared to raw video. Video coding is based in a complementary pair of systems, an encoder (compressor) and a decoder (decompressor). Video encoder converts raw video into a compressed form, prior to storing or transmission. This process is also known as video encoding. Video decoder converts the compressed video back to the original (or very similar to the original) video representation. This process is also known as video decoding. The encoder/decoder pair is often described as a (enCOder/DECoder). Video compression is achieved by removing redundancy, i.e. information that is not necessary for video representation. Video compression may also introduce subjective redundancy, i.e. information that can be removed without significantly affecting viewer's perception of video quality. If the decoded video is identical than original raw video, the encoding process is lossless. In lossy compression, subjective redundancy is also employed, resulting in difference between raw video and decoded video. Lossy compression is applied to achieve higher compression. The higher compression comes with a decrease in video quality of decoded video compared with raw video (RICHARDSON, 2010).

Video coding standards are developed to encode (compress) video. Most video coding standards employ lossy compression to attain high video compression efficiency. When developing a video coding standard, the goal is to compress video with minimal video quality loss under a certain compressed video size (or to achieve minimum compressed video size under a given target video quality). Video coding standards evolved in the last two decades, primarily driven by new video applications and the increase in video resolution. The advances of recent video coding standards in order to provide increasingly video compression result in a huge computational effort. Electronic devices capable of video processing are demanded to provide increased performance at each video coding standard generation, to encode and decode high resolution videos in real time. In this context, section 1.1 presents motivation and problem definition which are driving this thesis.

#### 1.1 Motivation and Problem Definition

The recent demand for ultra-high resolution videos (beyond 1920x1080 pixels) drives the development of new and more efficient video coding standards to provide high compression efficiency. The most efficient new coding standard that arises is the High Efficiency Video Coding (HEVC) standard, developed by the Joint Collaborative Team on Video Coding (JCT-VC), formed by experts of Video Coding Experts Group (VCEG) of International Telecommunication Union (ITU), and Motion Picture Experts Group (MPEG) from the International Standardization Union (ISO). HEVC was published in April 2013 as ITU-T H.265 recommendation (ITU-T, 2013).

HEVC reaches the double compression efficiency (or 50% bit rate reduction) compared to the most efficient video coding standard at that time, and most used in the market, the H.264/AVC (Advanced Video Coding) standard (ITU-T, 2011). The double compression efficiency of HEVC over H.264/AVC is achieved for a similar video quality, since both standards provide lossy compression. HEVC achieves such compression efficiency by employing larger block sizes (to deal with increased resolutions), sophisticated block partitioning, and new advanced coding tools (SULLIVAN, 2012).

The higher compression efficiency of HEVC comes with a significant increase in the computational effort of the HEVC encoder that ranges from 1.2x to 3.2x of the H.264/AVC encoding complexity (VANNE, 2012). It requires further performance improvement of video-capable devices to deal with the increased encoding complexity still being able to encode high video resolutions in real time. A substantial research effort, especially in HEVC encoder, is forecasted to reach this goal (BOSSEN, 2012).

Performance improvement was achieved in the past with the advances of silicon fabrication technology, which enable higher operation frequencies through smaller and faster transistors. Recently, advances in silicon fabrication still enable smaller and faster transistors at every new Complementary metal-oxide-semiconductor (CMOS) technology node. Chips continue to integrate more transistors into the same area, following the Moore's law for density (MOORE, 1965). Recent CMOS technologies are able to integrated more and more processing cores in the same chip, the so-called multicore and many-core processors.

However, in new decananometer technologies, performance increase is limited by thermal design power, since transistor power density is now increasing at each CMOS technology node (ESMAEILZADEH, 2011). To ensure that chips remain below the

thermal design power, not all transistors of the chip can switch at full speed all the time, resulting in the so-called utilization wall (VENKATESH, 2010). The portion of the chip that is most of the time underclocked or powered-off is referred in general as "dark silicon" (ESMAEILZADEH, 2011) (TAYLOR, 2013). Recent work (TAYLOR, 2013) foresees that the percentage of dark silicon will increase at each technology node and will be around 94% in the early 2020's. Dark silicon will limit core and frequency scaling for performance improvement.

To cope with the increased performance required by the new HEVC standard and to keep chips below the thermal design power, future processors will integrate many on-chip hardware accelerators for specific computational kernels, i.e. the so-called accelerator-rich architectures (IYER, 2012) (CONG, 2014). Specialized hardware accelerators are 500X more energy efficient than general purpose processors doing the same job (HAMMED, 2011). As the computational kernels are not executed simultaneously all the time, the accelerators can be powered off when not in use. Hence, specialized hardware accelerators for important computational kernels are an efficient way to "fill" the dark region of chips.

While dedicated hardware accelerators provide high performance and energy efficiency for real-time video encoding and decoding, they have some drawbacks. They are fixed in design time and cannot change the hardware in the field, after silicon fabrication. They also incur in high costs for design and silicon fabrication. Reconfigurable hardware provides a platform solution with low design costs, faster time-to-market, and flexibility of quick upgrades through dynamic reconfigurations (TUAN, 2006). Designs based on Field-programmable Gate Array (FPGA) combine the performance efficiency of dedicated accelerators due to their capability to exploit high degree of parallelism along with a high degree of flexibility due to their programmability and hardware reconfigurability (SHAFIQUE, 2009)(COMPTON, 2002). The drawback of FPGA designs is the higher power compared with dedicated accelerators.

The thesis author foresees that both dedicated and reconfigurable accelerators will be used in future accelerator-rich processor architectures. This thesis provides different contributions for both dedicated and reconfigurable acceleration, as discussed in section 1.2., which can be applied to the current HEVC and also to future generation video encoders, as long as they are based on CUs comprised of blocks of video pixels.

#### 1.2 Thesis Contribution

The goal of this thesis is the research on novel dedicated and reconfigurable hardware accelerators for important computational kernels of the new HEVC standard. Analysis of the HEVC application presented in Chapter 3 verifies that the most important coding tools in terms of computational effort are the Fractional-pixel Interpolation Filter, the Deblocking Filter (DF) and the Sum of Absolute Differences (SAD).

In the domain of dedicated accelerators dealt with in Chapter 4, this thesis introduces the following novel contributions:

• A high-throughput hardware architecture for HEVC Fractional-pixel Interpolation Filter (Section 4.2) employing 12-pixel parallel filter acceleration engines for luminance and chrominance with multiplierless configurable interpolation datapaths and a scheduling scheme to manage the

- operation of these interpolation datapaths depending upon the execution scenario.

- A hardware architecture for HEVC Fractional-pixel Interpolation Filter using Adder Compressors (Section 4.3) to improve area, performance, and power dissipation.

- A high-throughput hardware architecture for HEVC Deblocking Filter (Section 4.4) employing hardware reuse to accelerate filtering decision units at low area cost.

- A comparative analysis and comparison of architectural alternatives for SAD hardware architecture processing element (Section 4.5) in terms of hardware area, throughput, and power dissipation.

Regarding reconfigurable video coding accelerators, this thesis additionally introduces the following novel contributions:

- A reconfigurable hardware architecture for HEVC Fractional-pixel Interpolation Filter, developed in Chapter 5. The architecture incorporates a prediction scheme to estimate the number of interpolation filter calls on a picture-by-picture basis, using the knowledge of the coding structure. A set of different implementation versions for interpolation filter hardware accelerator engines is developed to allow an area versus performance tradeoff. An implementation version selection scheme is proposed. It selects an implementation version of interpolation filter accelerator for each picture, depending upon the predicted number of interpolation filter calls provided by the prediction scheme. A scheduling scheme is introduced to determine the order of processing and configure filter types. It facilitates the reuse of input samples and prevents redundant fetching.

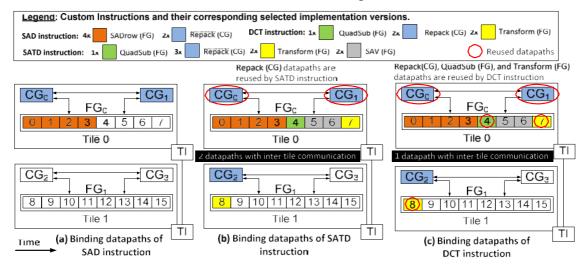

- A run-time accelerator binding scheme for tile-based mixed-grained reconfigurable architectures is proposed and analyzed in Chapter 6. The scheme employs datapath reuse and inter-tile communication cost estimation to perform a communication-minimizing binding for datapaths of custom instructions at run-time.

#### 1.3 Thesis Outline

This text is organized as follows. Chapter 2 provides a background of video coding (focusing on the new HEVC video coding standard), reconfigurable computing, power dissipation and it discusses related work on these topics. Chapter 3 presents an analysis of HEVC application based on software profiling and observation of function calls at run time. Chapter 4 presents our novel dedicated hardware accelerators for HEVC. Chapter 5 presents a new reconfigurable hardware architecture for HEVC Fractional-pixel Interpolation Filter. Chapter 6 introduces the novel run-time accelerator binding scheme for tile-based mixed-grained reconfigurable processors. Chapter 7 presents the conclusions of this thesis and describes future work.

#### 2 BACKGROUND AND RELATED WORK

This chapter gives a background on the concepts required to understand the novel contributions of this work. It revises the concepts of digital video capture, representation, quality and coding (sections 2.1 and 2.2) with an overview of the new HEVC standard (section 2.3). Concepts of reconfigurable computing and power dissipation in CMOS are also revised in sections 2.4 and 2.5. Related work about hardware design and architectures for HEVC and accelerator binding schemes are presented in section 2.6.

#### 2.1 Digital Video Capture, Representation, and Video Quality

### 2.1.1 Digital Video Capture

Digital video is a discrete approximation (in time and space) of a natural scene. It is represented by a sequence of pictures (a rectangular matrix of pixels) captured at regular time interval. Each picture is 2D projection of a natural scene captured by an analog semiconductor sensor, formed by an array of Charge Coupled Devices (CCD) (RICHARDSON, 2010). Each CCD captures one pixel. For color images, there are three matrixes of CCDs, one to capture each color. Each color component of a pixel is called sample. Each sample is represented by a number of bits, e.g. 8 bits, that define the intensity level of the specific color.

The size of CCD array (in horizontal and vertical pixels) defines the spatial sampling of video, which is called resolution. There are some defined resolution formats, e.g. Standard Definition (SD) with 720x480 pixels, Full-HD (High Definition) with 1920x1080 pixels, 4Kx2k with 4096x2160 pixels, etc.

The time interval each picture is captured define the temporal sampling of video. It is called picture rate or frame rate, commonly defined as frames per second (fps). With a sufficient high capture rate, it is possible to give the observer the feeling of motion. Common picture rates are 24 fps, 30 fps, 50 fps and 60 fps, etc. The higher is the picture rate, more smooth is the feeling of motion to the observer (RICHARDSON, 2010).

#### 2.1.2 Color Spaces and Color Sub-sampling

The pixel in a color picture is represented by three color components, following a color space. A common color space is Red, Green, and Blue (RGB), which uses these three primary colors captured by the human visual system to form the pixel. Video coding standards uses Luminance, Chrominance Red and Chrominance Blue (YCbCr) color space, instead. The main advantage of YCbCr color space is because the human visual system has different photoreceptor cells, namely the rods, to sense intensities of light (luminance, or luma), and the cones, to sense colors (chrominance, or chroma). As the human visual system is less sensitive to color than to luminance, it is possible to sub-sample the color pixels.

Common color sub-sampling rates are 4:2:0, in which for each four luma samples, there are only one Cb sample and one Cr sample. It actually represents 4:1:1 ratio, but the literature defined as 4:2:0. Other chroma sub-sampling ratios are 4:2:2 and 4:4:4, the later with no sub-sampling (RICHARDSON, 2010). Color sub-sampling may be considered a first tool for video compression.

#### 2.1.3 Video Quality Metrics

Since video coding standards provides usually lossy compression, to achieve large compression rates, it is important to measure the final video quality after video encoding. Video quality is a complex parameter to define, because it is based on subjective criteria of video observers. Subjective metrics, such as Mean Opinion Score (MOS) exist and are used to evaluate the video quality to compare different video coding standards. However, MOS cannot be used in all contexts, because in some cases it is needed to compare and evaluate videos faster and objectively.

Peak Signal-to-Noise Ratio (PSNR) is a well-known objective video quality metric used in the literature (GHANBARI, 2003). PSNR is defined in Equation 2.1, in which MAX is the maximum value of representation of one sample  $(2^n - 1$ , for 8 bits, MAX is equal to 255) and Mean Squared Error (MSE) is calculated as shown in Equation 2.2. In Equations 2.1 and 2.2, m and n are the horizontal and vertical dimensions of the picture. In Equation 2.2, O and R are the original and reconstructed pictures, respectively. Reconstruced picture is the picture after the coding losses.

$$PSNR(dB) = 20 \cdot \log_{10} \left( \frac{MAX}{\sqrt{MSE}} \right)$$

(2.1)

$$MSE = \frac{1}{mn} \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} (R_{i,j} - O_{i,j})^2$$

(2.2)

Often it is useful to compare video quality between two different coded videos (e.g. using different codecs) of a same input raw video. Two different coded videos of a same input raw video may incur in different PSNR, but also different bit rate (the rate of a coded video bits, in bits/s). In this case, a simple PSNR comparison is not useful, because videos have also different bit rate values. In this situation, the Bjontegaard Delta PSNR (BD-PSNR) metric (BJONTEGAARD, 2001) must be used. This metrics is based on curve fitting of two different Rate Distortion (RD) curves (of the two different coded videos) formed by four bit rate/PSNR points. BD-PSNR represents an average difference of PSNR values (in dB) over the range of four bit rates. BD-Rate metric also exists and represents an average bit rate difference (in %) over the range of four PSNR values (BJONTEGAARD, 2001). More details about BD-PSNR and BD-Rate calculation can be found in (BJONTEGAARD, 2001).

## 2.2 Video Coding Background

#### 2.2.1 Brief History of Video Coding Standardization

The history of video coding standardization can be summarized by revising the video coding standards developed by ITU and ISO organizations. The first video coding standard is H.261 (ITU, 1990). Three years later, ISO produced its first video coding standard, MPEG-1 (ISO, 1993). One year later, ITU and ISO groups jointly produced the H.262/MPEG-2 video coding standard (ITU and ISO, 1994). In 1995, ITU produced the H.263 standard (ITU, 1995). ISO produced MPEG-4 Visual standard in 1999 (ISO, 1999). After that, ITU and ISO jointly produced the H.264/MPEG-4 Advanced Video Coding (AVC) standard (also known as H.264/AVC) (ITU and ISO, 2003).

H.264/AVC is the current video coding standard in use in the market, targeting many video applications and ranging different video resolutions. It was developed by the Joint Video Team (JVT) formed by experts of both ITU and ISO. H.264/AVC

doubles the video compression when compared to MPEG-2 standard for similar video quality (WIEGAND, 2003).

The new High Efficiency Video Coding (HEVC) standard was recently developed by JCT-VC, formed by experts of ITU and ISO, and published in April 2013 (ITU and ISO, 2013). Its primary goal was to double compression efficiency of the most efficient video coding standard until now, namely the H.264/AVC, especially focusing on ultrahigh resolution video encoding (beyond 1920x1080 pixels). In recent video coding standards, i.e. H.264/AVC and HEVC, only the video decoder and the bitstream syntax are subject of standardization. The video encoder flow is not standardized. It gives some freedom to design video encoder, because the only requirement for video encoder is to generate a conformed bitstream (WIEGAND, 2003).

### 2.2.2 Video CODEC

Digital video pictures are compressed by a video encoder that transforms original pictures into a stream of bits of coded video (also called bitstream). To display the coded video, a video decoder must be used to transform the coded video into a reconstructed picture. Usually, the reconstructed pictures are different from original pictures (in lossy compression). When reconstructed and original pictures are equal, it is called a lossless compression (RICHARDSON, 2010). The pair encoder/decoder forms the so-called COder/DECoder (CODEC).

An abstract diagram of video encoder is depicted in Figure 2.1. It is formed by three main functional units: a prediction model, a spatial model and the entropy encoder (RICHARDSON, 2010). The prediction model receives original (raw, uncompressed) pictures and reduces the spatial and temporal redundancies present in video, by exploiting stored coded data, e.g. neighboring pictures or the same picture. The difference of prediction result and the original picture is called residue. The residue is processed by a spatial model that transforms residue into coefficients, exploiting similarities in the residual picture to reduce spatial redundancy. Prediction and Spatial model parameters are further processed by entropy encoder, which is a lossless encoder that removes statistical redundancy in the data.

Prediction model Spatial Entropy encoder 010010...

Stored coded data parameters

Figure 2.1 – Abstract system diagram of video encoder

Source: the author, modified from (RICHARDSON, 2010).

Advanced video coding standards, e.g. H.264/AVC and HEVC, follows basically the same CODEC structure. The video encoder is based on the abstract video encoder system diagram shown in Figure 2.1. However, advanced video coding standard are block-based, i.e. video pictures are partitioned into smaller blocks that are processed by the encoder and the decoder. H.264/AVC splits pictures into blocks of 16x16 pixels called macroblocks. The macroblock is the main coding unit that is processed by all the

coding tools of video encoder. HEVC supports larger blocks of size up to 64x64 pixels (SULLIVAN, 2012). More details of HEVC are given in section 2.3.

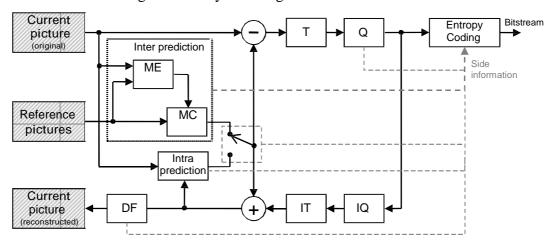

Figure 2.2 shows the diagram of a generic video encoder. It includes Inter and Intra predictions, Forward Transform (T), Quantization (Q), Inverse Transforms (IT), Inverse Quantization (IQ), Entropy Coding and Deblocking Filter (DF). Intra prediction generates a prediction of a block based on the information of neighboring blocks in the current picture (captured by the camera) that are already processed and reconstructed. Inter prediction is formed by Motion Estimation (ME) and Motion Compensation (MC) coding tools. The goal of Inter prediction is to generate a prediction based on previous pictures, so-called reference pictures. ME searches for the best match, i.e. the block in the reference pictures that is the most similar to the block in the current picture. The most similar block is chosen by ME as the best block, and a motion vector indicates the displacement between current block position and the position of the best block. ME/MC process is detailed in section 2.2.2.1.

Figure 2.2 – System diagram of video encoder

Source: the author, modified from (AGOSTINI, 2007).

After the prediction, the residual blocks (difference between predicted blocks and original blocks from the current picture) are processed by Transforms and Quantization modules. In H.264/AVC, transform module includes a 4x4/8x8 Discrete Cosine Transforms (DCT) and 2x2/4x4 Hadamard Transform, depending on the residues and the block type (WIEGAND, 2003). Quantization is the module that produces coding losses in the residual blocks, controlled by a Quantization Parameter (QP). QP value is directly proportional to the strength of coding loss. All coding information (residual blocks and side information from other modules, e.g. prediction types, motion vectors, etc.) is further encoded by the Entropy coding module. Advanced video coding standards support sophisticated lossless entropy coding algorithms such as Context Adaptive Binary Arithmetic Coding (CABAC). In particular, H.264/AVC also includes Context Adaptive Variable Length Coding (CAVLC) for entropy coding. The output of entropy coding module is the coded video (bitstream).

Prediction, Transforms, Quantization, and Entropy coding form the forward path of video encoder. The inverse path is formed by Inverse Transforms (IT), Inverse

Quantization (IQ) and Deblocking Filter (DF). The inverse path is included in video encoder to avoid mismatch between encoder and decoder. Reconstructed pictures in video encoder, further used as reference pictures, must match exactly the reconstructed pictures in video decoder, because decoder also uses the reference pictures to perform Motion Compensation (MC). MC is the inverse process of motion estimation. The result of MC or Intra prediction is added to the output of IT to reconstruct the block. Before picture reconstruction, a Deblocking Filter (DF) is applied to remove blocking artifacts caused by strong quantization.

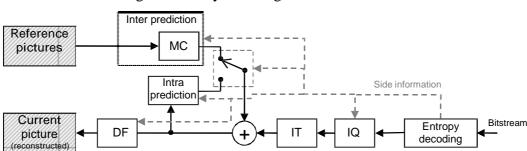

The general diagram of a video decoder is shown in Figure 2.3. It is similar to the inverse path of the video encoder. The coded video (bitstream) inputs to an entropy decoding module. The residual blocks are processed by Inverse Transforms and Inverse Quantization modules. Decoded side information e.g. prediction types, motion vectors, feeds other modules. The result of prediction (either Intra or Inter) is added to the output of Inverse Transforms and is processed by deblocking filter (DF in Figure 2.3) to reconstruct the picture (which will be displayed in the user device). Reconstructed pictures are stored as reference pictures to be used by Motion Compensation.

Figure 2.3 – System diagram of video decoder

Source: the author, modified from (AGOSTINI, 2007).

Motion Estimation and Deblocking Filter modules are detailed in sections 2.2.2.1 and 2.2.2.2, since they are the focus of hardware accelerators proposed in this work.

#### 2.2.2.1 Motion Estimation (ME)

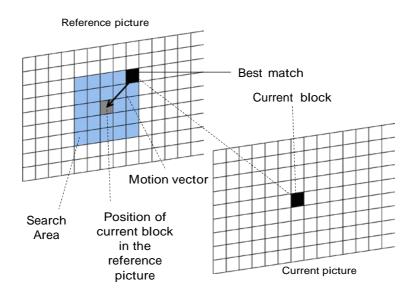

Motion Estimation is available only in video encoders, in the Inter prediction module. Figure 2.4 shows the Motion Estimation process. It has the goal to search in the references pictures which block is the most similar with the current block (to be encoded) in the current picture, the so-called best match.

ME search is usually limited to a search area in the reference picture. When the best match is found, a Motion Vector (MV) is generated to indicate the displacement of current block position and the selected block position in the reference picture. The MV is encoded by an entropy encoder and is sent to the bitstream, along with the residue between the best block and the current block, which is transformed and quantized. The ME search is conducted and guided by a block-matching algorithm, which is usually optimized according to specific coding efficiency goals set by the designer (performance, video quality, power, or area, for instance).

Figure 2.4 – Motion estimation process

Source: the author, modified from (PORTO, 2008).

A vast number of ME search algorithms were proposed in the literature, since they are a non-standardized coding tool. A survey of ME algorithms is given in (HUANG, 2006). Independent of the search algorithm, they need to use a video quality metric to determine the best match. PSNR metric, based on MSE, is very complex to be used in practice. Sum of Squared Differences (SSD) is a video quality metric with good correlation with MSE and PSNR. However, calculating square values also requires huge computational effort in real systems. Some video quality metrics that require lower computational effort are the Sum of Absolute Transformed Differences (SATD) and the Sum of Absolute Differences (SAD). SAD is the simpler and requires the lowest computational effort. SATD is based on transformed differences and requires usually a Hadamard transform (RICHARDSON, 2010).

SAD calculation, used in this work, is shown in Equation 2.3, where m and n are the dimensions of the block in samples (horizontal and vertical), O is the current (original) block and R is the reference block.

$$SAD = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} \left| R_{i,j} - O_{i,j} \right|$$

(2.3)

One SAD is calculated for one current block and for one specific block out of the many possible block candidates in the reference picture, as determined by the ME search algorithm. The SAD metric is then often used for low complexity video quality measure in the context of block matching for ME.

In advanced video coding standards, ME has many features, e.g. variable block size, bi-prediction (B pictures), weighted prediction, fractional-pixel motion vectors, etc. Fractional-pixel motion vectors require an Interpolation Filter to calculate the value of the fractional position pixels.

# 2.2.2.2 Deblocking Filter (DF)

Deblocking Filter is included in the advanced video coding standards to improve the reconstructed picture to be used as reference pictures for ME/MC. It reduces the blocking artifacts present in a reconstructed video, which are introduced by the inherent block partitioning and strong quantization in video encoding. This is done by modifying samples along the vertical and horizontal borders of blocks. The Deblocking filter is adaptive to identify whether the artifacts are real edges of the picture (and thus must not be filtered) or are the edges introduced by the encoding process, which then must be filtered. Therefore, many decisions are applied before the sample modifying to decide whether the filter must be applied or not.

## 2.2.3 Temporal picture structure

There are two different picture types in video coding standards: Intra (I) picture, which includes only Intra prediction blocks, and Inter picture, that may include Inter and Intra blocks. Regarding Inter prediction, there are two types of pictures: Predictive (P) pictures (only P blocks) which employ Inter prediction with only one reference picture, and Bi-predictive (B) pictures, that may include P and B blocks. Bi-prediction is the Inter prediction in which two reference pictures must be used together to predict the same block. Intra picture is always the first picture in a video sequence, because there are no previous (reference) pictures to perform Inter prediction. It is usual to also include Intra pictures in regular intervals between Inter pictures to provide the so-called Random Access, i.e. for broadcast and streaming video applications, the decoder must find the first Intra picture to start decoding the video stream. The period of pictures between two Intra pictures is referred in this work as intra period.

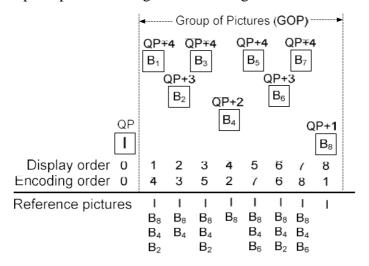

Both P and B pictures may use reference pictures from the past or from the future of pictures. To support this feature, the encoding order is different to the display order. The display order is often referred as Picture Order Count (POC). The encoding order is called frame number or picture number. In video coding standards, pictures are organized in Group of Pictures (GOP) for encoding. An efficient temporal picture coding structure in terms of compression is the hierarchical B-picture coding structure shown in Figure 2.5. In this structure, pictures are encoded as I pictures or B pictures (B pictures are more generic than P pictures, because they include both P and B blocks).

Figure 2.5 – Temporal picture coding structure using Random Access configuration

Source: the author, modified from (VANNE, 2012).

In the picture structure shown in Figure 2.5, different QP values are assigned for each picture depending on their picture index and type (I or B). Figure 2.5 also shows the prediction dependencies among pictures, i.e. reference pictures (VANNE, 2012).

# 2.3 Overview of the High Efficiency Video Coding (HEVC) Standard

HEVC is the new video coding standard (ITU and ISO, 2013). It achieves approximately 50% bit rate reduction over H.264/AVC standard (ITU and ISO, 2003). HEVC follows the same block-based video encoder structure as reviewed in section 2.2. To achieve such compression efficiency, HEVC employs larger block sizes (up to 64x64 pixels) and a new flexible quadtree structure that splits those blocks hierarchically down to 4x4-pixel elementary blocks. A new set of advanced coding tools was also introduced in HEVC, as we review in this section.