# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# RAUL DARIO CHIPANA QUISPE

# SINGLE EVENT TRANSIENT EFFECTS IN CLOCK DISTRIBUTION NETWORKS

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microelectronics

Prof. Dra. Fernanda Lima Kastensmidt Advisor

Porto Alegre, December 2014.

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

#### CHIPANA QUISPE, RAUL DARIO.

Single Event Transient Effects in Clock Distribution Networks / Raúl Darío Chipana Quispe. – Porto Alegre: PGMICRO - UFRGS, 2014.

119 f.: il.

Orientador: Fernanda Lima Kastensmidt.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2014.

1. Single Event Transient. 2. Clock distribution networks 3. Clock extraction. 4. Clock tree. 5. Clock mesh. I. Kastensmidt, Fernanda G. L. II. Single Event Transient Effects in Clock Distribution Networks.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PGMICRO: Prof. Gilson Inácio Wirth

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **ABSTRACT**

Technology scaling to semiconductor has increased the radiation-induced susceptibility of electronic devices. Single Event Transient (SET) are becoming increasingly problematic for integrated circuits (ICs). Radiation effects may occur in the clock distribution networks of the ICs. During the strike of an ionizing particle, charge may be collected on the output node of the clock buffer, provoking a clock glitch, clock jitter and clock skew. As consequence of the impact, it is possible to notice errors in the control flow or data flow of the system. This work investigates the SET susceptibility in the clock distribution network of the circuit. We are interested in the most sensitive paths of the network and registers that are most likely to flip in the clock network. Some bitflips are most likely to provoke a fault in the IC output once a failure occur in those elements. In the present work we propose a new methodology to identify the most sensitive nodes and to calculate the soft error rate due to SET in clock distribution network. This new methodology uses a tool developed in this thesis named EXT-CLK. The tool extracts the clock network from layout design files, to perform different simulations of SET injection in electrical and logic level. The SRAM arbiter circuit has been chosen as a case study. Thousands of electrical simulations have been performed in order to identify the sensitive nodes of the clock network. Results show that 17 registers of SRAM arbiter exhibit high vulnerability factor. This information can help the designers to use some mitigation techniques on those registers before the manufacturing process.

# **RESUMO**

A redução na escala dos semicondutores tem aumentado a suceptibilidade de componentes eletrônicos a radiação. Single event transient (SET) afeta cada vez mais os circuitos integrados. Os efeitos da radiação podem afetar as redes de relógio dos circuitos integrados. Durante o impacto de uma partícula ionizada, a carga pode ser coletada na saída do buffer da rede de relógio e provocar um clock glich, clock jitter e clock skew. Como consequência do impacto, é possivel notar erros no fluxo do controle e no fluxo de dados do sistema. A presente tese investiga a suscetibilidade ao SET nas redes de relógio dos circuitos. Nós estamos interessados nos caminhos mais sensíveis da rede e nos registros que apresentam mais probabilidade de mudar de estado (bit-flip). Alguns bitflips tem mais probabilidade de provocar uma falha na saída do circuito, enquanto outros podem ser mascarados pela aplicação. Nesta tese propomos uma nova metodologia para identificar os nós mais sensíveis e calcular o soft error rate causado pelo SET nas redes de relógio. Nossa metodologia utiliza uma ferramenta desemvolvida para esta tese chamada EXT-CLK, a ferramenta extrai a rede de relógio dos archivos de desenho do circuito para realizar diferentes simulações de injeção de SET. Como estudo de caso foi selecionado o circuito SRAM arbiter. Centenas de simulações foram feitas com o intuito de identificar os nós mais sensíveis da rede de relógio. Os resultados mostram 17 registros do ciruito SRAM arbiter terem alto índice de suscetibilidade. A informação encontrada nos resultados poderão ajudar os desenhadores a escolher a técnica de mitigação mais apropriada para o circuito antes de ser fabricado.

# **ACKNOWLEDGMENTS**

# I dedicate my sincere thanks:

- To my lovely wife Raquel for helping me in everything.

- To my parents Darío and Ana for giving me the life and take care of me.

- To my sisters Helena, Ana and Norma for encouraging and supporting my decisions.

- To my advisor Prof. Fernanda Lima Kastensmidt for giving me the chance to research at the PGMICRO.

- To my friends Jorge, Eduardo, Walter, Jimmy, Lucas, William, José,

Felipe, Samuel, Gracieli, Anelise, Calebe, Guillerme, Jerson and Gustavo

Wilke.

# LIST OF FIGURES

| Figure 1.1 General clock distribution networks for processors (Wilke, 2008)                      | 15   |

|--------------------------------------------------------------------------------------------------|------|

| Figure 1.2 Radiation induced jitter and race (Seifert et al., 2005).                             | 16   |

| Figure 2.1 Van Allen radiation belts.                                                            |      |

| Figure 2.2 Ionizing Dose: Cumulative effects                                                     | 20   |

| Figure 2.3 Charge distribution in a gate oxide after expose to radiation (Lacoe, 2008).          | . 21 |

| Figure 2.4 Edge transistor current (Lacoe, 2008).                                                | 23   |

| Figure 2.5 $I_D$ - $V_G$ curves as a function of total dose for 0.35 $\mu$ m minimum geometry NM | OS   |

| transistor (Lacoe, 2008)                                                                         | 24   |

| Figure 2.6 $I_D$ - $V_G$ curves as a function of total dose for 0.18 $\mu$ m (Lacoe, 2008)       | 24   |

| Figure 2.7 Mechanism for heavy ions and protons in semiconductors (Lacoe, 2008)                  | 26   |

| Figure 2.8 Energetic particle strike a p-n junction extending the depletion region a             | ıs a |

| funnel (Lacoe, 2008)                                                                             | 27   |

| Figure 2.9 SRAM core under ion strike.                                                           | 28   |

| Figure 2.10 Ionization upset threshold in SRAM core (hspice simulation 65nm)                     | 28   |

| Figure 2.11 SET propagation in an inverter chain (Dodd et al., 2004).                            | 29   |

| Figure 2.12 Logic masking.                                                                       | 30   |

| Figure 2.13 Electrical masking.                                                                  |      |

| Figure 2.14 Latching-window masking                                                              | 31   |

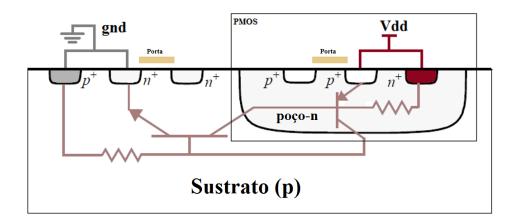

| Figure 2.15 PNPN structure in CMOS technology (Deepon Saha, 2010)                                | 31   |

| Figure 2.16 Equivalent circuit of CMOS latchup                                                   | 32   |

| Figure 2.17 Logic path mapping in the Flash-based FPGA.                                          | 33   |

| Figure 2.18 Propagation delay of an inverter gate                                                |      |

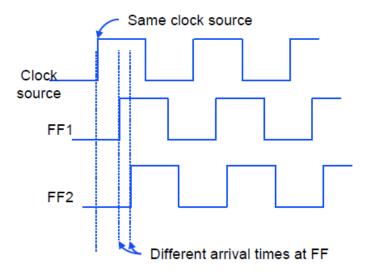

| Figure 3.1 Clock skew definition.                                                                |      |

| Figure 3.2 Clock skew in circuits.                                                               | 37   |

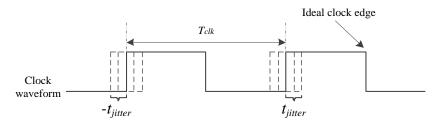

| Figure 3.3 Jitter in clock waveform.                                                             | 38   |

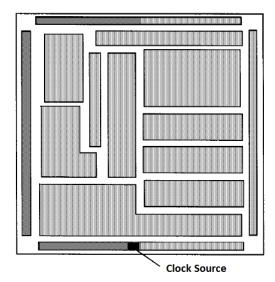

| Figure 3.4 Floorplanning of structured custom VLSI circuit (Friedman, 2001)                      | 39   |

| Figure 3.5 General clock distribution networks in integrated circuit (Friedman, 2001).           | . 39 |

| Figure 3.6 Geometric matching for zero skew (Friedman, 2001)                                     |      |

| Figure 3.7 Symmetric H-tree distribution (Wilke, 2008).                                          | 41   |

| Figure 3.8 Clock mesh structure                                                                  | 42   |

| Figure 3.9 Global mesh using H-tree distribution (Cadence, 2003)                                 | 43   |

| Figure 3.10 Effects of radiation particle strike on a regular clock path (Dash et al., 200       | )9). |

|                                                                                                  | 46   |

| Figure 3.11 Inverter proposed: (a) conventional inverter, (b) hardened dual port inverter        | rter |

| (Ming e Shanbhag, 2005).                                                                         |      |

| Figure 3.12 Hardened dual port inverter as clock path (Ming e Shanbhag, 2005)                    | 47   |

| Figure 3.13 SEU hardened clock leaf inverter (Mallajosyula e Zarkesh-Ha, 2008)                   |      |

| Figure 3.14 TMR clock regenerator circuit (Dash et al., 2009).                                   |      |

| Figure 3.15 Split-output inverter based clock regenerator hardening (Dash et al., 200            |      |

|                                                                                                  |      |

| Figure 3.16 Split-output SEU tolerant inverter                                                   |      |

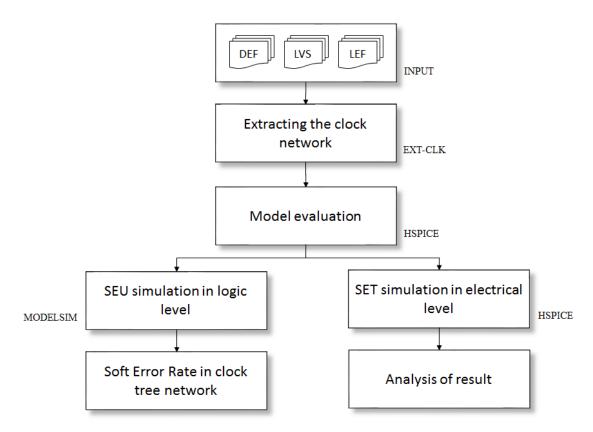

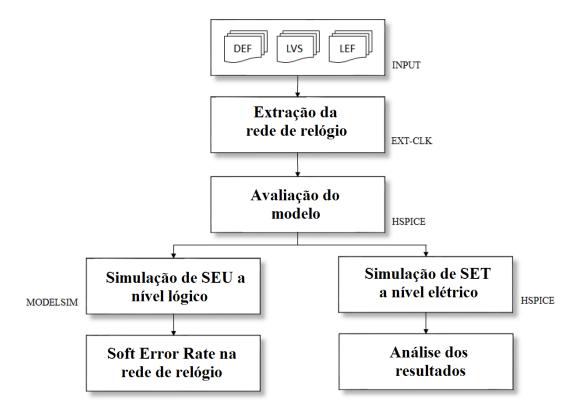

| Figure 4.1 Proposed methodology to analyze SET susceptibility in clock networks                  | 53   |

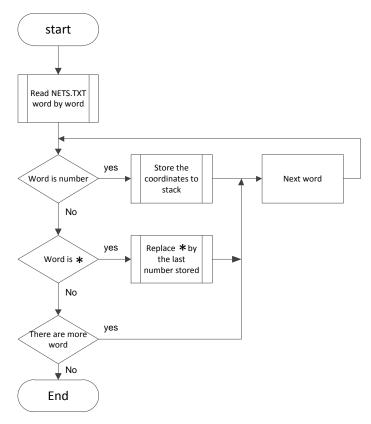

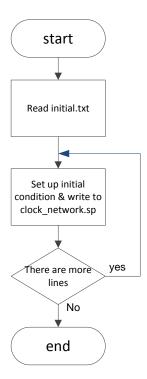

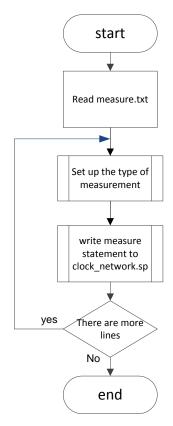

| sectionsFigure 4.3 Flowchart to logic cell subcircuits statement                    |            |

|-------------------------------------------------------------------------------------|------------|

| Figure 4.4 Representation of a net                                                  | 57         |

| Figure 4.5 Example of a net description in DEF file                                 |            |

| Figure 4.6 Algorithm to separate nets concerning the clock network                  |            |

| Figure 4.7 Asterisk convention used in net description                              | 59         |

| Figure 4.8 Algorithm to replace asterisks by numbers                                |            |

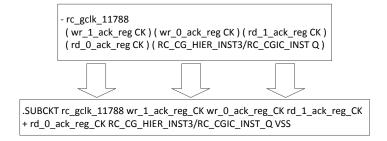

| Figure 4.9 Writing the net subcircuit headline.                                     |            |

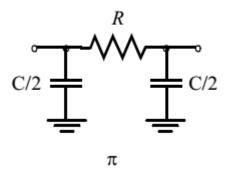

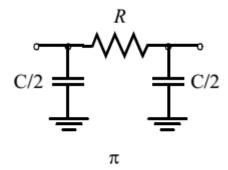

| Figure 4.10 Pi model for wire simulation in hspice (Rabaey et al., 1999)            |            |

| Figure 4.11 Net description in DEF syntax (left) and Net description in netl        |            |

| (right)                                                                             |            |

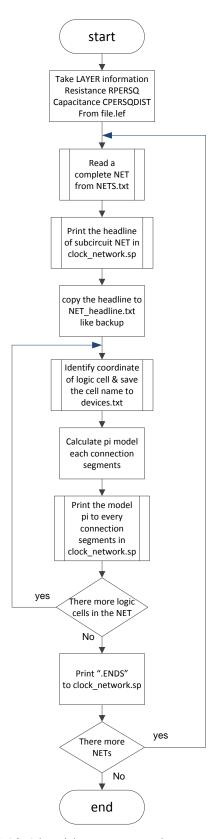

| Figure 4.12 Algorithm to create the net subcircuit                                  | 63         |

| Figure 4.13 Flowchart of the algorithm to call the subcircuit of components         | 65         |

| Figure 4.14 Flowchart of the algorithm to call the subcircuit of nets               |            |

| Figure 4.15 Algorithm to define initial condition                                   |            |

| Figure 4.16 Algorithm to measure statement                                          | 69         |

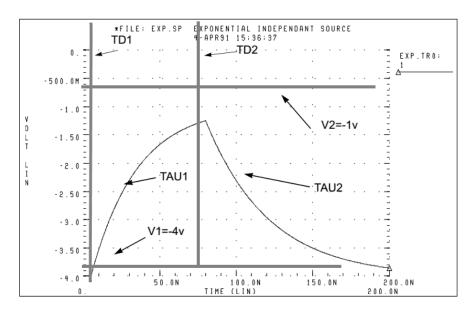

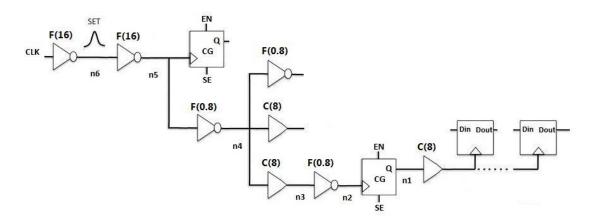

| Figure 5.1 Example of exponential source function                                   | 71         |

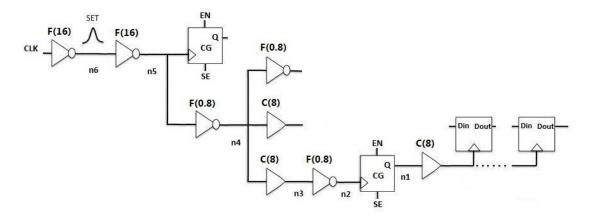

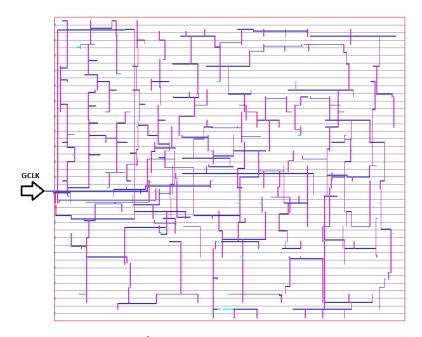

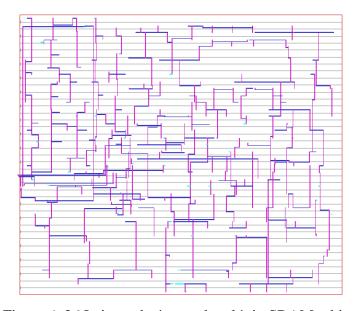

| Figure 5.2 Clock Tree Network in SRAM arbiter circuit                               | 72         |

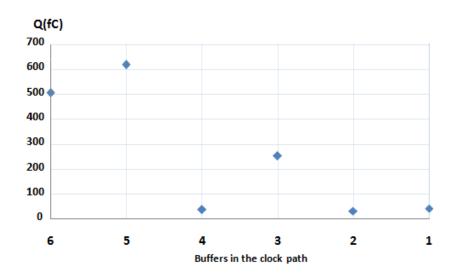

| Figure 5.3 Minimum charge injected in the output of buffers to produce a bit        | -flip in a |

| last one register                                                                   |            |

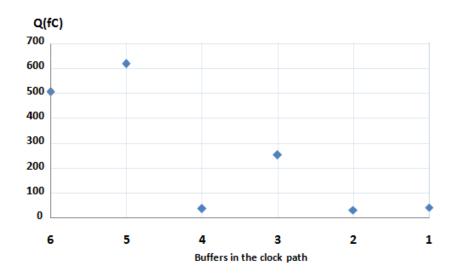

| Figure 5.4 Clock path in SRAM arbiter to be analyzed                                | 75         |

| Figure 5.5 Critical charge results in the SRAM arbiter clock path                   | 75         |

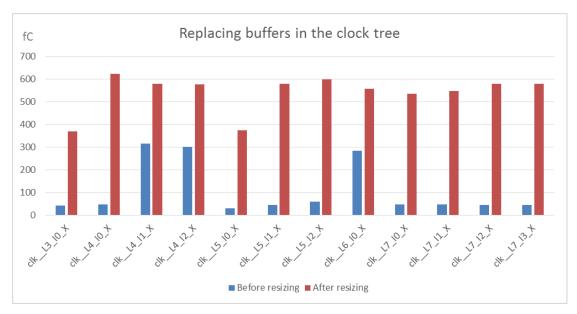

| Figure 5.6 Result of the SET simulation replacing small devices                     | 77         |

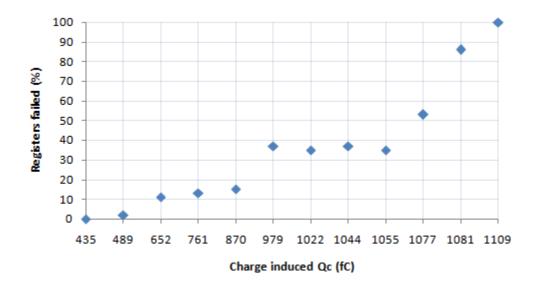

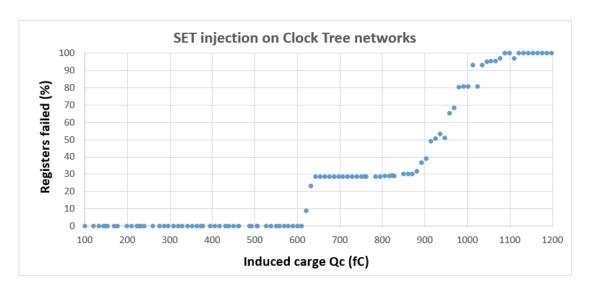

| Figure 5.7 Percentage of registers failed due to induced charge injected in the clo | ck source  |

|                                                                                     |            |

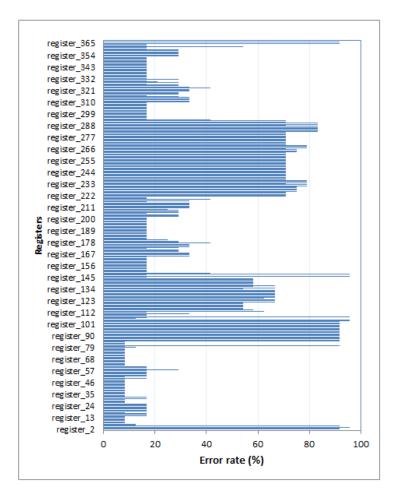

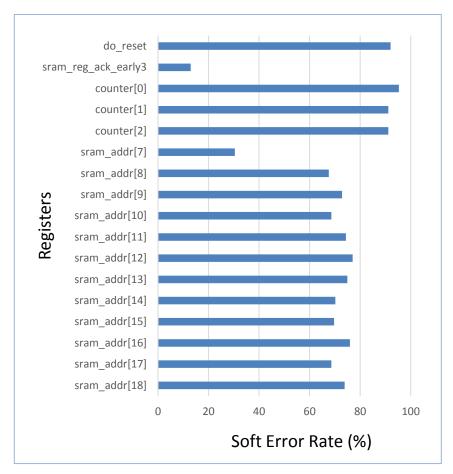

| Figure 5.8 Bit-flip rate in registers due to SET injection by electrical simulation |            |

| Figure 5.9 Error rate the circuit outputs due to SEU injections in the registers    |            |

| simulation.                                                                         |            |

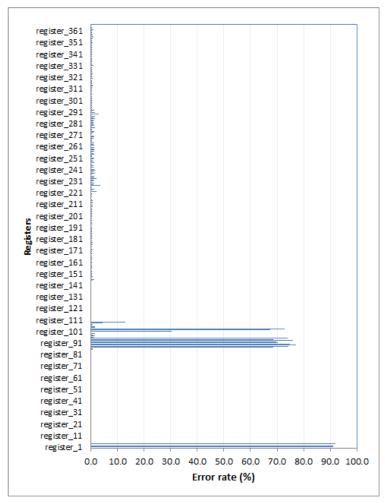

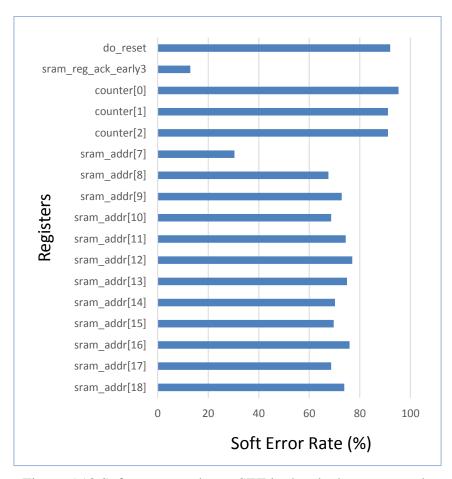

| Figure 5.10 Soft error rate due to SET in the clock tree network                    |            |

| Figure 5.11 SRAM arbiter layout using clock tree topology at 65nm                   |            |

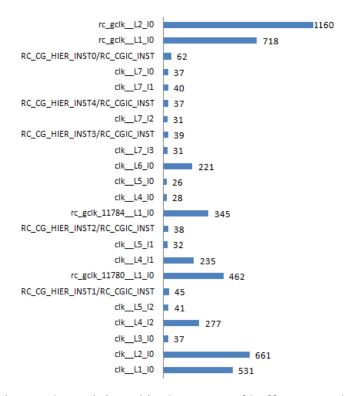

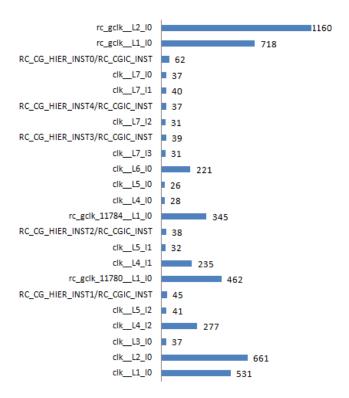

| Figure 5.12 Profile SRAM arbiter using clock tree topology                          | 83         |

| Figure 5.13 Electric model of mesh.                                                 |            |

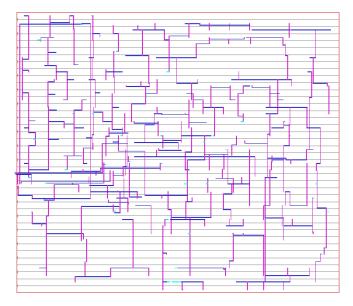

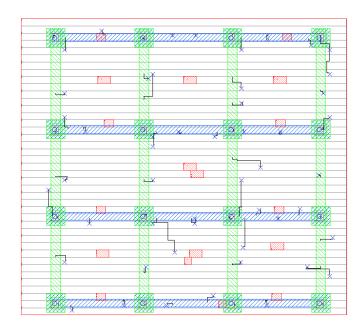

| Figure 5.14 SRAM arbiter layout using clock mesh                                    |            |

| Figure 5.15 Profile SRAM arbiter using clock mesh                                   |            |

| Figure 5.16 Comparison between clock tree and clock mesh                            | 86         |

# LIST OF TABLES

| Table 2.1 Results of SET fault injection in FPGA prototype in critical path | 33 |

|-----------------------------------------------------------------------------|----|

| Table 2.2 Result of SET propagation in critical path at hspice level        | 34 |

| Table 5.1 Types of Buffers                                                  | 72 |

| Table 5.2 Details of SET simulation replacing the small devices             | 76 |

# LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application Specific Integrated Circuits

BICS Build-In Current Sensor

CMOS Complementary Metal Oxide Semiconductor

CTS Clock Tree Synthesis

DEF Design Exchange Format

FF Flip-Flop

FIT Failure In Time

FPAA Field Programmable Analog Array

FPGA Field Programmable Gate Array

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor

LEF Library Exchange Format

LET Linear Energy Transfer

LVS Layout vs. Schematic

MBU Multi-bit Upset

MOS Metal Oxide Semiconductor

PIPB Propagation Induced Pulse Broadening

PLL Phase Locked Loop

PTM Predictive Technology Model

SEB Single Event Burnout

SER Soft Error Rate

SEGR Single Event Gate Rupture

SET Single Event Transient

SEU Single Event Upset

SEL Single Event Latch

SEE Single Event Effects

SPICE Simulation Program with Integrated Circuits Emphasis

SRAM Static Random Access Memory

TID Total Ionizing Dose

TMR Triple Modular Redundancy

VLSI Very Large Scale Integration

# TABLE OF CONTENTS

| ABS  | STRAC  | T                                                       | 3  |

|------|--------|---------------------------------------------------------|----|

| RES  | UMO.   |                                                         | 4  |

| LIST | ΓOF F  | IGURES                                                  | 6  |

| LIST | ΓOFT   | ABLES                                                   | 8  |

| LIST | Γ OF A | BBREVIATIONS AND ACRONYMS                               | 9  |

| 1    | Introd | luction                                                 | 14 |

| 1.1  | Motiv  | ation                                                   | 16 |

| 1.2  | Thesis | s Proposal                                              | 16 |

| 2    | Radia  | tion Environment and Effects on Semiconductors Devices  | 18 |

| 2.1  | Total  | Ionizing Dose (TID)                                     | 20 |

| 2.2  | Gate-  | oxide effects mechanism                                 | 20 |

|      | 2.2.1  | Threshold voltage shift                                 | 22 |

|      | 2.2.2  | Radiation-induced edge leakage                          | 23 |

| 2.3  | Single | Event Effects (SEE)                                     | 25 |

|      | 2.3.1  | Single Event Upset (SEU)                                | 26 |

|      | 2.3.2  | Single Event Transient (SET)                            | 28 |

|      | 2.3.3  | Single Event Latchup (SEL)                              | 31 |

| 2.4  | Propa  | gation induced pulse broadening (PIPB)                  | 32 |

| 3    | Clock  | Distribution Networks                                   | 36 |

| 3.1  | Defin  | itions                                                  | 36 |

|      | 3.1.1  | Skew                                                    | 36 |

|      | 3.1.2  | Jitter                                                  | 37 |

| 3.2  | Clock  | Distribution Architectures                              | 38 |

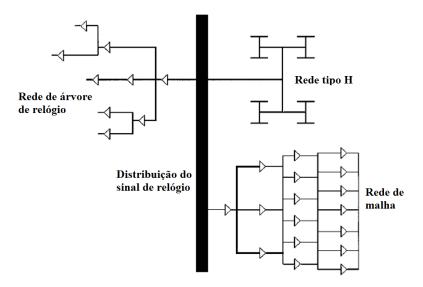

|      | 3.2.1  | Buffered Clock Tree Networks                            | 39 |

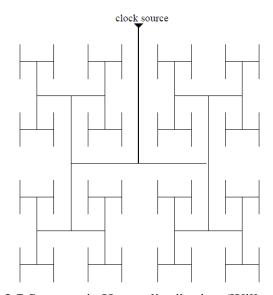

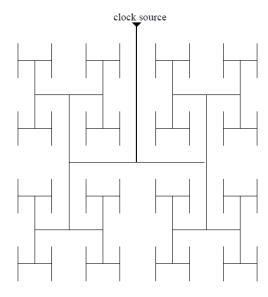

|      | 3.2.2  | H-Tree Clock Distribution Networks                      | 41 |

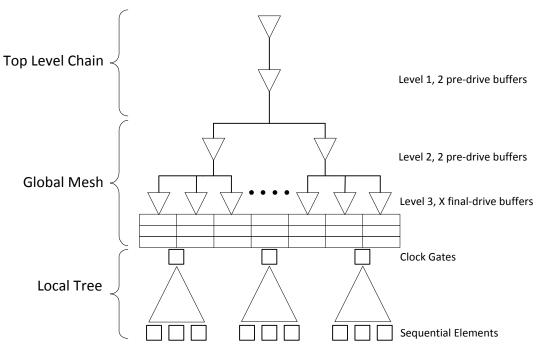

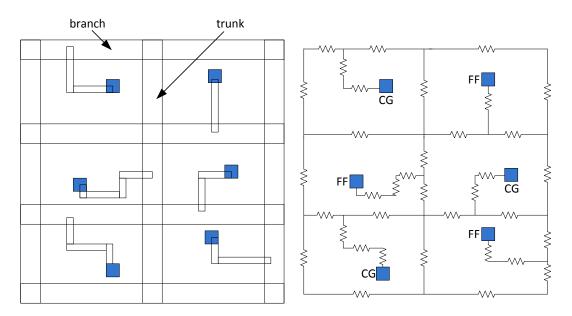

|      | 3.2.3  | Clock Mesh Distribution                                 | 41 |

| 3.3  | Power  | Dissipation in Clock Distribution Networks              | 44 |

| 3.4  | Radia  | tion Effects on Clock Tree Networks                     | 45 |

| 3.5  | State- | of-the-Art Mitigation Techniques to Clock Tree Networks | 46 |

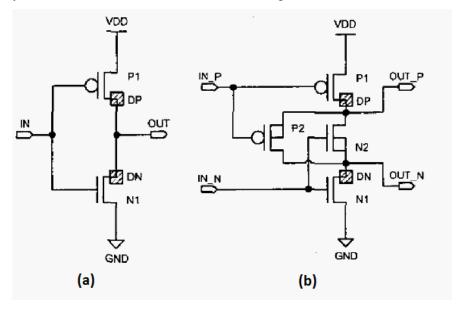

|      | 3.5.1  | Hardened Dual Port Inverter                             | 46 |

|      | 3.5.2  | SEU Hardened Clock Leaf Inverter                        | 47 |

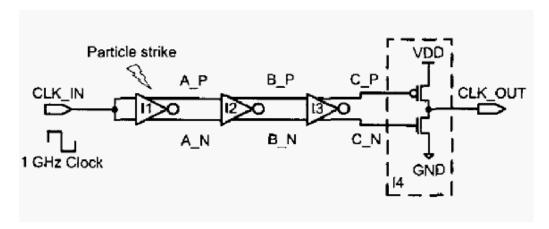

|      | 3.5.3  | TMR Clock Regenerator Circuit                           | 48 |

|      | 3.5.4  | Split-output Inverter Based Clock Regenerator Hardening | 49 |

| 3.6  | Problem Definition                                                      | 51       |

|------|-------------------------------------------------------------------------|----------|

| 4    | Proposed Methodology to analyze the set susceptibility in clock network | vorks 52 |

| 4.1  | Proposed Methodology                                                    | 52       |

| 4.2  | EXT-CLK tool                                                            | 53       |

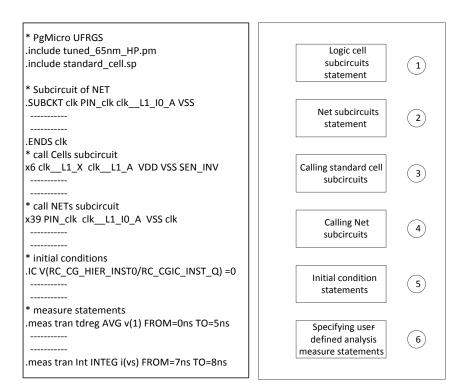

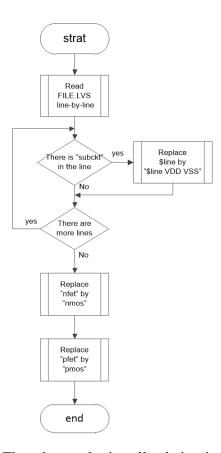

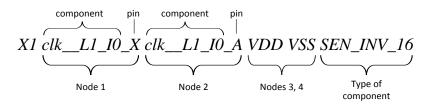

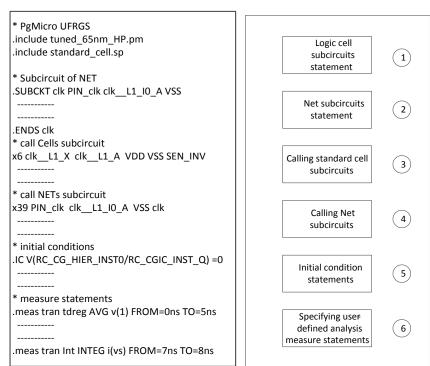

|      | 4.2.1 Logic cell subcircuits statement                                  | 55       |

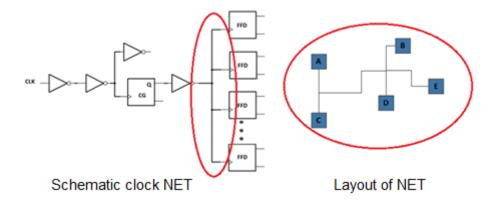

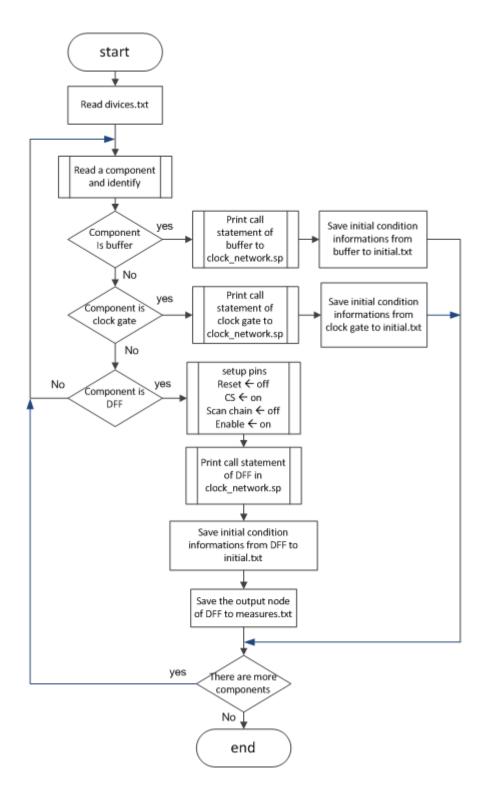

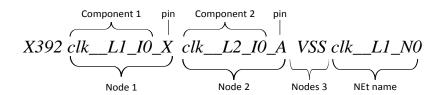

|      | 4.2.2 Nets subcircuit statement                                         | 56       |

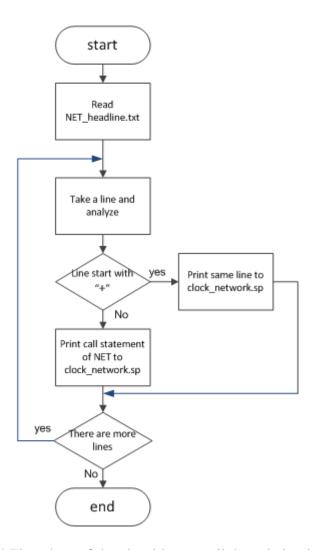

|      | 4.2.3 Net subcircuit headline                                           | 60       |

|      | 4.2.4 Call subcircuit of components                                     | 64       |

|      | 4.2.5 Call statement of net                                             | 66       |

|      | 4.2.6 Initial condition statement                                       | 67       |

|      | 4.2.7 Measure statement                                                 | 68       |

| 5    | Fault Injection Simulations                                             | 70       |

| 5.1  | Case study: SRAM arbiter                                                | 72       |

| 5.2  | SET injection in every node of the clock tree                           | 73       |

| 5.3  | SET injection in a particular path of the clock tree                    | 75       |

| 5.4  | Replacing small devices on clock tree                                   | 76       |

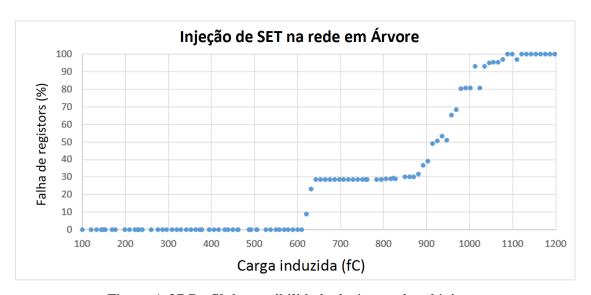

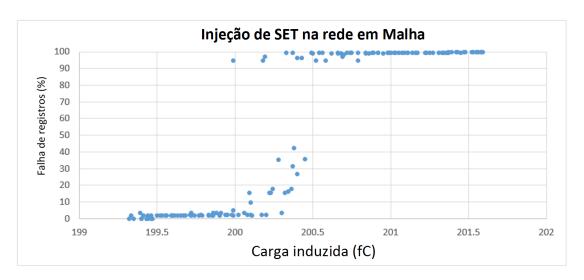

| 5.5  | SET injection in the clock source                                       | 77       |

| 5.6  | Soft Error Rate methodology                                             | 79       |

|      | 5.6.1 Soft error rate due to SET in clock tree networks                 | 81       |

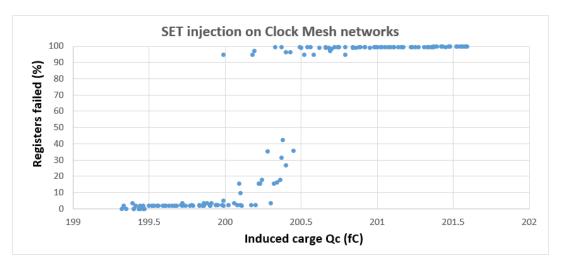

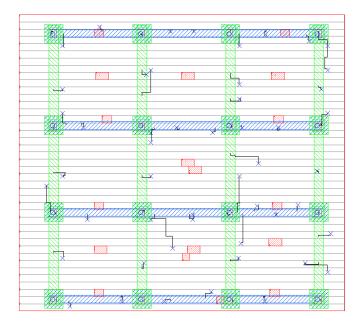

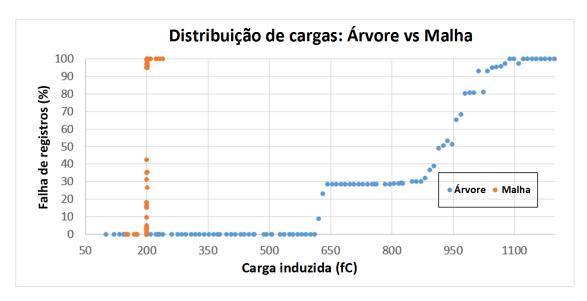

| 5.7  | Clock Mesh vs Clock Tree                                                | 82       |

| 6    | Conclusion                                                              | 87       |

| Refe | erences                                                                 | 88       |

| Apê  | endice A:                                                               | 94       |

| Aná  | ilise de single event effect em redes de relógio                        | 94       |

| A.1  | l Introdução                                                            | 94       |

|      | A.1.1 Motivação                                                         | 95       |

| A.2  | 2 Efeitos da radiação em componenes semicondutores                      | 96       |

|      | A.2.1 Total Ionizing Dose                                               | 96       |

|      | A.2.2 Mecanismo de TID sobre o gate                                     | 97       |

|      | A.2.3 Deslocamento da voltagem umbral                                   | 98       |

|      | A.2.4 Corrente de fuga nas bordas                                       | 99       |

|      | A.2.5 Single event effects (SEE)                                        | 99       |

| A.3  | 3 Redes de relógio em semicondutores                                    | 102      |

|      | A.3.1 Árvore de relógio                                                 | 102      |

|      | A.3.2 Rede de distribuição H                                            | 103      |

| A.3.3 Rede de relógio em malha (mesh)                              | 104 |

|--------------------------------------------------------------------|-----|

| A.4 Metodologia proposta para a análise do SET em redes de relógio | 105 |

| A.4.1 Metodologia proposta                                         | 105 |

| A.4.2 Ferramenta EXT-CLK                                           | 106 |

| A.5 Simulação de injeção de falhas                                 | 108 |

| A.5.1 Injeção de SET em cada nó                                    | 109 |

| A.5.2 Injeção de SET num caminho da rede                           | 110 |

| A.5.3 Substituição de buffers pequenos por maiores                 | 111 |

| A.5.4 Injeção de SET no início da rede                             | 112 |

| A.5.5 Soft error rate na árvore de relógio                         | 113 |

| A.5.6 Comparação entre rede de árvore e rede de malha              | 115 |

| A.6 Conclusões                                                     | 118 |

# 1 INTRODUCTION

The semiconductor manufacturing is becoming a major industry in the world. Success in the industry requires constant attention to the state of art in each stage. Techniques in chemistry and physics must be improved over the time. Semiconductor industry makes possible the production of integrated circuits (IC) to all electronic devices, like computers, mobile phones, tablets and other digital home appliances that are now inextricable parts of the modern society.

In the early days of integrated circuits, only a few transistors could be placed on a chip, because the scale used was large due to the contemporary technology and manufacturing yields were low compared to the current standards. As the level of integration was small, the design process was relatively simple. Over time, the numbers of transistors placed in the same area was improved to millions and billions. Then, in the early 1980s the term Very Large Scale Integration (VLSI) was introduced as the final step in the development process of design. This new process allows the creation of complex design such as Applications Specific Integrated Circuit (ASIC) or System-on-chip (SoC) that have multiple interfaces running with multiple asynchronous clocks, having frequency as high as multiple gigahertz.

Any error introduced in any stage of the manufacturing process may appear on the final electronic testing, and consequently the device may be lost. There are other errors that can be introduced when the IC is in operation, during its lifetime. In radiation environment the presence of heavy ions, protons and electrons, may introduce new type of errors. Particle strikes can ionize directly or indirectly the ICs provoking transient and permanent faults (Schrimpf, 2007).

Cosmic radiation is gamma radiation that has emanated from the sun and other terrestrial bodies traveled to our planet. On its journey, cosmic rays have not to pass through any substantial matter, only space. Hence, it can travel large distances without being absorbed. Once the radiation reaches our atmosphere it begins to be absorbed by the air, thus reducing the radiation level on the ground. Radiation belts, solar flares and cosmic rays are the main source of the space radiation. Protons, neutrons, electrons and heavy ions in space, are responsible for interference and malfunction of transistors operating in space. These charged particles pass through the semiconductor junctions and liberate electrons from the atoms. The effects of radiation on semiconductors have been classified as Single-Event Effects (SEE) (Barnaby et al., 2008). SEE caused by atmospheric radiation have been recognized as a design issue for avionics systems, as well as for high reliability ground-based systems due to the interaction with neutrons. If this transient effect occurs inside a memory cell it is known as Single Event Upset (SEU) and if the effect occurs in a combinational logic it is known as Single Event Transient

(SET). When SET and SEU are not logically masked by the application, they can provoke faults in the circuit functional behavior (Wissel et al., 2009) (Battezzati et al., 2009).

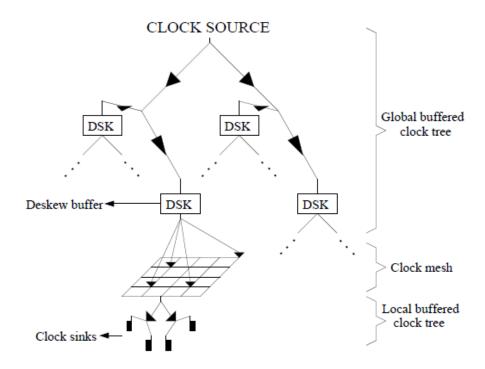

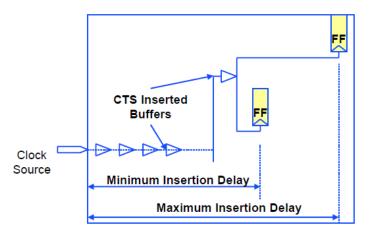

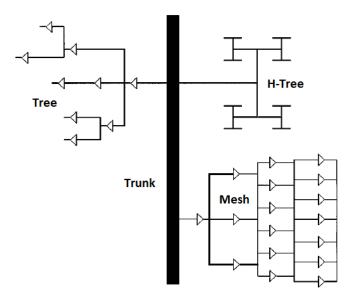

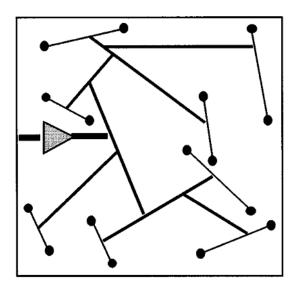

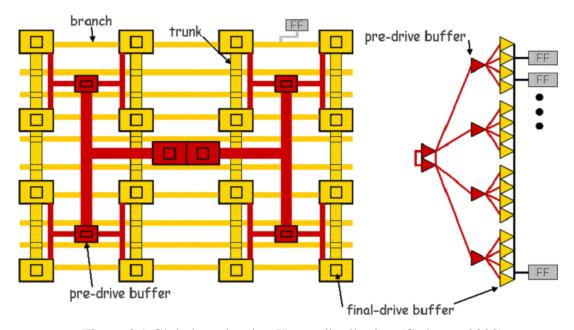

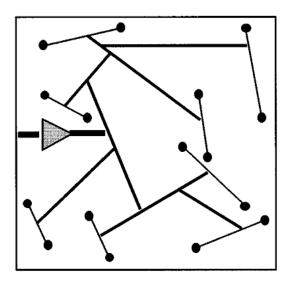

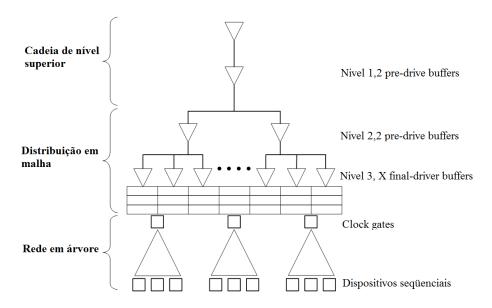

Decreasing the size of the transistors decreases also their capacitance, making them more susceptible to disruption caused by charge generated by radiation. Studies have indicated that high frequency operations with supply voltage reduced exhibit higher soft error rates (SER) (Juhnke e Klar, 1995). All the circuitry present in the clock tree networks is becoming vulnerable to radiation effects as well. SET may also occur at the output node of the clock buffers (Chellappa et al., 2011). Transient pulse can propagate through the network depending on the width and the amplitude of the pulses (Lacoe, 2008). Figure 1.1 depicts the scheme of a complex clock distribution topology of a modern microprocessor which consists of a root and many branches and buffers.

Figure 1.1 General clock distribution networks for processors (Wilke, 2008).

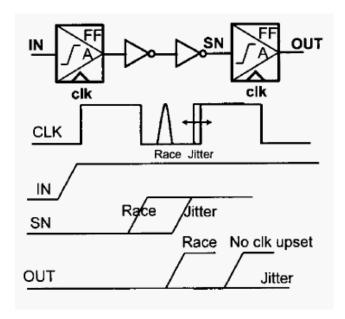

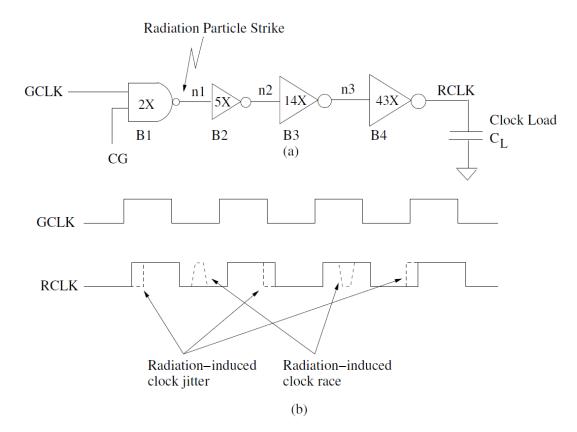

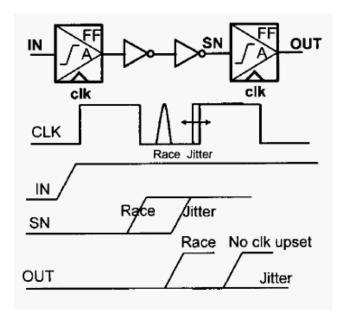

The effects of these transient pulses may be translated to clock glitches, clock jitter and clock skew (Ming e Shanbhag, 2005). Some authors classify this glitch as clock race (Seifert et al., 2005) (Dash et al., 2009). If the SET reaches one or more register elements, depending on the topology, those may have the stored value changed, resulting in a bit-flip.

In Figure 1.2, the additional clock pulse (race) results in a premature latching of the input data, which means that the output node will change the value early, becoming an erroneous data. This phenomenon may be a result of a particle strike. Depending on the type the application, these effects may alter the control or data flow of the circuit, resulting in an error.

Figure 1.2 Radiation induced jitter and race (Seifert et al., 2005).

#### 1.1 Motivation

As technology scaling is rapidly increasing, circuit designs become increasingly complex. Synchronizing each block or stage is a priority. Consequently clock distribution network is very relevant to ensure the correct behavior of the circuit when the clock signal must be delivered. Especially when the integrated circuit will work in aerospace, because radiation may generate single event effects over the clock network. This effect may be translated as a clock pulse and reach register elements storing incorrect data. There are techniques to analyze and improve the design against radiation effects, but there is a lack of techniques to analyze the susceptibility of single event effects focused in clock distribution networks which is our main motivation.

# 1.2 Thesis Proposal

Before developing any optimization technique for clock distribution networks resistant to radiation effects, it is necessary to develop an efficient analysis of susceptibility to single event effects (SET) in clock networks. Therefore, we investigate a method for accurate analysis of SET susceptibility in different clock network topologies. Then, we decide to elaborate a tool to extract the clock distribution network from the layout design and perform the analysis of susceptibility.

Hence, we evaluate the SET susceptibility in clock distribution networks of ASIC design. The main contributions of this work are presented below:

• Development of EXT-CLK tool, which allows the extraction the clock distribution network from the layout design to electrical model. This tool is able to extract different clock networks design such as clock tree, clock mesh and H-topology. The results obtained from this tool allow many types of SET simulations using hspice.

- Simulation of SET injection over different nodes in the clock distribution networks. These simulations will result in a profile of the susceptibility of the clock network to a specific circuit design. This profile helps us to identify vulnerable nodes in terms of critical charge (Q<sub>c</sub>).

- Simulation of SET injection in a particular path of the clock network, which allows making a profile of a path of the clock signal, showing the relation between the charges needed to provoke a failure and size of the cell used in the path.

- SET injection simulation in the clock source. Through this simulation, we identify the susceptibility of each register of the circuit in response to a given value of charge injected in the root the network. The result shows the minimum value of charge to achieve a failure and the maximum value to get 100% of fail on the registers. The same simulation allows the identification of the percentage of fail to each register and identifying the most sensitive register.

- Replacing smaller buffers. We show a simple experiment to evaluate the relation between size and susceptibility of buffers used in the clock network. We replace smaller buffers by larger and compute the SET injection simulation.

- Simulation of soft error rate in clock networks. This simulation combines electrical level simulation and logic level simulation. The results obtained are the soft error rate of each register of the clock network taking into account the masking effects of the application level.

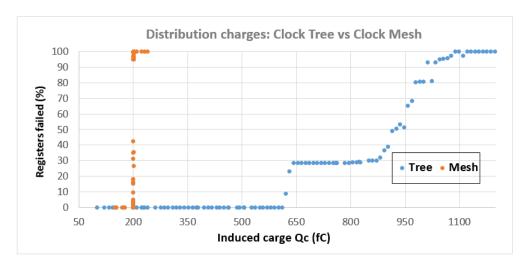

- Comparison between clock mesh and clock tree networks. We take a case study circuit in clock tree and developed the same circuit using clock mesh. After the extraction of the clock mesh, we make the profile of susceptibility and compare with the clock tree version. The result of the simulation shows a remarkable difference.

In this work, we present a new method for evaluating SET caused by radiation effects in clock distribution networks. In order to perform this method, we introduce EXT-CLK, a new tool developed in Bash command line for Linux environment and OS X environment (Mac OS). The main feature of EXT-CLK is the capability of performing several simulations to identify the susceptibility of the clock network. The simulations are focused in nodes, buffers, gates, and registers, which assists the production of a profile for the circuits. This tool can be used to perform accurate and efficient analyses of susceptibility of single-event effects (SET) in clock networks. As case study, SRAM arbiter circuit was selected to evaluate the proposed analysis method.

This work is organized as follows: the next chapter describes the radiation effects on semiconductor devices. In chapter 3 we discuss the types of clock distribution networks. In chapter 4 we describe in detail the EXT-CLK tool and how it works. In chapter 5 we show many SET simulation results obtained from the clock network. Finally, in chapter 6 we discuss the results and how this work can help designers to optimize the clock network for resisting against radiation effects.

# 2 RADIATION ENVIRONMENT AND EFFECTS ON SEMICONDUCTORS DEVICES

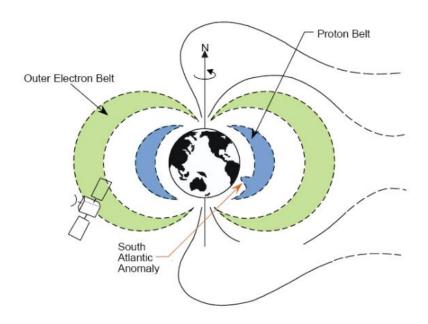

Looking back to the historical event, the first artificial satellite by US, Explorer I, launched on January 31, at 1958, carried a cosmic rays counter. The counter suddenly stopped to count cosmic rays when the spacecraft reached some altitude. It was later found that the counter was in fact saturated by an extremely high particle count rate. This was the day of the discovery of the Van Allen belts (Garber, 2007); that event was one of the outstanding discoveries of the International Geophysical Year. The evidence of trapped particles in Earth's radiation belts can be considered as the very first scientific outcome of the Space Age. The radioactive phenomena encountered in space are classified into four categories by source of origin: Radiation belts, solar flares, solar wind and cosmic rays.

- Radiation belts: The belt contains a combination of trapped electrons and protons from the outer belt to inner belt, as shown in Figure 2.3. The inner belt contains electrons with energy lower than 5 MeV and the outer belt may reach up to 7 MeV (Boudenot, 2007).

- Solar flares: Are a sudden brightening observed over the surface of the Sun, which is interpreted as a large energy release up to  $6 \times 10^{25}$  joules. Radiation is emitted across the entire electromagnetic spectrum from long wavelength up to gamma rays. Then, electrons, protons, and heavy ions are heated and accelerated in the solar atmosphere and reach the space environment.

- Solar wind: Is a stream of charged particles released from the upper atmosphere of the Sun. It mostly consists of electrons and protons with energy between 1.5 and 10 KeV. These particles can escape from the gravity of Sun caused by their high kinetic energy.

- Cosmic rays: Are very high-energy particles, mainly originated outside the Solar System. These particles may produce secondary particles, which penetrate and impact the Earth's atmosphere and sometimes even reach the surface of the Earth. Cosmic rays are originated from supernovas, but this is not thought to be their only source.

Figure 2.1 Van Allen radiation belts.

The flow of high-energy particles experienced in orbit and flight altitude demands the shielding of electronics with component redundancy, and radiation hardening. Thereby, this can increase their cost and reduce their performance. One of the effects of Total Ionizing Dose (TID) is an accumulative effect in the silicon oxides, which degrades the performance of the transistors, similar to an aging effect.

As the dimensions and operating voltage of commercial ICs are reduced to satisfy the increasing demand for high density, and low power, their sensitivity to radiation has to increase dramatically. Recently, soft errors have become a big concern in advanced commercial ICs because they can increase the product failure rate. In a qualified manufacturing silicon process, the typical failure rate for the hard reliability mechanisms is 10-100 failure-in-time (FIT), while the soft error rate can easily exceed 50,000 FIT (where one FIT is equivalent to one failure in a billion device hours) (Schrimpf e Fleetwood, 2004). For a single chip customer system even a soft error rate of 50,000 FIT is usually not problematic, but this failure rate is intolerant for high reliability systems with multi-chip assembly.

In the late 1970s, alpha particles emitted from the natural radioactivity decay of uranium, thorium and daughter isotopes present as impurities in package materials were found to be the predominant cause of soft error rate in DRAMs (Dodd e Massengill, 2003). During the same period, it was demonstrated that ionizing reaction products created from the interaction of cosmic neutrons with electronic material could cause soft error. In the mid-1990s, it has been established that the high energy cosmic radiation was the dominant error source in the DRAMs devices. Soft error was identified from low energy cosmic neutrons interactions with <sup>10</sup>B in devices material, especially in the borophosphosilicate glasses (BPSG), used extensively as insulating layers in integrated circuits. This mechanism has exhibited to be the dominant soft error rate in 0.25 and 0.18 µm CMOS SRAMs (Kobayashi et al., 2002). Despite of low levels of compounds found in package materials, sufficient alpha particles are generated to cause a significant rate of upsets in SRAM FPGAs (Actel, 2007). But after identifying the source of radiation on

package materials, high purity materials are employed to reduce the alpha emission. In devices requiring high reliability, uranium and thorium impurities have been reduced below one hundred parts per trillion. For conventional integrated circuits packaging, the reduction of material alpha emission was from 5-10 alphas/cm²-hr to less than 0.001 alphas/cm²-hr. To reduce soft error rate induced due to the <sup>10</sup>B activation by low energy neutrons, BPSG is replaced by other insulators that do not contain boron. When all these techniques are used, the soft error rate of the integrated circuit is reduced significantly, but ultimately limited by cosmic high-energy neutrons interactions that cannot be easily prevented.

The nature of the interaction between semiconductors and high-energy particles depends on the properties of the particle such as its charge, energy, momentum, and target material: density and mass. Other parameters that determine the damage are the flux and the fluency of particles over the device in exposition. Spacecraft anomalies can be divided mainly in two effects: Total Ionizing Dose (TID) affects associated with trapped particles in the magnetic Van Allen belts. And the second, Single Event Effect (SEE) resulting from the interaction of highly energetic particles (including protons, cosmic rays and other heavy particles). These can be a source of significant data corruption in the FPGAs (Actel, 2007) and multiple devices.

# 2.1 Total Ionizing Dose (TID)

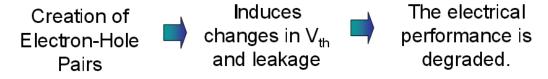

Exposure to radiation produces long-term changes in device and circuit characteristics that may result in parametric degradation or functional failure. Total Ionizing Dose (TID) mainly affects insulating layers, because trapped charges degrade the electrical performance. Non-ionizing energy results in displacement damage and defects in both insulator and semiconductor regions. In older technologies, these effects were described by a spatially uniform representation of the cumulative amount of energy deposited. The accuracy of this description relies on the relatively large size of the devices and the energy deposit by individual particles or photons. In very small devices, less than 130 nm, this approach is no longer valid (Schrimpf, 2007). A simple way to explain the TID effects is shown in Figure 2.2. The consequence of TID in CMOS transistors are: threshold voltage shift, leakage current and isolation oxide. But first we will describe the mechanism of gate-oxide effects.

Figure 2.2 Ionizing Dose: Cumulative effects

#### 2.2 Gate-oxide effects mechanism

The cumulative damage incurred in semiconductor due to exposure to radiation is referred as the total dose effect. This mechanism can be described in four steps. In the first step, the ionizing radiation creates electrons-holes pairs. When an energetic particle

(proton, electron, or heavy ion) impacts a semiconductor. The particle loses energy at a constant rate as it passes through the solid material, as long as it is not near the end of its range. The mechanism by which electrons and protons lose energy, is primarily by inelastic Coulomb scattering in which the incident particle ejects an outer shell electron from an atom. The incident particle repeats this scattering process as it continues through the solid producing a line of electrons-holes pairs. The rate at which a particle loses energy is normalized by the density of the material in which the energy is deposited, and it is referred as linear energy transfer (LET) rate. The elements most sensitive to total dose effects from ionizing radiation in a CMOS device are the gate and isolation oxides, which are most often fabricated with SiO<sub>2</sub>.

Immediately after the creation of a line of electrons-holes pairs, a fraction of the pairs recombine. The temporal window during where recombination occurs is very short and limited by the time of electron to transit and be removed from the gate oxide (typically less than 0.1 ps). The recombination occurs in response of the gate electric field. Even with no voltage applied to the gate, recombination will be completed in at most a few picoseconds due to the built-in gate electric field. The amount of recombination depends on the density of electrons-holes pairs and the applied electric field. For high LET particles, the density of electrons-holes pairs is high, the Coulomb interaction between an isolated electrons-holes pair is effectively screened out, and the fraction of electrons-holes pairs that recombine can be high. For lower LET particles, the density of electrons-holes pairs is less, the interaction between different electrons-holes pairs is negligible, and the Coulomb interaction between the isolated electron and hole of a pair dominates the recombination process. The effect of an electric field on the recombination processes is to separate the electrons and holes, which will result in less recombination. Furthermore, both electrons and holes that are within a characteristic tunneling length of SiO<sub>2</sub>, 4-5 nm are tunnel out of the gate oxide rapidly after a radiation pulse.

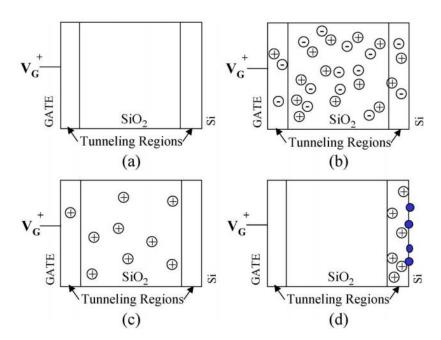

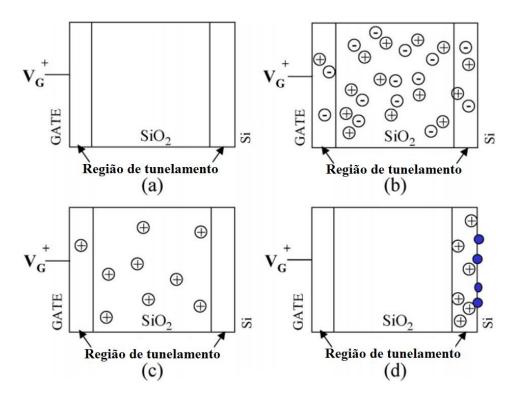

Figure 2.3 Charge distribution in a gate oxide after expose to radiation (Lacoe, 2008).

At this point, the only charges that left in the gate oxide are holes, as shows Figure 2.3 (c). The second step is the drift of the remaining holes to the oxide/silicon interface, due to electric field from the positively biased gate electrode. This process has been studied in depth, and it has been determined that the transport by holes is primarily by hopping between localized sites in the gate oxide. This process is both thermally and field-activated. The holes transported are highly dispersed, occurring over many decades in time after a radiation pulse. The transport of these holes to the interface occur via polaron hopping where the holes become self-trapped by their own deformation potential.

In the third step, a fraction of the holes are trapped at the interface. This oxide-trapped charges are positively charged, and can be neutralized over time by either electron tunneling from the silicon or by thermal emission of an electron. The activation energy for this process is relatively low, significant recovery can occur for radiation exposure over a long time period such as for a space mission

In the fourth step, the formation of "interstate traps" can occur. A simplistic view is that interface states are associated with dangling bonds between the silicon and the SiO<sub>2</sub>. Interface states exist within the silicon band gap at the interface with SiO<sub>2</sub>. For NMOS transistors, the interface states act as negative charges in the gate-oxide of a NMOS transistor, or positive charges in the gate-oxide of a PMOS transistor. These steps are described pictorially in Figure 2.3 (d).

#### 2.2.1 Threshold voltage shift

The effect of introducing charges in the gate oxide and/or at the gate-oxide/silicon interface is to shift the threshold voltage  $\Delta V_T$  in CMOS transistors. The shift in threshold voltage is determined by integrating the weighted additional charge density  $(\rho)$  over the oxide thickness  $(t_{ox})$ .

$$\Delta V_T = \Delta V_{ot} + \Delta V_{it} = \frac{-1}{C_{ox}t_{ox}} \int_0^{t_{ox}} x \, \rho(x) dx$$

Equation 2.1

Equation 2.1 describes the shift threshold voltage, where x = 0 represents the polysilicon/gate oxide interface, and  $C_{ox}$  is the gate capacitance. The trapped holes charges in oxide (ot) is always positive. Hence,  $\Delta V_{ot}$  for both NMOS and PMOS transistor are always negative. For NMOS transistors, interface trapping charge (it) is negative, while for PMOS transistors, interface trapping charge is positive. The net threshold voltage shift  $\Delta V_T$  will be the sum of  $\Delta V_{ot}$  and  $\Delta V_{it}$ . The amount of charge generated in the oxide by radiation is proportional to the oxide thickness. In addition, the effect of the oxide charge on the threshold voltage is proportional to the distance of the charge from the gate electrode, as describes the Equation 2.2

$$\Delta V_T = -\frac{Q_{ot}}{C_{ox}} \propto x_{ox}^2$$

Equation 2.2

Thus, thin oxide, such as modern gate oxides, are much less sensitive to ionizing radiation than field oxides or older gate oxides. Thin gate oxides are even less sensitive to total ionizing dose than this estimate would suggest because most of the charge within 5 nm of the interface is quickly removed by tunneling (Schrimpf, 2007).

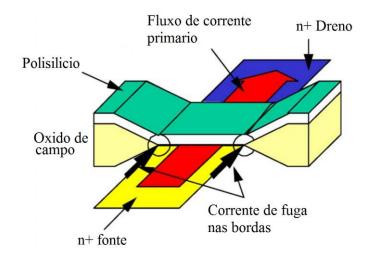

#### 2.2.2 Radiation-induced edge leakage

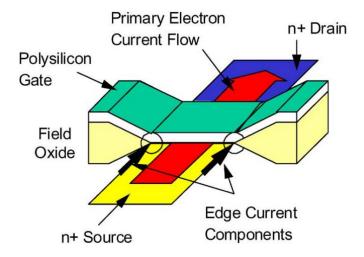

Transistors are electrically isolated from one another by a thick field oxide (FOX). The edges for a standard transistor layout are defined by the gate oxide interfaces with the FOX. Figure 2.4 shows an off-axis view of a standard MOS transistor. Since the quality of the oxide near the FOX/gate interface is poorer than that of the gate oxide, it may be more efficient in trapping charge. Radiation-induced trapped holes in these edge transistors can result in a negative shift in the threshold voltage, then if this is large enough, the edge transistors becoming conductive resulting in a source-drain current in the transistor off state. That off-state current can increase due to radiation-induced edge effects. The consequences of increase off-state current may be result in signal corruption and reduced margins of work. In some cases this can lead to functional failure, as the transistors are always active. Edge leakage is not a problem for PMOS transistors, for PMOS transistors the effect of oxide-trapped charge and interface trapped charge are to shift an already negative threshold voltage even further in the negative direction.

Figure 2.4 Edge transistor current (Lacoe, 2008).

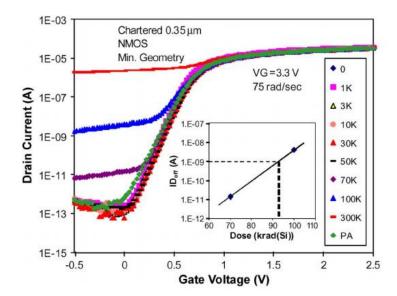

Edge leakage in a commercial CMOS process could exceed 1  $\mu$ A for total dose levels as low as 10 krad(Si). The  $I_D$ - $V_G$  characteristics as a function of total dose for a 0.35  $\mu$ m (minimum geometry) NMOS transistor fabricated by Chartered Semiconductor are show in Figure 2.5. This process uses local oxidation of silicon (LOCOS) and has a gate-oxide thickness of 7.6 nm. For exposure up to 50 Krad, the  $I_D$ - $V_G$  characteristics no change. At 70 Krad, there is an increase in the off-state current of approximately  $10^{-11}$  A. At 100 Krad, the off-state current has increased a little more than 1 nA. At 300 Krad the off-state current has increased approximately 5 times the drive current.

Figure 2.5  $I_D$ - $V_G$  curves as a function of total dose for 0.35  $\mu$ m minimum geometry NMOS transistor (Lacoe, 2008).

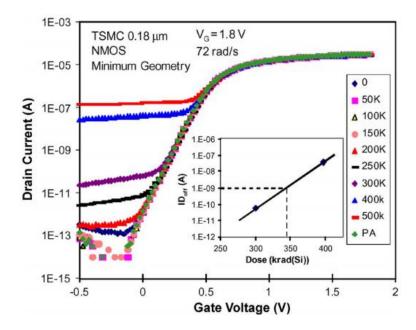

Figure 2.6 shows the  $I_D$ - $V_G$  characteristics as a function of total dose for a 0.18  $\mu$ m (minimum geometry) NMOS transistor fabricated by TSMC. This process uses Shallow Trench Isolation (STI) technology and has a gate-oxide thickness of 3.2 nm. The curves are similar to 0.35  $\mu$ m process, but for 0.18  $\mu$ m the total-dose hardness level is approximately 345 krad under high dose rate. The drain current in 0.18  $\mu$ m is 1 nA at approximately 350 krad. While, for 0.35  $\mu$ m process, 1 nA is caused by 100 krad.

Figure 2.6  $I_D$ - $V_G$  curves as a function of total dose for 0.18 µm (Lacoe, 2008).

In older technologies, TID effects are described by the cumulative amount of energy deposited. In very small devices, less than 130 nm, this approach is no longer valid, as has been shown in Figure 2.5 and Figure 2.6 (Schrimpf, 2007).

After explaining the effects of TID on CMOS devices, the semiconductor industry is addressing this issue by researching potential new materials to replace SiO<sub>2</sub> as the gate dielectric material. The key is material with dielectric constant (K) values larger than SiO<sub>2</sub>. This potential gate dielectric material is often referred as high-K dielectric. Because the dielectric constant is larger than SiO<sub>2</sub>, the thickness can be increased to maintain the same capacitance while decreasing the tunneling current. Among the materials under consideration are hafnium oxide Hf-O/SiO<sub>2</sub>/Si and aluminum oxides Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>N<sub>y</sub>/Si (Lacoe, 2008). The TID effects on capacitors and transistors fabricated with high-K gate dielectrics indicate that while for thick oxides they can trapping efficiency. For test structures with dielectric thickness less than 5 nm, the amount of charge trapping is very small, resulting in very small shifts. Since the high-K dielectric thickness in advanced CMOS technologies be less than 5 nm, the results look encouraging using these technologies for space applications.

# 2.3 Single Event Effects (SEE)

Single event effects is a phenomena which result from the interaction between a single energetic particle and sensitive region of a microelectronic circuit. This particle can be energetic protons, neutrons or ions (Munteanu e Autran, 2008). These effects are classified in hard errors and soft errors. Hard errors are non-recoverable errors, while soft errors may be recoverable by a reset, a power cycle or simply rewriting the information. Hard errors such as Single Event Burnout (SEB) in power MOS, IGBT or power bipolar transistors, single event gate rupture (SEGR), micro-dose induced threshold voltage variation in MOS transistor, are not be discussed in this work, but they represent also an important issue in SEEs.

Soft errors include a great variety of manifestation depending upon the device considered. In memory devices, SEU is manifested in latch and register. This correspond to a bit-flip of the one cell. If more than one bit-flip occurred by a single event, a Multi-bit Upset (MBU) is obtained. In analog devices SETs are mainly transient pulses in operational amplifiers, comparator or reference voltage circuits. In combinatorial logic, SETs are transient pulses generated in a sensitive node that may propagate in a combinatorial circuit and eventually be latched in a storage cell. In bulk CMOS technology, PNPN parasitic structure may be triggered giving a Single Event Latch-up (SEL). SEL is associated with a strong increase of power supply current. SEL can be destructive by overheating of the structure and localized metal fusion.

In this section we will focus on devices and nondestructive SEEs. Also we will describe the mechanism of SEE with particular emphasis on SEU in static random access memories (SRAM) and SET in logic circuits. The only destructive SEE that we describe will be SEL.

#### 2.3.1 Single Event Upset (SEU)

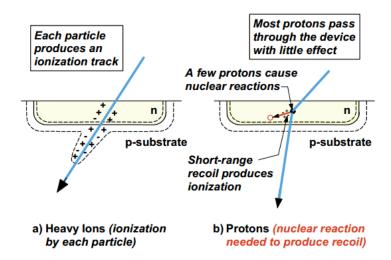

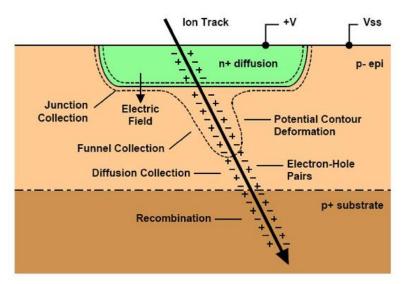

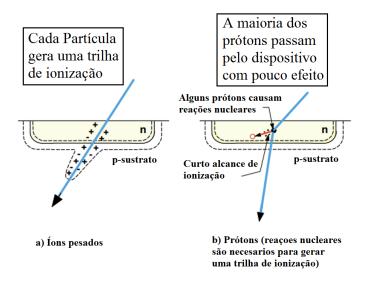

Single event upset (SEU) is defined by NASA as "radiation-induced errors in microelectronic circuits caused when charged particles lose energy by ionizing the medium through which they pass, leaving behind a wake of electron-hole pairs" (Baloch et al., 2006). SEUs are non-destructive events and a simple reset or rewriting results in normal device behavior. This phenomenon may occur in a digital circuit when a particle strike causes data to change states in a storage element such a flip-flop, latch or memory bit (Vargas e Nicolaidis, 1994). Direct ionization is the primary charge deposition mechanism for upsets caused by heavy ions, which are rather loosely defined as an ion with atomic number  $Z \ge 2$ . Lighter particles, such as protons and neutrons, usually do not produce enough charge by direct ionization to cause upsets in memory circuits, as show in Figure 2.7, although this can change with the technologies scale and the critical charge to create an upset decreases. These particles can, however, produce upsets due to indirect mechanisms. When a high-energy proton or neutron strikes a semiconductor, it may undergo an inelastic collision with a target nucleus. This can generate a nuclear reaction resulting in the emission of alpha particles or gamma particles and the recoil of a daughter nucleus, or a spallation reaction in which the target nucleus is broken into two fragments, each of which can recoil. Any of these reaction products can now deposit charge along their paths by direct ionization, because these particles are much heavier than the original protons and neutrons, they can deposit greater linear charge density as they travel through the semiconductor, which is more likely to cause upsets than the ionization created by the original particle. A depict of the mechanism is shown in Figure 2.8 (Lacoe, 2008).

Figure 2.7 Mechanism for heavy ions and protons in semiconductors (Lacoe, 2008).

Figure 2.8 Energetic particle strike a p-n junction extending the depletion region as a funnel (Lacoe, 2008).

When the heavy ion strikes a p-n junction, the most sensitive sites for upset in bulk CMOS, creating a funnel extension of the depletion region under the junction. The funnel is caused by the projection of the electrostatic potential of the heavily doped surface electrode along the wire charge. In response, the current flow creates an effective short across the p-n junction for the period of time needed to dissipate the generated charge, typically a few nanoseconds. The later contribution of the current flow is associated whit diffusion of the charge toward the critical node. The impact of this current on the circuit operation depends strongly on the location and angle of the particle trajectory though the circuit, and the circuit response of an inadvertent current pulse at the particle location. The SRAM is a useful example of an SEU sensitive component.

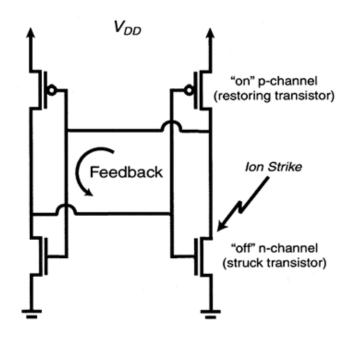

The upset in SRAMs is due to the active feedback in the cross-coupled inverter pair that forms a typical SRAM memory cell, shown in Figure 2.9. When an energetic particle strikes a sensitive location in a SRAM (typically the reverse-biased drain junction of a transistor biased in the "off" state, for example the "off" n-channel transistor shown in Figure 2.9, charge collected by the junction results in a transient current in the struck transistor. As this current flows through the struck transistor, the restoring transistor ("on" p-channel transistor in Figure 2.9.) attempt to balance the particle-induced current. Unfortunately, the restoring transistor has a finite amount of current drive, and equally importantly, a finite channel conductance. The current flows through the restoring transistor therefore induces a voltage drop at its drain. This voltage transient in response to the single-event current transient is actually the mechanism that can cause upset in SRAM cells (Dodd e Massengill, 2003). The voltage transient is essentially similar to a write pulse and can cause the wrong memory state to be locked into the memory cell.

Figure 2.9 SRAM core under ion strike.

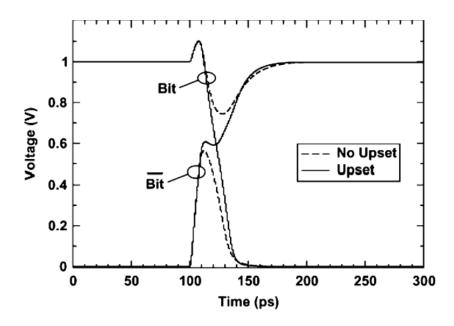

Figure 2.10 Ionization upset threshold in SRAM core (hspice simulation 65nm).

Figure 2.10 shows the drain voltage waveform of two side of the SRAM cell. The value data change (upset) when the ionization density reach the critical charge. The dashed lines represent when the ionizing density is slightly lower (no upset) and this cannot change the data.

# 2.3.2 Single Event Transient (SET)

A single event transient (SET) is the result of a voltage disturbance on a signal line caused by a particle strike. This single event occurs on non-latched elements such as

combinatorial logic and clock line or global control lines (Loveless et al., 2012). The voltage transient generated by this phenomena can propagate any significant distance through the combinatorial logic depending of the width of the transient pulse and the capacitance of the transistor (Wirth et al., 2007). Combinatorial circuit can interpret a SET voltage as a high-level state by the short time and produce unwanted behavior in the circuit. With the technology scaling the combinatorial circuit are more sensitive to transient pulse width narrow. The width of the SET is one of the main factors that determine whether an SET will result in an upset (fault) or not (Narasimham et al., 2009). According to Dodd (Dodd et al., 2004), which recall the SET as digital-SET (DSET) at least there are four criteria that must be met for a phenomena to result in a circuit error.

- The particle strike must be generate a transient pulse capable to propagating through the circuit.

- There must be an open logic path through which the DSET can propagate to arrive at a latch or other memory element.

- The DSET must be of sufficient amplitude and duration to change the state of the latch or memory element.

- In synchronous logic, the DSET must arrive at the latch during the latching edge of the clock.

The probability that transient pulse glitches will be captured as valid data in combinational logic increase linearly with frequency because the frequency of clock edges increases. As circuit speeds increase, it is also expected that the ability of a given transient pulse to propagate increases, however, one might also conjecture that the duration of transient pulse decreases. Due to both their greater ability to propagate in high speed circuits and their higher probability of capture by subsequent storage elements, such as latches, this phenomena have been predicted to became a very important issue in deep submicron digital ICs.

Figure 2.11 SET propagation in an inverter chain (Dodd et al., 2004).

Figure 2.11 shows an example of combinational circuit that is under ion strike in the off-biased n-channel transistor. The transient pulse generated in the first inverter travel from the second inverter through the chain of inverter to flip-flop. Depending of the

properties of each inverter the transient pulse may be broadening or attenuated and finally reaching the flip-flop and storing a data invalid.

On the other hand, a transient pulse will not affect the results of a computation unless it is captured in a memory circuit. Therefore, Shivakumar (Shivakumar et al., 2002) defines a soft error in combinational logic as a transient error in the result of a logic circuit that is subsequently stored in a memory circuit. A transient pulse in a logic circuit might not be captured in a memory circuit because it could be masked by one of the following three phenomena.

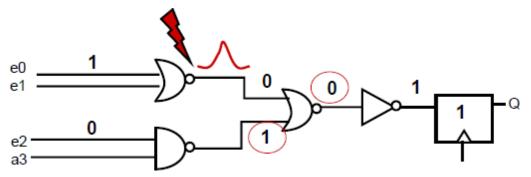

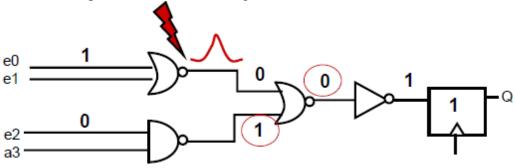

• Logic masking occurs when a particle strikes a portion of the combinational logic that is blocked from affecting the output due to a subsequent gate whose result is completely determined by its other input values. An example is shown in Figure 2.12. Other example of logic masking is when the combinational logic have a clock gate blocking the signal in case of clock networks.

Figure 2.12 Logic masking.

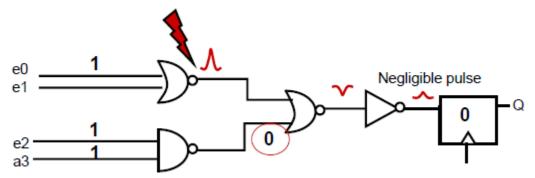

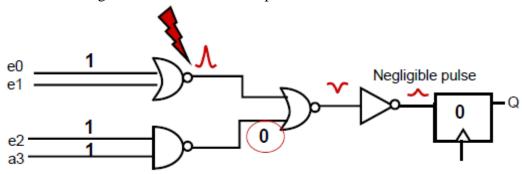

• **Electrical masking** occurs when the transient pulse, resulted from a particle strike, is attenuated by subsequent logic gates due to the electrical properties of the gates, to the point that it does not affect the result of the circuit. Figure 2.13 shows an example of electrical masking.

Figure 2.13 Electrical masking.

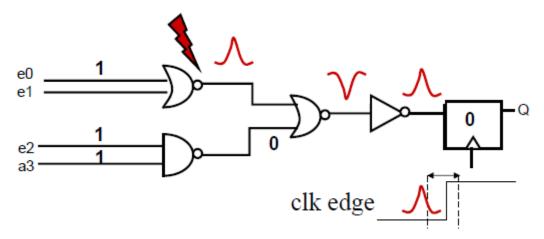

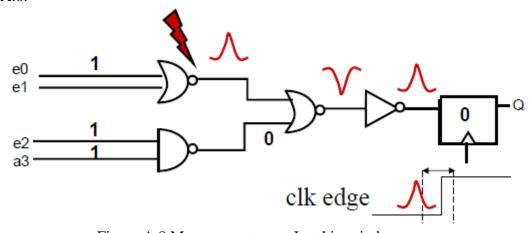

• Latching-window masking occurs when the transient pulse, generated from a particle strike, reaches the latch, but not at the clock transition where the latch captures its input value. Figure 2.14 shows how the transient pulse reach the flip-flop but it is ignored because the clock edge is not available.

Figure 2.14 Latching-window masking.

# 2.3.3 Single Event Latchup (SEL)

Single Event Latchup is an abnormal high-current state in a device caused by the passage of a single energetic particle through sensitive regions resulting in the loss of device functionality. Adjacent n-type and p-type regions in CMOS circuits may form a parasitic thyristor composed of two pairs of parasitic bipolar transistors. Some PNPN structure can switch from a high impedance to a low impedance. A spurious current spike in one of these transistors may be amplified by the large positive feedback of the thyristor to cause a virtual short between  $V_{DD}$  and ground (Nicolaidis, 2006). If power is not removed quickly, catastrophic failure may occur due to excessive heating or bond wire failure.

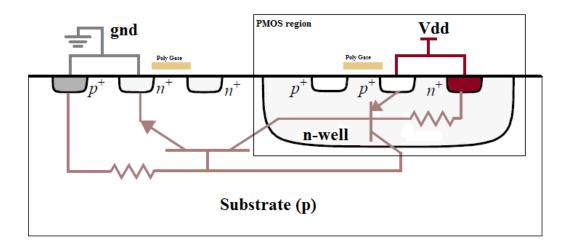

Figure 2.15 PNPN structure in CMOS technology (Deepon Saha, 2010)

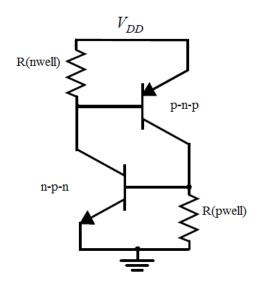

Consider the n-well structure in the Figure 2.15. The NPNP structure is formed by the source of the NMOS, the p-substrate, the n-well and the source of the PMOS. A circuit equivalent is also shown in Figure 2.16. When one of the two bipolar transistors gets forward biased (due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out (Rabaey et al., 1999).

Figure 2.16 Equivalent circuit of CMOS latchup.

An ideal PNPN structure is active if the gain product of the NPN and PNP transistors is  $\beta 1$  x  $\beta 2 > 1$ , where  $\beta 1$  and  $\beta 2$  are the current gains Ic/Ib of the bipolar transistors. Other important parameters that influence the sensitivity are the resistivity and depth of the well and the resistivity of the substrate. To reduce the base-emitter resistor can be used a thin epitaxial layer on a high doped substrate. Multiple substrate and well contacts also reduce the base-emitter resistors.

# 2.4 Propagation induced pulse broadening (PIPB)

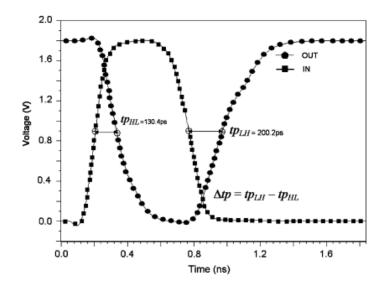

Propagation Induced Pulse Broadening (PIPB) is another concern to take into account in the design. Since an initial transient pulse is broadened enough through the logical circuit that have more probability of generating a data corrupted (Mogollon et al., 2009) (Ferlet-Cavrois et al., 2007). A logical circuit, as a chain of inverters or structure of the clock tree network, is susceptible to glitch voltage and a transient pulse with a few picoseconds can be broadened to about a few nanoseconds. Several simulations have been performed in (Mogollon et al., 2009) to show the PIPB effects dependence on the  $V_T$  voltage. They show that in a chain of two identical inverters after the first inverter the transient pulse is broadened, however, when passing through the second inverter the effect is reverted and the initial transient pulse width is recovered. Any SET broadening or attenuation will arrive from the imbalance between  $t_{PHL}$  (propagation time from high to low) and  $t_{PLH}$  (propagation time from low to high).

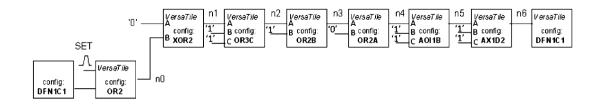

Sterpone *et al.* investigated the effects of PIPB on SET in Flash-based FPGA (Sterpone et al., 2011) using as case study ProASIC3 family manufactured in 130mn technology. The circuit under experiment was a logic path of a Pipelined Multiplier including logic gates (2-bits NOR, 2-bits AND and 2-bits EX-OR), as shown in Figure 2.17.

Figure 2.17 Logic path mapping in the Flash-based FPGA.

The result of the experiment is shown in Table 2.1, the measurement have been performed considering the average measurement over 15 electrical injections. Table 2.1 shows two types of SET injection simulations, SET pulse 0-1-0 and SET pulse 1-0-1. The SET pulse 0-1-0 was attenuated and filtered, in some cases it is possible to confirm that shorter pulses are more susceptible to filtered effects. On the other hand, when the SET pulse 1-0-1 is considered, the effect is quite opposite. The SET pulse are broadened. The broadening effect is more relevant for shorter pulses, reaching the 82% of effect PIPB for a 350 ps of injected pulse.

| node     | SET    | PIPB     | PIPB factor       | SET    | PIPB     | PIPB factor       | SET      | PIPB     | PIPB factor       |

|----------|--------|----------|-------------------|--------|----------|-------------------|----------|----------|-------------------|

|          | width  | Effect % | [ps / logic path] | width  | Effect % | [ps / logic path] | width    | Effect % | [ps / logic path] |

| OP.      | 350 ps |          |                   | 700 ps |          |                   | 1,200 ps |          |                   |

| SET      |        |          |                   | _      |          |                   |          |          |                   |

| /\_      |        |          |                   |        |          |                   |          |          |                   |

| n6       | 0 ps   | filtered | -350              | 355 ps | -50%     | -355              | 876 ps   | -27%     | -324              |

| SET<br>V | 350 ps |          |                   | 700 ps |          |                   | 1,200 ps |          |                   |

| n6       | 640 ps | +82%     | +290              | 888 ps | +27%     | +188              | 1,410 ps | +18%     | +210              |

Table 2.1 Results of SET fault injection in FPGA prototype in critical path

In order to characterize the PIPB effect, the same critical path was modeled at transistor level using hspice at 130 nm of Predictive Technology Model (NIMO, 2012). Each logic gates of the critical path was modeled according to Versatile from ProASIC3, more details in (Sterpone et al., 2011). Table 2.2Error! Reference source not found. shows the simulation of PIPB effects in SET propagation at hspice based on Figure 2.17. Note that at each Versatile output SET may be filtered or broadened according to the SET width and its direction (1-0-1 or 0-1-0). Note also that the PIPB effects may vary along the logic path.

| node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SET      | PIPB Effect % | SET   | PIPB Effect % | SET   | PIPB Effect % |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|-------|---------------|-------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Width    |               | Width |               | Width |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (ps)     |               | (ps)  |               | (ps)  |               |

| SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 350      | -             | 700   |               | 1200  |               |

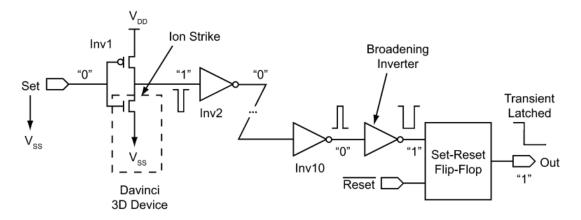

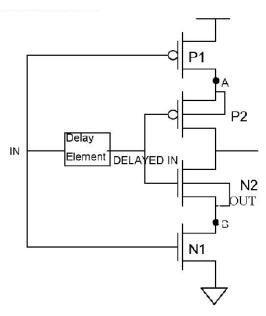

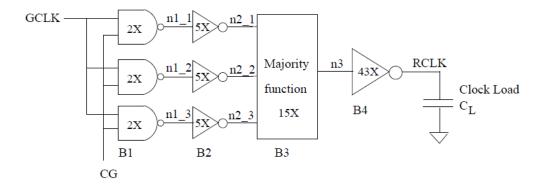

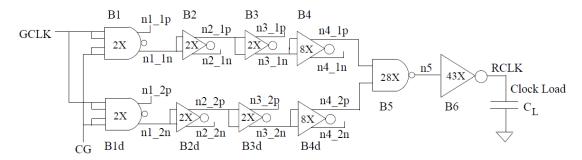

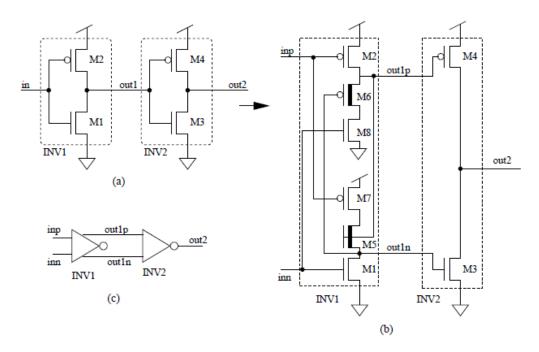

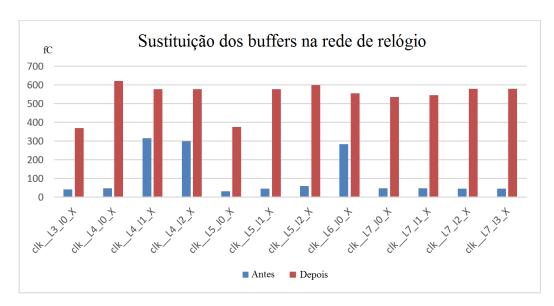

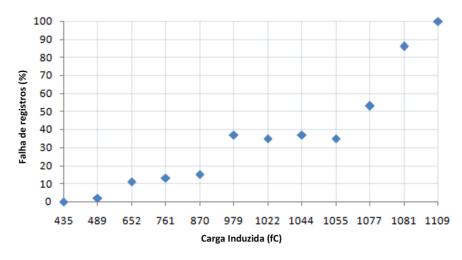

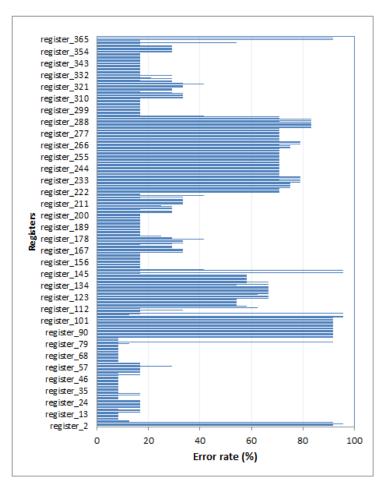

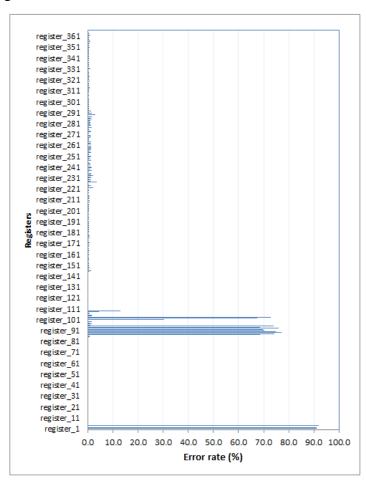

| n0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 276      | -21%          | 630   | -10%          | 1132  | +5            |