UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

**GRACIELI POSSER**

### **Electromigration Aware Cell Design**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Ricardo Augusto da Luz Reis

Co-advisor: Prof. Dr. Sachin S. Sapatnekar

Posser, Gracieli

Electromigration Aware Cell Design / Gracieli Posser. – Porto Alegre: PPGC da UFRGS, 2015.

117 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2015. Advisor: Prof. Dr. Ricardo Augusto da Luz Reis; Co-advisor: Prof. Dr. Sachin S. Sapatnekar.

1. Electromigration. 2. Circuit Lifetime. 3. Cell-level. 4. AC EM. 5. Physical Design. 6. Microelectronics. I. Reis, Prof. Dr. Ricardo Augusto da Luz. II. Sapatnekar, Prof. Dr. Sachin S.. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb Coordenador do PPGC: Prof. Luigi Carro Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"The love you take is the love you make." The Beatles (Lennon-McCartney)

### ACKNOWLEDGMENTS

Agradeço primeiramente a DEUS, por me acompanhar sempre e em todo lugar. Aos meu PAIS que sempre me apoiaram e me deram a maior riqueza que alguém pode ter: amor e educação. A toda minha FAMÍLIA que sempre torceu por mim, em especial ao meu esposo Eduardo, que sempre me ajudou em tudo, compreendendo a necessidade de dedicar um tempo a mais para os estudos.

Agradeço de coração aos COLEGAS Tania, Cristina, Anelise, Guilherme, Jorge, Felipe, Calebe, Lucas, Adriel, Jucemar, Jozeanne, Daniel, Glauco, Walter, Gerson, Tiago, Jimmy, Alexandra, Julia, Vivek, Deepashree e demais, que sempre foram companheiros e amigos, não medindo esforços para ajudar ou compartilhar as dúvidas, ideias e estudos.

Ao meu orientador Ricardo Reis e ao co-orientador Sachin Sapatnekar por todo o incentivo e apoio em todas as etapas do doutorado. Pelo apoio para fazer o doutorado sanduíche em Minnesota e com isso formarmos uma parceria muito produtiva. Aos AMI-GOS e FAMILIARES que sempre me deram força e compartilharam estes momentos comigo.

Agradeço também aos demais professores que fizeram parte da minha formação desde as séries iniciais até hoje, pela educação, instrução e apoio.

## CONTENTS

| LIST                                                                            | OF ABBREVIATIONS AND ACRONYMS                                                                                                                                                                                                  | 7                                                                                                          |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| LIST                                                                            | OF SYMBOLS                                                                                                                                                                                                                     | 8                                                                                                          |

| LIST                                                                            | OF FIGURES                                                                                                                                                                                                                     | 9                                                                                                          |

| LIST                                                                            | OF TABLES                                                                                                                                                                                                                      | 13                                                                                                         |

| ABST                                                                            | TRACT                                                                                                                                                                                                                          | 14                                                                                                         |

| RESL                                                                            | JMO                                                                                                                                                                                                                            | 15                                                                                                         |

| 1 IN<br>1.1<br>1.2<br>1.3<br>1.4                                                | NTRODUCTION         Electromigration (EM)         Electromigration in Future Technologies (LIENIG, 2013)         Motivation and Contributions         Thesis Organization                                                      | 16<br>17<br>18<br>20<br>24                                                                                 |

| 2 S <sup>°</sup><br>2.1                                                         | TATE OF THE ART          Mitigating the EM effects in Different IC Design Flow Stages                                                                                                                                          | 25<br>25                                                                                                   |

| 2.1.1                                                                           | Method of managing electro migration in logic designs and design struc-<br>ture thereof (BARWIN; BICKFORD, 2013)                                                                                                               | 27                                                                                                         |

| 2.1.2                                                                           | Electromigration and its impact on physical design in future technologies (LIENIG, 2013)                                                                                                                                       | 28                                                                                                         |

| <ul><li>2.1.3</li><li>2.1.4</li></ul>                                           | Smart Non-default Routing for Clock Power Reduction (KAHNG; KANG;LEE, 2013)On potential design impacts of electromigration awareness (KAHNG; NATH;POSING 2013)                                                                 |                                                                                                            |

| 2.2                                                                             | ROSING, 2013)          Mitigating the EM Effects in Different Types of Interconnections                                                                                                                                        | 30<br>32                                                                                                   |

| 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.3<br>2.4                         | TSVs       TSVs         Power Delivery Network       Clock Network         Vias       Cell-internal EM         Summary of Related Works       Conclusions                                                                      | <ul> <li>32</li> <li>33</li> <li>33</li> <li>35</li> <li>35</li> <li>38</li> <li>41</li> <li>41</li> </ul> |

| 3 M                                                                             | IODELING CELL-INTERNAL EM                                                                                                                                                                                                      | 43                                                                                                         |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.2.1</li> <li>3.3</li> <li>2.2.1</li> </ul> | Modeling Time-to-Failure Under EM         Joule Heating         Local hot spots from Joule Heating (LI et al., 2014)         Current Divergence         New electromigration validation: Via Node Vector Method (DA DK: LA IN: | 43<br>44<br>45<br>45                                                                                       |

| <ul><li>3.3.1</li><li>3.3.2</li></ul>                                           | New electromigration validation: Via Node Vector Method (PARK; JAIN;<br>KRISHNAN, 2010)                                                                                                                                        | 46<br>48                                                                                                   |

| 3.3.3<br><b>3.4</b>                                                                          | -                                             | pact of Blech Length on Cell-Internal Interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50<br>50                               |

|----------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <ul> <li>4 C</li> <li>4.1</li> <li>4.2</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.3</li> </ul> | Current F<br>Algebra fe<br>Algebra<br>Algebra | CALCULATION         Flows Using Graph Traversals         or Average/RMS Current Updates         for Computing Average Current         for Computing the RMS Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51<br>53<br>55<br>56<br>57<br>61       |

| 5 E                                                                                          | XPERIME                                       | NTAL SETUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                     |

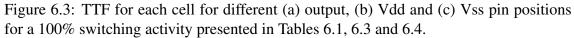

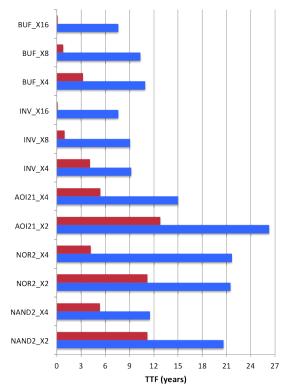

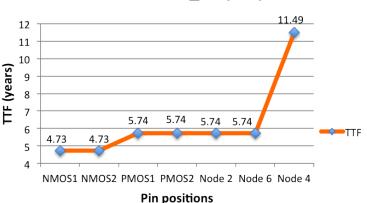

| 6 R<br>6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.2                                        | NAND2<br>AOI21_<br>NOR2_2<br>INV_X1           | romigration Effects for Different Logic Gates         2_X2 and NOR2_X2 gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66<br>79<br>80<br>82<br>84<br>86<br>88 |

|                                                                                              |                                               | G THE ELECTROMIGRATION EFFECTS ON DIFFERENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

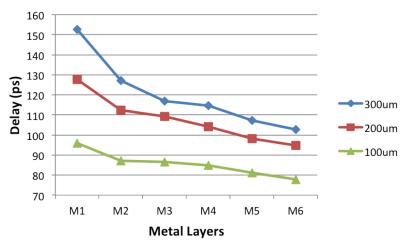

|                                                                                              | ENGTHS<br>Experime<br>Simulatio               | YERS AND DIFFERENT WIRE  Intal Setup In Results Intervention Intervent | 89<br>89<br>91<br>94                   |

| 8 C                                                                                          | ONCLUSI                                       | ON AND FUTURE WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95                                     |

| 8.1                                                                                          | •                                             | of Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95                                     |

| 8.2                                                                                          |                                               | orks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96                                     |

| <b>8.3</b> 8.3.1                                                                             |                                               | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 97<br>97                               |

| 8.3.2                                                                                        |                                               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

| 8.3.3                                                                                        |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98                                     |

| 8.3.4                                                                                        |                                               | ional Conferences, Symposiums and Workshops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98                                     |

| 8.3.5                                                                                        | Local C                                       | onferences, Symposiums and Workshops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99                                     |

| REFE                                                                                         | RENCES                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101                                    |

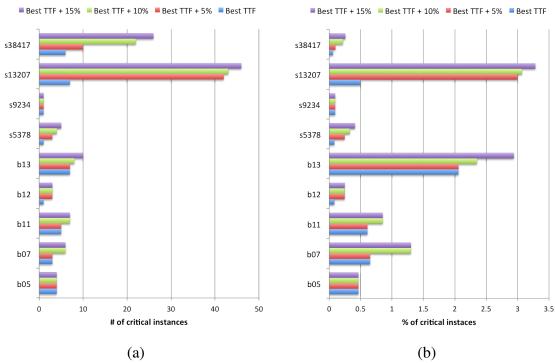

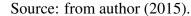

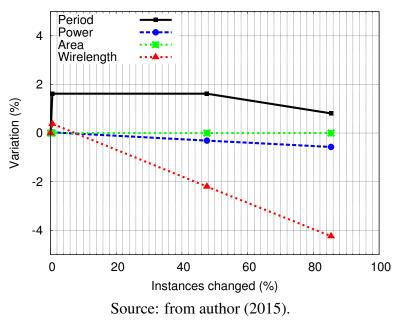

| APPE                                                                                         | NDIX A                                        | IMPACT ON PHYSICAL SYNTHESIS CON-SIDERING DIF-<br>FERENT AMOUNTS OF INSTANCES WITH EM AWARE-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                    |

|                                                                                              |                                               | NESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 108                                    |

| APPE                                                                                         | NDIX B                                        | COUPLING CAPACITANCE CURRENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 115                                    |

# LIST OF ABBREVIATIONS AND ACRONYMS

| AC    | Alternating Current                                           |

|-------|---------------------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit                       |

| AOI   | Complex logic gate composed by the AND, OR and inverter gates |

| CAD   | Computer-Aided Design                                         |

| CMOS  | Complementary Metal-Oxide Semiconductor                       |

| DC    | Direct Current                                                |

| FF    | Flip-Flop                                                     |

| GDS   | Graphic Data System                                           |

| GND   | Ground - Negative supply voltage                              |

| HDL   | Hardware Description Language                                 |

| IC    | Integrated Circuit                                            |

| INV   | inverter gate                                                 |

| J     | Current Density                                               |

| LEF   | Library Exchange Format                                       |

| MTTF  | Mean time to failure                                          |

| NAND  | Logic gate that represents the boolean function (A . B)       |

| NDR   | Non-Default Routing Rules                                     |

| NLDM  | Non-Linear Delay Models                                       |

| NMOS  | N-type metal-oxide-semiconductor                              |

| NOR   | Logic gate that represents the boolean function $(A + B)$     |

| RMS   | Root Mean Square                                              |

| RTL   | Register Transfer Level                                       |

| SDC   | Synopsys Design Constraints                                   |

| SPICE | Simulation Program with Integrated Circuit Emphasis           |

| TTF   | Time to Failure                                               |

| UFRGS | Universidade Federal do Rio Grande do Sul                     |

| VDD   | Positive supply voltage                                       |

# LIST OF SYMBOLS

- A Ampere

- a Atto

- F Farad

- f Femto

- $\mu$  Micro

- m Mili

- n Nano

- $\Omega$  Ohms

- p Pico

# **LIST OF FIGURES**

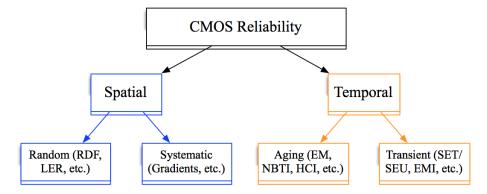

| Figure 1.1: | A CMOS circuit can fail from spatial or temporal unreliability effects.                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

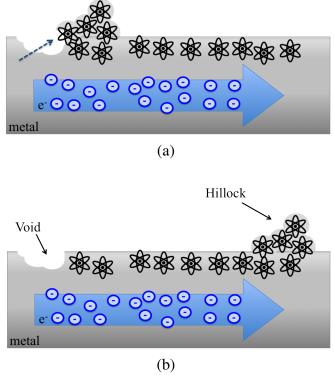

| Figure 1.2: | (a) The drift of metal atoms along with the flow of electrons (b) causing voids and hillocks.                                                                                                                                                                                                                                                                                                                                                              | 17 |

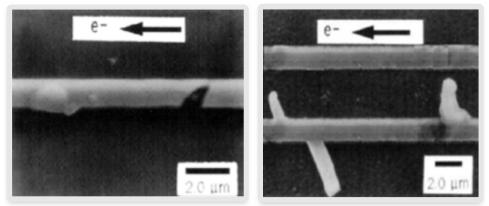

| Figure 1.3: | Void (open circuit) and hillock (short circuit).                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

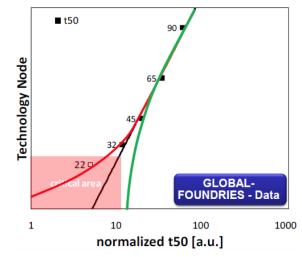

| Figure 1.4: | Evolution of lifetime versus technology node. Black line shows the effect of reduced critical void volume: Green line shows the EM enhancement urgently needed.                                                                                                                                                                                                                                                                                            | 19 |

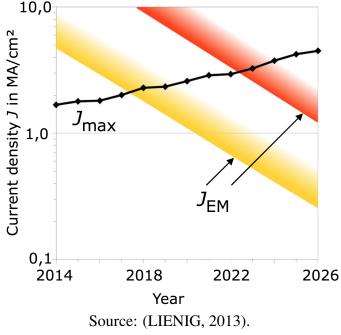

| Figure 1.5: | Expected development of current densities $(J_{max})$ needed for driving<br>four inverter gates, according to ITRS 2011 (see also Table 1.1). EM<br>degradation needs to be considered when crossing the yellow barrier<br>of current densities $(J_{EM})$ . As of now, manufacturable solutions are<br>not known in the red area.                                                                                                                         | 19 |

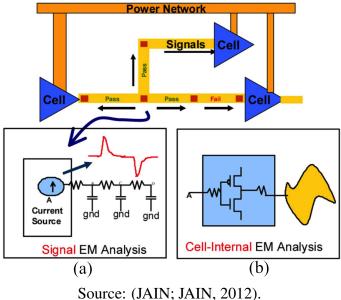

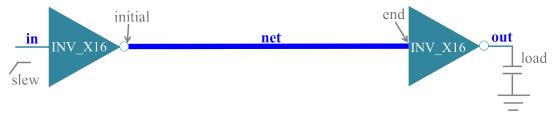

| Figure 1.6: | Problem space: (a) current source modeling for signal-EM analysis and (b) load abstraction for cell-internal EM analysis                                                                                                                                                                                                                                                                                                                                   | 20 |

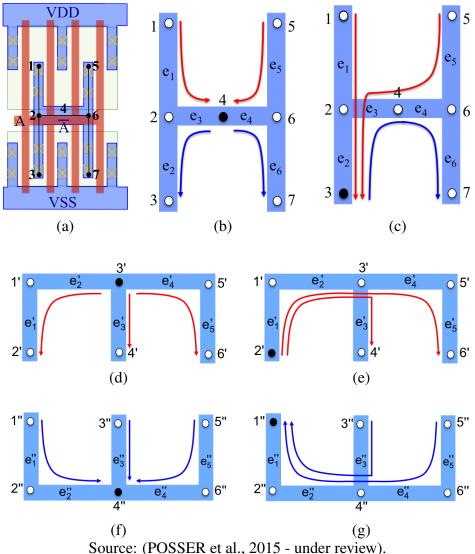

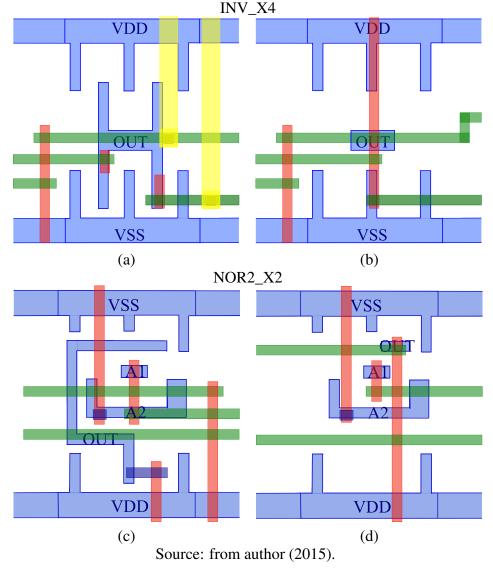

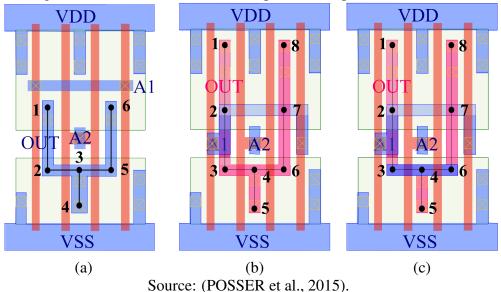

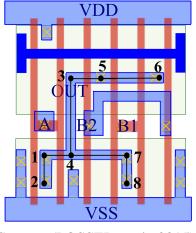

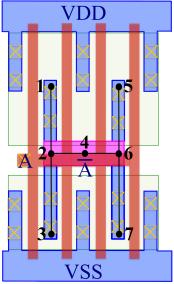

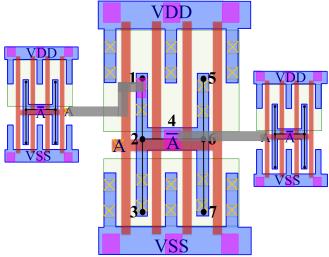

| Figure 1.7: | (a) The layout and output pin position options for INV_X4. Charge/dis-<br>charge currents when the output pin is at (b) node 4 and (c) node 3.<br>The red [blue] lines represent rise [fall] currents. (d) The Vdd pin<br>position options for INV_X4 and the currents when the Vdd pin is at<br>node 3' and (e) node 2'. (f) The Vss pin position options for INV_X4                                                                                      |    |

|             | and the currents when the Vss pin is at node $4''$ and (g) node $1''$                                                                                                                                                                                                                                                                                                                                                                                      | 22 |

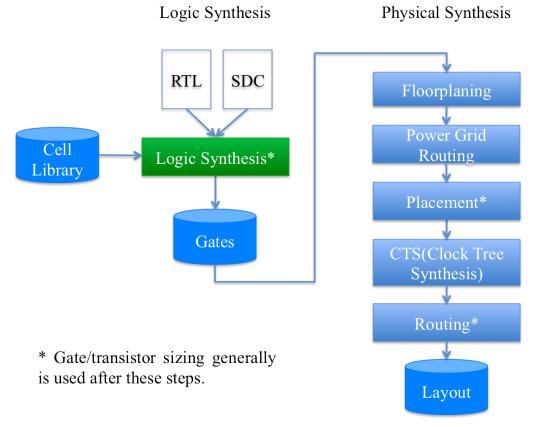

| Figure 2.1: | Standard-cell based synthesis flow                                                                                                                                                                                                                                                                                                                                                                                                                         | 26 |

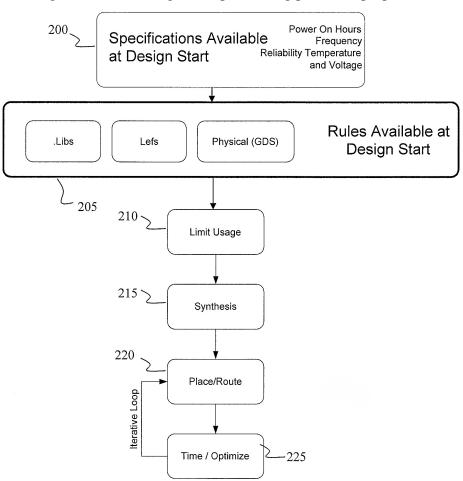

| Figure 2.2: | Flow diagram implementing processes proposed                                                                                                                                                                                                                                                                                                                                                                                                               | 27 |

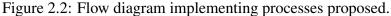

| Figure 2.3: | Synthesis-analysis loops in the design flow for digital circuits. The critical steps - physical synthesis (a) and analysis (b) - are shown, supplemented by options to address current density and other elec-                                                                                                                                                                                                                                             |    |

|             | tromigration issues (c)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29 |

| Figure 2.4: | Overall implementation flow                                                                                                                                                                                                                                                                                                                                                                                                                                | 30 |

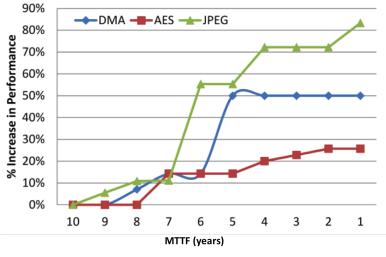

| Figure 2.5: | Percentage increase in $F_{max}$ at 45nm due to reduced MTTF requirement.                                                                                                                                                                                                                                                                                                                                                                                  | 30 |

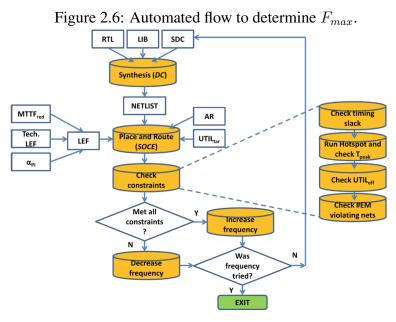

| Figure 2.6: | Automated flow to determine $F_{max}$                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

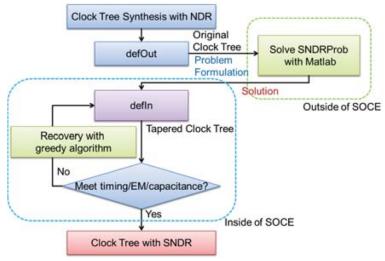

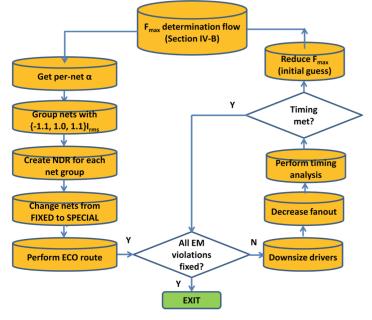

| Figure 2.7: | Per-net NDRs flow to fix EM $I_{rms}$ violations                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

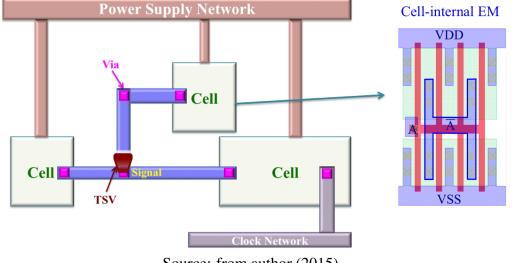

| Figure 2.8: | Different types of interconnections within the circuit where EM occurs.                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

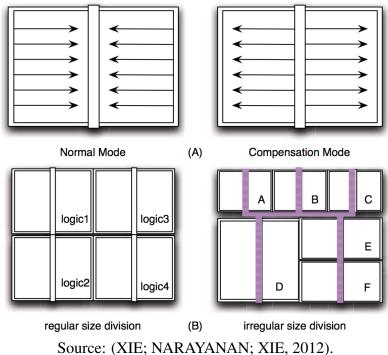

| Figure 2.9: | (A) A vertical Power/Ground (P/G) strip (compensation strip) is added<br>in the middle of the layout with two working modes (normal mode:<br>power is supplied to the block from the P/G ring with the compen-<br>sation strip in high-impedance state; compensation mode: the PAD<br>supplies the compensation strip, with the regular P/G ring in high-<br>impedance state); (B) chip layout divided into regular or irregular<br>sizes with power grid. | 34 |

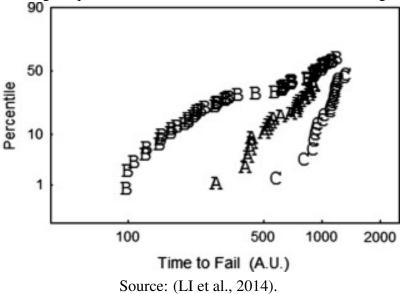

| Figure 2.10:               | EM performance variation with different via sizes. A - 2 regular square vias along line width; B - 1 rectangular bar via with 2x the cross sectional area of a regular square via; C - 1 larger square via                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

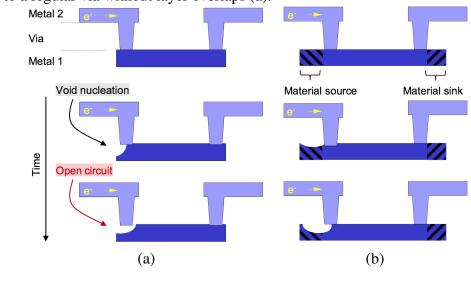

| Figure 2.11:               | with 4x the cross sectional area of a regular square via                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36 |

| -                          | compared to a regular via without layer overlaps (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37 |

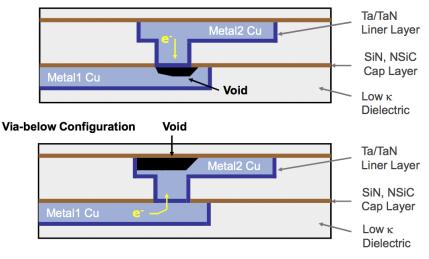

| Figure 2.12:               | Via-above and via-below configurations with their different damage<br>locations partly due to the interface/surface diffusion prevalent in<br>copper wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

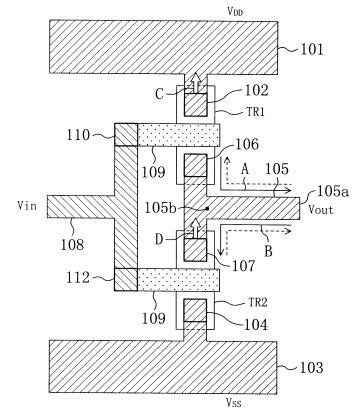

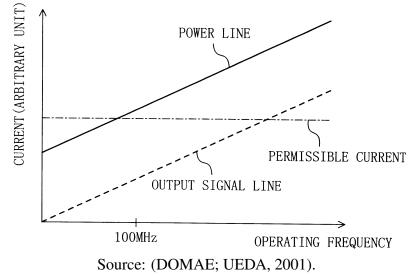

| Figure 2.13:               | copper wires.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       < | 39 |

|                            | The relationships between the operating frequency of a CMOS in-<br>verter and the amount of current flowing through a power line and<br>between the operating frequency and the amount of current flowing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                            | through an output signal line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

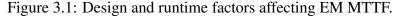

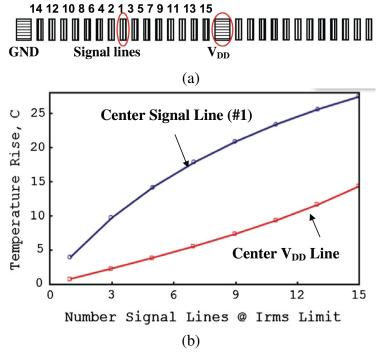

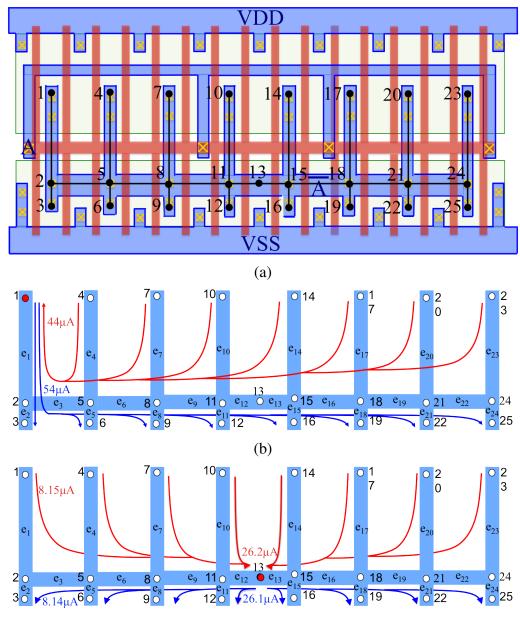

| Figure 3.1:<br>Figure 3.2: | Design and runtime factors affecting EM MTTF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

|                            | closest neighbors of the subject line (#1 signal line or the center (cir-<br>cled) VDD line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46 |

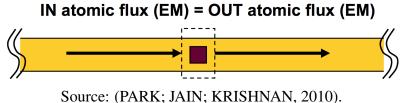

| Figure 3.3:                | As the 'IN' and 'OUT' atomic flux are the same, the atomic flux divergence along the interconnect is zero, resulting in no EM damage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47 |

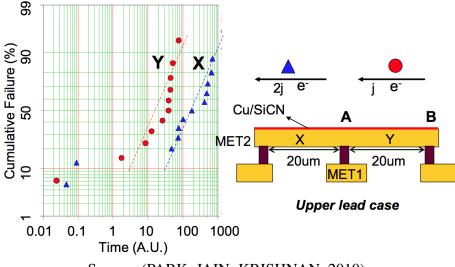

| Figure 3.4:                | Lead Y flows at half the current density of lead X, but fails faster than lead X; contrary to the conventional EM expectation. The new via node vector method explains it well with the divergence effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47 |

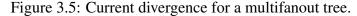

| Figure 3.5:                | Current divergence for a multifanout tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48 |

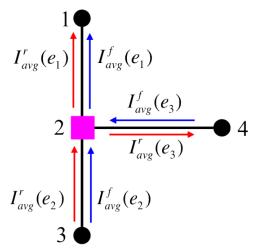

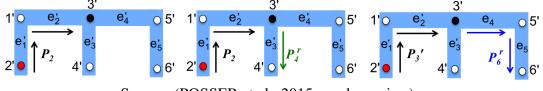

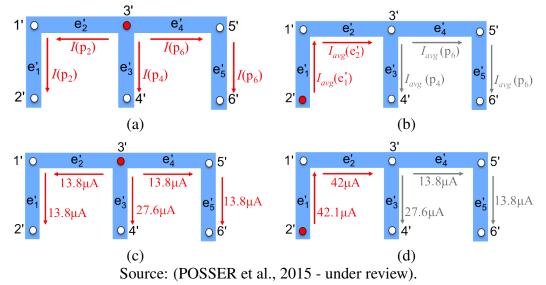

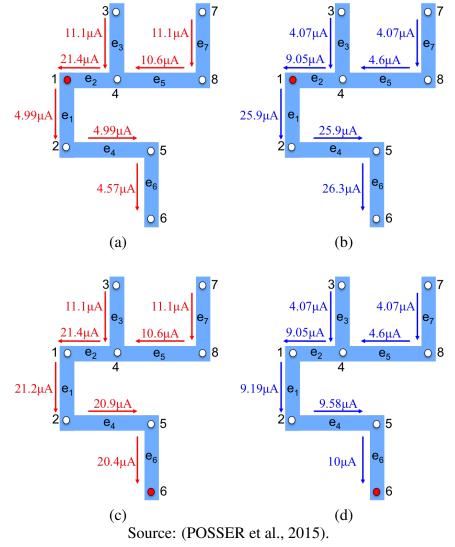

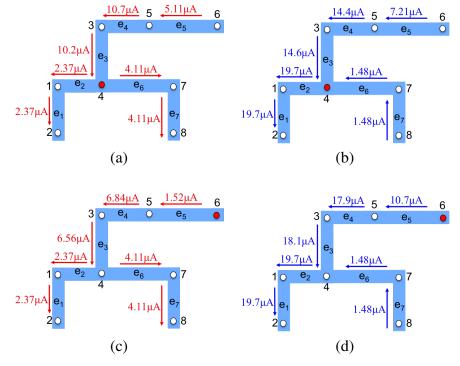

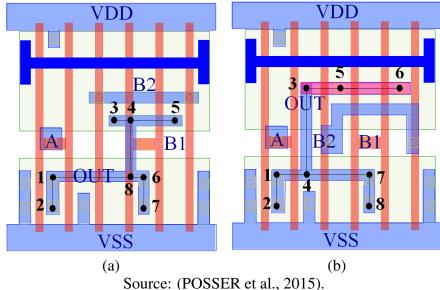

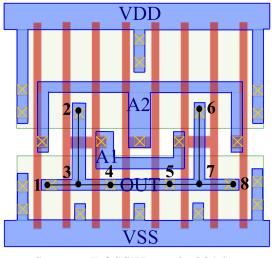

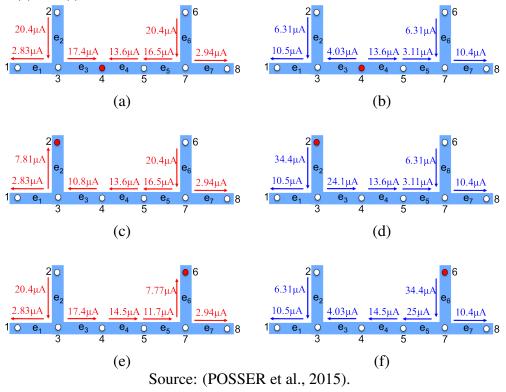

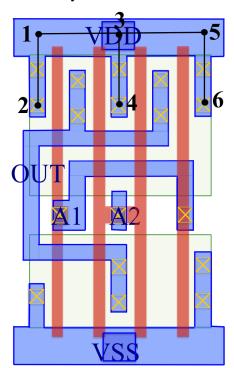

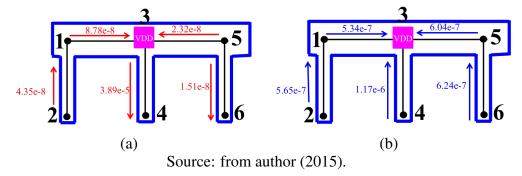

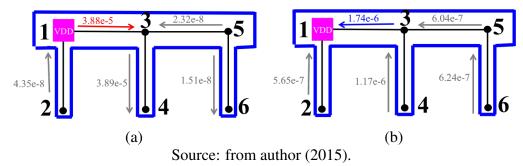

| Figure 4.1:                | (a) The layout and output pin position options for INV_X4. Charge/discharge currents when the output pin is at (b) node 4 and (c) node 3. The red [blue] lines represent rise [fall] currents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52 |

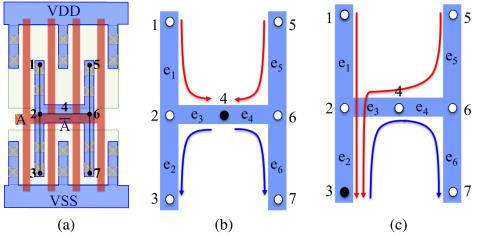

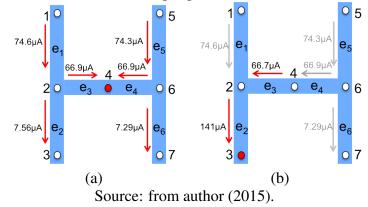

| Figure 4.2:                | <ul><li>(a) AVG current values in Ampere (A) for the rise transition from SPICE simulation for the INV_X4 when the output pin is at node 4,</li><li>(b) node 2 and (c) node 6.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52 |

| Figure 4.3:                | (a) AVG current values in Ampere (A) for the rise transition from SPICE simulation for the INV_X4 when the output pin is at node 4 and (b) node 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53 |

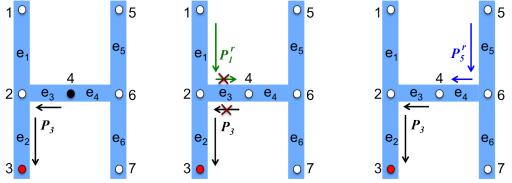

| Figure 4.4:                | Recomputation of the rise currents when the pin is moved from ref-<br>erence node 4 to node 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55 |

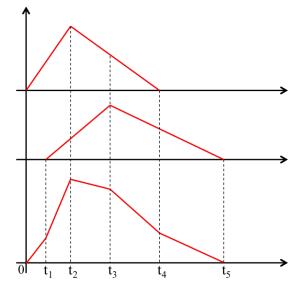

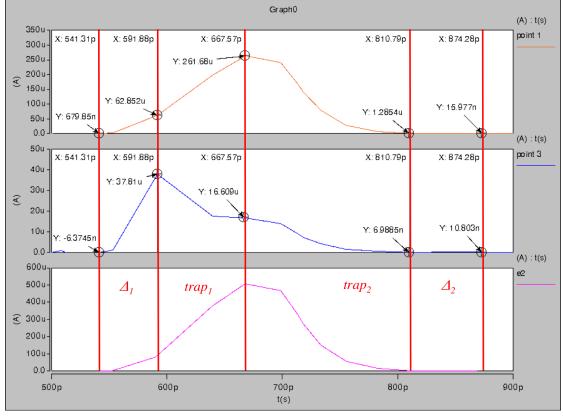

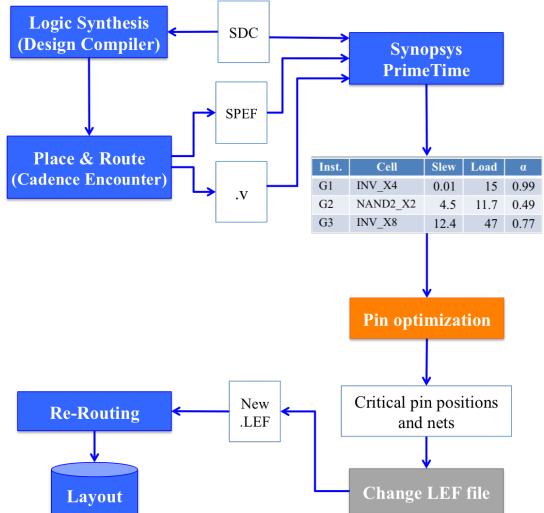

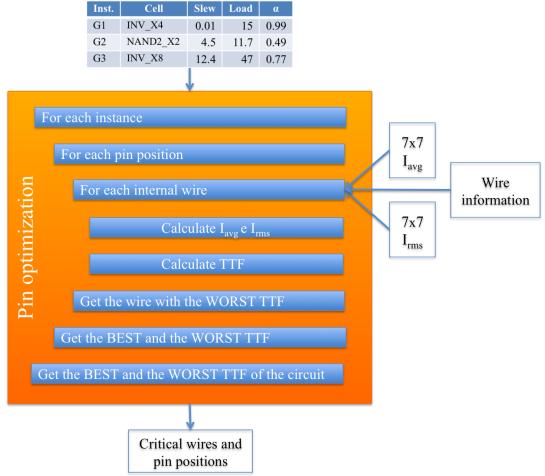

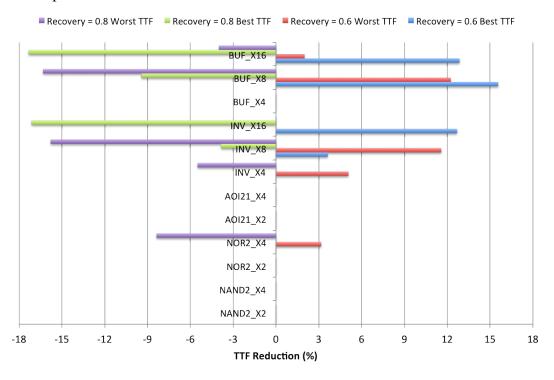

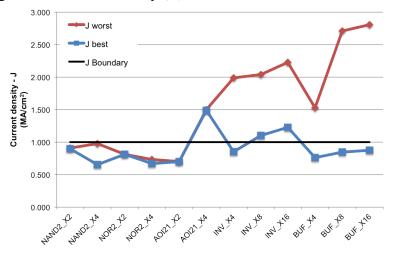

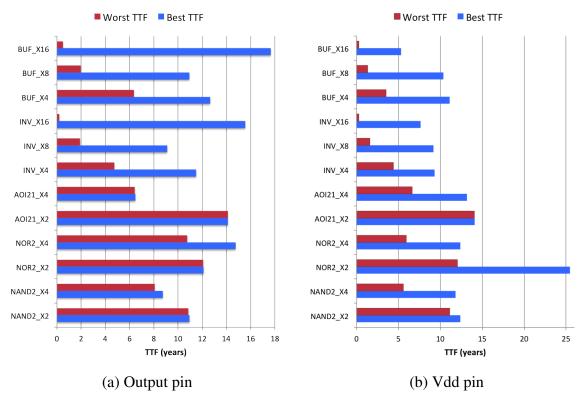

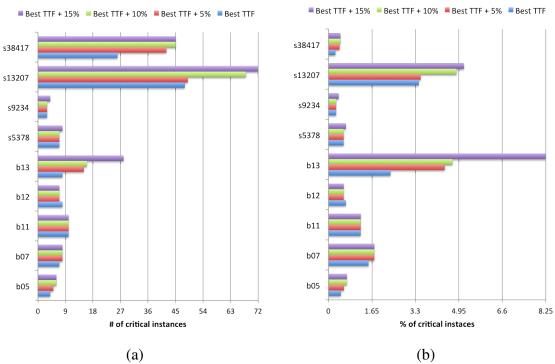

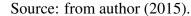

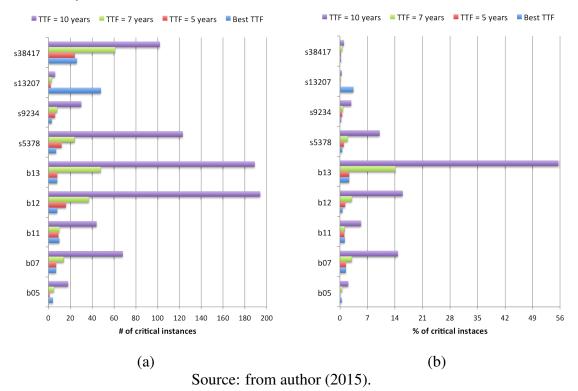

| Figure 4.5:                | Our graph based algorithm applied to the Vdd pin when the pin is moved from node 3' to node 2'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55 |