# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### RONALDO RODRIGUES FERREIRA

## The Transactional HW/SW Stack for Fault Tolerant Embedded Computing

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Dr. Luigi Carro Advisor

Prof. Dr. Álvaro Freitas Moreira Co-advisor

#### CIP - CATALOGING-IN-PUBLICATION

Ferreira, Ronaldo Rodrigues

The Transactional HW/SW Stack for Fault Tolerant Embedded Computing / Ronaldo Rodrigues Ferreira. – Porto Alegre: PPGC da UFRGS, 2015.

129 p.: il.

Thesis (Ph.D.) — Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2015. Advisor: Luigi Carro; Coadvisor: Álvaro Freitas Moreira.

1. Compiler Design, Coverage, Error Detection, Error Recovery, Fault Injection, Hardening By Design, Latency, LLVM, Modular Redundancy, Register File, Rollback, Single Event Effects, Soft Error. I. Carro, Luigi. II. Moreira, Álvaro Freitas. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ABSTRACT**

Fault tolerance implementation in embedded systems is challenging because the physical constraints of area occupation, power dissipation, and energy consumption of these systems. The need for optimizing these three physical constraints while doing computation within the available performance goals and real-time deadlines creates a conundrum that is hard to solve. Classical fault tolerance solutions such as triple and dual modular redundancy are not feasible due to their high power overhead or lack of efficient and deterministic error recovery. Existing techniques, although some of them reduce the power and area overhead, incur heavy performance penalties and most of the time do not assume a feasible fault model. This dissertation introduces the Transactional HW/SW Stack, or simply Stack, to efficiently manage the area, power, fault coverage, and performance conundrum. The Stack introduces a new compilation strategy that assembles programs into Transactional Basic Blocks, together with a novel microprocessor, the TransactiOnal Basic Block Architecture (ToBBA), which provides fine-grained error detection and deterministic error rollback and elimination using the Transactional Basic Blocks (TBBs) both as a container for errors and as a small unit of data checkpointing. Two solutions to sustain the TBB semantics in hardware are introduced: software- and hardware-based. Stack's area, power, performance, and coverage were evaluated using ToBBA's hardware implementation model. The Stack attains an error correction coverage of 99.35% with 2.05 power overhead within an area overhead of 2.65. The Stack also presents a performance overhead of 1.33 or 1.54, depending on the hardware model adopted to support the TBB.

**Keywords:** Compiler Design, Coverage, Error Detection, Error Recovery, Fault Injection, Hardening By Design, Latency, LLVM, Modular Redundancy, Register File, Rollback, Single Event Effects, Soft Error.

## Pilha HW/SW Transacional para Computação Embarcada Tolerante a Falhas

#### **RESUMO**

O desafio de implementar tolerância a falhas em sistemas embarcados advém das restrições físicas de ocupação de área, dissipação de potência e consumo de energia desses sistemas. A necessidade de otimizar essas três restrições de projeto concomitante à computação dentro dos requisitos de desempenho e de tempo-real cria um problema difícil de ser resolvido. Soluções clássicas de tolerância a falhas tais como redundância modular dupla e tripla não são factíveis devido ao alto custo em potência e a falta de um mecanismo para se recuperar erros. Apesar de algumas técnicas existentes reduzirem o overhead de potência e área, essas incorrem em alta degradação de desempenho e muitas vezes assumem um modelo de falhas que não é factível. Essa tese introduz a Pilha de HW/SW Transacional, ou simplesmente Pilha, para gerenciar de maneira eficiente as restrições de área, potência, cobertura de falhas e desempenho. A Pilha introduz uma nova estratégia de compilação que organiza os programas em Blocos Básicos Transacionais (BBT), juntamente com um novo processador, a Arquitetura de Blocos Básicos Transacionais (ABBT), a qual provê detecção e recuperação de erros de grão fino e determinística ao usar o BBT como um contâiner de erros e como unidade de checkpointing. Duas soluções para prover a semântica de execução do BBT em hardware são propostas, uma baseada em software e a outra em hardware. A área, potência, desempenho e cobertura de falhas foram avaliadas através do modelo de hardware do ABBT. A Pilha provê uma cobertura de falhas de 99,35%, com overhead de 2,05 em potência e 2,65 de área. A Pilha apresenta overhead de desempenho de 1,33 e 1,54, dependento do modelo de hardware usado para suportar a semântica de execução do BBT.

**Palavras-chave:** Compiladores, Cobertura, Detecção de Erros, Injeção de Falhas, Latência, LLVM, Redundância Modular, Banco de Registradores, Soft Error..

## LIST OF FIGURES

| 1.1 | hardened microprocessors (white triangles) along decades                                                                                                                                                                                                                     | 20 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Overhead of checkpointing an application when the number of executed instructions increase                                                                                                                                                                                   | 21 |

| 2.1 | Segments of the Transactional Basic Block                                                                                                                                                                                                                                    | 32 |

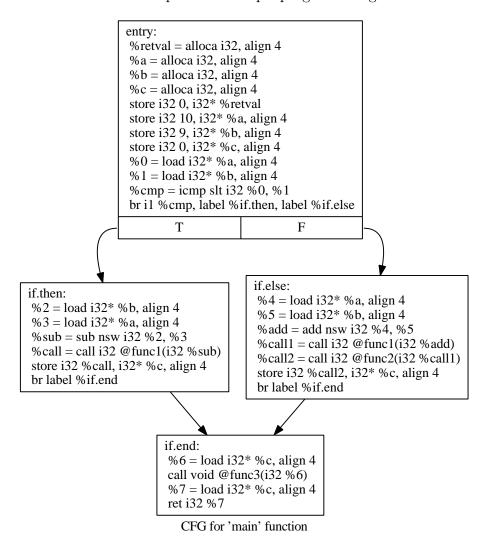

| 2.2 | Control-Flow Graph of the sample program using standard Basic Blocks                                                                                                                                                                                                         | 42 |

| 2.3 | Control-Flow Graph of the BB's performing function calls after Algorithm 2.2 is executed in the original 'if.else' BB shown in Figure 2.2                                                                                                                                    | 42 |

| 2.4 | Control-Flow Graph of the sample program using TBB's                                                                                                                                                                                                                         | 43 |

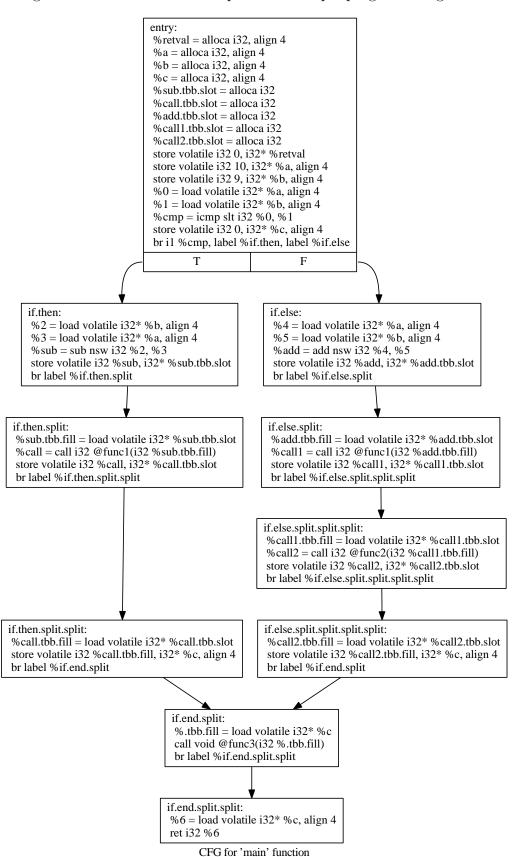

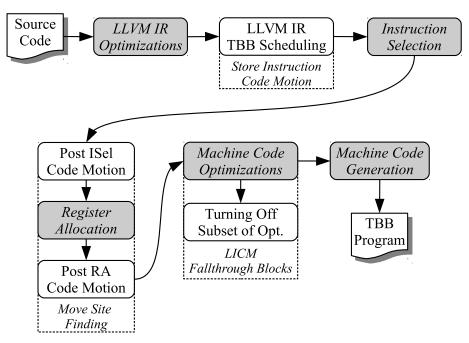

| 2.5 | Algorithm for generating TBB programs in LLVM. Gray shapes represent standard LLVM's steps                                                                                                                                                                                   | 46 |

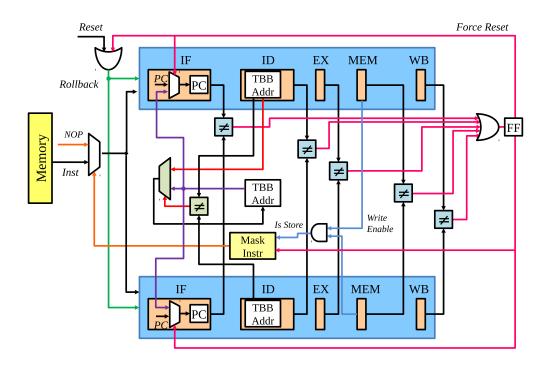

| 3.1 | Block diagram of the ToBBA architecture                                                                                                                                                                                                                                      | 50 |

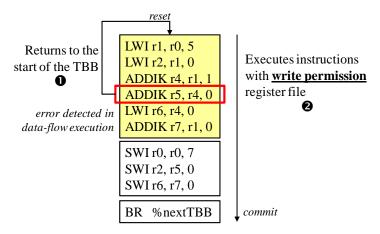

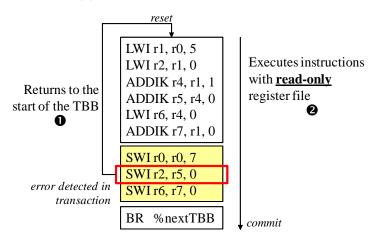

| 3.2 | Transactional basic-block error scenario                                                                                                                                                                                                                                     | 52 |

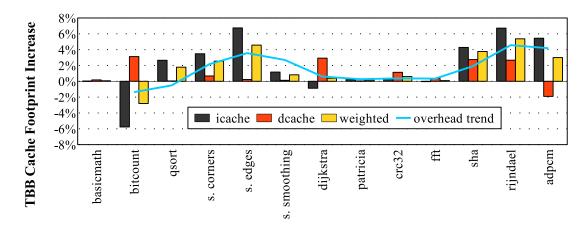

| 4.1 | Cache footprint increase for both the data cache (dcache) and the instruction cache (icache). Negative values are footprint reduction. Overhead trend line corresponds to the TBB cache footprint increase weighted by icache and dcache sizes (32KB and 64KB, respectively) | 62 |

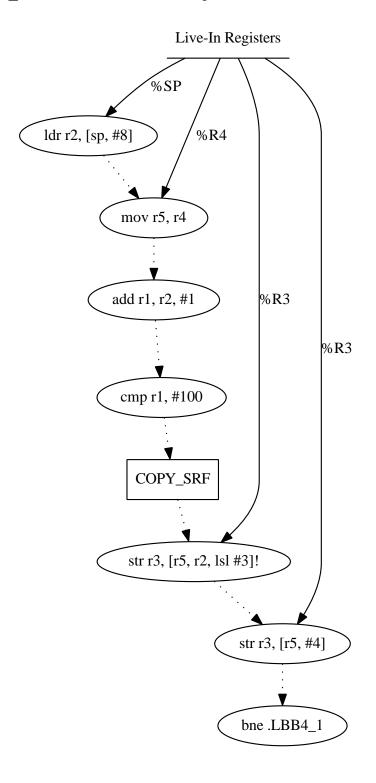

| 4.2 | TBB sample from 'dijkstra', showing the live-in registers of the block, and the COPY_SRF instruction. This sample uses ARM instructions                                                                                                                                      | 64 |

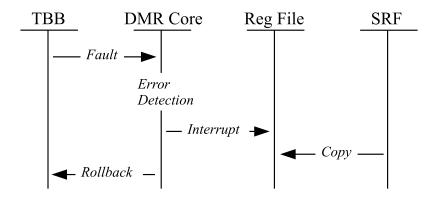

| 4.3 | Flow from fault occurrence to error correction depicting ToBBA with its Working Register File (Reg File) and the SRF                                                                                                                                                         | 65 |

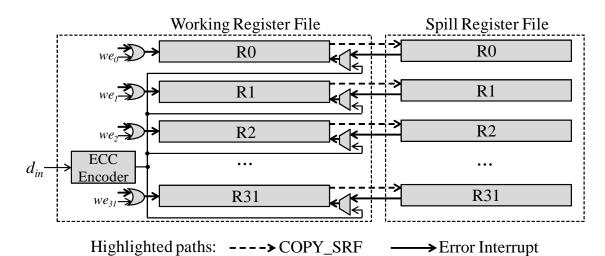

| 4.4 | SRF hardware and its data path. $d_{in}$ represents the data available in the write port, and $we_0 \dots we_{31}$ are the write enable signals                                                                                                                              | 66 |

| 4.5 | Algorithm for generating TBB programs in LLVM for the Spill Register File. Gray shapes represent standard LLVM's steps                                                                                                                                                       | 67 |

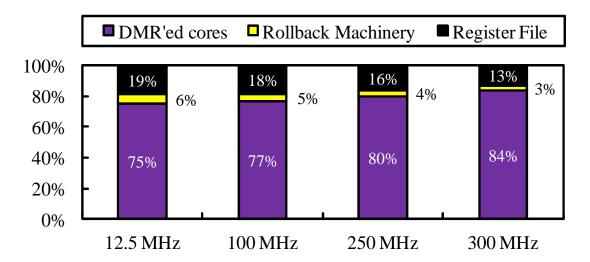

| 5.1 | ToBBA's relative area occupation of each architectural unit                                                                                                                                                                                                                  | 73 |

|     |                                                                                                                                                                                                                                                                              |    |

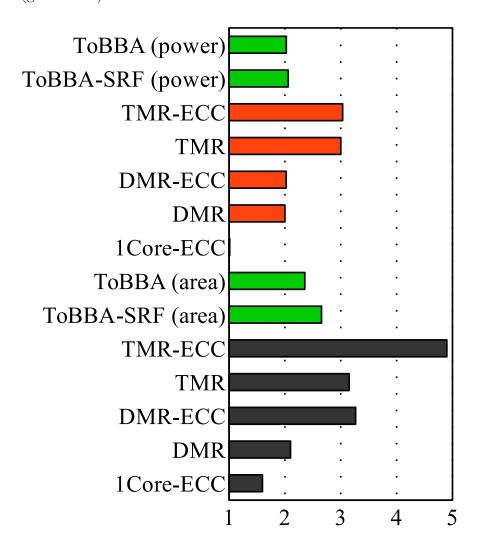

| 5.2 | Area occupation (gray bars) and peak power dissipation (orange     |    |

|-----|--------------------------------------------------------------------|----|

|     | bars) overhead wrt. unhardened single core with one register file  |    |

|     | (baseline). The chart shows data using unhardened and ECC          |    |

|     | protected register files for five configurations: single-core with |    |

|     | ECC (1Core-ECC), DMR and TMR without ECC (DMR, TMR),               |    |

|     | DMR and TMR with ECC (DMR-ECC, TMR-ECC), and ToBBA                 |    |

|     | (0)                                                                | 74 |

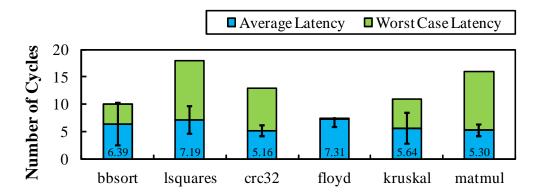

| 5.3 | Worst case and average error recovery latency with standard de-    |    |

|     | viation in number of executed cycles to rollback after an error is |    |

|     |                                                                    | 76 |

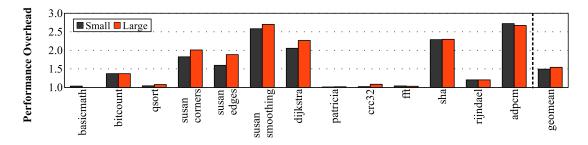

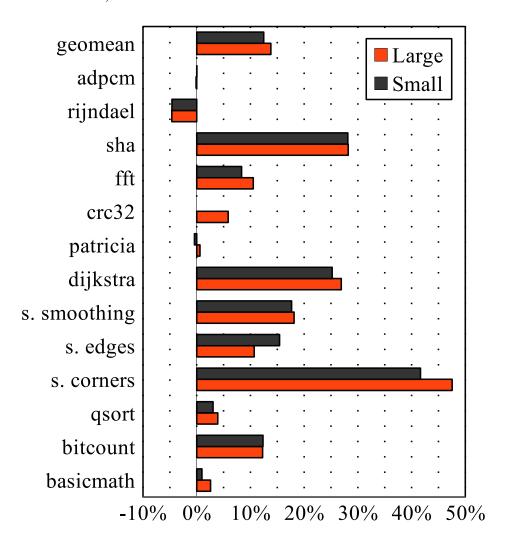

| 5.4 | ToBBA's performance overhead without the Spill Register File.      |    |

|     | These results were obtained for the MiBench subset using the       |    |

|     | small and large data sets to show how the TBB scales. The          |    |

|     | measured geometric mean for large data set ('geomean' in the       |    |

|     |                                                                    | 76 |

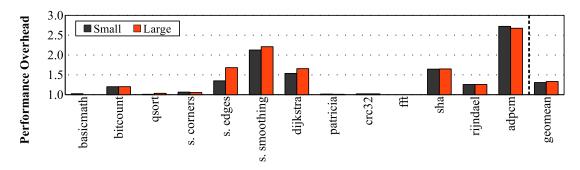

| 5.5 | Performance overhead of ToBBA-SRF's TBB programs using the         |    |

|     | Spill Register File instead of additional spill instructions. The  |    |

|     | measured geometric mean for large data set ('geomean' in the       |    |

|     | ,                                                                  | 77 |

| 5.6 | ToBBA-SRF performance improvement over TBB implemented             |    |

|     | with additional spill instructions. The measured geometric mean    |    |

|     | 9 (9                                                               | 78 |

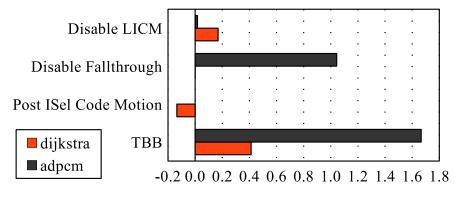

| 5.7 | Cumulative performance overhead off all modifications in the orig- |    |

|     | 1 0                                                                | 78 |

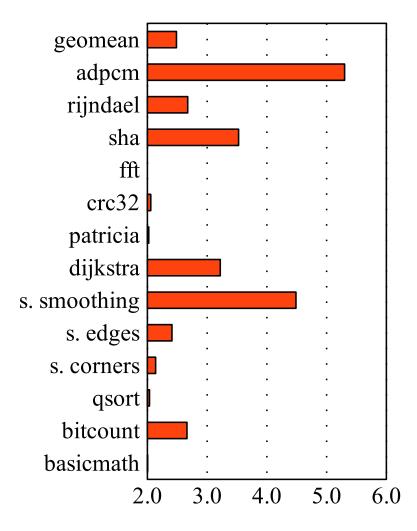

| 5.8 | TBB's energy overhead. There results overestimate the SRF us-      |    |

|     | age, because it counts twice the Working Register File energy      |    |

|     | consumption. The SRF would consume much less energy than           |    |

|     | the WRF due to less frequent access to it                          | 80 |

## LIST OF TABLES

| 3.1 | Corner cases of the rollback machinery depending on the in-flight |  |  |  |

|-----|-------------------------------------------------------------------|--|--|--|

|     | instructions in the pipeline                                      |  |  |  |

| 5.1 | Benchmark used to evaluate the Stack for error coverage 70        |  |  |  |

| 5.2 | gem5 simulation configuration                                     |  |  |  |

| 5.3 | ToBBA's fault injection results                                   |  |  |  |

| 5.4 | Stuck-at outcome for each rollback internal signal 82             |  |  |  |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ABFT Algorithm Based Fault Tolerance

ACCE Automatic Correction of Control flow Errors

ASIC Application-Specific Integrated Circuit

AVF Architectural Vulnerability Factor

BB Basic Block

DFE Data Flow Error

DMR Dual Modular Redundancy

CCA Control flow Checking Approach

CEDA Control flow Error Detection through Assertions

CFCSS Control Flow Checking by Software Signatures

CFE Control Flow Error

CFG Control Flow Graph

COTS Commercial Off-The-Shelf

ECC Error Correcting Code

ECCA Enhanced CCA

FPGA Field-Programmable Gate Array

GCC GNU C Compiler

GPU Graphics Processing Unit

HETA Hybrid Error detection Technique using Assertions

HW Hardware

ILP Instruction Level Parallelism

IR Intermediate Representation

ISel Instruction Selection

ISA Instruction Set Architecture

IVI Instruction Vulnerability Index

JIT Just In Time compilation

LDMR Lightweight Dual Modular Redundancy

LICM Loop Invariant Code Motion

LSQ Load/Store Queue MBU Multiple Bit Upset

OOO Out-of-Order

PC Program Counter

RA Register Allocation

RISC Reduced Instruction Set Computing

RMT Redundant Multi Threading

ROB Reorder Buffer

RTL Register Transfer Level

RVF Register Vulnerability Factor

SDC Silent Data Corruption

SEE Single Event Effect

SET Single Event Transient

SEU Single Event Upset

SIHFT Software-Implemented Hardware Fault Tolerance

SP Stack Pointer

SRF Spill Register File

SSA Static Single Assignment Form Stack Transactional HW/SW Stack

SW Software

SWAT SoftWare Anomaly Treatment

TBB Transactional Basic Block

TMR Triple Modular Redundancy

ToBBA TransactiOnal Basic Block Architecture

URISC Ultra Reduced Instruction Set Co-processor

WRF Working Register File

YACCA Yet Another CCA

## TABLE OF CONTENTS

| 1 1                                                                                  | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                             |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1.1                                                                                  | Computers In The Wild                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             |

| 1.2                                                                                  | $The \ Area/Coverage/Performance/Power \ Conundrum \ \dots \ \dots$                                                                                                                                                                                                                                                                                                                                         | 19                                                             |

| 1.3                                                                                  | Error Correction Design Space                                                                                                                                                                                                                                                                                                                                                                               | 23                                                             |

| 1.4                                                                                  | Rethinking The HW/SW Stack                                                                                                                                                                                                                                                                                                                                                                                  | 25                                                             |

| 1.5                                                                                  | Text Organization                                                                                                                                                                                                                                                                                                                                                                                           | 28                                                             |

| 2 T                                                                                  | RANSACTIONAL BASIC BLOCK                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                             |

| 2.1                                                                                  | Definition and Instruction Formation                                                                                                                                                                                                                                                                                                                                                                        | 31                                                             |

| 2.2                                                                                  | Transforming Programs into Transactions                                                                                                                                                                                                                                                                                                                                                                     | 33                                                             |

| 2.2.1                                                                                | Preliminaries and Definitions                                                                                                                                                                                                                                                                                                                                                                               | 33                                                             |

| 2.2.2                                                                                | Promoting Functions' Return Value Into Global Variable                                                                                                                                                                                                                                                                                                                                                      | 34                                                             |

| 2.2.3                                                                                | Splitting Basic Blocks Around Call Sites                                                                                                                                                                                                                                                                                                                                                                    | 35                                                             |

| 2.2.4                                                                                | Spilling Live-Out Values                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                             |

| 2.2.5                                                                                | TBB Generation Example and Further Discussion                                                                                                                                                                                                                                                                                                                                                               | 40                                                             |

| 2.3                                                                                  | Compilation Flow in the LLVM Framework                                                                                                                                                                                                                                                                                                                                                                      | 44                                                             |

| 2.4                                                                                  | Crosscutting the HW Layer                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                             |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                |

| 3 T                                                                                  | RANSACTIONAL CORE                                                                                                                                                                                                                                                                                                                                                                                           | 49                                                             |

| 3 T<br>3.1                                                                           | RANSACTIONAL CORE                                                                                                                                                                                                                                                                                                                                                                                           |                                                                |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                             |

| 3.1                                                                                  | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50                                                       |

| 3.1<br>3.2                                                                           | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50<br>53                                                 |

| 3.1<br>3.2<br>3.3                                                                    | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50<br>53<br>54                                           |

| 3.1<br>3.2<br>3.3<br>3.4                                                             | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50<br>53<br>54<br>56                                     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                      | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50<br>53<br>54<br>56<br>58                               |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                        | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50<br>53<br>54<br>56<br>58<br>59                         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                        | TransactiOnal Basic Block Architecture  Error Detection and Recovery  Register Liveness and Error Recovery Latency  Rollback Machinery Algorithm  ToBBA Fault Model  Current Limitations and How To Overcome Them  Crosscutting the SW Layer                                                                                                                                                                | 49<br>50<br>53<br>54<br>56<br>58<br>59                         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>4 S                                 | TransactiOnal Basic Block Architecture                                                                                                                                                                                                                                                                                                                                                                      | 49<br>50<br>53<br>54<br>56<br>58<br>59<br>61<br>61             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>4 S                                 | TransactiOnal Basic Block Architecture  Error Detection and Recovery  Register Liveness and Error Recovery Latency  Rollback Machinery Algorithm  ToBBA Fault Model  Current Limitations and How To Overcome Them  Crosscutting the SW Layer  PILL REGISTER FILE  Sources of Overhead in the TBB                                                                                                            | 49<br>50<br>53<br>54<br>56<br>58<br>59<br>61<br>61             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>4 S<br>4.1<br>4.1.1                 | TransactiOnal Basic Block Architecture  Error Detection and Recovery Register Liveness and Error Recovery Latency Rollback Machinery Algorithm ToBBA Fault Model Current Limitations and How To Overcome Them Crosscutting the SW Layer  PILL REGISTER FILE Sources of Overhead in the TBB Sensitiveness to Register Allocation                                                                             | 49<br>50<br>53<br>54<br>56<br>58<br>59<br>61<br>61             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>4.1<br>4.1.1<br>4.1.2               | TransactiOnal Basic Block Architecture  Error Detection and Recovery  Register Liveness and Error Recovery Latency  Rollback Machinery Algorithm  ToBBA Fault Model  Current Limitations and How To Overcome Them  Crosscutting the SW Layer  PILL REGISTER FILE  Sources of Overhead in the TBB  Sensitiveness to Register Allocation  Additional Committed Instructions                                   | 49<br>50<br>53<br>54<br>56<br>58<br>59<br>61<br>61<br>62       |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>4 S<br>4.1<br>4.1.1<br>4.1.2<br>4.2 | TransactiOnal Basic Block Architecture  Error Detection and Recovery  Register Liveness and Error Recovery Latency  Rollback Machinery Algorithm  ToBBA Fault Model  Current Limitations and How To Overcome Them  Crosscutting the SW Layer  PILL REGISTER FILE  Sources of Overhead in the TBB  Sensitiveness to Register Allocation  Additional Committed Instructions  The Spill Register File Hardware | 49<br>50<br>53<br>54<br>56<br>58<br>59<br>61<br>61<br>62<br>63 |

| 5 E   | EXPERIMENTAL EVALUATION                                                            | 69    |

|-------|------------------------------------------------------------------------------------|-------|

| 5.1   | Methodology                                                                        |       |

| 5.2   | Error Coverage                                                                     |       |

| 5.3   | Power & Area Characterization                                                      |       |

| 5.4   | Performance & Error Recovery Latency Analysis                                      | . 75  |

| 5.4.1 | Error Recovery Latency                                                             |       |

| 5.5   | Performance Overhead Without the Spill Register File                               |       |

| 5.6   | Performance Overhead With the Spill Register File                                  |       |

| 5.7   | Energy Consumption                                                                 |       |

| 5.8   | Stuck-At Outcome in ToBBA's Rollback Machinery                                     |       |

| 6 R   | RELATED WORK                                                                       |       |

| 6.1   | Literature Organization                                                            |       |

| 6.2   | Software-Based Techniques                                                          | . 85  |

| 6.2.1 | Control-Flow Error Detection                                                       |       |

| 6.2.2 | Data-Flow Error Correction                                                         | . 87  |

| 6.2.3 | Redundant Multi-Threading                                                          | . 89  |

| 6.2.4 | Compiler-Guided and Program Transformation Reliability                             | . 90  |

| 6.2.5 | Comparison with the Stack                                                          | . 92  |

| 6.3   | Hardware-Based Techniques                                                          | . 93  |

| 6.3.1 | Control-Flow Monitoring                                                            | . 93  |

| 6.3.2 | Checkpointing                                                                      |       |

| 6.3.3 | Instruction Replay                                                                 |       |

| 6.3.4 | Pipelining                                                                         | . 97  |

| 6.3.5 | Comparison with the Stack                                                          | . 98  |

| 6.4   | Hybrid HW/SW Techniques                                                            | . 100 |

| 6.4.1 | Comparison with the Stack                                                          | . 101 |

| 7 F   | INAL REMARKS AND FUTURE WORK                                                       | 103   |

| 7.1   | Summing Up the Transactional Stack and Contributions                               |       |

| 7.1.1 | Compilation Strategy for Error Correction without Checkpointing .                  |       |

| 7.1.2 | Reduction of Rollback Data to the Bare Minimum                                     | . 104 |

| 7.1.3 | Error Correction Without Duplicating the Register File                             |       |

| 7.1.4 | Spill Register File as Auxiliary Container of Rollback Data                        | . 105 |

| 7.1.5 | Implementation of the TBB Generation in a Production Compiler .                    | . 105 |

| 7.1.6 | Comprehensive Evaluation of the Full HW/SW Stack Using an Adequate Fault Model     | 105   |

| 7.9   | •                                                                                  |       |

| 7.2   | Future Works                                                                       | . 100 |

| 7.2.1 | Implementing the Checking Mechanism in the Commit Stage for Out-Of-Order Execution | . 106 |

| 7.2.2 | Supporting Permanent Fault Mitigation Through Selective DMR Ac-                    | 105   |

| 700   | tivation                                                                           |       |

| 7.2.3 | Fault Tolerant Multicore Architecture                                              |       |

| 7.2.4 | Developing and Orchestrating Compiler Optimizations                                |       |

| 7.2.5 | Performing the Radiation Test Using an FPGA                                        |       |

| 7.3   | List of Publications                                                               |       |

| 7.3.1 | Currently Under Review                                                             |       |

| 7.3.2 | Conferences                                                                        | . 109 |

| 7.3.3          | Book Chapters                                                   |

|----------------|-----------------------------------------------------------------|

| 7.3.4          | Journals                                                        |

| 7.3.5          | Workshops                                                       |

| REFE           | RENCES                                                          |

| APPE           | ENDIX A RESUMO EM PORTUGUÊS                                     |

|                | Introdução                                                      |

|                | Metodologia                                                     |

| $\mathbf{A.3}$ | Resumo dos Resultados Experimentais                             |

| A.3.1          | Cobertura de Falhas                                             |

| A.3.2          | Caracterização de Área e Potência                               |

| A.3.3          | Análise de Desempenho e de Latência de Recuperação de Erros 126 |

| A.3.4          | Consumo de Energia                                              |

| A.3.5          | Comportamento do Circuito de Recuperação sob Stuck-At 129       |

|                |                                                                 |

#### 1 INTRODUCTION

#### 1.1 Computers In The Wild

Computers fail. They always did, and always will do. But we still depend on them. Deal with it.

Computing systems are exposed to a myriad of threats during their life cycle. Design errors, intentional attacks from external sources, harsh operating environment, just to name a few. But still, users of these computing systems expect them to operate correctly with acceptable performance, and without exposing sensitive data or incurring any critical threat to them. *Dependability*, i.e., the delivery of service that it is possible to justify the trust put on it (AVIZIENIS ET AL., 2004), walks hand in hand with the design, production, and delivery of any computing system. But still, computers fail.

Embedded systems are a particular case of computing systems operating under tight physical and performance requirements such as low power dissipation, low energy consumption due to limited power source, area constraints, or even real-time requirements (MARWEDEL, 2011). Due to the connection between embedded computers and the environment they are deployed onto, natural faults become an important source of service failure. Natural faults are caused by the interaction between the computing system with natural phenomena, without any human intervention to produce the fault (AVIZIENIS ET AL., 2004).

Due to the aggressive transistor scaling industry is going forward, with predictions saying transistor size will be as low as 5.9 nm by 2026 (ITRS, 2012), two natural phenomena became of utter importance for the dependability of computing systems, especially the embedded ones deployed in harsh environments: accelerated

aging and soft errors (HAMDIOUI ET AL., 2013).

Aging is a natural phenomena occurring when the device is reaching the end of its intended life cycle, leading to wear out failures such as performance degradation with its associated timing faults, and breakdown in transistor gates (Keane and Kim, 2011). Scaling transistors in such a steep speed accelerates the aging effect, because even small upsets in voltage caused by natural aging can disrupt the transistor state, taking the system faster to wear out (Moore, 2009).

Soft errors are produced by intermittent (or transient) faults, and can hardly be reproduced during system operation due to their probabilistic nature (AVIZIENIS ET Al., 2004). Radiation induced soft errors are a common source of service failure in space and aeronautics applications, but transistor scaling increases the soft error rate in new technology generations (BAUMANN, 2005), making circuits vulnerable even at sea level. In this scenario, terrestrial systems such as automotive systems will be prone to radiation induced soft errors. Soft errors due to radiation effects can be traced down to Single Event Effects (SEE). SEE's occur when a highly energized particle hits the device, provoking current glitches. In bigger transistors, the most common SEE is the Single Event Upset (SEU), when that energized particle disrupts a memory element such as a flip-flop. However, smaller operational voltages in new transistor generations increase the susceptibility of Single Event Transients (SET) as well, when the energized particle hits logic (Petersen, 2011). Because more transistors occupy the same area, in new technology nodes there is also a higher probability of Multiple Bit Upsets (MBU), where several bits of data are flipped by the same single particle (REED ET AL., 1997).

New generations of embedded computing systems cannot circumvent the scenario of high error rate, making the deployment of fault tolerance mandatory. Fault tolerance implementation always requires some sort of redundancy to achieve high fault tolerance coverage (AVIZIENIS ET AL., 2004). However, redundancy does not come for free, and, as it is discussed in this dissertation, it creates a conundrum that cannot be easily solved by the system designer. Redundancy requires extra physical resources of power, area, and performance. A system designer can navigate in these optimization axes, but at some point s/he will either reduce physical overhead or compromise fault tolerance coverage.

Redundancy creates the following scenario and design trade-offs for power, area, coverage, and performance a system designer has to cope with:

- Power and Area: redundancy implies in extra components, either hardware or software ones. In fault tolerance, the usual approach is modular spatial redundancy, where distinct replicas of a hardware module have their output voted to do fault masking. The problem of this approach is that replicating hardware modules increases power dissipation (and area) by the same replication factor. Bottom line, although replication potentially increases coverage, replication makes power dissipation skyrocket;

- Performance: redundancy can also be applied in time either in hardware or software. If it is applied in software, an unit of execution (e.g., a thread) executes ahead of its replica, and at the end their results are voted. Clearly, as the delta of replication increases, the performance overhead also does. If the duplication is entirely in software, although peak power dissipation is not increased, energy consumption does because software executes for more cycles. In addition, error recovery mechanisms relying on time redundancy can jeopardize real-time behavior, a mandatory characteristic to be observed for most of embedded systems (HAMDIOUI ET AL., 2013);

- Coverage: the redundancy degree can be adjusted to frame power and performance overhead within acceptable margins. However, when redundancy degree decreases, potentially, the fault coverage also does. No need to mention that a system with inadequate fault tolerance coverage cannot be considerable dependable.

In the next two sections, these physical trade-offs are discussed in more details, and the solution this dissertation proposes is briefly introduced.

### 1.2 The Area/Coverage/Performance/Power Conundrum

The overhead in terms of power dissipation, area occupation and performance of the additional circuitry needed to harden an embedded processor for SEE is typically far from negligible. In hardened chips targeted to low power embedded

scenario.

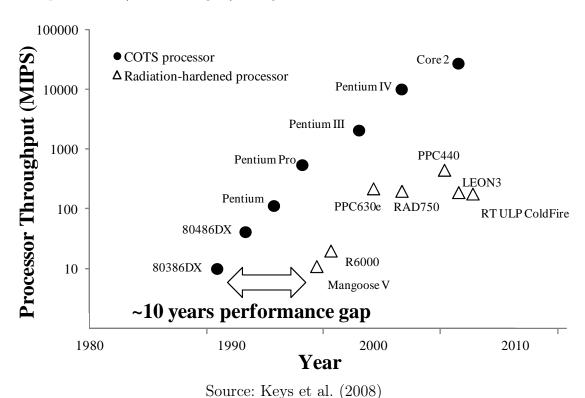

Figure 1.1 – Performance gap between COTS (black circles) and radiation hardened microprocessors (white triangles) along decades

systems, the limited power budget and energy source will steep these chips into 'dark silicon' faster than general purpose microprocessors. *Dark silicon* (ESMAEILZADEH ET AL., 2011) mandates that increasing the transistors count with the same power budget will stop giving performance and energy benefits due to the end of Dennard scaling (DENNARD ET AL., 1974). In radiation hardening, considerable area of the circuit is used to sustain reliable operation instead of performance, aggravating this

Engineers of application domains that cannot trade reliability for performance are having hard times with the low-performance offered by radiation tolerant architectures. Fig. 1.1 shows a comparison of commercial off-the-shelf (COTS) microprocessors against radiation hardened ones for performance (KEYS ET AL., 2008). Rad-hardened microprocessors have a performance gap of approximately 10 years to their COTS counterparts at the same generation. The gap is even bigger in terms of unitary price: a 25 MHz radiation hardened RAD6000 microprocessor costs U\$ 200,000 (PENIX AND MEHLITZ, 2005), while an Intel i7 costs U\$ 300. NASA launched a call for projects to design the next generation of rad-hardened

Fault Detection Overhead - Recovery Overhead - Total Overhead 70% Performance overhead 60% 50% 40% 30% 20% 10% 0%<u>-</u> 200 900 2000 9000 20000 30000 50000 No. of checkpointed instructions

Figure 1.2 – Overhead of checkpointing an application when the number of executed instructions increase

Source: Chen and Yang (2013)

space microprocessors constructed only with COTS parts (NASA, 2013), with the main requirements being: i) high-performance and multicore parallel architecture; ii) adaptability in power consumption; iii) radiation hardened; and iv) programmability in C and compatibility with standard development and debug tools.

Due to their simplicity and generality, the usual solution for radiation hardening in circuits are the triple and dual modular redundancies (TMR and DMR, respectively) (BERNICK ET AL., 2005; MORGAN ET AL., 2007). TMR provides high error coverage, but in the dark silicon context it may not meet the power constraints due to its huge power overhead. DMR incurs in considerably less power overhead, but it has to be enhanced with some additional hardware to save periodically the architectural context to allow for error recovery instead of only error detection (BERNICK ET AL., 2005), known as 'checkpointing'.

Checkpointing is a technique used to create a consistent architectural state where the system can rollback in case an error is detected. The problem with checkpointing is that its efficiency is severely reduced depending on how many instructions are allowed to execute before the architectural state is stored. Fig. 1.2 summarizes the findings presented in Chen and Yang (2013) about the efficiency of redundant multithreading checkpointing, where two threads execute the same code and their store instructions are compared for error detection and rolled back to the last checkpoint

to recover the error, which shows that in the best case scenario, the total overhead to recover the architecture to a consistent state is at least 25% of the total execution time. In critical embedded systems, which usually have some sort of real-time behavior, this high overhead may jeopardize its timing constraints.

Time redundancy for microprocessors is a DMR approach where the duplicated cores are not synchronized and one of them executes ahead of the other (ABATE ET AL., 2009). In these solutions, a large area of custom circuitry is necessary to put the cores back in a correct state in case of an error (ABATE ET AL., 2009), plus at least 200% performance and power overhead due to the time redundancy and the memory needed to checkpoint the architectural state. Time redundancy can also be applied in a single core system, by launching two identical threads with a time difference between them. This approach saves power due to the single core arrangement, but incurs in heavy performance costs.

In microprocessors, one of the most critical component in terms of reliability and peak power dissipation in the chip is the register file (BLOME ET AL., 2006). Registers are typically built with the most advanced technology transistor node available to save silicon area, and their cell node capacitance is shrunk as much as possible to increase performance. The register file is central to many existing architectural solutions designed to increase application performance, such as deep pipelining and speculation. On the other hand, these architectural constructs create a tough challenge for efficient hardening because they do not allow the precise worst case execution time computation (HAMDIOUI ET AL., 2013; WILHELM AND GRUND, 2014), not to mention the additional power required to make them work, leading to unfeasible hardening solutions when considering modern architectures in the context of constrained real-time and low power embedded systems.

The challenge that power imposes on the reliability of embedded computing has made efficient error correction a 'wishful thinking'. Research has concentrated on i) exact schemes of error detection based on the assumption of using bigger transistors for detection logic (Austin, 1999); or, wherever, possible, on ii) exploiting the characteristics of the system domain to perform error correction based on accepting an error margin in the correction precision (YETIM, MARTONOSI AND MALIK, 2013). Besides missing the benefits of Moore's Law, the first approach does not

apply because the old technology of today is already sensitive to radiation. The second approach is not feasible as a general solution because some domains do require an exact behavior when handling errors in computation, even though general purpose approximate architectures aimed to reduce the energy overhead wrt. exact computation exist (ESMAEILZADEH ET AL., 2012).

The discussion of this section leads to the requirements that an architecture for reliable embedded computing has to meet to be feasible:

- The checkpointing rate and the size of checkpointed data must be reduced to a

bare minimum. This reduction overcomes the performance overhead presented

in Fig. 1.2 and allows the reliability mechanism to be deployed even in realtime systems;

- The vulnerability of the register file must also be reduced as much as possible.

In an ideal setting, the register file cannot be duplicated in order to avoid the increase on sensitiveness to upsets;

- 3. The reliability mechanism must be power efficient because of the predicted 'power wall' of 3 Watts (ITRS, 2012);

- 4. Performance overhead must be minimum to reduce the performance gap of radiation hardened architectures:

- 5. Area overhead must be minimum to mitigate (or avoid) dark-silicon;

- 6. Software development has to be supported by a full-fledged production level compiler.

This work shows how power, area, error coverage and performance can be reconciled in fault tolerant general purpose embedded computing. The path taken in this dissertation for that is to rethink the HW/SW Stack supported by a new compilation strategy, reduced duplication, and bare-minimum checkpointing.

#### 1.3 Error Correction Design Space

Error correction in microprocessors is challenging to implement due to the performance and power costs involved. A fault tolerance technique for constrained systems

aims to reduce power and performance overhead without compromising error coverage, usually using TMR as baseline. To understand what limits error correction and how the Stack addresses these challenges, it is necessary to consider a complex design space.

Checkpointing architectural state. Checkpointing stores the processor state periodically, creating a correct state that the architecture can rollback to if an error needs to be recovered. Because checkpointing occurs concurrently with software execution, the performance and power overheads introduced to take these architectural snapshots come from two interdependent sources: (1) the number of instructions that are allowed to commit before the architecture state is stored; and (2) the location in the architecture where the checkpoint data is stored.

The number of instructions allowed to commit before creating the architectural snapshot should be the smallest possible. This instruction window composes the granularity of the checkpointing method. A fine-grain approach corresponds to a single or a few instructions; in the opposite side of the spectrum, a coarse-grain approach corresponds to a thread. The granularity of the checkpointing method impacts performance due to both the error detection latency and the error recovery latency. The checkpointing granularity also impacts hardware: a fine-grain technique requires less hardened storage but additional custom hardware, while a coarse-grain one requires more hardened storage but fewer hardware modifications even none, in some cases. A complete checkpointing taxonomy is given by Prvulovic, Zhang and Torrellas (2002).

Error detection and correction latency. In the software level, fault tolerance imposes two main sources of performance overhead: (1) the additional instructions or routines executed until the fault tolerance mechanism flags that the system has an error, known as error detection latency; and (2) the additional code executed to remove the error from the system, known as error correction latency. Error detection is a periodic task that executes concomitantly with software execution, thus it impacts systems performance even in error-free execution. To mitigate error detection costs, the fault tolerance technique may be dormant for several cycles, and activated in a given period. The longer the dormant period, the higher the error detection latency will be, which implies a larger size of the checkpointing data.

Hardware support for error correction. In the hardware level, the costs to support error correction correspond to how many redundant or hardened components are included within the Sphere of Replication (SoR), i.e., the logical domain of redundant execution to support a given fault tolerant mechanism and its fault model (Reinhardt and Mukherjee, 2000). For standard DMR and TMR systems, the SoR usually encloses two and three full copies of the microprocessor, respectively. In addition to the redundant components enclosed within the SoR, it is also necessary to consider how the systems memory components are protected, i.e., the main memory and the register file. The register file is the most sensitive component for soft errors of an embedded microprocessor (BLOME ET AL., 2006), and, as such, it is mandatory to harden it with ECC or some other error correction technique if the chip is going to be used in a mission critical application. Because the chip is inside the SoR, the power dissipation cost to protect with ECC a DMR or TMR system can correspond to up to six times the original unhardened register file (BLOME ET AL., 2006). This cost is important because much of the work in the error correction literature considers a hardened register file without considering the costs to implement that protection.

#### 1.4 Rethinking The HW/SW Stack

The *Transactional HW/SW Stack* (or simply, Stack) is an integrated approach between software compilation and computer architecture designed to put together power, area, error coverage, and performance in fault tolerant embedded computing.

In the hardware layer of the Stack, the *TransactiOnal Basic Block Architecture* (ToBBA) introduces a novel mechanism for doing dual modular redundancy we call *Lightweight DMR* (LDMR). In the LDMR, the microprocessor control logic and pipeline are duplicated, but the register file and remaining controllers are not. The two cores inside the LDMR share a single register file, which requires a fierce policy on how ToBBA coordinates data read and write to the register file. Still in the hardware layer, ToBBA introduces a fast and predictable mechanism for error recovery. At this point, the hardware layer crosscuts the software layer in the Stack.

In the software layer of the Stack, the *Transactional Basic Block* (TBB) revisits how program's basic blocks (BB's) are defined and generated. The TBB is an atomic

unit of execution that either finishes after computing correct data or fails in case of errors. In the software level, standard basic blocks communicate through the register file and memory, being the compiler job to reduce memory communication and maximize register communication. Differently from a standard BB, a TBB only communicates with others TBBs using the memory. By eliminating register communication between TBBs, register liveness (time between the last write and a read of a register) is also eliminated. Also because the elimination of register communication, in case a TBB fails to execute, the error recovery is simply to reexecute the TBB from its start, respecting some policy on how data are written and read from the register file.

The innovation behind the Stack is how it performs error recovery based on the TBB execution and fault semantics. In this work, two proposals are evaluated: (1) the TBB holds all the data envelope necessary to correct the error; and (2) ToBBA is enhanced with auxiliary hardware, the *Spill Register File*, which will store the data envelope necessary to correct the error. Recalling the conundrum we have discussed before, proposal (1) saves hardware area and power, but incur higher performance overhead. Conversely, proposal (2) incur less performance overhead but requires additional area and power.

To summarize, the proposed Stack has the following characteristics, which will be discussed throughout this dissertation.

- Early Error Detection: the ToBBA architecture has two in-order RISC cores executing in loose lock-step for general purpose computation. The instructions executing in the two cores are compared against each other during their entire life cycle in the pipeline, e.g., if an error is detected as early as in the fetch state, this instruction is discarded and the error can be corrected early;

- **Tight Error Containment**: the TBB is a basic block that defines all registers it needs for computation, and it also terminates them at the end of its execution. The execution of a TBB does not share any registers with another TBB, eliminating the need for register file coherency;

- On-Line and Efficient Error Recovery: due to tight error containment, if

a TBB finishes with no errors, that TBB is asserted as correct and committed. Otherwise, an error is detected and only the faulty TBB is re-executed without any software checkpoint;

- Memory Correctness: because errors are contained inside a single TBB, only the store instructions can corrupt memory. The proposed architecture guarantees that only the correct execution of store instructions are allowed to modify the memory and that the incorrect ones are discarded before they can corrupt the memory;

- Low Power within Small Area: ToBBA, in comparison with standard TMR and even DMR arrangements, does not duplicate the register file, leading to aggressive power and area savings. Even when it introduces the Spill Register File, there area and power savings with respect to TMR;

- **High Predictability**: because the TBB prevents the propagation of errors to other program regions, the error recovery latency in the worst case is equal to the number of instructions of the TBB where the error was detected. The latency of the proposed error recovery scheme can be computed during compilation, a much desired characteristic for real-time systems;

- Stateless Design: because there is no need for register file coherency and memory is correct, ToBBA becomes stateless, meaning that it can just be reset and replay the TBB execution with no need to checkpoint its not-existing internal state to do error recovery.

Experimental evaluation supports mean performance overhead of 1.54 for a MiBench (GUTHAUS ET AL., 2001) subset in proposal (1) i.e., using only the TBB as data envelope for error correction; and 1.33 in proposal (2) i.e, using the auxiliary Spill Register File as data envelope for error correction. The measured area overhead is 2.65 with respect to a single core, and the power overhead is 2.05, also with respect to a single core. The measured error correction coverage based on VHDL fault injection is 99.35%, and 99.88% of error detection coverage, leading to 0.12% of silent data corruption (SDC). These power, area and coverage results show that the Stack provides TMR-like error coverage with DMR-like hardware costs.

The measured performance overhead is considerably smaller than state-of-the-art techniques.

In summary, the contributions of this dissertation are:

- A new compilation strategy based on the elimination of live-out register-toregister communication, making the basic block an atomic unit of execution and error containment;

- The auxiliary Spill Register File, which reduces the performance overhead associated with the TBB;

- The LDMR arrangement, which is capable of executing the TBB and error recovery based on the TBB fault semantics;

- The implementation of the compilation strategy in LLVM, showing the real usage scenario and evaluation of the compilation strategy;

- Putting it all together, a new hybrid HW/SW error correction technique that

does not make unfeasible assumptions about the fault model or the error detection latency.

#### 1.5 Text Organization

This dissertation is organized as follows:

- Chapter 2 introduces the TBB, its instruction ordering, execution semantics, and the algorithm to transform an original program into a transactional one with TBB's. That Chapter also discusses the implementation of the TBB generation in the full-fledged production level LLVM (LATTNER AND ADVE, 2004) compiler, and how the TBB concept crosscuts the HW layer of the Stack;

- Chapter 3 presents the LDMR, and how it is realized in the in-order ToBBA architecture. That Chapter also discusses in details the error recovery mechanism, its corner cases for the in-order ToBBA, and the comprehensive fault model ToBBA can handle. The Chapter finishes by discussing how the LDMR and ToBBA crosscuts the SW layer of the Stack;

- Chapter 4 presents the Spill Register File (SRF), an auxiliary hardware where the live-out values of the TBBs are stored. The SRF removes the need for adding additional load and store instructions in the TBB, although it still relies in the TBB instruction ordering and semantics. This Chapter discusses the hardware implementation and how the TBB generation needs to change in order to be compatible with the SRF;

- Chapter 5 evaluates the Stack for performance overhead, area occupation, error coverage, and error recovery latency. That Chapter sustains the claims made in this introductory Chapter and shows how the elicited requirements for fault tolerant embedded computing are met;

- Chapter 6 compares the Stack with existing techniques in the published literature for fault tolerant computing. That Chapter shows how the Stack advances the state-of-the-art;

- Chapter 7 concludes this dissertation, summing up the discussions made in the text, and some possible future work.

#### 2 TRANSACTIONAL BASIC BLOCK

#### 2.1 Definition and Instruction Formation

This section introduces the TBB definition and how the error handling and rollback mechanism works in the software layer of the Stack. The TBB algebraic description is presented in Section 2.2. The TBB definition and execution semantics is as follows:

The TBB is a basic block that starts with a sequence of load, arithmetic and logic instructions for register definition, followed by a sequence of store instructions for register termination, and ends with a terminator instruction finishing the TBB. The execution of a TBB is only concluded when no error is detected. If an error is detected, the Stack error handling starts the rollback mechanism to re-execute the TBB from its first instruction.

The TBB definition contains two distinct basic block 'segments': i) register definition; and ii) register termination. Fig. 2.1 presents a TBB to illustrate these two segments using a MIPS-like ISA to facilitate the understanding.

The **register definition** segment computes the architectural register file, i.e., the data a TBB are currently operating over. This TBB segment only contains load, arithmetic, and logic instructions (Load|ALU for short). The **register termination** segment writes in the memory all data computed by a TBB that is required by another portion of the program, i.e., the 'live-out' values of the current TBB have to be stored in memory before the next TBB starts executing. The register termination segment only contains store instructions.

The TBB is an atomic unit of execution in terms that its execution either completes correctly or a rollback is triggered to correct the error. To enable the simply

Figure 2.1 – Segments of the Transactional Basic Block

LWI r1, r0, 5

LWI r2, r1, 0

ADDIK r4, r1, 1

ADDIK r5, r4, 0

LWI r6, r4, 0

ADDIK r7, r1, 0

SWI r0, r0, 7

SWI r2, r5, 0

SWI r6, r7, 0

BRANCH

Register definition

Register termination

re-execution of the TBB when an error is detected, if a TBB A defines a value x that is also used by TBB B, B cannot assume the register containing the value x computed by A is correct when execution reaches B, i.e., register communication between two different TBB's is not allowed.

A central concept in the TBB is 'live-out' value. A live-out is any value defined in a standard basic block (BB) that is later used in a different BB. In a TBB, all live-out values in registers must be spilled, i.e., stored in memory before the TBB execution ends. In this way, the spilled live-out value of a TBB has to be filled into a register before its use in any other TBB. Therefore, the transformation of a BB into a TBB involves the definition and use (def-use) chain of values in the control flow graph (CFG). Spilling all live-out values of all BB's and enforcing the instruction ordering of the register definition and termination segments define a TBB. The transformation presented in Section 2.2 formalizes these concepts.

The TBB generation requires a compiler to support it, because the ordering of the register definition and termination segments must be enforced, as well as the spilling of all BB's live-out values. In this work, we have implemented the TBB generation in the LLVM (LATTNER AND ADVE, 2004) open-source compiler. The benefit of implementing the TBB generation in LLVM is that we can generate TBB's for any architecture LLVM supports. Because the TBB requires the software to be compiled beforehand, thus ToBBA does not offer binary compatibility for previously compiled programs. The LLVM implementation details are discussed in Section 2.3.

The TBB definition has explicit connections with the hardware layer, i.e., how

ToBBA implements error handling based on the TBB's instruction ordering. In short, the TBB defines how the register file state is constructed. Based on the register definition and termination segments and their respective instruction ordering, ToBBA selects the appropriate error handling and rollback actions depending on the segment being executed. The connections between the TBB and ToBBA are listed and briefly discussed in Section 2.4 to overview the hardware layer before going deeper inside it.

#### 2.2 Transforming Programs into Transactions

#### 2.2.1 Preliminaries and Definitions

The TBB generation in this work was implemented in the LLVM (LATTNER AND ADVE, 2004) compiler, and, as such, much of the algebra and constraints discussed in this Section are due to how LLVM works and represents programs.

In brief, the transformation that takes a program with standard BB's and gives an equivalent program with TBB's operates in two points of the LLVM compiler. The first one is in the middle-end, after the source code is compiled and transformed into the LLVM's Intermediate Representation (IR). The LLVM IR is an 'almost' target-agnostic language designed to be amenable for program transformations, such as loop unrolling and vectorization <sup>1</sup>. More on the LLVM implementation is discussed in Section 2.3.

After the program is compiled in LLVM, a standard control-flow graph (CFG) is created. A CFG is a directed graph  $C = (V, E, e_o, E_e)$  where V is the set of BB's and E is the set of possible branches between the elements of V. In any CFG, there is an *entry* basic block  $e_o$  which has no predecessor, and a set  $E_e \in E$  of *exit* blocks that terminates the program (or function) with no successors (ALLEN, 1970).

LLVM respects the classical CFG definition of Allen (1970) with an additional constraint: the basic blocks are defined in Static Single Assignment Form (SSA). In SSA, all variables are assigned once, and it also requires that any variable use must have a prior definition of that used variable (ROSEN, WEGMAN AND ZADECK, 1988). The adoption of SSA in LLVM means that in LLVM IR there is an infinite

<sup>&</sup>lt;sup>1</sup>For a discussion about the target-independence in LLVM IR, readers should check http://lists.cs.uiuc.edu/pipermail/llvmdev/2011-October/043719.html

number of registers, being the job of the register allocator to lower SSA into the available registers of the architecture.

The TBB generation requires a LLVM IR without  $\phi$  nodes.  $\phi$  nodes are used in SSA to assign a value depending on the predecessor of the current BB. Let us say that in the current BB, there's a variable x that is assigned the variable y. However, the value of y depends on which block is the predecessor of the current BB, because the predecessors also assign a value to y. In SSA, a data-flow statement that depends on control-flow resolution is represented as  $x \leftarrow \phi(y_1, y_2)$ , where  $y_1$  and  $y_2$  are the y instances created on each predecessor BB. These  $\phi$  nodes can be removed in the IR level, because they do not exist in the final generated assembly code anyway. In this work, we just assume they were removed. In LLVM,  $\phi$  removal is accomplished with the auxiliary function **DemotePHIToStack**  $^2$ .

Lastly, it is necessary to define a program. A program  $P = \langle F, G \rangle$  is a tuple where F is the set of functions of P and G is the set of global variables of P. Any function  $f \in F$  can read and write any  $g \in G$ . This definition slightly differs from LLVM, where it would correspond to a 'module'.

The program transformation encompasses three steps that need to be executed in that given order. The first step is to promote the return values of all functions into a global variable. This value promotion is necessary to spill the return value. Otherwise, that return value would reside only in the registers. This first step is presented in Section 2.2.2. The second step is to split basic blocks with function calls in such a way that the call instruction becomes the terminator of the new basic block. Notice that this step modifies the CFG. This step is given in Section 2.2.3. The third step is the actual live-out spilling briefly discussed before, which is given in Section 2.2.4.

#### 2.2.2 Promoting Functions' Return Value Into Global Variable

Most of microprocessors store a function's return value into dedicated registers. For instance, in MIPS registers **\$v0** and **\$v1** are dedicated to temporarily store the return values produced when a function returns. However, preserving a register from the called function to the callee creates a register communication between these two

<sup>2</sup>http://llvm.org/docs/doxygen/html/DemoteRegToStack\_8cpp\_source.html#100110

functions, which by the TBB definition is not allowed.

The solution in the TBB generation is simply to spill the return value of the called function into a global variable of the same type as the function. In that way, any other TBB in the program can fill a register with that global variable whenever it needs to access that return value. In the next, the function Type(value) gives the return type of the argument if it is a function, and the type if it is a variable.

```

Algorithm 2.1: PromoteFuncRetToGlobalVar

Data: P = \langle F, G \rangle

Result: P = \langle F, G' \rangle where G' contains the new spill global return variables.

1 begin

G' \leftarrow G

\mathbf{2}

for all the f_k \in F do

3

if Type(f_k) = void then

4

skip

5

Create new global variable g_k where

6

Type(g_k) = Type(f_k)

7

g_k \leftarrow \mathbf{undef}

8

G' \leftarrow g_k \cup G'

9

```

There are two points that need to be clarified in Algorithm 2.1. Line 4 skips the iteration if the return type of the function  $f_k$  is 'void'. Void functions do not return value, thus, there is nothing to spill, and, as such, it is not necessary to create a global variable for  $f_k$ . Line 8 initializes the new global variable  $g_k$  with the 'undef' value. In LLVM, an undef value says to the compiler that the program is well-defined no matter the value an undef variable is assigned. Assign undef to  $g_k$  is correct because this global variable is going to store the return value of  $f_k$ , thus before  $f_k$  returns  $g_k$  will contain its correct value.

#### 2.2.3 Splitting Basic Blocks Around Call Sites

After a global variable g is created for each non-void function f of the program P, it is now possible to spill the return value of f to g. The first step in the TBB generation is to schedule each function call in an unique BB. This is simply done by splitting every BB with 'call' instructions around the call, creating a new BB to hold the necessary register fills to hold the function's arguments before the call instruction, which terminates the BB. It is also necessary to spill the call's return

value.

The rationale behind this algorithm is the following. Microprocessors pass arguments to functions through the use of dedicated registers for that, thus, there's register communication also between the called and the callee functions. However, if the callee BB were only to have load instructions to fill those arguments into the dedicated registers, after the call instruction is committed, the execution flow goes to the entry block of the called function. In the microprocessor level, because of how TBB is defined, the instructions executed *before* the entry block are only register definition ones. Thus, we might consider them as being part of the entry block of the called function. This makes the function call to respect the TBB.

The other aspect to be considered is when the called function returns. Recall that the called function has to spill its return value after the callee's call instruction. The last instruction executed in any of the exit blocks of the called function mandatorily is a return, a terminator one. The callee BB already finished executing, because its last instruction was the call to the called function. Therefore, the callee BB will fall through to the next BB. If this next BB were to use the return value of the called instruction, it now can just fill a register with the respective spill variable holding the value it needs. Thus, the return value also respects the TBB definition.

In the following, we use the LLVM type 'CallInst' to represent the set of call instructions existing in a function. We also use a function Parent(value) that returns the BB a instruction is member of, and the function Next(value), which gets the next instruction of the instruction passed as argument in the BB Parent(value). The BB splitting is done with the LLVM auxiliary function SplitBlock <sup>3</sup>. The SplitBlock function takes as arguments the BB to be split, and the instruction where the BB will be split around. This function creates two BB's as follows. Let us say that a BB b will be split around its instruction  $i_k$ , and that  $b = i_1 \dots i_{k-1} i_k \dots i_n$ . Calling  $SplitBlock(b, i_k)$  produces the BB's  $b_{before} = i_1 \dots i_{k-1}$ , and  $b = i_k \dots i_n$ . It also creates one unconditional branch  $b_{before} \to b$  connecting these BB's. SplitBlock returns b. Therefore, SplitBlock modifies the CFG of the program P.