# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

# JECKSON DELLAGOSTIN SOUZA

# **Evaluation of Heterogeneous CReAMS**

Paper presented as partial requirement for the degree of Bachelor in Computer Engineering.

Advisor: Prof. Dr. Antonio Carlos Schneider Beck

Co-advisor: Prof. Mateus Beck Rutzig

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Graduação: Prof. Sérgio Roberto Kieling Franco Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do Curso de Engenharia de Computação: Prof. Marcelo Götz Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **AGRADECIMENTOS**

Agradeço a minha família, pelo apoio durante toda a minha diplomação. Ao meu pai, Valerio, que sempre incentivou, mesmo que de forma implícita, todas as minhas decisões. À minha mãe, Genelci, por não ter me expulsado de casa mesmo perante a falta de organização explícita de um concluinte de graduação. E ao meu irmão, Jonatas, por estar sempre disponível para ajudar.

Agradeço aos meus amigos – os que conheci antes, durante ou fora da faculdade – que ajudaram a tornar o todo o processo mais simples. Em especial, agradeço a Alessandra Leonhardt, Arthur Rauter, Eduardo Conto, Gennaro Rodrigues, Ingrid Lopes, Lucas Schons, Luís Henrique Reinicke, Luis Henrique Grassi e Marcelo Brandalero que tornaram todo esse final do curso mais especial. Aos meus amigos de Glasgow, que foram como uma família por um ano e com os quais eu dividi alguns dos melhores momentos da minha vida, e, por isso, estarão sempre presentes comigo, mesmo que distantes. Em especial, ao Eduardo Couto, Juliana Versiane, Lucas de Souza e Aline Carvalho por terem me recebido em suas casas e feito viagens fantásticas comigo. Esses dias roubados de férias inventadas foram muito importantes para o andamento deste trabalho.

Aos colegas do laboratório de sistemas embarcados, que ajudaram neste projeto não apenas tecnicamente, mas também com amizade e fartas ofertas de pizza (muitas das quais eu tive que recusar de má vontade por causa deste projeto). Agradeço ao Cláudio e Daniel Walter, que além de me proporcionarem minha primeira experiência profissional quando eu era apenas técnico em informática, ainda me deram todo o tipo de apoio para que eu ingressasse na graduação e continuasse minha formação.

Ao meu orientador e meu coorientador, por estarem sempre dispostos a ajudar e incentivar a minha produção intelectual. Em especial ao Caco, que me convenceu de que ainda pode existir vida acadêmica após a graduação. Também ao meu orientador de Glasgow, Iain Thayne, por ter me inserido no ambiente de pesquisa e em um projeto inspirador e que, mesmo que não tenha se tornado minha área, me fez querer continuar na produção científica.

Agradeço à CAPES por financiar todo o meu intercâmbio e o CNPQ pela oportunidade de realizar a iniciação científica. À UFRGS, por fornecer a educação de qualidade, e principalmente àqueles professores que não apenas estiveram dispostos a compartilhar conhecimento, mas também me inspiraram no aprendizado.

Por fim, agradeço também a todos aqueles que fizeram parte da minha vida durante esses anos de pleno amadurecimento e aprendizagem. Obrigado a todos.

## **RESUMO**

Arquiteturas reconfiguráveis são uma alternativa às clássicas organizações superescalares para explorar o paralelismo em nível de instruções em aplicações (ILP, do inglês Instruction Level Parallelism), enquanto que as organizações multinúcleos são a estratégia normalmente adotada para tirar proveito do paralelismo no nível de threads (TLP, do inglês Thread Level Parallelism). Este trabalho é baseado no CReAMS, um sistema reconfigurável que explora os benefícios de ambos o ILP – através de um array reconfigurável – e TLP – por multinúcleos. Contudo, o CReAMS foi inicialmente projetado como um sistema homogêneo, cujos núcleos são exatamente iguais, o que é uma estratégia ineficiente quando considerado que aplicações atuais possuem grande variação de carga entre suas threads. O objetivo deste trabalho é introduzir o conceito de CReAMS heterogêneo, uma versão cujos núcleos possuem recursos distintos. Mostraremos as motivações para usar um sistema heterogêneo ao invés de um homogêneo, especialmente no aspecto das aplicações atualmente executadas nos sistemas embarcados. Este trabalho propõe encontrar algumas configurações heterogêneas de CReAMS que ganhem, em desempenho, de versões homogêneas de mesma área. Mostraremos a metodologia usada para criar tais configurações, o processo de simulação e os resultados, os quais sugerem que sistemas heterogêneos baseados em CReAMS tem melhor performance que versões homogêneas quando as aplicações executadas possuem baixa distribuição de carga entre as threads ou alto potencial para exploração de ILP.

## **ABSTRACT**

Reconfigurable architectures are an alternative for classic superscalar organizations to the exploitation of instruction level parallelism (ILP) on applications, while the multicore organizations are the most commonly used strategy to exploit thread level parallelism (TLP). This work is based on CReAMS, a multicore reconfigurable system that explores the advantages of both ILP – through a reconfigurable array – and TLP – through multicores. However, CReAMS was conceived as a homogeneous system, in which cores are exactly the same. This is an inefficient strategy when we consider current applications that have great variability through its threads. The main goal of this work is to introduce the concepts of heterogeneous CReAMS, a version in which cores have distinct resources. We will show the motivations for using a heterogeneous system over a homogeneous one, especially in the aspect of the current applications executed in the embedded systems. This work proposes to find some heterogeneous configurations of CReAMS that outperform a homogeneous configuration of same area. We will show the methodology for creating such configurations, the simulation processes and the results, which suggest that heterogeneous systems based on CReAMS have better performance than homogeneous versions when the executed applications have poor load balance between threads or have high potential for exploiting ILP.

**Keywords**: Reconfigurable architectures. Multicore systems. Heterogeneous systems. Homogeneous systems.

# LIST OF FIGURES

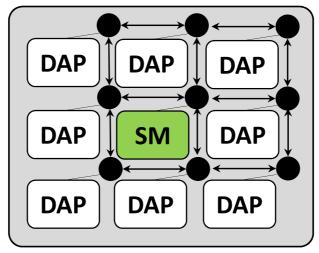

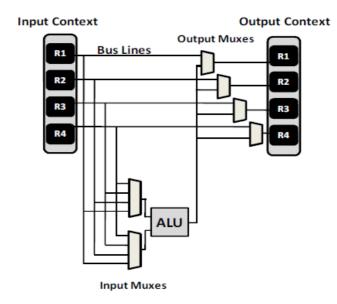

| Figure 1 CReAMS of 8 cores (DAPs) and a L2 shared memory (SM)                                    | 19    |

|--------------------------------------------------------------------------------------------------|-------|

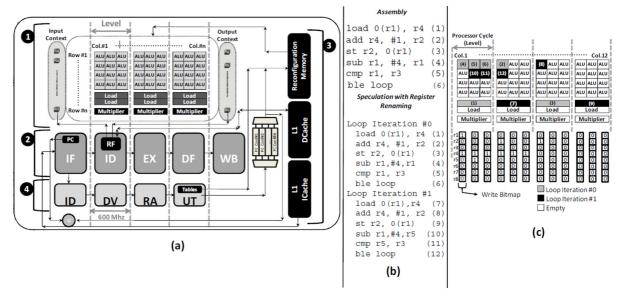

| Figure 2 (a) DAP blocks (b) Assembly of a loop (c) Allocation inside of reconfigurable datapath  | 20    |

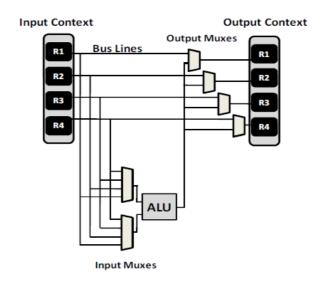

| Figure 3 Interconnection mechanism                                                               | 21    |

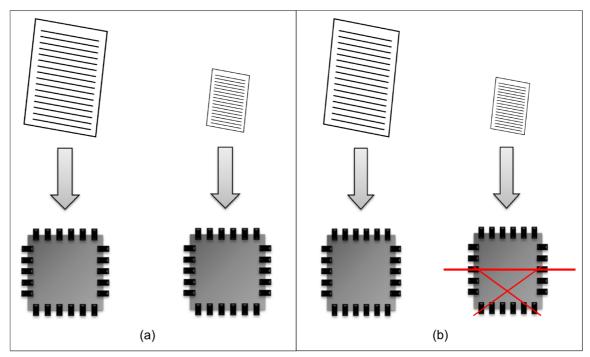

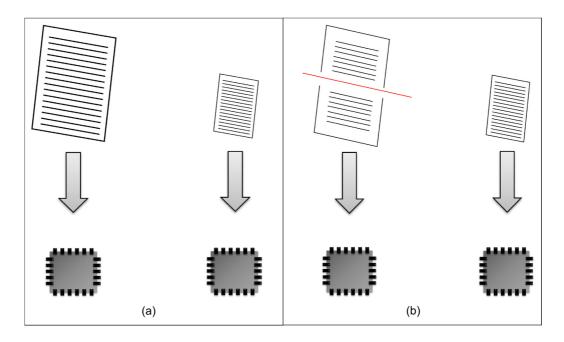

| Figure 4 (a) Heterogeneous threads running on big cores. (b) Parts of the array are wasted       | 24    |

| Figure 5 (a) Heterogeneous threads running on small cores. (b) Bigger threads have to be split   | 25    |

| Figure 6 Heterogeneous threads running on heterogeneous cores                                    | 25    |

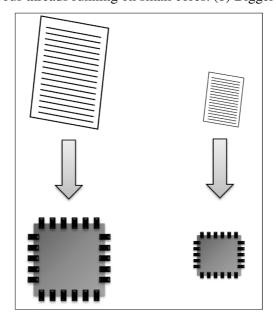

| Figure 7 An eight-core homogeneous version of CReAMS and a quad-core heterogeneous version       | on 26 |

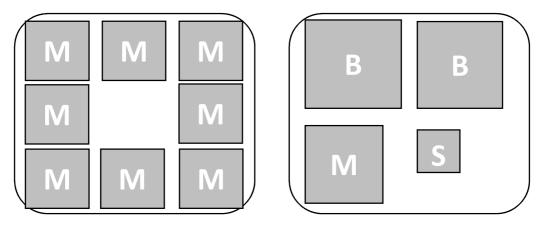

| Figure 8 Methodology in steps. (A) Configurations creation thought area spreadsheet. (B) Scripts | s for |

| simulation of each configuration. (C) Simulation of scripts. (D) Compilation of results. (E)     |       |

| Comparison and chart anylisis.                                                                   | 28    |

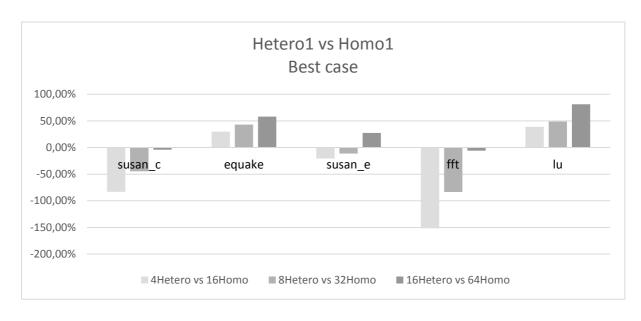

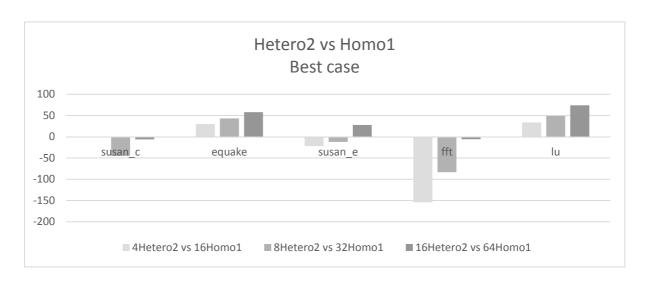

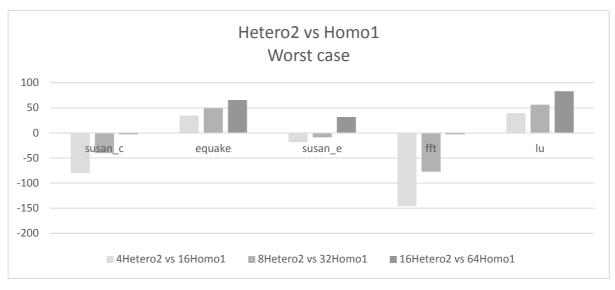

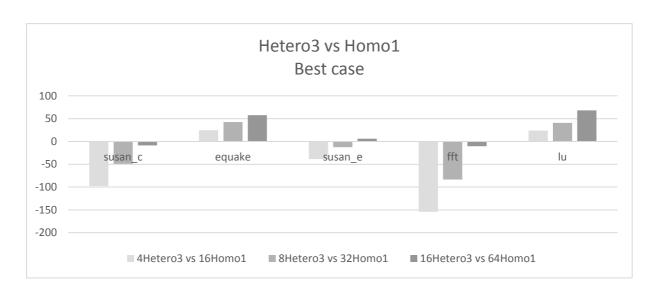

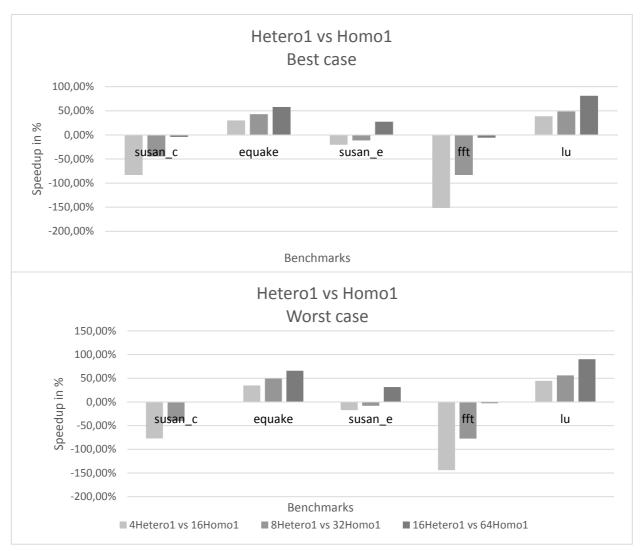

| Figure 9 Hetero1 vs Homo1: Best and worst cases                                                  | 39    |

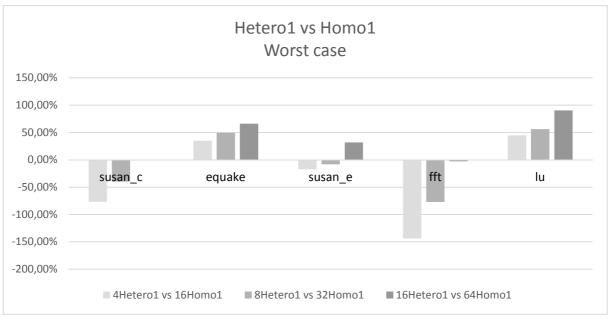

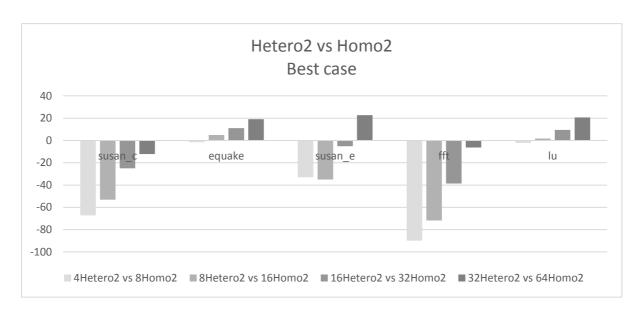

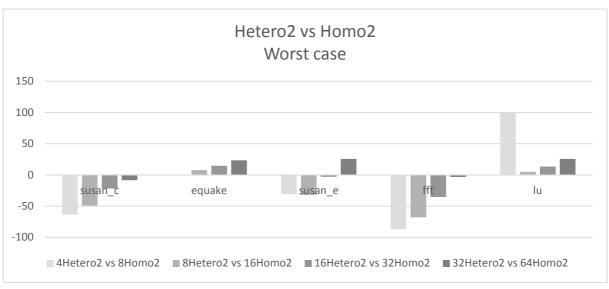

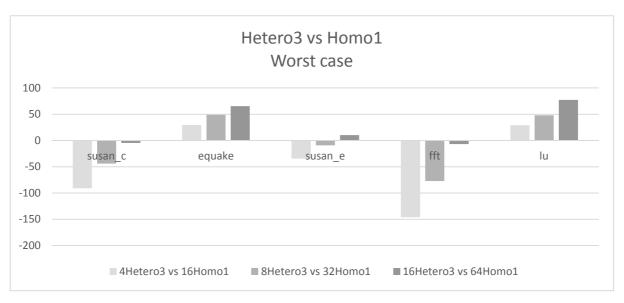

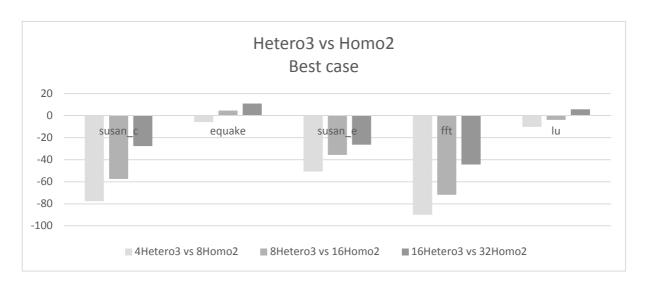

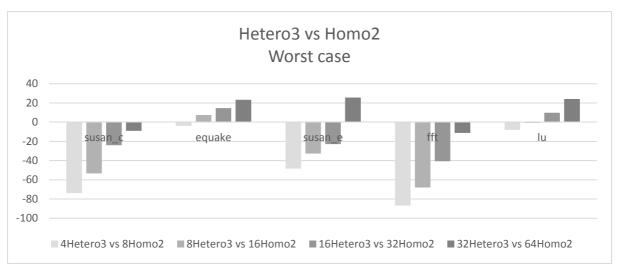

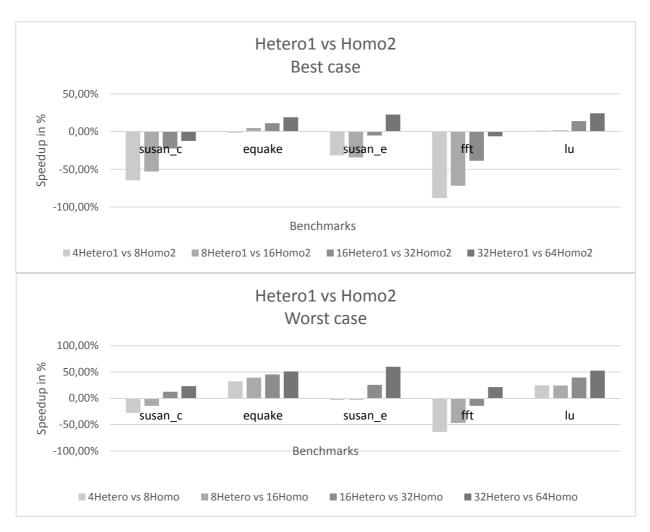

| Figure 10 Hetero1 vs Homo2: Best and worst cases                                                 | 40    |

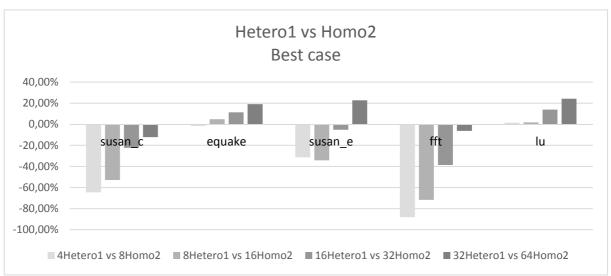

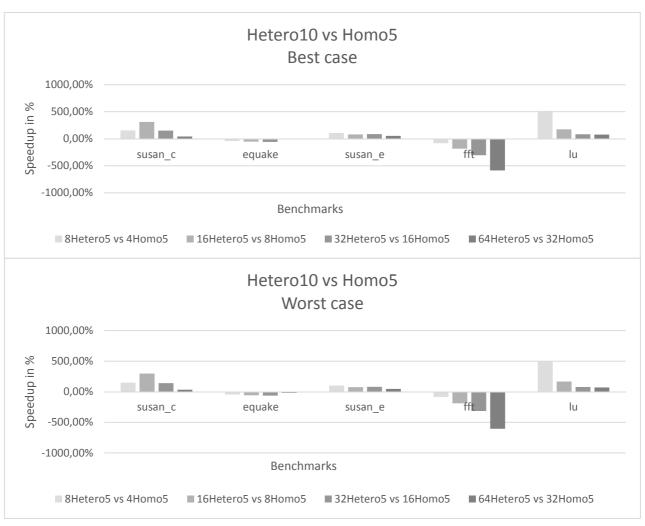

| Figure 11 Hetero10 vs Homo5: Heterogenous version is smaller than the homogeneous                | 42    |

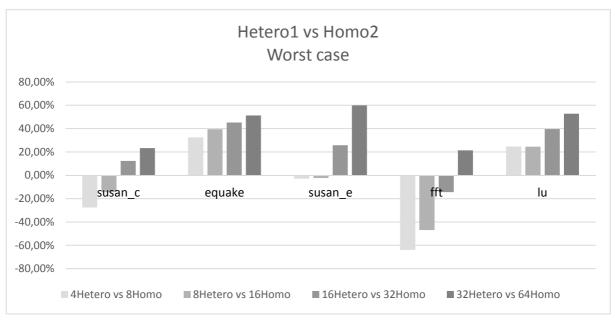

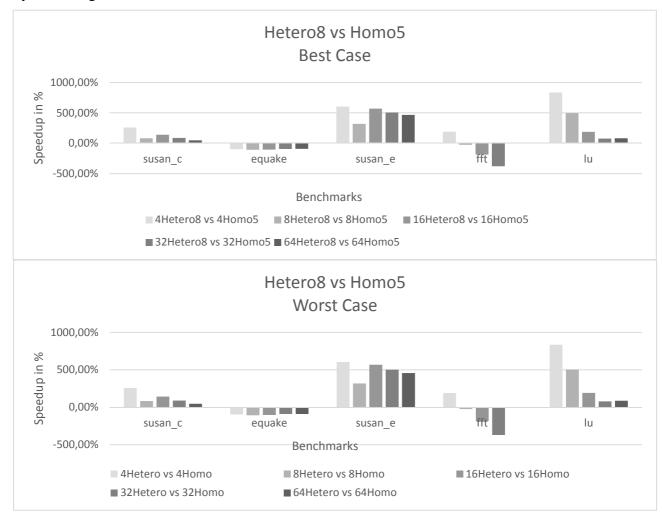

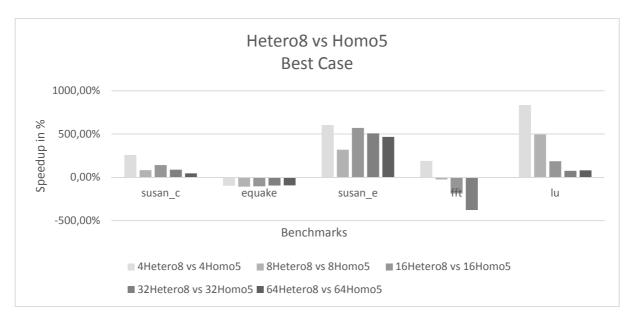

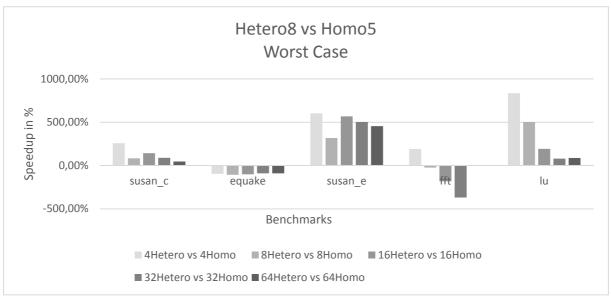

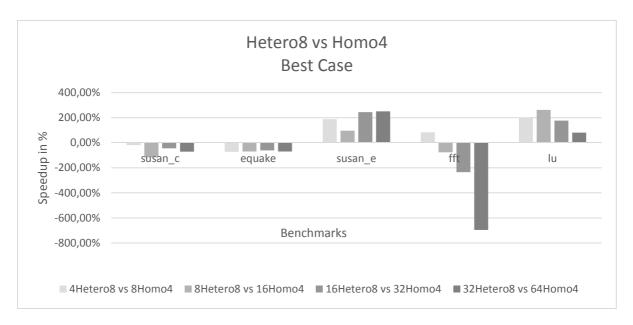

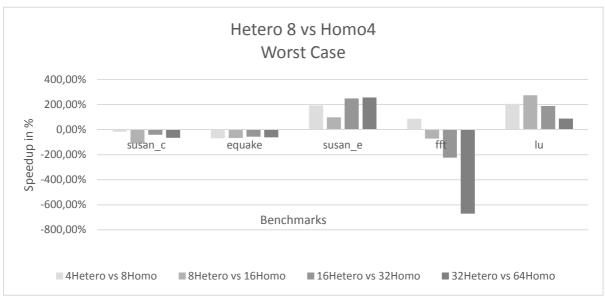

| Figure 12 Hetero8 vs Homo5: Both configurations have the same area                               | 43    |

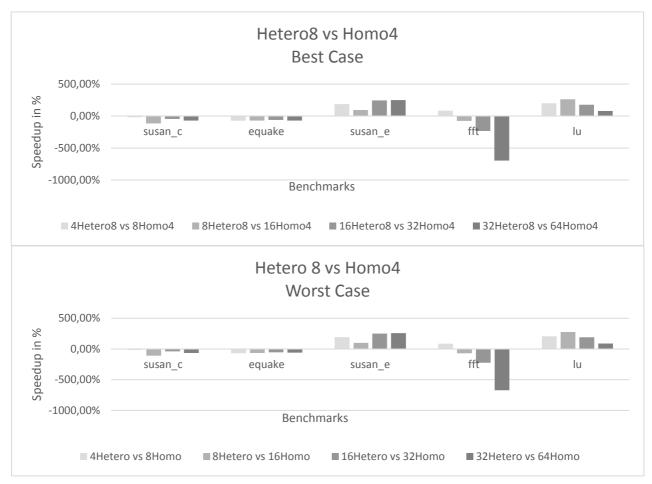

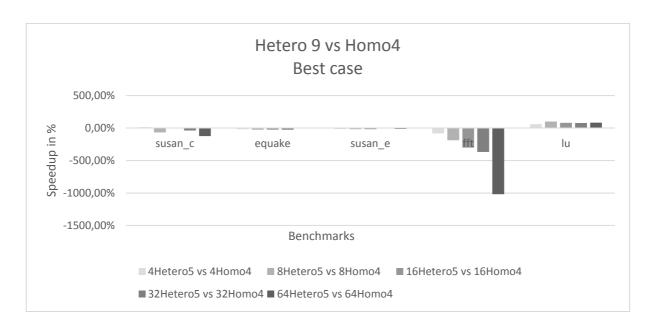

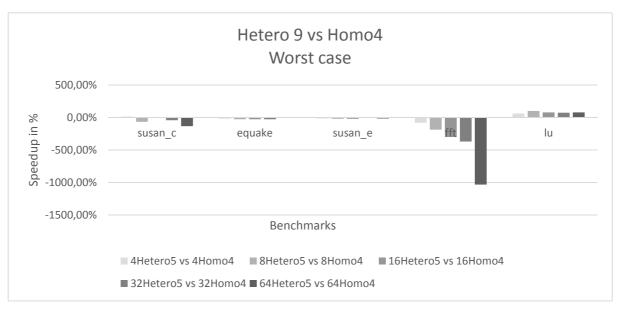

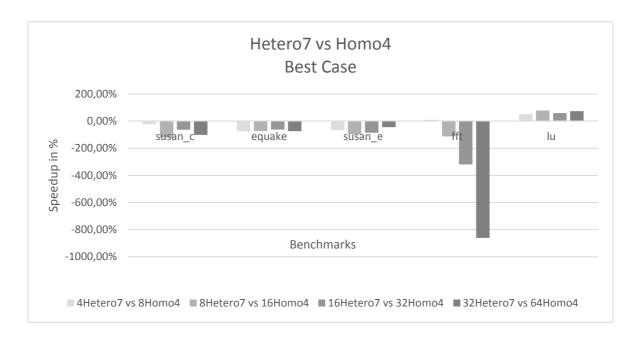

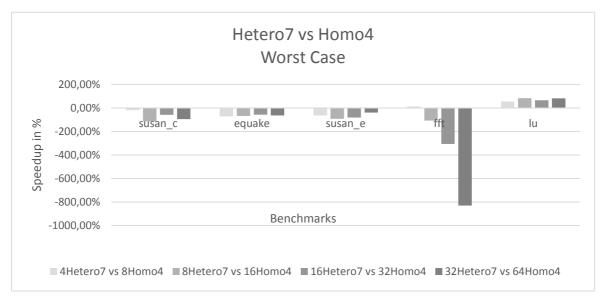

| Figure 13 Hetero8 vs Homo4: Heterogenous version is bigger than the homogeneous                  | 44    |

# LIST OF TABLES

| Table 1 Load balancing and mean basic block size of selected applications | 30 |

|---------------------------------------------------------------------------|----|

| Table 2 Average number of hops for cores                                  | 31 |

| Table 3 Configurations of small cores                                     |    |

| Table 4 Configurations of medium cores                                    |    |

| Table 5 Configurations of big cores                                       |    |

| Table 7 New homogeneous configurations                                    |    |

| Table 6 Homogeneous configurations                                        |    |

| Table 8 New heterogeneous configurations (4-7)                            |    |

| Table 9 New heterogeneous configurations (8-11)                           |    |

|                                                                           |    |

## LIST OF ABBREVIATIONS AND ACRONYMS

OS Operating System

SMS Short Message Service

UFRGS Universidade Federal do Rio Grande do Sul

ILP Instruction Level Parallelism

ARM Advanced RISC Machine or Acorn RISC Machine

RISC Reduced Instruction Set Computing

TLP Thread Level Parallelism

CReAMS Custom Reconfigurable Arrays for Multiprocessor Systems

DAP Dynamic Adaptive Processor

SM Shared Memory

DDH Dynamic Detection Hardware

ASIP Application Specific Instruction Set Processors

**Application Programming Interface**

ASIC Application Specific Integrated Circuits

GPP General Propose Processor

FPGA Field Programmable Gate Array

ALU Arithmetic and Logic Unit

ISA Instruction Set Architecture

VLIW Very Large Instruction Word

CPI Cycles per Instruction

DDH Dynamic Detection Hardware

CSV Comma-Separated Values

LUT Look-Up Table

API

MLP Memory-Level Parallelism

# TABLE OF CONTENTS

| 1.         | INTRODUCTION                                        | 11             |

|------------|-----------------------------------------------------|----------------|

| 1.1        | Contributions                                       | 12             |

| 2.         | RECONFIGURABLE ARCHITECTURES                        | 13             |

| 2.1        | Basic Principles                                    | 13             |

| 2.2        | Classification                                      | 14             |

| 3.         | RELATED WORK                                        | 15             |

| 3.1        | Multithreaded Reconfigurable Systems                | 15             |

| 3.2        | Heterogeneous Systems                               | 17             |

| 4.<br>SYST | CUSTOM RECONFIGURABLE ARRAYS FOR MULTIPROCESSOR EMS | 18             |

| 4.1        | CReAMS                                              | 18             |

| 4          | DAP - Dynamic Adaptive Processors                   | 20<br>22       |

| 5.         | HETEROGENEOUS CREAMS                                | 24             |

| 6.         | METHODOLOGY                                         | 26             |

| 6.1        | Simulation environment                              | 29             |

| 6.2        | Benchmarks                                          | 30             |

| 6.3        | Communication overhead                              | 31             |

| 6.4        | Dynamic Scheduler                                   | 31             |

| 7.         | RESULTS                                             | 32             |

| 7.1        | The configurations created                          | 32             |

|            | Simulations Results                                 | 38<br>40<br>41 |

|            |                                                     |                |

| 8.  | CONCLUSION AND FUTURE WORK | 45 |

|-----|----------------------------|----|

| REI | FERENCES                   | 46 |

| API | PENDIX A                   | 1  |

| API | PENDIX B                   | 1  |

## 1. INTRODUCTION

For many years, the majority of embedded systems was designed to execute tasks that were specific to the device it was built in. For instance, the system inside an MP3 player was designed to decode digital music files and little else. However, the advance of industry technology pushed by the constant market competition has brought the project of embedded processors to a completely new level of complexity. Nowadays, these systems execute many tasks and comprise as many features as possible in just one device. Current smartphones are a clear example of these devices. Smartphones running Google's Android, Apple's iOS or Microsoft's Windows Mobile OS are capable of executing applications that can not only make calls and send SMS, but also play music, browse the web, monitor user activity and location, take pictures and movies, suggest activities for the user and much more. However, all these embodied features require significant amounts of energy and chip area. The latter is an important issue, considering that the user wants to charge the device only once a day. Thus, each new generation of embedded hardware is expected to not only provide more functionalities and be faster, but also to be more energetically and area efficient.

A processor's performance can be improved in many ways: from its manufacturing process to its organization. This work focuses on optimizing the organization, by exploiting the parallel execution of a program's instructions, as it is a common strategy used to increase performance and efficiently use the resources of a processor. If a sequence of independent instructions (that do not operate over the same data set in a read-after-write fashion) is dispatched, the processor can allocate them to different functional units and process them concurrently. This provides performance gains due to the exploitation of the instruction level parallelism (ILP). The superscalar approach is widely used to exploit ILP in both general purpose – as the Intel x86 architectures – and embedded processors – like the ARM architecture. However, it is expensive in terms of power consumption, since for each incoming instruction block, the superscalar processor has to evaluate repeatedly the data dependencies for the dependence analysis. If the same block is processed multiple times – as in a loop – the superscalar processor needs to evaluate the data dependencies at each execution, because it does not keep any sort of history of these dependencies.

Another possible strategy to exploit ILP is dynamic reconfigurable architectures. They are projected to adapt themselves according to the application at hand, reconfiguring their datapath so that the stream of data through a large set of functional units is optimized. The great advantage of these architectures is that they can also optimize data dependent instructions,

besides executing the non-dependent ones concurrently. Another advantage is that some of these organizations are able to store sequences of instructions with their dependencies already resolved. Thus, differently from the superscalar, the processor does not need to analyze the dependencies each time a block is executed.

Moreover, it is also possible to exploit the parallel execution of program threads. The employment of multicore organizations coupled with the support of the scheduler from the operating system, enables the simultaneous execution of application threads through many processor cores. This is defined as thread level parallelism (TLP) and can be used in any organization, as long as precautions with data consistency in cache and synchronization between cores are taken, which involve hardware support. Therefore, it is also possible to increase performance on reconfigurable organizations through the exploitation of TLP, by the replication of cores that have their own reconfigurable datapath each. CReAMS (Custom Reconfigurable Arrays for Multiprocessor Systems) is an example of such a system.

CReAMS is a reconfigurable system that exploits ILP through an array of functional units capable of adapting itself to execute many instructions concurrently. CReAMS also exploits TLP by replicating its basic core (composed of the processor, the array and additional circuitry to control them), called DAP. Additionally, CReAMS is homogeneous: all cores are the same, which means that the reconfigurable array is also identical on every core.

However, as already mentioned, current applications on embedded processors are quite heterogeneous. Running them on homogeneous multicore systems leads to inefficient usage of the aforementioned architecture. When the cores are not under full usage, many of the functional units on the reconfigurable array are not used, wasting resources and power.

## 1.1 Contributions

Considering the motivations discussed above, this work will study the potential of using a heterogeneous configuration of CReAMS. A heterogeneous CReAMS differs from the homogeneous by the size of the reconfigurable array in each DAP that composes the system. Although CReAMS was originally created to be homogeneous, two different configurations heterogeneous CReAMS were already studied in [1]. This work will further explore the variation of performance on heterogeneous CReAMS by creating many other versions.

In the first step, we have created many heterogeneous versions of CReAMS considering an area parity with a few fixed homogeneous configurations. We have varied the number of functional units, the input context size and the reconfiguration memory to achieve a good diversification of configurations. Our goal was to verify the potential of heterogeneous CReAMS by identifying points of performance improvements. Then, we have selected a few of these proposed configurations and simulate them on a variety of benchmarks – chosen to cover a wide range of applications. We show that one can find heterogeneous configurations that have better performance on some applications, but worst in others.

This work is organized as following: in section 2 we discuss about the reconfigurable architectures and their main classifications; section 3 has a collection of related works both in multithreaded reconfigurable systems and heterogeneous architectures; section 4 introduces CReAMS and its organization; section 5 discusses about the heterogeneous version of CReAMS; section 6 shows the methodology used in this work including the simulation environment and the tools used to reach the results; section 7 discusses and shows some of the most interesting results; and, finally, section 8 gives conclusions and the expected future work for this project.

## 2. RECONFIGURABLE ARCHITECTURES

The architectures that can adapt themselves to provide a hardware expertise for a specific application are known as reconfigurable systems. Because of this specialization, these architectures are expected to provide performance and energy saving improvements. However, these systems are still built aiming flexibility to execute many kinds of tasks, which means that they have smaller gains if compared to dedicated circuits, like Application-Specific Instruction Set Processors (ASIPs) and Application-Specific Integrated Circuits (ASICs) [2].

## 2.1 Basic Principles

Reconfigurable systems are usually composed of a reconfigurable logic, a controller – to control the logic and the communications – and a context memory – to store the configurations – that are usually coupled to a General Propose Processor (GPP). Pieces of code are executed in the reconfigurable logic while others are executed in the GPP. The more code is executed in the reconfigurable logic, the better, as this will be processed in a more efficient

way. However, this could lead to higher costs for the circuitry: there is need for bigger area and memory to implement the reconfigurable logic.

Reconfigurable systems usually implement the following six steps:

- 1) Code Analysis: The identification of the parts of code that can be transformed to execute in the reconfigurable logic. Usually, these are the pieces of code that are most used, like loops, and are named as hot spots or kernels.

- 2) *Code transformation:* The kernels are replaced by reconfigurable instructions, which are handled by the control unit in the reconfigurable logic.

- 3) Reconfiguration: The reconfigurable logic is then reorganized to perform the function that the current reconfiguration instruction was designed for. The configuration of the logic is stored in a special memory, called configuration context. The time needed to configure the whole system is called reconfiguration time, while the memory required for storing the reconfiguration data is called context memory. Both these parameters constitute the reconfiguration overhead.

- 4) Input Context Loading: The input operands are fetched. These could come from the register file, a shared memory or transmitted by message passing.

- 5) Execution: The actual execution of the reconfiguration instruction.

- 6) Write Back: The results from the reconfiguration logic execution are written back in the register file or shared memory, or transmitted by message to the reconfigurable control unit or the GPP.

Steps 3 - 6 are repeated while reconfigurable instructions are found in the code.

### 2.2 Classification

A reconfigurable system can have many classifications, as shown in [2]. Here we will discuss the ones that are most important for our work.

1) Code Analysis: The code analysis can be done directly in the binary/source code or in the trace generated by the execution of the program on the GPP. The trace method has the advantage of keeping dynamic information. For instance, the system designer cannot know if loops with non-fixed bounds are the most used ones by only analyzing the static source code. However, the designer can use tools that

- dynamically analyze the trace and indicate which are the kernels of the application that are being most executed.

- 2) Coupling: This determines how the reconfigurable unit (RU) is coupled to the GPP. The way the coupling is applied determines how the data transmission and synchronization are done. There are three main places where the RU can be placed relative to the main processor:

- Attached to the processor: The reconfigurable logic communicates with the processor by an I/O bus, having to pass through the main memory, which generates high overhead.

- **Coprocessor:** The RU is placed next to the GPP. The communication is usually done using a protocol similar to those used by coprocessors.

- **Functional Unit:** The logic is placed inside the main processor. This way, the RU has full access to the register file of the processor, greatly reducing the communication overhead, but increasing the chip area.

- 3) Granularity: This defines the level of data manipulation of the RU. For fine-grained logic, the smallest blocks that can be configured are usually gates (like on LUTs of FPGAs, they are efficient for bit level operations). On the other hand, coarse-grained RUs have larger blocks (e.g.: ALUs), better suited for bit parallel operations (like bytes, or words).

## 3. RELATED WORK

In this section, we will show some of the works that were developed and are considered the state of the art in reconfigurable systems with multi core processors. However, as by our knowledge, there are no currently solidified systems that combine reconfigurable architectures and heterogeneous cores. Thus, we present current works on thread scheduling and power consumption on heterogeneous systems.

# 3.1 Multithreaded Reconfigurable Systems

One can find different single- and multi- processing environments which apply some kind of adaptability to improve the performance of applications [3] [2] [4]. They can be

homogeneous or heterogeneous, considering their architecture (i.e. what ISA is implemented) and organization (i.e. if the processors that comprise the system are the same or not).

Watkins [5] presents a procedure for mapping functions in the ReMAPP system, which is composed of a pair of coarse-grained reconfigurable arrays that is shared among several cores. As an example of a system with homogeneous architecture and heterogeneous organization, one can find Thread Warping [6]. It extends the Warp Processing [7] system to support multiple-thread execution. In this case, one processor is totally dedicated to execute the operating system tasks needed to synchronize threads and to schedule their kernels in the accelerators. ARM's big-LITTLE [8] also implements a heterogeneous organization and homogeneous architecture by grouping a Cortex A7 and a Cortex A15 within the same chip. This strategy aims to provide high performance as well as power efficiency by selecting at runtime the right processor to execute the task at hand according to its requirements.

KAHRISMA [9] is another example of a totally heterogeneous architecture. It supports multiple instruction sets (RISC, 2- 4- and 6-issue VLIW, and EPIC) and fine and coarse-grained reconfigurable arrays. Software compilation, ISA partitioning, custom instructions selection and thread scheduling are made by a design time tool that decides, for each part of the application code, which assembly code will be generated, considering its dominant type of parallelism and resources availability. A run time system is responsible for code binding and for avoiding execution collisions in the available resources.

Both ReMAPP and KAHRISMA are able to optimize multiple threads, but they break the binary compatibility.

CReAMS have the following advantages:

- Unlike KAHRISMA, Thread Warping and big-LITTLE ARM's strategy, this proposal is physically homogeneous in both architecture and organization. Heterogeneity is achieved on the fly, without any human intervention, by employing a binary translation mechanism that will be explained later. It eases the software development process since a well-known tool chain (i.e. gcc) is used for any of its versions. Neither source code modifications nor additional libraries are necessary if new processing elements are inserted.

- KAHRISMA, Thread Warping and ReMAPP rely in special and particular tool

chains to extract thread-level parallelism and to prepare the platform for

execution. CReAMS approach does not change the current development flow,

so well known application programming interfaces (e.g. OpenMP) can be used.

This way, the programmer can extract TLP in a friendly interface, since such

APIs are already coupled to a great number of compilers (e.g. gcc and icc), which makes the software development and the binary generation process easier than the aforementioned approaches.

- In contrast to ReMAPP and Thread Warping, CReAMS employs a coarse-grained reconfigurable fabric instead of a fine-grained one. Fine-grained architectures provide higher acceleration levels, but their scope is narrowed to applications that have few kernels responsible for a large part of the execution time. Coarse-grained reconfigurable architectures reduce the reconfiguration time and memory footprint due to the small context size, which increases its field of applications, because they are capable of accelerating the entire application.

- In contrast to ARM's big.LITTLE strategy, CReAMS does not waste energy rediscovering parallelism like a superscalar does, but rather redefine the data path on the fly for ILP exploitation with minimum energy dissipation.

# 3.2 Heterogeneous Systems

Most of the works on heterogeneous systems focus on efficient thread schedule, as the real gains in performance and power that these systems present are directly related to the correct assignment of jobs to the cores – as discussed later in section 5. Thus, we show the current work being made on scheduling in heterogeneous systems.

An early work on heterogeneous systems [10] shows that by simply applying the heterogeneity, one can reach significant energy savings with small overhead in performance and area. In this work, the authors have replicated a number of different Alpha processors and the threads are reallocated (by OS decision) accordingly to their necessities. This is a very simple approach and used only as a proof of concept, as only one core is active, so no TLP is exploited.

In [11] the authors propose an algorithm that is implemented directly in the scheduler of the OS. The algorithm uses some metrics to make dynamic scheduling decisions, biasing each thread to be allocated in the most compatible core. However, this approach needs to modify the OS kernel. Moreover, the OS needs to be aware of the resources of each core so it can correctly allocate the threads.

Metrics to decide which core a thread must be allocated to can also be applied in hardware, as in [12]. On that work, the authors use hardware counters to create a profile based

on ILP, MLP and the CPI stack for each thread. This profile is then used to determine whether a thread should be swapped to another core, a decision that is constantly made at small periods of time.

Heterogeneity can be exploited, also, in runtime, as proposed in [13]. On this work, the authors create an out-of-order multicore superscalar processor in which cores are able to polymorph themselves into in-order cores whenever determined to be performance/Watt efficient. Using this approach, many units in a core can be switched off (such as the reorder buffer, load/store queue, etc) at runtime, creating heterogeneity inside the core, which avoids the performance overhead created by thread swapping and reduces energy consumption. Nonetheless, this comes at the cost of leaving many resources of the processor turned off, wasting chip area.

None of these approaches, however, addresses heterogeneity using a reconfigurable organization. The heterogeneous CReAMS brings together all the advantages of the homogeneous version – which includes simultaneous TLP and ILP exploitation, binary compatibility and OS transparency – with the power and area efficiency provided by heterogeneity.

# 4. CUSTOM RECONFIGURABLE ARRAYS FOR MULTIPROCESSOR SYSTEMS

# 4.1 CReAMS

The Custom Reconfigurable Arrays for Multiprocessor Systems (CReAMS) is an architecture based on the DAP and was presented in [14]. It is, actually, an extension of the later created to exploit TLP through the replication of the number of DAPs in a system. In this way, the reconfigurable system can now support (and take advantage of) multithreaded applications.

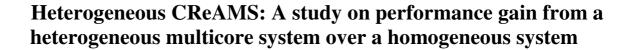

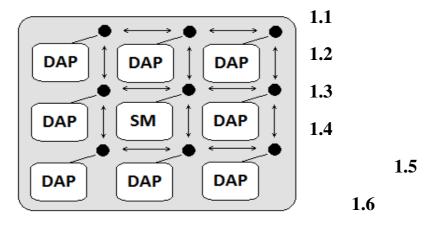

Figure 1 CReAMS of 8 cores (DAPs) and a L2 shared memory (SM)

The communication among the DAPs is done through a 2D-mesh Network on Chip (NoC) using a XY routing strategy. CReAMS also includes an on-chip unified L2 shared memory, illustrated as SM in the Figure 1. As in any multithreaded system, the communication between the cores produces an extra timing overhead. When a core needs to exchange information with another one or with the SM, the data must travel through the hops of the network, which can be just one (if the destination core/SM is just next to the origin) or many. The mean number of hops the data need to go through to reach the destination increases with the total number of cores the system has (as the network becomes bigger), so the higher the number of cores in a configuration, the higher the communication overhead will be. Thus, a communication model must be considered as well during the simulation of CReAMS.

The CReAMS system was originally created to be homogeneous between its cores, which means that all the DAPs on the configuration are exactly the same. They all have the same size in area, the same memory size (L1 cache size, reconfiguration memory table size, number of input and output context...) and the same functional units. This configuration represents the traditional approach to multicore systems – where the DAPs would be the generic cores – and it is simple to implement, as no special scheduling is necessary (a thread is simply allocated to the next free DAP). However, this is not the most efficient approach, whereas a low-duty thread will execute on the same environment as a heavy-duty one.

# 4.2 DAP - Dynamic Adaptive Processors

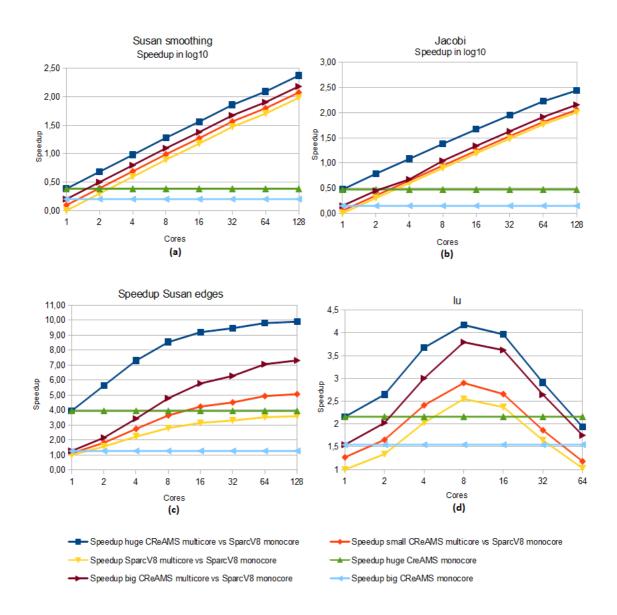

The DAP is a reconfigurable architecture tightly coupled to the processor and was presented in [15]. It is a transparent coarse-grained architecture – it is a reconfigurable datapath composed of functional units for word-level operations. To better explain the DAP, we divided it into four blocks, as shown in Figure 1(a).

Figure 2 (a) DAP blocks (b) Assembly of a loop (c) Allocation inside of reconfigurable datapath

# 4.2.1 Block 1 – Reconfigurable data path

Block 1 shows the structure for the reconfigurable data path. It is coarse-grained and tightly coupled to the processor's pipeline (there is no shared bus between them), which removes the necessity of external access to the memory and, consequently, saves power and reduces the reconfiguration time. As we can see in Figure 2(a), the data path is organized in a matrix structure, where the number of rows is the maximum number of instructions that can be executed in parallel. Independent instructions can be allocated on the same column. Therefore, the number of columns limits the ILP exploitation. Additionally, the number of columns dictates the maximum number of dependent instructions that can be executed in sequence in a configuration – the columns in one level are executed in sequence as a big combinational block. For example, the configuration in Figure 2 performs up to four arithmetic and logic operations, two memory accesses on cache and one multiplication at the same time, if all the data instructions are independent. As the critical path (the piece of combinational circuit that takes longer to produce a correct result) is the multiplier, it is possible to have other faster units in the

same level. In the above example, three arithmetic and logic units (ALUs) compose a level, while the multiplier and the memory access take the equivalent to one cycle of the processor. In other words, this configuration can execute twelve arithmetic and logic operations, two memory accesses and one multiplication on each level (within one clock cycle) at the very best case.

The entire structure of the reconfigurable data path is combinational, meaning that there is no temporal barrier (registers) between the functional units. The only registers present are at the entry point – the input context – and at the exit point – as temporary storage of the results. The feeding of the input context with the necessary data is the first step to configure the data path before starting the execution. The results are sent to the processor's register file on demand. It means that if any value is produced at any data path level (a cycle of the processor) and if it will not be changed in the next levels, this value can be written back on the next cycle. If the number of writes produced by the array is greater than the number of available write ports in the register file, than the excess instructions are forwarded to the next level. In the example shown in Figure 2(a), the maximum number of ports available is two.

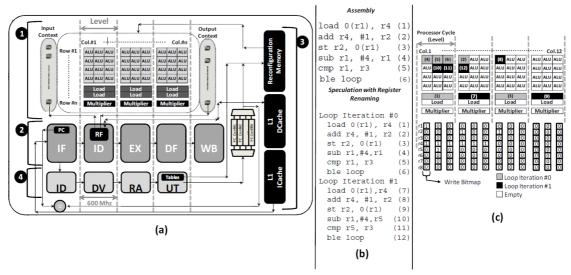

Figure 2 shows a simplified overview of the interconnection structure of the reconfigurable data path. Bus lines connect the input context with the functional units and the output context, while multiplexers are responsible for choosing the path this data will run. The input multiplexers – two for each functional unit – will decide which are going to be the input registers for a specific functional unit (in the Figure 3, an ALU). The output multiplexers, on the other hand, will select if the output will be provided directly from the input context registers or from a previous functional unit. The control signals for these multiplexers are stored on the reconfiguration cache.

Figure 3 Interconnection mechanism

# 4.2.2 Block 2 – Processor pipeline

Block 2 is the basic processor coupled to the array. It is also the reference for comparisons on the simulation performance. In this work, the baseline processor is a SparcV8-based architecture. Its five stage pipeline reflects a traditional RISC design (instruction fetch, decode, execution, data fetch and write back) and is similar to other RISC processors used in well-known embedded platforms (e.g. MIPS, ARM).

# 4.2.3 Block 3 – Storage components

There are two memory units specialized for the reconfiguration system: the address cache and the reconfiguration memory. The first holds the memory address of the first instruction of every configuration built by the dynamic detection hardware (explained later). This cache is implemented as a 4-way set associative table containing 64 entries (which means that the system can hold up to 64 configurations). An address cache hit indicates that a configuration was found, therefore this cache is used to verify the existence of a configuration and to point where it is stored on the reconfiguration memory.

The reconfiguration memory holds the bits for each configuration saved. Each bit is a control bit for the output and input multiplexers. They indicate which functional unit will be active and which register will be read as operators.

# 4.2.4 Block 4 – Dynamic detection hardware

The DDH is a binary translation mechanism that turns the instructions from SparcV8 ISA to reconfigurable array configurations. This block is responsible for instruction detection and allocation in the data path and it is implemented as a 4-stage pipelined circuit. The stages of the circuit are divided in Instruction Decode (ID), Dependence Verification (DP), Resource Allocation (RA) and Update Tables (UT). The translation process is performed as the processor executes the instruction (at the same time and independently), so there is no extra performance overhead, which means that it does not increase the processors critical path, leaving operating frequency unchanged.

For each column of the reconfiguration data path (Figure 2(a)), there is a bitmap responsible for storing in the target operands of the already allocated instructions in the

respective column, named as Write Bitmap (Figure 2(c)). Thus, for each incoming instruction, its source operands will be compared to the target operands in this bitmap to decide in which column this instruction will be allocated, according to data dependencies.

Figure 2(b) has an assembly code as an example. On Figure 2(c), the allocation of this code on the reconfigurable data path is shown. The first incoming instruction, a memory access, is allocated on the highest functional unit of the leftmost data path column. However, as in this case this type of operation takes an entire level (a processor cycle), the fourth bit of the write bitmap (representing the r4 register) of the columns 1, 2 and 3 are set to maintain the allocation consistency.

The dependency detection starts from the second instruction. In the example, the instruction number two reads the r4 register. As it is written by the previous instruction, a read after write (RAW) dependence is found. The DDH detects it (through the write bitmap) and allocates the instruction number two at the later column of instruction number one. The second bit of the fourth column of the write bitmap is set since this instruction has the register r2 as the target operand. The dependency analysis keeps these steps until instruction number five, where a loop is found.

The DDH supports speculation, so when the branch instruction is found, a speculation flag is set and the configuration continues the allocation of the following iterations. In other words, it is possible (if there is enough space on the array) to keep multiple iterations of a basic block on the same configuration. The instructions in black on Figure 2(c) represents the instructions allocated for the second iteration of the loop code of Figure 2(b).

This hardware is capable of performing register renaming, resolving false dependencies. In instruction number ten, the register r1 could be read by the incoming instruction in the second column, but could not write in this same register at this column. This is detected by the DDH and the register is renamed to r5 (the next empty register of the input context). All subsequent instructions that contain a reference to r1 are modified accordingly.

## 5. HETEROGENEOUS CREAMS

A heterogeneous version of CReAMS is a configuration where each DAP has a different number of functional units, input and output context length and memory size. This allows for some DAPs to be bigger than others (i.e.: some will be more efficient to execute threads that can exploit higher levels of instruction parallelism). Similarly, the smallest DAPs would be allocated to run jobs with low ILP.

For instance, in Figure 4(a) we illustrate two heterogeneous threads. The one in the left is bigger, meaning that it has larger basic blocks and has more potential for ILP exploitation. The one in the right is smaller, so its kernels are composed of groups of fewer instructions. On this case, both threads are being scheduled on cores that have large arrays. The processor will be able to execute both threads; however, the core that is receiving the smaller thread will not use most of its functional units on the reconfigurable datapath – as illustrated on Figure 4(b) – simply because the configurations this thread generates do not require all the resources available. This waste of resources also generates power leakage. Similarly, on Figure 5(a) we show an example where the same heterogeneous threads are executed in small cores. Again, the CReAMS processor will be able to run both threads, however – as illustrated in Figure 5(b)

Figure 4 (a) Heterogeneous threads running on big cores. (b) Parts of the array are wasted.

-, the DDH will have to split the kernels of the larger thread. As this thread has larger basic blocks, it will generate bigger configurations. The reconfigurable array, however, does not have enough resources to execute the configuration in one cycle, so they have to be split to fit the smaller array. This thread will need more cycles to finish, which means that it will take more time to execute and, consequently, will consume more power.

We aim to achieve a configuration like the one illustrated on Figure 6, where the larger threads are scheduled to bigger cores and smaller threads to smaller cores. This will lead to increased efficiency in processing heterogeneous applications.

Figure 5 (a) Heterogeneous threads running on small cores. (b) Bigger threads have to be split.

Figure 6 Heterogeneous threads running on heterogeneous cores

Figure 7 shows an example comparing an eight-core homogeneous CReAMS of medium cores with a quad-core heterogeneous CReAMS composed of two big cores, one medium and one small. On this illustration, both processors have the same area, as the large cores on the heterogeneous configuration compensate the area occupied by the extra medium cores on the homogeneous.

Figure 7 An eight-core homogeneous version of CReAMS and a quad-core heterogeneous version

This configuration, however, leads to some problems that need to be addressed carefully. For instance, how to determine the best sizes of DAPs to be used and the best combination – should we have many small sized DAPs or more big sized ones – that leads to better performance if compared to the homogeneous configuration.

# 6. METHODOLOGY

The first step of this work was to create many heterogeneous configurations and then choose the most suitable for testing. As the CReAMS simulator is already very generic when it comes to the resources configurations, no changes on it were necessary. The simulator works by emulating each DAP, using configurations that are passed as parameters. Then, it compiles the information (e.g. cycles taken, cache access) of each core and outputs a result file. Therefore, at first, to simulate heterogeneous configurations we only needed to create them and forward them to the simulator accordingly. Later on, a modification was made to simulate a dynamic scheduler as well. This scheduler is important to allocate the threads accordingly to their ILP requirements.

To create the configurations, a spreadsheet was used. This spreadsheet is part of the CReAMS project and it contains the area occupied for each of the CReAMS components. It

allows the user to vary the number of functional units on the datapath, the dimensions of the array and the input context length and receive the expected area occupied by this configuration – considering the number of cores as well. This spreadsheet was also modified to be able to vary the size of the reconfiguration cache – giving how many configurations the cache can hold –, a resource needed to create finer area parity combinations, as we will discuss later.

The latter tools discussed were already developed and from now on we show what was added on the process through this work. The next step was to create many scripts to run automatically the simulations. Each configuration needs a script for each application and number of cores. Thus, if there is a combination of five applications with five number of cores, each configuration needs a total of 25 scripts. Furthermore, to run all these jobs automatically, another script was created to iterate over the number of cores and call all the necessary simulations.

The second phase of tests was focused on two points: to compare versions of heterogeneous CReAMS that would be smaller than the homogeneous configurations; and to insert a dynamic scheduler, so we could analyze the impact of intelligent allocation on performance

The former is easily achieved by creating new heterogeneous and homogeneous configurations. The CReAMS simulator, also, already supported dynamic scheduling, so the only need was to create new simulation scripts with the correct parameters.

Figure 8 shows the steps from the creation of each configuration to the analysis of the results. On step (A), we use the spreadsheet that calculates the area of a CReAMS system to create the many configurations of same area. Step (B) uses each of these configurations to create many scripts for the selected applications, which are then simulated on step (C). The results of all the simulations are then compiled in a single file in step (D). Finally, we compare the configurations that have same area and format this data in a chart, for analysis.

Figure 8 Methodology in steps. (A) Configurations creation thought area spreadsheet. (B) Scripts for simulation of each configuration. (C) Simulation of scripts. (D) Compilation of results. (E)

Comparison and chart anylisis.

### **6.1 Simulation environment**

This work has used the Simics simulator [16], an instruction level simulator. Simics uses an environment, which is a set of configurations to specify the characteristics of the hardware and the software of the simulated system, to extract the instructions executed by a specific processor. For this work, we have used an environment with a Linux Ubuntu operating system running over a single SparcV8 processor. The benchmarks used were created using OpenMP and Pthreads, thus the number of threads spawned at run-time are user arbitrary, even if the system uses a single processor.

Simics produces a sequencial trace of instructions and data accesses for all threads. As they are all mixed by the simulator, special instructions marks were added to indicate where each thread trace starts and ends. The trace generated by Simics is then sent to a python script, named as Splitter. This script recognizes the instruction marks and splits the trace file, generating many new files, one for each running thread of the application.

Mkfifo is a UNIX process that manages automatically a first-in-first-out (FIFO) behavior. The Simics simulator and the Splitter communicate in a producer-consumer way, so this FIFO process was inserted to control such communication. The split files created by the Splitter are also mkfifo processes, as they communicate with the DAPs in a producer-consumer behavior as well.

For each thread that was created, an instance of a DAP simulator is used (in this case, a CReAMS simulator). Each DAP consumes the instructions sent by the Splitter and produces a file with results for performance, communication among threads and energy consumption. The Backward process is activated at the end of the simulation. It compiles the results that are generated for each thread in a single file, providing the results of the whole application simulation.

As the simulations are usually made for many core variations (from 4 to 64 cores) and each of them outputs results for the best and worst case of communication, a final python script is executed to merge all the results. It receives the name of the application and a code to identify the simulation batch as parameters. With this information, the script recursively searches for all the results of this batch and compiles a single, CSV formatted, file that can be easily imported to a spreadsheet software.

## **6.2 Benchmarks**

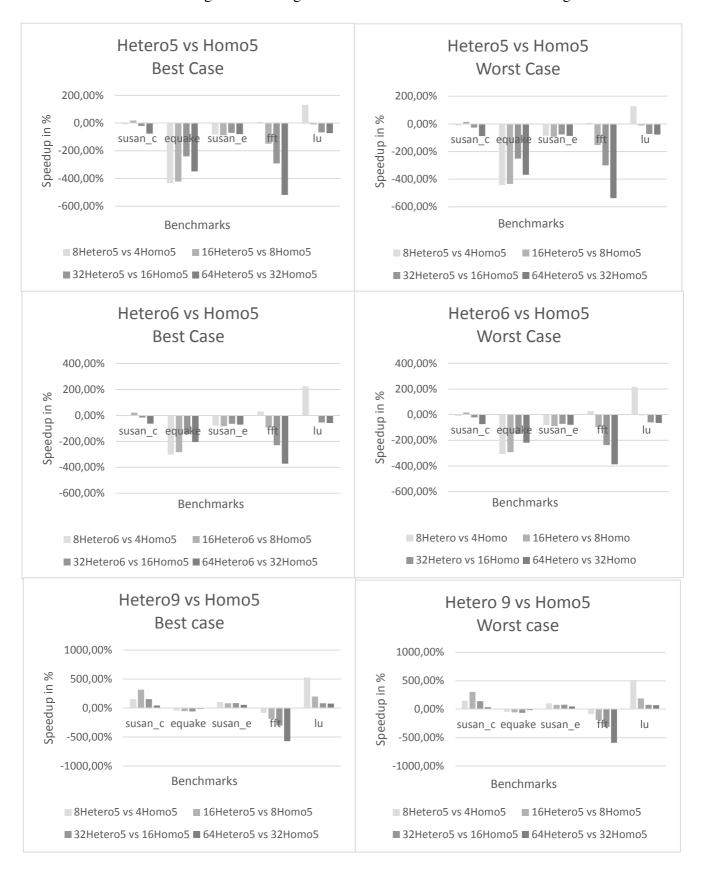

In order to measure the performance of CReAMS, benchmarks from different suites were selected to cover a wide range of behaviors in terms of type (i.e. TLP and ILP) and degree of existing parallelism. The five benchmarks chosen were *lu* and *fft* from parallel suites [17] [18], *equake* from the SPEC OMPM2001 [19] package and *susan edges* and *susan corners* from the MiBench suite [20]. In [1] a study was made to characterize the potential of these applications on obtaining performance improvements when TLP or ILP exploitation is applied. The mean basic block size gives us some clues about the limits of ILP that the selected application may provide. In addition, the percentage of the entire application code that is executed in parallel, when multithreaded application environment is considered, is an important metric to obtain the upper bound for TLP exploitation in the applications. This metric is also called load balancing and it gives the TLP potential for the application: the more an application can distribute its work through its threads, the more it will be able to take advantage of a multicore system. Table 1 shows the results of this study.

FFT is not shown on the table study, however, as will be discussed later, the results suggests that it has good load balancing, as for the homogeneous simulations, it has gradually improved performance with the increase of cores.

| Table 1 Load balancing a | d mean basic block | size of selected | applications |

|--------------------------|--------------------|------------------|--------------|

| Tuest I Bear customers   | <del> </del>       |                  | opprione on  |

| Benchmark | Mean BB      | ·     | Load Balancing | (%) in threads |       |

|-----------|--------------|-------|----------------|----------------|-------|

| Dencimark | Size(#instr) | 4     | 8              | 16             | 64    |

| equake    | 4,80         | 18,49 | 10,32          | 5,10           | 0,92  |

| susan_e   | 16,60        | 39,80 | 24,90          | 4,80           | 0,90  |

| susan_c   | 17,36        | 67,58 | 49,18          | 34,94          | 12,50 |

| lu        | 8,32         | 82,20 | 56,77          | 29,35          | 7,03  |

Table 1 shows that equake is a benchmark with small basic blocks, meaning that ILP is poorly exploited on this application. Moreover, it has also a very poor load balancing between threads, which worsens each time the number of cores is increased. That also suggests that equake is not a TLP oriented application. Overall, poor or none advantages are expected when running equake on a system that focus on ILP and TLP exploitation.

Similarly, lu has small basic blocks but good load balancing when the number of cores is small. Susan edges and susan corners have both big basic blocks, however susan corners has a better load balancing, meaning that we should see it performing better on configurations that have more cores. Susan edges, however, should perform better on systems with more resources on the arrays – consequently, which have less cores, as we work with area parity.

### **6.3 Communication overhead**

As any multicore system, the cores of CReAMS must communicate between themselves to perform synchronization. In section 4.1 we have discussed that the communication between the DAPs are done through a NoC using the XY strategy, which introduces an overhead each time the cores have to change information. This overhead depends on the size of the mesh (which is directly dependent on the number of cores) and the distance between cores, i.e., the number of router the information must go through between origin and destination.

In [1] a model for the corner cases of communication in CReAMS is proposed. It consider the best and worst cases of communication overhead, being the best case when the traffic of data is uniformly distributed among the NoC nodes and the worst when data is concentrated in a specific node. This is the average number of hops and the model calculates it as follows:

Distributed

$$\begin{cases} AvgHops = \frac{2h}{3}, h \ even \\ AvgHops = 2\left(\frac{h}{3} - \frac{1}{3h}\right), h \ odd \end{cases}$$

Centralized

$$AvgHops = \frac{k^2}{k+1}$$

where  $h = \sqrt{N}$

Table 2 shows the number of hops for a single communications process considering the formulas presented above.

Table 2 Average number of hops for cores

|             | 4 Cores | 8 Cores | 16 Cores | 32 Cores | 64 Cores |

|-------------|---------|---------|----------|----------|----------|

| Distributed | 1.33    | 1.88    | 2.66     | 3.77     | 5.33     |

| Centralized | 1.33    | 2.09    | 3.20     | 4.81     | 7.11     |

## 6.4 Dynamic Scheduler

On the first extracted results, the simulator used a static scheduler for the DAPs, meaning that once a thread starts running in a core, it will end its execution on the same core. Dynamically scheduling threads to work on the most efficient cores have been proved to be one

of the main advantages of heterogeneous systems [21]. Thus, for the second phase of simulations, a dynamic thread scheduler (proposed on [1]) was applied.

This scheduler keeps instruction counters for each thread on the reconfiguration memory and based on this data, it changes the threads to the cores that most suits their needs. Thus, threads that contain more instructions on their configurations will be allocated to cores that have more resources, while threads that have small load will be sent to cores with small arrays. The main goal of this algorithm is not to employ the best scheduling possible, but to verify if performance losses provided by the heterogeneous CReAMS in some applications are due to wrong thread scheduling.

### 7. RESULTS

In this section, we will present the results obtained by this work. We start with all the heterogeneous and homogeneous configurations that were created. Then, we show the ones that were chosen to be simulated. Finally, we present the results of the simulations, both with and without a scheduling mechanism.

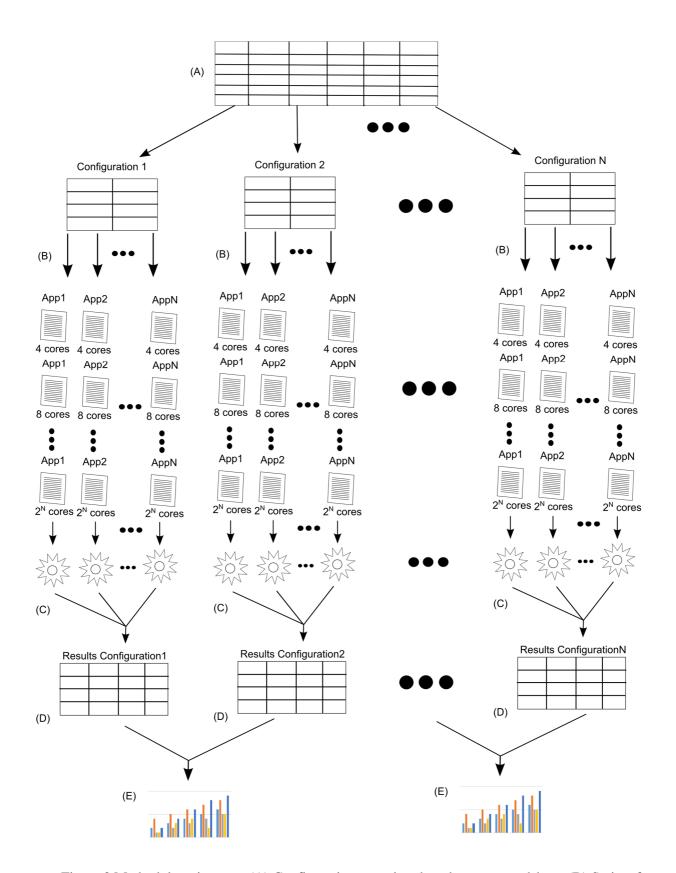

## 7.1 The configurations created

To create new configurations of CReAMS, one can change the resources on the array, the input context size or the length of the reconfiguration memory. However, these characteristics are also connected. If the array is greatly expanded, but the input context stays short, just a few registers will be able to be addressed by the array at each cycle, so the system will take many cycles to fill the context. Moreover, if the reconfigurable cache is not expanded as well, the system will not be able to hold big configurations, in other words, the array will not be fully used during a reconfiguration process. Thus, to select the best configurations, we had to consider a good balance between these characteristics of the system, as we will discuss later.

A great number of configurations were created considering area parity. We started creating configurations that would have parity with a certain number of SparcV8 processors (the basic processor of CReAMS) and then combine these cores to compare them with homogenous versions of CReAMS. This strategy lead to 15 configurations of small cores arrays, 22 configurations of medium cores and other 22 of large cores, shown in tables 3, 4 and 5. Combined over, we could use 15x44 variations to create configurations using to sizes of core and 15x22x22 to create configurations with the three sizes. This would lead to almost 8000

configurations to simulate. Furthermore, ours simulations were made on five benchmarks (discussed later) from with five different core sizes, so for each configuration, a total of 25 simulations were needed. As some of the benchmarks can take several hours to execute, the simulation of all the configurations created was not practicable and just a few of them were selected.

Table 3 Configurations of small cores

| <b>Small Core</b> | SC1 | SC2 | SC3 | SC4 | SC5 | SC6 | SC7 | SC8 | SC9 | SC10 | SC11 | SC12 | SC13 | SC14 | SC15 |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|

| Lines             | 9   | 9   | 9   | 9   | 9   | 9   | 9   | 9   | 9   | 9    | 9    | 9    | 9    | 9    | 9    |

| ALU               | 4   | 2   | 1   | 2   | 3   | 8   | 3   | 2   | 4   | 6    | 10   | 4    | 2    | 5    | 8    |

| Load/Store        | 1   | 7   | 2   | 2   | 2   | 4   | 12  | 5   | 3   | 4    | 4    | 16   | 6    | 5    | 6    |

| Multiplier        | 1   | 1   | 6   | 2   | 1   | 1   | 3   | 9   | 3   | 2    | 2    | 4    | 12   | 5    | 4    |

| Input Context     | 4   | 6   | 4   | 10  | 8   | 8   | 12  | 12  | 20  | 12   | 16   | 16   | 16   | 24   | 16   |

| Sparcs (Parity)   | 2   | 2   | 2   | 2   | 2   | 3   | 3   | 3   | 3   | 3    | 4    | 4    | 4    | 4    | 4    |

Table 4 Configurations of medium cores

| <b>Medium Cores</b> | MC1  | MC2                | MC3     | MC4          | MC5          | MC6               | MC7  | MC8     | MC9           | MC10         | MC11               |

|---------------------|------|--------------------|---------|--------------|--------------|-------------------|------|---------|---------------|--------------|--------------------|

| Lines               | 15   | 15                 | 15      | 15           | 15           | 15                | 15   | 15      | 15            | 15           | 15                 |

| ALU                 | 2    | 1                  | 4       | 3            | 1            | 2                 | 4    | 7       | 3             | 1            | 3                  |

| Load/Store          | 1    | 2                  | 2       | 8            | 3            | 2                 | 3    | 3       | 10            | 4            | 2                  |

| Multiplier          | 1    | 2                  | 1       | 1            | 6            | 2                 | 1    | 1       | 3             | 10           | 2                  |

| Input Context       | 15   | 15                 | 15      | 15           | 15           | 28                | 15   | 15      | 15            | 15           | 28                 |

| Parity              | 2    | 2                  | 3       | 3            | 3            | 3                 | 3    | 4       | 4             | 4            | 4                  |

|                     |      |                    |         |              |              |                   |      |         |               |              |                    |

| ,                   | MC12 | MC13               | MC14    | MC15         | MC16         | MC17              | MC18 | MC19    | MC20          | MC21         | MC22               |

|                     | MC12 |                    |         |              |              |                   |      | MC19    | MC20<br>15    | MC21         | MC22               |

|                     |      |                    |         |              |              |                   |      |         |               |              |                    |

|                     | 15   | 15                 |         |              | 15           |                   | 15   |         |               |              | 15                 |

|                     | 15   | 15                 | 15<br>6 | 15<br>2      | 15           |                   | 15   | 15<br>5 | 15<br>2       | 15<br>5<br>5 | 15                 |

|                     | 15   | 15<br>12<br>6<br>4 | 15<br>6 | 15<br>2<br>8 | 15<br>4<br>4 | 15<br>8<br>6<br>4 | 15   | 15<br>5 | 15<br>2<br>10 | 15<br>5<br>5 | 15<br>10<br>8<br>4 |

Table 5 Configurations of big cores

| <b>Big Cores</b> | BC1          | BC2                | BC3           | BC4                | BC5          | BC6               | BC7         | BC8  | BC9          | <b>BC10</b> | BC11               |

|------------------|--------------|--------------------|---------------|--------------------|--------------|-------------------|-------------|------|--------------|-------------|--------------------|

| Lines            | 24           | 24                 | 24            | 24                 | 24           | 24                | 24          | 24   | 24           | 24          | 24                 |

| ALU              | 2            | 1                  | 5             | 2                  | 1            | 2                 | 4           | 8    | 2            | 2           | 3                  |

| Load/Store       | 1            | 2                  | 1             | 6                  | 3            | 2                 | 3           | 2    | 12           | 4           | 3                  |

| Multiplier       | 1            | 2                  | 1             | 2                  | 6            | 2                 | 1           | 1    | 2            | 8           | 3                  |

| Input Context    | 24           | 24                 | 24            | 24                 | 24           | 42                | 24          | 24   | 24           | 24          | 42                 |

| Parity           | 4            | 4                  | 6             | 6                  | 6            | 6                 | 6           | 8    | 8            | 8           | 8                  |

|                  |              |                    |               |                    |              |                   |             |      |              |             |                    |

|                  | BC12         | BC13               | <b>BC14</b>   | BC15               | <b>BC16</b>  | <b>BC17</b>       | <b>BC18</b> | BC19 | <b>BC20</b>  | BC21        | BC22               |

|                  | BC12<br>24   |                    |               |                    |              |                   |             |      | BC20<br>24   |             |                    |

|                  |              | 24                 | 24            |                    |              |                   |             | 24   |              |             |                    |

|                  | 24           | 24                 | 24            | 24                 |              | 24                | 24          | 24   | 24           |             |                    |

|                  | 24           | 24                 | 24            | 24                 |              | 24<br>8           | 24          | 24   | 24           |             |                    |

|                  | 24<br>6<br>4 | 24<br>10<br>4<br>1 | 24<br>3<br>16 | 24<br>1<br>4<br>14 | 24<br>4<br>4 | 24<br>8<br>6<br>3 | 24          | 24   | 24<br>1<br>8 |             | 24<br>11<br>9<br>4 |

We have analyzed and selected the best configurations on the three tables to create a few heterogeneous versions of CReAMS. To select these configurations, we have considered those which had a good balance between the functional units. For instance, SC3 in Table 1 has many multipliers and just a few ALUs and memory access units. It is well known that most programs use more ALU operations than multiplications, furthermore, the lack of load/store units can highly compromise the performance of an application, as each time those units fully occupied, the reconfiguration datapath will need to wait for the next cycle to execute them. On the other hand, SC7 has too many load/store units, which will probably be wasted and just occupy a great amount of area, as most of the applications do not need to access memory so often [20].

The final heterogeneous configurations tested were based on a small core version (SC6), a medium core (MC7), and a big core (BC7). Those configurations have a good balance between their functional units and input context length. From these, we have created other three version of heterogeneous cores. One of them with 50% of big cores, 25% of medium cores and 25% of small cores (called Hetero1), another with 25% of big cores, 50% of medium cores and 25% of small cores (the Hetero2) and the last one with 25% of big cores, 25% of medium cores and 50% of small cores (the Hetero3). For instance, a 4-core version of Hetero1 would have two big cores, one medium core and one small core, while the Hetero2 would have one big, two medium and one small. Those three configuration allowed us to analyze the impact of the sizes of the cores over the applications.

Homogeneous versions of CReAMS were also simulated, so we could compare the results. However, these results were already done on the first part of this project (see

APPENDIX A), hence they were reused. Nonetheless, for convenience, we show these configurations on Table 7. Homo1 is a small version of CReAMS – if compared with the size of the cores on the heterogeneous versions, it would be classified as small – while the Homo2 is a medium version.

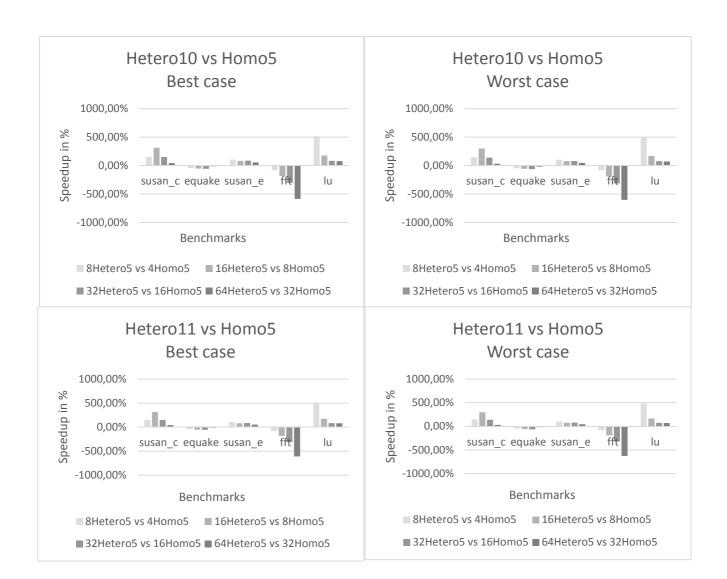

For the second phase, which we inserted the scheduler in the simulations, we have created three new homogeneous configurations of CReAMS focusing on having more size variation on the cores. These configurations are listed on Table 6.

Similarly, we have created five new heterogeneous (Hetero 4, 5, 6, 7 and 8) configurations and re simulated the same heterogeneous versions from the first phase (Hetero 9, 10 and 11), but now with the scheduler. We wanted to analyze the behavior of these configurations and what changed when the scheduler was inserted. These versions are shown in Table 8 and Table 9. These were fine adjusted to have similar area if compared with the homogeneous versions of Table 6. On the bigger cores, we have increased and decreased the size of the reconfiguration cache, because theses cores already have enough functional units to exploit ILP and increasing them even further would not result in great performance increase (as shown on the first part of this work, in APPENDIX A). However, medium and smaller cores still have room for ILP exploitation, so we have fine adjusted their functional units.

In Table 6 the line "Total Sparcs" represents the number of SparcV8 processors that would fit (that have the same area as) one core of the homogeneous configuration. In Table 8 and Table 9 the line "Total 4Core Configuration Sparc" represents the number of SparcV8 processors that would fit a 4-Core version of the heterogeneous configuration. These numbers are used as basis for our area parity.

Table 7 Homogeneous configurations

| Configuration | Lines | ALU | Load/Store | Multipliers | <b>Input Context</b> |

|---------------|-------|-----|------------|-------------|----------------------|

| Homo1         | 9     | 3   | 1          | 2           | 8                    |

| Homo2         | 15    | 4   | 4          | 2           | 16                   |

Table 6 New homogeneous configurations

| Homogeneous  |        |  |              |        |  |              |         |  |  |  |

|--------------|--------|--|--------------|--------|--|--------------|---------|--|--|--|

| Name         | Homo3  |  | Name         | Homo4  |  | Name         | Homo5   |  |  |  |

| Total Sparcs | 2      |  | Total Sparcs | 4      |  | Total Sparcs | 8       |  |  |  |

| Lines        | 6      |  | Lines        | 15     |  | Lines        | 21      |  |  |  |

| ALUs         | 4      |  | ALUs         | 5      |  | ALUs         | 6       |  |  |  |

| Load/Stores  | 3      |  | Load/Stores  | 4      |  | Load/Stores  | 5       |  |  |  |

| Muls         | 2      |  | Muls         | 2      |  | Muls         | 4       |  |  |  |

| Input C.     | 8      |  | Input C.     | 16     |  | Input C.     | 24      |  |  |  |

| Cache Rec    | 32conf |  | Cache Rec    | 64conf |  | Cache Rec    | 128conf |  |  |  |

Table 8 New heterogeneous configurations (4-7)

|                                      |          | He           | tero4       |                         |            |

|--------------------------------------|----------|--------------|-------------|-------------------------|------------|

| Subname                              | BigCores | Subname      | MedCores    | Subname                 | SmallCores |

| Proportion                           | 50%      | Proportion   | 25%         | Proportion              | 25%        |

| Total Sparcs                         | 12       | Total Sparcs | 6           | Total Sparcs            | 25/0       |

| Lines                                | 27       | Lines        | 15          | Lines                   | 6          |

| ALUs                                 | 7        | ALUs         | 8           | ALUs                    | 3          |

| Load/Stores                          | 5        | Load/Stores  | 5           | Load/Stores             | 2          |

| Muls                                 | 4        | Muls         | 4           | Muls                    | 1          |

| Input C.                             | 28       | Input C.     | 16          | Input C.                | 8          |

| Cache Rec                            | 128conf  | Cache Rec    | 64conf      | Cache Rec               | 32conf     |

| Total 4Core Configuration Sparcs:    |          |              |             |                         |            |

|                                      |          | Не           | tero5       | c configuration spares. | 32         |

| Subname                              | BigCores | Subname      | MedCores    | Subname                 | SmallCores |

| Proportion                           | 25%      | Proportion   | 50%         | Proportion              | 25%        |

| Total Sparcs                         | 6        | Total Sparcs | 4           | Total Sparcs            | 2          |

| Lines                                | 21       | Lines        | 15          | Lines                   | 6          |

| ALUs                                 | 5        | ALUs         | 5           | ALUs                    | 4          |

| Load/Stores                          | 4        | Load/Stores  | 4           | Load/Stores             | 3          |

| Muls                                 | 2        | Muls         | 2           | Muls                    | 2          |

| Input C.                             | 24       | Input C.     | 16          | Input C.                | 8          |

| Cache Rec                            | 64conf   | Cache Rec    | 64conf      | Cache Rec               | 32conf     |

|                                      |          | •            | Total 4Core | e Configuration Sparcs: | 16         |

| Hetero6                              |          |              |             |                         |            |

| Subname                              | BigCores | Subname      | MedCores    | Subname                 | SmallCores |

| Proportion                           | 25%      | Proportion   | 25%         | Proportion              | 50%        |

| Total Sparcs                         | 8        | Total Sparcs | 4           | Total Sparcs            | 2          |

| Lines                                | 21       | Lines        | 15          | Lines                   | 6          |

| ALUs                                 | 6        | ALUs         | 5           | ALUs                    | 4          |

| Load/Stores                          | 5        | Load/Stores  | 4           | Load/Stores             | 3          |

| Muls                                 | 4        | Muls         | 2           | Muls                    | 2          |

| Input C.                             | 24       | Input C.     | 16          | Input C.                | 8          |

| Cache Rec                            | 128conf  | Cache Rec    | 64conf      | Cache Rec               | 32conf     |

| Total 4Core Configuration Sparcs:    |          |              |             |                         | 16         |

| Hetero7                              |          |              |             |                         |            |

| Subname                              | BigCores | Subname      | MedCores    | Subname                 | SmallCores |

| Proportion                           | 25%      | Proportion   | 50%         | Proportion              | 25%        |

| Total Sparcs                         | 14       | Total Sparcs | 7           | Total Sparcs            | 4          |

| Lines                                | 21       | Lines        | 15          | Lines                   | 6          |

| ALUs                                 | 9        | ALUs         | 9           | ALUs                    | 10         |

| Load/Stores                          | 7        | Load/Stores  | 7           | Load/Stores             | 8          |

| Muls                                 | 5        | Muls         | 4           | Muls                    | 5          |

| Input C.                             | 32       | Input C.     | 20          | Input C.                | 16         |

| Cache Rec                            | 128conf  | Cache Rec    | 64conf      | Cache Rec               | 32conf     |

| Total 4Core Configuration Sparcs: 32 |          |              |             |                         |            |

Table 9 New heterogeneous configurations (8-11)

| Hetero8                                      |          |                     |           |                         |            |  |  |  |  |

|----------------------------------------------|----------|---------------------|-----------|-------------------------|------------|--|--|--|--|

| Subname                                      | BigCores | Subname             | MedCores  | Subname                 | SmallCores |  |  |  |  |

| Proportion                                   | 25%      | Proportion          | 25%       | Proportion              | 50%        |  |  |  |  |

| Total Sparcs                                 | 16       | Total Sparcs        | 8         | Total Sparcs            | 30%        |  |  |  |  |

| Lines                                        | 21       | Lines               | 15        | Lines                   | 6          |  |  |  |  |

| ALUs                                         | 10       | ALUs                | 10        | ALUs                    | 10         |  |  |  |  |

| Load/Stores                                  | 8        | Load/Stores         | 8         | Load/Stores             | 8          |  |  |  |  |

| Muls                                         | 6        | Muls                | 5         | Muls                    | 5          |  |  |  |  |

| Input C.                                     | 32       | Input C.            | 20        | Input C.                | 16         |  |  |  |  |

| Cache Rec                                    | 128conf  | Cache Rec           | 64conf    | Cache Rec               | 32conf     |  |  |  |  |

| Cacile Rec                                   | 12800111 | Cacile Rec          |           |                         |            |  |  |  |  |

| Total 4Core Configuration Sparcs: 32 Hetero9 |          |                     |           |                         |            |  |  |  |  |

| Subname                                      | BigCores | Subname             | MedCores  | Subname                 | SmallCores |  |  |  |  |

| Proportion                                   | 50%      | Proportion          | 25%       | Proportion              | 25%        |  |  |  |  |

| Total Sparcs                                 | 6        | Total Sparcs        | 3         | Total Sparcs            | 23/0       |  |  |  |  |

| Lines                                        | 24       | Lines               | 15        | Lines                   | 9          |  |  |  |  |

|                                              | 4        |                     | 13        |                         | 3          |  |  |  |  |

| ALUs<br>Load/Stores                          |          | ALUs<br>Load/Stores | 4         | ALUs<br>Load/Stores     | 2          |  |  |  |  |

| -                                            | 3        | Muls                | 3         |                         |            |  |  |  |  |

| Muls                                         | 24       |                     | 12        | Muls                    | 1          |  |  |  |  |

| Input C.                                     |          | Input C.            | 12        | Input C.                | 8          |  |  |  |  |

| Cache Rec                                    | 128conf  | Cache Rec           | 64conf    | Cache Rec               | 32conf     |  |  |  |  |

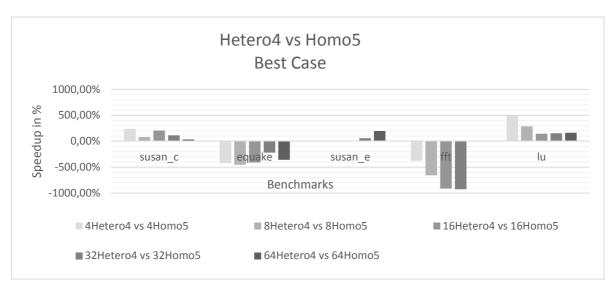

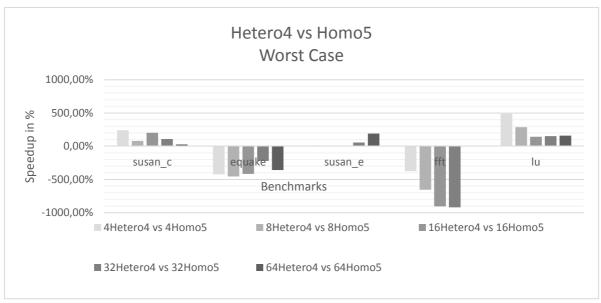

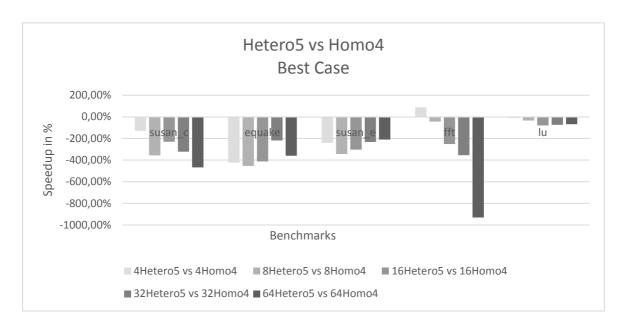

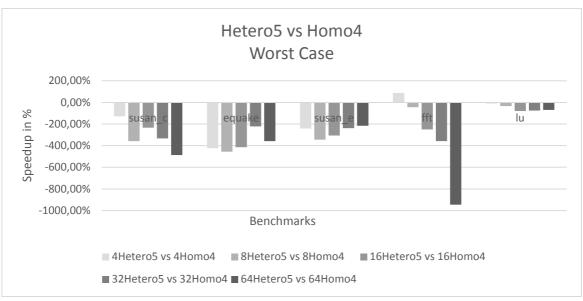

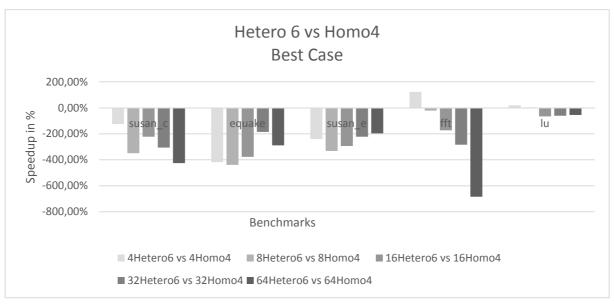

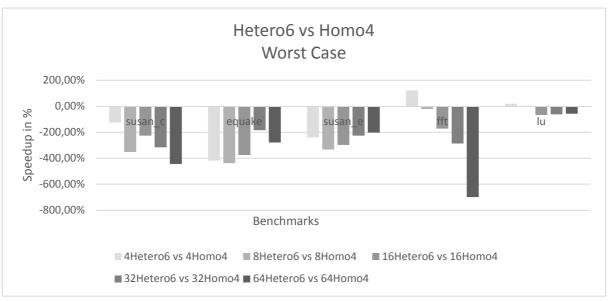

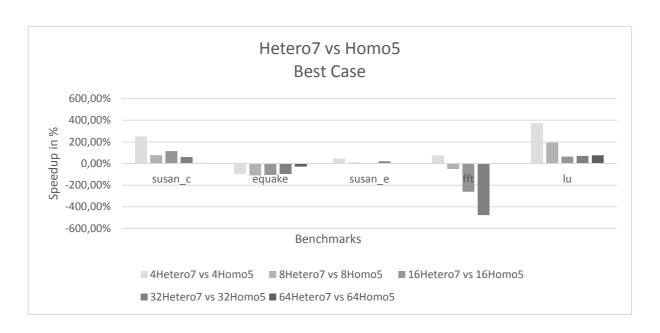

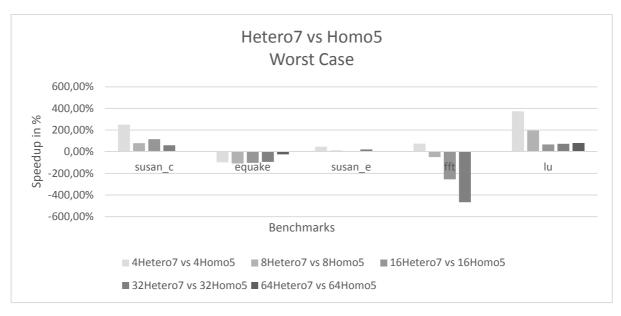

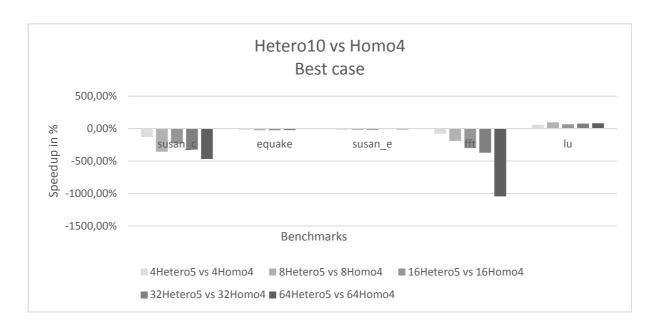

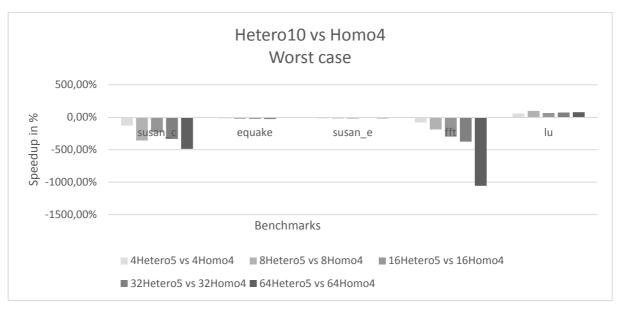

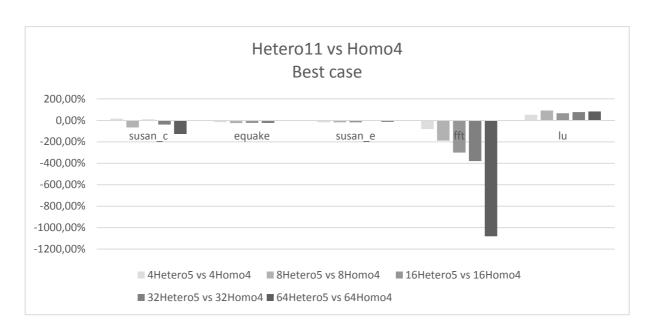

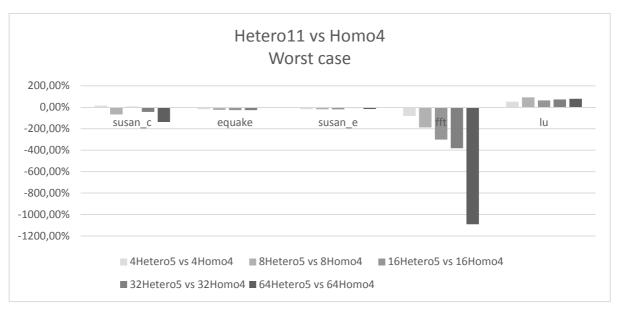

|                                              |          | l let               | ero10     | e Configuration Sparcs: | 17         |  |  |  |  |