## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

## PAULO CÉSAR COMASSETTO DE AGUIRRE

PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO APLICADOS À CONVERSÃO AD

### PAULO CÉSAR COMASSETTO DE AGUIRRE

## PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO APLICADOS À CONVERSÃO AD

Dissertação de mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica, da Universidade Federal do Rio Grande do Sul, como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica.

Área de concentração: Engenharia de Computação - Micro e Nano Eletrônica

ORIENTADOR: Altamiro Amadeu Susin

CO-ORIENTADOR: Hamilton Duarte Klimach

## PAULO CÉSAR COMASSETTO DE AGUIRRE

## PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO APLICADOS À CONVERSÃO AD

Esta dissertação foi julgada adequada para a obtenção do título de Mestre em Engenharia Elétrica e aprovada em sua forma final pelo Orientador e pela Banca Examinadora.

|            | Orientador:                                                                |

|------------|----------------------------------------------------------------------------|

|            | Prof. Dr. Altamiro Amadeu Susin, UFRGS                                     |

|            | Doutor pela Institut National Polytechnique de Grenoble -                  |

|            | Grenoble, França                                                           |

|            |                                                                            |

| Banca Exan | ninadora:                                                                  |

|            |                                                                            |

| Pro        | of. Dr. Alexandre Balbinot, UFRGS                                          |

| Do         | utor pela Universidade Federal do Rio Grande do Sul – Porto Alegre, Brasil |

| Pro        | of. Dr. Cesar Augusto Prior, UFSM                                          |

| Do         | utor pela Universidade Federal de Santa Maria – Santa Maria, Brasil        |

| Pro        | of. Dr. Tiago Roberto Balen, UFRGS                                         |

| Do         | utor pela Universidade Federal do Rio Grande do Sul – Porto Alegre, Brasil |

|            |                                                                            |

|            | Coordenador do PPGEE:                                                      |

|            | Prof. Dr. Alexandre Sanfelice Bazanella                                    |

|            | i 101. Di. Aicadiule Salliellee Dazallella                                 |

# **DEDICATÓRIA**

Dedico este trabalho aos meus pais, Maria Zenir e David, a minha irmã, Mariana, a minha noiva, Natalia, e a minha avó, Elsa (*in memoriam*), pelo amor e constante incentivo.

#### **AGRADECIMENTOS**

Aos meus pais, Maria Zenir Comassetto de Aguirre e David Oliveira de Aguirre, a minha irmã, Mariana Comassetto de Aguirre, pela imensa confiança, apoio e principalmente pelo incentivo nas horas de fraqueza.

A minha amada noiva e melhor amiga, Natalia Braun Chagas, pelo carinho, amor, compreensão e suporte técnico nesta etapa da minha vida.

Aos colegas de mestrado Thiago, Ricardo, Alan, Catalina, Alisson, Fábio e Cristiano, pelo convívio harmonioso e amizade dentro e fora do laboratório.

Ao Professor Altamiro Susin, pelos ensinamentos, amizade, confiança e orientação prestada durante a execução deste trabalho.

Ao Professor Hamilton Klimach, pela amizade, co-orientação e troca de conhecimentos durante o desenvolvimento deste trabalho.

Ao professor Sergio Bampi, pela colaboração e acesso à MOSIS, o que tornou possível a fabricação do circuito projetado.

Ao Professor Cesar Prior pela grande colaboração e sugestões prestadas no desenvolvimento deste trabalho.

Aos amigos Crístian Müller e Edinei Santin pela amizade e trocas de conhecimento que foram essenciais para o desenvolvimento deste trabalho.

Aos colegas do LAB110 Filipe, Oscar, Arthur, Moacir e Dalton pela troca de conhecimentos e suporte durante a realização prática deste trabalho.

Aos meus demais amigos e colegas pela amizade e horas de alegria.

A Deus.

### **RESUMO**

Conversores analógico-digitais (ADCs) têm papel fundamental na implementação dos sistemas-em-chip, do inglês System-on-Chip (SoC), atuais. Em razão dos requisitos destes sistemas e dos compromissos entre as características fundamentais dos ADCs, como largura de banda, consumo de energia e exatidão, diversas topologias e estratégias para sua implementação em circuitos integrados (CIs) têm sido desenvolvidas através dos tempos. Dentre estas topologias, os conversores sigma-delta (SDC) têm se destacado pela versatilidade, aliada ao baixo consumo e excelente exatidão. Inicialmente desenvolvidos e empregados para a conversão de sinais de baixa frequência e com operação em tempo discreto (DT), esta classe de conversores têm evoluído e nos últimos anos está sendo desenvolvida para operar em tempo contínuo e ser empregada na conversão de sinais com frequências de centenas de kHz a dezenas de MHz. Neste trabalho, os moduladores sigma-delta em tempo contínuo (SDMs-CT) são estudados, visando sua aplicação à conversão analógico-digital (AD). Os SDMs-CT oferecem vantagens significativas sobre seus homólogos em tempo discreto, como menor consumo de energia, maior largura de banda do sinal de entrada e filtro anti-alias, do inglês anti-alias filter (AAF), implícito. Entretanto, os SDMs-CT apresentam limitações adicionais, responsáveis pela degradação de seu desempenho, como os efeitos do jitter do sinal de relógio, o atraso excessivo do laço de realimentação, do inglês Excess Loop Delay (ELD), e as limitações impostas aos integradores analógicos. Após o estudo e análise de SDMs-CT e de suas limitações, foi desenvolvido um modelo comportamental no ambiente Matlab/Simulink®, que permite a simulação do impacto destas limitações no modulador, possibilitando a obtenção de uma estimativa mais aproximada do seu desempenho. Com base nestas simulações foi possível a determinação das especificações mínimas de cada bloco analógico que compõe o modulador (como o slew rate, a frequência de ganho unitário  $(f_u)$  e o ganho DC dos amplificadores operacionais utilizados nos integradores) e os valores toleráveis de ELD e jitter do sinal de relógio. Adicionalmente, neste trabalho foi desenvolvida uma metodologia para simulação de SDMs-CT compostos por DACs a capacitor chaveado e resistor, do inglês Switched-Capacitor-Resistor (SCR). Com base neste modelo e no estudo das diferentes topologias de SDMs, um circuito foi desenvolvido para aplicação em receptores de RF, sendo do tipo passa-baixas de laço único, do inglês single-loop, single-bit, de terceira ordem, voltado ao baixo consumo de energia. Este circuito foi desenvolvido em tecnologia CMOS IBM de 130 nanômetros, tendo sido enviado para fabricação. Através das simulações pós-leiaute realizadas espera-se que seu desempenho fique próximo ao que tem sido publicado recentemente sobre SDMs-CT passa-baixas de laço único e single-bit.

Palavras-chave: Modulação Sigma-Delta, Modulador Sigma-Delta em Tempo Contínuo, Conversor Analógico-Digital (ADC), Modelagem Comportamental.

### **ABSTRACT**

Analog-to-Digital Converters (ADCs) play a fundamental role in the implementation of current systems-on-chip (SoC). Due to the requirements of these systems and the tradeoffs between the main ADCs characteristics, such as signal bandwidth, power consumption and accuracy, many topologies and strategies for their implementation in integrated circuits (ICs) have been developed through the ages. Among these topologies, the sigmadelta converters (SDC) have highlighted the versatility combined with low power consumption and excellent accuracy. Initially developed and used for the conversion of low frequency signals and operation in the discrete time (DT) domain, this class of converters have been evolved and developed over the past to operate in continuous time domain for the conversion of signals with frequencies of hundreds of kHz up to tens of MHz. In this work, continuous time sigma-delta modulators (CT-SDMs) are studied focusing its application to the analog-to-digital (AD) conversion. CT-SDMs offer significant advantages over their discrete-time counterparts, such as lower power consumption, higher input signal bandwidth and implicit anti-alias filter (AAF). However, CT-SDMs present additional limitations that are responsible for their performance degradation, such as the clock jitter, Excess Loop Delay (ELD) and the limitations imposed on the analog integrators. After the study and analysis of CT-SDMs and their performance limitations, a behavioral model approach was developed in the Matlab/Simulink® environment, which allows the simulation of the limitations impact on the modulator, allowing the obteinment of a more accurate estimate of its performance. Based on these simulations it was possible to determine the minimum specifications for each block that composes the analog modulator (such as slew rate, the unity gain frequency  $(f_u)$  and the DC gain of the operational amplifiers used in integrators) and tolerable values of ELD and clock jitter. Additionally, it was developed in this work a methodology for simulate CT-SDMs with Switched-Capacitor-Resistor (SCR) DACs that provide exponential waveforms. Based on this model and the study of different SDMs topologies, it was developed a low-pass, single-loop, single-bit, third order circuit focused on low-power intended for application in RF receivers. This circuit was developed in an IBM 130 nanometers CMOS technology, and was send to manufacturing. Based on the post-layout simulations it is expected to have performance close to what has been recently published of low-pass, single-loop, single-bit CT-SDMs.

Keywords: Sigma-Delta Modulation, Continuous-Time Sigma-Delta Modulator, Analog-to-Digital Converter (ADC), Behavioral Modeling.

# LISTA DE ILUSTRAÇÕES

| Figura 1:  | Diagrama conceitual de um ADC SD                                        | 18 |

|------------|-------------------------------------------------------------------------|----|

| Figura 2:  | Processo de quantização                                                 | 22 |

| Figura 3:  | Modelo linear de um quantizador                                         | 22 |

| Figura 4:  | Ruído de quantização                                                    | 23 |

| Figura 5:  | Imagens do sinal de entrada e AFF                                       | 24 |

| Figura 6:  | Ruído de quantização dentro da banda de interesse de acordo com $f_s$ . | 24 |

| Figura 7:  | Efeito do <i>noise-shaping</i> em um SDM                                | 25 |

| Figura 8:  | Modulador SD                                                            | 26 |

| Figura 9:  | SDM de primeira ordem                                                   | 27 |

| Figura 10: | Potência teórica do ruído de quantização dentro da banda de interesse   |    |

|            | em função da taxa de sobreamostragem para SDMs de ordem L               | 28 |

| Figura 11: | DR ideal de um SDM em função da taxa de sobreamostragem para            |    |

|            | SDMs de ordem L (single-bit)                                            | 28 |

| Figura 12: | Número de SDMs à capacitor chaveado e número de SDMs-CT pu-             |    |

|            | blicados de 1990-2012                                                   | 31 |

| Figura 13: | Modulador SD em tempo contínuo                                          | 32 |

| Figura 14: | Forma de onda de um DAC RZ de 1 bit                                     | 34 |

| Figura 15: | Forma de onda de um DAC NRZ de 1 bit                                    | 34 |

| Figura 16: | Forma de onda de um DAC SCR                                             | 34 |

| Figura 17: | DR versus banda de sinal de SD                                          | 35 |

| Figura 18: | Topologia CIFB de terceira ordem                                        | 36 |

| Figura 19: | SDM-DT: AAF                                                             | 36 |

| Figura 20: | SDM-CT: AAF                                                             | 37 |

| Figura 21: | Laços equivalentes de SDMs                                              | 38 |

| Figura 22: | Sinal de relógio com <i>jitter</i>                                      | 39 |

| Figura 23: | Formas de onda de saída de DACs de 1 bit NRZ, RZ e SCR conside-         |    |

|            | rando o efeito do jitter do sinal de relógio                            | 40 |

| Figura 24: | Efeitos do ELD em SDMs-CT                                               | 41 |

| Figura 25: | Compensação de ELD clássica                                             | 42 |

| Figura 26: | Compensação de ELD clássica para um período de relógio                  | 42 |

| Figura 27: | Integradores analógicos                                                 | 43 |

| Figura 28: | Integrador RC-ativo                                                     | 47 |

| Figura 29: | Modelo de um integrador RC-ativo                                        | 48 |

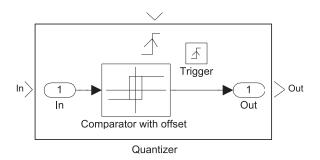

| Figura 30: | Modelo do quantizador                                                   | 48 |

| Figura 31: | Modelagem do DAC SCR: Geração da função de transferência                | 49 |

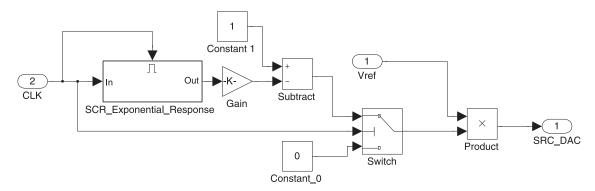

| Figura 32: | Modelagem do DAC SCR: Circuito de controle                              | 50 |

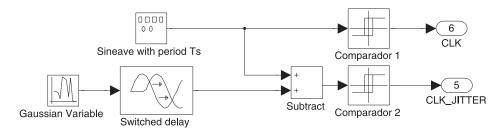

| Figura 33: | Fonte de sinal de relógio com <i>jitter</i>                             | 51 |

|            |                                                                         |    |

| Figura 34: | Topologia CIFB de terceira ordem                                             | 52 |

|------------|------------------------------------------------------------------------------|----|

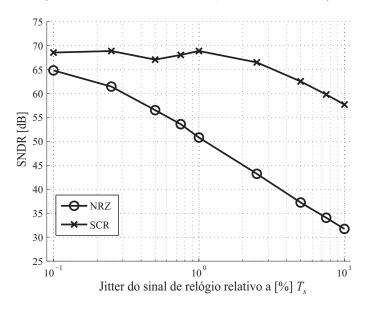

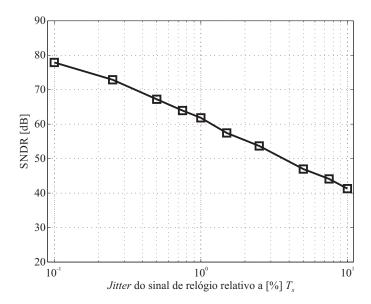

| Figura 35: | Variação do SNDR de acordo com <i>jitter</i> do sinal de relógio             | 52 |

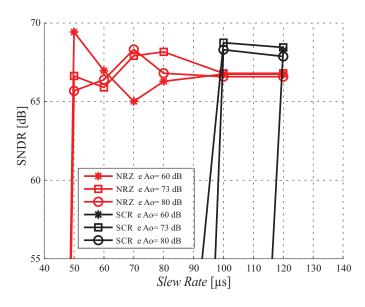

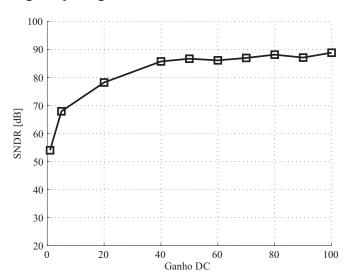

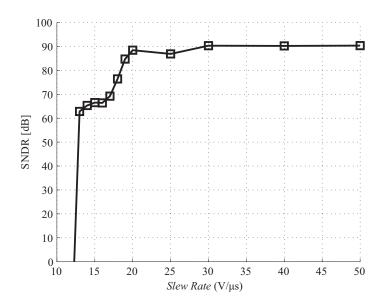

| Figura 36: | Variação do SNDR versus slew rate para ganhos DC distintos                   | 53 |

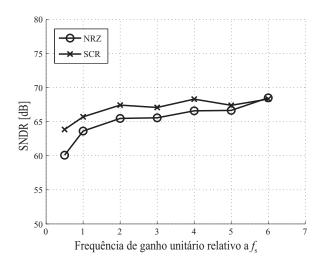

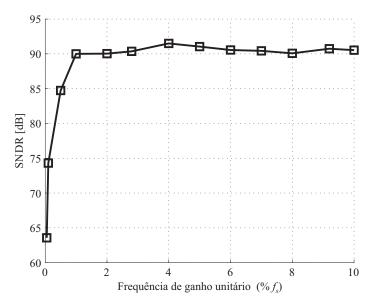

| Figura 37: | Variação do SNDR em função da frequência de ganho unitário dos               |    |

|            | amplificadores                                                               | 53 |

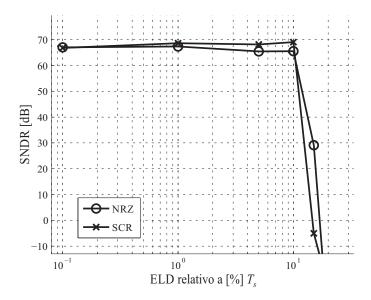

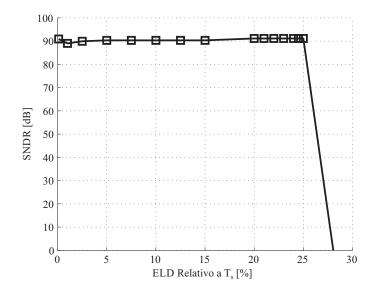

| Figura 38: | Variação do SNDR <i>versus</i> valores do ELD                                | 54 |

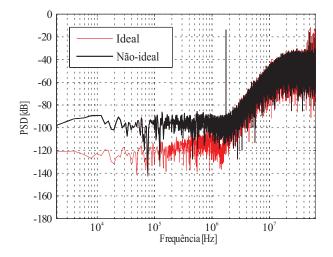

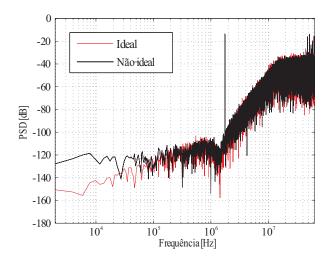

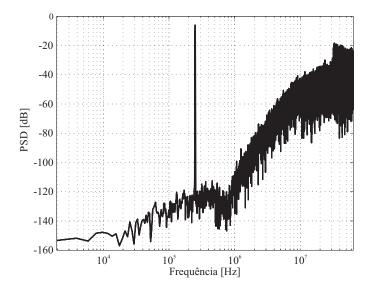

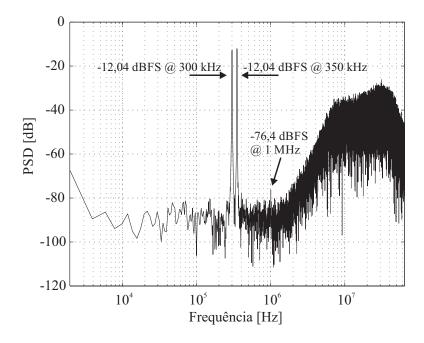

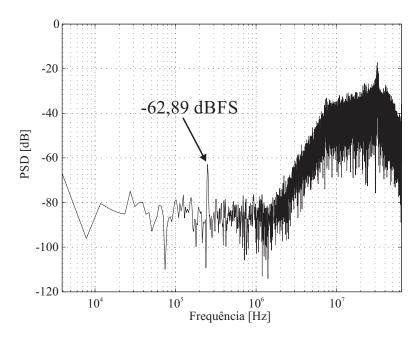

| Figura 39: | PSD do modulador com DACs NRZ                                                | 55 |

| Figura 40: | PSD do modulador com DACs SCR                                                | 55 |

| Figura 41: | Entrada de SDM-CT: Integrador RC-ativo                                       | 56 |

| Figura 42: | Topologia do SDM-CT projetado                                                | 60 |

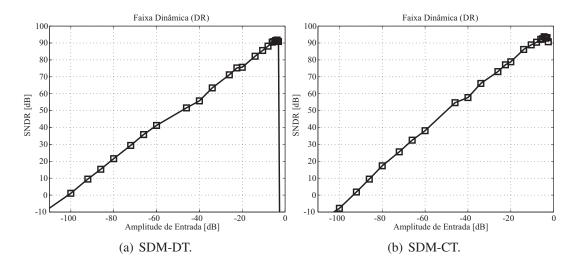

| Figura 43: | PSD ideal.                                                                   | 61 |

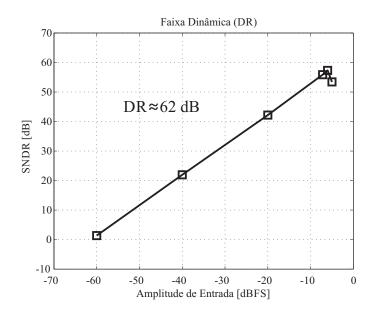

| Figura 44: | Faixa dinâmica ideal                                                         | 62 |

| Figura 45: | Impacto do <i>jitter</i> do sinal de relógio no SDM-CT projetado             | 62 |

| Figura 46: | Impacto do <i>jitter</i> do sinal de relógio no SDM-CT projetado             | 63 |

| Figura 47: | Impacto do ganho DC dos amplificadores no SDM-CT projetado                   | 63 |

| Figura 48: | Impacto da $f_u$ dos amplificadores no SDM-CT projetado                      | 64 |

| Figura 49: | Impacto do SR dos amplificadores no SDM-CT projetado                         | 64 |

| Figura 50: | PSD do modulador com não-idealidades                                         | 65 |

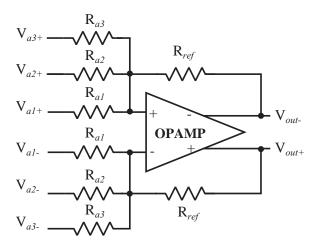

| Figura 51: | Implementação da soma dos coeficientes de alimentação em avanço.             | 67 |

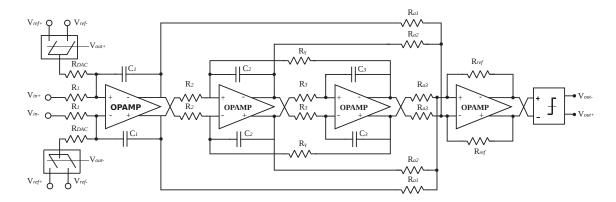

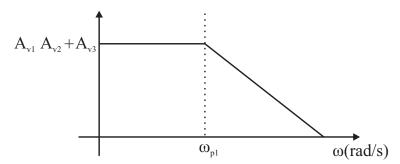

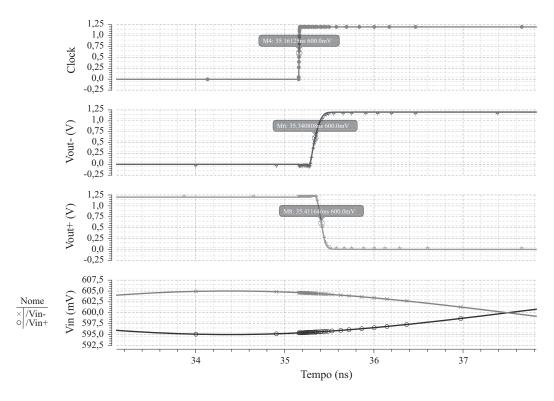

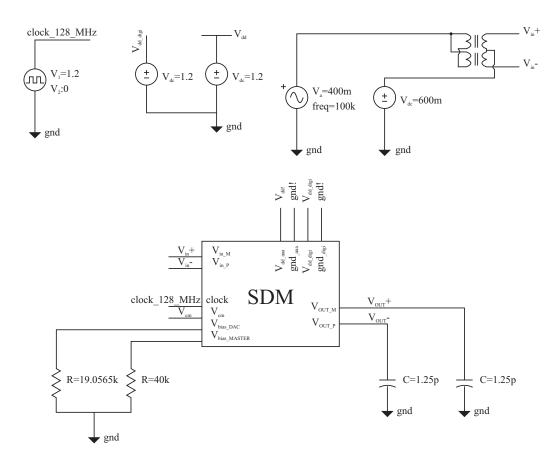

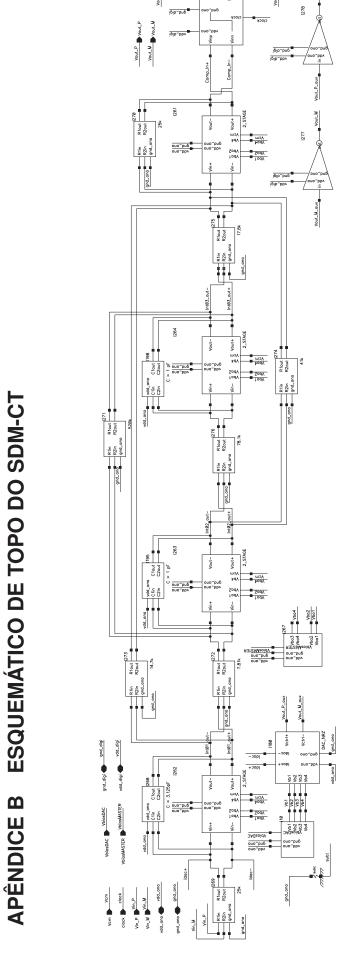

| Figura 52: | Esquemático de topo do SDM-CT projetado                                      | 68 |

| · ·        |                                                                              | 00 |

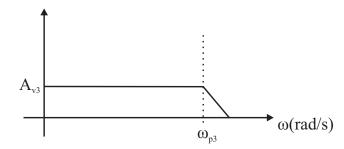

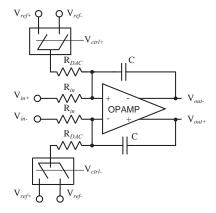

| Figura 53: | Diagrama de blocos do amplificador de dois estágios com compensa-            | 71 |

| Eiguro 54. | ção em avanço.                                                               | 72 |

| Figure 54: | Resposta em frequência                                                       | 73 |

| Figura 55: | Esquemático do amplificador operacional de dois estágios                     |    |

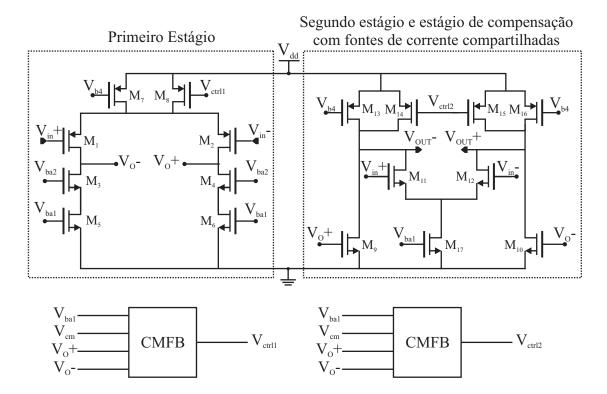

| Figura 56: | Esquemático do circuito de CMFB                                              | 74 |

| Figura 57: | Circuito de polarização geral.                                               | 74 |

| Figura 58: | Diagrama de bode do amplificador.                                            | 76 |

| Figura 59: | Simulação de <i>corner</i> do amplificador: diagrama de bode do amplificador | 77 |

| Figura 60: | Simulação pós-leiaute do amplificador: diagrama de bode                      | 78 |

| Figura 61: | Esquemático de um <i>latch</i> composto por dois inversores                  | 78 |

| Figura 62: | Latch clássico com efeito de kickback-noise                                  | 79 |

| Figura 63: | Esquemático do comparador do tipo <i>latch</i> dinâmico                      | 80 |

| Figura 64: | Esquemático do pré-amplificador                                              | 81 |

| Figura 65: | Esquemático do quantizador de 1-bit                                          | 81 |

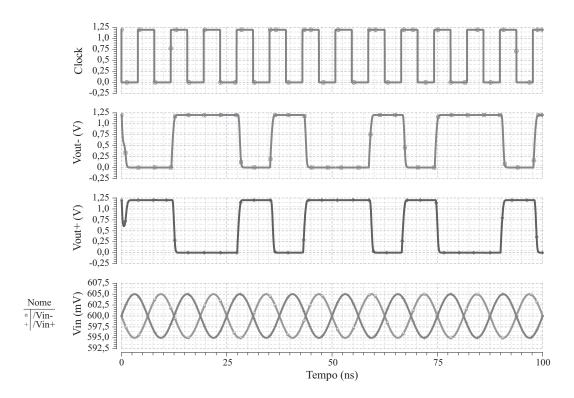

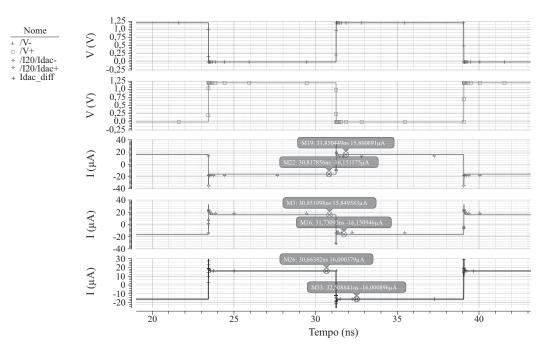

| Figura 66: | Simulação transiente do quantizador de 1-bit                                 | 83 |

| Figura 67: | Simulação transiente do quantizador de 1-bit: <i>zoom</i>                    | 83 |

| Figura 68: | Implementação clássica de um DAC de 1-bit para SDMs-CT                       | 84 |

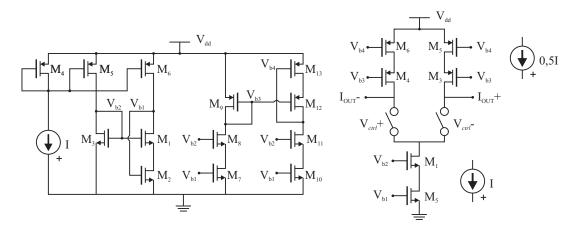

| Figura 69: | DAC current-steering (DAC + Polarização)                                     | 84 |

| Figura 70: | Resultados de simulação do DAC current-steering                              | 85 |

| Figura 71: | Testbench do modulador                                                       | 87 |

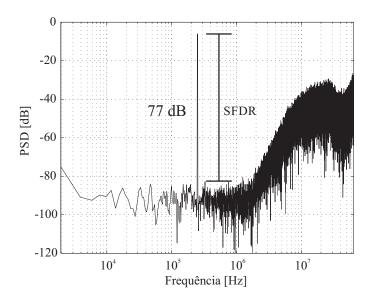

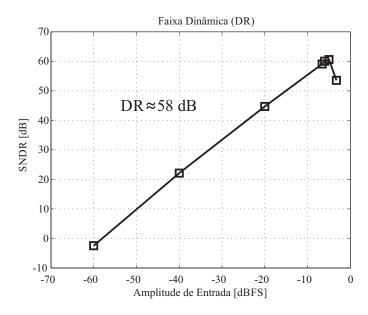

| Figura 72: | PSD da saída do modulador: simulação em nível de esquemático                 | 88 |

| Figura 73: | DR do modulador.                                                             | 89 |

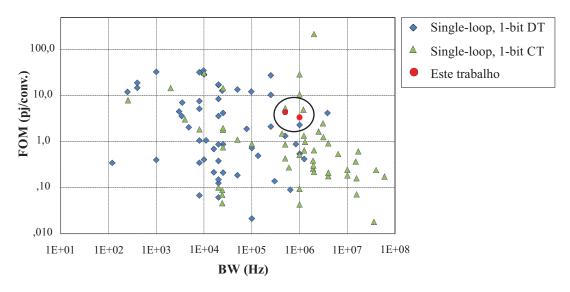

| Figura 74: | FOM versus largura de banda: comparação com o estado da arte                 |    |

| <i>G</i> • | (ROSA, 2013)                                                                 | 90 |

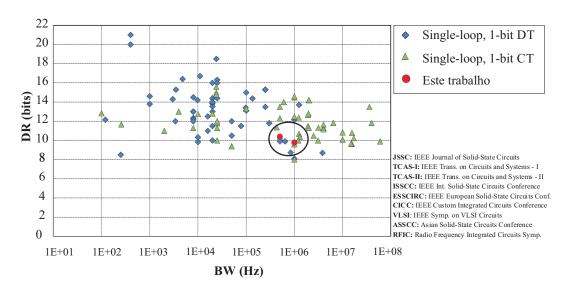

| Figura 75: | DR versus largura de banda: comparação com o estado da arte (ROSA,           | 90 |

| Figure 76. | 2013)                                                                        | 90 |

| Figura 76: | DR do modulador: simulação pós-leiaute                                       | 71 |

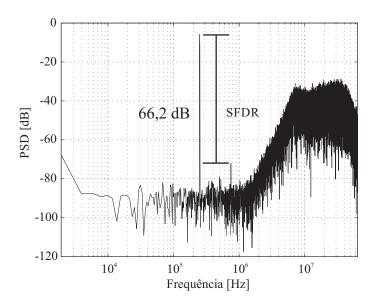

| Figura 77: | PSD da saída do modulador: simulação pós-leiaute                      | 91 |

|------------|-----------------------------------------------------------------------|----|

| Figura 78: | PSD da saída do modulador para um teste com 2 tons: simulação         |    |

|            | pós-leiaute                                                           | 92 |

| Figura 79: | PSD da saída do modulador para o teste do AAF: simulação pós-leiaute. | 93 |

## LISTA DE TABELAS

| Tabela 1:  | Medidas de simulação de densidade de ruído para o resistor de preci-  |    |

|------------|-----------------------------------------------------------------------|----|

|            | são de polisilício (com W= 1 $\mu m$ e T= 300 K) empregado no projeto |    |

|            | do modulador SD CT                                                    | 58 |

| Tabela 2:  | Medidas de ruído para o resistor de precisão (com W= 1 $\mu m$ e T=   |    |

|            | 300 K) empregado no projeto do modulador SD CT                        | 59 |

| Tabela 3:  | Valores dos resistores e capacitores dos integradores                 | 70 |

| Tabela 4:  | Valores dos resistores empregados no modulador                        | 70 |

| Tabela 5:  | Tamanho dos transistores do amplificador                              | 75 |

| Tabela 6:  | Tamanho dos transistores do circuito de CMFB                          | 75 |

| Tabela 7:  | Tamanho dos transistores do circuito de polarização                   | 75 |

| Tabela 8:  | Tamanho dos transistores do <i>latch</i> dinâmico                     | 82 |

| Tabela 9:  | Tamanho dos transistores do DAC                                       | 85 |

| Tabela 10: | Tamanho dos transistores do circuito de polarização do DAC            | 85 |

| Tabela 11: | Desempenho do modulador em nível de esquemático para diferentes       |    |

|            | larguras de banda.                                                    | 89 |

| Tabela 12: | Sumário da performance do modulador para largura de banda de 1        |    |

|            | MHz: esquemático <i>versus</i> pós-leiaute                            | 92 |

| Tabela 13: | Desempenho do modulador em nível de leiaute para diferentes largu-    |    |

|            | ras de banda                                                          | 92 |

| Tabela 14: | Sumário da performance do modulador e comparação com outros tra-      |    |

|            | balhos.                                                               | 94 |

## LISTA DE ABREVIATURAS

AAF Anti-Alias Filter, Filtro Anti-Alias

AD Analog-to-Digital, Analógico-Digital

ADC Analog-to-Digital Converter, Conversor Analógico-Digital

BW Bandwidth, Largura de Banda

CI Circuito Integrado

CIFB Cascade of Integrators Feedback, Cascata de Integradores com Realimentação

CIFF Cascade of Integrators Feed-Forward, Cascata de Integradores com Alimen-

tação em Avanço

CMFB Common Mode Feedbak, Realimentação de Modo Comum

CMOS Complementary Metal Oxide Semiconductor, Semicondutor Metal-Óxido Com-

plementar

CS Common Source, Fonte Comum

CT Continuous Time, Tempo Contínuo

DAC Digital-to-Analog Converter, Conversor Digital-Analógico

DC Direct Current, Corrente Contínua

DOR Digital Output Rate, Taxa Digital de Saída

DR Dynamic Range, Faixa Dinâmica

DT Discrete Time, Tempo Discreto

ELD Excess Loop Delay, Atraso Excessivo do Laço de Realimentação

ENOB Effective Number of Bits, Número Efetivo de Bits

FOM Figure of Merit, Figura de Mérito

FS Full-Scale, Fundo de Escala

GBW Gain Bandwidth Product, Produto Ganho-Faixa

IBN In Band Noise, Ruído Dentro da Banda de Interesse

IC Integrated Circuit

IF Frequência Intermediária

IIT Impulse-Invariant Transformation, Transformada Invariante ao Impulso

IM3 Intermodulação de Terceira Ordem

LHP Left Half-Plane, Semi-Plano Esquerdo

MASH Multi-Stage Noise-Shaping, Noise-Shaping de Múltiplos Estágios

MIM *Metal-insulator-Metal*, Metal-isolante-Metal

MPW Multiple Project Wafer, Wafer de Projetos Múltiplos

NRZ Non Return-to-Zero, Sem Retorno para Zero

NTF Noise Transfer Function, Função de Transferência do Ruído

OSR Oversampling Ratio, Taxa de Sobreamostragem

OTA Operational Transconductance Amplifier, Amplificador de Transcondutância

PSD Power Spectrum Density, Densidade Espectral de Potência

RF Rádio Frequência

RZ Return-to-zero Retorno para Zero

SAR Successive Approximation Register, Conversor de Aproximações Sucessivas

SC Switched-Capacitor, Capacitor Chaveado

SCR Switched-Capacitor-Resistor, Capacitor Chaveado com Resistor

SD Sigma-Delta

SDC Sigma-Delta Converters

SDM Modulador Sigma-Delta

SDM-CT Modulador Sigma-Delta em Tempo Contínuo

SDM-DT Modulador Sigma-Delta em Tempo Discreto

SFDR Spurious Free Dynamic Range, Faixa Dinâmica Livre de Espúrios

SI Switched-Current, Corrente Chaveada

SNDR Signal to Noise and Distortion Ratio, Relação Sinal-Ruído e Distorção

SNR Signal to Noise Ratio, Relação Sinal-Ruído

SoC System-on-Chip, Sistemas em Chip

SQNR Signal to Quantization Noise Ratio, Relação-Sinal Ruído de Quantização

SR Slew Rate, Taxa de Variação

STF Signal Transfer Function, Função de Transferência do Sinal

# LISTA DE SÍMBOLOS

| $A_0$         | Ganho DC do Amplificador                                             |

|---------------|----------------------------------------------------------------------|

| $a_f$         | Expoente do Ruído flicker                                            |

| dBFS          | dB em Relação ao Fundo de Escala                                     |

| δ             | Incerteza do Período de Relógio                                      |

| Δ             | Diferença Entre Dois Níveis de Quantização                           |

| e(n)          | Erro de Quantização                                                  |

| e(z)          | Erro de Quantização Processado                                       |

| E(z)          | Transformada Z do Ruído de Quantização                               |

| $f_{in}$      | Input Signal Frequency, Frequência do Sinal de Entrada               |

| $f_s$         | Sampling Frequency, Frequência de Amostragem                         |

| $f_u$         | Frequência de Ganho Unitário                                         |

| $g_{mOTA}$    | Transcondutância do OTA                                              |

| H(s)          | Filtro do Laço em Tempo Contínuo                                     |

| H(z)          | Filtro do Laço em Tempo Discreto                                     |

| $I_{ref+}$    | Corrente de Referência Positiva                                      |

| $I_{ref-}$    | Corrente de Referência Negativa                                      |

| $k_f$         | Parâmetro do Ruído flicker Dependente da Tecnologia                  |

| $n_f$         | Fator de Excesso do Ruído flicker                                    |

| NTF(z)        | Função de Transferência do Ruído do Laço em Tempo Discreto           |

| $n_{thermal}$ | Fator de Excesso do Ruído Térmico                                    |

| $\omega_a$    | Frequência de Corte de -3 dB do Amplificador Expressa em rad/s       |

| $\omega_u$    | Frequência de Ganho Unitário do Amplificador Expressa em rad/s       |

| $P_E$         | Potência do Ruído de Quantização Dentro da Banda de Interesse        |

| $P_Q$         | Valor do Ruído Dentro da Banda de Interesse de um ADC Sobreamostrado |

| $R_{DAC}$     | Resistor do DAC                                                      |

$R_{DAC}(s)~$  Função de Transferência do DAC

$\rho_q(e)$ Função de Densidade de Probabilidade do Erro de Quantização  $S_E(f)$ Densidade Espectral de Potência do Erro de Quantização  $\sigma$ Desvio Padrão  $\sigma^2$ Variância  $\sigma^2(e)$ Potência Total do Ruído de Quantização STF(z)Função de Transferência do Sinal do Laço em Tempo Discreto  $T_{CLK}$ Período do Sinal de Relógio sem *Jitter*  $T_s$ Período do Sinal de Relógio  $\bar{v}_{DAC}^2$ Densidade de Ruído do DAC  $\bar{v}_R^2$ Densidade de Ruído de um Resistor  $\bar{v}_{R_{in}}^2$ Densidade de Ruído do Resistor de Entrada  $\bar{v}_{OTA}^2$ Densidade de Ruído do OTA  $\bar{\upsilon}^2_{total}$ Densidade de Ruído Total na Entrada do Integrador  $V_{ref+}$ Tensão de Referência Positiva  $V_{\it ref-}$ Tensão de Referência Negativa  $X_{FS}$ Amplitude de Entrada de Fundo de Escala do Quantizador  $Y_{FS}$ Faixa de Saída de Fundo de Escala do Quantizador  $P_{noise}$ Potência de Ruído na Entrada do Integrador

# **SUMÁRIO**

| 1 IN  | NTRODUÇÃO                                           | 18 |

|-------|-----------------------------------------------------|----|

| 1.1   | Motivação                                           | 19 |

| 1.2   | Objetivos do Trabalho                               | 19 |

| 1.3   | Contribuições do Trabalho                           | 19 |

| 1.4   | Organização da Dissertação                          | 20 |

| 2 M   | IODULAÇÃO SIGMA-DELTA                               | 21 |

| 2.1   | Princípios da Conversão AD                          | 21 |

| 2.1.1 | Amostragem                                          | 21 |

| 2.1.2 | Quantização                                         | 21 |

| 2.1.3 | Sobreamostragem                                     | 23 |

| 2.1.4 | Noise-shaping                                       | 24 |

| 2.2   | Modulador Sigma-Delta                               | 25 |

| 2.2.1 | Performance de Moduladores Sigma-Delta              | 27 |

| 2.2.2 | Classificação de Moduladores Sigma-Delta            | 29 |

| 2.3   | Considerações                                       | 29 |

| 3 M   | IODULADORES SD EM TEMPO CONTÍNUO                    | 31 |

| 3.1   | Introdução                                          | 31 |

| 3.2   | Características dos SDMs-CT                         | 32 |

| 3.2.1 | Amostragem                                          | 32 |

| 3.2.2 | Filtro                                              | 33 |

| 3.2.3 | Quantizador                                         | 33 |

| 3.2.4 | DAC                                                 | 33 |

| 3.3   | Vantagens dos SDMs-CT                               | 35 |

| 3.4   | Metodologias de Projeto em Alto Nível de SDMs-CT    | 37 |

| 3.4.1 | Transformação DT/CT                                 | 37 |

| 3.4.2 | Síntese Direta do Filtro do Laço                    | 39 |

| 3.5   | Desvantagens e Não-idealidades de SDMs-CT           | 39 |

| 3.5.1 | Jitter do Sinal de Relógio                          | 39 |

| 3.5.2 | Excess Loop Delay                                   | 41 |

| 3.5.3 | Não-idealidades do Filtro                           | 42 |

| 3.6   | Considerações                                       | 44 |

|       | IODELAGEM DAS NÃO-IDEALIDADES E PROJETO DE ALTO NÍ- |    |

| V     | EL DO SDM-CT                                        | 45 |

| 4.1   | Introdução                                          | 45 |

| 4.2        | Modelagem das Não-idealidades de SDMs                                     | 45 |

|------------|---------------------------------------------------------------------------|----|

| 4.3        | Modelagem das Não-idealidades de SDMs-CT                                  | 46 |

| 4.4        | Modelo Desenvolvido                                                       | 47 |

| 4.4.1      | Modelagem de Integradores RC-ativos                                       | 47 |

| 4.4.2      | Modelo de um Quantizador Single-bit                                       | 48 |

| 4.4.3      | Modelo de DACs Single-bit NRZ                                             | 48 |

| 4.4.4      | Modelo de DACs Single-bit SCR                                             | 49 |

| 4.4.5      | Modelo do ELD                                                             | 50 |

| 4.4.6      | Modelagem do Jitter do Sinal de Relógio                                   | 50 |

| 4.5        | Estudo de Caso: Simulação com o Modelo Desenvolvido                       | 51 |

| 4.5.1      | Efeitos do <i>Jitter</i>                                                  | 52 |

| 4.5.2      | Efeitos do Ganho DC e Slew Rate Finito dos Amplificadores                 | 52 |

| 4.5.3      | Efeitos da Frequência de Ganho Unitário Finita dos Amplificadores         | 53 |

| 4.5.4      | Efeito do ELD                                                             | 54 |

| 4.5.5      | Efeito de Todas as Não-idealidades Modeladas                              | 54 |

| 4.6        | Análise de Ruído                                                          | 55 |

| 4.6.1      | Ruído na Entrada de SDMs-CT                                               | 56 |

| 4.6.2      | Especificação do Ruído Máximo na Entrada do SDM-CT                        | 57 |

| 4.6.3      | Medidas de Ruído                                                          | 58 |

| 4.6.4      | Dimensionamento do Resistor de Entrada do CT Modulador                    | 59 |

| 4.7        | Projeto de Alto Nível do SDM-CT                                           | 59 |

| 4.7.1      | Escolha da Topologia                                                      | 60 |

| 4.7.2      | Projeto do Laço em Tempo Contínuo                                         | 60 |

| 4.7.3      | Performance Ideal                                                         | 61 |

| 4.7.4      | Performance com Não-idealidades                                           | 62 |

| 4.8        | Considerações                                                             | 65 |

| 5 P        | ROJETO DO SDM-CT EM TECNOLOGIA CMOS                                       | 66 |

| 5.1        | Definições Gerais                                                         | 66 |

| 5.1.1      | Definição da Topologia dos Integradores                                   | 66 |

| 5.1.2      | Implementação em Nível Elétrico dos Coeficientes de Alimentação em        |    |

|            | Avanço                                                                    | 67 |

| 5.1.3      | Implementação em Nível Elétrico dos Coeficiente de Realimentação $\gamma$ | 67 |

| 5.1.4      | Esquemático de Topo Simplificado do SDM-CT Projetado                      | 67 |

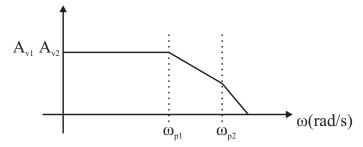

| 5.1.5      | Definição do Amplificador dos Integradores                                | 67 |

| 5.2        | Especificações da Implementação em Nível Elétrico                         | 69 |

| 5.3        | Implementação dos Coeficientes                                            | 69 |

| 5.3.1      | Cálculo dos Resistores e Capacitores dos Integradores                     | 69 |

| 5.3.2      | Implementação dos Coeficientes de Alimentação em Avanço                   | 69 |

| 5.3.3      | Definição do Tipo de Resistor Empregado                                   | 70 |

| 5.3.4      | Definição do Tipo de Capacitor Empregado                                  | 70 |

| 5.4        | Projeto do Amplificador Operacional                                       | 71 |

| 5.4.1      | Resultados de Simulação do Amplificador                                   | 76 |

| 5.5        | Projeto do Quantizador de 1-bit (ADC)                                     | 78 |

| 5.5.1      | Comparadores do Tipo <i>Latch</i>                                         | 78 |

| 5.5.2      | Topologia do Quantizador                                                  | 80 |

| 5.5.3      | Simulação do Quantizador                                                  | 82 |

| <b>5.6</b> | Projeto do DAC NRZ de 1-bit                                               | 82 |

| 5.6.1      | DAC de 1-bit Current-steering                                             | 82 |

|            |                                                                           |    |

| 5.6.2<br><b>5.7</b><br><b>5.8</b>                                        | Simulação do DAC                                                                                                                                                                                   | 85<br>86<br>86                         |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 6 R<br>6.1<br>6.2<br>6.3<br>6.4                                          | RESULTADOS OBTIDOS E DISCUSSÕES  Resultados em Nível de Esquemático  Resultados Pós-Leiaute  Comparação com o Estado da Arte  Discussões                                                           | 87<br>88<br>90<br>93<br>94             |

| <b>7.1</b> 7.1.1 7.1.2 7.1.3 7.1.4 7.1.5                                 | Trabalhos Futuros Teste e Caracterização do Chip Aprimoramento nos Modelos Comportamentais Otimizações nos Blocos Analógicos Projeto de um Modulador Reconfigurável Projeto de um Filtro Decimador | 95<br>96<br>96<br>96<br>97<br>97       |

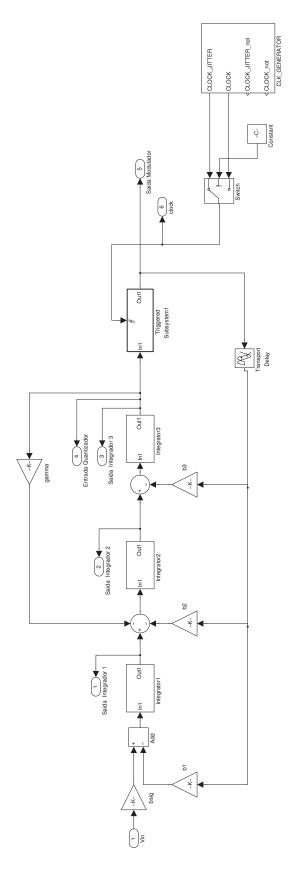

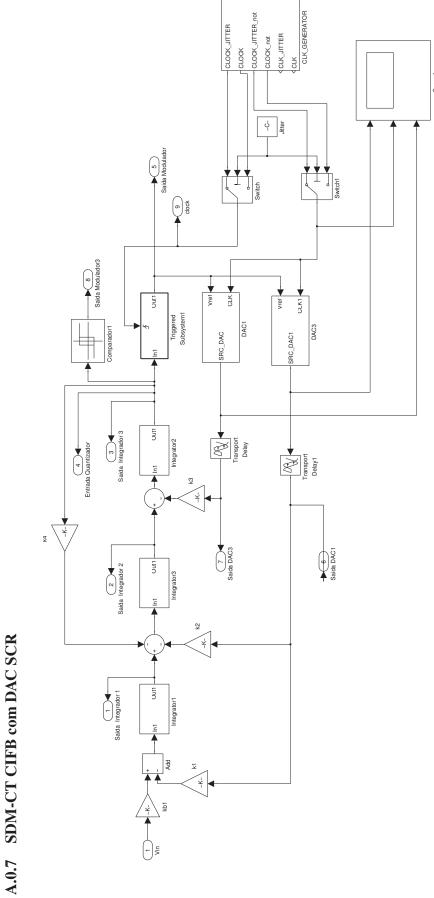

| _                                                                        | NDICE A MODELO COMPLETO DOS SDMS-CT NO AMBIENTE MATLAB/SIMULINK®                                                                                                                                   | 105<br>105<br>106                      |

| APÊN                                                                     | NDICE B ESQUEMÁTICO DE TOPO DO SDM-CT                                                                                                                                                              | 107                                    |

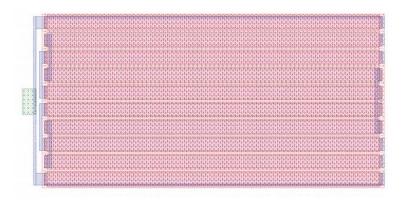

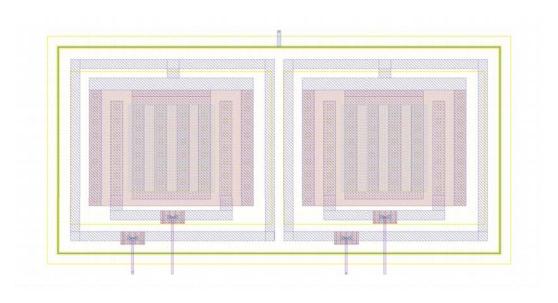

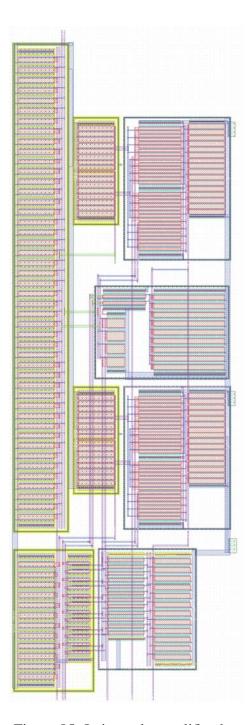

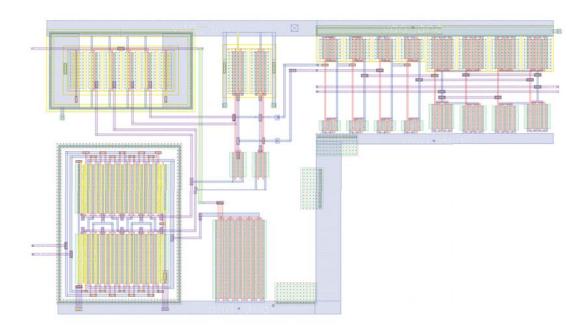

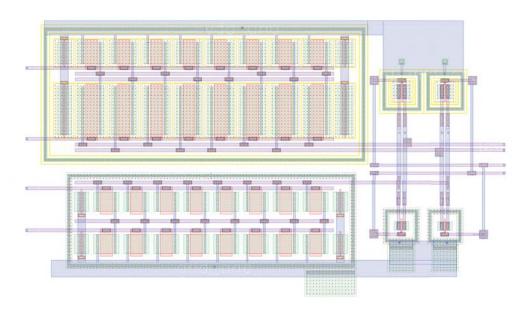

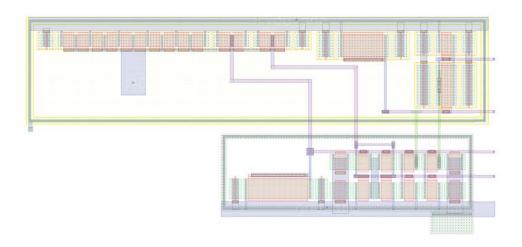

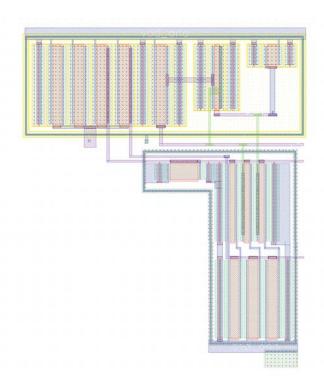

| APÊN<br>C.0.8<br>C.0.9<br>C.0.10<br>C.0.11<br>C.0.12<br>C.0.13<br>C.0.14 | Leiaute dos Resistores                                                                                                                                                                             | 108<br>109<br>110<br>110<br>111<br>111 |

|                                                                          | ANÁLISE DA IMPEDÂNCIA DE ENTRADA DE UM INTE-GRADOR RC-ATIVO                                                                                                                                        | 113<br>113                             |

|                                                                          |                                                                                                                                                                                                    |                                        |

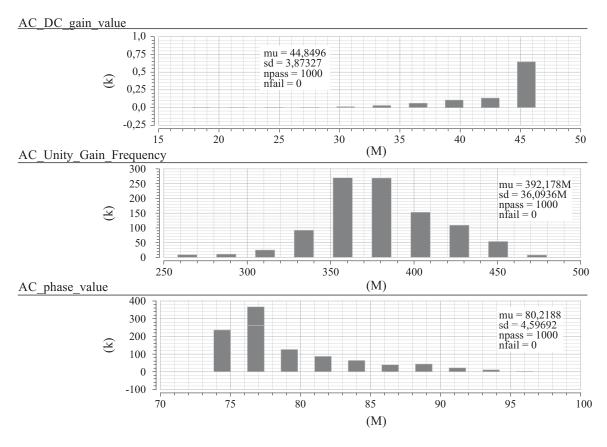

| AFEI                                                                     | NDICE E HISTOGRAMAS DA SIMULAÇÃO DE MONTE CARLO DO AMPLIFICADOR                                                                                                                                    | 115                                    |

|                                                                          | DO AMPLIFICADOR                                                                                                                                                                                    | 115<br>116                             |

## 1 INTRODUÇÃO

O processo de conversão Analógico-Digital (AD) destaca-se pela sua grande importância dentro da área de processamento de sinais (ALLEN; HOLBERG, 2002). Isto é explicado pois, atualmente, grande parte do processamento de sinais em circuitos eletrônicos é efetuado digitalmente (RAPUANO *et al.*, 2005).

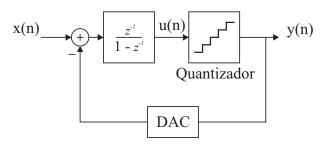

Os Moduladores Sigma-Delta (SDMs) surgiram na década de 60 e são empregados no desenvolvimento de conversores analógico-digitais (ADCs) do tipo Sigma-Delta (SD). Estes são compostos basicamente por um filtro anti-alias (AAF), um SDM e um filtro decimador na saída, conforme Figura 1, sendo o SDM o bloco fundamental de um ADC SD, visto que ele limita a largura de banda e precisão do ADC.

Figura 1: Diagrama conceitual de um ADC SD.

Os SDMs têm sido empregados em diferentes aplicações industriais que abrangem desde circuitos de instrumentação até aplicações em circuitos de comunicação, como em receptores de rádio frequência (RF) (A. MORGADO; ROSA, 2011).

Sistemas de comunicação e dispositivos móveis, como telefones celulares, notebooks e tablets, tendem a apresentar sistemas de comunicação sem fio com suporte a diferentes padrões de comunicação. Conversores analógico-digitais estão presentes na maioria destes sistemas, principalmente nos receptores de rádio frequência, e eles devem apresentar um bom compromisso entre consumo de energia e largura de banda do sinal de entrada. Tal abordagem leva ao desenvolvimento de ADCs reconfiguráveis. Os ADCs SD são os candidatos mais adequados para a adaptação e desenvolvimento de ADCs reconfiguráveis. Assim, torna-se atraente o estudo, análise e desenvolvimento de SDMs.

Adicionalmente, uma das principais características dos SDMs é a sua robustez, apresentando menor sensibilidade às imperfeições dos circuitos analógicos que o compõe, o que os torna uma ótima escolha para o projeto de ADCs em circuitos integrados CMOS em escala nanométrica e em modernos sistemas em chip (SoC) (A. MORGADO; ROSA, 2011). Eles proporcionam alta resolução com componentes de relativamente baixa precisão devido aos benefícios de ambos, *noise-shaping* e sobreamostragem, enquanto apresentam um bom compromisso entre largura de banda do sinal de entrada e precisão.

Existem duas abordagens para o desenvolvimento de SDMs: projeto em tempo discreto (DT) e projeto em tempo contínuo (CT). Esta dissertação aborda o estudo, modelagem e o projeto de um SDM em tempo contínuo (SDMs-CT) com baixo consumo de energia em tecnologia CMOS de 130 nm.

### 1.1 Motivação

Os SDMs-CT têm recebido atenção crescente nos últimos anos devido à necessidade de desenvolvimento de ADCs com baixo consumo de energia, alta largura de banda e média e alta resolução para aplicações em sistemas de comunicação sem fio de banda larga implementados em tecnologias CMOS avançadas.

Enquanto os SDMs-CT oferecem vantagens significativas sobre seus homólogos em tempo discreto, como menor consumo de energia, maior largura de banda do sinal de entrada e AAF implícito, eles sofrem devido às não-idealidades do circuito que podem degradar o seu desempenho. Dentre essas não-idealidades as principais contribuições para a redução da relação sinal-ruído (SNR) são dadas por efeitos de *jitter* do sinal de relógio, *Excess Loop Delay* (ELD) e as limitações de integradores analógicos.

Assim, é necessário compreender as principais características e dominar o fluxo de projeto completo de SDMs em tempo contínuo visando o desenvolvimento destes para aplicações em circuitos de comunicação.

Adicionalmente, a análise e projeto de SDMs-CT têm sido alvo de pesquisas ao redor do mundo visando o desenvolvimento de moduladores com maior largura de banda e menor consumo de energia para suprir as demandas dos diferentes e crescentes protocolos de comunicação sem fio. Assim, como principal motivação do desenvolvimento deste trabalho de mestrado destaca-se a inserção da nossa Universidade dentro desta linha de pesquisa e desenvolvimento.

## 1.2 Objetivos do Trabalho

O principal objetivo deste trabalho é estudar, analisar e projetar SDMs em tempo contínuo aplicados à conversão AD. Para isto, deve-se compreender as principais não-idealidades que afetam o desempenho de SDMs-CT e qual o impacto destas na performance do mesmo. Deste modo, é necessário efetuar a modelagem destas não-idealidades para posteriormente analisar os seus impactos na performance dos SDMs-CT.

Objetivando explorar o modelo desenvolvido foi projetado neste trabalho um CT SDMs do tipo passa-baixas *single-loop single-bit* e baixo consumo de energia em tecnologia CMOS de 130 nm para aplicações em receptores de RF do tipo Zero-IF que abrangem os seguintes protocolos: GSM, Bluetooth e GPS.

## 1.3 Contribuições do Trabalho

Após o estudo e análise de SDMs-CT e de suas não-idealidades foi desenvolvido um modelo comportamental para simular e analisar o impacto destas não-idealidades na performance de SDMs-CT. O modelo comportamental foi desenvolvido no ambiente Matlab/Simulink® (MATLAB, 2014) e a metodologia de modelagem desenvolvida foi publicada em (AGUIRRE *et al.*, 2013).

A partir da modelagem e análise de performance de um SDM-CT pode-se obter uma estimativa do desempenho real de tal modulador e determinar as especificações mínimas

de cada bloco analógico que o compõe, como o *Slew Rate* (SR), frequência de ganho unitário ( $f_u$ ) e ganho DC dos amplificadores operacionais utilizados nos integradores, e os valores toleráveis de ELD e *jitter*. Adicionalmente, foi desenvolvida neste trabalho uma metodologia para simulação de SDMs-CT compostos por DACs com forma de ondas exponenciais, conhecidos como DACs a capacitor chaveado e resistor, do inglês *switched-capacitor-resistor* (SCR), no Matlab/Simulink<sup>®</sup>.

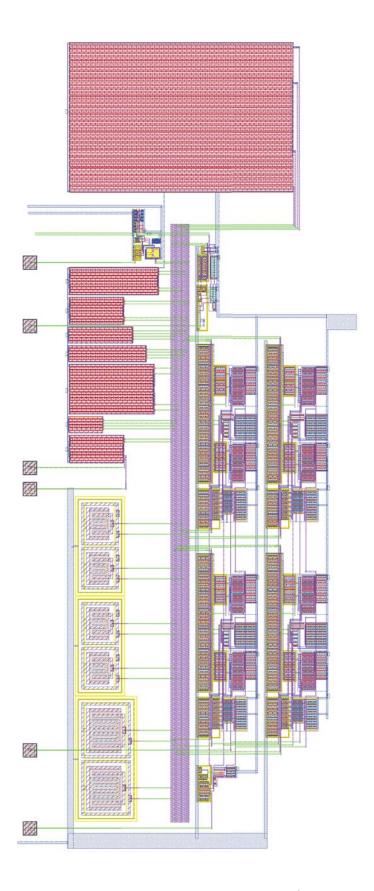

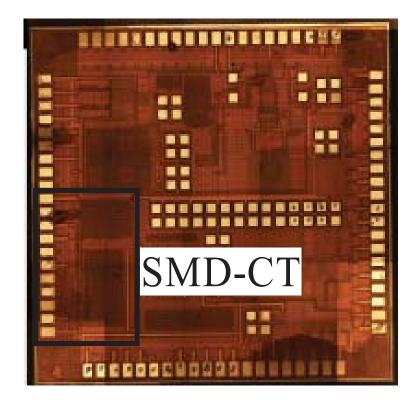

Com base neste modelo e no estudo das diferentes topologias de SDMs foi projetado um SDM-CT do tipo passa-baixas de laço único (*single-loop*), *single-bit*, de terceira ordem em tecnologia CMOS IBM 8RF-DM (MOSIS, 2014) de 130 nanômetros com tensão de alimentação de 1,2 V voltado ao baixo consumo de energia.

Os resultados de simulação pós-leiaute, com a inclusão de elementos parasitas, para uma banda de sinal de 1 MHz indicam uma Relação Sinal-Ruído e Distorção (SNDR) de pico de 57,31 dB, Número Efetivo de Bits (ENOB) de 9,23 bits, consumo de energia de 5,91 mW e uma Figura de Mérito (FOM) de 4,93 pJ/conv deixando o modulador próximo ao estado da arte em relação aos SDMs-CT do tipo passa-baixas *single-loop single-bit*.

Deste modo, foi possível compreender e analisar o fluxo completo de projeto de SDMs-CT em tecnologia CMOS. As análises críticas dos resultados obtidos encontram-se no final desta dissertação.

### 1.4 Organização da Dissertação

Este trabalho está organizado em 7 Capítulos. O Capítulo seguinte apresenta os principais conceitos sobre Modulação Sigma-Delta. O Capítulo 3 apresenta o embasamento teórico para a compreensão do princípio de funcionamento e projeto de SDMs-CT. A modelagem das não-idealidades presentes nos SDMs em tempo contínuo e o projeto em alto nível do modulador são apresentadas no Capítulo 4. O Capítulo 5 apresenta em detalhes o projeto elétrico em tecnologia CMOS de 130 nm do SDM-CT projetado. Os resultados obtidos e discussões referentes ao projeto e simulação em nível elétrico do modulador são apresentados no Capítulo 6. Finalmente, no Capítulo 7 são apresentadas as principais conclusões do trabalho e as sugestões para trabalhos futuros.

## 2 MODULAÇÃO SIGMA-DELTA

## 2.1 Princípios da Conversão AD

A conversão de sinais analógicos para o domínio digital é efetuada por um conversor analógico-digital e sua operação é dividida em duas fases: Amostragem no tempo e quantização em amplitude.

#### 2.1.1 Amostragem

De acordo com o Teorema de Nyquist (HAYKIN; MOHER, 2006), a frequência de amostragem,  $f_s$ , necessária para a perfeita reconstrução de um sinal após o processo de amostragem, sem distorção, deve ser de pelo menos duas vezes a máxima componente de frequência de interesse do sinal amostrado  $f_{in}$ :

$$f_s \ge f_N = 2 \times f_{in} \tag{1}$$

onde  $f_N$  é definida como a frequência de Nyquist.

Como os conversores analógico-digitais são responsáveis por converter sinais contínuos dentro de uma largura de banda (BW) finita em um sinal discreto no tempo, assume-se que a frequência de amostragem deve satisfazer o teorema de Nyquist, assim:  $f_s > 2 \times \text{BW}$ .

A relação entre a frequência de amostragem e a frequência de Nyquist é referenciada como taxa sobreamostragem (OSR):

$$OSR = \frac{f_s}{2 \times BW} \tag{2}$$

Os conversores AD são classificados de acordo com o OSR. Os ADCs com OSR unitário ou levemente superior a um (tipicamente de 1,5 a 10) são denominados conversores do tipo Nyquist-rate, enquanto ADCs com OSR muito maior que um (tipicamente de 10 a 512) são denominados ADCs sobreamostrados (JOHNS; MARTIN, 1997) .

Dentre os ADCs do tipo Nyquist-rate pode-se citar os ADCs integradores duplarampa, conversores de aproximação sucessiva (SAR) e conversores *flash*. Já dentre os conversores sobreamostrados destacam-se os ADCs Sigma-Delta (MALOBERTI, 2007) (JESPERS, 2001).

#### 2.1.2 Quantização

O processo de quantização em amplitude, comumente chamado apenas de quantização, é o processo que transforma uma faixa de sinal contínuo em um conjunto de valores discretos finitos.

O processo de quantização é efetuado por um bloco chamado quantizador. Mesmo com o emprego de um quantizador ideal são introduzidos erros inerentes ao processo de quantização, conhecidos como erro de quantização. Adicionalmente, o processo de quantização é não reversível, ocasionando a redução da resolução do sinal digitalizado, ou seja, ocasiona a perda de informação do sinal original (ROSA, 2011).

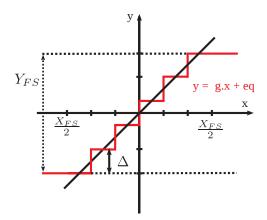

A Figura 2 ilustra o processo de quantização. Na Figura 2(a) observa-se a curva de transferência de um quantizador ideal onde os passos de quantização, cujos valores são representados no eixo y, são interligados através de uma reta que cruza por zero. O erro de quantização eq(x) é uma função não linear do sinal de entrada x e este é ilustrado na Figura 2(b).

(a) Quantização uniforme.

Figura 2: Processo de quantização.

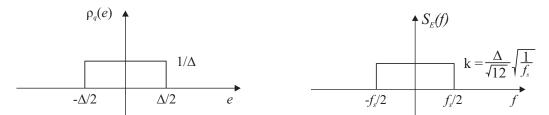

#### 2.1.2.1 Modelo do quantizador

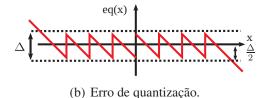

O erro de quantização pode ser fortemente correlacionado ao sinal de entrada do quantizador (JOHNS; MARTIN, 1997). Entretanto, se for considerado que não existe correlação pode-se aproximar o comportamento do erro de quantização pela adição de uma fonte de ruído branco ao sinal de entrada, conforme Figura 3.

Figura 3: Modelo linear de um quantizador.

O erro de quantização é a diferença entre o sinal de entrada e o sinal de saída do quantizador, e neste modelo ele é aproximado como um número aleatório independente

distribuído uniformemente entre  $\pm\Delta/2$ , onde  $\Delta$  é igual a diferença entre dois níveis de quantização adjacentes (JOHNS; MARTIN, 1997). Contudo, este modelo é valido apenas quando o sinal de entrada varia rapidamente e possui amplitude menor ou igual a amplitude de entrada de fundo de escala, do inglês *Full-Scale* (FS),  $\pm X_{FS}/2$  do quantizador. Caso a amplitude do sinal de entrada esteja fora do limite  $\pm X_{FS}/2$  o erro de quantização excede o valor  $\pm\Delta/2$  e cresce monotonicamente (ROSA, 2011).

Para um quantizador de N bits, o passo de quantização  $\Delta$  é definido pela Equação 3.

$$\Delta = \frac{Y_{FS}}{2^N - 1} \tag{3}$$

onde  $Y_{FS}$  é faixa de saída de fundo de escala do quantizador e N o número de bits do quantizador.

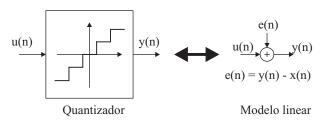

A função de densidade de probabilidade do erro de quantização,  $\rho_q(e)$ , é uniforme na faixa de  $[-\Delta/2$ ,  $+\Delta/2]$ , como ilustrado na Figura 4(a).

- (a) Função densidade de probabilidade.

- (b) Densidade espectral de potência.

Figura 4: Ruído de quantização.

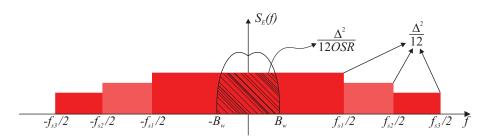

A potência total do ruído de quantização,  $\sigma^2(e)$ , é igual a  $\Delta^2/12$  e é independente da frequência de amostragem  $f_s$  (JOHNS; MARTIN, 1997), sendo distribuída uniformemente na faixa  $[-\frac{f_s}{2}, \frac{f_s}{2}]$ .

Assim, a densidade espectral de potência do erro de quantização,  $S_E(f)$ , é constante com amplitude  $k=\frac{\Delta}{\sqrt{12}}\sqrt{\frac{1}{f_s}}$  e concentrada no intervalo  $[-\frac{f_s}{2},\,\frac{f_s}{2}]$ , como mostra a Figura 4(b), sendo calculada através da Equação 4.

$$S_E(f) = \frac{\sigma^2(e)}{f_s} = \frac{\Delta^2}{12 \times f_s} \tag{4}$$

Assim, a potência do ruído de quantização dentro da banda de interesse  $(P_E)$  é calculada através de Equação 5.

$$P_{E} = \int_{-BW}^{BW} S_{E}(f) df = \int_{-BW}^{BW} k df = \frac{\Delta^{2}}{12 \times OSR}$$

(5)

#### 2.1.3 Sobreamostragem

O processo de sobreamostragem consiste em amostrar sinais à uma frequência superior à frequência de Nyquist, como visto anteriormente, e possui dois efeitos perceptíveis em um conversor AD.

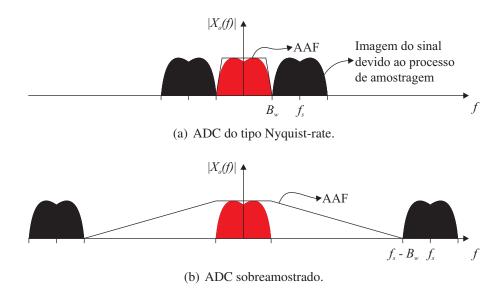

O primeiro efeito é que desde que  $f_s$  seja maior que a taxa de Nyquist, as imagens do sinal de entrada criadas pelo processo de amostragem ficam mais espaçadas no domínio da frequência do que em um ADC do tipo Nyquist-rate, como ilustrado na Figura 5.

Assim, as componentes espectrais do sinal de entrada nas faixas [BW,  $f_s$  - BW] não se sobrepõem com a banda de sinal e o fator de atenuação do AAF pode ser mais suave em um ADC sobreamostrado, simplificando o projeto e reduzindo o custo do AAF.

Figura 5: Imagens do sinal de entrada e AFF.

O segundo efeito é associado à distribuição uniforme do ruído de quantização dentro da faixa  $[-\frac{f_s}{2}, \frac{f_s}{2}]$ , onde apenas uma fração do ruído de quantização é localizada dentro da banda de sinal do ADC. Com base na Equação 5 nota-se que é possível diminuir a potência do ruído de quantização com o aumento do OSR. Por exemplo, se o OSR for incrementado duas vezes pode-se reduzir pela metade a potência do ruído de quantização dentro da banda de interesse, ou seja, 3 dB. Assim, o ruído de quantização dentro da banda de interesse é reduzido devido ao aumento do OSR à uma taxa de 3 dB/oitava. Isto pode ser verificado na Figura 6.

Figura 6: Ruído de quantização dentro da banda de interesse de acordo com  $f_s$ .

O cálculo da relação sinal-ruído (SNR) máxima para um ADC de N bits do tipo Nyquist-rate é efetuado através da Equação 6 (JOHNS; MARTIN, 1997).

$$SNR = 6,02 \times N + 1,76 \, dB$$

(6)

Como a potência do ruído de quantização dentro da banda de interesse depende da taxa de sobreamostragem pode-se adequar a Equação 6 para calcular a relação sinal-ruído de quantização (SQNR) máxima de um conversor AD, como mostra a Equação 7.

$$SQNR = 6,02 \times N + 1,76 + 10 \times \log(OSR) dB$$

(7)

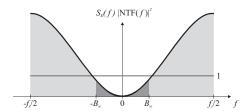

#### 2.1.4 *Noise-shaping*

A potência do ruído de quantização dentro da banda de sinal pode ser reduzida com o processamento do erro de quantização, possivelmente ao custo do aumento do ruído de

quantização fora da banda de sinal. Deste modo, o espectro plano do ruído de quantização é modificado resultando em um espectro modelado, como ilustra a Figura 7 (MALO-BERTI, 2007).

Figura 7: Efeito do noise-shaping em um SDM.

Destaca-se que o incremento do ruído de quantização em regiões de alta frequência não é crítico, pois utiliza-se um filtro digital depois do SDM que remove este ruído em altas frequências, ver Figura 1.

Considerando a quantização de um sinal sobreamostrado, e um elevado OSR, têmse que a amplitude do sinal de entrada irá mudar pouco em relação a última amostra. Conclui-se então que o erro de quantização e(n) entre uma amostra e outra será similar em baixas frequências e as maiores mudanças no valor do erro de quantização irão ocorrer em altas frequências (A. MORGADO; ROSA, 2011). Assim, para atenuar as componentes de baixa frequência do ruído de quantização basta subtrair a amostra anterior da amostra atual:

$$e_Q(n) = e(n) - e(n-1)$$

(8)

Adicionalmente, pode-se empregar um número maior de amostras anteriores durante o processamento do ruído de quantização (A. MORGADO; ROSA, 2011). Pode-se generalizar este procedimento no domínio Z empregando a transformada Z de acordo com a Equação 9.

$$e(z) = (1 - z^{-1})^L \times E(z)$$

(9)

onde E(z) é a transformada Z do ruído de quantização. Nota-se que o erro de quantização processado, e(z), é uma versão filtrada por um filtro passa-altas do erro de quantização original (A. MORGADO; ROSA, 2011). A função de transferência deste filtro é conhecida como função de transferência de ruído (NTF) e é definida como:

$$NTF(z) = (1 - z^{-1})^{L}$$

(10)

onde L é a ordem do filtro. Deste modo, pode-se calcular aproximadamente o valor do ruído dentro da banda de interesse de um conversor AD sobreamostrado,  $P_Q$ , através da Equação 11 (SCHREIER; TEMES, 2005).

$$P_Q = \frac{\Delta^2}{12} \times \frac{\pi^{(2L)}}{(2L+1) \times OSR^{(2L+1)}} \tag{11}$$

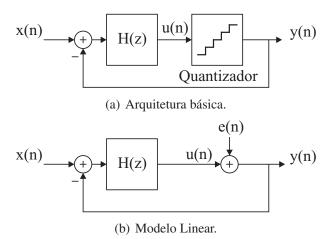

## 2.2 Modulador Sigma-Delta

A modulação sigma-delta é baseada na sobreamostragem e no emprego de *noise-shaping* para reduzir o ruído de quantização dentro da banda de sinal. Assim, a essência

de um modulador SD é a incorporação de um quantizador de N bits dentro de um laço realimentado.

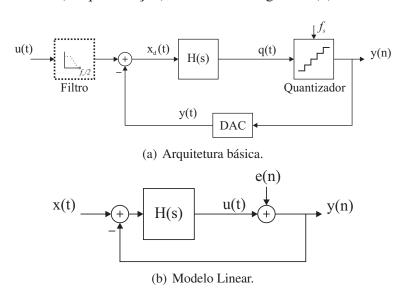

A arquitetura básica de um SDM, ilustrada na Figura 8(a), apresenta um sinal de entrada, x(n), que é amostrado, e após processado pelo bloco H(z) e convertido em um valor digital através do quantizador de N bits.

Figura 8: Modulador SD.

O laço de realimentação é composto por um conversor digital-analógico (DAC) de N bits, responsável pela geração de uma representação analógica do sinal digital, recém convertido pelo quantizador de N bits, que será subtraída do sinal de entrada na entrada do modulador.

O erro de quantização ocorre devido ao quantizador e é representado no modelo linear do SDM como uma adição de ruído branco junto ao quantizador, conforme Figura 8(b). Deste modo, o modulador pode ser analisado como um sistema de duas entradas cuja saída é representada no domínio Z como:

$$Y(z) = STF(z) \times X(z) + NTF(z) \times E(Z)$$

(12)

onde X(z), Y(z) e E(z) são, respectivamente, as representações dos sinais de entrada, de saída e do erro de quantização do SDM no domínio Z, STF(z) é a função de transferência do sinal de entrada e NTF(z) é a função de transferência do ruído de quantização.

Ambas funções de transferência podem ser obtidas através da escolha correta da função de transferência do laço H(z). Almeja-se que H(z) não influencie no sinal de entrada e filtre o ruído de quantização na banda de interesse. Deste modo, H(z) deve ser escolhida de tal maneira que a STF(z) se comporte como um filtro passa-baixas para o sinal de entrada e a NTF(z) se comporte como um filtro passa-altas para o ruído de quantização. A função de transferência H(z) que melhor se adéqua a estes propósitos é a de um integrador, que no domínio Z é expressa como:

$$H(z) = \frac{z^{-1}}{(1 - z^{-1})} \tag{13}$$

O diagrama de blocos de um SDM clássico de primeira ordem empregando a função de transferência H(z) da Equação 13 é apresentado na Figura 9. A representação no domínio Z do sinal de saída do modulador Y(z) é agora apresentado na Equação 14.

$$Y(z) = z^{-1} \times X(z) + (1 - z^{-1}) \times E(z)$$

(14)

A partir da Equação 14 é possível concluir que o sinal de entrada estará atrasado por um ciclo de sinal de relógio, enquanto o erro de quantização é filtrado por um filtro do tipo passa altas cuja função de transferência no domínio Z é  $(1-z^{-1})$ .

Figura 9: SDM de primeira ordem.

#### 2.2.1 Performance de Moduladores Sigma-Delta

A performance dos SDMs pode ser avaliada através de alguns parâmetros: faixa dinâmica, do inglês *Dynamic Range* (DR), relação sinal-ruído e distorção, do inglês *Signal-to-Noise-plus-Distortion Ratio* (SNDR), e número efetivo de bits, do inglês *Effective Number of Bits* (ENOB).

O DR é a amplitude do sinal de entrada em que o SNDR do modulador é igual a zero (MALOBERTI, 2007) e o seu valor é aproximadamente igual ao SNDR (JOHNS; MARTIN, 1997). O SNDR é taxa entre a potência do sinal (normalmente um sinal senoidal) e a potência do ruído total produzido pelo circuito e pelo processo de quantização, considerando também as distorções causadas pelo circuito do modulador (ORTAMANNS; GERFERS, 2006). Já o ENOB é a representação em bits do SNDR, ou seja, é a resolução de um ADC ideal necessária para o valor da relação sinal-ruído-de-quantização, do inglês *Signal-to-Quantization-Noise Ratio* (SQNR), deste ADC ser igual ao SNDR do modulador (JOHNS; MARTIN, 1997).

O DR ideal de um SDM é calculado através da Equação 15 (A. MORGADO; ROSA, 2011) e o ENOB pode ser calculado de através da Equação 16.

$$DR \approx SNDR \approx 10 \times \log_{10}(\frac{3}{2} \times (2^N - 1)^2 \times \frac{(2L + 1) \times OSR^{(2L + 1)}}{\pi^{(2L)}})$$

(15)

$$ENOB = \frac{SNDR - 1,76}{6,02} \tag{16}$$

onde N é o número de bits do quantizador, L é ordem do filtro e OSR é a taxa de sobreamostragem. A partir da Equação 15 nota-se que o SNDR é proporcional à taxa de sobreamostragem, à ordem do filtro e ao número de bits do quantizador. Assim, as estratégias para o incremento da performance de SDM são baseadas no incremento de um ou mais destes parâmetros.

#### 2.2.1.1 Aumento da ordem do filtro

O aumento da ordem do filtro de um SDM ocasiona o aumento de performance do DR. Entretanto, problemas de instabilidade surgem a partir do projeto de SDM com L>3 (SCHREIER; TEMES, 2005).

#### 2.2.1.2 Aumento da taxa de sobreamostragem

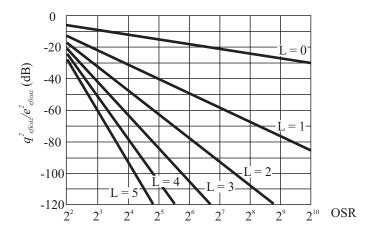

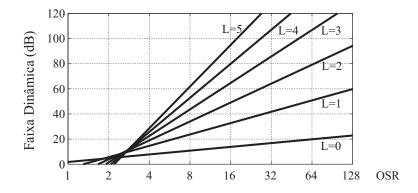

O aumento da taxa de sobreamostragem ocasiona um incremento do DR, e este é dependente da ordem L do filtro. Em um SDM de primeira ordem aumenta-se o DR em 1,5 bit/oitava de OSR. De maneira geral, pode-se dizer que o incremento da taxa de sobreamostragem gera um aumento de  $(2 \times L + 0, 5)$  bits/oitava no DR de um SDM com filtro de ordem L. A Figura 10 apresenta a potência do ruído de quantização dentro da banda de interesse em função da taxa de sobreamostragem para SDMs de ordem L. Já a Figura 11 ilustra o DR ideal em função da taxa de sobreamostragem de SDMs de ordem L (single-bit).

Figura 10: Potência teórica do ruído de quantização dentro da banda de interesse em função da taxa de sobreamostragem para SDMs de ordem L.

Figura 11: DR ideal de um SDM em função da taxa de sobreamostragem para SDMs de ordem L (*single-bit*).

#### 2.2.1.3 Aumento do número de bits do quantizador

O incremento do DR de um SDM é de aproximadamente 1 bit (6 dB) para cada bit extra do quantizador. Isto leva ao desenvolvimento de quantizadores e DACs multi-bit, que ao contrário de quantizadores e DACs de 1-bit, não são lineares.

As não-linearidades geradas pelo DAC multi-bit são adicionadas diretamente na entrada do modulador e não são reduzidas pelo *noise-shaping*. Deste modo, a linearidade do DAC deve possuir a mesma especificação de linearidade do SDM, o que incrementa a complexidade de projeto do DAC multi-bit, gerando também o incremento do consumo de energia do modulador.

#### 2.2.2 Classificação de Moduladores Sigma-Delta

Diferentes arquiteturas de SDMs já foram e continuam a ser reportadas na literatura (SCHREIER; TEMES, 2005) (ROSA, 2011). Tais arquiteturas foram desenvolvidas visando o aumento da performance dos SDMs através das estratégias citadas na subsecção anterior. Abaixo segue as principais classificações de SDMs.

#### 2.2.2.1 Banda de sinal

Os SDMs podem ser empregados para o processamento de sinais em banda base com frequência intermediária (IF) igual a zero ou diferente de zero. Os SDMs do tipo passabaixas são empregados para processamento de sinais de banda base com IF igual a zero e os SDMs do tipo passa-banda são empregados para processamento de sinais com IF diferente de zero.

#### 2.2.2.2 Número de bits do quantizador

Os SDMs podem ser classificados como *single-bit* ou multi-bit, conforme o número de bits do quantizador (RíO *et al.*, 2006).

#### 2.2.2.3 Número de quantizadores

Os SDMs que possuem apenas um quantizador são classificados como estruturas de laço único, do inglês *single-loop*. Já os SDMs que apresentam mais de um quantizador, e consequentemente mais que um laço, são classificados como SDMs em cascata. Filtros do laço de estruturas de laço único de ordem superior a dois estão sujeitos a instabilidade (SCHREIER; TEMES, 2005). Assim, os SDMs em cascata são utilizados para gerar um *noise-shaping* de ordem elevada, empregando mais de um laço de ordem, geralmente, menor ou igual a 2 (ORTAMANNS; GERFERS, 2006).

#### 2.2.2.4 Natureza do laço

Os SDMs são classificados em relação a natureza do laço basicamente em dois grupos: os SDMs em tempo discreto e os SDMs em tempo contínuo, foco deste trabalho. Recentemente, outro tipo de classificação surgiu: os SDMs híbridos, que misturam as características de ambos, SDMs-DT e SDMs-CT (MORGADO; ROSA; RIO, 2009).

#### 2.2.2.5 Estado da arte

Visto que os SDMs são amplamente estudados e pesquisados é mantido em (ROSA, 2013) um estudo e análise de performance dos SDMs publicados na literatura. Esta lista é atualizada a cada 6 meses e possibilita uma comparação com os SDMs estado da arte. Este levantamento é efetuado considerando apenas os trabalhos apresentados em revistas, jornais e conferências de impacto na área de projeto e análise de circuitos integrados.

## 2.3 Considerações

Neste Capítulo foram fornecidos os conceitos básicos sobre modulação sigma-delta e as principais características dos SDMs. O foco deste trabalho de mestrado concentra-se no estudo, análise e projeto de SDMs-CT do tipo passa baixas de laço único, *single-bit*. Assim, para mais detalhes sobre as diferentes arquiteturas e topologias de SDMs pode-se recorrer aos diversos livros e artigos encontrados na literatura (MALOBERTI,

2007) (A. MORGADO; ROSA, 2011) (ROSA; RIO, 2013) (ROSA, 2011) (SCHREIER; TEMES, 2005) (ORTAMANNS; GERFERS, 2006).

Na próximo Capítulo serão apresentadas as principais características e os fundamentos teóricos para a interpretação, análise e projeto de SDMs-CT.

## 3 MODULADORES SD EM TEMPO CONTÍNUO

## 3.1 Introdução

Desde o surgimento da modulação SD na década de 60 (CLUTER, 1960) e do primeiro SDM reportado (INOSE; YASUDA; MURAKAMI, 1962), diversos avanços e melhorias nas diferentes topologias de SDMs foram apresentados na literatura.

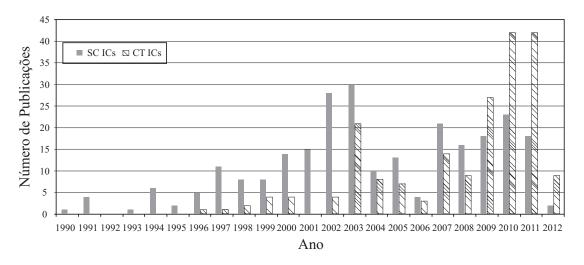

A maioria dos SDM reportados na literatura nos últimos tempos foram implementados em tempo discreto, normalmente através do emprego de técnicas à capacitor-chaveado ou, de modo minoritário, com técnicas de chaveamento em corrente (ROSA; RODRIGUEZ-VAZQUEZ; PEREZ-VERDU, 2002) (ROSA, 2011). Entretanto, a demanda de SDMs para aplicações em circuitos de comunicação que operam em alta velocidade e com elevada performance aumentou o interesse no desenvolvimento de SDMs em tempo contínuo (BREEMS; HUIJING, 2001) (CHERRY; SNELGROVE, 2000) (ORTAMANNS; GERFERS, 2006) (KULCHYCKI, 2008). A Figura 12 compara o número de SDMs à capacitor chaveado e o número de SDMs-CT publicados nos últimos anos (ROSA; RIO, 2013). Nota-se com base nesta Figura uma tendência do uso e desenvolvimento de técnicas de projeto de SDMs-CT.

Figura 12: Número de SDMs à capacitor chaveado e número de SDMs-CT publicados de 1990-2012.

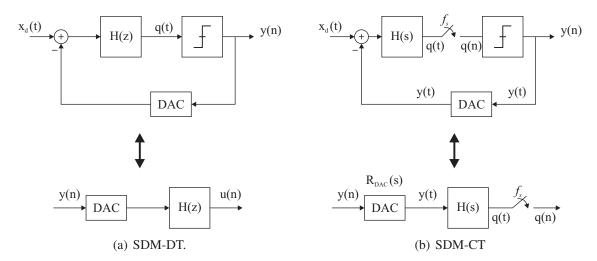

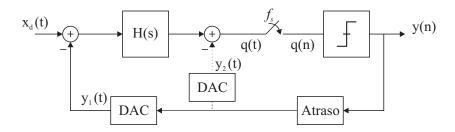

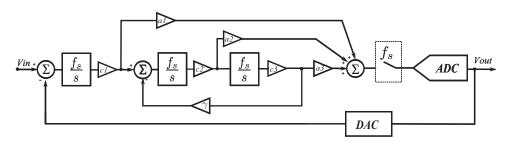

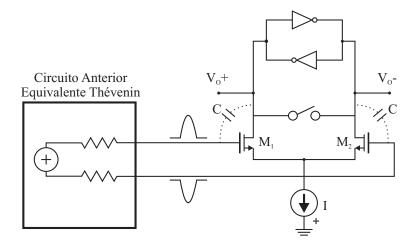

#### 3.2 Características dos SDMs-CT

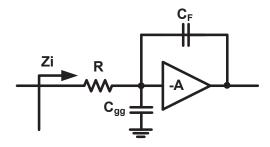

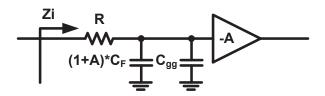

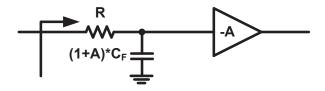

No capítulo anterior foi apresentada a teoria básica sobre modulação SD tomando como base a implementação clássica em tempo discreto. Entretanto, o filtro do laço do modulador pode ser desenvolvido em tempo contínuo, ou seja, com o emprego de integradores e ressonadores analógicos não chaveados. A Figura 13(a) apresenta a arquitetura básica de um SDM-CT de primeira ordem, que apresenta como blocos básicos um filtro no laço, um quantizador e um DAC. Adicionalmente, pode-se empregar um filtro antialias na entrada do modulador.

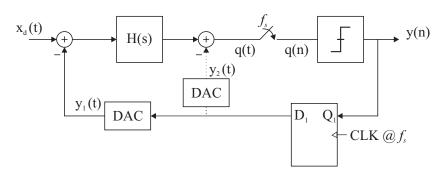

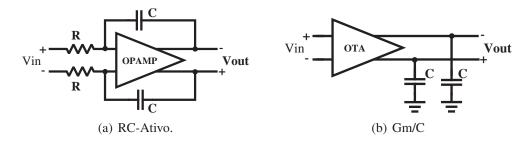

O filtro do laço, cuja função de transferência é representada por H(s), é um filtro analógico que pode ser realizado através de integradores do tipo RC-ativo, integradores Gm/C ou ainda ressonadores LC. A ordem do filtro do laço fornece a ordem do SDM.

Destaca-se também que a amostragem dos sinais é efetuada à uma frequência de amostragem  $f_s$  no quantizador do modulador. Como o erro de quantização é gerado pelo quantizador, pode-se empregar também um modelo linear do quantizador com a adição de uma fonte de ruído branco (de quantização), ilustrado na Figura 13(b).

Figura 13: Modulador SD em tempo contínuo.

#### 3.2.1 Amostragem

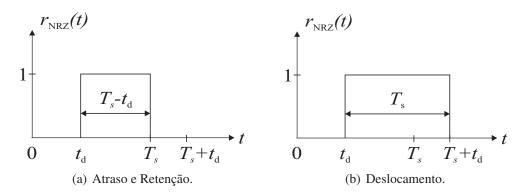

A principal diferença entre um SDM-CT e um SDM-DT é que no primeiro a amostragem ocorre dentro do laço do modulador e no segundo a amostragem ocorre normalmente em um circuito *sample-and-hold* na entrada do modulador (ORTAMANNS; GERFERS, 2006). Geralmente o *sample-and-hold* insere erros no sistema e como estes erros são inseridos na entrada do modulador eles são tratados como sinal de entrada e não sofrem o efeito do *noise-shaping*, reduzindo assim o *noise-floor* do modulador e a performance do mesmo. Já em um SDM-CT as não-idealidades devido ao processo de amostragem sofrem o efeito do *noise-shaping* e não degradam de forma demasiada a performance do modulador (CHERRY; SNELGROVE, 2000). Outra característica oriunda da localização do processo de amostragem é o filtro anti-alias implícito ao modulador, o que é discutido com mais detalhes na próxima seção.

#### **3.2.2** Filtro

Os sinais internos ao laço dos SDMs-CT são analógicos e representados por formas de onda contínuas no tempo, apresentando perturbações de baixa amplitude de tensão devido a inexistência de chaveamento dentro do laço. Isto fornece um nó de terra virtual com baixo ruído e boa linearidade (ORTAMANNS; GERFERS, 2006).

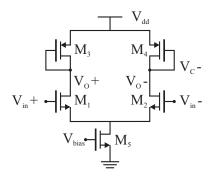

A função de transferência do filtro é implementada através de integradores analógicos. Diferentemente dos SDMs-DT onde os ganhos dos integradores são determinados através da razão entre duas capacitâncias (SCHREIER; TEMES, 2005), os ganhos dos integradores analógicos dos SDMs-CT dependem de componentes como resistores e capacitores em um integrador do tipo RC-ativo, ou da razão entre a transcondutância de um OTA e um capacitor em um integrador do tipo Gm/C (JOHNS; MARTIN, 1997). É possível concluir que o coeficiente de um integrador analógico em tempo contínuo está sujeito às variações de processo inerentes ao processo de fabricação da tecnologia CMOS, o que pode levar à mudança da função de transferência do filtro podendo reduzir a performance ou ainda gerar instabilidade no modulador.

O filtro de um SDM-CT é composto por componentes passivos e ativos, e estes componentes podem apresentar não-linearidades, além de contribuir com a geração de ruído, o que acaba por limitar a performance do modulador. Deste modo, deve-se analisar principalmente as especificações de ruído e linearidade na entrada do modulador pois o ruído na entrada do modulador estará presente na saída do mesmo, aumentando o ruído dentro da banda de interesse do SDM. Então, pode-se concluir que a exatidão do sistema está diretamente relacionada com a exatidão do estágio de entrada do modulador.

#### 3.2.3 Quantizador

Como característica genérica de SDMs o quantizador pode ser *single-bit* ou multibit, o que impacta no número de bits do DAC. Porém, em SDMs-CT o tempo necessário para se efetuar o processo de quantização deve ser extremamente rápido para gerar os sinais que controlam o DAC, que por sua vez gera os sinais em tempo contínuo para efetuar a realimentação do laço. O tempo necessário entre o processo de quantização e a geração dos sinais de realimentação do laço, oriundos do DAC, é um dos limitantes da performance dos SDMs-CT, conhecido como atraso excessivo do laço de realimentação, do inglês *Excess Loop Delay* (ELD). Maiores detalhes serão fornecidos na seção 3.5.

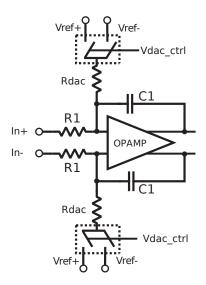

#### 3.2.4 DAC

O DAC é o circuito responsável por gerar os sinais de realimentação do laço. Em um SDM-DT os sinais de referência gerados pelo DAC são amostrados e integrados através de um capacitor em um SDM à capacitor-chaveado ou em um integrador de corrente em um SDMs implementado com técnicas de chaveamento em corrente. Destaca-se que a integração ocorre em apenas uma fase de operação do SDMs-DT.

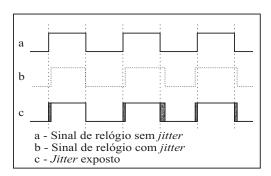

Já em SDMs-CT o sinal de referência gerado pelo DAC, e empregado durante a realimentação do laço, é integrado ao longo do tempo e deve ser atualizado exatamente a cada ciclo de relógio. Qualquer atraso na atualização do sinal de realimentação impactará na performance do modulador. Com base nisso, nota-se uma sensibilidade do SDMs-CT em relação a qualidade do sinal de relógio, especificamente em relação ao *jitter* e ruído de fase. Maiores detalhes sobre o efeito do *jitter* do relógio em SDMs-CT serão abordados na seção 3.5.

#### 3.2.4.1 Formas de Onda dos DACs

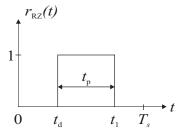

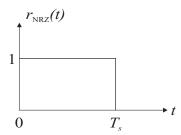

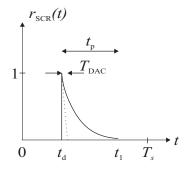

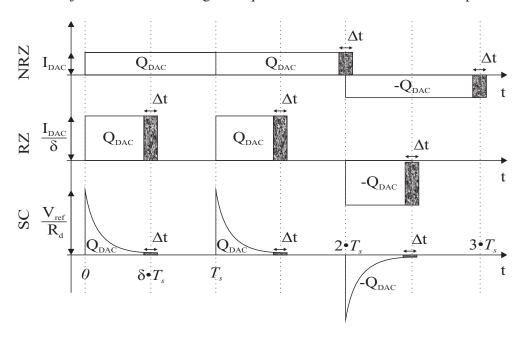

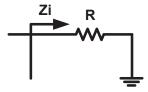

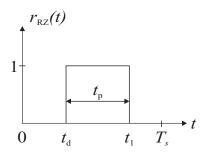

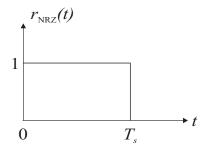

Em SDMs-CT pode-se empregar DACs com diferentes formas de onda de saída. As formas de onda de saída dos DACs clássicos são retangulares e conhecidos como DACs com formas de onda com retorno para zero (RZ) e DACs com formas de onda sem retorno para zero (NRZ), ilustradas nas Figuras 14 e 15, respectivamente.

Em um DAC RZ o sinal gerado apresenta o valor de referência durante um determinado tempo  $t_p$  do período  $T_s$ , e no restante do período o valor do sinal de referência é igual a zero. Já em um DAC NRZ o sinal de referência gerado é mantido constante durante todo o período  $T_s$ . A polaridade do sinal gerado varia de acordo com o sinal de controle gerado pelo quantizador.

Figura 14: Forma de onda de um DAC RZ de 1 bit.

Figura 15: Forma de onda de um DAC NRZ de 1 bit.

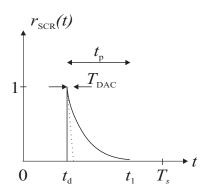

Outro DAC bastante empregado é o DAC SCR, que gera uma forma de onda exponencial semelhante a forma de onda da descarga de um capacitor. Neste DAC a forma de onda apresenta um pico de sinal cujo valor é igual ao sinal de referência e este sofre uma descarga do tipo exponencial de duração  $t_p$  durante parte do período  $T_s$ .

Também é importante destacar que a forma de onda do DAC influencia diretamente no projeto do laço dos SDMs-CT, como abordado na seção 3.4.

Figura 16: Forma de onda de um DAC SCR.

## 3.3 Vantagens dos SDMs-CT

Nesta seção são sintetizadas, de modo geral, as principais características e vantagens dos SDMs-CT em relação aos seus homólogos em tempo discreto. O fundamento teórico para compreender tais vantagens foi apresentado nas seções anteriores.

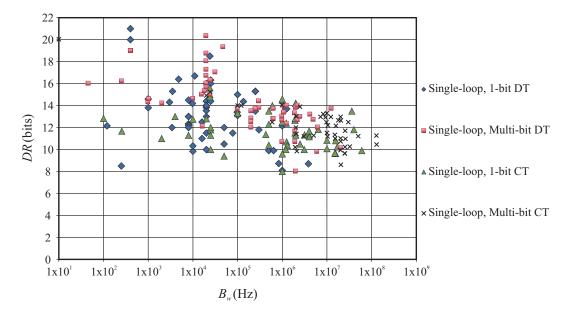

Os SDMs-CT são conhecidos por trabalharem com maiores taxas de amostragem e com menor consumo de energia se comparados com os SDMs-DT. Isto possibilita o seu emprego em receptores de rádio-frequência e em aplicações de alta velocidade, antes não abrangidas por SDMs (A. MORGADO; ROSA, 2011). A Figura 17 apresenta um comparativo entre o DR e a banda de sinal de entrada de SDMs (ROSA, 2011). Nota-se que com SDMs-CT a banda de sinal de entrada atingida é maior, ao custo de uma redução no DR do modulador.

Figura 17: DR versus banda de sinal de SD.

A etapa de amostragem em SDMs-CT não ocorre na entrada do modulador e sim antes do quantizador, após o filtro do laço. Esta construção possibilita uma redução do consumo de energia em relação aos demais conversores AD e SDMs-DT visto que não é necessário um estágio de ganho de alta velocidade para o circuito amostrador na entrada do ADC. Adicionalmente, torna-se mais fácil acionar a entrada do modulador, e a injeção de ruído dentro do sistema é menor do que em um sistema com amostragem na entrada (KULCHYCKI, 2008).

Outra vantagem comumente citada é o AAF implícito, que pode reduzir os requisitos do AAF na entrada do ADC, ou ainda eliminar a necessidade do mesmo. Esta característica é possível devido ao processo de amostragem ocorrer antes do quantizador e pelo fato do modulador possuir um filtro do tipo passa-baixas no laço. Entretanto, é necessário analisar a topologia do modulador e a sua construção em nível elétrico visto que o AAF intrínseco pode ter suas características degradadas (PAVAN, 2011), ou mesmo não existir quando se utiliza a topologia descrita em (SILVA *et al.*, 2001).

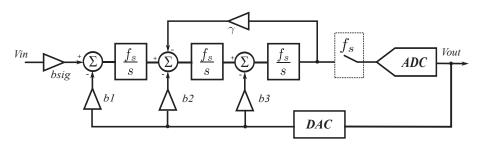

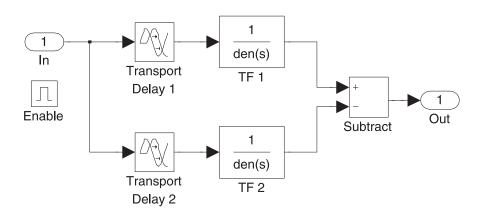

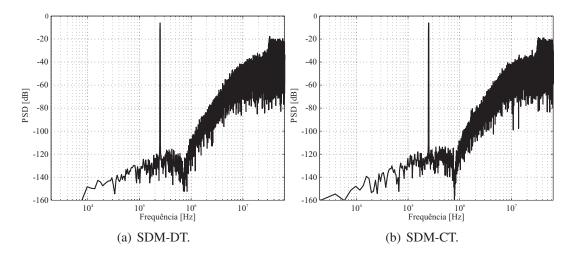

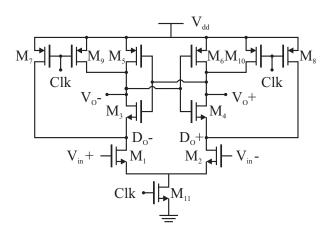

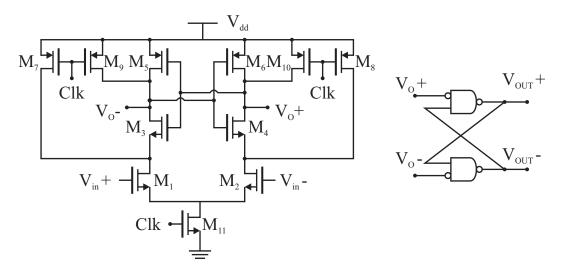

Para ilustrar o efeito do AAF implícito ao laço é apresentada a simulação em alto nível do SDM-CT apresentado em (AGUIRRE *et al.*, 2013), projetado através do seu homólogo em tempo discreto com o emprego da metodologia de projeto de conversão DT/CT, discutida em 3.4.1. O modulador em questão é do tipo passa-baixas de laço

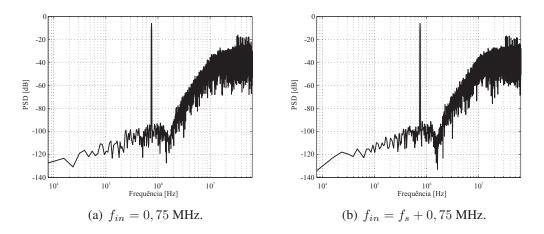

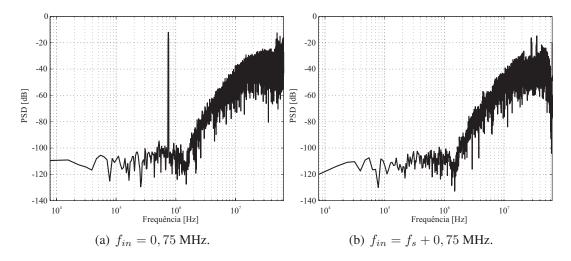

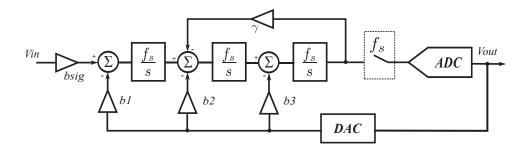

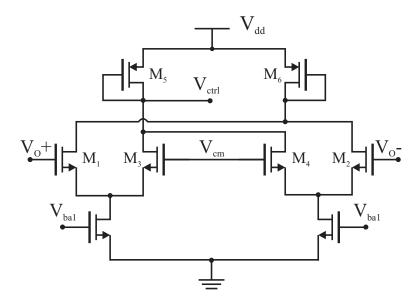

único, terceira ordem e *single-bit* com topologia do tipo Cascata de Integradores com Realimentação (CIFB), ilustrado na Figura 18, projetado para uma banda de sinal de 2 MHz e  $f_s$  de 128 MHz. Primeiramente, simulou-se o SDM-DT aplicando um sinal puramente senoidal com frequência de entrada  $f_{in}$  de 0,75 MHz, e após aplicando um sinal senoidal com  $f_{in}$  de 128,75 MHz, ou seja  $f_s + f_{in}$ . O espectro de densidade de potência (PSD) do modulador para ambas as simulações é apresentado na Figura 19. Nota-se em 19(b) que ocorreu alias do sinal de entrada e surge no espectro de saída do modulador uma componente de frequência de 0,75 MHz de mesma amplitude do sinal com  $f_{in}$  de 128,75 MHz. A mesma simulação foi efetuada para versão em tempo contínuo deste modulador e os resultados são apresentados em 20. Nota-se em 20(b) que para uma  $f_{in}$  de 128,75 MHz a componente de frequência de 0,75 MHz não aparece no PSD de saída do modulador, comprovando o funcionamento do AAF implícito de SDMs-CT.

Figura 18: Topologia CIFB de terceira ordem.

Figura 19: SDM-DT: AAF.

Outra vantagem dos SDMs-CT é a sua tolerância às imperfeições dos circuitos analógicos que o compõe, quando comparados com SDMs-DT e outras topologias de ADCs, tornando-os uma ótima escolha para o projeto de ADCs em circuitos integrados CMOS em escala nanométrica e em modernos SoC (A. MORGADO; ROSA, 2011). Isto é possível pois em SDMs-CT o impacto do ruído e das não-linearidade associadas ao processo de amostragem é reduzida significativamente, garantindo o seu emprego em tecnologias com tensão de alimentação reduzida. Adicionalmente, com o *scaling* das tecnologias CMOS ocorre um incremento da corrente de fuga dos transistores o que deteriora a qualidade das chaves CMOS reduzindo a performance dos moduladores à capacitor-chaveado.

Também, pode-se reduzir o consumo de energia para determinada frequência de amostragem se SDMs-CT forem utilizados. Isto é explicado pois os integradores a capacitores-

Figura 20: SDM-CT: AAF.

chaveados de SDMs-DT demandam amplificadores operacionais com frequência de ganho unitário entre oito a dez vezes a frequência de amostragem e um ganho tipicamente acima de 80 dB para fornecer um tempo de estabilização adequado aos sinais internos do modulador. Já os integradores dos SDMs-CT necessitam de amplificadores com frequência de ganho unitário de uma a duas vezes o valor da frequência de amostragem e um ganho DC comumente na faixa de 40 a 60 dB, reduzindo drasticamente o consumo de energia do modulador (ORTAMANNS; GERFERS, 2006).

# 3.4 Metodologias de Projeto em Alto Nível de SDMs-CT

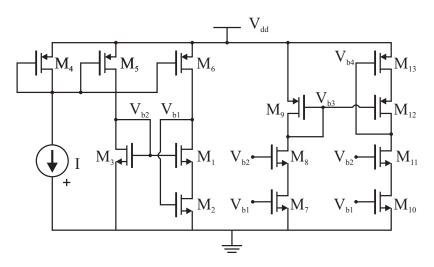

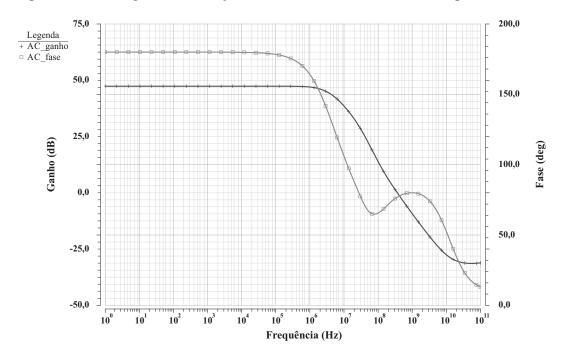

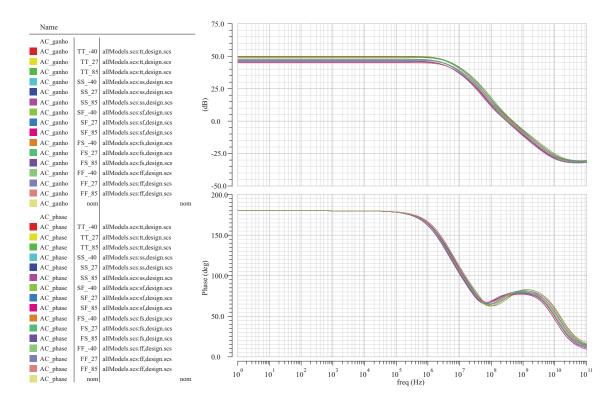

O projeto em alto nível de SDMs-CT começa a partir da definição da largura de banda (BW) e da relação sinal-ruído (SNR) do modulador. Para isto, é necessário o conhecimento prévio da aplicação e do sistema onde o modulador será inserido. Com base nestas informações parte-se para a definição das especificações do modulador, como definição do OSR, e consequentemente da frequência de amostragem, da ordem do modulador e do número de bits do quantizador.