#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### MARCO ANTONIO ZANATA ALVES

# **Increasing Energy Efficiency of Processor Caches via Line Usage Predictors**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Dr. Philippe O. A. Navaux Advisor

#### CIP - CATALOGING-IN-PUBLICATION

Alves, Marco Antonio Zanata

Increasing Energy Efficiency of Processor Caches via Line Usage Predictors / Marco Antonio Zanata Alves. – Porto Alegre: PPGC da UFRGS, 2014.

116 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2014. Advisor: Philippe O. A. Navaux.

1. Line Usage Predictors. 2. Sub-block Usage Predictors. 3. Replacement Policy. 4. Early Write-Back. 5. Cache Memories. 6. Energy Efficient. I. Navaux, Philippe O. A.. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Pró-Reitor de Coordenação Acadêmica: Prof. Pedro Cezar Dutra Fonseca Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### **ACKNOWLEDGEMENTS**

To all my family, friends, collaborators and advisors a sincere thank you.

### **LIST OF FIGURES**

| Figure 1.1:  | Breakdown of Core 2 Duo energy consumption                                  |    |

|--------------|-----------------------------------------------------------------------------|----|

| Figure 1.2:  | Breakdown of Sandy Bridge energy consumption                                | 24 |

| Figure 2.1:  | Opportunities for increasing the cache memory efficiency                    | 30 |

| Figure 2.2:  | Overall cache energy consumption for the oracle line usage and ora-         |    |

|              | cle sub-block usage predictors                                              | 31 |

| Figure 3.1:  | SiNUCA architecture with its main components and interconnections.          | 41 |

| Figure 3.2:  | Results for the single-threaded microbenchmarks                             | 54 |

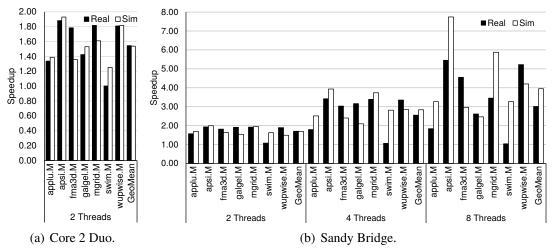

| Figure 3.3:  | Results for the SPEC-CPU2006 suite                                          | 57 |

| Figure 3.4:  | Results for the SPEC-OMP2001 suite                                          | 58 |

| Figure 3.5:  | Results for the NAS-NPB suite                                               | 58 |

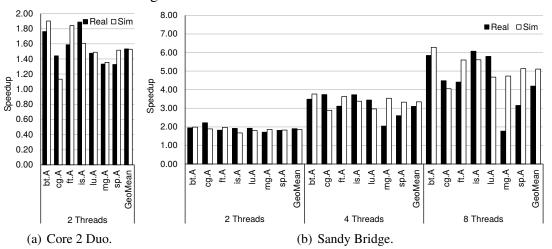

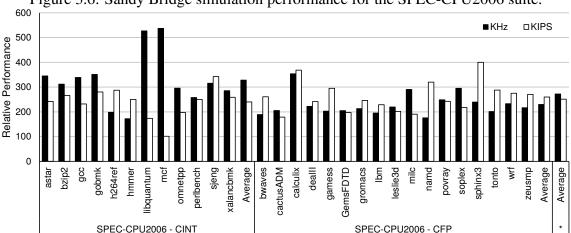

| Figure 3.6:  | Sandy Bridge simulation performance for the SPEC-CPU2006 suite              | 60 |

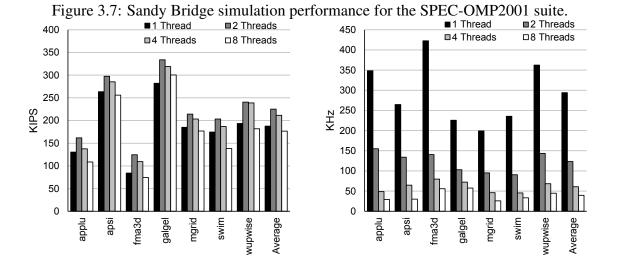

| Figure 3.7:  | Sandy Bridge simulation performance for the SPEC-OMP2001 suite.             | 61 |

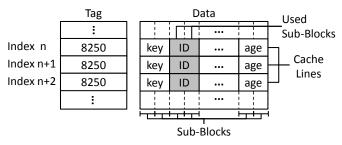

| Figure 4.1:  | Scenario with low cache sub-block usage                                     | 64 |

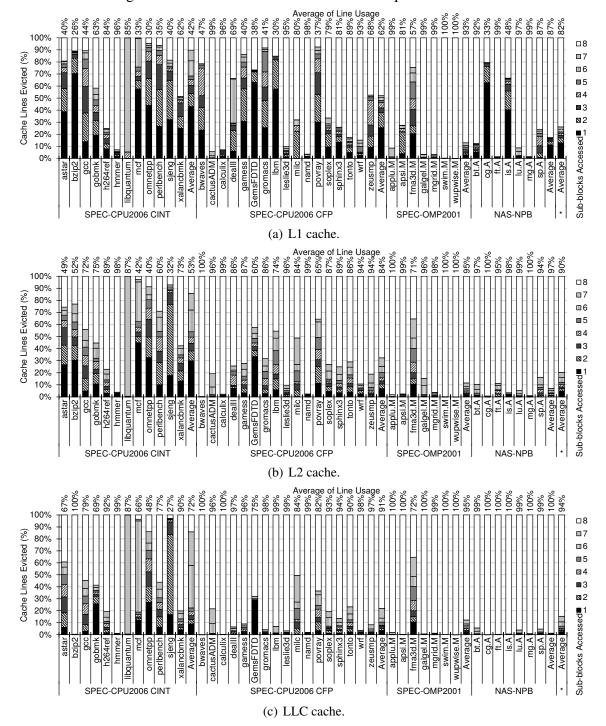

| Figure 4.2:  | Number of sub-blocks accessed per cache line                                | 65 |

| Figure 4.3:  | Number of sub-block accesses before cache line eviction                     | 66 |

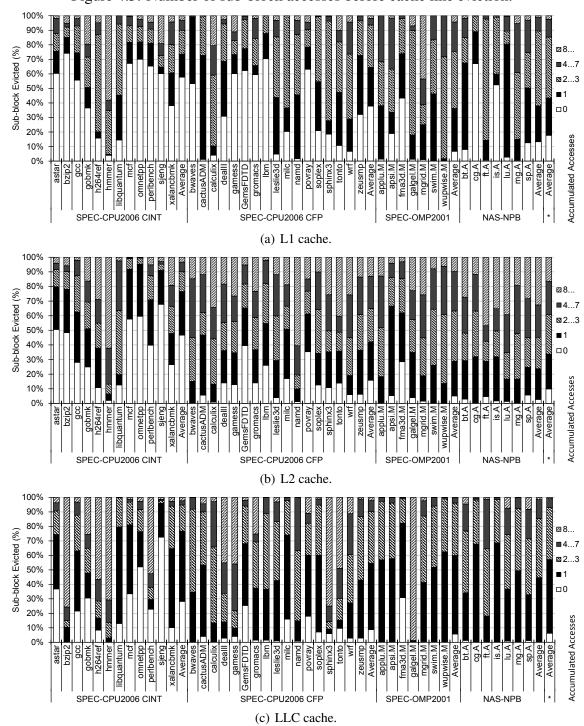

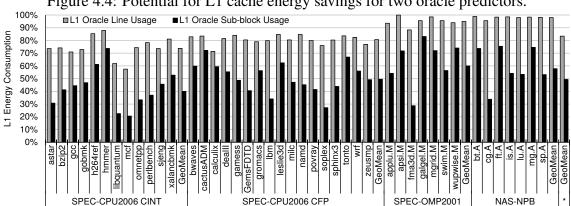

| Figure 4.4:  | Potential for L1 cache energy savings for two oracle predictors             | 67 |

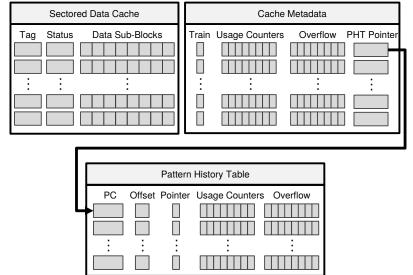

| Figure 4.5:  | DSBP: Mechanism architecture including cache metadata and PHT               | 68 |

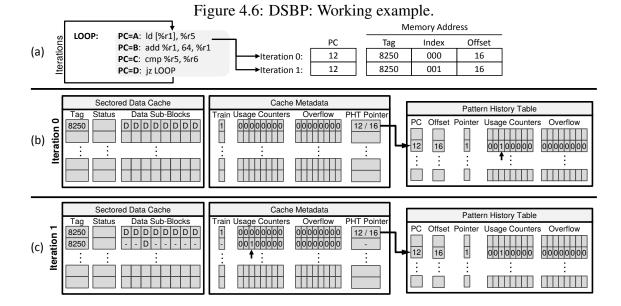

| Figure 4.6:  | DSBP: Working example                                                       | 70 |

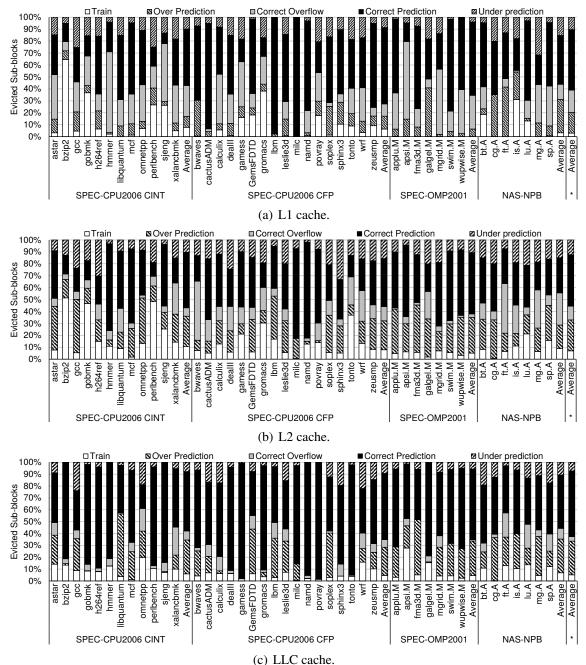

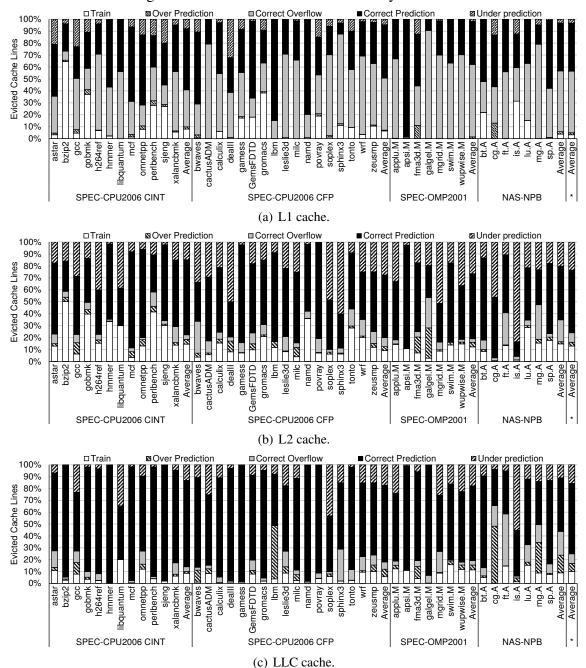

| Figure 4.7:  | DSBP: Mechanism accuracy results                                            | 73 |

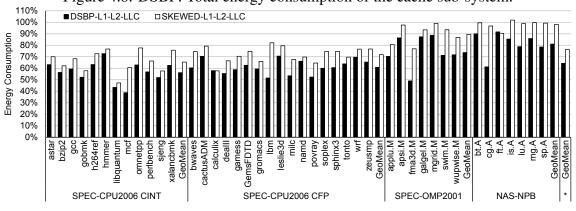

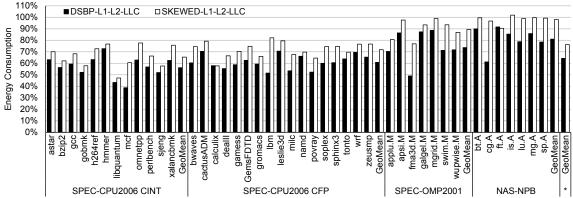

| Figure 4.8:  | DSBP: Total energy consumption of the cache sub-system                      | 74 |

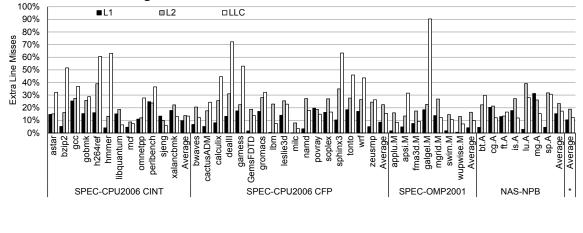

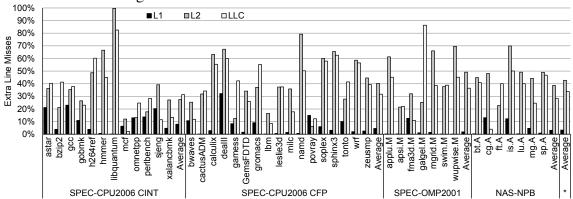

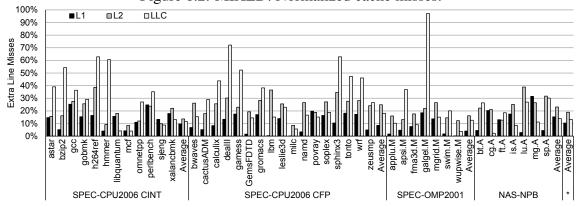

| Figure 4.9:  | DSBP: Normalized extra cache misses                                         | 76 |

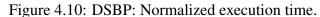

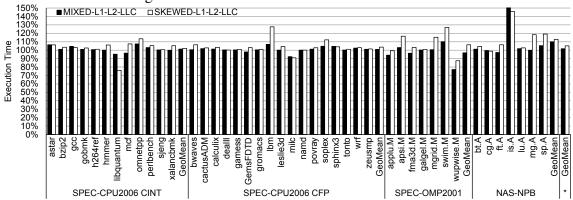

| Figure 4.10: | DSBP: Normalized execution time                                             | 76 |

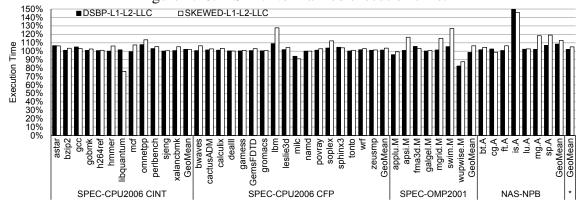

| Figure 4.11: | DSBP: Pattern History Table (PHT) design space exploration                  | 77 |

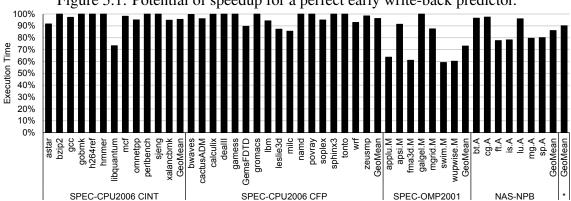

| Figure 5.1:  | Potential of speedup for a perfect early write-back predictor               | 80 |

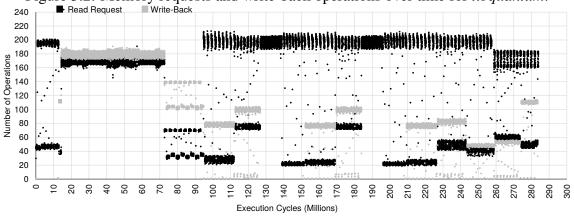

| Figure 5.2:  | Memory requests and write-back operations over time for <i>libquantum</i> . | 81 |

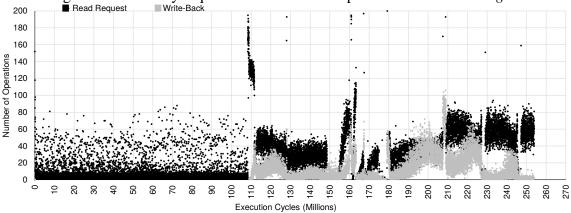

| Figure 5.3:  | Memory requests and write-back operations over time for gcc                 | 81 |

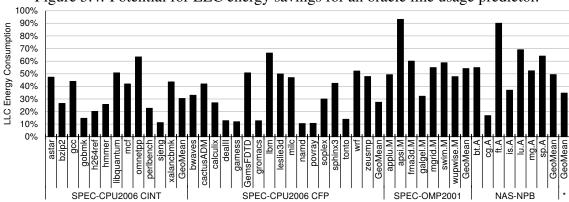

| Figure 5.4:  | Potential for LLC energy savings for an oracle line usage predictor         | 82 |

| Figure 5.5:  | DEWP: Mechanism architecture including cache metadata and AHT.              | 83 |

| Figure 5.6:  | DEWP: Mechanism accuracy results                                            | 87 |

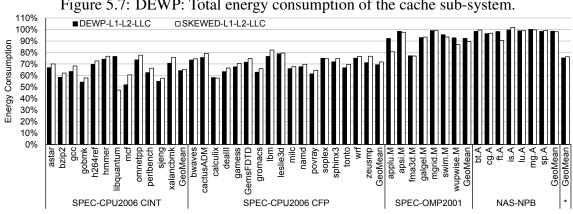

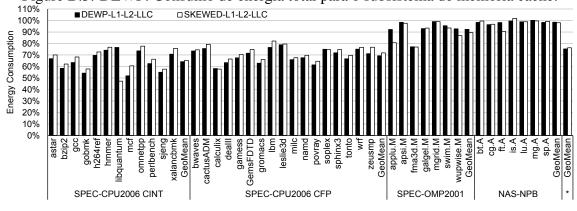

| Figure 5.7:  | DEWP: Total energy consumption of the cache sub-system                      | 88 |

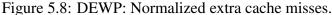

| Figure 5.8:  | DEWP: Normalized extra cache misses                                         | 88 |

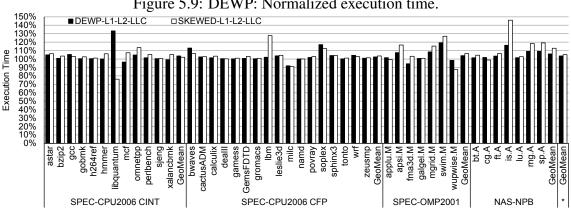

| Figure 5.9:  | DEWP: Normalized execution time                                             | 88 |

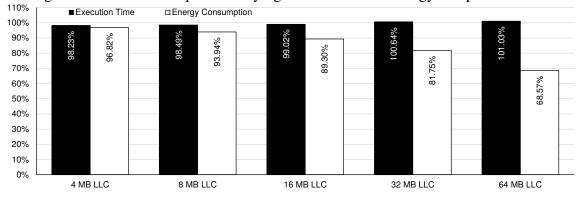

| •            | DEWP: Impact of varying the LLC size on energy and performance              | 90 |

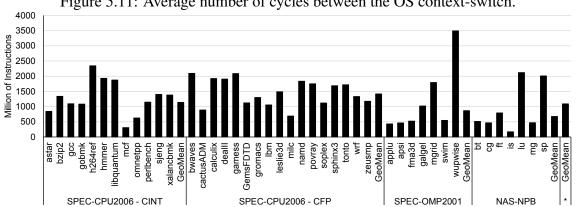

|              | Average number of cycles between the OS context-switch                      | 91 |

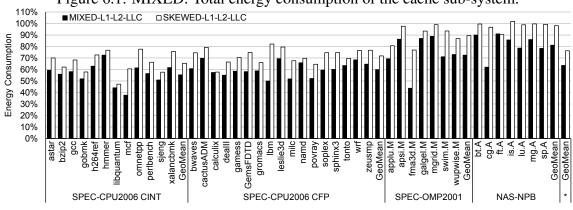

| Figure 6.1: | MIXED: Total energy consumption of the cache sub-system | 94 |

|-------------|---------------------------------------------------------|----|

| Figure 6.2: | MIXED: Normalized cache misses                          | 94 |

| Figure 6.3: | MIXED: Normalized execution time                        | 96 |

### **LIST OF TABLES**

| Table 2.1:  | State-of-the-art last access predictors                        | 34 |

|-------------|----------------------------------------------------------------|----|

| Table 2.2:  | State-of-the-art last write predictors                         | 35 |

| Table 3.1:  | Comparison of state-of-the-art simulators                      | 40 |

| Table 3.2:  | Source code example written in C and Assembly                  | 45 |

| Table 3.3:  | SiNUCA traces for a simple source code                         | 45 |

| Table 3.4:  | Average number of instructions (millions) per thread           | 49 |

| Table 3.5:  | Memory footprint of the benchmarks                             | 50 |

| Table 3.6:  | Parameters to model the Core 2 Duo and Sandy Bridge processors | 51 |

| Table 3.7:  | Single-threaded microbenchmarks results for Core 2 Duo         | 52 |

| Table 3.8:  | Single-threaded microbenchmarks results for Sandy Bridge       | 53 |

| Table 3.9:  | Multi-threaded microbenchmarks results for Core 2 Duo          | 55 |

| Table 3.10: | Multi-threaded microbenchmarks results for Sandy Bridge        | 55 |

| Table 4.1:  | DSBP: Total energy consumption of the cache sub-system         | 75 |

| Table 5.1:  | DEWP: Total energy consumption of the cache sub-system         | 89 |

| Table 6.1:  | MIXED: Total energy consumption of the cache sub-system.       | 95 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

**AHT** Access History Table

AIP Access Interval Predictor

AL Added Latency for column accesses

**BBV** Basic Block Vector

**BTB** Branch Target Buffer

CAS Column Address Strobe

**CCD** Column to Column Delay

**CMP** Chip Multiprocessor

**CMT** Chip Multithreading

CWD Column Write Delay

**DBI** Dynamic Binary Instrumentation

**DDR** Double Data Rate

**DEWP** Dead Line and Early Write-Back Predictor

**DRAM** Dynamic Random Access Memory

**DSBP** Dead Sub-Block Predictor

**FAW** Four row Activation Window

FCFS First-Come First-Serve

**GAg** Global Adaptive branch prediction using one Global PHT

GAs Global Adaptive branch prediction using per-Set PHT

GCC GNU Compiler Collection

**GEMS** General Execution-driven Multiprocessor Simulator

**ILP** Instruction Level Parallelism

**IPC** Instructions per Cycle

**ISA** Instruction Set Architecture

**KIPS** Kilo Instructions per Second

**LFSR** Linear Feedback Shift Register

LLC Last-Level Cache

LRU Least Recently Used

LTP Last-Touch Predictor

LvP Live-time Predictor

**LWP** Last Write Predictor

McPAT Multi-core Power, Area, and Timing

**MOB** Memory Order Buffer

**MPKI** Misses per Kilo Instructions

**MSHR** Miss-Status Handling Registers

**NAS** Numerical Aerodynamic Simulation

NoC Network-on-Chip

**NUCA** Non-Uniform Cache Architecture

**NUMA** Non-Uniform Memory Access

**OoO** Out-of-Order

**OpenMP** Open Multi-Processing

**OS** Operating System

PAg Per-address Adaptive branch prediction using one Global PHT

PAs Per-address Adaptive branch prediction using per-Set PHT

**PC** Program Counter

**PCM** Performance Counter Monitor

**PHT** Pattern History Table

**RAPL** Running Average Power Limit

RAS Row Address Strobe

**RAT** Registers Alias Table

RC Row Cycle

**RCD** RAS to CAS Delay

**ROB** Reorder Buffer

**RP** Row Precharge

**RRD** Row to Row activation Delay

RTP Read To Precharge

**SDP** Skewed Dead-Block Predictor

SFP Spatial Footprint Predictor

**SiNUCA** Simulator of Non-Uniform Cache Architectures

**SMT** Simultaneous Multi-Threading

**SPP** Spatial Pattern Predictor

SSV Search Set Vector

TLB Translation Look-aside Buffer

TLP Thread Level Parallelism

VWQ Virtual Write Queue

**WR** Write To Read delay time

WTR Write Recovery time

### **CONTENTS**

| ABS1                                    | TRACT                                                                                | 19                               |

|-----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|

| RESU                                    | JMO                                                                                  | 21                               |

| 1 IN<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | The Problem Motivation Hypotheses and Objectives Contributions Document Organization | 23<br>23<br>25<br>26<br>27<br>27 |

| 2 E                                     | NERGY EFFICIENCY IN CACHE MEMORIES                                                   | 29                               |

| 2.1                                     | Sources of Inefficiency in Cache Memories                                            | 29                               |

| 2.2                                     | Related work                                                                         | 32                               |

| 2.2.1                                   | Line Usage Predictors                                                                | 32                               |

| 2.2.2                                   | Counter Based Dead Line Predictor                                                    | 33                               |

| 2.2.3                                   | Trace Based Dead Line Predictors                                                     | 33                               |

| 2.2.4                                   | Time Based Dead Line Predictors                                                      | 33                               |

| 2.2.5                                   | Last Write Predictors                                                                | 34                               |

| 2.2.6                                   | Overall Comparison                                                                   | 34                               |

| 3 S                                     | IMULATOR OF NON-UNIFORM CACHE ARCHITECTURE (SINUCA)                                  | 37                               |

| 3.1                                     | Related Work                                                                         | 38                               |

| 3.2                                     | SiNUCA                                                                               | 40                               |

| 3.2.1                                   | System Model                                                                         | 41                               |

| 3.2.2                                   | Processor Description                                                                | 43                               |

| 3.2.3                                   | Simulator Traces                                                                     | 44                               |

| 3.2.4                                   | Energy Modeling                                                                      | 46                               |

| 3.3                                     | Microbenchmarks                                                                      | 47                               |

| 3.3.1                                   | Single-Threaded Microbenchmarks                                                      | 47                               |

| 3.3.2                                   | Multi-Threaded Microbenchmarks                                                       | 48                               |

| 3.4                                     |                                                                                      | 49                               |

| 3.4.1                                   | Methodology                                                                          | 49                               |

| 3.4.2                                   | Results                                                                              | 52                               |

| 3.4.3                                   | Sources of Difference                                                                | 57                               |

| 3.4.4                                   | Simulator Performance                                                                | 60                               |

| 3.5                                     | Summary                                                                              | 61                               |

| 4 C           | DEAD SUB-BLOCK PREDICTOR (DSBP)                     | 63  |

|---------------|-----------------------------------------------------|-----|

| 4.1           | Motivation                                          | 64  |

| 4.1.1         | Cache Line Usage on the Sub-Block Level             | 64  |

| 4.1.2         | Potential for Energy Savings in L1 Cache            | 67  |

| 4.2           | The Dead Sub-Block Predictor (DSBP)                 | 67  |

| 4.2.1         | Usage Example                                       | 69  |

| 4.2.2         | Improving the Cache Replacement Policy              | 70  |

| 4.2.3         | Prefetching Adaptations                             | 70  |

| 4.2.4         | Implementation on Multiple Cache Levels             | 71  |

| 4.3           | Methodology                                         | 71  |

| 4.4           | Evaluation                                          | 72  |

| 4.4.1         | Mechanism Accuracy                                  | 72  |

| 4.4.2         | Energy Savings                                      | 73  |

| 4.4.3         | Performance Impact                                  | 74  |

| 4.5           | Design Space Exploration                            | 76  |

| 4.6           | Summary                                             | 77  |

| 5 E           | DEAD LINE AND EARLY WRITE-BACK PREDICTOR (DEWP)     | 79  |

| 5.1           | Motivation                                          | 80  |

| 5.1.1         |                                                     | 80  |

| 5.1.1         | Sensitivity to Early Write-Back                     | 81  |

| 5.1.2         | Overall Potential Benefits                          | 82  |

| <b>5.1.</b> 3 | The Dead Line and Early Write-Back Predictor (DEWP) | 82  |

| 5.2.1         | Overview of the Mechanism                           | 82  |

| 5.2.2         | Mechanism Operations                                | 83  |

| 5.2.3         | Improving the Cache Replacement Policy              | 84  |

| <b>5.3</b>    | Methodology                                         | 85  |

| 5.4           | Evaluation                                          | 85  |

| 5.4.1         | Mechanism Accuracy                                  | 86  |

| 5.4.2         | Energy Savings                                      | 86  |

| 5.4.3         | Performance Impact                                  | 87  |

| 5.5           | Design Space Exploration                            | 89  |

| 5.6           | Summary                                             | 90  |

|               | ·                                                   |     |

|               | COMBINING DSBP AND DEWP                             | 93  |

| 6.1           | Introduction                                        | 93  |

| 6.2           | Evaluation                                          | 93  |

| 6.2.1         | Energy Savings                                      | 94  |

| 6.2.2         | Performance Impact                                  | 94  |

| 6.3           | Summary                                             | 96  |

| 7 (           | CONCLUSIONS AND FUTURE WORK                         | 97  |

| 7.1           | Future Work                                         | 97  |

| 7.1           | Published Papers                                    | 98  |

| 1 • 2         | i unimmed i apero                                   | 70  |

| REF           | ERENCES                                             | 101 |

| APP        | NDIX A ADDITIONAL VALIDATION RESULTS 107             |  |

|------------|------------------------------------------------------|--|

| <b>A.1</b> | <b>SPEC-CPU2006 Results</b>                          |  |

| <b>A.2</b> | <b>SPEC-OMP2001 Results</b>                          |  |

| <b>A.3</b> | NAS-NPB Results                                      |  |

| APP        | NDIX B RESUMO EXPANDIDO EM PORTUGUÊS                 |  |

| <b>B.1</b> | Simulator of Non-Uniform Cache Architecture (SiNUCA) |  |

| <b>B.2</b> | Dead Sub-Block Predictor (DSBP)                      |  |

| <b>B.3</b> | Dead Line and Early Write-Back Predictor (DEWP)      |  |

| <b>B.4</b> | Combinando os mecanismos DSBP e DEWP                 |  |

| <b>B.5</b> | <b>Conclusões</b>                                    |  |

#### **Increasing Energy Efficiency of Processor Caches via Line Usage Predictors**

#### **ABSTRACT**

Energy consumption is becoming more important for processor architectures, where the number of cores inside the chip is increasing and the total power budget is kept at the same level or even reduced. Thus, energy saving techniques such as frequency scaling options and automatic shutdown of sub-systems are being used to maintain the trade-off between power and performance. To deliver high performance, current Chip Multiprocessors (CMPs) integrate large caches in order to reduce the average memory access latency by allocating the applications' working set on-chip. These cache memories have traditionally been designed to exploit temporal locality by using smart replacement policies, and spatial locality by fetching entire cache lines from memory on a cache miss.

However, recent studies have shown that the number of sub-blocks within a line that are actually used is often low, and those sub-blocks that are used are accessed only a few times before becoming dead (that is, never accessed again). Additionally, many of the cache lines remain powered for a long period of time even if the data is not used again, or is invalid. For modified cache lines, the cache memory waits until the line is evicted to perform the write-back to next memory level. These write-backs compete with read requests (processor demand and cache prefetch), increasing the pressure on the memory controller. For these reasons, the energy efficiency and performance of cache memories are not ideal.

This thesis introduces cache line usage predictors to increase the energy efficiency of cache memories. We propose the Dead Sub-Block Predictor (DSBP) and Dead Line and Early Write-Back Predictor (DEWP) mechanisms to enable energy savings without performance degradation. DSBP is used to predict which sub-blocks of a cache line will be actually accessed and how many times they will be used in order to bring into the cache only those sub-blocks that are necessary, and power them off after they are accessed the predicted number of times. DEWP predicts dead lines as soon as they receive the last access, and turns off these lines. Dirty lines are scheduled for write-back after the last write operation occurs, increasing the energy savings potential and also reducing the pressure on the memory controller. Both proposed mechanisms also reduce pollution in cache memories by prioritizing dead lines for eviction in the existing replacement policy.

Although each introduced mechanism is capable of performing separately inside a system, both mechanisms can also be mixed in the same cache hierarchy. This mixed implementation is interesting because the sub-block granularity is more suitable for cache levels closer to the processor, where the cache lines are quickly evicted, while the Last-Level Cache (LLC) tends to use the whole cache line before its eviction.

In order to evaluate our proposed mechanisms, we introduce the Simulator of Non-Uniform Cache Architectures (SiNUCA). This cycle-accurate microarchitecture simulator is validated in terms of performance and energy consumption by comparing it to a real

processor. Our performance results were obtained executing single-threaded applications from SPEC-CPU2006 and multi-threaded applications from SPEC-OMP2001 and NAS-NPB benchmark suites. The energy related results were obtained by integrating SiNUCA with the Multi-core Power, Area, and Timing (McPAT) framework and the CACTI power modeling tool.

When applying our mechanisms on all the cache levels, we observe on average a 36% energy reduction for DSBP, 25% energy reduction using DEWP and an average reduction of 37% in the energy consumption applying DSBP on L1 and L2 and DEWP on the LLC. All these reductions caused a negligible performance loss of less than 4% on average.

**Keywords:** Line Usage Predictors, Sub-block Usage Predictors, Replacement Policy, Early Write-Back, Cache Memories, Energy Efficient.

## Aumentando a Eficiência Energética da Memória Cache de Processadores através de Preditores de Uso de Linhas da Cache

#### **RESUMO**

O consumo de energia se torna cada vez mais importante para a arquitetura de processadores, onde o número de *cores* dentro de um mesmo *chip* está aumentando mas o total de energia disponível se mantém no mesmo nível ou até mesmo se reduz. Assim, técnicas para economizar energia, tais como opções de escala de frequência e desligamento automático de subsistemas, estão sendo usadas para manter a troca entre energia e desempenho. Para se obter alto desempenho, os atuais *Chip Multiprocessors (CMPs)* integram grandes memórias *cache* a fim de reduzir a latência média para acesso a memória principal, através da alocação do conjunto de dados da aplicação dentro do *chip*. Essas memórias *cache* tem sido projetadas tradicionalmente para explorar a localidade temporal usando políticas de substituição inteligentes e localidade espacial buscando todos os dados da linha da *cache* após uma falta de dados.

Entretanto, estudos recentes mostraram que o número de sub-blocos dentro da linha da memória *cache*, que são realmente usados, costuma ser baixo, sendo que, os sub-blocos que são usados recebem poucos acessos antes de se tornarem mortos (isto é, nunca mais são acessados). Além disso, muitas da linhas da memória *cache* permanecem ligadas por longos períodos de tempo, mesmo que os dados não sejam usados novamente ou são inválidos. Para linhas de *cache* modificadas, a memória *cache* aguarda até que a linha seja expulsa para que esta seja gravada (*write-back*) de volta no próximo nível de memória. Essas escritas competem com as requisições de leitura (demanda do processador e prébusca da *cache*), aumentando a pressão no controlador de memória. Por essas razões, a eficiência energética e o desempenho das memórias *cache* não são ideais.

Essa tese propõe a aplicação de preditores de uso de linhas da *cache* para aumentar a eficiência energética das memórias *cache*. São propostos os mecanismos *Dead Sub-Block Predictor (DSBP)* e *Dead Line and Early Write-Back Predictor (DEWP)* para permitir economia de energia sem que haja degradação do desempenho. DSBP é usado para prever quais sub-blocos da linha da *cache* serão usados e quantas vezes eles serão acessados de forma a trazer para a *cache* apenas os sub-blocos úteis e desliga-los após eles serem acessados pelo número de vezes previsto. *DEWP* prevê linhas de *cache* mortas assim que elas recebem o último acesso, desligando essas linhas. As linhas sujas são escalonadas para sofrerem *write-back* após a última operação de escrita, aumentando o potencial de salvar energia, reduzindo também a pressão no controlador de memória. Ambos os mecanismos propostos também reduzem a poluição nas memórias *cache*, dando prioridade para a expulsão de linhas mortas, melhorando as atuais políticas de substituição.

Embora cada mecanismo apresentado seja capaz de funcionar separadamente dentro do sistema, ambos os mecanismos podem também ser misturados em uma mesma hierarquia de *cache*. Essa implementação mista é interessante pois a granularidade de sub-bloco é preferível para níveis de *cache* próximos do processador, onde as linhas de memória *ca*-

*che* são expulsas rapidamente, enquanto o último nível de *cache* tende a usar toda a linha antes da sua expulsão.

Com o intuito de avaliar os mecanismos propostos, é apresentado o *Simulator of Non-Uniform Cache Architectures (SiNUCA)*. Esse simulador de microarquitetura com precisão de ciclos é validado em termos de desempenho e consumo de energia através da comparação com um processador real.

Os resultados de desempenho foram obtidos executando aplicações das cargas de trabalho *single-threaded* do conjunto SPEC-CPU2006 e aplicações *multi-threaded* dos conjuntos SPEC-OMP2001 e NAS-NPB. Os resultados relativos a energia foram obtidos integrando o *SiNUCA* com as ferramentas de modelagem *Multi-core Power, Area, and Timing (McPAT)* e CACTI.

Quando aplicados os mecanismos em todos os níveis de memória *cache*, observou-se em média uma redução de 36% no consumo de energia usando o *DSBP*, 25% usando o *DEWP* e 37% quando usou-se o *DSBP* nos níveis L1 e L2 e o *DEWP* no último nível. Todas essas reduções causaram uma perda desprezível de desempenho de menos de 4% em média.

Palavras-chave: Preditores de Linha da Cache, Memórias Cache, Eficiência Energética.

#### 1 INTRODUCTION

High performance computing uses aggressive techniques to obtain parallelism in multiple levels: at the instruction level using superscalar pipelines with Out-of-Order (OoO) execution (SMITH; SOHI, 1995), larger OoO execution windows, frequency increase, and others (HENNESSY; PATTERSON, 2007) such as better branch predictors and data prefetchers; at the thread and process level using Chip Multithreading (CMT) techniques with Chip Multiprocessor (CMP).

However, Instruction Level Parallelism (ILP) techniques have less room for improvements due to limits imposed by wire-delay problems (clock wall), power consumption limit (power wall) (BORKAR, 1999), and ILP extraction problems (ILP wall) (AGARWAL et al., 2000). Thus, Thread Level Parallelism (TLP) techniques such as CMP with increasing number of cores have become the most likely way for the industry to continue delivering more powerful processors on each new generation.

Most of the multi-core processors are built with cores simpler than traditional single cores, with shorter pipelines and simpler control structures (OLUKOTUN et al., 1996). This leads to the possibility of integrating more cores on the same physical silicon area. This complexity reduction on the cores is also beneficial for the power constraints inside the chip. For these reasons, the focus has changed to also explore the thread and process parallelism (UNGERER; ROBIC; SILC, 2002).

Recently, energy efficiency has become a key design parameter in computer architectures. While the number of transistors on a chip has been increasing rapidly, the total power budget remains at the same level or even decreases. In this context, each technique that leads to reduction of power consumption has a great impact on the total energy consumption of the system. Thus, new processors begin to present frequency scaling options, automatic shutdown of sub-systems and other techniques to ensure that machines will reduce the unnecessary energy consumption, and will consume full power only when demanded.

#### 1.1 The Problem

Cache memories, while key to high performance, consume a significant fraction of total chip power (LI et al., 2009), varying from 15% to 23% of the total chip power. As such, designing energy efficient processors starts with efficient design of such power-hungry components.

In order to evaluate the cache energy consumption inside the chip, we executed the SPEC-CPU2006 single threaded benchmark suite and the SPEC-OMP2001 and NAS-NPB parallel benchmark suites modeling two different processors using the *McPAT* frame-

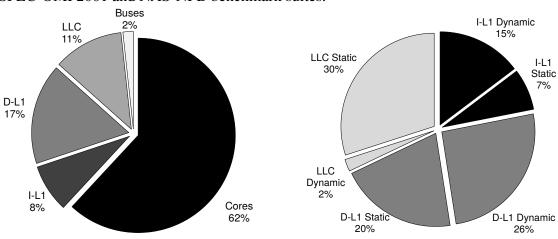

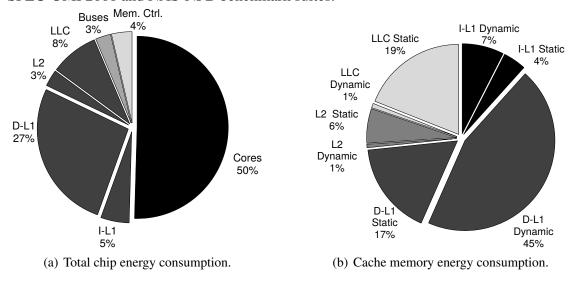

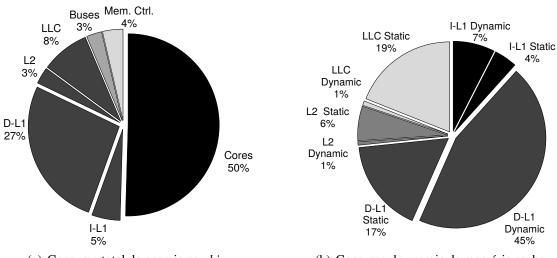

Figure 1.1: Breakdown of Core 2 Duo energy consumption, executing SPEC-CPU2006, SPEC-OMP2001 and NAS-NPB benchmark suites.

Figure 1.2: Breakdown of Sandy Bridge energy consumption, executing SPEC-CPU2006, SPEC-OMP2001 and NAS-NPB benchmark suites.

(b) Cache memory energy consumption.

(a) Total chip energy consumption.

work (LI et al., 2009). The parallel benchmarks execute with the same number of threads as the number of cores available in the processor.

Figure 1.1 shows the Intel Core 2 Duo (Conroe microarchitecture (BOJAN et al., 2007)) energy consumption. The average power consumed by the chip corresponds to 22 W according to our energy model. It can be observed that 36% of energy consumed inside the chip is consumed by the cache memories, while each core (2 cores in total) is responsible for 31% of the energy consumed by the chip (62% in total).

Figure 1.2 shows the Intel Xeon (Sandy Bridge microarchitecture (YUFFE et al., 2011)) energy consumption. The average power consumed by the chip corresponds to 37 W. It can be observed that 43% of energy consumed inside the chip is consumed by the cache memories, while each core (8 cores in total) is responsible for 6% of the energy consumed by the chip (50% in total).

Due to the reduced power budget, and the increasing portion of energy being consumed by the cache memories, mechanisms to improve the cache efficiency are becoming

more important. Moreover, as we can see in Figures 1.2(b),1.3(b) the major sources of energy consumption inside the cache sub-system are related to the L1 dynamic and static energy, and the Last-Level Cache (LLC) static energy, which can be explained by to the high number of L1 operations and to the large area occupied by the *LLC*.

For today's processors with a fixed cache line size, energy inefficiency can occur on two levels: 1) on a cache line level where a line is kept alive much longer than necessary, and 2) on a sub-block level, when parts of a cache line that will never be used are brought into the cache, and also when active sub-blocks become dead after a few accesses but are kept alive until the line is evicted.

Besides the energy consumption problem, keeping cache lines that will not be used anymore (dead lines) inside the cache, increases cache pollution and memory contention. Cache pollution increases when the replacement policy takes wrong decisions by removing alive blocks instead of already dead blocks. Pollution can also increase the number of cache misses, thus generating negative impact on the performance of the system. The impact on memory contention happens when the cache keeps dirty lines which already received the last write. By doing so, these lines will only suffer write-back to the main memory whenever the cache line is evicted. However, considering that memory accesses occur in bursts (WANG; KHAN; JIMÉNEZ, 2012a), the write-back operation can increase the memory pressure in those moments when lots of data are being requested (burst of operations).

#### 1.2 Motivation

In order to evaluate the inefficiency of current cache memories, we measured the average usage of L1 cache lines in the sub-block granularity. Figure 4.2 using SPEC-CPU2006, SPEC-OMP2001 and NAS-NPB shows that on average only 57% of a line is used by the single threaded benchmarks and 81% for multi-threaded benchmarks. Similar results were observed in (KUMAR; WILKERSON, 1998; CHEN et al., 2004; KHAR-BUTLI; SOLIHIN, 2008). We make the new observation (Figure 4.3) that 83% of sub-blocks become dead after less than four accesses.

Measuring the average time between the last access to a cache line and the line eviction from the cache memory, we can evaluate the inefficiency in the cache line granularity. On average the time between the last access to a cache line and its eviction is 40% of the lifetime of the line (KAXIRAS; HU; MARTONOSI, 2001).

These results show that there are several opportunities for energy savings in traditional cache designs. Cache lines are unused for long periods of time while still consuming energy. Furthermore, the L1 and L2 caches present more inefficiency on the sub-block level, while the LLC uses the whole line more consistently, but the line is still powered on for a long time without accesses.

Based on the Sandy Bridge processor, we show in Section 4.1 that an oracle mechanism that perfectly predicts the dead sub-blocks inside the L1 cache and turns-off those sub-blocks can save on average 51% of the L1 cache energy consumption, that represents savings of 34% for the entire cache sub-system energy consumption.

Another oracle mechanism, presented in Section 5.1, that turns off LLC lines after their last access or when the cache line becomes invalid, generates LLC energy savings of 65% on average, that represents savings of 11% for the entire cache sub-system energy consumption.

Considering the high theoretical energy savings achieved by cache line usage predictors, at the sub-block or cache line granularities, the benefits of such mechanisms inside the cache memory to increase its energy efficiency are clear.

#### 1.3 Hypotheses and Objectives

In order to increase the energy efficiency of cache memories, we formulate the following hypotheses:

- By studying the historic memory access behavior of the application, it is possible to predict the cache line usage.

- Using the predicted cache line usage, dead lines can be identified and turned off in order to save energy and reduce the cache pollution and memory pressure.

- Looking at the sub-block granularity allows to further increase the energy savings.

Based on these hypotheses, the main goal of this thesis is to introduce mechanisms to increase the energy efficiency of the cache memories. This objective will be achieved by the following steps:

- We propose a Dead Sub-Block Predictor (DSBP) to predict at run-time the cache line usage at the sub-block granularity. This mechanism will be used to store only the useful sub-blocks inside the cache line and to turn-off the sub-blocks when they become dead.

- We propose a Dead Line and Early Write-Back Predictor (DEWP) to detect when a cache line receives its last read and last write. This predictor will be used to early write-back dirty lines as soon as they receive their last access and to turn-off the line as it receives its last read.

- To evaluate the new mechanisms, we developed the Simulator of Non-Uniform Cache Architectures (SiNUCA), a new cycle accurate, trace-driven simulator composed of the following main components: processor, cache memories, interconnections and memory system. This simulator is able to simulate multi-core systems, with multi-banked caches and Network-on-Chip (NoC) interconnections. This simulator is validated with a real machine in terms of performance and energy consumption.

DSBP and DEWP overlap in functionalities, however, the sub-block granularity fits better for small caches that are closer to the processor while the line granularity fits better for big LLC memories. The smaller caches have a lower sub-block usage compared to the cache levels closer to the main memory. The reason for this low usage is that the smaller caches tend to evict the cache lines sooner, reducing the chances for full cache line usage.

The dead line predictors should also be used to improve the cache replacement policy in order to reduce cache pollution. For the cases where the cache lines are dirty, the last write predictor will help to reduce the memory pressure in the memory controller.

The general goal of this thesis is to design mechanisms that enable energy savings in the cache memory, maintaining the performance of the system. The overhead of such mechanisms will also be evaluated in order to show their benefits and possible drawbacks.

The simulator used for the evaluations will be mainly developed to verify our mechanisms, by providing a controlled environment capable to simulate the microarchitecture inside the cores, the cache memory sub-system with multi-banked caches, including the *NoC* interconnection and a detailed memory controller.

#### 1.4 Contributions

The main contributions of this thesis are:

• DSBP – Dead Sub-Block Predictor (ALVES et al., 2012)

**Sub-block usage predictor:** A mechanism to predict and turn on only the useful sub-blocks of each cache line.

**Dead sub-block predictor:** A mechanism to predict when each sub-block inside a cache line becomes dead and turn off these dead sub-blocks.

**Earlier eviction of dead lines:** A mechanism to improve the cache replacement algorithm. The sub-block predictor gives feedback to the replacement algorithm after all the sub-blocks become dead, marking dead lines as future victims for eviction.

• DEWP – Dead Line and Early Write-Back Predictor (ALVES et al., 2013)

**Last line read predictor:** A mechanism that aims to save energy by turning off dead or invalid cache lines when the cache line receives a write in another cache.

**Last line write predictor:** A mechanism to perform early write-back of dirty cache lines to main memory, since these lines will not be modified anymore.

**Earlier eviction of dead lines:** A predictor to detect whenever a cache line receives its last access, prioritizing those lines for early eviction.

• SiNUCA – Simulator of Non-Uniform Cache Architectures

**Performance and energy validated simulator:** Our simulator is validated in terms of performance and energy compared to real processor. It will be used to implement and evaluate our proposed mechanisms.

Compared to the related work, our mechanisms produce more accurate predictions achieving higher energy savings, with a negligible overhead that keeps the performance on the same level. DSBP is the first mechanism that is capable of predicting and turning off cache lines on the sub-block granularity, enabling dynamic and static cache energy savings. DEWP predicts last writes, saving static energy whenever the cache line becomes dead. Both mechanisms do not require broadcast signals for all the cache lines nor complex internal simulators to predict the cache line usage.

#### 1.5 Document Organization

The remainder of this text is organized as follows. Background and related work are presented in Chapter 2. Chapter 3 gives a detailed overview of the new simulator, together with the workloads used in our evaluations. Chapter 4 presents the Dead Sub-Block Predictor. Chapter 5 introduces the Dead Line and Early Write-Back Predictor. Chapter 6 presents the analysis of a system implementing both predictors. Chapter 7 discuss the main conclusions of this thesis. Appendix A shows additional SiNUCA validation results.

#### 2 ENERGY EFFICIENCY IN CACHE MEMORIES

This chapter introduces the concepts and the sources of inefficiency in cache memories. We also discuss the related work on cache usage predictors. The prior work related to the simulator is discussed in the next chapter.

#### 2.1 Sources of Inefficiency in Cache Memories

Cache memories are energy and performance inefficient in cache line and sub-block granularity. In order to understand the sources of inefficiency some terms must be explained first:

**Dead line:** A cache line is considered being dead on the period of time between its last access (read or write) and its eviction from the cache memory.

**Dead sub-block:** In the same way as the dead line, a sub-block is dead after its last access. However, a sub-block may become dead before the line is declared dead. This is because some sub-block can be accessed separately from the others.

**Cache pollution:** The fact of having multiple cache lines, that the program will not use in a close future, residing inside the cache, causing other still useful lines to be prematurely evicted from the cache, is considered a cache pollution problem. This cache pollution problem is also called as cache noise by some authors.

**Memory pressure:** Considering that memory operations tends to occur in bursts of accesses (see Figure 5.2), the high number of requests into the main memory causes a memory pressure, which is even higher considering that dirty cache lines need to be writtenback to the main memory before its complete eviction to make room for a new cache line. These write-back operations competing with the read requests into the memory controller is a source of a high memory pressure.

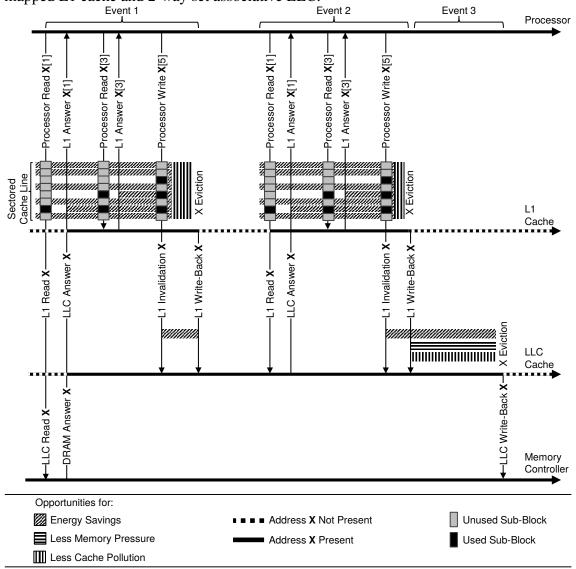

Figure 2.1 presents a scenario with several opportunities to increase the cache memory efficiency. This figure shows a series of memory accesses (reads and writes) from the processor to several addresses of cache lines (*X*, *Y* and *Z*) over the time. There are two cache levels. The L1 cache is a direct-mapped sectored cache, split into 8 sub-blocks of 8 bytes each. The LLC is a 2-way set associative without sub-blocks. For simplicity we assume that these addresses have the same index, which means that they get mapped to the same cache set. The two horizontal lines referent to lines *A* and *B* show two specific cache lines in the L1 cache and LLC. A solid line indicates that the line with address *X* is present and valid, while the dashed line indicates not present.

Several events are shown in the figure:

Figure 2.1: Opportunities for increasing the cache memory efficiency, modeling a direct-mapped L1 cache and 2-way set associative LLC.

**Event 1:** The processor reads the address *X*, requesting the sub-block 1. As the line is not present in the L1 cache and LLC, it needs to be requested from the memory controller. After one more read and write operations all the sub-blocks inside the cache line become dead due to the read of another line. Due to another cache accesses the address *X* is written-back to the LLC and then evicted from the L1 cache.

On the sub-block level (L1 cache), we can observe two opportunities to save static energy. First, when a never used sub-block is brought to the cache line, it could be turned off. Second, when a sub-block receives its last access and it becomes dead, it could also be turned off. Cache pollution could also be reduced by early evicting the cache line X after it receives its last access (all the sub-blocks are dead). Notice that the sub-block number X[5] needs to be turned on until the write operation, considering that the processor is capable of writing only one part within the sub-block.

On the cache line granularity (LLC), we have the opportunity to save energy by turning off the cache line during the time the line is invalid.

**Event 2:** Once again, the processor requests the address *X*, bringing a copy of this line from the LLC. We can observe the same opportunities to save energy and reduce cache pollution.

**Event 3:** At this point, the cache address *X* is evicted from the L1 cache and written-back to the LLC. After a certain period of time, this line *X* is evicted from the LLC, performing thus a write-back to the main memory of the dirty cache line *X*. Energy savings can be obtained by turning off the line *X* in the LLC when it is invalid and after it receives the write-back. We can also observe opportunities to reduce the memory pressure between the moment when the LLC receives the last write-back of the address *X* and it writes-back this line to the main memory. The opportunity to reduce cache pollution happens in the same time, when the line becomes dead and it could be marked for early eviction to make room for a new line.

During a L1 cache miss, the first operation performed by the cache is to access the whole cache line at the same time as the tag is obtained. The second operation is to compare the tag to the target memory address and forward the requested bytes in the same cycle (HUANG et al., 2001). The parallel access to the data and the tag arrays guarantees a low cache latency.

Besides the static energy on the sub-block level, we could also save dynamic energy during cache reads. If several sub-blocks are turned off, less bytes need to be accessed, which requires less dynamic energy.

The gains in terms of cache energy savings using an oracle line predictor can be easy modeled by computing the time when the line is invalid, as well as between the last access and the line eviction, subtracting the static energy spent on those cycles from the total energy consumption of the cache sub-system. For the oracle sub-block predictor, the static energy savings can be easily extended from the line predictor. The dynamic energy savings can be computed by analyzing the number of alive sub-blocks on every cache line access. Further modeling details are presented in Sections 4.3 and 5.3.

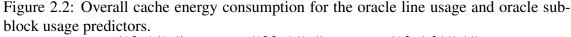

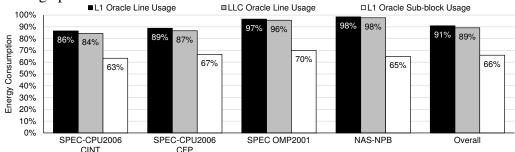

Figure 2.2 presents the overall energy consumption for the entire cache sub-system considering two different oracles (line usage and sub-block usage) applied to different cache levels (L1 and LLC), modeling a Sandy Bridge machine.

We can observe that energy savings are achievable on both the line and sub-block granularities. However, working on the sub-block basis, more opportunities for energy savings are present. The reason is that the applications tend to access the sub-blocks of line unevenly during the lifetime of the line, such that waiting for the whole line to become dead loses energy savings opportunities. The oracle mechanisms can also reduce

the energy consumption of never used prefetched cache lines, reducing the impact of these lines on the total static energy consumption.

The possible gains in terms of performance are hard to be modeled, because any small difference in the replacement policy leads the cache to have a completely different line allocation.

To exploit these energy savings opportunities, it is necessary to create an accurate and low overhead mechanism capable of predicting line and sub-block usage. We propose two mechanisms to work in both sub-block and cache line granularity, in order to reduce the energy consumption, while using the performance opportunities to keep the final execution time at the same level.

#### 2.2 Related work

Previous work has introduced line usage predictors, dead line predictors and last write predictors, which are applied to problems such as reducing static energy consumption, prefetching, cache pollution, memory controller contention among others.

This section discusses these mechanisms and compares them to our approaches. We also introduce the mechanism based on related work that will be compared to our predictors.

#### 2.2.1 Line Usage Predictors

KUMAR; WILKERSON (1998) proposed a Spatial Footprint Predictor (SFP) which predicts the neighboring words to be prefetched on a cache miss. The goal is to reduce the L1 miss ratio while keeping the cache pollution at a minimum. Based on run-time history tables, the predictor explores spatial locality by using a cache with small lines but fetching multiple neighboring lines that are likely to be used in the near future.

CHEN et al. (2004) proposed a Spatial Pattern Predictor (SPP) to predict cache line usage patterns. The mechanism uses the Program Counter (PC) and the first data offset requested to correlate historical data about line usage to predict future usage patterns of L1 cache lines. The goal of this technique is to reduce static energy by bringing into the cache just those sub-blocks that were predicted to be accessed. The authors also introduce a prefetching technique to bring only the predicted spatial patterns for contiguous groups of up to 512 bytes.

PUJARA; AGGARWAL (2008) studied three types of mechanisms to predict the useless data in a cache block (cache noise), guided by the usage history of words in a cache line. Their results motivate the use of PC and offset as the index of a history table. In order to couple their mechanism with any prefetcher, the authors proposed an implementation considering that the pattern of the line being prefetched will be the same as the line which triggered the prefetcher.

Line usage predictors like SPP (CHEN et al., 2004) could be easily extended in order to start predicting dead sub-blocks. We extended SPP to predict useful and dead sub-blocks. However, our results show that DSBP performs on average 10% better in terms of energy reduction than the adapted SPP. Moreover, the adapted SPP increased the total cache misses on all the cache levels by 20% on average compared to the baseline without any predictor. This increase on total cache misses caused a 9% increase in the execution time.

The reason adapted SPP achieves poor results is that it uses an algorithm that resets the old pattern and starts a new one every time a new cache line comes into the cache so that

new patterns can be learned quickly. However, this allows multiple Pattern History Table (PHT) pointers to the same PHT entry to simultaneously co-exist and therefore incorrect patterns are recorded more frequently.

#### 2.2.2 Counter Based Dead Line Predictor

KHARBUTLI; SOLIHIN (2008) presented two counter-based mechanisms (AIP and LvP). Access Interval Predictor (AIP) counts the number of accesses to the set that has the line during the line's current access interval and identifies it as dead when the event count reaches the threshold. Live-time Predictor (LvP) records the number of accesses to a cache line and predicts the line as dead when the access counter reaches a certain threshold. The results show that LvP delivers higher accuracy with less complexity. The mechanism uses a hash of the PC which caused the cache miss to index into a table that stores the history of the number of accesses from previously evicted lines. The mechanism is used to identify dead lines and to evict them early, and also to bypass never re-accessed cache lines.

#### 2.2.3 Trace Based Dead Line Predictors

LAI; FIDE; FALSAFI (2001) introduced the Last-Touch Predictor (LTP) which uses an execution trace to predict the last touch to a cache line. The key intuition behind LTP is that memory evictions are triggered by program instructions and that program behavior tends to repeat. The mechanism generates a signature based on a trace of instructions that access a cache line. By matching current signatures with previously stored signatures that lead to dead cache lines, the mechanism can predict when a given line becomes dead. The goal of this work is to allow the lines to self-invalidate when their last access is detected.

KHAN et al. (2010) proposed a Skewed Dead-Block Predictor (SDP) to predict dead lines and use these lines as a virtual victim cache. This skewed predictor is similar to the LTP mechanism, but uses two global tables. Each one of the tables is indexed by a different hash function to reduce the impact of conflicts between them. They also propose a more complex mechanism (KHAN et al., 2010), which uses three tables to implement the skewed predictor. This mechanism also introduces a sampling cache structure which uses only some of the cache lines to build the prediction table's information.

#### 2.2.4 Time Based Dead Line Predictors

KAXIRAS; HU; MARTONOSI (2001) presented a cache decay mechanism which uses theories from competitive algorithms to create a time-based strategy. They exploit long dead periods by turning off cache lines during such periods. This approach aims to reduce static power dissipated by the cache. Each line contains a counter with a number of cycles since the last access and each line is turned off after a certain interval. A hierarchical counter mechanism is adopted to reduce the bits required per cache line. This hierarchical counter is formed by a global counter which broadcasts an increment signal to the smaller counters every time it overflows. The authors also explore an adaptive mechanism to automatically choose the best decay interval on a cache line granularity.

ABELLA et al. (2005) introduced the Inter-Access Time per Access Count (IATAC) mechanism to predict and turn off dead lines with the objective of reducing L2 cache static energy. This mechanism predicts a cache line to be dead when it detects that the line has not received any access for a period greater than the average time between different accesses. The mechanism keeps track of the average time between accesses in a global

table with a separate entry for each access count (i.e., there is a different average time stored for the difference between the 1st and 2nd access and the difference between the 2nd and 3rd access and so on).

#### 2.2.5 Last Write Predictors

LEE; TYSON; FARRENS (2000) proposed the Eager Write-back mechanism which performs early write-back of dirty lines from the L1 cache whenever the line achieves the Least Recently Used (LRU) position. The objective of this work is to speculatively "clean" the dirty cache lines prior to their eviction, in order to avoid the performance degradation during clustering bus traffic in a write-back approach.

STUECHELI et al. (2010) presented the Virtual Write Queue (VWQ) technique, which exposes to the memory controller the dirty blocks near to the LRU position in the LLC. The mechanism issues scheduled write-backs to improve the write-back efficiency when the memory rank is idle, considering that a bank can be formed by more than one rank. This technique uses a Search Set Vector (SSV) which gathers information from all the sets, in order to keep track of the dirty lines and how close they are from the LRU position. As a cache line becomes close to the LRU position, that line is marked as critical blocks to write-back.

WANG; KHAN; JIMÉNEZ (2012a) proposed a Last Write Predictor (LWP) to predict whenever the cache line receives its last write. The prediction mechanism uses three tables with a skewed organization similar to SDP mechanism to detect the last-written blocks and store pointers of these blocks into a last-write buffer. The objective of this mechanism is to make the last-write blocks available for the main memory scheduling before the line gets evicted. This predictor issues a write-back request to the memory when no read request targets the same rank.

WANG; KHAN; JIMÉNEZ (2012b) presents a two level rank idle predictor to schedule the write-back to the memory only when long phases of idle rank cycles are predicted. Together with the rank idle predictor, this paper uses the SSV in order to keep track of dirty lines and send the blocks close to the LRU position to write-back.

#### 2.2.6 Overall Comparison

| Table 2.1: State-of-the-ar | t iast acce | ess predicto | rs. |

|----------------------------|-------------|--------------|-----|

| em                         | Saves       | Predicts     | •   |

| Mechanism                                                           | Saves  | Predicts          | Sub-block |

|---------------------------------------------------------------------|--------|-------------------|-----------|

| Description                                                         | Energy | <b>Dead Lines</b> | Level     |

| SPP: Line usage predictor. (CHEN et al., 2004).                     | Yes    | No                | Yes       |

| LvP: Counter based dead line predictor. (KHARBUTLI; SOLIHIN, 2008). | No     | Yes               | No        |

| LTP: Trace based dead line predictor. (LAI; FIDE; FALSAFI, 2001).   | No     | Yes               | No        |

| SDP: Trace based dead line predictor. (KHAN et al., 2010).          | No     | Yes               | No        |

| IATAC: Time based dead line predictor. (ABELLA et al., 2005).       | Yes    | Yes               | No        |

| <b>DSBP: Dead Sub-Block Predictor.</b> (ALVES et al., 2012).        | Yes    | Yes               | Yes       |

Table 2.1 presents a comparison between DSBP and its related work. DSBP performs better than previous work by treating the energy consumption problem at all the levels

of the cache hierarchy, and not only predict which sub-blocks should be brought into the cache, but also when active sub-blocks become dead. Additionally, DSBP reduces the number of accesses to the pattern history table by updating it only when a new pattern is detected.

Table 2.2: State-of-the-art last write predictors.

| Mechanism                                       | Saves  | Predicts   | Early      |

|-------------------------------------------------|--------|------------|------------|

| Description                                     | Energy | Dead Lines | Write-Back |

| Eager Write-Back.                               | No     | No         | Yes        |

| (LEE; TYSON; FARRENS, 2000).                    | INO    | NO         | 168        |

| VWQ: Virtual Write Queue.                       | No     | No         | Yes        |

| (STUECHELI et al., 2010).                       |        |            |            |

| SSV: Search Set Vector.                         | No     | No         | Yes        |

| (LAI; FIDE; FALSAFI, 2001).                     | 110    | 110        | ics        |

| LWP: Last Write Predictor.                      | No     | No         | Yes        |

| (WANG; KHAN; JIMÉNEZ, 2012a).                   | NO     | NO         | 168        |

| Two Level Rank Idle Predictor.                  | Yes    | No         | Yes        |

| (WANG; KHAN; JIMÉNEZ, 2012b).                   |        |            |            |

| DEWP: Dead Line and Early Write-Back Predictor. | Vac    | Yes        | Vac        |

| (ALVES et al., 2013).                           | Yes    | ies        | Yes        |

Table 2.2 shows a comparison between DEWP and its related work. Regarding the DEWP mechanism, none of the previous approaches have taken into account that dirty lines remain turned on for long periods of time, wasting energy while these lines could be evicted early. Thereby, energy can be saved and memory contention reduced. This thesis introduces a mechanism that performs the prediction of last read, last write and last access on a cache line basis, exploring the energy savings achievable by turning off invalid and dead lines, and performing early write-backs.

To evaluate DSBP and DEWP, we implemented a mechanism similar to those present in LTP (LAI; FALSAFI, 2000; LAI; FIDE; FALSAFI, 2001), SDP (KHAN et al., 2010) and LWP (WANG; KHAN; JIMÉNEZ, 2012a). These previous predictors represent the state-of-the-art and they were proposed to be used for bypassing dead lines or prioritizing them for eviction or perform early write-back after the cache line receives its last write. In our evaluations, we implemented the basis of these previous mechanisms, the *skewed predictor*, to power off the cache lines predicted to be dead and prioritizing them for eviction, also performing early write-back of dirty cache lines when predicted to be dead. This implementation is called SKEWED in the thesis.

# 3 SIMULATOR OF NON-UNIFORM CACHE ARCHITEC-TURE (SINUCA)

Some existing open source academia simulators have been verified for single threaded applications (DESIKAN; BURGER; KECKLER, 2001). However, with the latest advances in CMP, Simultaneous Multi-Threading (SMT), branch prediction, memory disambiguation prediction (DOWECK, 2006), Non-Uniform Cache Architecture (NUCA) (KIM; BURGER; KECKLER, 2003, 2002), NoC (BJERREGAARD; MAHADEVAN, 2006; BERTOZZI et al., 2005) and other mechanisms, academia does not continue the process of validating its microarchitecture simulators. For parallel architectures, mechanisms such as cache coherence, locks and synchronization between threads, interconnection networks and memory controllers affect application performance. The correct use of these shared resources can be very different depending on their implementation.

Another problem that academia researchers suffer when validating their simulators is the lack of a suite of microbenchmarks that stresses different hardware components independently to correlate their implementation with real processors. Each developer usually creates his own microbenchmarks and seldom shares them. The reason why the community accepts this is because there is no better option currently available. Moreover, the operation of specific components in the processor is not published for intellectual property reasons. For this reason, the processor must be seen as a black box, whose behavior can only be measured on a high level. As a possible way to observe the behavior at a finer granularity, microbenchmarks should be used. An emerging issue is the energy consumption modeling of the processor components, which is another feature missing from current simulators.

For these reasons, writing an accurate and validated simulator for modern microarchitectures is a difficult task, and no publicly available simulator is validated for modern parallel architectures.

With these problems in mind, we developed SiNUCA, a performance and energy validated, trace-driven, cycle accurate simulator for the x86 architecture. The simulator is capable of running single and multi-threaded applications and multiple workloads with a high level of detail of all the pipeline components. Additionally, we implemented a large set of microbenchmarks to correlate the simulator results (performance and other statistics) with two existing x86 platforms.

SiNUCA has the following main features:

**High Accuracy:** SiNUCA implements architectural components with a high level of detail, not only in the execution pipeline, but also in the memory and interconnection components. We also accurately model parallel architectures such as multi-core and multi-processor systems. We used publicly available information for the implementation of the

simulator. Where this information was not available, we used microbenchmarks in order to observe the behavior of a real machine.

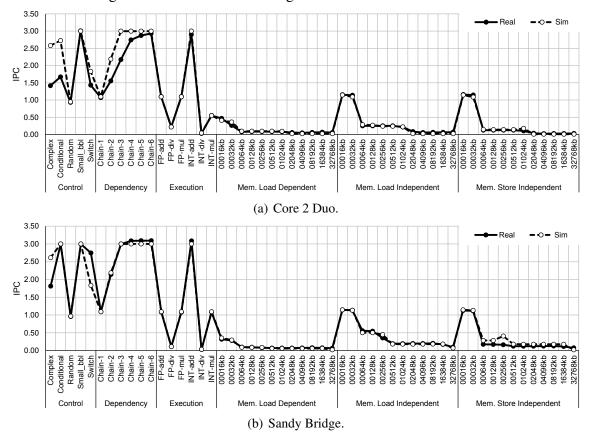

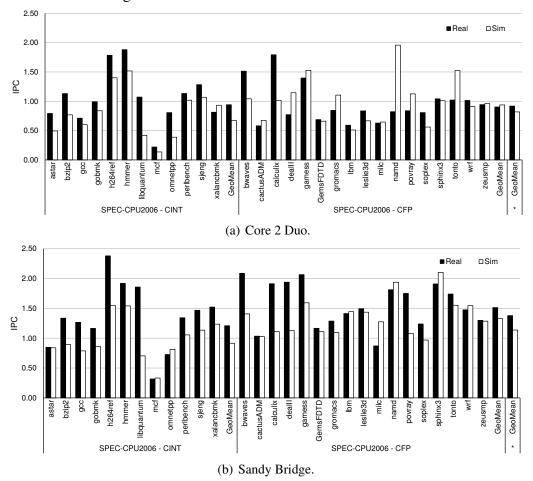

SiNUCA was validated with single-threaded and multi-threaded applications using microbenchmarks and larger workloads. The simulation statistics are compared to real machines. The microbenchmarks had an average difference of 7% while the SPEC-CPU2006 achieved a difference of 12% comparing the Instructions per Cycle (IPC) when simulating machines with the x86 Sandy Bridge architecture.

**Energy Model:** Energy consumption is becoming more important for current and future processor architectures. However, most current simulators do not model energy consumption, only performance. To evaluate the energy consumption, we integrated the Multi-core Power, Area, and Timing (McPAT) (LI et al., 2009, 2013) tool, which uses component statistics generated by SiNUCA. These results were validated using energy hardware counters in the real machine. Our results show a difference of 18% comparing the average energy consumption when simulating the microbenchmarks.

**Support for Emerging Techniques:** SiNUCA is able to model several state-of-the-art technologies, such as NUCA, Non-Uniform Memory Access (NUMA), NoC and Double Data Rate (DDR) 3 memory controllers. Besides the traditional techniques such as cache prefetchers, branch predictors and others, the support for new technologies is important for accurate simulation of new systems.

**Flexibility:** Another important feature to support computer architecture research is the ease of implementing or extending features. This is provided by SiNUCA with a modular architecture, written in C++, which provides a direct access to the operational details of all the components. Other simulators are limited by metalanguages that do not expose all the functionalities of the microarchitecture, making it more difficult to model new mechanisms and modify the existing ones.

The rest of this chapter is organized as follows: We begin with an overview of the state-of-the-art in computer architecture simulation. SiNUCA is presented in Section 3.2. The microbenchmarks are introduced in Section 3.3. The evaluation methodology and results are presented in Section 3.4. We summarize SiNUCA in Section 3.5.

# 3.1 Related Work

In this section, we analyze related computer architecture simulators and compare them to our proposed simulator.

The work of (DESIKAN; BURGER; KECKLER, 2001) validates *sim-alpha*, a simulator based on the *sim-out-order* version of SimpleScalar (AUSTIN; LARSON; ERNST, 2002). In this work, the authors aim to simulate the Alpha 21264 processor, using all available documentation. They use microbenchmarks in order to scrutinize every aspect of the architecture, being able to achieve an average error of 2% for a set of microbenchmarks, and an error of 18% for the SPEC-CPU2000 applications. The authors identify the memory model as the main source of errors. They show that often used simulators, such as SimpleScalar, might contain modeling errors and become less reliable to test certain new features.

We use a similar validation process for SiNUCA, making separate evaluations for specific components inside the processor by using microbenchmarks. We extend the control and memory microbenchmarks and include parallel applications.

Virtutech SimICS (MAGNUSSON et al., 2002) is a full-system, functional simulator which measures execution time based on the number of instructions executed multiplied by a fixed IPC, and the number of stall cycles caused by the latency of all components.

WEAVER; MCKEE (2008) compared the SESC simulator (RENAU et al., 2005) to the Dynamic Binary Instrumentation (DBI) using QEMU (BELLARD, 2005). The authors show that in general, cycle-accurate simulators generate inaccurate results over a long execution time, due to lack of correctness in architectural details. They are able to obtain similar results in an order of magnitude shorter time with DBI. The paper also lists the flaws in cycle-accurate simulators. They cite speed, obscurity, source code forks, generalization, validation, documentation and lack of operating system influence as the major factors when considering the use of a simulator. Regarding these issues, SiNUCA solves several issues with code modularity, use of traced instructions and validation.

Gem5 (BINKERT et al., 2011) is a combination of two simulators: M5 (BINKERT et al., 2006) and General Execution-driven Multiprocessor Simulator (GEMS) (MARTY et al., 2005). Within Gem5, M5 simulates the cores, whereas GEMS simulates the memory hierarchy. The validation of the Gem5 simulator, modeling a simple embedded system (BUTKO et al., 2012), shows that errors can vary from 0.5% to 16% for the applications from the SPLASH-2 and ALPBench suites. However, for small synthetic benchmarks with tiny input sizes, the error varies from 3.7% to 35.9%. The authors conclude that the Dynamic Random Access Memory (DRAM) model is inaccurate.

PTLsim (YOURST, 2007) is a cycle accurate, full-system x86-64 microprocessor simulator and virtual machine. It is integrated with the Xen hypervisor in order to provide full-system capabilities.

Multi2Sim (UBAL et al., 2007) is an event-driven simulator based on the premise of simulating multi-threaded systems. It was extended to simulate heterogeneous CPU-GPU systems in (UBAL et al., 2012).

COTSon is a simulator framework jointly developed by HP Labs and AMD (AR-GOLLO et al., 2009) to provide fast and accurate evaluation of current and future computing systems, covering the full software stack and complete hardware models. As Sim-ICS, COTSon also abstracts processor microarchitecture details, prohibiting development of novelty at this level.

MARSSx86 (PATEL et al., 2011) is a cycle-accurate simulator based on PTLSim. Although it simulates all architectural details, it does not ensure accuracy, as can be seen in their comparison to the SPEC-CPU2006 workload, getting errors of up to 60% with an average error of 21%.

Table 3.1 summarizes the main characteristics for computer architecture simulators. Full-system simulation enables processor designers to evaluate OS improvements or its impact on the final performance. However, the OS simulation can introduce noise during the evaluations, requiring several simulation repetitions (higher simulation time) in order to obtain reliable results with a reduced Operating System (OS) influence.

Microarchitectural and multi-core simulation are required to evaluate most of the state-of-the-art component proposals.

We consider SimICS, GEMS, Gem5 and COTSon as not easy to extend because these simulators have private source code, need metalanguages to modify the architecture or require modifications of multiple simulation levels in order to perform microarchitectural changes.

|           | Full-      | Micro-       |                   |             |          |                | Memory     |

|-----------|------------|--------------|-------------------|-------------|----------|----------------|------------|

| Simulator | System     | Architecture | <b>Multi-Core</b> | Extension   | NoC      | <b>NUCA</b>    | Controller |

| Name      | Simulation | Simulation   | Simulation        | Flexibility | Modeling | <b>Support</b> | Modeling   |

| SimAlpha  | No         | Yes          | No                | High        | No       | No             | No         |

| SimICS    | Yes        | No           | Yes               | Low         | No       | No             | No         |

| SESC      | No         | Yes          | Yes               | High        | Detailed | Yes            | Extension  |

| GEMS      | No         | Yes          | Yes               | Low         | Simple   | Yes            | No         |

| M5        | Yes        | Yes          | Yes               | High        | Simple   | Yes            | No         |

| Gem5      | Yes        | Yes          | Yes               | Low         | Simple   | Yes            | No         |

| PTLsim    | Yes        | Yes          | No                | High        | No       | No             | Extension  |

| Multi2Sim | No         | Yes          | Yes               | High        | Detailed | Yes            | No         |

| COTSon    | Yes        | No           | Yes               | Low         | Detailed | Yes            | No         |

| MARSSx86  | Yes        | Yes          | Yes               | High        | Detailed | No             | No         |

| SiNUCA    | No         | Yes          | Yes               | High        | Detailed | Yes            | Detailed   |

Table 3.1: Comparison of state-of-the-art simulators.

Regarding NoC modeling, different detail levels can be observed among the simulators. SimAlpha, SimICS and PTLsim do not natively support it. GEMS, M5 and Gem5 model only the interconnection latency without modeling traffic contention.

Considering NUCA, we classified the simulators as having support if they model at least multi-banked caches, also known as static NUCA (KIM; BURGER; KECKLER, 2003).

The memory controller is becoming more important in modern processors, because of its integration inside the processor chip. If a simulator only simulates a fixed latency for every DRAM request, it is classified as not capable of modeling a memory controller. Although SESC and PTLsim do not support memory controller modeling natively, extensions were proposed in order to overcome this deficiency.

We can observe that SiNUCA offers all the features required to evaluate cache memory mechanisms, simulating in detail the cache memories and memory controllers, while offering a highly detailed model of the OoO processor microarchitecture.

# 3.2 SiNUCA

We developed SiNUCA, a trace-driven simulator, which executes traces generated on a real machine with a real workload without the influence from the OS or other processes. The traces are simulated in a cycle-accurate way, where each component is modeled to execute its operations on a clock cycle basis. SiNUCA currently focuses on the x86\_32 and x86\_64 architectures.

SiNUCA was developed in C++ to make use of object-oriented principles and generate modular components. Such characteristics are preferable for simulators in order to ease the implementation of new features or components.

The ideal simulator should be as flexible as possible. Considering this, multiple parameters are available to be set through the SiNUCA configuration file. The configuration file is split into modules, such that each module contains the internal parameters to be used by the simulator. The simulator uses a component called SiNUCA configurator. It uses the *libconfig* (LINDNER, 2013) library internally to read the configuration file and to instantiate all the components inside SiNUCA. Libconfig is a fully reentrant parser and it supports include directives. In this way, SiNUCA components can be defined separately and included multiple times inside the main configuration file, facilitating the description of multi-core and many-core systems.

# 3.2.1 System Model

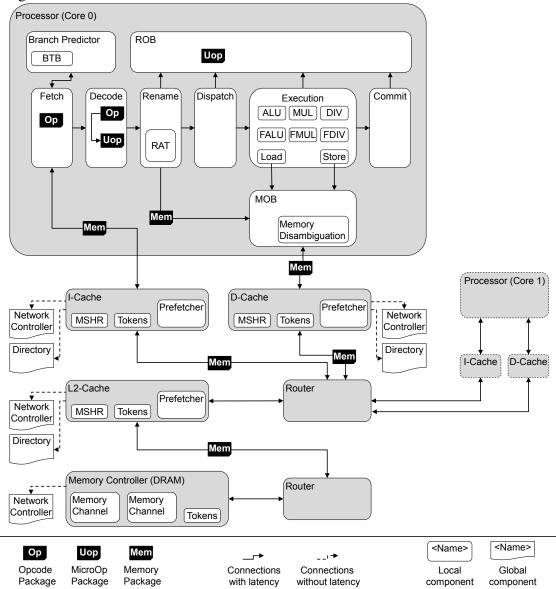

Figure 3.1: SiNUCA architecture with its main components and interconnections, modeling an Intel Core 2 Duo architecture.

The main components of SiNUCA are illustrated in Figure 3.1. The description of the components is presented below:

**Memory Package:** Every memory operation inside the simulator is encapsulated within this component.

**Opcode Package:** The instructions inside the simulator trace and front-end are encapsulated within this component.

**MicroOp Package:** After decoding the Opcode Package, the micro-operations are encapsulated within this component.

**Token:** Every communication between two memory components, such as cache memories and memory controllers, needs to request a token from the final package destination

before the communication starts. Tokens avoid deadlocks during package transfers that require more than one hop to reach their final destination.

**Processor:** This component is responsible for executing the Opcodes. It consists of the fetch, decode, rename, dispatch, execute and commit stages. Currently, only an OoO processor is modeled, implementing a Reorder Buffer (ROB) to handle the OoO execution. Further details about the processor's internal components will be presented in Section 3.2.2.

**Cache Memory:** This component is responsible for modeling instruction and data caches, both single and multi-banked models (static NUCA), implementing a Miss-Status Handling Registers (MSHR) internally per bank. This component keeps only the tag array of the cache, reducing the memory usage and the trace size.

**Miss-Status Handling Register (MSHR):** This buffer keeps information about the cache misses which arrive at each cache bank. The requests wait to be serviced and are then sent back to the requester in the case of a cache hit, or replicated to the next memory level in the case of a cache miss.

**Prefetcher:** The memory packages serviced by the cache memory are sent to the prefetcher, so that the memory addresses required by the application in the future can be predicted and fetched. This component is responsible for implementing several prefetch policies and to provide the cache memory with the generated requests as soon the cache has space in its MSHR. Currently, a *stride prefetcher* (BAER; CHEN, 1991) and a *stream prefetcher* (JOUPPI, 1990) are available to be simulated.

**Memory Controller:** This component implements the memory controller, formed by multiple channels, each channel with multiple banks. All memory requests that miss in all the cache levels will be sent to this component, which will schedule the requests to the memory banks. The memory controllers can support NUMA modeling as well.

**Memory Channel:** Inside the memory controller, multiple memory channels can be instantiated. Each channel may be connected to one or more banks, each bank with its own read and write buffers.

**Router:** This component was developed to model the contention and delays imposed by the interconnections. It implements a general NoC router that automatically delivers packages using the routing information inside each package.

**Network Controller:** This controller is used to generate a communication graph with the routes available in the modeled architecture. All packages that need to be transmitted have a pointer to the routing information contained in the routing table. The routing information describes which path to take for each intermediary component (routing input/output ports).