## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### CLAUDIO CARVALHO MENEZES

# Geração Automática de Leiaute Através de Matriz de Células – MARTELO

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Dr. Ricardo Augusto da Luz Reis Orientador

# CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Menezes, Claudio Carvalho

Geração Automática de Leiaute através de uma Matriz de Células NAND – MARTELO / Claudio Carvalho Menezes. – Porto Alegre: Programa de Pós-Graduação em Computação, 2003.

58f.: il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2003. Orientador: Ricardo Augusto da Luz Reis.

1.Microeletrônica. 2. Ferramentas de CAD. 3.Síntese Física. 4. Posicionamento. 5. Algoritmos. I. Reis, Ricardo Augusto da Luz. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitora: Profa. Wrana Maria Panizzi

Pró-Reitor de Ensino: Prof. José Carlos Ferraz Hennemann

Pró-Reitor Adjunto de Pós-Graduação: Prof. Jaime Evaldo Fernsterseifer Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux

Coordenador do PPGC: Prof. Carlos Alberto Heuser

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **FELICIDADE**

Casei por amor!!

Pois ela Roubou meu coração.

Foi Impossível dizer não.

Ser feliz?

Só o Tempo vai dizer.

Ilusão?

Não. Nasci para dividir:

Dar Alegria,

Dar Ternura, Dar Emoção,

Dar Amizade, Dar Magia. E descobrir aO final, Que não fui eu quem mais amou.

Claudio Menezes

# **AGRADECIMENTOS**

À minha família que soube compreender meu esforço e, em especial, à minha esposa Cristina pelo carinho, incentivo e paciência nas horas difíceis. Aos meus filhos Vítor e Rafael peço desculpas pelas brincadeiras das quais não pude participar e momentos em que fui obrigado a interromper-lhes os jogos de computador.

Aos colegas Reginaldo Tavares, Cristiano Lazzari e Renato Hentschke que contribuíram de maneira decisiva para a conclusão desse trabalho.

Finalmente, agradeço ao Prof. Ricardo Reis, por ter incentivado meu ingresso no mestrado e por sua preocupação constante em virtude das dificuldades que minhas atividades externas impuseram ao andamento dos trabalhos.

# **SUMÁRIO**

| LISTA DE ABREVIATURAS E SIGLAS                                | 6   |

|---------------------------------------------------------------|-----|

| LISTA DE FIGURAS                                              | 7   |

| LISTA DE TABELAS                                              | 8   |

| RESUMO                                                        | 9   |

| ABSTRACT                                                      | 10  |

| 1 INTRODUÇÃO                                                  | 11  |

| 1.1 Trabalhos Desenvolvidos pela UFRGS                        | 12  |

| 1.2 Objetivo da pesquisa                                      | 13  |

| 1.3 Organização da dissertação                                | 14  |

| 2 AS TECNOLOGIAS SUBMICRÔNICAS E ALTERNATIVAS PARA A SÍNT     | ESE |

| FÍSICA                                                        | 15  |

| 2.1 O impacto das interconexões nas tecnologias submicrônicas | 23  |

| 2.2 A Utilização de circuitos regulares                       | 26  |

| 3 O GERADOR DE LEIAUTE DE MATRIZES REGULARES - MARTELO        | 28  |

| 3.1 Fluxo de síntese utilizado                                | 29  |

| 3.2 Descrição da ferramenta de geração de leiaute MARTELO     | 30  |

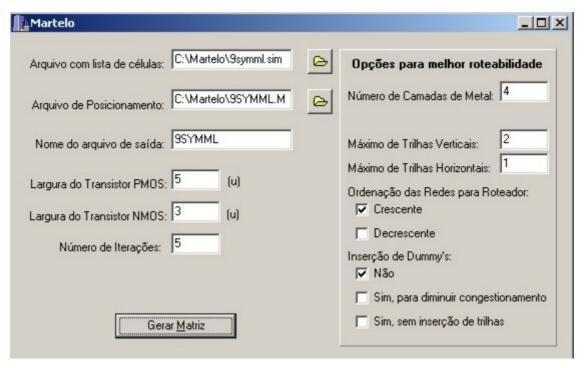

| 3.3 A interface da ferramenta MARTELO                         | 41  |

| 4 RESULTADOS                                                  | 43  |

| 5 CONSIDERAÇÕES FINAIS E TRABALHOS FUTUROS                    | 50  |

| REFERÊNCIAS BIBLIOGRÁFICAS                                    |     |

| ANEXO I                                                       | 56  |

# LISTA DE ABREVIATURAS E SIGLAS

ASIC Application Specific Integrated Circuit

CAD Computer-Aided Design

CMOS Complementary MOS

FPGA Field Programmable Gate Array

FOTC Full Over The Cell

GND Ground – Tensão de Referência

ITRS International Technology Roadmap for Semiconductors

LUT Look-up Table

NAND Célula lógica que representa a função booleana ~(A . B)

NOR Célula lógica que representa a função booleana ~(A + B)

NMOS N-channel Metal Oxide Semiconductor Field –effect transistor

PMOS P-channel Metal Oxide Semiconductor Field –effect transistor

TOF Time-of-Flight

VDD Tensão da Fonte de Alimentação

# **LISTA DE FIGURAS**

| Figura 2.1 – Efeito de Diminuição do Atraso através do aumento da Relação W/L,           |

|------------------------------------------------------------------------------------------|

| mantido um Fan-out de 2 para a Tecnologia de 0.25 μm (SYLVESTER;                         |

| KEUTZER, 1998)17                                                                         |

| Figura 2.2 – Efeito de diminuição do Atraso através do aumento da Relação W/L,           |

| mantido um Fan-out de 2 para a Tecnologia de 0,1um. (SYLVESTER; KEUTZER,                 |

| 1998)17                                                                                  |

| Figura 2.3 – Percentuais de Interconexões acima do Comprimento Crítico por               |

| Tecnologia e Tamanho do Módulo (HO et al., 1999),18                                      |

| Figura 2.4 – Implementação de uma LUT de três entradas em VPGA (PILEGGI et al,           |

| 2003)22                                                                                  |

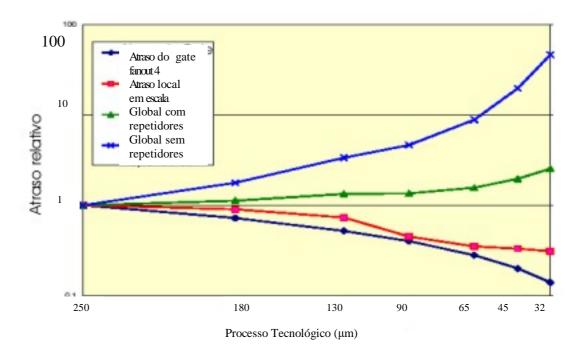

| Figura 2.5 – Atraso das interconexões segundo o Processo Tecnológico (ITRS 2001)24       |

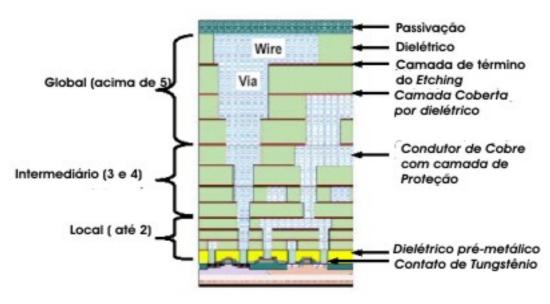

| Figura 2.6 – Visão em corte da distribuição das interconexões (ITRS, 2001)24             |

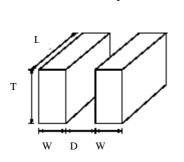

| Figura 2.7 – Dimensões das interconexões                                                 |

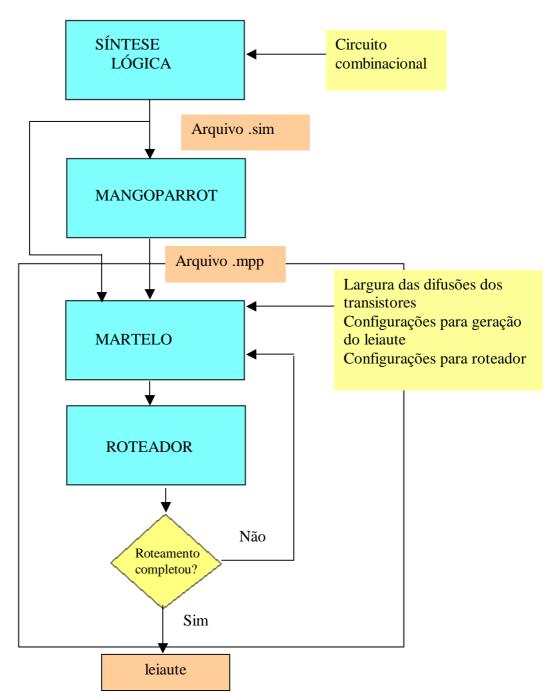

| Figura 3.1 – Fluxo de síntese para a geração do leiaute através de matrizes de células   |

| NANDs                                                                                    |

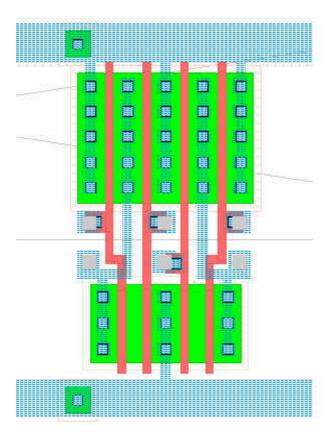

| Figura 3.2 – Leiaute de um par de NANDs utilizado como <i>template</i> para a geração da |

| matriz.                                                                                  |

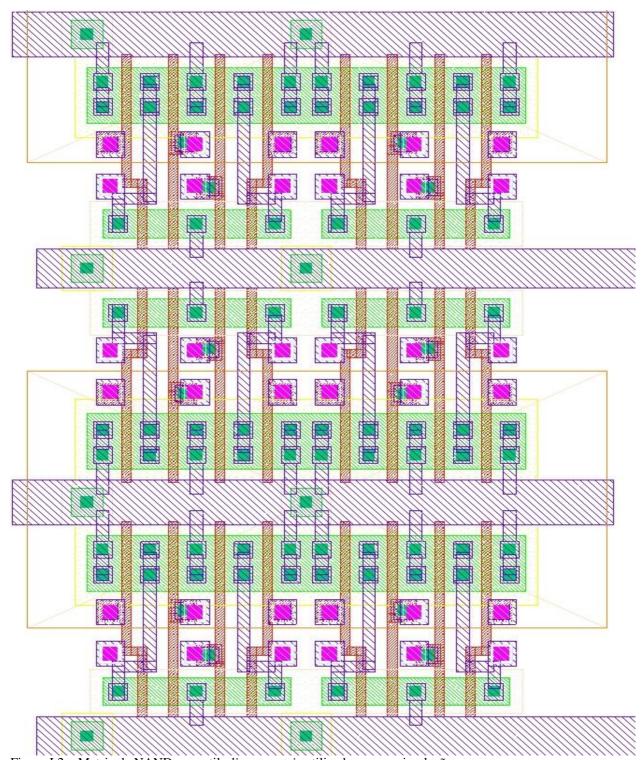

| Figura 3.3 – Leiaute de uma matriz 3 x 10 de NANDs gerada pelo MARTELO322                |

| Figura 3.4 – Contatos em metal1 inseridos entre NANDs pertencentes ao mesmo par33        |

| Figura 3.5 – Contato em metal1 inserido entre NANDs de pares distintos344                |

| Figura 3.6 – Inserção de trilha vertical pelo MARTELO                                    |

| Figura 3.7 – Inserção de trilhas horizontais pelo MARTELO36                              |

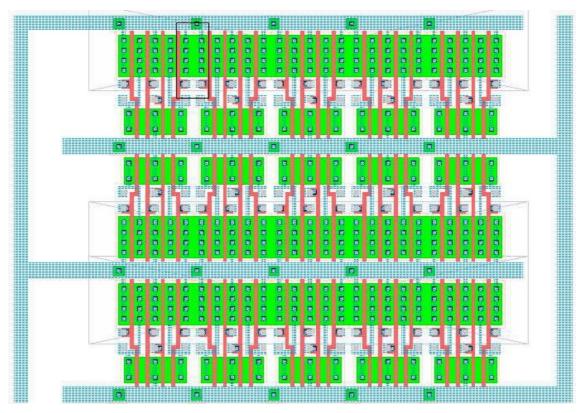

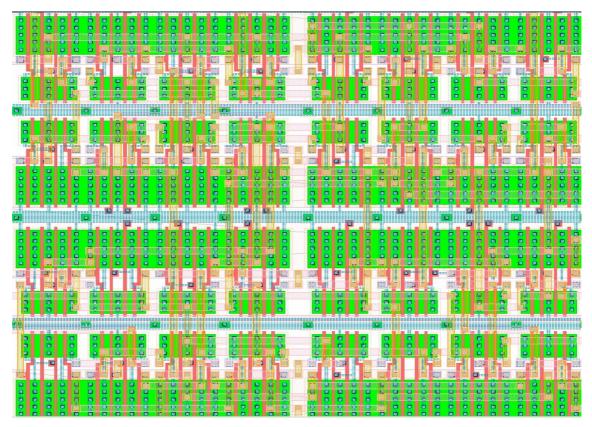

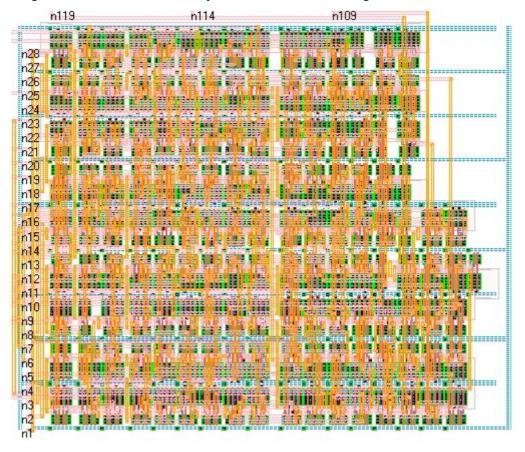

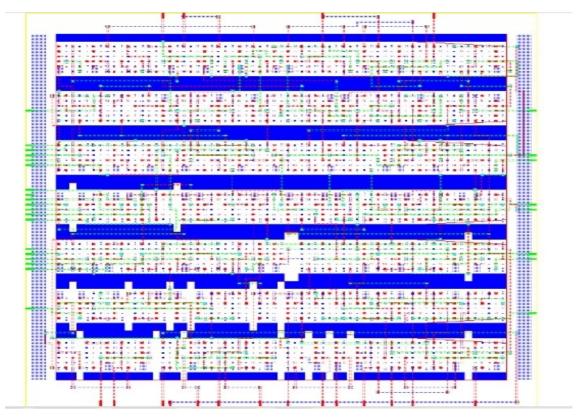

| Figura 3.8 – Leiaute do circuito 7seg com fanout 1 gerado com a ferramenta               |

| MARTELO39                                                                                |

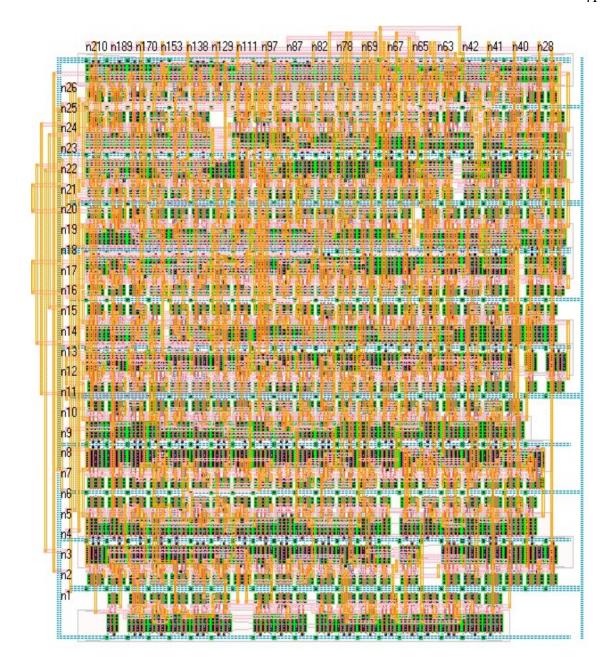

| Figura 3.9 – Leiaute do circuito 9symml com fanout máximo 4 gerado com a ferramenta      |

| MARTELO40                                                                                |

| Figura 3.10 – Leiaute do circuito frg1 com fanout máximo 4 gerado com a ferramenta       |

| MARTELO40                                                                                |

| Figura 3.11- Leiaute do circuito Lal com fanout 1 gerado com a ferramenta MARTELO.       |

| 41                                                                                       |

| Figura 3.12 – Interface da Ferramenta MARTELO42                                          |

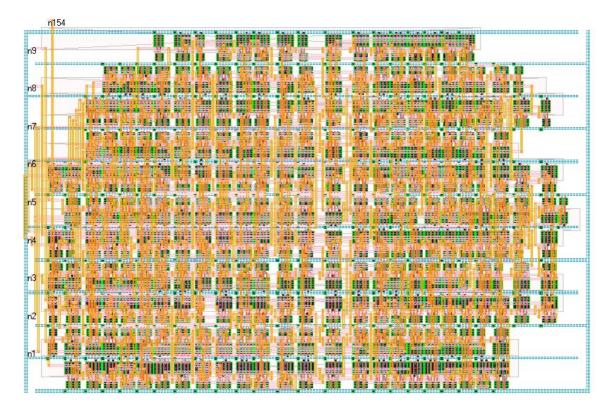

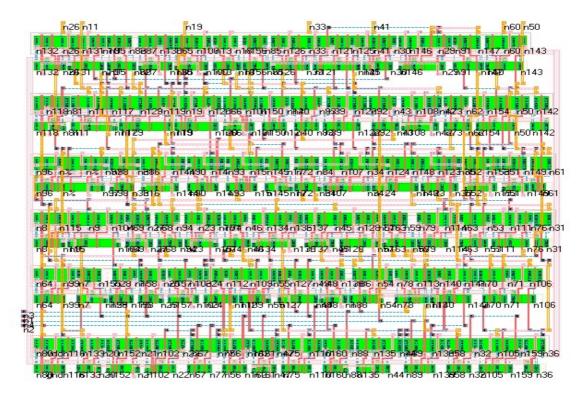

| Figura 4.1 – Leiaute do cirtuito 7seg com fanout 1 gerado com a ferramenta TROPIC.       |

| 48                                                                                       |

| Figura 4.2 - Leiaute do circuito 9symml com fanout máximo de 4 gerado com a              |

| ferramenta TROPIC                                                                        |

| Figura 4.3 – Leiaute do circuito 9symml com fanout 1 gerado com a ferramenta             |

| PKS_SHELL49                                                                              |

| Figura 4.4 – Leiaute do circuito Lal com fanout máximo 4 gerado com a ferramenta         |

| PKS_SHELL                                                                                |

# LISTA DE TABELAS

#### **RESUMO**

Esta dissertação enquadra-se em um processo de busca de soluções para a geração do leiaute de circuitos integrados que permitam aumentar a qualidade da previsibilidade do comportamento de um circuito após a sua implementação.

Isso é importante face ao crescimento dos problemas referentes aos efeitos elétricos adversos que surgem em nanocircuitos, tais como eletromigração, efeito antena, contatos mal formados e outros, assim como o aumento da variabilidade do processo de fabricação em tecnologias submicrônicas.

O foco deste trabalho de pesquisa é a busca de soluções regulares através do uso de matrizes de portas lógicas. A experimentação efetuada realiza a geração de uma matriz de portas NAND que viabiliza a implementação de equações lógicas mapeadas para redes de portas NAND e inversores, admitindo-se a parametrização do fanout máximo.

Foi desenvolvida uma ferramenta de CAD, o MARTELO, que permite efetuar a geração automática de matrizes de portas lógicas, sendo que a versão inicial está voltada para a geração de matrizes com portas NAND em tecnologia CMOS.

Os experimentos efetuados revelam que esta técnica é promissora, sendo apresentados alguns dos resultados obtidos.

**Palavras-chave:** síntese física, leiaute regular, Projeto visando Manufaturabilidade, CAD, tecnologia CMOS, concepção de circuitos integrados, microeletrônica.

### **ABSTRACT**

This work fits in a search of soluctions for layout generation of integrated circuits to allow an increase of circuit behavior previsibility after its implementation.

This is important due to the increase of problems relating to the electric issues that must be considered in nanocircuits, like electromigration, antenna effect, bad contacts and others as well as the variability of the fabrication process in submicron technologies.

This research looks for solutions using regular circuits based on the use of matrix of logic cells. The experimentation is related to the generation of a matrix of NAND cells for circuits that were mapped to a set of NANDs and inverters, including the parametrization of the fanout.

It was developed a CAD tool, MARTELO, that allows the automatic generation of matrix of logic cells, and its initial version generates matrices with NAND cells using CMOS technology.

The experiments showed that this is a promising technique and some results are presented.

**Keywords**: physical synthesis, regular layout, Design for Manufacturability, CAD, CMOS technology, integrated circuits design, microelectronic.

# 1 INTRODUÇÃO

A geração do leiaute de circuitos integrados está sempre envolta em novos desafios decorrentes dos avanços tecnológicos que permitem a fabricação de circuitos cada vez menores, viabilizando assim, uma maior densidade de integração. Com o desenvolvimento de tecnologias em escalas submicrônicas, é possível integrar mais de um bilhão de transistores em um único circuito integrado, o que exige a adoção de estratégias bem planejadas para que se consiga obter resultados com desempenho satisfatório. Em especial, as interconexões exigem um esforço extra de pesquisa, pois elas constituem um dos desafios importantes em projetos com alta escala de integração.

Por esses motivos, torna-se necessária a obtenção de ferramentas de síntese física cada vez mais complexas para possibilitar o tratamento adequado dos parâmetros de projeto dos circuitos e que respondam inclusive, aos novos problemas decorrentes da variabilidade dos processos de fabricação.

Problemas de potência, aquecimento, níveis de ruído e distribuição do relógio também são variáveis que integram esse cenário e aumentam ainda mais a complexidade de um projeto, obrigando o estabelecimento de um alto nível de cooperação entre a equipe de projeto lógico e a de síntese física, visto que as possíveis soluções passam, provavelmente, por uma maior integração das ferramentas hoje disponíveis.

Verifica-se portanto, que é necessário buscar novas metodologias de projeto que permitam o aumento da previsibilidade das etapas do processo de síntese. Uma alternativa é a utilização de leiautes regulares, pois os mesmos facilitam o gerenciamento da complexidade de circuitos em tecnologias submicrônicas.

Esses trabalhos buscam através da diminuição da complexidade do problema, obter resultados que satisfaçam às especificações do projeto e viabilizem a produção de circuitos em escala comercial em menor prazo.

Desta forma, têm sido publicados trabalhos que exploram alternativas como VPGA – *Via Pattern Gate Array* (PILEGGI et al., 2003), River PLA – *Programmable Logic Array* (MO; BRAYTON, 2002), e metodologia de fabricação de circuitos 'sem ruído' (KHATRI et al., 1999). Entre os objetivos desses trabalhos cita-se: aumentar a capacidade de produzir circuitos com maior índice de produtividade e resolver problemas decorrentes da variabilidade randômica das tecnologias submicrônicas, ao mesmo tempo em que satisfazem às restrições impostas ao projeto.

A UFRGS possui dois trabalhos nessa área: o MARCELA (GÜNTZEL,1993) e o MARAGATA (LIMA, 1999). Ambos tratam da geração de leiaute de circuitos integrados com a utilização de matrizes regulares e se encaixam nos mesmos objetivos propostos pelos trabalhos acima citados.

Essas pesquisas envolvendo a utilização de estruturas regulares para a geração do leiaute de circuitos integrados estão buscando alternativas que permitam diminuir o

"Déficit de Produtividade de Projeto" – problema que está aumentando sensivelmente à medida que as tecnologias submicrônicas estão se aproximando dos limites físicos dos materiais e suscitando problemas de ordem atômica.

Ocorre que hoje, o aumento do número de etapas do processo de fabricação e a diminuição das dimensões dos dispositivos levam ao aumento da complexidade do mesmo, pois aumentam os detalhes de ordem física que precisam ser controlados com a precisão necessária para a correta fabricação de um circuito integrado.

Para a condução exata do processo de fabricação exige-se, não somente, instrumentos e técnicas avançados, mas trabalhar detalhes a nível de síntese física a fim de impedir que configurações que diminuem o rendimento predominem no leiaute do circuito integrado a ser fabricado, como por exemplo, áreas onde há maior número de camadas e áreas onde há menor número de camadas. A combinação desses dois fatores causa o surgimento de áreas espessas (com diversas camadas) e áreas finas (com poucas camadas) no circuito integrado e mesmo utilizando técnicas de correção de desnível, algumas acabam sofrendo distorções acima dos limites permitidos (Pileggi et al., 2003).

Em outro exemplo, a distribuição randômica de vias com contatos mal formados pode ser minimizada com utilização de pequenas quebras nas interconexões de forma a evitar a mudança desnecessária entre níveis de metal (Pileggi et al., 2003).

Por esses motivos, circuitos que seguem determinados padrões de repetição facilitam a condução do processo de fabricação, pois são mapeados para as máscaras com maior precisão e com menor probabilidade de gerar erros, permitindo que a fabricação em si possua maior rendimento e também aumentando o controle e a previsibilidade dos resultados.

Deste modo, a utilização de circuitos regulares consiste em uma metodologia de projeto que visa obter uma maior previsão dos resultados sem sacrificar demasiadamente o desempenho e/ou a área, ao mesmo tempo que concede ao projetista melhores estimativas de desempenho e consumo dos circuitos integrados produzidos.

#### 1.1 Trabalhos Desenvolvidos pela UFRGS

A Universidade Federal do Rio Grande do Sul tem realizado pesquisas nessa área, cujos resultados fazem parte de diversas publicações. Especificadamente, tratando-se da área de projeto físico, destacam-se alguns trabalhos como o TRAMO – TRAnca Module Generator, elaborado por Lubaszewski (1990), que utiliza uma biblioteca de células padrão e busca otimizações baseadas nas observações realizadas em leiautes de bloco de lógica aleatória desenhados a mão, conforme trabalho de Reis (1983). Essa metodologia utiliza células provenientes de uma biblioteca específica, mas prevendo o uso de células geradas automaticamente.

Ainda nessa época, foi concluído o TRAGO (MORAES, 1990) que também utiliza a metodologia TRANCA (TRANspatrent Cell Approach), porém realiza a síntese automática de leiaute sem utilizar biblioteca de células. Este trabalho utiliza a topologia de leiaute em bandas, onde os transistores são dispostos em tiras horizontais para permitir a parametrização elétrica e a união dos transistores por justaposição.

Posteriormente, surgiu o TRAMO II, elaborado por Reis (1993), onde foi pesquisada a construção de um método para a geração automática das células e foram efetuadas modificações na ferramenta TRAMO para possibilitar a utilização de padrões gerados automaticamente, usar uma segunda camada de metal no roteamento e aumentar a transparência da célula em ambas as direções (horizontal e vertical).

Logo após foi desenvolvido o TRAMO III (KINDEL, 1997) que também faz a geração do leiaute de circuitos integrados, porém desta vez foi realizada a síntese automática das células em vez de utilização de uma biblioteca. Essa ferramenta utiliza o estilo *linear matrix* para a geração do leiaute, porém os transistores são dispostos verticalmente "[....] a fim de aproximar-se de resultados observados em leiautes manuais" (KINDEL, 1997).

Outro importante trabalho na área de síntese física é o TROPIC, desenvolvido por Moraes (1994), que utiliza uma biblioteca virtual de células, permite até três níveis de metal, tem independência tecnológica e roteamento interbandas. Esse trabalho compõese de um conjunto de três ferramentas: um posicionador, um roteador e um gerador de leiaute. Uma característica importante deste trabalho é a geração do leiaute de qualquer célula complexa de quatro entradas, possibilitando assim uma otimização da lógica utilizada.

Existem também dois trabalhos que tratam da geração de leiaute através de matrizes regulares. O primeiro trabalho denomina-se MARCELA – Geração de Circuitos Utilizando Matrizes de Células Pré-difundidas, desenvolvido por Güntzel (1993) que utiliza uma matriz composta por quatro de tipos de células básicas (NAND, NOR, Inversor e *Transmission Gate*) como estrutura básica para a geração de circuitos integrados. Essa estrutura é replicada para formar uma matriz regular, e utiliza algoritmos dedicados para posicionamento e roteamento.

Outra pesquisa importante na área é o MARAGATA – Projeto de Matrizes de Células Lógicas Programáveis – elaborado por Lima (1999), que investigou a utilização de blocos lógicos programáveis – *Universal Logic Gates (ULG)* – para geração de circuitos integrados através de uma matriz programável pelo último nível de metal.

Além das pesquisas específicas para geração de leiaute, outras na área de síntese lógica (TAVARES, 1995), análise de *timing* (GÜNTZEL, 2000), roteamento (JOHANN, 1994) e posicionamento (Hentschke, 2002) complementam os estudos precedentes e compõem um conjunto de ferramentas para síntese de circuitos integrados disponibilizados pela Universidade através do projeto FUCAS (maiores detalhes podem ser obtidos na página www.inf.ufrgs.br/gme).

Face aos trabalhos já realizados na UFRGS, procurou-se então desenvolver um estudo que contemplasse a geração automática de leiaute baseando-se em matrizes que explorassem soluções visando à regularidade das estruturas. Essa proposta vem em encontro das dificuldades de geração de leiaute *full custom* por causa do aumento da complexidade da síntese física nas tecnologias submicrônicas, ao mesmo tempo em que se coloca como uma opção para a geração do leiaute de circuitos integrados que satisfizesse critérios para a obtenção de maior produtividade.

É necessário que a matriz possa gerar o leiaute de circuitos em tecnologia CMOS e que seja compatível com um método de síntese lógica que vise mapear a função para matrizes de células.

## 1.2 Objetivo da pesquisa

O objeto de pesquisa dessa dissertação é a busca de estratégias para geração de leiaute através de uma matriz de células. Porém existem duas diferenças importantes em relação aos dois estudos anteriores realizados na UFRGS: a primeira, diz respeito ao tipo de célula utilizada, pois se trata de uma matriz de células parametrizáveis de configuração; a segunda, é que estas células deverão estar dispostas numa estrutura regular que permita o roteamento total por sobre as células.

Os principais objetivos que se deseja alcançar com esse tipo de geração automática de leiaute são: regularidade do leiaute; possibilidade de produzir a matriz como um prédifundido e fazer a customização pelas trilhas de metal; a obtenção de uma melhor e mais fácil caracterização elétrica dos atrasos das interconexões – pela regularidade e repetição da "paisagem" sobre as quais as conexões são realizadas; e a melhor caracterização do atraso das portas lógicas utilizadas, visto que as mesmas estão dispostas em uma estrutura regular.

Nessa dissertação, foi implementado um gerador de leiautes regulares baseado em uma matriz de NANDs de duas entradas. Elas estão dispostas segundo o estilo de leiaute *linear matrix*. Esta ferramenta fará parte de um fluxo de síntese de circuitos integrados desenvolvido pela UFRGS e que integra o projeto FUCAS.

## 1.3 Organização da dissertação

Para compreender o escopo desse estudo, inicia-se com uma discussão sobre as tecnologias submicrônicas, onde se coloca o estado da arte na geração de leiaute de circuitos integrados e os desafios decorrentes dos avanços tecnológicos. Procura-se informar as perspectivas de pesquisas que estão sendo realizadas na área.

Após esse detalhamento, procura-se justificar a escolha do modelo utilizado para a geração da matriz. Os resultados das simulações elétricas estão descritos no trabalho de Menezes, em 2003 e serão brevemente mencionados. Procurou-se, nesse texto, focar mais nos fatores estratégicos que resultaram na escolha realizada.

Esse mesmo capítulo descreve o funcionamento das ferramentas de CAD associadas ao projeto. A ferramenta de síntese física é descrita com mais detalhes, em especial os ajustes de largura dos transistores PMOS e NMOS, a realização de conexões em metal 1 entre NANDs vizinhas, as opções de ordenamento das redes para o roteador, a possibilidade de inserção de trilhas verticais e horizontais para facilitar a tarefa do roteador e a inserção de células de interconexão em posições estratégicas.

Posteriormente, passa-se a detalhar os resultados das simulações elétricas realizadas em vários circuitos, destacando-se os impactos em área e desempenho.

Por fim, apresentam-se as considerações finais e trabalhos futuros.

# 2 AS TECNOLOGIAS SUBMICRÔNICAS E ALTERNATIVAS PARA A SÍNTESE FÍSICA

As tecnologias submicrônicas, apesar de permitirem a geração de circuitos com maior desempenho e maior densidade de integração, também trazem dificuldades causadas por problemas como maior variabilidade dos parâmetros do processo e efeitos físicos indesejáveis como eletromigração, efeito 'antena', *cross-talk*, contatos mal formados ou com alta resistividade, distribuição do relógio, aquecimento, níveis de ruído e outros.

Além disso, está se chegando ao limite físico dos materiais<sup>1</sup> atualmente utilizados, inclusive com a necessidade de busca de substitutos apropriados para aqueles que em virtude de suas propriedades físicas não poderão ser utilizados por causa da degradação do desempenho ou por incompatibilidade com o processo de fabricação.

Esses problemas vêm se intensificando cada vez mais por causa da redução da escala da tecnologia, do acréscimo do número de etapas no processo de fabricação, do aumento das dimensões do *wafer* e da área do circuito em virtude da maior quantidade de lógica incluída, em suma, a complexidade da tarefa tem aumentado.

No trabalho de Maly, et al. (1996), pode-se ter uma visão mais abrangente desses problemas e de estratégias que vêm sendo estudadas para contornar esses efeitos já que eles têm afetado drasticamente os custos de fabricação<sup>2</sup> pois reduzem a taxa de produtividade e conseqüentemente aumentam aqueles. São estudados nesse trabalho, desde problemas oriundos de poeiras, passando pelo mapeamento dos mecanismos de geração de erros no processo de fabricação e alcançando, inclusive, a identificação de tipos de projetos que são mais suscetíveis a falhas por maior sensibilidade às variações do processo.

Merecem destaque algumas metodologias que visam diminuir o impacto desses efeitos, como por exemplo:

- a utilização de bibliotecas mais 'resistentes' a mecanismos de erros: as células dessas bibliotecas são construídas de forma a ter menor probabilidade de falha quando submetidas a processo de fabricação em meio a contaminação;

- inclusão de modelos de produtividade na síntese lógica que indiquem o índice de aproveitabilidade do processo de fabricação baseado nos tipos de células utilizadas, densidade do leiaute e na disposição das interconexões; e

<sup>&</sup>lt;sup>1</sup> O ITRS 2001 estima que no atual ritmo de *scaling* o Transistor MOS deve atingir seu limite físico por volta de 2007.

<sup>&</sup>lt;sup>2</sup> Os custos de implantação de uma fábrica de circuitos integrados subiram de \$ 50 milhões na década de 1980 para \$ 2,7 bilhões em 2001[ITRS 2001].

escolha da escala da tecnologia como fator ponderado entre produtividade, desempenho e time-to-market<sup>3</sup>.

Os trabalhos de Sylvester; Keutzer (1998) e Sylvester; Keutzer (1999), levantam diversas questões que precisam ser levadas em consideração para a obtenção de circuitos integrados que satisfaçam às restrições do projeto nas tecnologias submicrônicas. Um dos principais fatores diz respeito ao percentual de influência das interconexões no atraso total do circuito que em certos casos responde por 80% ou mais do atraso. Outro item importante são os efeitos decorrentes do aumento da densidade de corrente em algumas áreas do circuito, ocasionando problemas na potência dissipada.

Além disso, à medida que a escala da tecnologia diminui, os problemas acima mencionados aumentam pois as distâncias entre os diversos componentes do leiaute ficam cada vez menores. Por esses motivos, Sylvester; Keutzer (1998) buscam identificar qual a quantidade de transistores que, incluídos num mesmo módulo, não apresentariam efeitos que degradassem seu desempenho, quando submetidos à redução de escala da tecnologia.

Em seus estudos, eles chegam a conclusão de que módulos de, aproximadamente, 50.000 transistores, poderiam ser sintetizados utilizando o máximo que a tecnologia dispõe e não ocorreria a degradação do desempenho do circuito integrado quando da mudança de escala de tecnologia, pois as interconexões utilizadas nesse bloco seriam predominantemente curtas e uma redução de escala não afetaria o desempenho do circuito a ponto de comprometer seu funcionamento.

Observa-se que com essa quantidade de transistores, podem ser embutidos diversos tipos de ASIC num mesmo módulo.

Outro fato importante mencionado pelos autores, é que em blocos lógicos de até 50.000 transistores, um aumento da relação W/L, ou seja, entre a largura (W) da difusão do transistor e comprimento (L) do canal do transistor, reduz o efeito no atraso causado pelas interconexões, apesar do aumento da área do circuito. Entretanto, existe um ponto ideal acima do qual o aumento dessa relação não acarreta nenhum benefício.

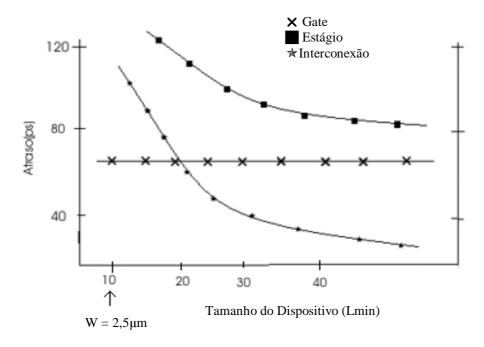

Os autores inferem que isso se deve ao pequeno aumento do comprimento médio das interconexões e à utilização de novos materiais. As Figuras 2.1 e 2.2 mostram os resultados dos testes efetuados. Eles sugerem a manutenção de uma relação W/L em torno de 20 como relação ótima entre a largura (W) do transistor e a largura(L) do canal do transistor para se obter uma redução da influência do atraso das interconexões em contrapartida ao aumento de área do circuito em virtude do aumento da largura da difusão do transistor.

Cabe aqui uma menção no que diz respeito à utilização de circuitos regulares para a síntese desses módulos, pois como há área disponível, um acréscimo pequeno da mesma pode não representar perdas significativas. E conforme será colocado adiante, a regularidade permite uma maior probabilidade de geração de circuitos sem os erros decorrentes das variabilidades do processo de fabricação. Isso resultaria em maior número de circuitos funcionais por *wafer*.

\_

<sup>&</sup>lt;sup>3</sup> É preferível lançar o produto no mercado, mesmo com menor desempenho, do que perder a oportunidade e o investimento aplicado.

$0.25 \ \mu m \ L = 80 \ \mu m \ FO = 2$

Figura 2.1 – Efeito de diminuição do atraso através do aumento da relação W/L, mantido um fanout de 2 para a tecnologia de  $0.25~\mu m$  (SYLVESTER; KEUTZER, 1998)

Figura 2.2 – Efeito de diminuição do atraso através do aumento da relação W/L, mantido um fanout de 2 para a tecnologia de 0,1um. (SYLVESTER; KEUTZER, 1998)

Em seu trabalho, Ho et al (1999), faz algumas colocações sobre os estudos de Sylvester; Keutzer (1998) e Sylvester; Keutzer (1999). Basicamente, ambos concordam que blocos de até 50.000 portas lógicas podem ter a escala da tecnologia reduzida sem comprometimento do desempenho do circuito e que as interconexões dentro desse bloco seriam predominantemente curtas.

Porém, divergem quanto a capacidade das ferramentas de CAD atuais manusearem circuitos com até 50.000 transistores por causa do aumento da complexidade do processo à medida que há redução da escala da tecnologia. Ho et al (1999) conclui que circuitos com essa quantidade de transistores podem apresentar interconexões acima do comprimento crítico<sup>4</sup>, pois possuem perímetro em torno de 4mm para uma tecnologia de 0,25µm.

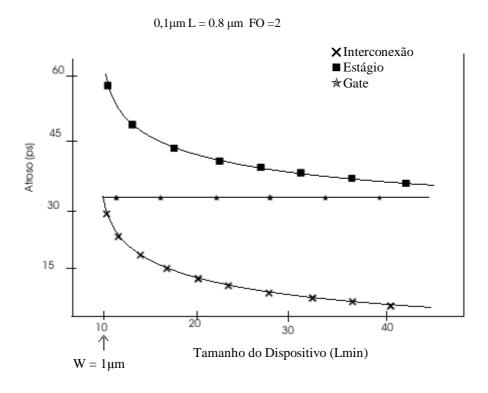

O trabalho de Ho et al (1999) apresenta uma estimativa do percentual da presença desse tipo de conexão, nesses circuitos. Observe na Figura 2.3 os resultados dos testes que estimam o percentual de interconexões que excedem o comprimento crítico para diversos tamanhos de circuitos integrados.

Fanout = 3; 70% de ocupação

Figura 2.3 – Percentuais de interconexões acima do comprimento crítico por tecnologia e tamanho do módulo (HO et al., 1999),

Verifica-se portanto, que apesar dos pequenos percentuais de conexões longas para os diversos tamanhos de blocos lógicos apresentados, elas aumentam à medida que a escala de tecnologia é reduzida. Isso vai exigir ferramentas de CAD capazes de identificar e contornar essas dificuldades.

Assim, novos detalhes deverão ser tratados pelas ferramentas de CAD e entre eles cita-se: o gerenciamento das interconexões que ultrapassarem o comprimento crítico (HO et al., 1999), o aumento do número de módulos a serem gerenciados conjuntamente

<sup>&</sup>lt;sup>4</sup> É o tamanho mínimo para que uma interconexão sofra degradação de propagação do sinal por causa das altas freqüências hoje utilizadas. Para a tecnologia 0,25um, o comprimento crítico é de aproximadamente, 1,3mm(Ho et al 1999).

(HO et al., 1999),o efeito da indutância associada a essas interconexões(MEIJS; SMEDES, 1996) e a influência do *cross-talk* entre circuito e substrato (MEIJS; SMEDES, 1996), dentre outras.

Todos os itens mencionados mostram a complexidade cada vez maior do problema e, além deles, outros também já causam problemas como: as interconexões globais<sup>5</sup> com vários milímetros de comprimento que exigem a inclusão de repetidores para que seja mantida a integridade do sinal; o tempo-de-vôo<sup>6</sup> (TOF) do sinal no circuito que representa um limite físico ao aumento da freqüência de operação; e, a complexidade de tratar em conjunto todos esses módulos, em especial quanto aos efeitos de *cross-talk* entre os circuitos e o substrato (MEIJS; SMEDES, 1996).

A partir desses problemas, outras dificuldades surgem decorrentes das alternativas de soluções propostas:

- ➢ ao criar níveis de metal específicos para o roteamento global, utilizando largura maior que o mínima de duas a vinte vezes maior que a largura mínima da interconexão com o objetivo de diminuir a resistência das mesmas é necessário resolver problemas de congestionamento, priorização das conexões e indutância associadas. Esses canais mais largos são ainda subdivididos de acordo com a localização das conexões globais a serem efetuadas em zonas isocrônicas<sup>7</sup> ou não isocrônicas.

- ➤ a inserção de repetidores é conseqüência da degradação do sinal por efeito do atraso RC e pelo aumento da capacitância associada a interconexões globais. Isso causa um aumento da potência dissipada pois juntos, as interconexões e os repetidores, na tecnologia de 50nm, respondem por valores entre 30% a 40% da potência dissipada pelo circuito, além de aumentar a sensibilidade ao ruído.

- Como o TOF inibe a utilização de freqüências acima da maior distância a ser percorrida, passa-se a trabalhar com mais de uma freqüência no *chip*, sendo uma utilizada entre módulos isocrônicos e outra, de menor valor, utilizada para as conexões globais. Além disso, são necessárias adaptações no encapsulamento para permitir a distribuição do relógio por toda a superfície do circuito e não mais somente na periferia.

Com certeza, face aos obstáculos mencionados, a obtenção de resultados satisfatórios na geração dos circuitos integrados passa pela integração cada vez maior das ferramentas de CAD e, via de regra, se estará aquém daquilo que a tecnologia pode oferecer, pois aquelas necessitam tratar o aumento da densidade de integração conjuntamente com a complexidade cada vez maior do processo de fabricação. Todos esses fatores estão reduzindo a taxa de produtividade e, conseqüentemente, aumentando consideravelmente os custos de produção.

Esse é o conhecido "Déficit de Produtividade do Projeto" mencionado por Kahng (2001) e Pileggi et. al. (2003).

O trabalho de Kahng (2001) também menciona vários dos desafios que estão sendo enfrentados na busca por soluções que viabilizem os investimentos em novas tecnologias e propiciem a continuidade dos avanços tecnológicos na área de circuitos integrados. Entretanto, Kahng não se restringe apenas aos aspectos técnicos da geração

\_

<sup>&</sup>lt;sup>5</sup> Estima-se que uma conexão global num circuito integrado varie entre 2 a 8 mm dependendo da tecnologia utilizada e do tamanho do circuito. Casos extremos chegam a incluir conexões com até 15mm.(SYLVESTER; KEUTZER, 1999)

<sup>&</sup>lt;sup>6</sup> Tempo que um sinal leva para percorrer o circuito integrado de ponta a ponta.

<sup>&</sup>lt;sup>7</sup> Região dentro da qual o sinal de *clock* não sofre diferença de fase.

do circuito integrado, mas tenta interrelacionar outros campos, em especial o econômico, visto deste depender o aporte de recursos para o prosseguimento das pesquisas.

Após descrever alguns dos atuais desafios já acima apresentados, Kahng (2001) estima que para se obter produtos economicamente viáveis num futuro próximo, é necessário alcançar altos volumes de produção com alto valor agregado. Porém, para a obtenção desses resultados, será obrigatória a integração das diversas ferramentas de CAD e, além disso, ser capaz de contornar os obstáculos de produtividade.

Os projetos desenvolvidos por Kahng (2001), no *MARCO Gigascale Silicon Research Center* também estão procurando saídas factíveis para essas barreiras físicas e de complexidade crescente, descrevendo-se abaixo algumas das principais alternativas estudadas:

- A integração das ferramentas de síntese, posicionamento e roteamento é vista como um fator importante para se obter uma melhor convergência dos projetos e cada vez mais as otimizações são obtidas somente a partir de um trabalho harmônico entre essas ferramentas;

- As variabilidades randômicas do processo de fabricação e, em especial, as variabilidades sistemáticas devem ser consideradas ainda nas etapas de síntese lógica, posicionamento e roteamento. Como exemplo, eles citam problemas na litografia que, para a correção do arrendondamento nas bordas e diminuição da largura de interconexões, são utilizadas técnicas que afetam os custos de inspeção das máscaras e aumentam os erros produzidos por variabilidades do processo. Outros problemas decorrem da variação de densidade do leiaute, surgindo assim áreas altas e baixas no circuito integrado que causam dificuldades durante o processo de planarização químico-mecânica;

- Avanços nas técnicas de litografia também serão decisivos para se fabricar circuitos que, apesar de obedecerem às regras de projeto ainda possuem sérias restrições por problemas de variabilidades randômicas e sistemáticas do processo. Inclusive, dependendo do tipo de técnica utilizada durante a fabricação pode-se afetar substancialmente um ou outro aspecto do circuito, devendo o projetista ter conhecimento de qual setor do leiaute deve se ter mais atenção em seu projeto de forma a aumentar a produtividade através da redução de falhas devido à variabilidade do processo;

- A vida útil de uma máscara, por estar limitada a algo em torno de 500 wafers (KAHNG, 2001), precisa ser maximizada através da inclusão de uma maior quantidade de circuitos por máscara; e

- A complexidade dos projetos em desenvolvimento tem obrigado o projetista a procurar soluções utilizando estratégias em níveis de abstração cada vez mais altos. Como exemplo, os autores citam que a solução de problemas de potência dissipada pelo circuito pode envolver mudanças no posicionamento, na lógica, na distribuição do relógio e/ou adição de modo de 'espera' no circuito. Essas estratégias estão em um nível de hierarquia superior do projeto, porém a complexidade das informações manipuladas a nível de síntese física nas tecnologias submicrônicas, mantém a implementação do circuito integrado em baixo nível de abstração, inexistindo ainda ferramentas que façam a interligação entre essas duas etapas do processo a fim de estimar os efeitos decorrentes das mudanças propostas.

Todos esses desafios visam satisfazer não só à necessidade de aumento do desempenho dos circuitos, mas também aos critérios econômicos que sustentam os investimentos no setor. Além disso, o tempo que as inovações tecnológicas levam para serem utilizadas em produtos comerciais demora algo em torno de cinco a sete anos, conforme dados de Kahng (2001), obrigando os projetistas a trabalharem na busca de soluções sem poder dispor dessas inovações.

Como citado anteriormente, a isso se denomina "Déficit de Produtividade de Projeto" e consiste num obstáculo que foi bem resumido na frase abaixo:

"[...] what we can build in a next generation technology is continually outpacing what we can afford to build in that technology." (PILEGGI et al., 2003)<sup>8</sup>

Como os autores anteriores, Pileggi et al. (2003), atribui essa dificuldade ao aumento da complexidade da síntese física e discute pontos específicos do processo de fabricação, apontando problemas decorrentes da existência de variabilidades randômicas e sistemáticas do processo de fabricação, dificuldades de realizar apropriadamente o *etching*, o polimento químico mecânico, além de outras etapas do processo de síntese física.

Por outro lado, a adoção de técnicas que aumentam a regularidade do projeto podem representar uma possibilidade que permita utilizar as vantagens decorrentes dos avanços tecnológicos sem os altos custos envolvidos face às perdas provocadas pelo rendimento do processo de fabricação.

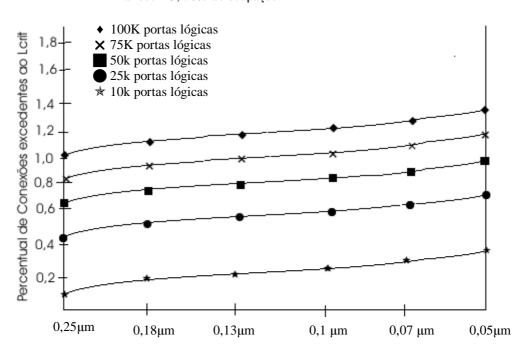

Pileggi et al. (2003) exploram a utilização de uma estrutura denominada Via Patterned Gate Array – VPGA. Esta representa uma solução de compromisso entre o FPGA e *standard cells*. Ao utilizarem *look-up-tables* como a da Figura 2.4 ou blocos de células lógicas heterogêneas e customizando o roteamento por meio de máscaras em vez de chaves CMOS, eles obtiveram um alto grau de regularidade do projeto.

Desta forma, apesar das perdas em área e desempenho, eles observam que a regularidade do projeto pode melhorar as estimativas das previsões de desempenho, que conseqüentemente podem ser ajustadas por meio de otimizações na lógica, compensando em parte as desvantagens do projeto regular.

Convém ressaltar que a utilização de estruturas regulares personalizáveis pelas camadas de metal já foi utilizada nos projetos MARCELA e MARAGATA desenvolvido na UFRGS, respectivamente por Güntzel (1993) e Lima (1999).

Pileggi et al. (2003) realiza testes com alguns circuitos e os resultados podem ser observados na Tabela 2.1. Todos os projetos foram gerados utilizando a tecnologia 0.13μm CMOS e foram sintetizados para alcançar o máximo desempenho possível. O resultado A refere-se à utilização de *standard cells*, os resultados B e C refletem o uso da metodologia VPGA. Os valores dos atrasos correspondem à média dos 10 maiores atrasos encontrados. Pode-se perceber que em termos de desempenho, ambos os resultados possuem valores aproximados, entretanto há uma perda considerável em área.

\_

<sup>&</sup>lt;sup>8</sup> [...] o que podemos construir com a próxima geração tecnológica está continuamente defasado com o que podemos ser capazes de construir naquela tecnologia.

Figura 2.4 – Implementação de uma LUT de três entradas em VPGA (PILEGGI et al, 2003)

Tabela 2.1 – Resultados de síntese utilizando Standard Cells (A) e a metodologia VPGA (B e C).

| Circuitos      | n.° de | Atraso médio 1-10 (ns) |        |        | Área (micra quadrados) |        |         |

|----------------|--------|------------------------|--------|--------|------------------------|--------|---------|

|                | portas | A                      | В      | C      | A                      | В      | С       |

| A51LU          | 651    | -0.45                  | -0.30  | -0.31  | 5600                   | 7800   | 18225   |

| DLX Controller | 552    | -1.05                  | -0.942 | -0.961 | 5476                   | 9216   | 16875   |

| Firewire       | 4247   | -1.31                  | -1.45  | -1.77  | 27027                  | 40944  | 56250   |

| FPU            | 24640  | -7.68                  | -7.81  | -9.35  | 409600                 | 562500 | 1103625 |

Fonte: Pileggi et al., 2003.

Outro trabalho na área é o desenvolvido por Mo; Brayton (2002), através da estrutura denominada River-PLA. Como primeira justificativa para a adoção de estruturas regulares eles citam a utilização pelos fabricantes de técnicas que detectam padrões geométricos nas máscaras que permitam alcançar melhor qualidade de exposição e de imagem; e como segundo principal motivo, a previsibilidade das características dos circuitos.

Eles também incluem entre suas motivações que uma maior previsibilidade permite diminuir consideravelmente o tempo de projeto, face à não necessidade de refazer parte (ou todo) o trabalho por não se alcançar os resultados devido à dificuldade de se alcançar os valores de desempenho propostos em projetos *standard cells*.

O River-PLA consiste em uma matriz de portas AND associada com portas OR de forma a mapear quaisquer soma-de-produtos da lógica booleana. Além disso, essa estrutura é 'empilhada' de forma que as saídas de um bloco podem ser utilizadas pelos blocos seguintes.

Uma vantagem dessa metodologia é a alta precisão das estimativas de área e atraso. Além disso, o tempo de síntese é muito menor que utilizando *Standard Cells* e elimina as etapas de posicionamento, roteamento e mapeamento tecnológico. Quando comparados resultados de síntese de circuitos com 300 a 17k *portas*, num total de 16 circuitos, na tecnologia 0.35um, os resultados apresentados mostram que apesar das perdas em área, os tempos de atraso são compatíveis nas duas metodologias.

Cabe citar ainda o trabalho desenvolvido por Khatri et al. (1999). Nele se descreve uma metodologia de projeto imune a ruídos, ou seja, onde a influência entre interconexões vizinhas é inexpressiva e o atraso de uma conexão deve-se exclusivamente a sua capacitância intrínseca e sua resistência.

Para obter esse resultado, Khatri et al. (1999) utilizam em todos os níveis de metal a intercalação de uma linha de alimentação com uma de roteamento, ou seja, num nível há trilhas de roteamento intercaladas com VDD e no nível imediatamente superior ou inferior, há trilhas de roteamento intercaladas com GND. Assim, com a redução de influência da interconexão vizinha obtém-se com grande precisão, a capacitância de cada interconexão.

Entre as vantagens apresentadas por essa metodologia também estão a redução das resistências associadas à alimentação porque elas estão distribuídas por todo o circuito; maior previsibilidade do valor da indutância associada a cada interconexão; eliminação do *cross-talk* entre interconexões vizinhas; diminuição da complexidade dos extratores pela inexistência das influências acima citadas; maior precisão na estimativa do atraso do circuito; e não ser necessárias grandes adaptações no roteador, bastando modificar o espaçamento entre os metais.

Nos resultados dos testes apresentados ocorre perda em área em torno de 65%, o que é altamente comparável com o acréscimo da relação W/L proposto por Sylvester; Keutzer (1999) para minimizar os efeitos de *cross-talk* entre as interconexões, conforme indicação dos próprios autores.

#### 2.1 O impacto das interconexões nas tecnologias submicrônicas.

Como mencionado nas pesquisas acima, as interconexões exercem grande influência na determinação da desempenho<sup>9</sup> e na produtividade<sup>10</sup> dos projetos submicrônicos. Por esse motivo, foi realizado um detalhamento maior desse item, a fim de descrever um pouco mais suas características principais, ou seja, sua capacitância, resistividade e indutância associadas, assim como as alternativas de projeto que estão sendo adotadas para diminuir sua influência.

A figura 2.5 apresenta uma estimativa do ITRS 2001 para os atrasos decorrentes das interconexões. Conforme pode ser observado na Figura 2.5, nas conexões locais, a influência das interconexões do atraso é compatível com os avanços do atraso do canal do transistor, entretanto, as conexões globais apresentam sérias restrições que são contornadas através de várias medidas como adoção de linhas de metal com largura maior que o mínimo admitido pela tecnologia, a inserção de repetidores, a identificação de zonas isocrônicas e a utilização de interconexões óticas ou por rádio-freqüência (ITRS, 2001).

<sup>&</sup>lt;sup>9</sup> Na tecnologia 25nm, as interconexões globais respondem por mais de 40% do atraso nos piores casos, conforme Kahng;Mantik;Markov (2001).

<sup>&</sup>lt;sup>10</sup> A existência de poeiras durante o processo de fabricação pode ocasionar a formação de curtos circuitos ou de linhas abertas que levam ao não funcionamento do circuito. Além disso, vias mal formadas podem aumentar em demasia a resistência da interconexão, levando à degradação do desempenho. Esses são exemplos de dois fatores que influenciam o rendimento do processo de fabricação de circuitos integrados.

Figura 2.5 – Atraso das interconexões segundo o processo tecnológico (ITRS 2001).

Conforme citado acima, uma possibilidade amplamente utilizada, é a adoção de conexões com maior largura (W) nas camadas superiores a fim de diminuir a resistência das mesmas. Entretanto, ocorre aumento da capacitância entre camadas justapostas, de modo que deve existir uma solução de compromisso no dimensionamento dessa interconexão.

Além disso, várias camadas para roteamento (entre 7 e 8) estão sendo disponibilizadas para permitir a realização das conexões entre os milhões de transistores que podem ser incluídos em um ASIC. A figura 2.6 apresenta uma visão em corte da distribuição das conexões.

Figura 2.6 – Visão em corte da distribuição das interconexões (ITRS, 2001).

Apesar de todas essas medidas que visam reduzir o impacto no desempenho provocado pelas interconexões, ainda existem outros problemas que estão ligados às estimativas de atraso calculadas por ferramentas de CAD. Primeiramente, a qualidade dessas estimativas é bastante variável, pois o comprimento da interconexão não é o único fator a ser considerado, visto que as interconexões vizinhas também influenciam no cálculo do seu atraso, assim como o tipo de sinal que ela carrega e a sensibilidade às variações dos sinais de seus vizinhos.

Em especial, o Efeito de Acoplamento Miller – que ocorre quando ambos terminais de um capacitor são chaveados simultaneamente em direções opostas – provoca alterações nos valores dessas estimativas. Esse fator se agrava por causa da diminuição da tensão de alimentação dos circuitos integrados para acompanhar a redução da escala da tecnologia.

Além dele, o ruído causado pelas variações de tensão das interconexões vizinhas está causando o aumento do impacto do *cross-talk*. Ressalta-se que essa influência devida ao ruído, só pode ser mensurada por ocasião dos testes.

Os efeitos acima são proporcionais à capacitância entre interconexões vizinhas e depende das dimensões do condutor. Com a redução da escala tecnológica, a largura (W) do condutor está diminuindo e, para impedir que a resistência deles cresça quadraticamente, a altura (T) está sendo mantida constante. Observe as equações de cálculo da resistência e das capacitâncias entre camadas diferentes( $C_f$ ), entre interconexões na mesma camada ( $C_P$ ), conforme a representação gráfica constante da Figura 2.6.

$R = \rho.L \ / \ T \ . \ W \qquad \qquad C_f = K \ . \ \epsilon_o \ . \ W \ . \ L/H \qquad \qquad C_P = K \ . \ \epsilon_o \ . \ T \ . \ L \ / D$

Onde: p é resistividade do material;

L é o comprimento da interconexão

T é a altura da interconexão

W é a largura da interconexão

D é a distância entre interconexões

K é constante dielétrica do material

H é a altura relativa ao plano

$\varepsilon_0$  é a constante de permissividade do espaço livre

Figura 2.7 – Dimensões das interconexões.

Assim, a forma como está sendo realizada a redução de escala da tecnologia, de modo a evitar o aumento quadrático da resistência, está aumentando a capacitância entre duas conexões vizinhas. E como o atraso da interconexão é calculado através do produto da resistência pela capacitância, está se tornando difícil identificar qual a melhor relação de compromisso entre estes dois fatores.

Outros problemas decorrentes da redução da escala tecnológica, se devem ao aumento das influências recíprocas entre os transistores e o substrato. Elas aparecem em

virtude da diminuição das camadas de isolamento entre as diversas camadas de metal e pelo aumento das freqüências utilizadas (MEIJS; SMEDES, 1996). Não bastasse essa influência, o aumento do tamanho do circuito integrado agravou ainda mais essa questão. A indutância das interconexões, cujos principais efeitos adversos são a reflexão do sinal e aumento do ruído, também está começando a se fazer presentes e as estimativas de suas influências também passam a ser importantes.

Todas essas características das interconexões nas tecnologias submicrônicas, juntamente com a redução progressiva de escala das tecnologias, com o aumento do número de etapas do processo de fabricação e com as variabilidades randômicas e sistêmicas do processo, têm causado um incremento considerável na complexidade da síntese física. Além disso, modificações necessárias para ajustar o desempenho, a área ou a potência dissipada pelo projeto podem causar problemas que acarretem a total redefinição do mesmo ou serem difíceis de atingir pela inexistência de ferramentas ainda não capacitadas a tratar esse nível de complexidade.

### 2.2 A Utilização de circuitos regulares

A complexidade do processo de síntese física, assim como as variabilidades randômicas e sistemáticas do processo de fabricação estão provocando a busca de alternativas que permitam diminuir os custos decorrentes do maior tempo de projeto e do menor número de circuitos em bom estado de funcionamento ao final do processo.

Assim, os trabalhos de Khatri et al. (1999), Pileggi et al (2003) e Mo; Brayton (2002) utilizam circuitos regulares como opção ao projeto *standard cells* a fim de obter maior rendimento no processo de fabricação, diminuir a influência no desempenho das capacitâncias das interconexões e um menor tempo de projeto, porém, em contrapartida, obtêm circuito. S com maior área e desempenho um pouco menor.

Veja-se o caso do VPGA – *ViaPatterned Gate Array* – que consiste em blocos lógicos de um FPGA personalizável quanto ao roteamento. Com a estrutura regular do VPGA é possível a obtenção de uma maior taxa de aproveitabilidade dos circuitos com a utilização de técnicas que tornam a célula do VPGA mais estável às variações de processo.

Observe-se que não basta somente utilizar corretamente as regras para geração de máscaras da tecnologia para se obter um resultado exeqüível, é necessário estimar quais as configurações mais suscetíveis às variabilidades no processo e suas conseqüências no leiaute, para se obter circuitos em bom estado de funcionamento. O mapeamento desses problemas passa a ser importante para o projetista, que precisa levá-los em consideração nas suas decisões.

Assim, a impossibilidade do processo de litografia tratar corretamente os diversos problemas existentes por causa das flutuações atômicas ou pela própria natureza física dos materiais que estão chegando ao seu limite, está contribuindo para que se busquem alternativas que possam diminuir os impactos dos custos na produção dos circuitos integrados.

Por outro lado, a utilização de máscaras padronizadas contribui para melhor enquadramento das mesmas durante o processo de litografia e para a diminuição do seu custo associado, por repetirem o mesmo padrão.

Os fatos acima descritos mostram que na evolução tecnológica dos circuitos integrados existe uma distância entre o que se tem a capacidade de produzir e o que se pode produzir, ou seja, existem recursos tecnológicos 'ociosos' por falta de capacidade de utilizá-los proficuamente. Pileggi et al. (2003), se refere a essa distância como

"Déficit de Produtividade de Projeto"> Afirma ainda que essa barreira é decorrente da incapacidade humana em acompanhar os rápidos passo da tecnologia e tratar os complexos problemas dela decorrentes (complexidade do problema cresce exponencialmente, detalhes de implementação física, falhas paramétricas, ruído, atraso) de forma eficaz e eficiente.

A regularidade no projeto de circuitos integrados surge então, como uma opção que ao restringir as opções do projetista por um lado, permite-lhe obter melhores estimativas de desempenho, menor tempo de projeto e maior rendimento.

Um aspecto interessante é que apesar dos circuitos regulares, provavelmente, utilizarem maior área para produzir um mesmo circuito, pode-se obter maior número de circuitos aproveitáveis por *wafer*, face ao melhor rendimento e conformidade com as restrições de tempo e potência necessários, quando comparado com um circuito que utilizando uma metodologia *Standard Cells*, mesmo tendo maior número de unidade por *wafer* apresente uma menor taxa de produtividade e menor previsibilidade do cálculo do atraso. Ou seja, o aumento dos custos de produção pode não compensar a utilização desta metodologia.

Por outro lado, a redução do impacto no desempenho causado pelas interconexões na metodologia *standard cells* em virtude da redução de escala da tecnologia, exige a utilização de maior relação W/L, assim como maior número de iterações entre as etapas de síntese para que o projeto satisfaça os critérios de desempenho. Como ocorre aumento na área, há uma certa compensação na utilização de leiautes regulares.

Outro ponto a se considerar diz respeito a melhor previsibilidade e facilidade de cálculo do atraso das interconexões nos circuitos regulares, pois as células estão previamente caracterizadas e a paisagem do leiaute regular é repetitiva e conseqüentemente pode-se obter melhores estimativas da influência das interconexões no atraso.

Essas considerações iniciais suscitam a importância da pesquisa de opções de projeto que possam conduzir a geração de circuitos integrados regulares, que possuam maior aproveitabilidade e rendimento.

Assim, a opção de explorar esse espaço na geração de leiaute de circuitos integrados, permite obter novas informações que podem contribuir com soluções para os atuais problemas enfrentados na síntese de circuitos integrados usando tecnologias submicrônicas.

# 3 O GERADOR DE LEIAUTE DE MATRIZES REGULARES - MARTELO

Para o desenvolvimento dessa pesquisa, inicialmente foi identificado o tipo de matriz regular que seria elaborado. Foi analisado então, qual tipo de célula seria mais adequado para sintetizar circuitos em tecnologia CMOS.

Como a lógica booleana trabalha com soma-de-produtos ou produto-de-somas, procurou-se identificar uma célula que oportunizasse mapear essa solução. Observando-se ainda, que na tecnologia CMOS é melhor em termos de área e desempenho, implementar uma porta com saída negada, recaiu-se entre as opções de utilizar uma célula NAND ou uma NOR, como forma de diminuir o número de transistores por unidade lógica da matriz e também por ser mais fácil implementar uma função booleana através dessas portas lógicas.

Essas células possuem as seguintes características:

- facilidade de implementar um inversor nos dois tipos de célula, sendo apenas necessário conectar uma das entradas em VDD para a NAND ou GND para a NOR;

- ➤ a soma-de-produtos é implementada diretamente através de células NANDs e o produto-de-somas em células NOR, de acordo com as propriedades da lógica booleana.

Entretanto, em tecnologia CMOS é preferível implementar a célula NAND a célula NOR pelo seguinte motivo:

➤ A NAND, possui os transistores PMOS em paralelo, o que diminui o tempo de transição *low-high*, quando comparado à célula NOR, visto que esses transistores têm maior dificuldade de chavear por causa de suas características elétricas;

Outro fator que também exerceu influência na escolha é a existência de uma ferramenta de síntese lógica (TAVARES, 2003) que realiza o mapeamento de qualquer função booleana através de células NAND e inversores. Essa ferramenta permite regular o *fanout* máximo do circuito, de forma que é possível controlar a quantidade de lógica gerada, dimensionando-a de acordo com o resultado desejado.

Além de gerar lógica dedicada a matriz de NANDs, outras características também são exploradas por essa ferramenta:

- ➢ ela busca explorar a possibilidade da formação de conexões curtas através da regulagem do fanout, embora isso implique em duplicação da lógica;

- ➤ a forma como a lógica foi gerada permite ao posicionador distribuir as células sem a existência de conexões que ficam percorrendo o circuito de um lado a outro.

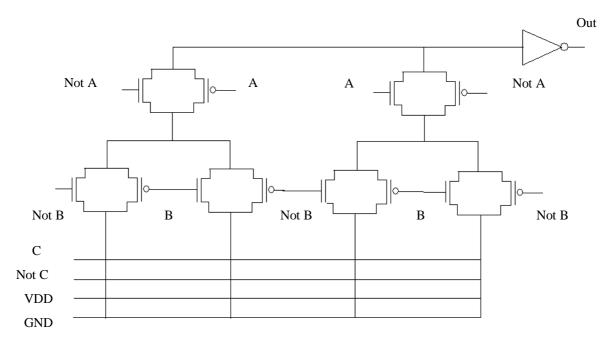

#### 3.1 Fluxo de síntese utilizado

A Figura 3.1 explicita o fluxo de síntese utilizado para a geração de leiautes através de matrizes de NANDs. Basicamente, o processo de geração do leiaute consiste em três etapas distintas. Durante a primeira é realizado o mapeamento do circuito para a lógica negativa através da ferramenta de síntese lógica. Essa etapa permite que o usuário informe qual o *fanout* máximo que o circuito pode ter e ao final da mesma obtém-se um circuito no formato ".sim", que consiste numa listagem das células, suas conexões e a identificação das entradas e saídas do circuito.

A opção de definição do *fanout* máximo é importante para a caracterização do circuito, pois permite regular a largura adequada da difusão dos transistores da matriz, baseando-se na estimativa da capacitância máxima que a saída de uma célula irá suportar. Essa informação precisa ser somada à capacitância das interconexões, mas a realização de testes comparativos pode identificar a relação de compromisso entre o *fanout* máximo admitido, a largura da difusão dos transistores e o número de transistores do circuito.

Além disso, a formação de conexões curtas também é um dos objetivos almejados e ao se reduzir o *fanout* máximo, obtêm-se resultados interessantes para esse item que também contribui para reduzir o atraso geral do circuito.

O próximo passo consiste em realizar o posicionamento das células a fim de obterse a ordenação relativa das células para posterior geração do leiaute. Essa tarefa é efetuada pelo posicionador MANGOPARROT (HENTSCHKE, 2002) que possui uma configuração específica para efetuar o posicionamento das células da matriz.

Como as células possuem o mesmo tamanho, a qualidade do posicionamento obtido exerce influência significativa para o sucesso do roteamento do circuito conforme será visto mais adiante. Além disso, o posicionador realiza, se necessário, a inserção de células de interconexão<sup>11</sup> para diminuir o congestionamento e assim facilitar a tarefa do roteador.

Por fim, o posicionador procura manter NANDs que compartilham entradas e/ou saídas num mesmo par na matriz em virtude das estratégias de roteamento que foram utilizadas e que serão objeto de detalhamento na próxima seção.

Como saída, o posicionador gera um arquivo no formato ".mpp" com a descrição do número de bandas e a seqüência das células dentro das bandas. O usuário pode ainda especificar a quantidade de bandas e de células por banda ou permitir que o programa efetue o dimensionamento da matriz de forma a torná-la o mais quadrada possível.

A terceira etapa consiste na geração do leiaute propriamente dito. Com base nas informações do arquivo gerado pela síntese lógica e do arquivo gerado pelo posicionador, a ferramenta denominada MARTELO gera o leiaute do circuito integrado.

Ainda nessa etapa, são repassados ao programa, informações sobre a largura das difusões e opções para o roteamento. Este por sua vez é realizado com a ferramenta desenvolvida por Hentschke et al (2003) que realiza iterações conjuntamente com a ferramenta MARTELO até que seja finalizado o roteamento ou seja atingido o número máximo de iterações informadas pelo usuário. Menciona-se ainda que o roteamento é totalmente realizado por sobre as células, não existindo espaçamento interbandas.

O formato da saída do MARTELO é um arquivo .cif descrevendo o leiaute gerado.

<sup>&</sup>lt;sup>11</sup> São espaços com as dimensões de uma NAND que são inseridos em posições específicas para facilitar a tarefa do roteador.

## 3.2 Descrição da ferramenta de geração de leiaute MARTELO

A estrutura da matriz gerada pela ferramenta deve permitir que a mesma se disponha em bandas justapostas de modo a ocupar a menor área possível. Para identificar um modelo compatível com as características desejadas, realizou-se um estudo entre dois modelos de leiaute onde foram realizadas simulações elétricas para identificação do desempenho e área. Esses modelos podem ser observados no Anexo I.

Figura 3.1 – Fluxo de síntese para a geração do leiaute através de matrizes de células NANDs.

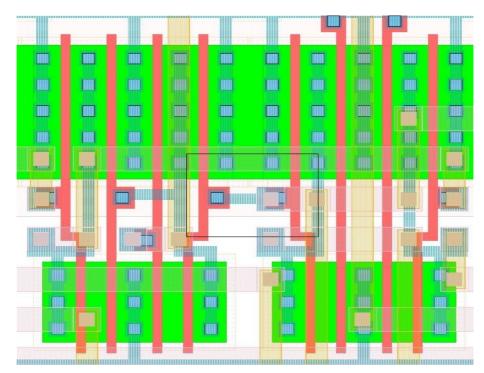

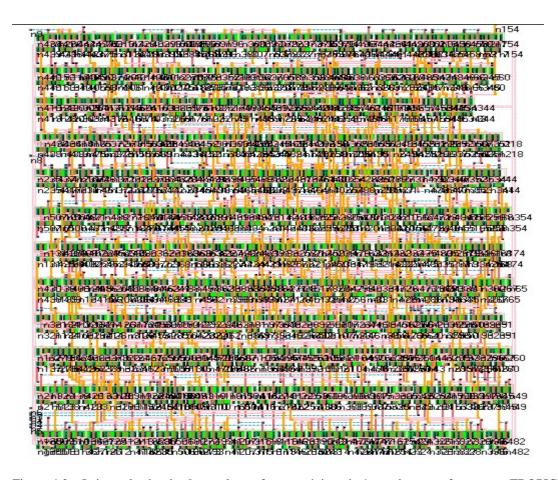

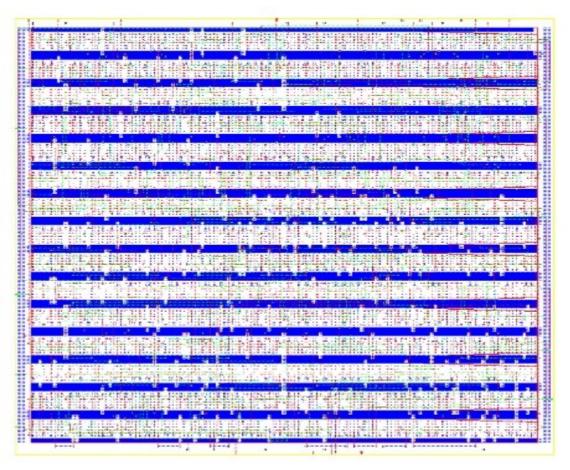

No estudo precedente, chegou-se ao modelo constante da Figuras 3.2 e 3.3 que foi implementado nas regras da AMS  $0.35\mu m$ . A Figura 3.2 representa um par de NANDs

que podem ser espelhadas em todos os sentidos. Na Figura 3.3 é representada a matriz de uma forma mais ampla, possibilitando a análise do arranjo global das células.

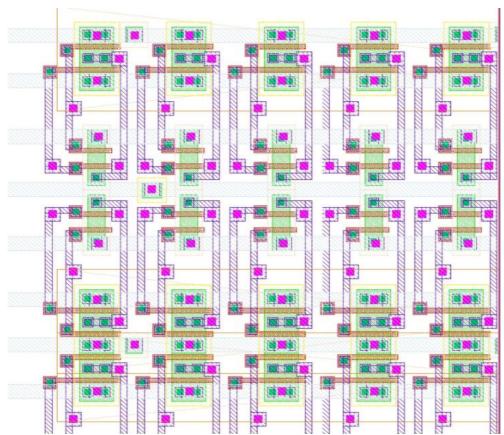

Na Figura 3.2 é apresentado o leiaute de um par de NANDs que será a célula básica de formação da matriz. Porém, quando uma banda possuir número ímpar de transistores, a última NAND estará sem o par. Observa-se ainda, que as NANDs que compõem o mesmo par possuem as mesmas dimensões, implicando em características elétricas semelhantes.

Para a geração de inversores existem duas opções: a primeira consiste em estabelecer uma linha de *poly* que conecte as duas entradas da NAND; a segunda consiste em conectar a entrada que fica mais ao centro da célula à VDD.

A opção utilizada na implementação da matriz foi a segunda porque ela diminui o tempo de transição *High-Low* visto que as capacitâncias do transistor próximo ao GND já estão descarregadas. Além disso, como apenas o *gate* de um transistor necessita ser descarregado, é menor o *fanout* da célula que antecede o inversor deve descarregar, permitindo um chaveamento mais rápido.

Figura 3.2 – Leiaute de um par de NANDs utilizado como template para a geração da matriz.

Para possibilitar a justaposição dos pares de NANDs conforme a Figura 3.3, foram colocados dois contatos com VDD entre os transistores PMOS (região demarcada por retângulo na Figura 3.3). Isso diminui a área de dreno do transistor assim como as capacitâncias parasitas, influenciando o desempenho elétrico do dispositivo.

O gerador de leiaute de matrizes MARTELO utiliza um template das células básicas para a tecnologia AMS 0,35  $\mu$ m, porém podem ser criados templates para outras tecnologias.

A célula básica utilizada como *template* para a tecnologia AMS 0,35 μm permite ao usuário configurar a largura (W) dos transistores PMOS e NMOS. Para esse *template*

existe entretanto, uma largura mínima de 2,0μm para o transistor PMOS e 1,0μm para o transistor NMOS, sendo estes os mínimos valores admitidos para as dimensões dos transistores.

A disposição dos contatos das entradas e saídas no centro da célula permitiu diminuir a altura geral da célula, pois a colocação de contatos externos à banda prejudicaria a justaposição das mesmas e, além disso, existe uma distância mínima entre as difusões P e N que impede uma aproximação que compense a colocação dos contatos externamente à célula. Porém, a concentração das entradas e saídas das células numa estreita faixa pode dificultar o roteamento.

Figura 3.3 – Leiaute de uma matriz 3 x 10 de NANDs gerada pelo MARTELO.

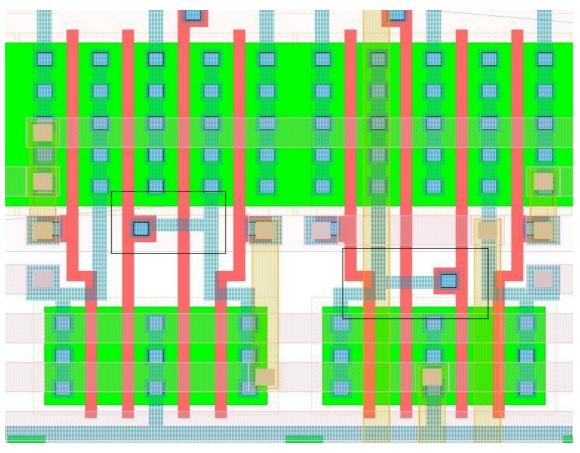

Em virtude da limitação acima, foram implementadas estratégias que buscam diminuir o impacto da concentração dos contatos em estreitas faixas do circuito. A primeira delas consiste na realização de conexões em metal1 para casos específicos conforme abaixo detalhado.

Primeiramente, pode ocorrer da saída de uma NAND ser conectada à entrada da outra NAND do mesmo par. Essa situação é indicada na Figura 3.4 através das áreas selecionadas. A inclusão de conexões em metal1 permite a eliminação de uma ou duas vias para as camadas de metal superiores e desta forma diminui o trabalho do roteador, pois esses pontos do circuito já estarão conectados, além de liberar mais espaço para roteamento. Essa opção também reduz as capacitâncias parasitas associadas a essa interconexão, pois se a mesma tivesse que ser realizada em metal2 ou 3 teria maior comprimento e largura, estando também sujeita à influência das interconexões vizinhas.

Outra situação ocorre quando duas NANDs de pares distintos possuem a mesma entrada. Nesse caso, uma conexão em metal1 também pode ser estabelecida conforme ilustra a Figura 3.5. Esta conexão de metal possui comprimento variável pois depende do número de trilhas verticais inseridas.

Para dar a maior amplitude possível à utilização de conexões através de metal1, antes de fixar uma entrada da NAND, o programa verifica se a troca de posição das entradas (e não a troca de posição das NANDs) permite a realização da conexão com o metal1.

A adoção dessa estratégia permitiu nos vários circuitos analisados, uma redução de 7 a 16% das vias repassadas para as próximas camadas de roteamento, pois as conexões passaram a realizar-se em metal1, causando um impacto considerável na diminuição do congestionamento.

Figura 3.4 - Contatos em metal1 inseridos entre NANDs pertencentes ao mesmo par.

Observe a Tabela 3.1 com os resultados das conexões realizadas em metal1 e sua comparação com o total de conexões dos circuitos. O percentual representa o quanto o roteador terá de conexões a menos para realizar. Além disso, conforme já mencionado, o posicionador MANGOPARROT desenvolvido por Hentschke (2002), ao posicionar as células da matriz, procura formar pares entre NANDs que possuam entradas e saídas em comum para permitir a utilização dessa estratégia.

Além da possibilidade de realização de contatos em metal1, ainda foram utilizadas três estratégias para facilitar o roteamento:

- > a inserção de trilhas verticais;

- > a inserção de trilhas horizontais; e

- > a inserção de células de interconexão.

As trilhas verticais e horizontais possuem a largura necessária a passagem de uma coluna ou uma linha de metal utilizada para o roteamento e foram importantes para possibilitar o roteamento dos circuitos gerados, pois com a concentração dos contatos numa estreita faixa, ocorre rápido congestionamento desta faixa.

Figura 3.5 – Contato em metal1 inserido entre NANDs de pares distintos.

| Tabela 3.1 – Resultados das conexões realizadas em metal1 pelo MARTELO após posicionamento |

|--------------------------------------------------------------------------------------------|

| realizado com a ferramenta MANGOPARROT.                                                    |

| Circuitos | Fanout | N.º de  | N.º total de | N.º contatos conectados | Percentual |

|-----------|--------|---------|--------------|-------------------------|------------|

|           | máximo | células | contatos     | através de Metal1       |            |

| 7seg      | 1      | 160     | 391          | 63                      | 16,11      |

| 7seg      | 4      | 92      | 241          | 28                      | 11,62      |

| 9symml    | 1      | 784     | 1907         | 251                     | 13,16      |

| 9symml    | 4      | 501     | 1271         | 148                     | 11,64      |

| Alu2      | 1      | 1333    | 3235         | 385                     | 11,90      |

| Alu2      | 4      | 796     | 2018         | 207                     | 10,25      |

| Alu4      | 4      | 2797    | 7023         | 574                     | 8,17       |

| Frg1      | 1      | 870     | 2086         | 256                     | 12,27      |

| Frg1      | 4      | 285     | 718          | 106                     | 14,76      |

| Lal       | 1      | 515     | 1258         | 159                     | 12,64      |

| Lal       | 4      | 266     | 684          | 116                     | 16,95      |

| X1        | 1      | 2688    | 6465         | 573                     | 8,86       |

| X1        | 4      | 1014    | 2554         | 196                     | 7,67       |

Essa estratégia baseou-se na observação de que ao se abrir um espaço em toda uma coluna, ocorreria o deslocamento uma parte do circuito para a direita de uma forma conjunta, de modo que não ocorreriam prejuízos ao posicionamento relativo, visto que todas aquelas células após a coluna ou linha de inserção sofreriam igual deslocamento.

Para a inserção de trilhas horizontais e verticais, foi realizada uma análise dos nodos não roteados, identificando-se onde ocorreu o problema. Essa informação é fornecida pelo roteador que, não conseguindo terminar o roteamento, gera um arquivo de saída com essas informações. Essa tarefa evitou que houvesse a inserção de trilhas desnecessárias e somente no local onde há problema de roteamento é inserida uma trilha

horizontal ou vertical. Essa trilha, por sua vez estende-se por toda a altura ou largura da matriz.

Além disso, foi fixada uma prioridade: as trilhas verticais são preferenciais às horizontais, pois a NAND possui uma relação de aspecto aproximada de 1:4 quando comparada a largura com a altura (considerando-se o W do transistor PMOS igual a 5μm e do transistor NMOS igual a 3μm), logo há maior número de trilhas horizontais disponíveis. As Figuras 3.6 e 3.7 apresentam a ocorrência dessas situações.

Finalmente, cabe ao usuário personalizar o número máximo permitido de trilhas verticais e horizontais que o MARTELO pode inserir entre as colunas e/ou bandas.

Finalmente, o gerador de leiaute só insere uma trilha vertical por par de NANDs ou uma trilha horizontal por banda em cada iteração, pois pode ocorrer de uma única trilha resolver o problema em toda aquela coluna ou banda do leiaute. Também há a seguinte observação: antes de inserir trilhas horizontais, são inseridas trilhas verticais no ponto de localização do problema e entre os pares de NANDs imediatamente antes e depois do problema.

Essa estratégia revelou-se eficiente pois o roteador com esse espaço extra nas imediações, encontrou melhores opções para realizar as conexões entre as células. Finalmente, quando não se obtém sucesso após a inserção de trilhas verticais, é inserida uma ou mais trilhas horizontais, segundo os mesmos critérios para inserção de trilhas verticais, ou seja, uma trilha entre bandas por vez, de acordo com a localização do problema.

Como pode ser observado, enquanto o roteamento não é finalizado, o MARTELO efetua iterações conjuntamente com o roteador para completar o leiaute do circuito. A cada iteração, o roteador identifica os nodos que não foram completamente roteados. Estes pontos, por sua vez, são repassados ao MARTELO para que na próxima iteração seja inserida uma trilha de acordo com a localização do problema. Novamente o roteador é acionado e o programa fica realizando iterações até finalizar o roteamento ou pela quantidade de vezes que o usuário definir.

A Tabela 3.2, apresenta os resultados obtidos na geração do leiaute de vários circuitos. A inserção de trilhas horizontais e/ou verticais só é efetuada se o roteamento não conseguir rotear todos os pontos na primeira iteração e, conforme já mencionado, sua função é diminuir o congestionamento para facilitar o trabalho do roteador. Observa-se também que à medida que o número de camadas de metal aumenta, o roteador consegue realizar a tarefa com menos iterações e conseqüentemente o leiaute fica mais compacto.

Verifica-se pelos dados da Tabela 3.2 que havendo disponibilidade de quatro camadas de roteamento, todos os circuitos precisaram de apenas uma iteração para rotear completamente. Quanto aos demais, apenas o Alu4 com fanout 1 e o X1 com fanout 2 não conseguiram rotear com duas trilhas de metal, mesmo aumentando-se o número de iterações.

Finalmente, tem-se a inserção de células de interconexão. Destaca-se que a largura de uma célula de interconexão é aproximadamente a de duas trilhas verticais, com a vantagem de ser colocada apenas na banda e na posição onde houve o problema de roteamento.

Estas são inseridas de duas formas: a primeira e principal é efetuada pelo programa MANGOPARROT (Hentschke, 2002) – que realiza a posicionamento das células de forma a obter uma estrutura com menor comprimento médio das conexões e de forma a reduzir o congestionamento; a segunda pelo gerador de leiaute MARTELO através de dois métodos:

- insere células de interconexão como substituição às trilhas verticais e horizontais;

- insere células de interconexão 'estratégicas' após a primeira iteração com o objetivo de realizar mais conexões em metal1, para depois continuar inserindo trilhas verticais e horizontais.

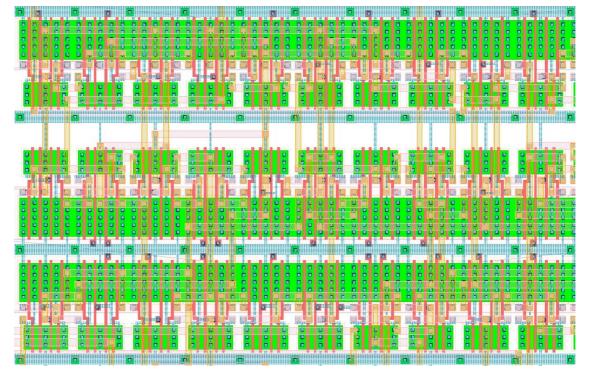

Figura 3.6 – Inserção de trilha vertical pelo MARTELO.

Figura 3.7 – Inserção de trilha horizontal pelo MARTELO.

Tabela 3.2 – Resultados da geração de leiaute de circuitos integrados com o MARTELO, segundo o número de camadas de metal disponíveis para roteamento, trilhas verticais e horizontais inseridas.

| Circuitos   | Fanout | N.º de  | Camadas  |    | rilhas verticais e <b>Trilhas</b> | N.º | Completou  |

|-------------|--------|---------|----------|----|-----------------------------------|-----|------------|

| Circuitos   | ranout | células | de metal |    | Horizontais                       |     |            |

|             |        | Cciuias | 2        | 0  | 0                                 | 1   | Sim        |

| 7seg        | 1      | 160     | 3        | 0  | 0                                 | 1   | Sim        |

| 7505        | 1      | 100     | 4        | 0  | 0                                 | 1   | Sim        |

|             |        |         | 2        | 0  | 0                                 | 1   | Sim        |

| 7seg        | 4      | 92      | 3        | 0  | 0                                 | 1   | Sim        |

| rseg        | -      | 92      | 4        | 0  | 0                                 | 1   | Sim        |

|             |        |         | 2        | 6  | 0                                 | 5   | Sim        |

| 9symml      | 1      | 784     | 3        | 0  | 0                                 | 1   | Sim        |

| ) Syllilli  | 1      | 704     | 4        | 0  | 0                                 | 1   | Sim        |

|             |        |         | 2        | 12 | 0                                 | 4   | Sim        |

| 9symml      | 4      | 501     | 3        | 0  | 0                                 | 1   | Sim        |

| Jsymmi      | _      | 301     | 4        | 0  | 0                                 | 1   | Sim        |

|             |        |         | 2        | 8  | 0                                 | 5   | Não        |

| Alu2        | 1      | 1333    | 3        | 0  | 0                                 | 1   | Sim        |

| AluZ        | 1      | 1333    | 4        | 0  | 0                                 | 1   | Sim        |

|             |        |         | 2        | 28 | 0                                 | 5   | Sim        |

| Alu2        | 4      | 796     | 3        | 6  | 0                                 | 4   | Sim        |

| AluZ        | 4      | 790     | 4        | 0  | 0                                 | 1   | Sim        |

|             |        |         | 2        | 9  | 0                                 | 5   | Não        |

| Era 1       | 1      | 870     | 3        | 0  | 0                                 | 1   | Sim        |

| Frg1        | 1      | 870     | 4        | 0  | 0                                 | 1   | Sim        |

| -           |        |         | 2        | 3  | 0                                 | 3   | Sim        |