# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### **EDUARDO CHIELLE**

CFT-tool: Ferramenta Configurável para Aplicação de Técnicas de Detecção de Falhas em Processadores por Software

> Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Prof. Dr. Fernanda Lima Kastensmidt Orientadora

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

#### Chielle, Eduardo

CFT-tool: Ferramenta Configurável para Aplicação de Técnicas de Detecção de Falhas em Processadores por *Software /* Eduardo Chielle. – Porto Alegre: Programa de Pós-Graduação em Computação, 2012.

104 f.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2012. Orientadora: Fernanda Lima Kastensmidt.

1. Técnicas de detecção em *software*. 2. Processadores. 3. Injeção de Falhas. I. Kastensmidt, Fernanda G. L.. II. CFT-tool: Ferramenta Configurável para Aplicação de Técnicas de Detecção de Falhas em Processadores por *Software*.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb

Coordenador do PPGC: Prof. Álvaro Freitas Moreira

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **AGRADECIMENTOS**

Quero agradecer aos meus pais, Márcia e Roque, e irmãos, Daniel, Douglas e Gustavo, que apesar de estarem longe, sempre se fizeram presentes.

Agradeço também ao pessoal do laboratório e demais laboratórios da redondeza, Anelise, Ângelo, Carol, Duda, Felipe (Tonin), Jimmy, Jorge, José Eduardo, José Rodrigo, Lucas Rosa, Lucas Tambara, Maurício, Paulo, Raul Barth, Raul Chipana, Samuel e William por terem contribuído, ou não, para o bom andamento do mestrado.

Ao pessoal oriundo da EC11 André Zangado e Rodrigo Stilera e aos adjacentes Bruno Piteco e Tiago Pinta, pelo apoio tático e momentos de descontração. Aos irmãos ninjas alemães, Adriana e Angel Tateishi, pelo tererê nosso de cada dia. E, também, aos amigos Cleber, Cicero, Giane e Lê.

Não posso esquecer a professora Fernanda, que me deu a oportunidade e a orientação necessária para a concretização deste trabalho.

Por fim, agradeço aos demais amigos de Porto Alegre, Foz do Iguaçu e outras andanças por onde passei.

# **SUMÁRIO**

| LISTA DE                         | ABREVIATURAS E SIGLAS                                                                      | 7                    |

|----------------------------------|--------------------------------------------------------------------------------------------|----------------------|

| LISTA DE                         | FIGURAS                                                                                    | 8                    |

| LISTA DE                         | TABELAS                                                                                    | . 10                 |

| RESUMO                           |                                                                                            | . 11                 |

| ABSTRAC                          | T                                                                                          | . 12                 |

| 1 INTRO                          | DUÇÃO                                                                                      | . 13                 |

| 2 CONC                           | EITOS DE DETECÇÃO DE ERROS EM SOFTWARE                                                     | . 17                 |

| 2.1.1<br>2.1.2                   | Cas de Detecção de Erros em Software                                                       | 17<br>18             |

| 2.2.1<br>2.2.2                   | amas que Implementam Técnicas de Detecção em Software                                      | 22<br>22             |

|                                  | OOL: FERRAMENTA PARA APLICAÇÃO DE TÉCNICAS DE<br>EM SOFTWARE PARA DIFERENTES PROCESSADORES |                      |

| 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4 | lo de Configuração                                                                         | 26<br>27<br>29<br>29 |

| 3.2 Módu                         | lo de Verificação                                                                          | 33                   |

| 3.3.1                            | lo de Complementação                                                                       | 36                   |

| 3.4   | Módulo de Proteção a Falhas Transientes                                        | 39 |

|-------|--------------------------------------------------------------------------------|----|

| 3.5   | Técnicas de Detecção em Software Implementadas                                 | 40 |

| 3.5   | 5.1 Variáveis 1                                                                |    |

| 3.5   | 5.2 Variáveis 2                                                                | 41 |

| 3.5   | 5.3 Variáveis 3                                                                | 42 |

| 3.5   | 5.4 Branches                                                                   | 42 |

| 3.5   | 5.5 Assinaturas                                                                | 43 |

| 4     | RESULTADOS E VALIDAÇÃO                                                         | 45 |

| •     | -                                                                              |    |

| 4.1   | Processadores Utilizados                                                       |    |

|       | 1.1 miniMIPS                                                                   |    |

| 4.    | 1.2 LEON3                                                                      | 47 |

| 4.2   | Metodologia de Injeção de Falhas                                               | 51 |

| 4.3   | Metodologia de Classificação de Erros                                          | 53 |

|       |                                                                                |    |

| 4.4   | Validação                                                                      |    |

|       | 4.1 Programas selecionados para validação                                      |    |

|       | 4.2 Validação das aplicação das técnicas de detecção em software pela CFT-tool |    |

| 4.4   | 4.3 Validação da configurabilidade da ferramenta                               | 67 |

| 5     | AVALIAÇÃO DO USO SELETIVO DOS REGISTRADORES                                    | 74 |

|       | •                                                                              |    |

| 5.1   | Métodos                                                                        |    |

|       | 1.1 Método Static First (SF)                                                   |    |

|       | 1.2 Método Static Target (ST)                                                  |    |

|       | 1.3 Método Static Source (SS)                                                  |    |

|       | 1.4 Método Static Source and Target (SST)                                      |    |

|       | 1.5 Método Dynamic Target (DT)                                                 |    |

|       | 1.6 Método Dynamic Source (DS)                                                 |    |

| 5.    | 1.7 Método Dynamic Source and Target (DST)                                     | 75 |

| 5.2   | Uso dos Registradores                                                          | 76 |

| 5.3   | Tempo de Execução e Ocupação de Memória                                        | 78 |

|       |                                                                                |    |

| 5.4   | Resultados de Injeção de Falhas                                                | 81 |

| 6     | CONCLUSÃO E TRABALHOS FUTUROS                                                  | 86 |

|       |                                                                                |    |

| REF   | FERÊNCIAS                                                                      | 88 |

| A NIE | EXO A - DETALHES TÉCNICOS DA IMPLEMENTAÇÃO                                     | 90 |

|       | lasse CFT                                                                      |    |

|       | asse AssemblyGenerator                                                         |    |

|       | asse CodeGenerator                                                             |    |

|       | asse Architecture                                                              |    |

|       | lasse ConfigParser                                                             |    |

|       | asse DB                                                                        |    |

|       | asse Loader                                                                    |    |

|       | lasse Techniques                                                               |    |

|       | asse ErrorManager                                                              |    |

| CI    |                                                                                |    |

|   | Classe Manager        | 93 |

|---|-----------------------|----|

|   | Classe ErrorTreatment |    |

|   | Classe BRA            | 94 |

|   | Classe SIG            |    |

|   | Classe VAR1           | 95 |

|   | Classe VAR2           | 95 |

|   | Classe VAR3           | 95 |

|   | Classe Global         | 96 |

|   | Classe Instruction    | 96 |

|   | Classe Register       | 96 |

|   | Classe Util           | 96 |

|   | Classe Checker        | 97 |

|   | Classe Format         | 97 |

|   |                       |    |

| A | NEXO B - ARTIGOS      | 98 |

|   |                       |    |

## LISTA DE ABREVIATURAS E SIGLAS

BID Basic Block Identifier

BRA Branches (Desvios Condicionais)

CCA Control Flow Checking using Assertions

CFCSS Control Flow Checking by Software Signatures

CFID Control Flow Identifier

CFT Configurable Fault Tolerant

CISC Complex Instruction Set Computer

DSP Digital Signal Processor

ECCA Enhanced Control Flow Checking using Assertions

EDAC Error Detection And Correction

EDDI Error Detection by Duplicated Instructions

HPCT Hardening Post Compiling Translator

LATW Latin American Test Workshop

PC Program Counter

RISC Reduced Instruction Set Computer

RTL Register Transfer Level

SEE Single Events Effects

SET Single Event Transient

SEU Single Event Upset

SIG Assinaturas

SPARC Scalable Processor Architecture

SWIFT Software Implemented Fault Tolerance

TEA2 TETRA Encryption Algorithm 2

VAR1 Variáveis 1 VAR2 Variáveis 2 VAR3 Variáveis 3

VHDL VHSIC Hardware Description Language

# LISTA DE FIGURAS

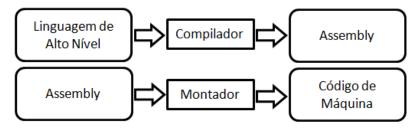

| Figura 1.1: Níveis de abstração e processos de transformação do programa                               | 15 |

|--------------------------------------------------------------------------------------------------------|----|

| Figura 2.1: Aplicação da técnica EDDI (REIS, 2005)                                                     |    |

| Figura 2.2: Exemplo da técnica CCA (ALKHALIFA, 1999).                                                  |    |

| Figura 3.1: Visão geral do funcionamento da CFT-tool                                                   |    |

| Figura 3.2: Processo de aplicação da proteção pela ferramenta CFT-tool                                 |    |

| Figura 3.3: Exemplo da configuração do formato do label                                                |    |

| Figura 3.4: Exemplo de instrução que deve ser declarada nas configurações gerais devido às suas        |    |

| funcionalidades.                                                                                       | 26 |

| ,<br>Figura 3.5: Configuração do branch delay slot para quando as instruções são reordenadas no código | 0  |

| assembly.                                                                                              |    |

| Figura 3.6: Configuração dos desvios condicionais logicamente inversos                                 |    |

| Figura 3.7: Exemplo de formato de instrução                                                            |    |

| Figura 3.8: Exemplo de grupo de instruções.                                                            |    |

| Figura 3.9: Exemplo de grupo de instruções com instruções sobrecarregadas                              |    |

| Figura 3.10: Exemplo de grupo de registradores.                                                        |    |

| Figura 3.11: Exemplo do formato de label no memory dump                                                |    |

| Figura 3.12: Exemplo do formato de instruções no memory dump                                           |    |

| Figura 3.13: Nome dos registradores no formato memory dump (à esquerda) e nome equivalente em          |    |

| assembly (à direita).                                                                                  | 30 |

| Figura 3.14: Nome das instruções no formato memory dump (à esquerda) e nome equivalente em             |    |

| assembly (à direita).                                                                                  | 31 |

| Figura 3.15: Configurações dos mnemônicos das instruções de salto incondicional para registrador,      |    |

| salto incondicional para endereço de memória e desvios condicionais                                    | 31 |

| Figura 3.16: Técnicas de detecção em software selecionadas                                             |    |

| Figura 3.17: Técnicas de detecção em software selecionadas                                             |    |

| Figura 3.18: Exemplo de configuração do modo de seleção de registradores                               |    |

| Figura 3.19: Tag de comentário configurada (acima) e linha de código com comentário (abaixo)           |    |

| Figura 3.20: Instrução analisada (à esquerda) e formato esperado para a instrução (à direita)          |    |

| Figura 3.21: Trecho de código no formato memory dump                                                   |    |

| Figura 3.22: Exemplo de chamada para sub-rotina.                                                       |    |

| Figura 3.23: Labels presentes no código assembly                                                       |    |

| Figura 3.24: Exemplo de sub-rotina não descrita no código pré ligação                                  |    |

| Figura 3.25: Sub-rotina extraída da descrição no formato memory dump (à esquerda) e código assen       |    |

| equivalente gerado pelo módulo de complementação (à direita)                                           |    |

| Figura 3.26: Visão geral do módulo de proteção a SEEs                                                  |    |

| Figura 3.27: Código original (à esquerda) e código com a técnica VAR1 (à direita)                      |    |

| Figura 3.28: Código original (à esquerda) e código com a técnica VAR2 (à direita)                      |    |

| Figura 3.29: À esquerda o código original e à direita o código com a técnica VAR3                      |    |

| Figura 3.30: À esquerda o código original e à direita o código com a técnica BRA                       |    |

| Figura 3.31: Código original (à esquerda) e código com a técnica BRA (à direita)                       |    |

| Figura 4.1: Comparação e desvio no processador miniMIPS.                                               |    |

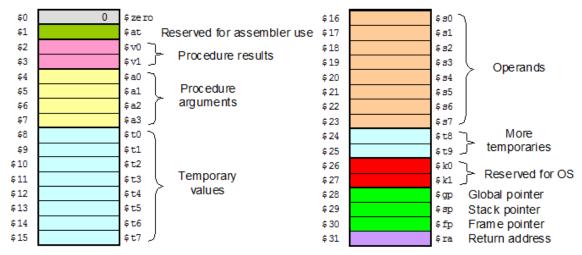

| Figura 4.2: Registradores do processador miniMIPS.                                                     |    |

| Figura 4.3: Transformações do programa para execução no processador miniMIPS                           |    |

| Figura 4.4: Instrução de comparação para o processador LEON3.                                          |    |

| Figura 4.5: Instrução de desvio condicional para o processador LEON3.                                  |    |

| Figura 4.6: Relação dos registradores do processador LEON3 (SPARC, 1991)                               |    |

| 5                                                                                                      |    |

| Figura 4.7: Janela de registradores do processador LEON3 (SPARC, 1991)                                                                    | 49              |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Figura 4.8: Fluxo de compilação para execução no processador LEON3                                                                        |                 |

| Figura 4.9: Formato SREC.                                                                                                                 | 51              |

| Figura 4.10: Inserção de falhas em nível lógico através do comando force                                                                  | 52              |

| Figura 4.11: Avaliação do valor do sinal pelo comando examine                                                                             | 52              |

| Figura 4.12: Atribuição do valor do sinal a uma variável                                                                                  | 52              |

| Figura 4.13: Visualização de parte do conteúdo da memória                                                                                 | 52              |

| Figura 4.14: Atribuição de parte do conteúdo da memória a uma variável                                                                    | 53              |

| Figura 4.15: PC da execução base, sem falhas (à esquerda) e PC da execução com erro                                                       |                 |

| nos dados (à direita)                                                                                                                     |                 |

| Figura 4.16: PC da execução base, sem falhas (à esquerda) e PC da execução com erro                                                       |                 |

| dados (à direita)                                                                                                                         | 55              |

| Figura 4.17: PC da execução base, sem falhas (à esquerda) e PC da execução com erro                                                       |                 |

| no controle (à direita)                                                                                                                   | 55              |

| Figura 4.18: PC da execução base, sem falhas (à esquerda) e PC da execução com erro                                                       | , detectado, no |

| controle (à direita)                                                                                                                      | 56              |

| Figura 4.19: Código, em C, do programa de multiplicação de matrizes                                                                       | 57              |

| Figura 4.20: Código, em C, do algoritmo de ordenação bubble sort                                                                          | 57              |

| Figura 4.21: Código, em C, do algoritmo encriptação                                                                                       |                 |

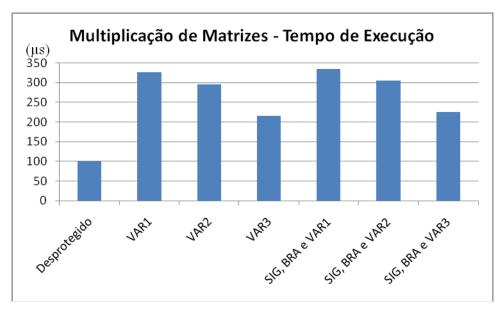

| Figura 4.22: Tempos de execução para a multiplicação de matrizes com diferentes técni                                                     |                 |

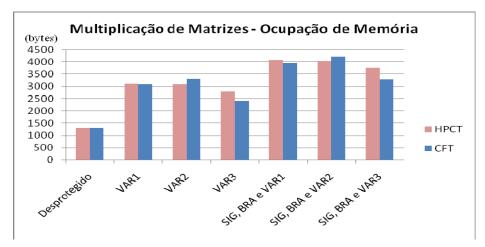

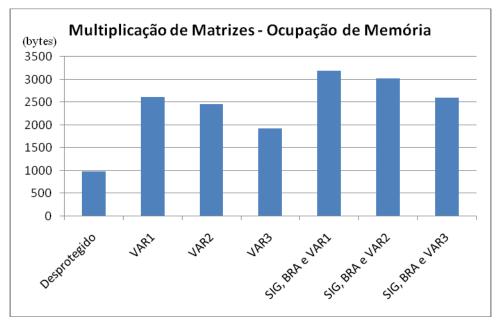

| Figura 4.23: Ocupação em memória da multiplicação de matrizes com diferentes técnic                                                       |                 |

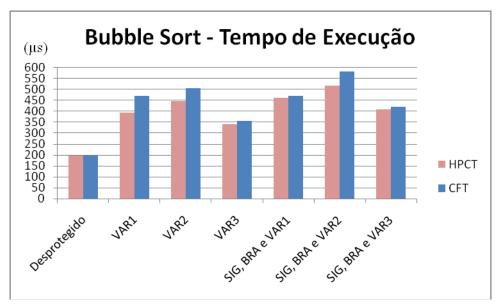

| Figura 4.24: Tempos de execução para o bubble sort com diferentes técnicas aplicadas.                                                     |                 |

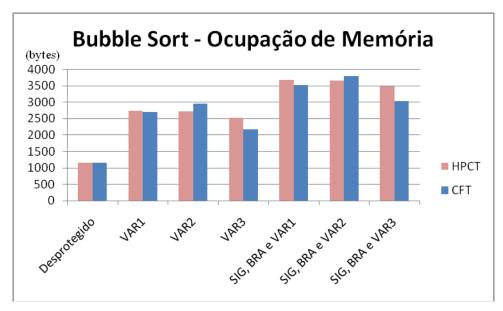

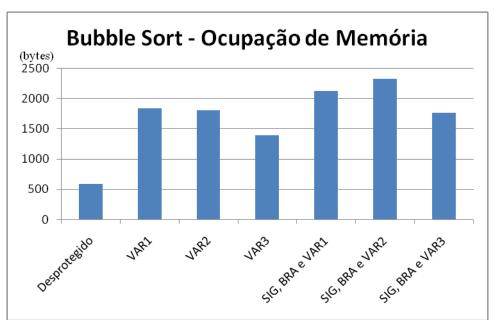

| Figura 4.25: Ocupação em memória do bubble sort com diferentes técnicas aplicadas                                                         |                 |

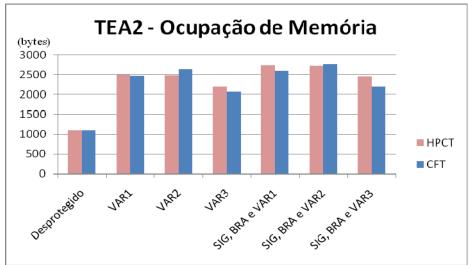

| Figura 4.26: Tempos de execução para o algoritmo de encriptação (TEA2) com diferent                                                       |                 |

| aplicadas.                                                                                                                                |                 |

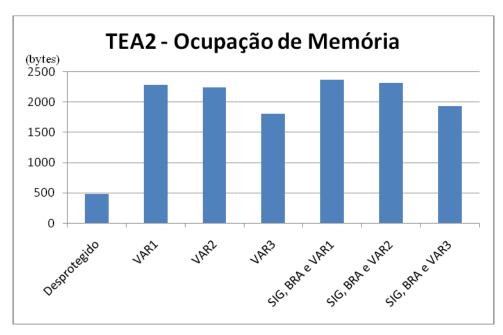

| Figura 4.27: Ocupação em memória do algoritmo de encriptação com diferentes técnico                                                       |                 |

| Figura 4.28: Proteção em código de máquina, à esquerda, e proteção em código assemi                                                       |                 |

| Figura 4.29: Tempos de execução para a multiplicação de matrizes rodando sobre o pro<br>LEON3                                             | ocessador       |

| Figura 4.30: Ocupação em memória da multiplicação de matrizes rodando sobre o proc                                                        |                 |

| - 1 on a new confusion control and manipulation are manipulated reduction of the                                                          |                 |

| Figura 4.31: Tempos de execução para o bubble sort (LEON3)                                                                                |                 |

| Figura 4.32: Ocupação em memória do bubble sort com diferentes técnicas aplicadas, 1                                                      |                 |

| processador LEON3.                                                                                                                        |                 |

| Figura 4.33: Tempos de execução para o algoritmo de encriptação (TEA2) com diferen                                                        |                 |

| aplicadas, rodando sobre o processador LEON3                                                                                              |                 |

| Figura 4.34: Ocupação em memória do algoritmo de encriptação com diferentes técnico                                                       |                 |

| rodando sobre o processador LEON3                                                                                                         |                 |

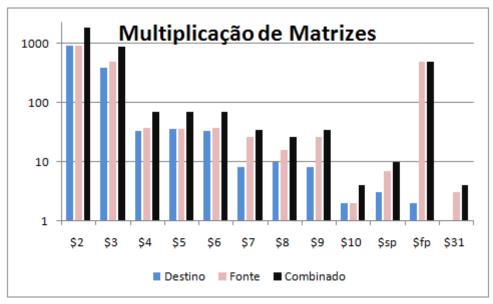

| Figura 5.1: Uso dos registradores para o bubble sort: destino (representa o contador de                                                   |                 |

| (representa o contador fonte) e combinado (representa o contador combinado)                                                               |                 |

| Figura 5.2: Uso dos registradores para a multiplicação de matrizes                                                                        |                 |

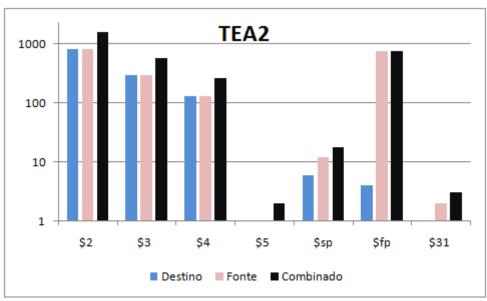

| Figura 5.2: Uso dos registradores para a munipheação de manizes<br>Figura 5.3: Uso dos registradores para o algoritmo de encriptação TEA2 |                 |

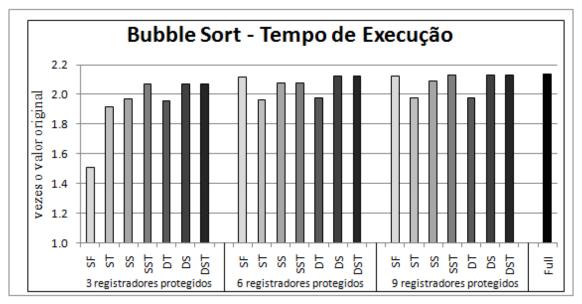

| Figura 5.5: Oso dos registradores para o aigorumo de encripiação TEA2<br>Figura 5.4: Tempos de execução para o bubble sort                |                 |

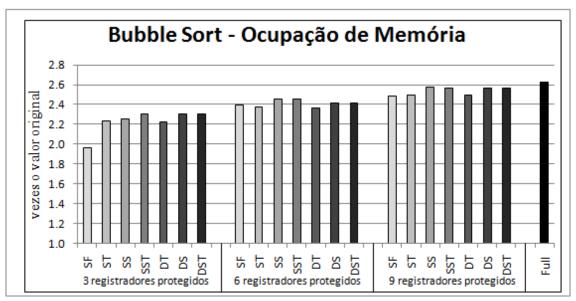

| Figura 5.4: Tempos de execução para o bubble sort                                                                                         |                 |

|                                                                                                                                           |                 |

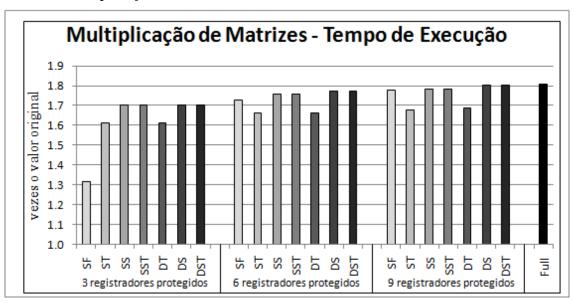

| Figura 5.6: Tempos de execução para a multiplicação de matrizes                                                                           |                 |

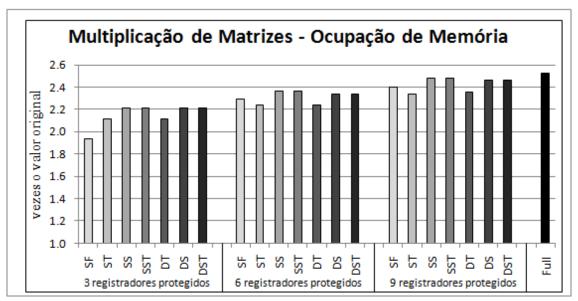

| Figura 5.7: Ocupações de memória para a multiplicação de matrizes                                                                         |                 |

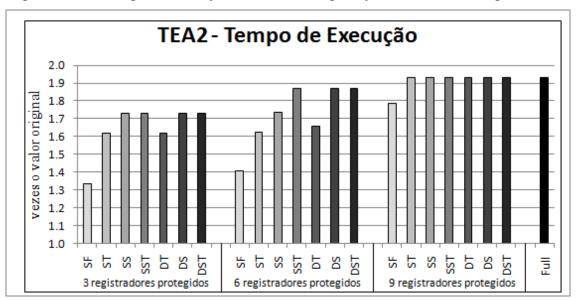

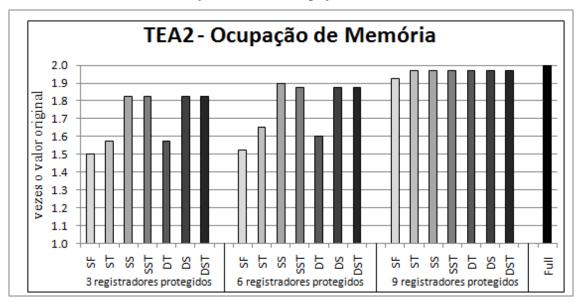

| Figura 5.8: Tempos de execução para o algoritmo de encriptação TEA2                                                                       |                 |

| Figura 5.9: Ocupações de memória para o algoritmo de encriptação TEA2                                                                     | 81              |

# LISTA DE TABELAS

| Tabela 4.1: Tipos de dados do formato SREC                    | 51 |

|---------------------------------------------------------------|----|

| Tabela 4.2: Multiplicação de Matrizes (MIPS) - CFT-tool       |    |

| Tabela 4.3: Multiplicação de Matrizes (MIPS) – HPCT Suite     |    |

| Tabela 4.4: Bubble Sort (MIPS) - CFT-tool                     | 64 |

| Tabela 4.5: Bubble Sort (MIPS) - HPCT Suite                   | 65 |

| Tabela 4.6: Algoritmo de Encriptação TEA2 (MIPS) - CFT-tool   | 65 |

| Tabela 4.7: Algoritmo de Encriptação TEA2 (MIPS) – HPCT Suite | 66 |

| Tabela 4.8: Multiplicação de Matrizes (LEON3) – CFT-tool      | 71 |

| Tabela 4.9: Bubble Sort (LEON3) – CFT-tool                    | 72 |

| Tabela 4.10: Algoritmo de Encriptação TEA2 (LEON3) – CFT-tool | 73 |

| Tabela 5.1: Bubble Sort                                       |    |

| Tabela 5.2: Multiplicação de Matrizes                         | 83 |

| Tabela 5.3: Algoritmo de Encriptação (TEA2)                   |    |

| 1 3 , , ,                                                     |    |

#### **RESUMO**

Este trabalho apresenta uma ferramenta configurável, denominada de CFT-tool, capaz de aplicar automaticamente técnicas de detecção de erros em *software* com o objetivo de proteger processadores com diferentes arquiteturas e organizações contra falhas transientes no *hardware*. As técnicas baseadas em redundância e comparação são aplicadas pela CFT-tool no código *assembly* de um programa desprotegido, compilado para a arquitetura alvo.

A ferramenta desenvolvida foi validada utilizando dois processadores distintos: miniMIPS e LEON3. O processador miniMIPS foi utilizado para verificar a eficiência, em termos de taxa de detecção de erros, tempo de execução e ocupação de memória, das técnicas de detecção em *software* aplicadas pela CFT-tool, comparando os resultados obtidos com os presentes na literatura. O processador LEON3 foi selecionado por ser amplamente utilizado em aplicações espaciais e por ser baseado em uma arquitetura diferente da arquitetura do processador miniMIPS. Com o processador LEON3 é verificada a configurabilidade da CFT-tool, isto é, a capacidade dela de aplicar técnicas de detecção em *software* em um código compilado para um diferente processador, o mantendo funcional e sendo capaz de detectar erros. A CFT-tool pode ser utilizada para proteger programas para outras arquiteturas e organizações através da modificação dos arquivos de configuração da ferramenta. A configuração das técnicas é definida segundo as especificações da aplicação, recursos do processador e seleções do usuário.

Programas foram protegidos e falhas foram injetadas em nível lógico em ambos os processadores. Para o processador miniMIPS, as taxas de detecção de erros, os tempos de execução e as ocupações de memórias dos programas protegidos se mostraram compatíveis com os resultados presentes na literatura. Resultados semelhantes foram encontrados para o processador LEON3. Diferenças entre os resultados ocorrem devido às características da arquitetura.

A ferramenta CFT-tool por ser configurável pode proteger o código na integralidade ou selecionar partes do código e registradores que serão redundantes e protegidos. A vantagem de proteger parte do código é reduzir o custo final em termos de tempo de processamento e ocupação de memória. Uma análise do impacto da seleção seletiva de registradores na taxa de detecção de erros é apresentada. E diretivas de alcançar um comprometimento ótimo entre quantidade de registradores protegidos, taxa de detecção de erros e custo são discutidas.

**Palavras-Chave:** tolerância a falhas, falhas transientes, SEU, SET, técnicas de detecção em *software*.

# CFT-tool: Configurable Tool to Application of Faults Detection Techniques in Processors by Software

## **ABSTRACT**

This work presents a configurable tool, called CFT-tool, capable of automatically applying software-based error detection techniques aiming to protect processors with different architectures and organizations against transient faults in the hardware. The techniques are based on redundancy and comparison. They are applied by CFT-tool in the assembly code of an unprotected program, compiled to the target architecture.

The developed tool was validated using two distinct processors: miniMIPS and LEON3. The miniMIPS processor has been utilized to verify the efficiency of the software-based techniques applied by CFT-tool in the assembly code of unprotected programs in terms of error detection rate, runtime and memory occupation, comparing the obtained results with those presented in the literature. The LEON3 processor was selected because it is largely adopted in space applications and because it is based on a different architecture that miniMIPS processor. The configurability of the CFT-tool is verified with the LEON3 processor, that is, the capability of the tool at applying software-based detection techniques in a code compiled to a different processor, maintaining it functional and capable of detecting errors. The CFT-tool can be utilized to protect programs compiled to other architectures and organizations by modifying the configuration files of the tool. The configuration of the techniques is defined by the specifications of the application, processor resources and selections of the user.

Programs were protected and faults were injected in logical level in both processors. When using the miniMIPS processor, the error detection rates, runtimes and memory occupations of the protected programs are comparable to the results presents in the literature. Similar results are reached with the LEON3 processor. Differences between the results are due to architecture features.

The CFT-tool can be configurable to protect the entire code or to select portions of the code or registers that will be redundant and protected. The advantage of protecting portions of the code is to reduce the final cost in terms of runtime and memory occupation. An analysis of the impact of selective selection of registers in the error detection rate is also presented. And policies to reach an optimum committal between amount of protected registers, error detection rate and cost are discussed.

**Keywords:** fault tolerance, transient faults, SEU, SET, software-based detection techniques.

# 1 INTRODUÇÃO

A evolução da indústria de semicondutores tem possibilitado a fabricação de circuitos integrados cada vez menores, fazendo com que o tamanho dos transistores se aproxime dos limites físicos (THOMPSON, 2005). Desse modo circuitos integrados compostos por transistores de dimensão reduzida, operando em baixa tensão de alimentação e alta frequência de operação, são mais sensíveis a defeitos de fabricação e falhas devido ao ruído do meio (DODD, 2010).

As falhas podem ser permanentes, transientes ou intermitentes. As falhas transientes podem vir do meio, como fonte de radiação ou de influencia eletromagnética. Single Event Effects (SEE) ou soft errors (NICOLESCU, 2003) são os efeitos transientes que ocorrem em circuitos integrados operando no espaço e mais recentemente em circuitos integrados fabricados em tecnologia nanométrica operando também na terra. São causados por efeitos da radiação devido à interação de nêutrons com o silício gerando partículas secundárias como alfa. Quando este efeito ocorre em um elemento de memória, é denominado Single Event Upset (SEU) e caracteriza-se pela inversão do valor armazenado no flip-flop (um bit-flip). Já quando esse efeito transiente afeta uma porta lógica de um bloco combinacional, é denominado Single Event Transient (SET) e é observado como um pulso de tensão transiente (glitch) de duração variável conforme carga coletada.

Um fator que tem aumentado a sensibilidade dos circuitos aos efeitos da radiação é o aumento do número de transistores por área, possibilitado pela redução do seu tamanho, o que faz com que as chances de uma partícula energizada afetem um ou mais nós sensíveis do circuito ao mesmo tempo sejam maiores, gerando múltiplas falhas.

Além disso, o Single Event Transient (SET) tem se mostrado um problema crescente com o avanço da tecnologia que tem permitido cada vez maiores frequências de operação. Enquanto a frequência está aumentando, o tempo de um pulso transiente tem se mantido constante (FERLET-CAVROIS, 2005), aumentando, com isso, a probabilidade de um pulso transiente causar um erro, pois, com um menor intervalo entre cada borda do relógio, a chance desse pulso ser capturado pela borda de relógio aumenta.

Para garantir o funcionamento correto de um circuito integrado na presença de falhas, podem ser usadas técnicas de tolerância a falhas que detectam ou detectam e corrigem falhas. A falha pode ocorrer e se manifestar como erro ou ser mascarada pela lógica do circuito e não ocasionando erro. Quando a falha se manifesta, normalmente se detecta o erro que ela gerou. No caso dos processadores, podemos ver o efeito das falhas SEU e SET como erros nos dados gerados pelo programa ou como erros no fluxo de execução do código original.

Para proteger os processadores, técnicas de tolerância a falhas podem ser aplicadas em *hardware* e/ou em *software*, fazendo uso de redundância de *hardware* ou de instruções no espaço ou no tempo para detectar falhas que se manifestem como erros nos dados ou no fluxo de execução do processador. O impacto do uso de técnicas de tolerância pode ser medido em área, desempenho, potência, tempo de execução e taxa de detecção de erros.

Nas técnicas em *hardware*, o sistema físico é alterado. O circuito normalmente é duplicado ou triplicado e verificadores ou votadores são inseridos (PRADHAN, 1995). Pode-se também usar códigos de correção de erro (EDAC) nos elementos de memória. Conforme as técnicas em *hardware* implementadas, o sistema apresenta diferentes custos como diminuição na frequência de operação, aumento em área e potência, além de possuir um alto custo de projeto e fabricação (ASENSI, 2011).

Já as técnicas em *software* mantém a parte física inalterada, permitindo o uso de processadores comerciais que são consideravelmente mais baratos que um processador específico desenvolvido para ser tolerante a falhas (processador rad-hard). O que deve ser modificado é somente o código do programa a ser protegido. O programa original é alterado onde técnicas de proteção em *software* são adicionadas, tais como técnicas de duplicação de variáveis, por exemplo, EDDI (OH, 2002a), ou técnicas de controle de fluxo, por exemplo, CFCSS (OH, 2002b), ou aplicando regras de transformação de código (CHEYNET, 2000). Contudo, essas aumentam consideravelmente o tempo de computação e a ocupação de memória da aplicação.

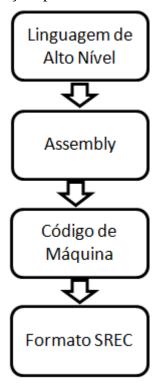

Para realizar a proteção de microprocessadores em *software* podem-se aplicar técnicas de proteção em três diferentes níveis de linguagem. Uma possibilidade é proteger o código em nível de linguagem de programação, por exemplo, na linguagem C. Contudo, o código protegido em alto nível está sujeito a otimizações pelo compilador o qual pode remover as redundâncias geradas pela técnica e tornar a proteção ineficaz. Outra possibilidade em alto nível é alterar o compilador para que esse não remova as redundâncias aplicadas pela técnica, tornando-a eficiente para a proteção da arquitetura alvo. A técnica também pode ser aplicada ao código *assembly* do programa, dessa forma, ficando livre das otimizações realizadas pelo compilador e não necessitando modificar o compilador ou o montador. Por fim, pode-se proteger diretamente o código de máquina do programa, o qual, como em *assembly* não necessita modificar o compilador ou o montador.

Aplicando as técnicas de proteção em *software* ao código de máquina tem-se a garantia que essas não sofrerão alterações, pois estão sendo aplicadas ao produto final do programa. Contudo, algumas dificuldades surgem na aplicação das técnicas de proteção nesse nível. Primeiramente, em alguns processadores, visando um aumento no desempenho, um determinado número de instruções após instruções de desvio é sempre executado. Para garantir a integridade do programa, o montador move essas instruções de desvio para cima. Dessa forma, essas instruções estão logicamente fora de ordem e isso deve ser levado em conta na hora da aplicação de técnicas de proteção para que a corretude do programa não seja perdida. O outro problema que afeta a aplicação dessas técnicas em código de máquina diz respeito aos endereços de destino dos desvios. Com a aplicação das técnicas de proteção em *software*, as instruções do programa têm seus endereços alterados, portanto, para que o programa funcione corretamente, é necessário calcular os novos endereços de destino das instruções de desvio.

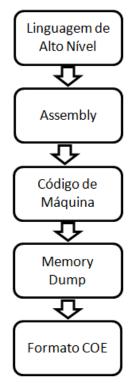

Uma alternativa para a aplicação das técnicas de proteção sem a necessidade de se preocupar com essas questões relativas ao processador é aplicá-las em um nível de abstração mais elevado. Contudo, aplicar as técnicas em uma linguagem de alto nível não é uma boa alternativa, visto que nesse nível o programa está sujeito às otimizações realizadas pelo compilador que remove as redundâncias no processo de compilação e consequentemente as proteções aplicadas pelas técnicas, deixando o programa desprotegido. Portanto, a saída é aplicar as técnicas em um nível intermediário, modificando o código *assembly*. O código *assembly* não está sujeito às otimizações realizadas pelo compilador, visto que ele é gerado justamente pelo compilador, após o processo de compilação. Isso pode ser visto na figura 1.1, a qual apresenta os diferentes níveis de abstração do programa e as transformações pela qual o código em alto nível sofre até a geração do código de máquina.

Figura 1.1: Níveis de abstração e processos de transformação do programa.

Depois de compilado, o programa encontra-se em sua versão em código assembly, um nível acima do código final que será executado pelo processador, o código de máquina. Entre o código assembly e o código de máquina existe o montador. O montador altera algumas instruções do código assembly no processo de montagem para o código de máquina, visando otimizá-lo. Um exemplo disso é a modificação das posições dos desvios, citado como um dos problemas de se aplicar as técnicas de proteção em código de máquina. Outro fator é que nem todas as instruções em código assembly são um-para-um em relação ao código de máquina, ou seja, para algumas instruções em assembly, o montador precisa gerar mais de uma instrução única instrução para realizar a função referente àquela instrução.

Este trabalho apresenta a CFT-tool, uma ferramenta capaz de proteger diversos microprocessadores com diferentes organizações e arquitetura contra falhas transientes através da detecção do efeito destas falhas. Para isso, é necessário que essa ferramenta seja configurável e que seja capaz de aplicar uma gama de técnicas de tolerância a falhas, capazes de detectar erros, ou seja, técnicas de detecção de erros em software, as quais possam ser configuradas pelo usuário, conforme custos como área, tempo de execução e taxa de detecção. Visto que a ferramenta deve ser independente de arquitetura, a melhor opção para se aplicar as técnicas seria na linguagem de alto nível, a qual é independente de arquitetura, porém, o compilador, no processo de otimização do código, acaba removendo as proteções aplicadas pela técnica. A outra possibilidade em alto nível é modificar o compilador para não retirar as redundâncias aplicadas pela técnica no processo de otimização. Essa abordagem torna a proteção eficiente, mas torna a ferramenta dependente da arquitetura para qual o compilador foi projetado. Como a ferramenta deve ser genérica, e modificar o compilador de cada arquitetura alvo é inviável, essa abordagem também foi rejeitada. As duas possibilidades restantes consistem em aplicar a proteção em assembly ou código de máquina. No entanto, ambas estão diretamente atreladas à arquitetura, o que também não torna essas abordagens genéricas. A solução encontrada é descrever a arquitetura alvo para que a ferramenta

seja capaz de interpretá-la e aplicar técnicas de tolerância a falhas à arquitetura descrita. Dessa forma, para alterar a arquitetura alvo, basta modificar a descrição da arquitetura.

A escolha em se aplicar as técnicas em *assembly* ou código de máquina ocorre pela facilidade de se aplicar as técnicas em assembly em relação ao código de máquina. Aplicando as técnicas em código de máquina, é necessário corrigir os endereços alvo instruções de desvio que tiveram seus alvos deslocados de posição no processo de aplicação das técnicas, além de levar em consideração se as instruções desvio foram deslocadas pelo montador, caso o processador alvo executa sempre um determinado número de instruções após os desvios. Por outro lado, aplicando-se as técnicas de proteção em *assembly*, abstraem-se esses problemas já que os destinos dos desvios são indicados por *labels* e as instruções estão na posição correta. Por esses motivos, foi escolhido aplicar as técnicas em *assembly*, onde pode ser utilizado um compilador e montador existente para a arquitetura alvo, sem necessitar modificá-los.

O trabalho foi dividido nas seguintes etapas. Primeiramente, algumas técnicas de proteção foram aplicadas em assembly e código de máquina a um caso de estudo para verificar a taxa de detecção da técnica sendo aplicada em assembly em relação ao código de máquina. Em seguida, a ferramenta foi desenvolvida implementando um conjunto de técnicas de proteção em software que se mostraram eficientes. Essas técnicas foram testadas e comparadas com resultados obtidos por Azambuja (2010), que adaptou um conjunto de técnicas para a aplicação em código de máquina e realizou os testes para o processador miniMIPS (HANGOUT, 2009), o qual também foi utilizado nesta dissertação. Depois de verificada a eficiência da ferramenta em nível assembly, a configurabilidade desta foi validada utilizando o processador LEON3 (GAISLER, 2004), o qual é bastante utilizado em aplicações espaciais. A validação final foi feita implementando um conjunto de técnicas de detecção a falhas em software nos processadores alvo e comparando as taxas de detecção de erros através de uma campanha de injeção de falhas, onde milhares de falhas transientes foram injetadas através de simulação lógica, sendo a eficiência da ferramenta analisada. Os processadores escolhidos são todos RISC, mas a maioria das técnicas aplica-se também em processadores CISC e superescalares (REBAUDENGO, 2000) (OH, 2002a). Mas caberá um estudo no futuro para otimizar as técnicas para essas arquiteturas assim como VLIW, por exemplo.

# 2 CONCEITOS DE DETECÇÃO DE ERROS EM SOFTWARE

Neste capítulo são apresentadas técnicas de detecção em *software* presentes na literatura. Além disso, também são abordadas, neste capítulo, ferramentas que implementam técnicas de detecção em *software* em diferentes níveis de linguagem são abordadas.

## 2.1 Técnicas de Detecção de Erros em Software

Em um sistema computacional, falhas transientes podem afetar o fluxo de execução de um programa (controle) ou modificar os dados armazenados em registradores ou na memória. Para proteção dos processadores, foram desenvolvidas diversas técnicas para proteção dos dados e do controle.

As técnicas de detecção em *software* podem ser classificadas conforme seu enfoque na proteção, sendo divididas em técnicas para proteção dos dados, técnicas para proteção do controle e técnicas de proteção híbridas. A seguir, são detalhadas essas três áreas.

#### 2.1.1 Técnicas para proteção dos dados

As técnicas de proteção dos dados têm por objetivo proteger os dados armazenados na memória e nos registradores. Tais técnicas duplicam as variáveis, criando cópias dessas variáveis, onde toda operação realizada sobre a variável original é também realizada sobre sua cópia. Operações de comparação entre a variável original e a cópia são realizadas em diferentes pontos do programa para verificar a integridade dos dados. Os pontos onde essas instruções de verificação são inseridas dependem da técnica utilizada. Esse tipo de técnica não é projetado para a proteção do fluxo de controle do programa, mas mesmo assim é capaz de detectar alguns erros causados por desvios no fluxo de controle que acabam causando diferenciação entre as variáveis originais e suas cópias.

Um exemplo de técnica de proteção aos dados implementada somente em *software*, proposta por Oh (2002a) é a EDDI (Error Detection by Duplicated Instructions). A EDDI é uma técnica capaz de detectar as falhas que venham a afetar os dados. Ela duplica toda a informação, ou seja, toda variável é duplicada e toda a operação que é executada sobre a variável original também é executada sobre sua cópia. Para garantir que os dados estejam consistentes, é realizada uma comparação no valor das variáveis originais e suas cópias, verificando se ambas têm o mesmo valor. Essa verificação é realizada antes dos dados serem armazenados na memória, ou seja, antes das instruções

de *store*, pois o armazenamento correto dos dados na memória implica em uma execução correta do programa. Portanto, realizar a comparação entre os dados antes das instruções de store torna-se uma boa estratégia. Contudo, verificar os dados somente antes de gravar na memória é insuficiente, já que dados errados podem levar os desvios a tomar a direção incorreta no fluxo de execução, afetando a corretude do programa. Portanto, os dados devem ser verificados também antes das instruções de desvio.

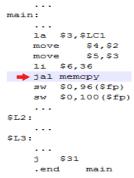

Na figura 2.1 é apresentado um exemplo de aplicação da técnica EDDI. Podemos ver que a instrução *load*, a qual carrega um valor de uma posição de memória indicada pela variável "GLOBAL" no registrador 12 foi duplicada, sendo carregada uma cópia do valor no registrador 22. Em seguida, a instrução *add* foi também duplicada, onde as cópias dos registradores 11, 12 e 13 são, respectivamente, os registradores 21, 22 e 23. A instrução store também foi duplicada. Para garantir que o dado também esteja duplicado na memória, um deslocamento é somado ao registrador que indica o endereço de memória. Contudo, como se trata de uma instrução de armazenamento, deve-se realizar a verificação dos registradores originais com suas respectivas cópias para garantir a integridade dos dados. Isso pode ser visto nas comparações entre os registradores 11 e 21 e os registradores 12 e 22. Caso ambos possuam o mesmo valor, o programa é executado normalmente, no entanto, se ocorrer uma discrepância em uma das comparações, o erro é detectado e o programa passa para a rotina de tratamento de erro.

Figura 2.1: Aplicação da técnica EDDI (REIS, 2005).

Desconsiderando as falhas detectadas pelo sistema operacional, a técnica EDDI consegue uma taxa de detecção de cerca de 93% para Fast Fourier Transform e multiplicação de matrizes (OH, 2002a) para as falhas que afetam os dados. Contudo, todos os registradores do programa precisam ser duplicados juntamente com todas as operações sobre tais registradores. Também é necessário incluir a verificação desses registradores com suas cópias antes de cada instrução de armazenamento ou desvio onde esses registradores estiverem sendo utilizados. Portanto, o aumento na ocupação de memória e o tempo de execução são significativos e deve ser levado em conta na utilização dessa técnica. Além disso, essa técnica não garante a detecção de erros que afetem o controle, o qual pode causar uma saída incorreta nos dados.

#### 2.1.2 Técnicas para proteção do controle

As técnicas de proteção ao controle buscam garantir a integridade do fluxo de execução do programa. As técnicas presentes na literatura dividem o programa em blocos básicos, que são porções de código sem instruções de desvio. Para cada bloco básico é atribuída uma assinatura que o identifica. Existem três tipos de falhas que afetam o controle: falhas que desviam o fluxo de execução do programa do meio de um

bloco básico para o meio de outro bloco básico; falhas que desviam o fluxo de execução de um bloco básico para o início de outro bloco; e falhas que desviam o fluxo de execução do programa para outra parte do bloco básico em execução. Esse último tipo de falha não é detectado pelas técnicas presentes na literatura.

Dentre as principais técnicas de proteção ao fluxo de controle temos a CCA (Control Flow Checking using Assertions), proposta por McFearin (1995), a qual divide o programa em blocos básicos. A técnica CCA precisa de três registradores para sua implementação, um para identificação do bloco básico, Basic Block Identifier (BID), e dois para identificação do fluxo de controle, Control Flow Identifier (CFID). Cada bloco básico possui um BID único que é assinalado no início da execução do bloco e é checado ao final da execução do bloco. O CFID do bloco básico é atribuído no fim da fila dos dois registradores de identificação quando o bloco é iniciado. E, ao final da execução do bloco, o CFID do bloco executado anteriormente é retirado. Nesse ponto, como pode ser visto na figura 2.2, o método é capaz de identificar se após a execução de um bloco básico, o fluxo de execução foi mudado para algum bloco que não deveria ser executado após aquele.

Figura 2.2: Exemplo da técnica CCA (ALKHALIFA, 1999).

No entanto, a técnica CCA não consegue detectar falhas para quando ocorre uma mudança no fluxo para dentro de um mesmo bloco básico ou quando o fluxo de execução é mudado, após o teste do BID para o início de outro bloco básico com o mesmo CFID que o bloco que deveria ser executado.

Uma modificação na técnica CCA foi proposta por Alkhalifa (1999), trata-se da técnica ECCA (Enhanced Control Flow Checking using Assertions). A diferença da técnica CCA para a ECCA consiste em que essa última utiliza assinaturas de tempo real, ou seja, que as assinaturas CFID dos blocos se modificam em tempo de execução através de uma assinatura de ajuste que nada mais é que uma operação "ou exclusivo" entre a assinatura do bloco básico pai e do bloco básico filho. Isso garante que falhas que desviam o fluxo de controle de um bloco básico para outro que não deveria ser executado em seguida seja detectado. Contudo, apesar dessa técnica detectar até 85%

dos erros (ALKHALIFA, 1999), ela aumenta o tempo de execução em relação à técnica CCA por exigir o cálculo de assinaturas em tempo real. Também não consegue detectar falhas que desviem o fluxo de execução do programa para dentro do mesmo bloco básico que está sendo executado.

Outra técnica de proteção ao fluxo de controle é a CFCSS (Control Flow Checking by Software Signatures) (OH, 2002b) que, da mesma forma que as outras técnicas de proteção ao fluxo de controle apresentadas, divide o programa em blocos básicos e adiciona uma assinatura a cada um. Um registrador é necessário para a implementação desse método, ele armazena o valor da assinatura do bloco básico em execução e, ao iniciar a execução de um novo bloco básico, uma operação "ou exclusivo" é executada com o atual valor do registrador e uma constante, resultando na assinatura do bloco básico atual. Caso o resultado seja diferente da assinatura do bloco, uma falha no fluxo de execução do programa ocorreu.

Essa técnica tem um menor custo em relação às técnicas de proteção ao fluxo de controle citadas anteriormente, pois necessita apenas de um registrador para armazenar o valor da assinatura atual, da inserção de uma operação ou exclusivo e uma comparação com a assinatura por bloco básico. Contudo, sofre dos mesmos problemas da técnica CCA, ou seja, não é capaz de detectar falhas que causem um desvio no fluxo de execução do programa de um bloco básico pai para um bloco básico filho que não seja o bloco básico que deveria ser executado, além de não ser capaz de detectar falhas que mudem o fluxo de execução do programa para dentro de um mesmo bloco básico.

#### 2.1.3 Técnicas híbridas

As técnicas de proteção híbridas buscam proteger tanto os dados quanto garantir que fluxo de execução do programa seja seguido corretamente. O que esse tipo de técnica faz é aplicar regras de transformação sobre o código, somando características das técnicas de proteção aos dados com características das técnicas de proteção ao fluxo de controle.

Um conjunto de regras de transformação proposto por Rebaudengo (1999) estabelece regras para a proteção dos dados e regras para proteção do fluxo de controle. Para proteger os dados, toda variável deve ser duplicada, sendo que cada operação de escrita realizada sobre a variável original deve ser realizada sobre sua cópia. Em toda operação de leitura da variável, deve ser realizado, além de uma operação de leitura sobre sua cópia, uma verificação entre os valores armazenados na variável original e em sua cópia. Caso seus valores não sejam iguais, o erro é detectado.

Visando a detecção das falhas que afetam o fluxo de execução do programa, um valor inteiro está associado a cada bloco básico, sendo o valor atribuído no início da execução do bloco e testado no final. Técnica semelhante às assinaturas BID da técnica de proteção ao fluxo de controle CCA. Além disso, uma nova regra destinada à proteção do fluxo de controle foi incluída, na qual deve haver réplicas dos desvios condicionais, uma para caso o desvio seja tomado e outra para caso o desvio não seja tomado. No local para onde o fluxo de execução vai caso o desvio seja tomado é inserido um desvio condicional logicamente inverso ao original. E no local para onde o fluxo de execução vai caso o desvio não seja tomado é inserido um desvio igual ao original. Ambas as cópias desviam o fluxo de execução do programa para uma rotina de tratamento de erro caso sua condição seja verdadeira, caso contrário, o programa segue sua execução normalmente. Por fim, a cada sub-rotina do sistema é associado um valor inteiro. Esse

valor é atribuído a um registrador imediatamente antes do retorno da sub-rotina, sendo testado na instrução seguinte à chamada de sub-rotina, ou seja, logo após o retorno da sub-rotina, onde é verificado se o valor do registrador é condizente com o valor esperado para aquela sub-rotina. Segundo Rebaudengo (1999), essa técnica é capaz de detectar quase 100% dos erros que afetam os dados, mas não é capaz de fazer o mesmo com os erros que afetam o controle. Além disso, essa técnica aumenta em cerca de 444% o tempo de execução do programa, o que a torna ineficiente, visto que esse tempo é mais que suficiente para executar o programa três vezes, realizar uma votação entre os três resultados e definir o resultado correto.

Outra técnica que busca proteger tanto os dados quanto o fluxo de execução do programa foi proposta por Nicolescu (2003) e também sugere um conjunto de regras que devem ser aplicadas ao programa. As variáveis são divididas em dois tipos: variáveis temporais e variáveis finais. Ambas devem ser duplicadas e toda operação sobre a variável original deve também ser realizada sobre a cópia. Contudo, a verificação da consistência dos dados é aplicada somente às variáveis finais após cada operação de escrita. Variáveis finais são aquelas que serão armazenadas em memória. Essa separação entre variáveis temporais e finais é a principal diferença dessa técnica para a técnica de Rebaudengo (1999) e influencia significativamente na diminuição do tempo de execução do programa que tem um aumento de cerca de 144% em relação ao programa original frente aos 444% da técnica de Rebaudengo (1999).

Para proteger o fluxo de execução do programa é atribuído um valor inteiro e um valor lógico a cada bloco básico. O valor lógico é verdadeiro quando o bloco não está em execução e falso quando o bloco está sendo executado. Os valores de identificação do bloco básico são associados a um registrador no início da execução do bloco. Por fim, como em Rebaudengo (1999), as instruções de desvio são replicadas. Além disso, também são atribuídos valores a cada sub-rotina do programa, sendo que nessa técnica a verificação da sub-rotina é realizada em dois pontos, antes e após a execução da sub-rotina.

Como foi citado, o aumento no tempo de execução gerado por essa técnica é significativamente menor que o aumento da técnica de Rebaudengo (1999), entretanto, suas taxas de detecção são inferiores, sendo capaz de detectar cerca de 85% das falhas que afetam os dados e 56% das falhas que afetam o controle.

Podemos perceber que as técnicas buscam proteger os dados e o fluxo de controle do programa separadamente. Logo, uma abordagem lógica seria combinar técnicas de proteção aos dados com técnicas de proteção ao fluxo de controle. Foi isso que REIS (2005) fez, combinando a técnica de proteção aos dados EDDI com a técnica de proteção ao fluxo de controle CFCSS e realizando algumas alterações nessa nova técnica, denominada SWIFT (Software Implemented Fault Tolerance). Primeiramente, foi modificada a parte destinada a proteção do controle. Foram atribuídos assinaturas a todos os blocos básicos, como a técnica CFCSS original, contudo a verificação foi somente realizada sobre blocos que possuem instruções store, pois somente esses realizam escritas na memória. Uma segunda modificação consiste na retirada da verificação realizada pela EDDI nos desvios condicionais, pois os desvios já são protegidos pela técnica CFCSS. Como as demais técnicas apresentadas, SWIFT não é capaz de detectar os erros desviam o fluxo de execução do programa para dentro do mesmo bloco básico.

## 2.2 Programas que Implementam Técnicas de Detecção em Software

Um programa descrito em linguagem de alto nível passa por vários processos até chegar a seu código de máquina. Primeiramente, o código é compilado, sendo passado da linguagem de alto nível para *assembly* a qual está associada a uma determinada arquitetura. No processo de compilação, o compilador realiza otimizações no programa. Através do montador, o código de máquina é gerado a partir do código *assembly*. A figura 1.1 mostra o programa em seus diferentes níveis de abstração, indicando os processos pelos quais ele passa até que possa ser executado pelo processador.

#### 2.2.1 Proteção em linguagem de alto nível

Como foi dito, as técnicas de proteção podem ser aplicadas em vários níveis de abstração. Uma ferramenta que altera o código em linguagem de alto nível, antes de passar por processo de compilação ou montagem chamada C2C Translator (NICOLESCU, 2003) aplica algumas técnicas de proteção em linguagem C. A aplicação de técnicas neste nível torna a ferramenta independente de arquitetura. Contudo, o compilador busca otimizar ao máximo o programa, retirando redundâncias, o que pode ocasionar no não funcionamento das técnicas aplicadas nesse nível. Além das complicações em verificar o *software* modificado onde redundâncias e testes foram inseridos a fim de garantir que erros não tenham sido inseridos no código.

Outra possibilidade é modificar o compilador, como fez Reis (2005), que modificou o compilador OpenIMPACT para aplicar a técnica SWIFT no processador Intel Itanium 2. As otimizações que removiam as proteções foram alteradas para respeitar a técnica aplicada. Contudo, esse processo tira a generalidade de uma ferramenta nesse nível, pois o que é ganho aplicando as técnicas em linguagem de alto nível é perdido pelo fato de para cada processador alvo, ter que ser realizada modificações sobre o compilador para tal processador.

#### 2.2.2 Proteção em linguagem assembly

Uma outra possibilidade consiste em modificar o código *assembly* do programa, evitando assim, que as otimizações do compilador removam a proteção. Esse nível é mais simples para aplicação das técnicas de proteção em relação ao código de máquina, pois, dependendo do processador, as instruções de desvio em código de máquina podem ser trocadas de posição após o processo de montagem, além de ser necessário recalcular o endereço de destino dos desvios, pois a aplicação da técnica modifica a posição das instruções na memória. Contudo, para se aplicar a técnica em *assembly*, algumas alterações que ocorrem no processo de montagem precisam ser verificadas para determinar a eficiência de se aplicar as técnicas de proteção nesse nível.

#### 2.2.3 Proteção em código de máquina

Na outra ponta está a proteção pela modificação do código de máquina do programa. Uma ferramenta que trabalha nesse nível é o HPCT Suite (AZAMBUJA, 2010) a qual altera o código de máquina do programa para o processador miniMIPS. Nesse nível, tem-se a garantia que o código não sofrerá alterações, contudo, apesar da eficiência da ferramenta para tal processador, ela está atrelada a ele. Porém, como o objetivo é aplicar as técnicas de forma genérica e não intrusiva, a proteção em código de máquina se torna um empecilho para o desenvolvimento de uma ferramenta genérica nesse nível.

# 3 CFT-TOOL: FERRAMENTA PARA APLICAÇÃO DE TÉCNICAS DE PROTEÇÃO EM SOFTWARE PARA DIFERENTES PROCESSADORES

Neste trabalho, foi desenvolvida uma ferramenta, denominada CFT-tool, que realiza transformações sobre o código *assembly* de programas. Técnicas de detecção em *software* são aplicadas pela CFT-tool sobre o código *assembly* de programas. O código *assembly* é modificado, sendo inseridos instruções redundantes e verificadores. As técnicas de detecção em *software* que a ferramenta implementa foram validadas por Azambuja (2010). A CFT-tool é independente da arquitetura e organização do processador, podendo ser utilizada para proteger diferentes processadores, com diferentes organizações e arquiteturas.

A CFT-tool foi desenvolvida na linguagem Java, uma linguagem multiplataforma, a qual permite a execução da ferramenta em diferentes sistemas operacionais. A ferramenta é dividida em módulos, baseados em suas funcionalidades. A linguagem Java foi escolhida devido a sua flexibilidade, praticidade e documentação vasta e organizada. Além disso, a linguagem Java possui uma comunidade grande e ativa de usuários, com muitas funções que auxiliam no desenvolvimento de programas.

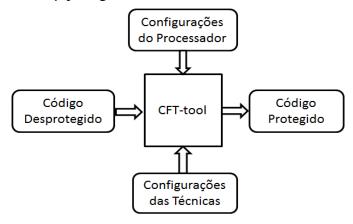

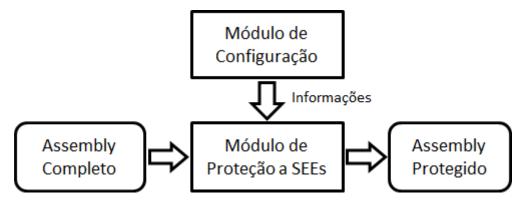

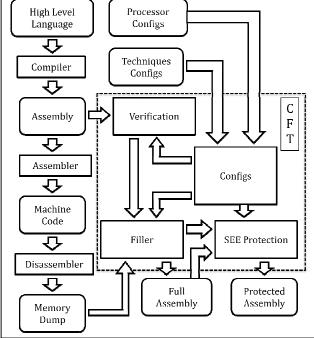

A figura 3.1 apresenta uma visão geral de como a CFT-tool trabalha. As configurações referentes à arquitetura e organização do processador alvo são carregadas. Da mesma forma, as configurações sobre as técnicas de detecção em *software* que serão aplicadas sobre o código *assembly* do programa a ser protegido também são carregadas. O código *assembly* do programa desprotegido é lido e processado pela CFT-tool. A CFT-tool realiza transformações sobre o código desprotegido, aplicando as técnicas de detecção em *software* selecionadas, gerando, ao final, um código *assembly* protegido.

Figura 3.1: Visão geral do funcionamento da CFT-tool.

Há algumas vantagens no emprego de tolerância a falhas no código *assembly* em vez de no código de máquina. Por exemplo, no código de máquina, os endereços de destino dos desvios devem ser corrigidos, pois as instruções estarão em posições diferentes após a aplicação das técnicas de detecção em *software*. No código *assembly* isso não é necessário, pois o destino dos desvios são *labels*, sendo o endereço físico definido após o processo de montagem do código *assembly* para código de máquina. Além disso, o *branch delay slot*, que consiste em reordenar instruções de desvio para ganhar desempenho, aproveitando de características do *pipeline* do processador é outro fator. Somado a isso, aplicar as técnicas sobre o código *assembly* torna a CFT-tool mais portátil entre diferentes arquiteturas, pois o montador do processador alvo se encarrega de criar o arquivo executável. Por essas razões foi escolhido trabalhar com o código *assembly*, onde um compilador e um montador existentes podem ser utilizados sem que haja necessidade de qualquer modificação.

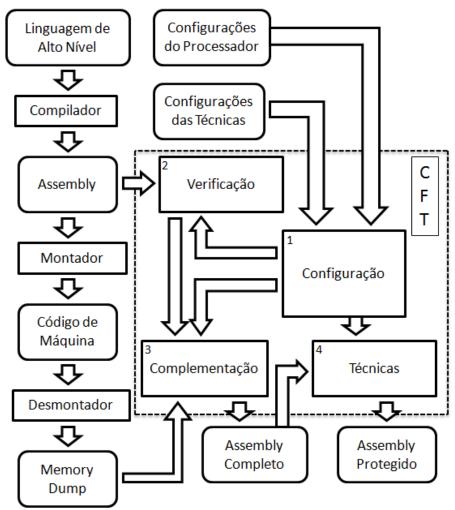

A figura 3.2 apresenta os estágios pelos quais o programa passa até que ser protegido pelas técnicas de detecção em *software*. O código do programa descrito em uma linguagem de alto nível é compilado, gerando o código *assembly* equivalente. Os números indicam a ordem de execução dos módulos da ferramenta.

Figura 3.2: Processo de aplicação da proteção pela ferramenta CFT-tool.

A CFT-tool carrega as configurações referentes à arquitetura e organização do processador e as configurações sobre as técnicas de detecção em *software* a serem

aplicadas. Essas configurações são lidas dos arquivos de configurações, sendo elas informadas pelo usuário. Depois disso, o módulo de verificação lê o código *assembly* do programa a ser protegido e verifica se o código do programa é condizente com a arquitetura do processador informada. Se for condizente, o programa passa para o próximo estágio, caso contrário, um erro é reportado e a execução da CFT-tool é finalizada. No próximo estágio, o módulo de complementação é responsável com gerar um novo código *assembly*, contendo todas as sub-rotinas utilizadas pelo programa. Finalmente, o módulo de proteção a falhas transientes (SEE) aplica as técnicas de detecção em *software* selecionadas pelo usuário sobre o código *assembly* gerado pelo módulo de complementação, criando uma versão protegida, em *assembly*, do programa.

A ferramenta CFT-tool é divida em quatro módulos. Esses módulos são apresentados em detalhes a seguir.

#### 3.1 Módulo de Configuração

A CFT-tool é independente da arquitetura e organização do processador. Como as técnicas de detecção em *software* são aplicadas sobre o código *assembly* do programa e o *assembly* está atrelado a uma arquitetura, é necessário que as características da arquitetura e organização do processador alvo sejam passadas para a CFT-tool. As técnicas de detecção em *software* selecionadas para serem aplicadas sobre o código *assembly* do programa também precisam ser informadas à ferramenta. Para isso, um padrão foi criando, onde são utilizados arquivos contendo as configurações da arquitetura e organização do processador e das técnicas a serem aplicadas.

Todas as instruções da arquitetura devem ser descritas, informando seu mnemônico, o formato como ela é apresentada no código e seu tipo (aritmético, *load, store*, saltos incondicionais, desvios condicionais ou outros). Informações sobre os registradores também são necessárias. Devem ser informados seus nomes, se podem ser lidos e escritos explicitamente e seu tipo (global, local, de entrada ou de saída). Além disso, outras características sobre a arquitetura e organização do processador devem ser informadas. Por exemplo, o formato dos *labels*, das *tag* de comentário e informações sobre reordenamento de instruções. As técnicas de detecção em *software* que serão aplicadas e quais os registradores que serão protegidos também devem estar informadas nos arquivos de configurações.

A função do módulo de configuração é carregar as configurações da arquitetura e organização do processador alvo e das técnicas de detecção em *software* a serem aplicadas e os padrões da arquitetura e as configurações aplicadas, informados nos arquivos de configuração, transformando em um formato que todos os outros módulos possam compreender. Ou seja, o módulo deve descrever toda a informação necessária sobre o processador e as técnicas para que os demais módulos possam executar suas funções de forma correta e independentemente da arquitetura.

O módulo de configuração é dividido em cinco partes. Configurações gerais apresentam características globais sobre a arquitetura e organização do processador. Configurações das instruções definem as instruções da arquitetura e configurações dos registradores contêm dados sobre os registradores existentes. As configurações do memory dump são necessárias para realizar a conversão de sub-rotinas do formato memory dump para assembly. E por fim, as configurações das técnicas apresentam as configurações para seleção e utilização das técnicas de detecção em software. Cada uma

dessas partes constitui um arquivo de configurações. As cinco partes do módulo de configuração são apresentadas em detalhes a seguir.

#### 3.1.1 Configurações gerais

As configurações gerais contêm informações gerais sobre a arquitetura e organização do processador. O formato dos *labels*, a *tag* de comentário e o caractere de separação de operandos devem ser informados nesse arquivo. A figura 3.3 apresenta um exemplo de formato de *label* configurado. O nome *label* indica onde estará o nome do *label* na linha de código. Os demais caracteres servem para auxiliar na identificação do *label*.

```

| [LABEL_FORMAT] | label:

```

Figura 3.3: Exemplo da configuração do formato do label.

Instruções que realizam alguma tarefa específica, necessária para que a CFT-tool consiga aplicar as técnicas de detecção em *software* sobre o código *assembly* do programa de forma correta, devem ter seu mnemônico informado nas configurações gerais. Por exemplo, a instrução que verifica se dois registradores têm valores diferentes é de extrema importância para a CFT-tool, pois ela faz a verificação entre os valores dos registradores originais e suas cópias. Por isso, ela deve ser declarada nas configurações gerais, como mostrado na figura 3.4. Outras instruções que se encaixam nessa classificação são as instruções de não operação, desvio condicional se diferente de zero, salto incondicional, associação de um valor constante a um registrador, cópia do valor de um registrador para outro, comparação entre registradores, comparação de registrador com constante e subtração de constante de um registrador.

```

[NON_EQUALITY_COMPARISON_INSTRUCTION]

bne

```

Figura 3.4: Exemplo de instrução que deve ser declarada nas configurações gerais devido às suas funcionalidades.

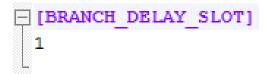

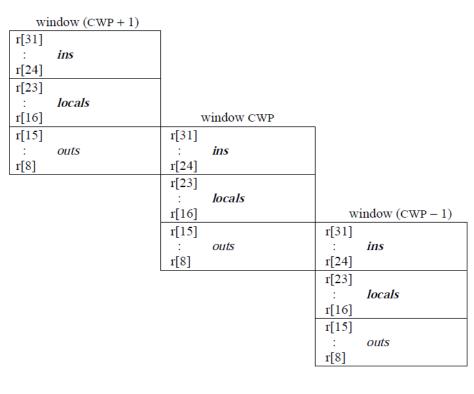

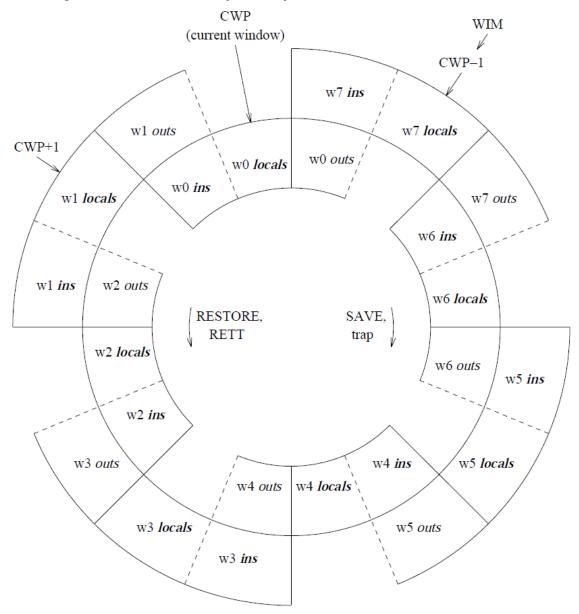

Branch delay slot é uma característica do pipeline de alguns processadores, onde instruções subsequentes à instrução de desvio em execução são sempre executadas, quer o desvio seja tomado ou não. Essa característica é mais comumente encontrada em processadores das arquiteturas DSP ou arquiteturas RISC mais antigas. No código, as instruções de desvio são deslocadas para cima, o número de vezes equivalente ao número de instruções que são sempre executadas após os desvios. Esse deslocamento pode acontecer no processo de compilação ou no processo de montagem. Se for realizado durante o processo de compilação, o código assembly terá instruções fora de ordem, e a CFT-tool precisa ter conhecimento disso para poder realizar as transformações no código assembly mantendo a corretude do programa. A informação sobre a existência do branch delay slot no código assembly deve ser informada no arquivo de configurações gerais, indicando o número de instruções que são sempre executadas após os desvios. A figura 3.5 mostra um exemplo dessa configuração para o processador LEON3. Por padrão, o valor dessa configuração é zero, portanto, não há necessidade de informá-lo caso essa característica não exista no processador alvo.

Figura 3.5: Configuração do *branch delay slot* para quando as instruções são reordenadas no código *assembly*.

Alguns registradores são utilizados por outras sub-rotinas antes do início da execução do programa. Esses registradores possuem algum valor atribuído e devem ser listados no arquivo de configurações gerais para que a CFT-tool não os utilize como registradores cópias.

Outra característica sobre registradores são as janelas de registradores, implementadas por algumas arquiteturas, como a SPARC. As janelas de registradores possuem registradores globais, acessáveis por todas as janelas, locais, exclusivos da janela em uso, e registradores de entrada e saída, para comunicação entre as janelas. Quando essa característica está presente no processador em uso, os mnemônicos das instruções que realizam a troca de uma janela de registradores para outra devem ser informados nos arquivos de configurações gerais.

As outras informações que devem estar contidas no arquivo de configurações gerais são o nome do arquivo que contém a representação do programa no formato *memory dump* e o mnemônico dos desvios condicionais, informando os desvios logicamente inversos na sequência. A figura 3.6 mostra como é feita essa associação entre os desvios logicamente inversos. Os mnemônicos de desvios condicionais logicamente inversos são separados por dois pontos e cada caso é separado por vírgula. As associações são realizadas nos dois sentidos, da primeira instrução para a segunda e da segunda para a primeira, ficando as duas ordens armazenadas na lista de desvios logicamente inversos do módulo de configuração.

```

[INVERTER_INSTRUCTIONS]

bne:beq, bltz:bgez, bgtz:blez, beqz:bnez, bgezal:bltzal

```

Figura 3.6: Configuração dos desvios condicionais logicamente inversos.

#### 3.1.2 Configurações das instruções

O arquivo de configurações das instruções contêm informações sobre o formato e tipo das instruções existentes na arquitetura do processador configurado. As instruções são configuradas em grupos, sendo que as instruções com as mesmas características são incluídas no mesmo grupo.

Os tipos aceitados são: arithmetic, load, store, branch\_to\_target, jump\_to\_target, jump\_to\_register, no\_operation e other. Arithmetic é usado para definir instruções aritméticas. Load define instruções que carregam dados da memória para registradores e store, instruções que armazenam dados na memória. Os desvios são classificados com o tipo branch\_to\_target, que indica que o destino do desvio são labels, o que é adotado no código assembly. Jump\_to\_target serve para saltos incondicionais para labels e jump\_to\_register, para saltos para a posição indicada por um registrador. No código assembly, instruções do tipo jump\_to\_register são usadas somente no retorno de subrotinas. A instrução de não operação é classificada como no\_operation. Instruções que não podem ser classificadas com nenhum dos tipos anteriores são do tipo other.

O formato da instrução serve para indicar a posição de cada elemento da instrução. A posição do mnemônico e dos operandos, sendo que esses ainda podem ser divididos em registradores fonte ou destino, valor imediato, valor de deslocamento e *label* de destino de desvios. A figura 3.7 apresenta um exemplo de formato de instrução. A posição do mnemônico é indicada pela identificação *ins*. O registrador destino é indicado por *rd* e registrador fonte por *rs*. O valor da constante de deslocamento, para operações de *load* e *store* é indicado por *offset*. Valores imediatos são referenciados por *imm*. Os destinos dos desvios, que são os nomes de *labels*, são identificados pela palavra *target*. Os outros caracteres presentes no formato são considerados constantes e servem para auxiliar na identificação do formato da instrução.

```

ins rd, offset (rs)

```

Figura 3.7: Exemplo de formato de instrução.

A figura 3.8 apresenta a configuração de um grupo de instruções. Essas instruções são do tipo aritmética. O formato das instruções desse grupo é formado pelo mnemônico da instrução, seguido por um espaço em branco e os operandos. Os operandos são o registrador destino e os registradores fontes, separados por vírgula.

```

[GROUP]

{INSTRUCTIONS}

add, addu, and, nor, or, sllv, slt, sltu, srav, srlv, sub, subu, xor

{FORMAT}

ins rd,rs,rs

{TYPE}

arithmetic

```

Figura 3.8: Exemplo de grupo de instruções.

A CFT-tool aceita sobrecargas de instruções, isto é, diferentes instruções com o mesmo mnemônico. Por exemplo, uma instrução *add* que realiza a soma entre dois registradores e outra instrução, com o mesmo mnemônico *add*, que realiza a soma entre um registrador e um imediato. A figura 3.9 apresenta outro grupo de instruções. Comparando a figura 3.9 com a figura 3.8, se pode notar que os formatos diferem por um valor imediato na figura 3.9 em relação a um registrador fonte na figura 3.8. Nas duas figuras apresentadas, estão presentes em ambas as instruções *addu*, *slt*, *sltu* e *subu*. Essas instruções são sobrecarregadas, pois possuem o mesmo mnemônico, mas tem um formato diferente. A diferenciação entre elas é realizada pela CFT-tool levando em conta a quantidade e posição de cada identificador.

```

GROUP]

{INSTRUCTIONS}

addi, addu, addiu, andi, ori, sll, slt, sltiu, sltu, sra, srl, subu, xori

{FORMAT}

ins rd,rs,imm

{TYPE}

arithmetic

```

Figura 3.9: Exemplo de grupo de instruções com instruções sobrecarregadas.

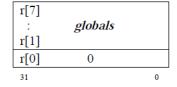

#### 3.1.3 Configurações dos registradores

Assim como as instruções, os registradores são configurados em grupos. Em cada grupo deve ser informado o nome dos registradores, se eles podem ser lidos e/ou escritos explicitamente e o tipo a que pertencem. O tipo do registrador pode ser *global*, *local*, *input* ou *output*. Se o processador configurado não utiliza janela de registradores, todos os registradores são do tipo *global*.

Na figura 3.10 pode ser visto um exemplo de grupo de registradores. Nesse grupo estão presentes os registradores \$2, \$3, \$4, \$5, \$6, \$7, \$8, \$9, \$10, \$11, \$12, \$13, \$14 e \$15. Esses registradores podem ser lidos e escritos explicitamente, isto é, podem ser usados pelas instruções regulares configuradas sem restrições. Os registradores são do tipo *global*.

```

☐ [GROUP]

{REGISTERS}

$2, $3, $4, $5, $6, $7, $8, $9, $10, $11, $12, $13, $14, $15

{READABLE}

YES

{WRITABLE}

YES

{TYPE}

global

```

Figura 3.10: Exemplo de grupo de registradores.

#### 3.1.4 Configurações do memory dump

O arquivo de configurações do *memory dump* contêm as informações referentes ao formato *memory dump* do processador configurado. Essas informações são necessárias para que o módulo de complementação possa converter o código de sub-rotinas do formato *memory dump* para código *assembly*.