# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

#### THIAGO ROSA FIGUEIRÓ

#### Multiple objective technology independent logic synthesis for multiple output functions through AIG functional composition

Thesis presented in partial fulfillment of the requirements for the degree of Master of Science in Microelectronics

PhD Prof. André Inácio Reis Advisor

PhD Prof. Renato Perez Ribas Co-advisor

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Figueiró, Thiago Rosa

Multiple objective technology independent logic synthesis for multiple output functions through AIG functional composition / Thiago Rosa Figueiró – Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2010.

77 f.:il.

Dissertação (mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2010. Orientador: André Inácio Reis; Coorientador: Renato Perez Ribas.

1. Logic Synthesis. 2. And-Inverter Graph. 3. Design Automation I. Reis, André Inácio. II. Ribas, Renato Perez. III. Multiple objective technology independent logic synthesis for multiple output functions through AIG functional composition.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PGMicro: Prof. Ricardo da Luz Reis

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor, André Inácio Reis for accepting me as his student even knowing that I could only provide a part-time dedication to this work. Moreover, I would like to acknowledge his support in providing and discussing ideas that are the core of this thesis. Moreover, I would like to thank him and my co-advisor, Renato Perez Ribas, for the discussions about career and future expectations. It is not easy to advise a part-time student and the results obtained by this work shows that it is possible.

This work was developed while working at Nangate. The support and understanding from my colleagues were essential so I could obtain my Master of Science degree.

During this project, although I was not a member of the LogiCS Lab, I spent several weeks working there and I'm very thankful for the support and friendship received from the entire team. I would like to specially thank Mayler Martins for his contribution in this work and Alex Goulart, who helped a lot in making things happen in the bureaucracy field.

Moreover, I want to thank my mother Cristina, who gave all the support I need in several hard times. Also, I would like to thank my brothers Rodrigo and Otávio, who understood my absence in several moments. Specially, I would like to acknowledge the support and caring received from my wife Nivea, whose love made this work possible.

## TABLE OF CONTENTS

| LIST OF ABREVIATIONS                            | 7  |

|-------------------------------------------------|----|

| LIST OF FIGURES                                 | 8  |

| LIST OF TABLES                                  | 10 |

| ABSTRACT                                        | 12 |

| RESUMO                                          | 13 |

| 1 INTRODUCTION                                  | 14 |

| 2 BACKGROUND                                    | 17 |

| 2.1 Basic Concepts                              | 17 |

| 2.1.1 Boolean Equation                          | 17 |

| 2.1.2 Cofactors and Cube-cofactors              | 18 |

| 2.1.3 Function Order                            | 18 |

| 2.1.4 Unateness                                 | 19 |

| 2.1.5 Read-once Functions                       | 19 |

| 2.1.6 Truth Tables                              | 19 |

| 2.1.7 Binary Decision Diagram                   | 20 |

| 2.1.8 And-Inverter Graph                        | 22 |

| 2.2 Logic Synthesis Flow                        | 23 |

| 2.3 Technology Independent Logic Synthesis Flow | 24 |

| 2.3.1 Equation Factorization                    | 25 |

| 2.3.2 Using Boolean Decision Diagrams           | 25 |

| 2.3.3 | 3 Equation Composition             | 25 |

|-------|------------------------------------|----|

| 2.3.4 | 4 Three-level And-Not Networks     | 26 |

| 2.3.5 | 5 Using And-Inverter Graph         | 27 |

| 2.3.6 | 6 Comparing Methods                | 28 |

| 2.4   | Cost Estimation                    | 29 |

| 2.4.1 | 1 Optimization Targeting Area      | 29 |

| 2.4.2 | 2 Optimization Targeting Delay     | 30 |

| 2.4.3 | 3 Optimizing Multiple Targets      | 32 |

| 2.5   | Related Tools                      | 33 |

| 2.5.1 | 1 ABC Tool                         | 33 |

| 3     | PROPOSED METHOD                    | 34 |

| 3.1   | Building the Allowed Functions     | 35 |

| 3.2   | Create Single Variable Functions   | 38 |

| 3.3   | Combining and Evaluating Functions | 39 |

| 3.4   | Cost Functions and Implications    | 42 |

| 3.5   | Multiple Outputs                   | 43 |

| 3.6   | Different Costs for Inputs         | 44 |

| 3.7   | Disjoint Approach                  | 45 |

| 3.8   | Algorithm Complexity               | 47 |

| 4     | EXAMPLES                           | 48 |

| 4.1   | Main algorithm                     | 48 |

| 4.2   | Logic sharing example              | 49 |

| 4.3   | Multiple outputs example           | 51 |

| 4.4   | Different input weights example    | 52 |

| 5     | RESULTS                            | 54 |

| 5.1   | Main Algorithm                     | 54 |

| 5.2   | Multiple Outputs                   | 55 |

| 5.3   | Secondary Criterion                | 56 |

| <b>5.</b> 4 | Different Costs for Inputs                                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5         | 5 Disjoint Approach58                                                                                                                                         |

| 6           | CONCLUSION 59                                                                                                                                                 |

| RI          | EFERENCES 62                                                                                                                                                  |

| VISA<br>MÚL | PPENDIX SÍNTESE LÓGICA INDEPENDENTE DE TECNOLOGIA<br>NDO MÚLTIPLOS OBJETIVOS, APLICADA A FUNÇÕES DE<br>TIPLAS SAÍDAS, EMPREGANDO COMPOSIÇÃO FUNCIONAL DE AIGS |

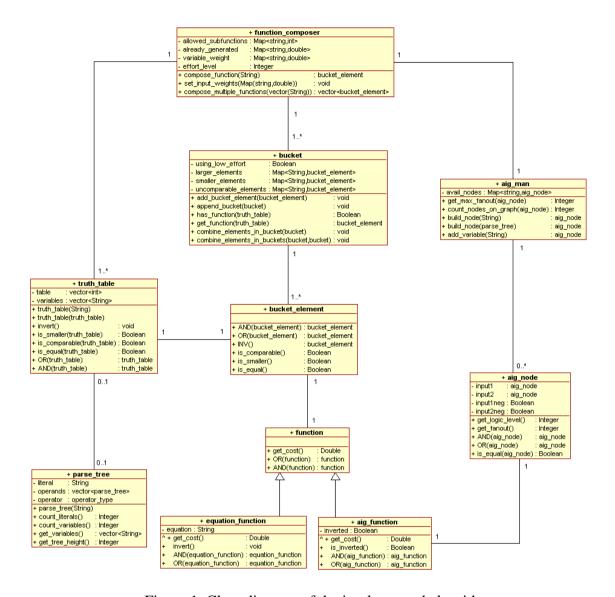

|             | NNEX DESCRIPTION OF THE CLASSES AND CLASS DIAGRAM OF PROPOSED METHOD71                                                                                        |

| Fu          | unction_Composer class71                                                                                                                                      |

| AI          | G_Manager class72                                                                                                                                             |

| AI          | G_Node class73                                                                                                                                                |

| Tr          | ruth_Table class74                                                                                                                                            |

| Pa          | rse_Tree class74                                                                                                                                              |

| Bu          | ıcket class75                                                                                                                                                 |

| Bu          | icket_Element class76                                                                                                                                         |

| Fu          | unction class76                                                                                                                                               |

| Eq          | quation_Function class76                                                                                                                                      |

| AI          | G Function class77                                                                                                                                            |

#### LIST OF ABREVIATIONS

AIG And-Inverter Graph

AND Logic operation "and"

BDD Binary Decision Diagram

DAG Directed Acyclic Graph

FRAIG Functional Reduced And-Inverter Graph

NAND Negated logic operation "and"

NOR Negated logic operation "or"

NOT Inverted (Negated) Logic

OR Logic operation "or"

POS Product of Sums

ROBDD Reduced Ordered Binary Decision Diagram

RTL Register Transfer Level

SOP Sum of Products

TANT Three-level And-Not Networks

TT Truth Table

XNOR Negated exclusive-or operation

XOR Exclusive-or operation

## LIST OF FIGURES

| Figure 2.1. BDD representing the function in Table 2.3                                    |

|-------------------------------------------------------------------------------------------|

| Figure 2.2. BDD representing the same function than BDD from Figure 2.1, but with a       |

| different variable ordering                                                               |

| Figure 2.3. ROBDD representing the same function than (a) BDD from Figure 2.1. and        |

| (b) BDD from Figure 2.2                                                                   |

| Figure 2.4. Sample of AIG for the function represented by the equation F=A*!B*C 22        |

| Figure 2.5. Sample of AIG representing the same function but described as (a) F=          |

| A*B+C and (b) $F=(A+C)*(B+C)$ .                                                           |

| Figure 2.6. Diagram representing the logic synthesis flow and its inputs and outputs 23   |

| Figure 2.7. Pseudo-code for the Equation Composition algorithm. (REIS, 2009) 26           |

| Figure 2.8. Pseudo-code of the AIGs construction by the FRAIG method                      |

| (MISHCHENKO 2005)                                                                         |

| Figure 2.9. Small circuit showing two paths from input C to output Q, represented as      |

| Path 1 (dashes) and Path 2 (dots)                                                         |

| Figure 2.10. A circuit long path from G to Q and a possible splitting of this circuit in  |

| three parts, (a), (b) and (c)                                                             |

| Figure 2.11. Same circuit path presented in Figure 2.10, including the hypothetical cost  |

| to the gates                                                                              |

| Figure 2.12. Same circuit presented in Figure 2.9 presenting costs in the inputs and      |

| gates                                                                                     |

| Figure 3.1. Diagram presenting how the AND and OR operations are applied to the           |

| functions during composition                                                              |

| Figure 3.2. The (a) AND operation and the (b) OR operation over two AIGs, generating      |

| a new one                                                                                 |

| Figure 3.3. The pseudo-code of the algorithm                                              |

| Figure 3.4. The pseudo-code of the build allowed sub-functions method                     |

| Figure 3.5. The vector with all distinct cofactors and cube-cofactors for the target      |

| function f=A*B+C                                                                          |

| Figure 3.6. The complete vector with all allowed sub-function                             |

| Figure 3.7. Diagram presenting how the AND and OR operations are applied to               |

| function representations during composition. The numbers in brackets indicates the        |

| algorithm step order                                                                      |

| Figure 3.8. The pseudo-code of the combining sub-functions method                         |

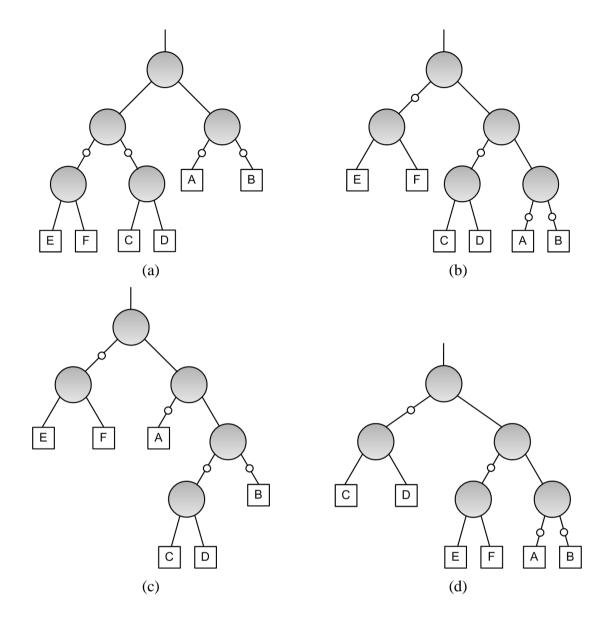

| Figure 3.9. (a) An AIG resulting for the function from the truth table presented in table |

| 3.10 and (b) another AIG for the same function, presenting the same number of nodes       |

| but a smaller graph depth                                                                 |

| Figure 3.10. (a) An AIG resulting for the function from the truth table presented in      |

| Table 3.11 without considering the inputs costs and (b) another AIG for the same          |

| function, presenting the same number of nodes but a smaller graph depth as it considers the costs in Table 3.12 |

|-----------------------------------------------------------------------------------------------------------------|

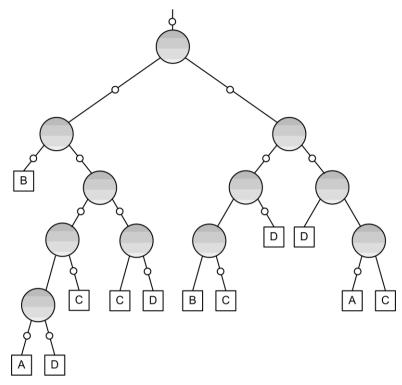

| Figure 4.1. The AIG built by running ABC followed by FRAIG, for the equation (4.1).                             |

| Figure 4.2. The AIG built by the proposed method for the equation (4.1)                                         |

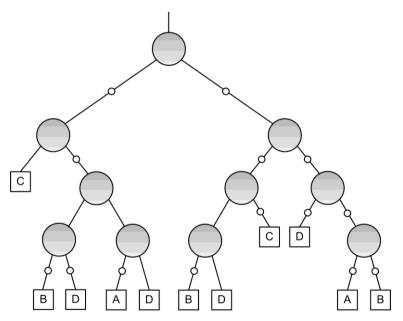

| Figure 4.4. The AIG built by running the proposed method for Equation 4.2. Notice the                           |

| circled node which presents fanout larger than one                                                              |

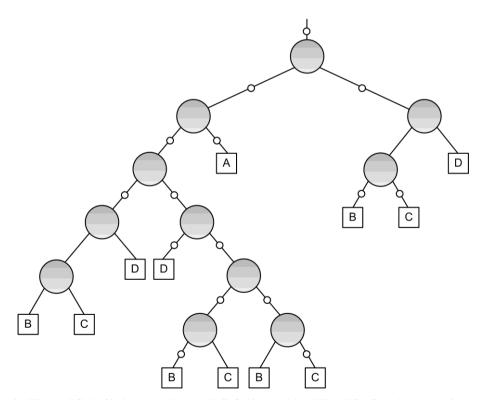

| Figure 4.5. The AIGs built by running the proposed method for (a) Equation 4.3 and (b)                          |

| Equation 4.4, one at a time                                                                                     |

| Figure 4.6. The AIGs built by running the proposed method for Equation 4.3 and                                  |

| Equation 4.4, both at the same time in multiple outputs mode                                                    |

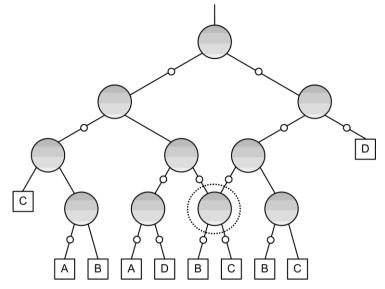

| Figure 4.7. The AIGs built by running the proposed method for the function represented                          |

| by Equation 4.5 and different input costs presented in Table 4.3. (a) for cost 1, (b) for                       |

| cost 2, (c) for cost 3 and (d) for cost 4                                                                       |

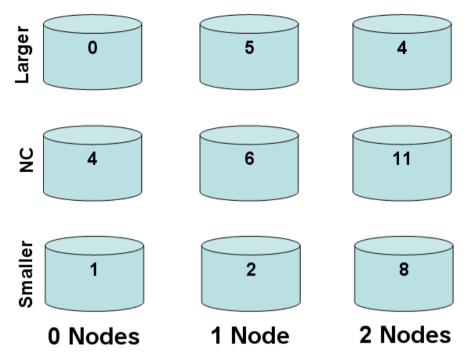

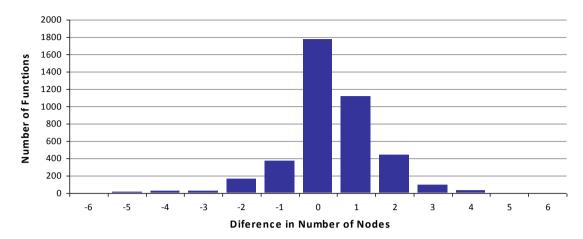

| Figure 5.1. The distribution of number of nodes gained by the proposed method when                              |

| compared to the ABC + FRAIG method, when applied to the input functions from set                                |

| A. Negative values represent advantage to ABC + FRAIG, while positive values                                    |

| represent advantage to the proposed method                                                                      |

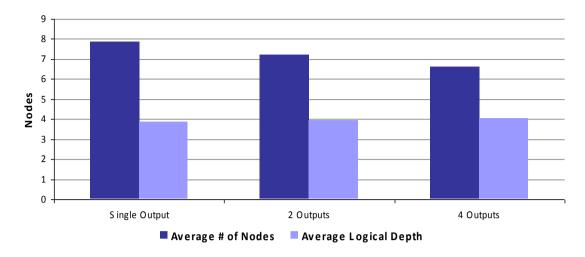

| Figure 5.2. The impact of grouping functions in order to perform the multiple outputs                           |

| algorithm in terms of average number of nodes and in terms of average logical depth                             |

| decrease, when applied to the input functions from set A                                                        |

| bettered, when approve to the imputioned from out the first out of                                              |

## LIST OF TABLES

| Table 2.1: Sample of truth table for the XOR function                                         | 19 |

|-----------------------------------------------------------------------------------------------|----|

| Table 2.2: Relation between the number of inputs, number of bits and number of                |    |

| integers required to store this information in both 32 and 64 bits architectures              | 20 |

| Table 2.3: Truth table for Q=A*B+C equation.                                                  | 20 |

| Table 2.4: Comparison between properties of the discussed methods                             | 29 |

| Table 2.5: The Logical Depth (Cost) of each path in the subcircuit presented in Figure        | •  |

| 2.12.                                                                                         |    |

| Table 3.1: Truth table for the equation $F = (A+C)*(B+C)$                                     | 36 |

| Table 3.2: Cofactors of the target function 01010111                                          | 37 |

| Table 3.3: Cube-cofactors of the cofactors of the target function $Q = A*B+C$                 | 37 |

| Table 3.4: AND operations applied over the cofactors and cube-cofactors resulting of          |    |

| previous steps                                                                                |    |

| Table 3.5: OR operations applied over the cofactors and cube-cofactors resulting of           |    |

| previous steps                                                                                | 38 |

| previous steps                                                                                | 39 |

| Table 3.7: OR (+) and AND(*) operations applied over the one variable functions               | 41 |

| Table 3.8: OR operations applied over the cofactors and cube-cofactors resulting of           |    |

| previous steps                                                                                | 41 |

| Table 3.9: OR operations applied (+) and AND(*) operations applied over the one               |    |

| variable functions (o nodes functions) with the 1 node functions                              | 41 |

| Table 3.10: Truth table for the equation $Q = A*B+C+D$ .                                      | 42 |

| Table 3.11: Truth table for the equation $Q = !A*B*!C*!D+!A*C*D$                              | 44 |

| Table 3.12: Costs for the inputs in the proposed example                                      | 44 |

| Table 4.1: Truth table for the equation                                                       |    |

| $Q = ((!B*!C*D) + (B*!C*!D) + (!A*C*D) + (A*!B*!D)) \dots$                                    | _  |

| Table 4.2: Truth table for the equation $Q = !B^*!C^*D + !A^*(B^*C^*D + !D^*(B^*!C + !B^*C))$ | 50 |

| Table 4.3: Costs used as inputs costs to the AIG construction algorithm.                      | 52 |

| Table 5.1: Comparison of And-Inverter Graphs generated by ABC + FRAIG and the                 |    |

| proposed method for set A of input functions.                                                 |    |

| Table 5.2: Evaluation of multiple outputs result for groups of 2 or 4 functions compar        |    |

| to single output as well                                                                      |    |

| Table 5.3: Comparison of And-Inverter Graphs generated by Equation Composition +              | -  |

| FRAIG and the proposed                                                                        |    |

| Table 5.4: Comparison of And-Inverter Graphs generated by Equation Composition +              | -  |

| FRAIG and the proposed                                                                        |    |

| Table 5.5: Inputs Cost vectors used during this test.                                         | 57 |

| Table 5.6: Comparison of And-Inverter Graphs generated by the proposed method                 |    |

| either ignoring or not the inputs cost                                                        | 57 |

| Table 5.7: Comparison of And-Inverter Graphs generated by the proposed method in |   |

|----------------------------------------------------------------------------------|---|

| both regular and disjoint efforts                                                | 3 |

|                                                                                  |   |

#### **ABSTRACT**

The use of design automation tools has allowed complex projects to reach feasible time-to-market and cost parameters. In this context, logic synthesis is a critical procedure in the design flow. The technology independent step (part of the logic synthesis which is performed regardless any physical property) is traditionally performed over equations. The development of new multi-level optimization algorithms has recently shifted towards the use of And-Inverter-Graphs (AIGs). The number of nodes and the graphs depth in AIGs present better correlation with resulting circuit area and delay than any characteristic of other representations. In this work, a technology independent synthesis algorithm that works on top of an AIG data structure is proposed. A novel approach for AIG construction, based on a new synthesis paradigm called functional composition, is introduced. This approach consists in building the final AIG by associating simpler AIGs, in a bottom-up approach. The method controls, during the graphs construction, the characteristics of final and intermediate graphs by applying a cost function as a way to evaluate the quality of those AIGs. The goal is to minimize the number of nodes and the depth of the final AIG. This multi-objective synthesis algorithm has presented interesting features and advantages when compared to traditional approaches. Moreover, this work presents a method for AIGs construction for multiple output functions, which enhances structural sharing, improving the resulting circuit. Results have shown an improvement of around 5% in number of nodes when compared to ABC tool.

**Keywords:** Logic Synthesis, And-Inverter Graph, Design Automation, CAD, Digital Circuits, Logic Gates, Design Flow, Technology Mapping

## Síntese lógica independente de tecnologia visando múltiplos objetivos, aplicada a funções de múltiplas saídas, empregando composição funcional de AIGs

#### **RESUMO**

O emprego de ferramentas de automação de projetos de circuitos integrados permitiu que projetos complexos atingissem time-to-market e custos de produção factíveis. Neste contexto, o processo de síntese lógica é uma etapa fundamental no fluxo de projeto. O passo independente de tecnologia (parte do processo de síntese lógica, que é realizada sem considerar características físicas) é tradicionalmente realizado sobre equações. O desenvolvimento de novos algoritmos de otimização multi-nível recentemente migrou para o emprego de And-Inverter Graphs (AIGs). O número de nodos e a altura de um grafo apresentam melhor correlação com os resultados em área e atraso de um circuito, se comparados com as características de outras formas de representação. Neste trabalho, um algoritmo de síntese lógica independente de tecnologia, que funciona sobre uma estrutura de AIGs, é proposto. Uma nova abordagem para a construção de AIGs, baseada no novo paradigma de síntese chamado de composição funcional, é apresentado. Esta abordagem consiste em construir o AIG final através da associação de AIGs mais simples, em uma abordagem bottom-up. Durante a construção do grafo, o método controla as características dos grafos intermediários e finais, a partir da aplicação de uma função de custo, como forma de avaliação da qualidade desses AIGs. O objetivo é a minimização do número de nodos e da altura do AIG final. Este algoritmo de síntese lógica multi-objetivo apresenta características interessantes e vantagens quando comparado com abordagens tradicionais. Além disso, este trabalho apresenta a síntese de funções com múltiplas saídas em AIGs, o que melhora a característica de compartilhamento de estruturas, melhorando o circuito resultante. Resultados mostraram a melhora em torno de 5% em número de nodos, quando comparados com os resultados obtidos com a ferramenta ABC.

**Palavras-chave:** Síntese lógica, And-Inverter Graph, Automação de Projetos, CAD, Circuitos Digitais, Portas Lógicas, Fluxo de Projeto, Mapeamento Tecnológico.

#### 1 INTRODUCTION

The advances in the integration scale of electronic devices have increased drastically the complexity of developing an integrated circuit (IC). Therefore, Electronic Design Automation (EDA) tools and an adequate project approach are essential to enable engineers to meet project requirements in a feasible time and without increasing the project cost. One of the most frequently adopted approaches for developing Application Specific Integrated Circuits (ASICs) is the standard cell project flow. The standard cell flow is based on cell libraries, consisting on having a specific design for a predefined set of logic gates. This approach leads to reduce the design time because of the reuse of previous made layouts in different circuits and of different parts of the same circuit.

A standard cell design flow consists of a sequence of steps starting from an abstract description of the circuit and resulting in the entire circuit, with all its elements properly specified, placed and routed. A standard cell flow may be divided into two main parts: logic synthesis and physical synthesis. The logic synthesis is responsible for optimizing the original description of the circuit and selecting the most appropriate cells to describe it. The physical synthesis is responsible for placing and routing these cells in the circuit area.

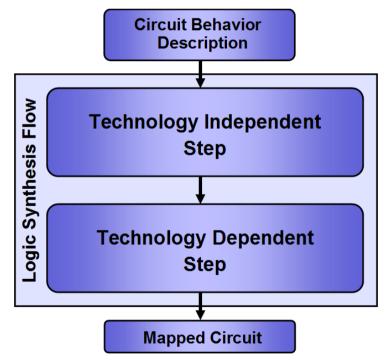

Traditionally, logic synthesis is usually performed in two steps: one performed over Boolean equations (regardless any physical property) and another where the resulting logic is mapped into a cell library or any other physical implementation. The first step is known as *technology independent step* and the second one is called *technology dependent step*.

During many years, the technology independent step was performed by equation factoring. Although it is a core procedure in logic synthesis, the only known optimality result for factoring (until 1996) was the one presented by Lawler in 1964, according to (HACHTEL, 1996). Heuristic techniques have been proposed for factoring and they have achieved high commercial success. This includes the quick\_factor (QF) and good\_factor (GF) algorithms available in the SIS tool (SENTOVICH, 1992). SIS (and others similar algorithms) is composed of several logic operations such as Decomposition Extraction, Factoring, Substitution and Elimination (HATCHTEL, 1996).

Most of the proposed factoring algorithms for technology independent logic synthesis take as input a sum-of-products (SOP) or a product-of-sums (POS). As SOP/POS forms are completely specified, the *don't cares* are not treated during the factoring but while generating the SOP/POS. Thus, the whole process is not completely optimized (not exact). However, algorithms that start from functional descriptions of the

functions and are able to handle *don't cares* are usually too slow to complete their execution for all functions of 4 variables (REIS, 2009).

Recently, factoring methods that produce exact results for functions that may be expressed without repeating literals (read-once factored forms) have been proposed (GOLUMBIC, 2001) and improved (GOLUMBIC, 2008). However, the proposed IROF algorithm is restrict to read-once functions. The Xfactor algorithm (GOLUMBIC, 1999) is exact for read-once forms and produces good heuristic solutions for functions not included in this category.

Recently, a novel approach based on function composition was proposed by (REIS, 2009). It works in a bottom-up way combining equations in order to generate the equation that implements the target function. The great achievement of this method is to provide good solutions in reasonable time, allowing optimizing multiple goals.

Other approach is the use of Binary Decision Diagrams (BDDs) for performing technology independent optimizations. The advantages of this approach rely mainly in the existence of well known algorithms for handling BDDs and the fact that BDDs do not depend of a previous equation description of the function. However, mapping circuits over a BDD is far more difficult than mapping over other Direct Acyclic Graphs (DAGs).

Three-level And-Not Networks (TANTs) were also considered as an alternative to equation factorization to perform technology independent optimization. The main advantage of TANT is the possibility of logic sharing and the fact that its description has as start point a function description. However, TANTs are not appropriate for implementing multi-objective optimizations (which consist in targeting more than one circuit characteristic at the same time, such as circuit area, delay propagation, etc.) and the characteristics of the TANT's graph are not strongly reflected in the resulting mapped circuit.

The factoring algorithms presented in (GOLUMBIC, 1999; REIS, 2009) do not include sub-expression reuse. The reuse of sub-expressions makes multi level representations, like TANT networks (LEE, 1978), more competitive than two-level expressions (MISCHENKO, 2003). The sub-expression reuse properties of multi level representations lead to another interesting use of these methods, which is multiple output synthesis. Supporting multiple functions allows the logic sharing of sub-expressions presented in more than one function, enhancing the circuit timing and consumption by reducing circuit area.

The development of new multi-level optimization algorithms has recently shifted towards the use of AIGs (MISHCHENKO, 2006). The use of AIG nodes is justified as it is expected to produce better correlation with final area and delay once the circuit has been mapped to a target technology (MISHCHENKO, 2006). This advantage, when comparing to using equations, comes from: (1) the fact that AIGs are multi-level representations, which allows sharing of nodes; and (2) the AIG node is a simple structure, which keeps correlation with area as all nodes have homogeneous simple granularity. However, a recent work (JOSWIAK, 2008) has shown that for small circuits there is still room for area gains with respect to AIG based tools. In this sense, there is a need for a Boolean algorithm for AIG rewriting.

The title of this work, "Multiple objective technology independent logic synthesis for multiple output functions through AIG functional composition", may be explained as follows:

- Multiple objective: consider a cost function with more than one parameter, in order to improve more than one characteristic that reflects improvements in the resulting circuit. In this work, number of nodes followed by graph height;

- Technology independent logic synthesis: step on the logic synthesis flow which is performed regardless any physical property;

- For multiple output functions: able to support several functions at a time, enhancing logic sharing.

- Through AIG functional composition: build functions as And-Inverter Graphs in a bottom-up approach.

The main purpose of this work is to propose a method to perform algorithmic logic synthesis using AIGs (due to the characteristics previously mentioned) associated with the new synthesis paradigm called *functional composition* (REIS, 2009). The approach proposed herein consists of constructing AIGs from association of simpler ones, in a bottom-up approach. The method controls, during the graphs construction, the characteristics of final and intermediate graphs by applying a cost function as a way to evaluate the quality of those AIGs (the cost function may reflect only the number of nodes, graph height or an association of these two criteria). This work also discuss the possibility of considering initial costs for the function variables, which may be used to represent the different arrival time of signals in a circuit and, therefore, that a given input must be favored in detriment of others. Moreover, an approach for handling multiple output functions during the function composition is proposed, presenting good results, especially when compared to handling each input separately. A post processing algorithm for duplicating logic in case of extremely large node fanouts makes the circuits resulting from this approach feasible.

Chapter 2 presents the basic concepts regarding logic synthesis and a short comparison among the most frequently adopted approaches, besides discussing briefly cost estimation fundamentals. Chapter 3 presents the proposed algorithm for AIG composition, describing each step of the main algorithm and detailing the characteristics for special situations such as optimizing multiple aspects of the resulting circuit and optimizing multiple output circuits. Chapter 4 presents examples of AIGs constructed by the proposed method and comparisons to other methods. The results are presented and discussed in Chapter 5. This chapter also compares the results from the proposed method with the results from the function composition method applied to equations (instead of AIGs). Moreover, the results from the proposed method are compared to the ones from the approach of using ABC (running equation factoring, using "good\_factor" from SIS, and building the AIGs using the FRAIG algorithm, which is also embedded in ABC). Chapter 6 presents the conclusion of this work and discusses the next steps for this research. In the annex the class diagram and a short description of all classes are presented.

#### 2 BACKGROUND

This chapter presents the basic concepts and the state of the art of the subjects of interest in this work. Section 2.1 discusses Boolean equations, the concept of cofactors, cube-cofactors and read-once functions. Moreover, it presents truth tables, binary decision diagrams (BDDs) and and-inverter graphs (AIGs). This review is important to understand the basis of the state of the art algorithms and the proposed method's characteristics.

Sections 2.2 and 2.3 present general aspects of the logical synthesis flow and detail the state of the art of the most frequently approaches adopted to perform the technology independent synthesis step. Moreover, in the end of Section 2.3, a comparison between these methods is performed. This comparison is part of the motivation of this work since any of the presented methods is able to provide all the desirable qualities. Finally, Section 2.4 presents the concept of cost estimation for a solution and the approaches for targeting area, delay or both. Cost estimation is an important concept since this work aims to improve multiple aspects of the resulting circuit.

#### 2.1 Basic Concepts

#### 2.1.1 Boolean Equation

A Boolean function describes how to determine a Boolean output based on some logical calculation performed over Boolean inputs. An equation is one representation of a function, which may also be described as a Binary Decision Diagram (BDD) or as a Truth Table (TT), for instance. Every representation of a function may be classified as canonical or non-canonical. A representation is said to be canonical if every function will always be described exactly in the same way. Examples of canonical representations are BDDs and TTs (as long as the variables ordering are the same). Usually, equations are non-canonical representations of a function; therefore, the same function may be described by different equations. For instance, equations (2.1) and (2.2) represent exactly the same function. However, there is a way to represent an equation in a canonical way, which is the SOP representation. An equation is composed of literals and operators. A literal is an instance of a variable (positive literal, for instance "A") or its complement (negative literal, for instance "!A"). Operators are AND ("\*\*"), OR ("+") and NOT ("!").

$$F=A*B+C (2.1)$$

$$F=(A+C)*(B+C)$$

(2.2)

#### 2.1.2 Cofactors and Cube-cofactors

A Shannon Decomposition is a method to represent any Boolean function as the sum of two sub-functions of the original one. A cofactor is a sub element of a Shannon Decomposition generated by either setting the value of a given variable to "0" or to "1", When a cofactor is generated for a function F by setting a variable v to "0", it is called the negative cofactor of the function F with respect to variable v.

For instance, equation (2.3) presents a function F represented by it's two sub elements, one related to x and the other one related to !x. There are the positive and negative cofactors of the F function in x, respectively.

$$F = x * F_x + !x * F_{!x}$$

(2.3)

A cofactor with respect to a given variable is obtained by setting the variable to one (positive cofactor) or to zero (negative cofactor), eliminating then the variable from the function. For example, consider the function (2.4).

$$F=(A*C)+(B*C)+(!A*B*D)$$

(2.4)

The positive cofactor with respect to the variable A (which is generated by setting A to one) is:

$$F_{(A=1)} = C + (B*C)$$

(2.5)

While the negative cofactor with respect to the variable A (which is generated by setting A to zero) is:

$$F_{(A=0)} = (B*C) + (B*D)$$

(2.6)

A cube-cofactor is obtained when setting more than one variable to a fixed logic value. In other words, a cube-cofactor is a cofactor from a cofactor. The cube-cofactor of the function presented in (2.4) with respect to A=0 and B=1 is presented in (2.7)

$$F_{(A=0, B=1)} = C + D$$

(2.7)

#### 2.1.3 Function Order

Two Boolean functions may be compared and classified according to their relative order. Considering G = F1 + F2:

- $F_1$  is larger than  $F_2$  if  $F_1 = G$  and  $F_1 \neq F_2$

- $F_1$  is smaller than if F2 if F2 = G and  $F_1 \neq F_2$

- $F_1$  **not comparable** to  $F_2$  if  $F_1 \neq F_2 \neq G$

#### 2.1.4 Unateness

Boolean function variables may be classified according to their unateness. A function F is said to be positive (negative) unate in a variable v if the positive cofactor of v in F is larger (smaller) than the negative cofactor of v in F. If the positive and negative cofactors are not-comparable, the function F is said to be binate in v. Therefore:

- F is positive unate in v if  $F_{v=1}$  is larger than  $F_{v=0}$

- F is negative unate in v if  $F_{v=1}$  is smaller than  $F_{v=0}$

- F is binate in v if  $F_{v=1}$  is not comparable to  $F_{v=0}$

#### 2.1.5 Read-once Functions

A function F is called read-once if it can be represented as a factored form in which each variable appears only once. In other words, a function is said to be read-once if there is a factored form of it that do not present any repeated literal.

If a function F can be represented through a read-once formula, all the partial sub-equations in the formula correspond to functions that are cube cofactors of F. As each variable appears as a single literal, they can all be independently set to non-controlling values, which makes only one literal disappear at a time. This way, any sub-equation (or sub-set) of F can be obtained by assigning non-controlling values to the variables to be eliminated.

#### 2.1.6 Truth Tables

A truth table (TT) is another way to represent Boolean functions. It consists in a table containing columns for all inputs and for the output of the function. Each line of the table consists in one combination of values for the inputs. For instance, the XOR function of two inputs is presented in Table 2.1.

Table 2.1: Sample of truth table for the XOR function

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 0       | 1       | 1      |

| 1       | 0       | 1      |

| 1       | 1       | 0      |

If two TTs present the same inputs in the same order, they will only vary on the output column. Therefore, a representation of a TT must only present the data of this column and the input names and ordering. The output column of the TT may be seen as a vector of Boolean values (for the example in Table 2.1, the output vector would be [0,1,1,0]). The vector may also be described as an integer (again in the example in Table 2.1., the integer would be 0110 in binary representation, or 6, in decimal

representation). The number of bits of an integer may vary from architecture to architecture, but usually they are limited to 32 or 64 bits. If the number of lines in the TT (and therefore the number of bits in the vector or the number of bits in the integer) is larger than the number of bits in a single integer, it is possible to use a vector of integers to store the TT data. Table 2.2 presents the relation between the number of inputs, number of bits and number of integers required to store this information in both 32 and 64 bits architectures.

Table 2.2: Relation between the number of inputs, number of bits and number of integers required to store this information in both 32 and 64 bits architectures.

| Inputs | Bits           | Integers   | Integers   |

|--------|----------------|------------|------------|

|        |                | (32 Bits)  | (64 Bits)  |

| 1      | 2              | 1          | 1          |

| 2      | 4              | 1          | 1          |

| 3      | 8              | 1          | 1          |

| 4      | 16             | 1          | 1          |

| 5      | 32             | 1          | 1          |

| 6      | 64             | 2          | 1          |

| 7      | 128            | 4          | 2          |

| 8      | 256            | 8          | 4          |

| 9      | 512            | 16         | 8          |

| 10     | 1024           | 32         | 16         |

| n      | 2 <sup>n</sup> | $2^{n}/32$ | $2^{n}/64$ |

#### 2.1.7 Binary Decision Diagram

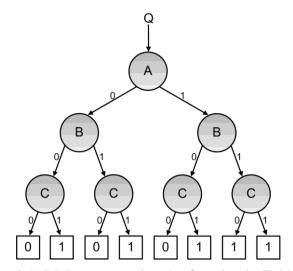

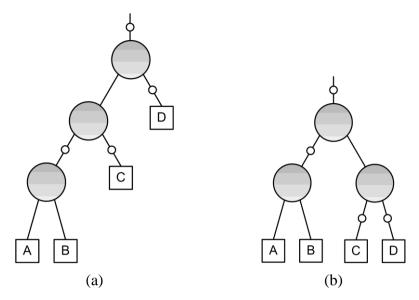

A Binary Decision Diagram (BDD) is a directed acyclic graph (DAG) which represents a Boolean function. The nodes contain the variables while the edges represent the values assumed by the variables. If no reduction rules are applied, the BDD is actually a tree, presenting the output node of the function it implements as the root and Boolean values '1' and '0' at the leaves. Figure 2.1 presents the BDD and the TT for the function represented by the equation Q=A\*B+C.

Table 2.3: Truth table for Q=A\*B+C equation.

| A | B | C | Q |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Figure 2.1. BDD representing the function in Table 2.3.

Considering the BDD without any reduction, it may be considered canonical if and only if the ordering of the variables is specified (for instance, if the variables are ordered lexicographically). For a different variable ordering (for instance, in Figure 2.2 the order is C, A and B, instead of A, B and C in Figure 2.1), the BDDs will differ.

Figure 2.2. BDD representing the same function than BDD from Figure 2.1, but with a different variable ordering.

The size of a BDD grows exponentially with the number of variables. Moreover, the time for building a BDD is also exponentially proportional to its number of variables. Therefore, several different techniques to reduce the size of a BDD were proposed. One of the most popular approaches is called ROBDD (which stands for Reduced Ordered Binary Decision Diagram). The ROBDD is a BDD with some specific improvements in building time (which does not increase the time for building the BDD). The most significant improvement is that if there are two identical nodes, they are collapsed.

Figure 2.3. ROBDD representing the same function than (a) BDD from Figure 2.1. and (b) BDD from Figure 2.2.

The advantage of using ROBDD instead of simple BDDs is the gain in size (number of nodes and complexity) without a significant penalty in building time. Moreover, it maintains the characteristic of being canonical, as long as the variable ordering is the same (as simple BDDs).

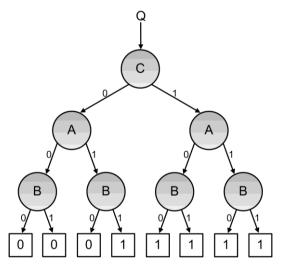

#### 2.1.8 And-Inverter Graph

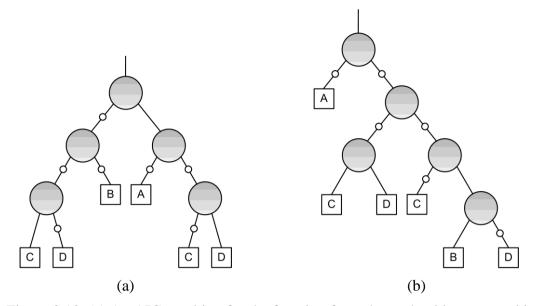

And-Inverter Graph (AIG) is another way to represent a Boolean function. An AIG is a directed acyclic graph (DAG) which is composed exclusively of two inputs AND gates and inverters. The inverters are usually represented as a special flag on the graph's edge and therefore all nodes on the graph represent two input ANDs. Figure 2.4 presents one AIG for the equation F=A\*!B\*C.

Figure 2.4. Sample of AIG for the function represented by the equation F=A\*!B\*C.

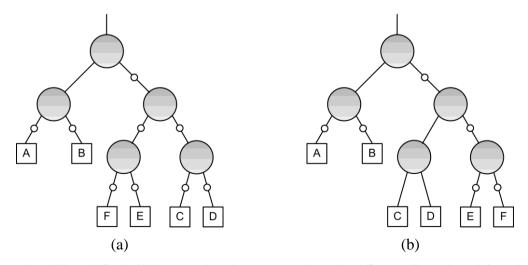

As AIGs are not canonical, different AIGs may represent the same Boolean function. Figure 2.5 presents three different AIGs for the same function (the output of the TT of this function is 01010111).

Figure 2.5. Sample of AIG representing the same function but described as (a) F = A\*B+C and (b) F = (A+C)\*(B+C).

#### 2.2 Logic Synthesis Flow

Logic synthesis is the process to generate a design implementation of a circuit from its abstract description (typically a structural or a RTL – register transfer level - description). Figure 2.6 presents a diagram representation of the logic synthesis steps and inputs.

Figure 2.6. Diagram representing the logic synthesis flow and its inputs and outputs.

The abstract description must inform mainly the logic behavior of the circuit to be synthesized and, therefore, must describe at least the set of inputs and outputs and the values of the outputs for all combination of the inputs (for combinational circuits) or must describe both the combination of the inputs and previous state information (for sequential circuits).

Considering only combinational circuits (in order to simplify the flow analysis), the logic synthesis is usually performed in two steps, one performed over Boolean equations (regardless any physical property) and another where the resulting logic is mapped into a physical cell library or other physical implementation.

The first step, called technology-independent step, may be either a two-level approach or a multi-level approach. The two-level approach consists of representing a function as a SOP, which means that the first level contains product terms (AND) and the second level logic contains sum terms (OR). It may also be necessary to employ inversions (NOT) to some of the inputs of the product terms.

The multi-level approach is composed of several logic operations such as Decomposition, Extraction, Factoring, Substitution and Elimination (HACHTEL, 1996). These operations may be either explicitly performed (SENTOVICH, 1992) or implicitly performed by other methods such as And-Inverter Graph (AIG) rewriting, as in the ABC tool (BERKELEY 2010). The result of this technology-independent step is an improved abstract description of the circuit. The typical cost function during this optimization is the total literal count of the factored representation of the logic function, although recent works proposed different cost functions considering multiple goals.

The second step, called technology-dependent step, uses the improved abstract description provided by previous step to build a DAG and perform technology mapping over this graph. The result of this step (and consequently, of the logic synthesis flow) is the circuit described as a network of gates in a given technology.

While the technology-independent step may be performed in the same way either in an ASIC or in a FPGA flow, the technology-dependent step must consider specific restrictions for each flow and, therefore, must present specific characteristics for ASIC and for FPGA flows. ASIC flow restricts technology mapping to the available cells in the cell library, while FPGA flow presents restriction regarding the maximum number of inputs of a given cell and other resources restrictions.

Some of the most used techniques for the technology-independent step are discussed in the next section.

#### 2.3 Technology Independent Logic Synthesis Flow

Technology independent synthesis consists in computing a representation of a given combinational circuit with optimized costs measured independently of the target technology. These costs may be related to the number of literals in an equation (e.g. number of literals and logic depth) or TANT (LEE 1978, PERKOWSKI 1990), BDD (YANG, 1999 – VEMURI, 2002) or AIG (KUEHLMANN, 2002, MISHCHENKO 2005, FIGUEIRO 2010) nodes (e.g. number of nodes and graph depth measured in nodes). In SIS (SENTOVICH 1992), the technology independent cost was based on literals. In more recent tools like ABC (BERKELEY 2010), the technology independent cost is based on AIG nodes.

The following sections discuss the most relevant algorithms types for performing technology independent synthesis.

#### 2.3.1 Equation Factorization

Equation Factorization was the first approach used in the technology-independent step in the logic synthesis flow. It consists of decomposing the equation in smaller and relatively independent elements, called factors. Equation 2.4 presents a simple equation in SOP form while equation 2.5 presents the same function implemented as a factorized equation.

$$F=A*B+A*C (2.4)$$

$$F=A^*(B+C) \tag{2.5}$$

The factorized equation always implements the same function than the original equation, but it usually presents a reduced number of literals once it groups equivalent elements. This enhancement in the equation is also reflected in the resulting circuit since it allows logic sharing of some equivalent elements.

This approach applies a sequence of optimization steps, having the goal of removing redundant nodes, finding better logic boundaries, discovering shared logic, and simplifying the node representations.

The method of factoring equations present several drawbacks, such as operating over equations and optimizing the number of literals, while technology mappers (CONG 1994, KUKIMOTO 1998) operate over DAGs and usually consider other cost functions than number of literals.

#### 2.3.2 Using Boolean Decision Diagrams

Although Equation Factorization may present good results in most AND-OR structures, it is not completely satisfactory when optimizing circuits which present some XOR behavior.

The BDD structure presents several characteristics that would be interesting to the technology independent optimization step (YANG, 1999 – VEMURI, 2002). These characteristics are:

- BDDs are canonical (when variables are ordered);

- BDDs allow logic sharing;

- Reductions on BDDs usually reflect reductions in circuit logic;

- Variable reordering on BDDs usually represent gain in final optimization.

The reason why BDDs are not widely used in the technology independent step in logic synthesis flow is that a BDD is not a good structure for technology mapping and it is not easy to convert the BDD to such structure.

#### 2.3.3 Equation Composition

Equation Composition is a novel approach (REIS, 2009) based on the construction of equations by associating simpler sub-equations. The objective of this method is to provide an equation that represents a good description of a given input function.

Figure 2.7 presents a description in pseudo-code of the algorithm. The method consists in first determining a set of allowed sub-functions, which will be the functions that are considered as possible partial elements of the target function (line 5). The second step is to create equations for all functions considering only one variable (line 7). The algorithm continues by combining these equations two by two until composing the final equation (lines 10 to 14). In order to evaluate whether a generated equation implements or not an allowed function (and therefore must be considered in further compositions). A TT is used for each equation, which specifies in a canonical way the functions (it was also possible to use BDDs in this point, but at (REIS, 2009) only TTs were used).

```

vector<factoredForms> optimizeEquation()

1

2

{

3

if (target_function==constant)

return constant;

compute_allowed_subfunctions();

bool sf ← false; //solutions found

7

sf=create_literals();

if (sf)

8

return solutions;

10

else for (int i=2; i<maxLit; i++) {</pre>

sf=fillBucket(i);

11

12

if (sf)

13

return solutions;

14

}

15

return "no solutions found";

16

```

Figure 2.7. Pseudo-code for the Equation Composition algorithm. (REIS, 2009).

This method is able to constructively control the characteristics of final and intermediate equations, allowing the adoption of secondary criteria other than the number of literals for optimization. The drawback of using Boolean equations in the optimization step is the difficulty of handling logic sharing.

#### 2.3.4 Three-level And-Not Networks

A Three-level And-Not Network (TANT) is a network composed exclusively of ANDs and inverters (NOTs) whose topology present only three levels (LEE, 1978, PERKOWSKI, 1994). It was proven (SASAO, 1982) that by using three logic levels it is possible to represent in a small quantity of nodes nearly all Boolean functions. On the other hand, using only two levels (such as in SOP or POS approaches) it affects drastically the logic size (SASAO, 1982).

Therefore, TANT networks are able to represent logic functions in a reduced form and there are several algorithms that perform this reduction efficiently and with low computational effort (LEE 1978, VINK 1978, PERKOWSKI 1990). Moreover, in opposition to other approaches, TANT networks are able to properly handle logic sharing by connecting several elements of a higher level to the same element in the lower level, increasing its Fan-In to more than 1.

However, one limitation of the TANT networks is exactly the number of levels (only three levels are possible). Moreover, the number of nodes in the TANT network is not directly correlated to the final circuit size (different fan-in nodes represent different

area in the resulting circuit), which both reduce the benefit of the nodes reduction (once it can actually represent an area increase of the circuit) and make difficult to apply TANT networks in multiple goals optimizations.

#### 2.3.5 Using And-Inverter Graph

AIGs are a multi-level logic representation, whose construction and size are proportional to the size of the circuit. The characteristics of the AIG are better correlated to the circuit characteristics than any other strategy mentioned in this chapter.

The best possible equation does not ensure the best AIG and, therefore, another AIG generated by a not-so-good equation may be the best AIG. This is the reason why recent logic synthesis applications are based in AIG and AIG optimization.

ABC (BERKELEY 2010) uses AIGs for optimizing the logic before performing any technology mapping. The AIG is first built and than AIG rewriting techniques are applied in order to reduce its number of nodes (MISHCHENKO 2006, BRUMMAYER 2006).

The rewriting procedure is a fast greedy algorithm that reduces the AIG size by iteratively selecting its subgraphs and replacing them with smaller pre-computed subgraphs, with the same functionality. The rewriting technique presented by (MISHCHENKO 2006) extends the work from (BJESSE 2004), by restricting rewriting to preserve the number of logic levels, using 4-feasible cuts instead of two-level subgraphs and by balancing AIGs using algebraic tree-height reduction.

It consists in enumerating all 4-feasible cuts and, for each cut, computing the Boolean function and search for its NPN-class in a hash-table. Fast manipulation of 4-variables functions is achieved by representing them as TT of 16 bits bit-strings. After this first reduction procedure, logic sharing between the new subgraphs and nodes already existent in the complete AIG is determined. In case of total or partial logic sharing, these new shared nodes are removed and the old subgraph is used instead. After trying all available subgraphs for the given node, the one that leads to the largest improvement at a node is used.

Another approach to improve AIGs is the Functional Reduced And-Inverter Graph (FRAIG) technique (MISHCHENKO 2005), which is also available in ABC and may be used to generate the first AIG before performing AIG rewriting procedures.

The FRAIG technique consists in a method for building AIGs from a factorized Boolean equation. Figure 2.8 present the pseudo-code for the FRAIG construction.

The FRAIG construction algorithm starts by using a structural hashing for ensuring that some equivalent nodes present the same behavior. This may be performed in one-level or in two-level modes, which consider input permutations - or even node permutations in two-level mode (KUEHLMANN, 2002) - and structural changes in the nodes. The second step is performed to detect functional equivalence by calling a SAT solver (it was used the MiniSat (EEN 2004)).

The resulting AIG is considerably reduced from normal AIGs without penalty performance, once the optimizations are performed in construction time. Moreover, the FRAIG gives the AIG a semi-canonical form, since most of the equivalences are detected and translated to the same AIG.

```

Aig Node * OperationAnd( Aig Man * p, Aig Node * n1, Aig Nodee * n2 )

Aig Node * res. * cand. * temp: Aig NodeArray * class:

/*** trivial cases ***/

if (n1 == n2) return n1:

if (n1 == NOT(n2)) return 0;

if ( n1 == const ) return 0 or n2;

if (n2 == const) return 0 or n1;

if ( n1 < n2 ) { /*** swap the arguments ***/

temp = n1; n1 = n2; n2 = temp;

/*** one level structural hashing ***/

res = HashTableLookup(p->pTableStructure, n1, n2);

if (res) return res;

res = CreateNode(p. n1. n2):

HashTableAdd( p->pTableStructure, res );

if (p->FlagUseOneLevelHashing) return res;

/*** functional reduction ***/

class = HashTableLookup( p->pTableSimulation, n1, n2 );

if ( class == NULL ) {

class = CreateNewSimulationClass( res );

HashTableAdd( p-> pTableSimulation, class ); return res;

for each node cand in class

if (CheckFunctionalEquivalence(cand, res)) {

AddNodeToEquivalenceClass( class, res ); return cand;

AddNodeToSimulationClass( class, res ); return res:

```

Figure 2.8. Pseudo-code of the AIGs construction by the FRAIG method (MISHCHENKO 2005).

#### 2.3.6 Comparing Methods

In this section, a simplified comparison between the presented methods for technology independent logic optimization in the logic synthesis flow is presented. Table 2.4 present a comparison of the characteristics of the presented methods.

The column "Start Point" compares the different approaches regarding the need of having either a Boolean equation in SOP form or may be any functional description. The next column, "Incompletely Specified Function" indicates if the method is able to handle Don't Care variables. The "Multiple Solutions" column indicate if the approach may return several results for a following evaluation and the "Multiple Objective" column indicate if it is possible to consider more than one goal while performing optimizations. The last column, "Logic Sharing", indicates if the method is able to provide logic sharing, whenever it is possible. In the case of BDDs, logic sharing may be possible depending on the specific method.

| Method                    | Start Point                      | Incompletely<br>Specified<br>Function | миниріе | Multiple<br>Objective | Logic<br>Sharing |

|---------------------------|----------------------------------|---------------------------------------|---------|-----------------------|------------------|

| Equation<br>Factorization | SOP                              | No                                    | No      | No                    | No               |

| Using BDD                 | Functional                       | Yes                                   | No      | No                    | Yes              |

| Equation<br>Composition   | Functional                       | Yes                                   | Yes     | Yes                   | No               |

| TANT                      | Functional                       | Yes                                   | Yes     | No                    | Yes              |

| Using AIG                 | SOP or<br>Factorized<br>Equation | No                                    | Yes     | Yes                   | Yes              |

Table 2.4: Comparison between properties of the discussed methods.

Although TANT networks present most of the desirable characteristics presented in Table 2.4, there are some other issues that must be considered when choosing the best approach for the technology independent step. One is the technology dependent step, i.e., the mapping algorithm that will be executed right after. There are several implemented solutions for mapping that consist in DAG / AIG covering, but are not able to properly cover a TANT if it presents large fan-in nodes. Moreover, as mentioned earlier, TANT size (number of nodes) does not correlate properly with resulting circuit area.

Moreover, none of the described methods is able to handle multiple equations and provide a logic sharing among these functions.

#### 2.4 Cost Estimation

#### 2.4.1 Optimization Targeting Area

Traditionally, improving circuit area is (and has always been) one key target for any well-succeeded logic synthesis tool. The reason for that is that any circuit area reduction usually reflects positively in several different optimization design goals, such as reducing circuit power consumption, reducing fabrication cost, reducing interconnections delay, improving circuit yield, among others. Moreover, circuit area is usually simpler to estimate and does not require any signal evaluation.

Therefore, all algorithms applied for circuit automatic synthesis usually present estimations of resulting circuit area. There are several ways to estimate area, and the best choice depends both on the information available and on the precision required at the evaluation moment. For instance, during the mapping stage (when the cells are chosen from a pre-characterized library) it is possible to use the precise area of the cells available and select the set of cells with the smaller area (although the effects of routing in circuit area are hard to estimate). In the technology independent step of the logical synthesis flow, where the cell area is unknown, a simpler estimation is used in order to

evaluate what is the best solution in terms of area. In this case the estimation will be performed according to the selected approach, but usually reflecting the number of nodes of a graph (in AIGs or BDDs), the number of nodes and their number of inputs (TANTs) or the number of literals and operations performed (equations).

#### 2.4.2 Optimization Targeting Delay

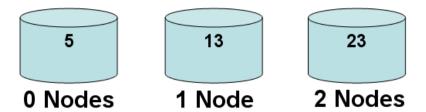

Although targeting area for circuit optimization has presented quality results for several years, recent works are including other goals for optimization in order to either improve or favor a given characteristic of their circuit.

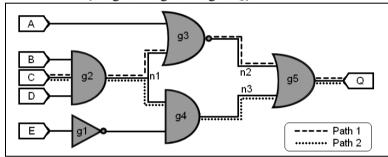

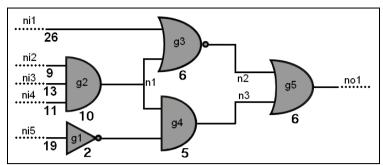

In a logic circuit, a path is a sequence of nets that are used to link two given points - usually linking one circuit input to one circuit output. Therefore, more than one path may exist linking a given input to a given output. Figure 2.9 shows an example of a small circuit containing two paths from input C to output Q, represented as Path 1 (dashes) and Path 2 (dots). Path 1 can be described as {C, g2, n1, g3, n2, g5, Q} while Path 2 can be described as {C, g2, n1, g4, n3, g5, Q}.

Figure 2.9. Small circuit showing two paths from input C to output Q, represented as Path 1 (dashes) and Path 2 (dots).

The effort (time) required to pass through the longest (slowest) path among all existent paths will be said to be the logical depth (complexity, cost) of this input regarding the output. Moreover, it is possible to define the logical depth of the complete circuit as the maximum of the logical depth among all inputs. There are several ways to measure logical depth, and the choice of the best measure depends both on the information available and on the precision required at the evaluation moment. For instance, during the mapping stage (when the cells are chosen from a pre-characterized library) it is possible to consider the delay of the cells, but it is hard to consider the interconnections delay. Another example is when the circuit is being globally placed and routed, where the interconnections parasites must be considered in order to obtain quality results. In the technology independent step of the logical synthesis flow, neither the cell information nor the interconnection information are available and, therefore, some simpler estimations are used in order to estimate the paths logical depth. These estimations depend on the structure used to perform the synthesis, but usually reflect the height of a graph (in AIGs or BDDs), the complexity of the elements (TANTs) or the operations performed (equations, which, in several times, are evaluated by the height of a parsing tree generated by the equation).

The logical depth is important because it is the expression of the time required to the output of the given circuit to reflect the changes in any of its inputs in a given instant. Therefore, it will affect directly the possible circuit operation frequency.

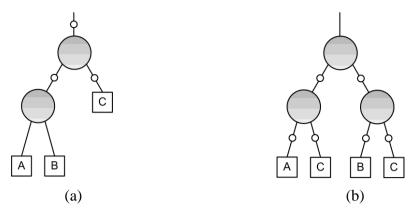

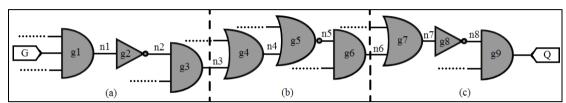

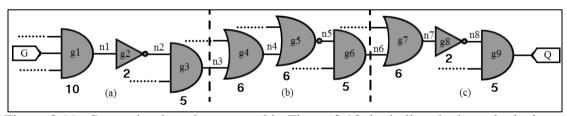

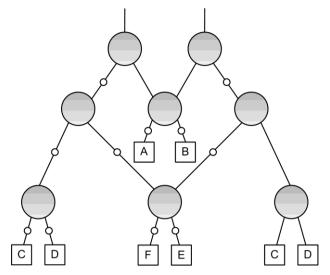

The existing algorithms for optimizing circuits are not able to handle hundreds of thousands cells at once (especially considering the amount of possible paths that this may generate and the interdependence of signals in the design. Therefore, splitting the circuit in subcircuits (as in divide-an-conquer approaches) is a common and efficient way to handle larger circuits in a feasible time. In this sense, several different strategies for circuit splitting were proposed (K-Cuts, KL-Cuts) and are not the focus of this discussion. Figure 2.10 presents a circuit long path from G to Q and a possible splitting of this circuit in three parts, (a), (b) and (c).

Figure 2.10. A circuit long path from G to Q and a possible splitting of this circuit in three parts, (a), (b) and (c).

The cost (delay) of the complete path may be considered as the sum of the costs attributed to each element in the path. Therefore, for any path starting in A, passing through B and ending in C, the cost function  $cf\{\{A\rightarrow C\}\}\$  will be  $cf\{A\rightarrow B\}+cf\{B\rightarrow C\}$ . For instance, Figure 2.11 presents the same path than Figure 2.10, plus adding hypothetical cost to all gates (and no cost to the interconnections, as if it was in the mapping step). The (a) portion of the path will present cost  $cf\{G\rightarrow g3\}=10+2+5=17$ , the (b) portion cost  $cf\{n3\rightarrow g6\}=6+6+5=17$  and the (c) portion cost  $cf\{n6\rightarrow Q\}=6+2+5=13$ . Therefore, the cost  $cf\{G\rightarrow Q\}=cf\{G\rightarrow g3\}+cf\{n3\rightarrow g6\}+cf\{n6\rightarrow Q\}=17+17+13=47$ .

Figure 2.11. Same circuit path presented in Figure 2.10, including the hypothetical cost to the gates.

Considering this transitiveness property of the cost function, it is possible to optimize a single portion of the circuit and it will improve the circuit as a hole (as long as all paths passing the given portion are considered together). For instance, consider the circuit presented in Figure 2.9 as a subcircuit, with hypothetical costs, as shown in Figure 2.12.

Figure 2.12. Same circuit presented in Figure 2.9 presenting costs in the inputs and gates.

The subcircuit presented in Figure 2.12 has the paths and costs presented in Table 2.5. The logical depth for each input to the subcircuit output is obtained by the maximum cost related to the input. Therefore, for *ni1* the cost is 38 (there is only one path associated) but for *ni2* it is 31 because it is the longest (more expensive) path associated to input *ni2*. The final cost of this subcircuit is the cost of the more expensive path of them all, which, in this case, is the cost of path 0, 38.

Table 2.5: The Logical Depth (Cost) of each path in the subcircuit presented in Figure 2.12.

| Path | Start | End  | Elements                     | Logical Depth (Cost) |

|------|-------|------|------------------------------|----------------------|

| 0    | ni1   |      | ni1, g3, n2, g5, no1         | 26 + 6 + 6 = 38      |

| 1    | ni2   |      | ni2, g2, n1, g3, n2, g5, no1 | 9+10+6+6= <b>31</b>  |

| 2    | 1112  |      | ni2, g2, n1, g4, n3, g5, no1 | 9 + 10 + 5 + 6 = 30  |

| 3    | ni3   | no1  | ni3, g2, n1, g3, n2, g5, no1 | 13 + 10 + 6 + 6 = 35 |

| 4    | 1113  | 1101 | ni3, g2, n1, g4, n3, g5, no1 | 13 + 10 + 5 + 6 = 34 |

| 5    | ni4   |      | ni4, g2, n1, g3, n2, g5, no1 | 11 + 10 + 6 + 6 = 33 |

| 6    | 1114  | m14  | ni4, g2, n1, g4, n3, g5, no1 | 11 + 10 + 5 + 6 = 32 |

| 7    | ni5   |      | ni5, g1, n4, g4, n3, g5, no1 | 19 + 2 + 5 + 6 = 32  |

Although optimizing any other path cost might be interesting in some situations, the main goal should be optimizing path 0 since its cost (38) is the cost that will be associated to *no1* for any evaluation of the next subcircuits that uses no1 as input.

#### 2.4.3 Optimizing Multiple Targets

Area optimization, for all mentioned in Section 2.4.1, continues to be an important goal in any circuit automatic synthesis process. Besides that, synthesizing a balanced circuit is desirable since the circuit delay will be its worst path delay. Moreover, other circuit characteristics such as the number of transistors in series are important and regarding more than one characteristic while synthesizing a circuit may provide much better results.

For instance, an algorithm for equation composition regarding both area (by controlling the number of literals in an equation) and number of transistors in series (by evaluating the sequence of operations in the resulting equation) is presented by Reis (REIS, 2009). Moreover, algorithms that optimize the number of nodes in a tree (either an AIG or a BDD) and try to generate a tree as balanced as possible are also available in the literature (YANG, 1999; MISCHENKO, 2006).

Hence, approaches targeting multiple objectives are rising in the last ten years. These approaches combine area and delay information either in a hierarchical improvement sequence (first improve area and among the results with smaller area obtain the one with smaller delay) or in a weighted cost function, attributing weights for each characteristic and reducing the resulting cost.

#### 2.5 Related Tools

#### 2.5.1 ABC Tool

ABC (BERKELEY, 2010) is a system for synthesis and verification for both combinational and sequential logic circuits appearing in hardware designs. ABC combines fast scalable logic optimization based on And-Inverter Graphs (AIG) with innovative algorithms for integrated sequential optimization and verification. ABC is meant to provide an experimental implementation of these algorithms and, at the same time, become a convenient programming environment for building similar applications in the future.

#### 3 PROPOSED METHOD

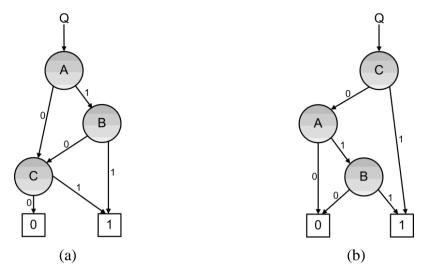

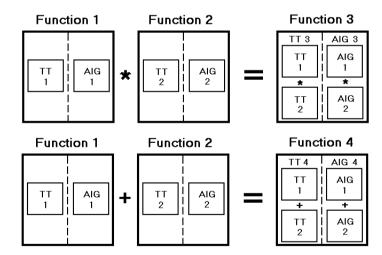

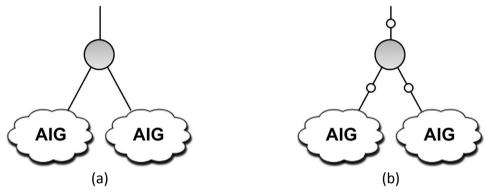

The method is based on combining AIGs of simpler functions in order to obtain AIGs of more complex functions until the target function is found. Functions are represented as pairs composed by one truth table (represented as an integer) and by one AIG node that is known to represent the function. The composition of the functions is performed by applying ANDs and ORs operations in both elements of the pair. Figure 3.1 illustrates this concept. There is a subtle consequence of using the double representation. Once the operations are made in both elements of the pair, the resulting pair will have a structural representation (AIG) whose functional representation (truth table) is also known. Notice that the double operations on the pair {AIG, Truth Table} are less expensive than computing the AIG from a truth table or vice-versa. This is a core observation for the understanding of the method. The AND operation and the OR operation on AIGs are very simple, as they imply only on the creation of a single node connecting the two AIGs, as shown in Figure 3.2. Notice that the OR operation in Figure 3.2. (b) is represented as a AND node with inverting signs on all three arcs, resulting in a De Morgan equivalent of an OR-operation node.

Figure 3.1. Diagram presenting how the AND and OR operations are applied to the functions during composition.

The truth table class is basically composed of the output vector of the function and the list of variables of the target function (ordered lexicographically). The AND and OR operations may be performed in a straightforward way on the output vector since the variable ordering is always the same in all functions. The AIG class consists basically in two pointers for other AIG object and one string used to store a variable

name. If the AIG object is a one variable function, it contains the variable name on the string and the two pointers are NULL. If it is not a one variable function, the string is empty and the pointers indicate the two AIGs associated to it. Since every AIG is composed only by AND nodes, the AND operation is performed by simply adding the two AIGs as children nodes of a new AIG node, which will correspond to the new graph. The OR operation is performed based on the DeMorgan property (A+B is equivalent to !(!A\*!B)) and therefore the new graph may be generated by including both children AIGs inverted and inverting its output as well.

Figure 3.2 presents how two AIGs are composed by AND and OR operations.

Figure 3.2. The (a) AND operation and the (b) OR operation over two AIGs, generating a new one.

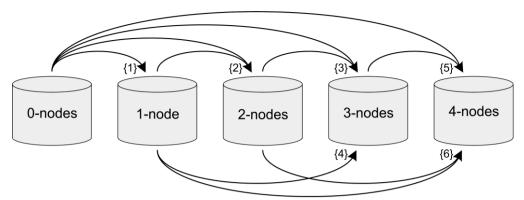

The proposed algorithm is performed in three steps. The first step is to construct a set of allowed sub-functions, to reduce the search space. The second step is to create the single variable function representations that will be used as the start point of the algorithm. From the single-variable function representations, the algorithm proceeds to combine existing functions to produce new associations that will be stored if they are in the list of allowed sub-functions and discarded otherwise. These steps are described in further detail in the following sections. The pseudo-code for the proposed method is presented in Figure 3.3.

```

AIG build_aig(TruthTable target_function) {

vector<TruthTable> allowed_functions = build_allowed_subfunctions(target_function);

create_one_variable_subfunctions(target_function);

while( solution not found) {

++bucket_number;

combine_subfunctions(allowed_functions, bucket_number);

}

return solution;

}

```

Figure 3.3. The pseudo-code of the algorithm.

#### 3.1 Building the Allowed Functions

In order to reduce the search space of sub-functions and, therefore, improve the performance and space required by the algorithm, a set of allowed sub-functions is

determined. The strategy to produce the allowed sub-functions is to compute the cofactors and the cube-cofactors of the target function. Moreover, it is necessary to add all the functions resulting of the AND-operation and the OR-operation between functions present in the list of cofactors and cube-cofactors. Also, the target function is also included as an allowed sub-function. Figure 3.4 presents the pseudo-code of the building allowed sub-functions algorithm.

```

vector<TruthTable> build_allowed_subfunctions(TruthTable target_function) {

vector<TruthTable> allowed_subfunctions = build_cofactors(target_function);

allowed_subfunctions += build_cube_cofactors(cofactors, target_function);

allowed_subfunctions += combine_cofactors(allowed_subfunctions);

return allowed_subfunctions;

}

```

Figure 3.4. The pseudo-code of the build allowed sub-functions method.

Suppose that the target function is given by Equation (3.1), and the truth table presented in Table 3.1. The cofactors are obtained by setting a single variable to a fixed logic value. For instance, making a=1 will result in cofactor b+c. The cube cofactors are obtained by setting more than one variable to a fixed logic value. For instance, making c=0 and b=1 will result in cube cofactor a. It is very important to notice that these operations are made directly into the truth table representation, before any AIG or equation is computed. Additionally, for the purpose of knowing if a function is allowed or not, only the functional representation (truth table) is stored. The complete set of distinct cofactors and cube-cofactors are listed in Figure 3.6.

$$F=(A+C)*(B+C)$$

(3.1)

First, as all truth tables may be represented by the output vector only, it is possible to represent the target function as 01010111.

|  | A | В | С | F |

|--|---|---|---|---|

|  | 0 | 0 | 0 | 0 |

|  | 0 | 0 | 1 | 1 |

|  | 0 | 1 | 0 | 0 |

|  | 0 | 1 | 1 | 1 |

|  | 1 | 0 | 0 | 0 |

|  | 1 | 0 | 1 | 1 |

|  | 1 | 1 | 0 | 1 |

|  | 1 | 1 | 1 | 1 |

Table 3.1: Truth table for the equation F = (A+C)\*(B+C).

The calculation of the negative and the positive cofactors for the "A" variable is performed as follows: The negative cofactor is built from the values from the output vector where "A" variable is '0' and these set is replicated for where the "A" variable is '1'. Therefore, since the values where "A" is '0' are 0101, after the replication the negative cofactor of the target function for "A" is 01010101. Similarly, the positive

cofactor of the target function for the variable "A" is built based on the values of the output when "A" is '1' and replicated for the values where "A" is '0'. Therefore, the positive cofactor for "A" is 01110111. The cofactors for the variables "B" and "C" are calculated in the same way and their values are presented in Table 3.2.

| Target   | A        |          | В        |          | С        |          |

|----------|----------|----------|----------|----------|----------|----------|

| Function | Neg.     | Pos.     | Neg.     | Pos.     | Neg.     | Pos.     |