# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# MATEUS PAIVA FOGAÇA

# Finding Placement-Relevant Clusters With Fast Modularity-Based Clustering

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microelectronics

Advisor: Prof. Dr. Ricardo A. da L. Reis Coadvisor: Prof. Dr. Andrew B. Kahng

### **CIP** — **CATALOGING-IN-PUBLICATION**

Fogaça, Mateus Paiva

Finding Placement-Relevant Clusters With Fast Modularity-Based Clustering / Mateus Paiva Fogaça. – Porto Alegre: PGMI-CRO da UFRGS, 2020.

88 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2020. Advisor: Ricardo A. da L. Reis; Coadvisor: Andrew B. Kahng.

1. Microelectronics. 2. EDA. 3. Physical Design. 4. Floorplanning. 5. Placement. 6. Modularity-Based Clustering. I. Reis, Ricardo A. da L.. II. Kahng, Andrew B.. III. Título.

### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGMENTS

I want to thank the many colleagues and friends have that contributed to my academic life. Many thanks to Cristina Meinhardt, Guilherme Flach, Jucemar Monteiro, Ygor Aguiar, Eder Monteiro, Gracieli Posser, Cristal Villalba, Geancarlo Abich, Marcelo Johann, among many others! I acknowledge my advisor, Prof. Ricardo Reis, for his guidance and commitment to my professional growth.

The current thesis is not the result of an "one man army" – It is the result of a collaboration that started in 2018 when Prof. Andrew Kahng has accepted me as a visiting Ph.D. student in his research group. I want to thank him for this lasting and profitable collaboration. I also thank Lutong Wang (UCSD), Mingyu Woo (UCSD) and Eder Monteiro (UFRGS) for putting their hard work in the project that resulted in the current thesis. I have written the remainder of the present document using the plural form to honor the effort of everyone that has contributed to the project.

I send a special acknowledgment to Prof. Paulo Butzen, not only for helping in the elaboration of the present document but also for reminding me that I have friends willing to help without any expectation of return. Thanks for the enormous technical and emotional support, Paulo! :-)

Finally, I acknowledge CAPES for the financial support throughout most of my Ph.D. and DARPA/Precision Innovations, Inc. for the financial support in the final months of my Ph.D.

#### **ABSTRACT**

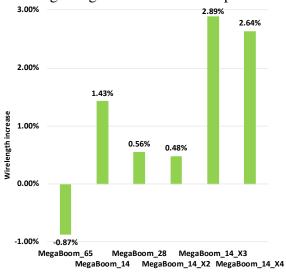

In advanced technology nodes, IC implementation faces an increasing design complexity as well as ever-more demanding design schedule requirements. This raises the need for new decomposition approaches that can help reduce problem complexity, in conjunction with new *predictive* methodologies that can help to avoid bottlenecks and loops in the physical implementation flow. Notably, with modern design methodologies it would be very valuable to better predict the final placement of the gate-level netlist: this would enable more accurate early assessment of performance, congestion and floorplan viability in the SOC floorplanning/RTL planning stages of design. In this work, we study a new criterion for the classic challenge of VLSI netlist clustering: how well netlist clusters "stay together" through final implementation. We propose the use of several evaluators of this criterion. We also explore the use of *modularity-driven clustering* to identify natural clusters in a given graph without the tuning of parameters and size balance constraints typically required by VLSI CAD partitioning methods. We find that the netlist hypergraph-to-graph mapping can significantly affect quality of results. Further, we empirically demonstrate that modularity-based clustering achieves better correlation to actual netlist placements than traditional VLSI CAD methods (our method is also  $2\times$  faster than use of hMetis for our largest testcases). Finally, we propose a flow with fast "blob placement" of clusters. The "blob placement" is used as a seed for a global placement tool that performs placement of the flat netlist. With this flow we achieve 20% speedup on the placement of a netlist with 4.9M instances with less than 3% difference in routed wirelength.

**Keywords:** Microelectronics. EDA. Physical Design. Floorplanning. Placement. Modularity-Based Clustering.

# Encontrando Grupos Relevantes ao Posicionamento com Agrupamento Baseado em Modularidade

#### **RESUMO**

Em nodos tecnológicos avançados, a implementação de circuitos integrados deve lidar com o aumento da complexidade dos projetos e também com cronogramas mais restritos. Portanto, cria-se a necessidade de novas abordagens de decomposição que ajudem a reduzir a complexidade do problema e novas metodologias preditivas para evitar gargalos e iterações no fluxo de implementação. Em metodologias de projeto modernas, seria útil predizer o posicionamento do circuito em nível de portas lógicas. Essa habilidade tornaria possível avaliar com maior precisão a planta baixa de um circuito em termos de desempenho e congestionamento ainda nas etapas de projeto da planta baixa e planejamento da descrição do circuito em nível de transferências de registradores de sistemas em chip. Este trabalho apresenta um novo critério de avaliação do problema clássico de agrupamento do circuito em nível de portas lógicas: avaliar se as portas lógicas de um grupo "permanecem próximas" ao longo do fluxo de implementação. Métodos para a avaliação desse critério são propostos. Além disso, o trabalho utiliza uma classe de técnicas de agrupamento chamada de agrupamento baseado em modularidade para identificar "grupos naturais" em um grafo, dispensando a necessidade de ajustes de parâmetros do algoritmo ou restrições de balanceamento de tamanho dos grupos, tradicionalmente necessários em técnicas de particionamento utilizadas por ferramentas de CAD (do inglês, computer-aided design). Os experimentos realizados mostram que o mapeamento do circuito de hipergrafo para um grafo afeta significativamente a qualidade dos resultados. Também demonstra-se empiricamente que grupos obtidos com técnicas de agrupamento baseadas em modularidade possuem uma maior correlação com o posicionamento quando comparadas com técnicas de particionamento tradicionalmente empregadas por ferramentas de CAD (A técnica utilizada neste trabalho também é 2× mais rápida que a ferramenta de particionamento tradicional hMetis nos maiores casos de teste). Por fim, é proposto um fluxo no qual se realiza posicionamento de grupos ("posicionamento de bolhas"). O "posicionamento de bolhas" é utilizado com ponto de partida ("semente") para uma ferramenta de posicionamento global. A ferramenta de posicionamento global utiliza a semente para realizar o posicionamento das portas lógicas do circuito. O fluxo proposto permite reduzir em 20% o tempo do posicionamento do circuito e a diferença nos resultados é menor que 3% em termos de comprimento de fios.

**Palavras-chave:** Microeletrônica. Automação do Projeto Eletrônico. Projeto Físico. Planta Baixa. Posicionamento. Agrupamento Baseado em Modularidade.

### LIST OF ABBREVIATIONS AND ACRONYMS

AS Alpha shape

BP "Blob placement"

CAD Computer-aided design

CH Convex hull

CL Number of clusters

CNM Clauset Newman Moore

CPU Central processing unit

CTS Clock tree synthesis

DARPA Defense Advanced Research Projects Agency

DBi Davies-Bouldin index

DBSCAN Density-based spatial clustering of applications with noise

DRC Design rule checking

DSP Digital signal processing

DT Delaunay triangulation

EDA Electronic design automation

ERC Electrical rule checking

GDSII Graphic Design System II

HDL Hardware description language

HLC Hierarchical Louvain clustering

HPWL Half-perimeter wirelength

I/O Input/output

IC Integrated circuit

IDEA Intelligent Design of Electronic Assets

ISPD International Symposium on Physical Design

LC Louvain clustering

LIFO Last in, first out

LVS Layout versus schematic

NP Nondeterministic polynomial

PDK Process design kit

RAM Random access memory

R&D Research and development

RTL Register-transfer level

SC Silhouette coefficient

SCAN Structural clustering algorithm for networks

SOC System on chip

SP "Seeded placement"

SPICE Simulation program with integrated circuit emphasis

TT Typical-typical corner

VHDL Very high speed integrated circuit hardware description language

VILE Very illegal

VLSI Very large scale integration

VRC Variance ratio coefficient

VT Threshold voltage

WL Wirelength

# LIST OF FIGURES

| Figure 2.1 VLSI design flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 A hyperedge (a) decomposed using the clique (b) and the star (c) models22                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 2.3 Alternative 2-way partitioning solutions of a circuit netlist (left). The first solution, obtained with $cut_1$ (upper), produces 2 partitions with 2 edges between them. The second solution, obtained with $cut_2$ (lower), produces 2 solutions with 4 edges between them                                                                                                                                                                                                                                    |

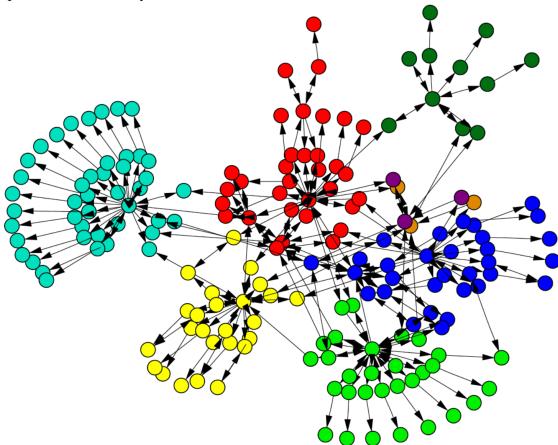

| Figure 2.4 Community structure for a set of webpages based on hyperlinks. Each color represents a community24                                                                                                                                                                                                                                                                                                                                                                                                              |

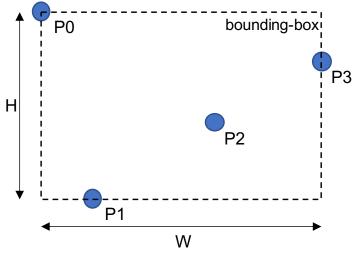

| Figure 2.5 The bounding-box of 4-pin net. The half-perimeter wirelength is the summation of the width (W) and height (H) of the bounding-box24                                                                                                                                                                                                                                                                                                                                                                             |

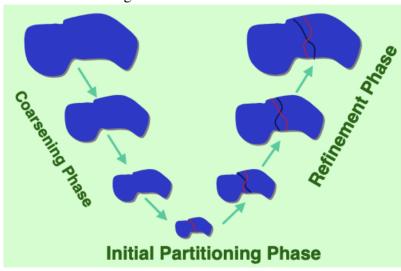

| Figure 3.1 The hMetis flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

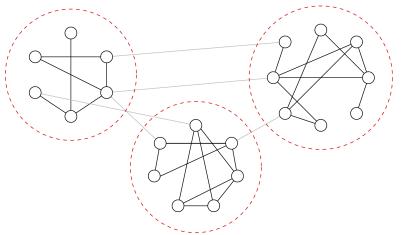

| Figure 3.2 Example of communities in a graph. Bold black lines are edges connecting vertices that belong to the same community; Gray lines are edges connecting vertices that belong to different communities and dashed red lines outline the communities.                                                                                                                                                                                                                                                                |

| Figure 3.3 Dendrogram of the clustering found by Newman for the "Karate club" benchmark. Numbers are the vertices indices and the shapes represent the ground-truth communities                                                                                                                                                                                                                                                                                                                                            |

| Figure 3.4 Runtime comparison between CNM and Wakita and Tsurumi36                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 3.5 Values of modularity for CNM and Wakita and Tsurumi. For the latter, different weighting schemes are shown                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 3.6 Outline of Louvain algorithm. The algorithm has two phases: <i>modular-ity optimization</i> and <i>community aggregation</i> . Each iteration of the two phases is called a <i>pass</i> .                                                                                                                                                                                                                                                                                                                       |

| Figure 3.7 A graph with two clusters, one hub and one outlier. The clusters are formed by vertices 0-5 and 7-12. Vertex 6 is a hub and vertex 13 is an outlier39                                                                                                                                                                                                                                                                                                                                                           |

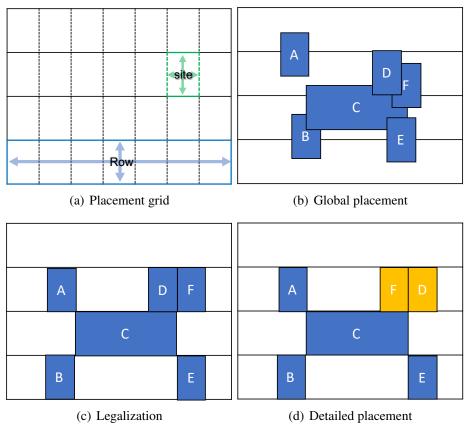

| Figure 3.8 (a) placement grid with a row outlined in blue lines and a site outlined in green; (b) global placement of a circuit with six instances; (b) legalization of the placement from (a) and (c) detailed placement where instances <i>D</i> and <i>F</i> are swapped                                                                                                                                                                                                                                                |

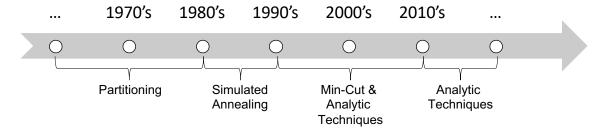

| Figure 3.9 Evolution of global placement techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

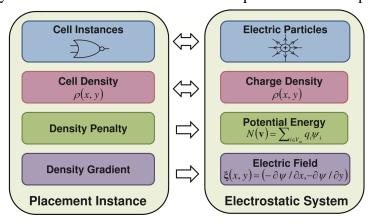

| Figure 3.10 ePlace modeling of the placement problem as an electrostatic system: instances are modeled as positive charges whose electric quantity is the instance area. Instance density is modeled as an electric force that spreads instances apart                                                                                                                                                                                                                                                                     |

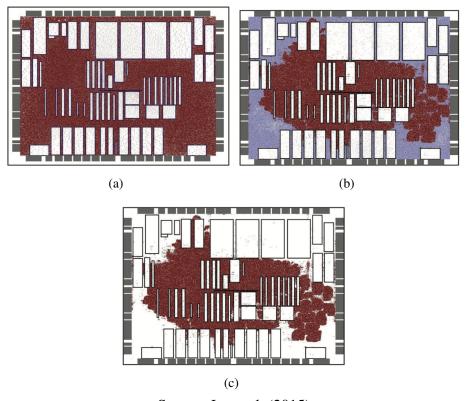

| Figure 3.11 ePlace result (a) without fillers, (b) with fillers and (c) after fillers are removed. Instances are drawn in red and fillers are drawn in blue                                                                                                                                                                                                                                                                                                                                                                |

| Figure 4.1 The process of "shelling" the cluster shape. Figure (a) shows a cluster with total cell area equal to $4.6 \times 10^3 \mu m^2$ and shape area equal to $23.0 \times 10^3 \mu m^2$ . Thus, the utilization of the cluster is equal to 20.2%. The cluster's "shell" is the set of red instances that are on the boundary of the shape. In (b), the cluster shape is recomputed after removing the shell from (a). The final shape has area equal to $11.6 \times 10^3 \mu m^2$ and utilization equal to $40.1\%$ |

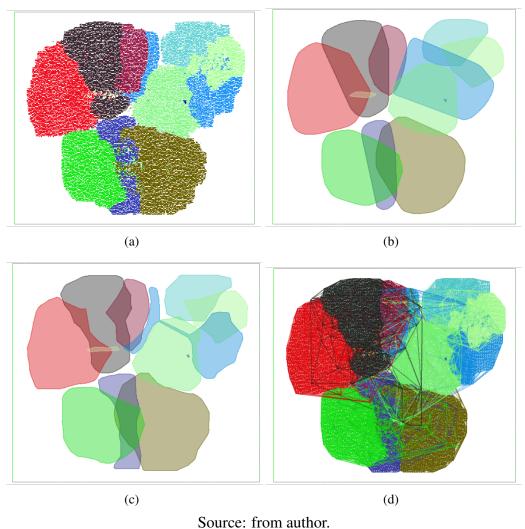

| Figure 4.2 Different approaches to correlate clusters with the placement for the                                                                            |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| circuit ispd18_test2 (MANTIK et al., 2018): (a) the placement with each                                                                                     |                |

| instance colored according to its cluster, followed by (b) the convex hulls; (c)                                                                            |                |

| the alpha shapes; and (d) the Delaunay triangulations of the clusters                                                                                       | 52             |

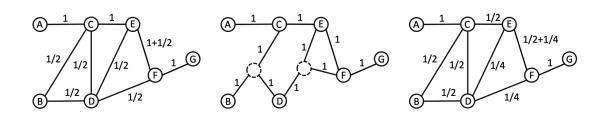

| Figure 4.3 Netlist decomposition.                                                                                                                           | 56             |

| Figure 4.4 Experiment 1 flow: Each netlist is modeled as a graph using the clique                                                                           |                |

| and star decompositions. In using clique, we compare five edge-weighting                                                                                    |                |

| approaches. Furthermore, we evaluate the use of I/O proximity weights in                                                                                    |                |

| the graph edges. Next, Louvain clusters the graphs. Finally, the clustering                                                                                 |                |

| solutions are evaluated in terms of DBi, VRC and SC.                                                                                                        | 57             |

| Figure 4.5 The average improvement of Lengauer w/o I/O proximity weights over                                                                               |                |

| C 1                                                                                                                                                         | 58             |

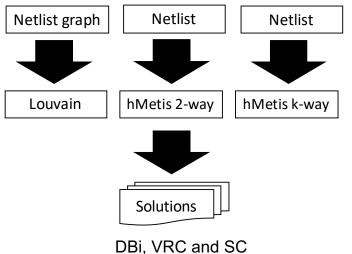

| Figure 4.6 Experiment 2 flow: Comparison of Louvain with hMetis 2-way and k-                                                                                |                |

|                                                                                                                                                             | 60             |

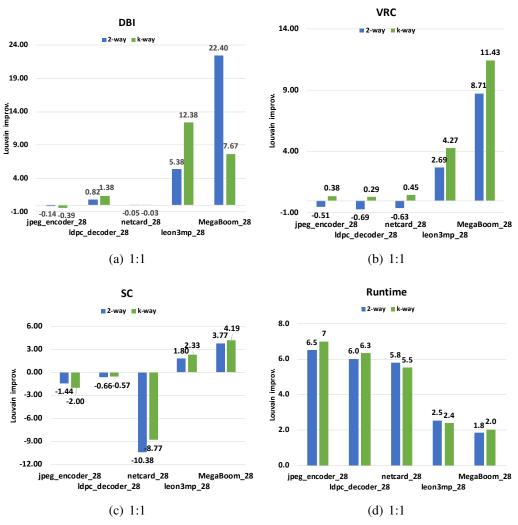

| Figure 4.7 Comparison between Louvain and hMetis in terms of DBi, VRC and SC.                                                                               | 62             |

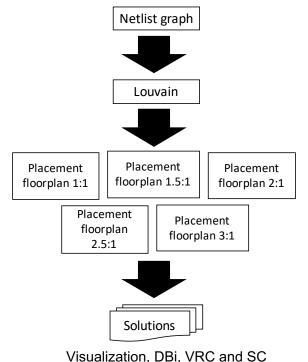

| Figure 4.8 Experiment 3 flow: The netlist graphs are clustered with Louvain and                                                                             | <i>J</i> _     |

| the clustering results are evaluated using placement under five floorplan as-                                                                               |                |

|                                                                                                                                                             | 63             |

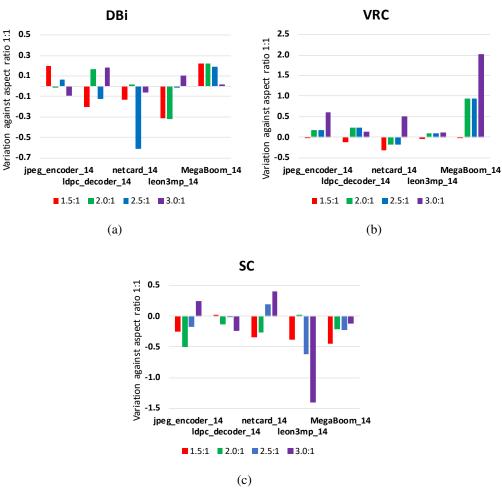

| Figure 4.9 The deltas of DBI, VRC and SC from the floorplan with aspect ratio 1:1                                                                           | ))             |

| to aspect ratios 1.5:1, 2:1,2.5:1 and 3:1. Values are normalized according to                                                                               |                |

|                                                                                                                                                             | 64             |

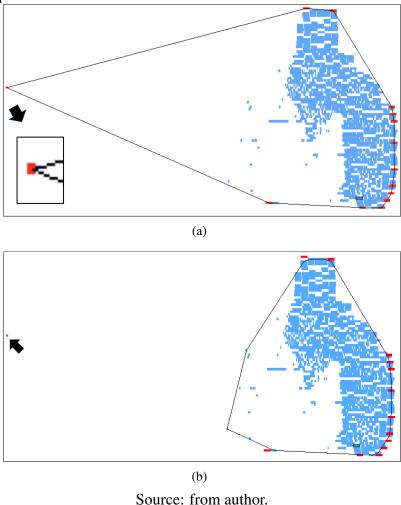

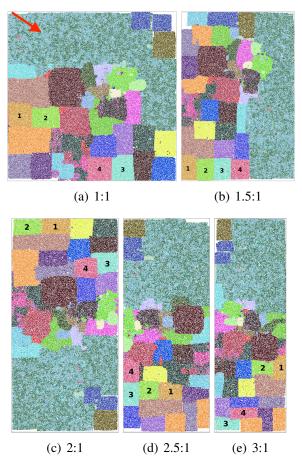

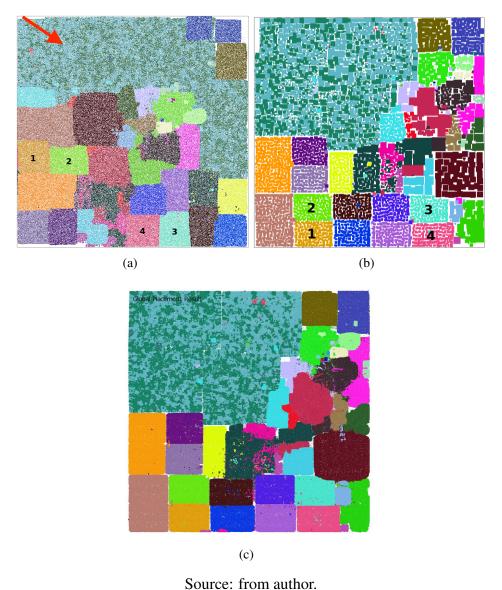

| Figure 4.10 Visual comparison of MegaBoom_14 with different aspect ratios and                                                                               | J <del>4</del> |

| same utilization. The images have been scaled for a better visualization. The                                                                               |                |

| red arrow highlights two blue clusters blending together                                                                                                    | 65             |

|                                                                                                                                                             | JJ             |

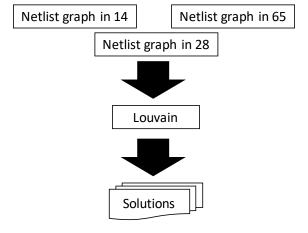

| Figure 4.11 Experiment 4 flow: We synthesize the same design in 14nm, 28nm and 65nm. Next, we cluster the netlist graphs using Louvain. Finally, we compare |                |

| the results visually and numerically using DBi, VRC and SC                                                                                                  | 66             |

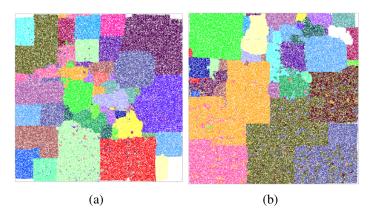

| Figure 4.12 Clustering results for (a) MegaBoom_28 and (b) MegaBoom_65. Com-                                                                                | 50             |

| pare with MegaBoom_14 from Figure 4.10(a).                                                                                                                  | 67             |

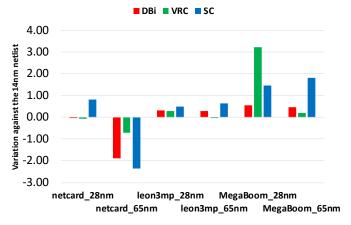

| Figure 4.13 Graphic representation of the Variation of DBi, VRC and SC for net-                                                                             | <i>J 1</i>     |

| card, leon3mp and MegaBoom when compared to their implementation in                                                                                         |                |

| 14nm. Values are normalized according to Equations (4.8)-(4.10)                                                                                             | 67             |

| Timil. Values are normalized according to Equations (1.0) (1.10)                                                                                            | <i>31</i>      |

| Figure 5.1 Experimental fast placement flow.                                                                                                                | 71             |

| Figure 5.2 MegaBoom_14: (a) flat placement, (b) "blob placement" and (c) "seeded                                                                            |                |

| placement".                                                                                                                                                 | 72             |

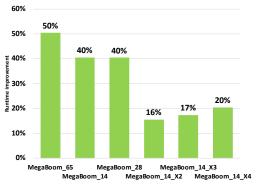

| Figure 5.3 Runtime improvement of "seeded placement" over flat placement                                                                                    | 74             |

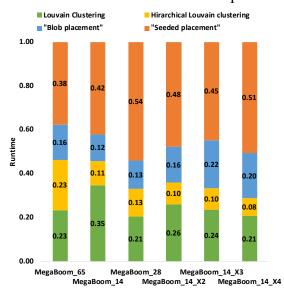

| Figure 5.4 Runtime breakdown of our fast placement flow.                                                                                                    | 74             |

| Figure 5.5 Post-route wirelength degradation of "seeded placement" over flat place-                                                                         |                |

| ment                                                                                                                                                        | 74             |

# LIST OF TABLES

| Table 3.1 Summary of the partitioning algorithms studied in this work and their     |    |

|-------------------------------------------------------------------------------------|----|

| category according to Alpert and Kahng (1995)                                       | 25 |

| Table 3.2 Summary of the community detection methods to be discussed in this        |    |

| Section                                                                             | 31 |

| Table 3.3 Global placement tools studied in our work and their taxonomy             | 44 |

| Table 4.1 Description of net weighting alternatives                                 | 54 |

| Table 4.2 Benchmarks and attributes.                                                |    |

| Table 4.3 Netlist tuning.                                                           | 59 |

| Table 4.4 Comparison among number of clusters (CL) and values of DBi, VRC,          |    |

| SC and runtime (CPU) for Louvain and hMetis. We highlight the best result           |    |

| for each evaluation criterion in each design                                        | 61 |

| Table 4.5 Variation of DBi, SC and VRC with aspect ratios 1.5:1, 2:1, 2.5:1 and 3:1 |    |

| compared to their implementation with aspect ratio 1:1. Values are normalized       |    |

| according to Equations (4.8)-(4.10).                                                | 64 |

| Table 4.6 Variation of DBi, VRC and SC for netcard, leon3mp and MegaBoom            |    |

| when compared to their implementation in 14nm. Values are normalized ac-            |    |

| cording to Equations (4.8)-(4.10)                                                   | 67 |

|                                                                                     |    |

| Table 5.1 Benchmark attributes and results of fast placement using "seeded place-   |    |

| ment." The runtime of fast placement is broken into Louvain clustering (LC),        |    |

| hierarchical Louvain clustering (HLC), "blob placement" (BP) and "seeded            |    |

| placement" (SP). Refer back to Table 4.2 for the instance complexities              | 73 |

# **CONTENTS**

| 1 INTRODUCTION                                                                                | 15   |

|-----------------------------------------------------------------------------------------------|------|

| 2 PRELIMINARIES                                                                               | 19   |

| 2.1 Design Flow of Digital Circuits                                                           | 19   |

| 2.2 Hyperedge Decomposition                                                                   |      |

| 2.3 Partitioning                                                                              | 22   |

| 2.4 Clustering and Community Detection                                                        | 22   |

| 2.5 Half-Perimeter Wirelength                                                                 |      |

| 3 LITERATURE REVIEW                                                                           | 25   |

| 3.1 VLSI Netlist Partitioning                                                                 | 25   |

| 3.1.1 Move-Based Approaches                                                                   |      |

| 3.1.1.1 hMetis                                                                                | 27   |

| 3.1.1.2 MLPart                                                                                |      |

| 3.1.2 Geometric Representation-Based Approaches                                               |      |

| 3.1.3 Combinatorial Formulations                                                              |      |

| 3.1.4 Clustering Approaches                                                                   |      |

| 3.2 Community Detection                                                                       | 30   |

| 3.2.1 Finding and Evaluating Community Structure in Networks (NEWMAN; GIR-VAN, 2004)          | 31   |

| 3.2.2 Fast Algorithm for Detecting Community Structure in Networks (NEWMAN, 2004)             | 32   |

| 3.2.3 Finding Community Structure in Very Large Networks (CLAUSET; NEW-MAN; MOORE, 2004)      | 33   |

| 3.2.4 Finding Community Structure in Mega-Scale Social Networks (WAKITA; TSURUMI, 2007)       |      |

| 3.2.5 Fast Unfolding of Communities in Large Networks (BLONDEL et al., 2008)                  |      |

| 3.2.6 SCAN: A Structural Clustering Algorithm for Network (XU et al., 2007)                   |      |

| 3.2.7 A Novel Similarity-Based Modularity Function for Graph Partitioning (FENG et al., 2007) |      |

| 3.2.8 Modularity-Driven Clustering for Hypergraphs                                            |      |

| 3.3 Placement                                                                                 |      |

| 3.3.1 Global Placement Tools                                                                  |      |

| 3.3.1.1 ePlace                                                                                | 46   |

| 3.3.1.2 RePlAce                                                                               |      |

| 4 FINDING PLACEMENT-RELEVANT CLUSTERS WITH FAST MODULARI                                      | ITY. |

| BASED CLUSTERING                                                                              | 49   |

| 4.1 Problem Definition                                                                        | 49   |

| 4.2 Methodology                                                                               | 50   |

| 4.2.1 Clustering Visualization                                                                |      |

| 4.2.2 Clustering Solution Evaluation                                                          |      |

| 4.2.3 Graph Model of the Netlist                                                              |      |

| 4.3 Experimental Setup and Results                                                            |      |

| 4.3.1 Evaluation of Different Graph Models                                                    |      |

| 4.3.2 Comparison With Traditional VLSI Clustering Methods                                     |      |

| 4.3.3 Robustness With Respect to Design Floorplan                                             |      |

| 4.3.4 Validation Across Technology Nodes                                                      |      |

| 4.4 Conclusion                                                                                |      |

| 4.4.1. Directions for Future Works                                                            | 60   |

| 5 FAST PLACEMENT OF INSTANCES WITH BLOB AND SEEDED PLACE | E- |

|----------------------------------------------------------|----|

| MENT                                                     | 70 |

| 5.1 Prototype Blob and Seeded Placement Flow             | 70 |

| 5.2 Experimental Setup and Results                       | 73 |

| 5.3 Conclusions                                          |    |

| 5.3.1 Directions for Future Works                        | 75 |

| 6 FINAL CONCLUSIONS                                      | 77 |

| REFERENCES                                               | 78 |

| APPENDIX A — PUBLICATIONS, AWARDS AND INTERNSHIPS        | 86 |

| A.1 Publications                                         | 86 |

| A.2 Awards                                               | 87 |

| A.3 Internships                                          |    |

| -                                                        |    |

#### 1 INTRODUCTION

Modern systems-on-chips (SOCs) aggregate billions of transistors within a single die, and drivers ranging from mobility to deep learning suggest that the Moore's-Law scaling of design complexity will continue (ITRS, 2015). EDA tools are continually challenged to incorporate new strategies to scale tool capacity without sacrificing quality of results or overall design schedule. Moreover, despite substantial R&D investments by the EDA industry, costs of IC design (engineers, tools, schedule) continue to rise. A recent keynote by Olofsson (OLOFSSON, 2018) asks, "Has EDA failed to keep up with Moore's Law?"

It is well-known that the ability to predict downstream outcomes of physical implementation algorithms and tools can enable reduction of loops (iterations) in the design flow, thus saving tool runtime and overall design schedule (KAHNG, 2018). The paradigm of physical synthesis is still the major success story along such lines, but this paradigm is now over two decades old. The recent DARPA Intelligent Design of Electronic Assets (IDEA) program (DARPA, 2018) highlights the cost crisis of modern IC design, and seeks to develop a framework capable of performing the complete RTL-to-GDSII flow without human interaction in 24 hours (OLOFSSON, 2018; DARPA, 2018). New tools that can help to avoid future failures (congestion, failed timing, etc.) while still in the early stages of floorplan definition or RTL planning appear mandatory to achieve the IDEA program goal.<sup>1</sup>

Clustering is a universal strategy for problem size reduction and for helping to enforce "known-correct" structure in solutions. Clustering has been used for many years in a wide range of EDA applications, including placement (ROY et al., 2006), clock tree synthesis (SHELAR, 2007) and, more recently, grouping of instances into different power domains (BLUTMAN et al., 2017). While many clustering methods for VLSI have been proposed, they have largely focused on *net cuts* (hyperedge min-cut, cluster perimeter, Rent parameter (RENTCON, 2008), etc.). Further, existing heuristics typically require design-dependent tuning and suboptimal heuristics. For instance, the well-known multilevel Fiduccia-Mattheyses (FIDUCCIA; MATTHEYSES, 1982) implementations hMetis (KARYPIS et al., 1997) and MLPart (CALDWELL; KAHNG; MARKOV, 2000) require *a priori* the target number of partitions as an input, and each aims to balance

<sup>&</sup>lt;sup>1</sup>This is a long-standing challenge to design productivity and the EDA industry. That so many commercial RTL planning and "RTL signoff" efforts have been made over the past 25 years (Tera Systems, Aristo, Silicon Perspective, Atrenta SpyGlass-Physical, Oasys, etc.) indicates the difficulty of this challenge.

the number of vertices or total vertex area across the partitions, which conflicts with the min-cut objective.

In this work, we seek to identify clusters of logic in a given gate-level netlist *that will remain together throughout the physical implementation flow*. Additionally, we propose a prototype flow that performs a fast placement of the netlist. This is a fundamentally different criterion than the min-cut or Rent-parameter criteria of previous clustering methods in VLSI CAD. We envision that such a clustering capability will help enable new predictors of performance and congestion during early physical floorplanning and RTL planning. For example, gates within the same cluster would be known to have spatial locality; this knowledge would then inform synthesis, budgeting and global interconnect planning optimizations. And, if combined with "blob placement" of clusters, fast evaluation of netlist and floorplan viability could be achieved.

Among the contributions of this work, we mention three broad aspects. The first aspect is the evaluation and application of *community detection* algorithms within the VLSI CAD context. Community detection is a comparatively recent class of graph clustering methods used to find densely-connected nodes in large networks such as those arising in social media, telecommunications and bioinformatics (FORTUNATO; HRIC, 2016). Community detection methods rely on metrics that help identify natural clusters inside graphs, notably, the *modularity* criterion (NEWMAN; GIRVAN, 2004). Our study centers on Louvain (BLONDEL et al., 2008), a well-known fast and efficient modularity-based graph clustering algorithm with near-linear runtime in sparse graphs. Louvain can cluster graphs with up to 700M edges within 12 minutes, using a single thread.

The second aspect is our study of new measures of the correlation between a netlist clustering method and the actual placement of netlists. The absence of previous work in this vein may be due to the fact that previous clustering techniques have aimed to drive placement algorithms instead of predicting them (i.e., the final evaluation of a clustering technique was the quality of the placement itself). We study three classical concepts from computational geometry to evaluate this correlation: *convex hulls* (CH), *alpha shapes* (AS), and *Delaunay triangulations* (DT) (BERG et al., 1997). The primary purpose of these techniques is to retrieve the geometric shape of a set of scattered points, a goal that correlates very closely to the concept of a cluster. To compare different clustering results, we apply the Davies–Bouldin index (DBi) (DAVIES; BOULDIN, 1979), Variance Ratio Criterion (VRC) (CALIńSKI; HARABASZ, 1974) and Silhouette Coefficient (SC) (ROUSSEEUW, 1987), which are traditionally used to evaluate how "well-

separated" clusters are. For spatial data, such as placements of standard-cell instances, our evaluation criteria measure (i) the distances from instances to the center of gravity of the clusters they belong and (ii) the distance among the center of gravity of clusters. In a "good" clustering solution, the ratio between (i) and (ii) is a small numeric value.

The third aspect is the proposal of a prototype flow that performs fast placement of clusters to predict the flat placement. In doing so, we feed a state-of-the-art analytic placement tool with a *cluster netlist* that is significantly smaller than the gate-level netlist. Then, we use the cluster locations to generate an initial placement for the gate-level netlist. Finally, we finish the placement with a fast call of incremental placement. We compare predicted and actual gate-level netlist placement in terms of routed wirelength with a leading commercial tool router.

Our contributions are summarized as follows.

- 1. We employ modularity-based clustering in conjunction with VLSI-relevant graph edge-weighting to predict groups of logic gates that will remain together through the stages of physical implementation without the need for user tuning.

- 2. We explore the use of convex hulls, alpha shapes, and Delaunay triangulations to visualize and measure the correlation between the netlist clustering and the "ground-truth" actual placement.

- 3. We adopt Davies–Bouldin index (DAVIES; BOULDIN, 1979), Variance Ratio Criterion (CALIńSKI; HARABASZ, 1974) and Silhouette Coefficient (ROUSSEEUW, 1987) as criteria to compare clustering results. These criteria are extensively used for evaluation of spatial clustering but have not been explored by the EDA community.<sup>2</sup>

- 4. We perform experiments showing 50% better clustering quality on average for Louvain (BLONDEL et al., 2008) versus the traditional VLSI netlist clustering tool hMetis (KARYPIS et al., 1997), with 2× faster runtime than hMetis for our largest benchmark.

- 5. We demonstrate an experimental flow that performs fast "blob placement" of clusters as a potential basis for future early-stage netlist and floorplan evaluation. Our flow can closely predict instances that remain together in the actual gate-level placement with a speed up of 50% compared to flat placement for a testcase with 1.2M

<sup>&</sup>lt;sup>2</sup>The silhouette metric has not been widely used in the VLSI CAD clustering literature, with (KAHNG; LI; WANG, 2016) being the only example of which we are aware.

instances and 20% speed up for a testcase with 4.5M instances.<sup>3</sup>

The remainder of the current thesis is organized as follows. Chapter 2 introduces the basic concepts for the understanding of this thesis. Chapter 3 gives an overview of the existing literature on VLSI partitioning, modularity clustering and placement. Chapter 4 presents our comparison between traditional VLSI clustering methods and modularity based clustering while Chapter 5 proposes our prototype "blob placement flow". In Chapter 6, we present our final remarks.

<sup>&</sup>lt;sup>3</sup>Note that the core motivation and contribution of our current work is to *rapidly predict* the placement. If instance placements can be quickly known, an expert designer is able to tune the flow setup (e.g., with small modifications to floorplan, density screens, grouping, etc.) to improve the quality of results or to fix timing and routability issues. In this context, our work provides a methodology to improve the outcomes and/or the turnaround time of the netlist-to-placement phase of the implementation flow. Additionally, our flow can be used to generate the actual placement in contexts where the quality of results can be sacrificed to reduce the placement runtime.

#### **2 PRELIMINARIES**

In this Chapter, our goal is to provide for the reader the fundamental background to understand the current thesis. We start reviewing the design flow of digital circuits in Section 2.1. In Section 2.2, we show how VLSI CAD algorithms represent the netlist hypergraph with graphs. Sections 2.3 and Section 2.4 define the concepts of partitioning and clustering. Finally, Section 2.5 presents wirelength estimation with half-perimeter wirelength. Readers with background on VLSI CAD literature may skip this Chapter.

## 2.1 Design Flow of Digital Circuits

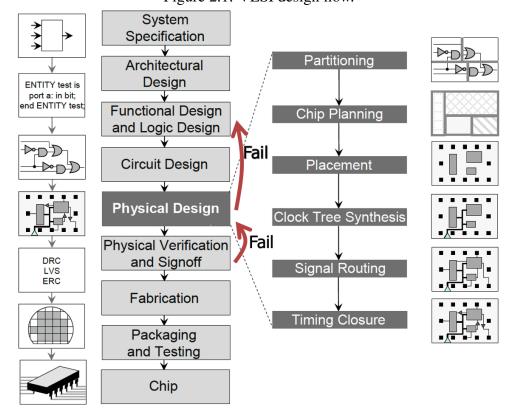

The VLSI design flow is a set of steps that transform the functional description of a system into geometric masks that allow the system to be manufactured as an integrated circuit. Each step is performed by teams of engineers with expertise in their field. Due to the tight design schedule, engineers rely on hundreds of licenses of foundry-qualified EDA tools and massively parallel servers. Figure 2.1 depicts the design flow according to Kahng et al. (2011).

Figure 2.1: VLSI design flow.

Source: Kahng et al. (2011).

The first step of the flow is the **system specification**. This step consists in defining the overall goals and requirements of the system in terms of functionality, performance and area. The production teams also decide what is the target technology for the product. Next, the **architectural design** determines how the system is going to meet the system specification in terms of analog and mixed-signal blocks, memory configuration, number of cores, DSPs, I/Os, IP blocks, die packing interface, power requirements, technology process choice, layer stacks choice, etc.

In the **functional and logic design**, the functionality and connectivity of each module in the architecture are defined. The high-level behavior of the system is modeled using hardware description languages (HDLs), such as Verilog and VHDL. These descriptions are validated in terms of behavior and timing using thorough simulations. After validation, *logic synthesis* tools translate the high-level description into a circuit. This is done by specifying the system description and a technology library and results in a list of signal nets and logic gates mapped to the technology (e.g. logic gates mapped to standard cells.) The result of this step is called *gate-level netlist*. However, some critical elements, such as RAMs and I/Os, have to be validated by SPICE simulations using transistor-level descriptions. Such descriptions are generated in the **circuit design**.

The **physical design** produces a geometric description of the design. Kahng et al. (2011) divide the physical design into six steps:

- Partitioning. Splits the flat netlist into smaller modules so they can be designed and analyzed individually. Partitioning allows algorithms that do not scale well to be applied in the modern and complex system-on-chip designs. Partitions can also be assigned to different teams and designed in parallel.

- Chip planning. Commonly referred to as floorplanning. Determines the area and location of the design modules. Also determines the location of I/O ports and macro blocks. The chip planning also is responsible for the realization of power and ground networks.

- **Placement**. Finds a location for each element of the netlist while trying to optimize an objective function. Common placement objectives include wirelength, timing, routability and power distribution. A review of placement algorithms is presented in Section 3.3.

- Clock tree synthesis (CTS). Performs the topology generation, buffering and routing of the clock network. The CTS usually tries to minimize the clock network power and latency given a skew target.

- Routing. Traces the signal paths using metal wires and vias.

- Timing closure. Optimizes the performance of the circuit using techniques such as sizing, cloning, buffering,  $V_t$  swapping, incremental-detailed placement and routing. Such optimizations are traditionally called after every step of the physical design.

Verification is the step that assesses whether the final layout meets the design specification and respects the technology rules. The verification is performed using extraction and analysis tools. The *formal verification* tool checks if the netlist from a given stage of the flow ("target") has the same functionality as a known "golden" netlist (e.g., pre-route netlist (target) vs. RTL (golden).) The *design rule check* (DRC) verifies geometric constraints such as minimum metal area and distance. The *layout versus schematic* (LVS) compares the functionality of the layout with the netlist generated in the logic design. The *electrical rule checking* (ERC) verifies whether the design respects fanout, slew and capacitance constraints and whether the power and ground distribution is well formed. Extraction tools derive the electric parameters of the design. These parameters are used by timing and power analysis tools to assess if the design meets the timing and power budgets. If the design does not pass in any of these verifications, the designers need to do incremental changes. These changes are often performed manually by designers as even small perturbations in the layout may create new violations.

Once the layout passes the verifications it is sent to the foundry for **fabrication**. In the foundry, the design is patterned using a lithographic process upon silicon wafers. Finally, the chips in the silicon wafer are diced and placed in **packages** and **tested**. The chips that pass the testing are ready to be commercialized.

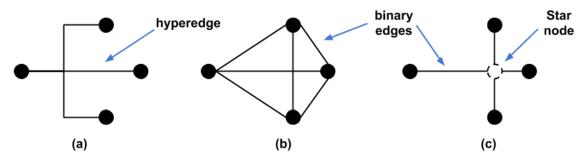

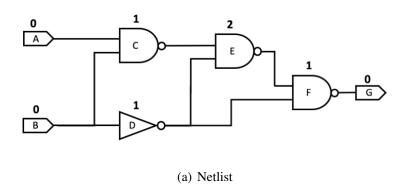

### 2.2 Hyperedge Decomposition

The circuit netlist is a hypergraph H(V,X) in which the nodes of the netlist (instances, macro blocks, ports) compose the set of vertices V and the signal nets compose the set of hyperedges X. However, many algorithms in the literature only work with graphs. Therefore, some models have been proposed to decompose the set of hyperedges into an equivalent set of edges E to represent the netlist using a graph G(V,E). The clique and star models depicted in Figure 2.2, are examples of decomposition models commonly used in placement algorithms (VISWANATHAN; CHU, 2004). In the clique

model every hyperedge is replaced by a complete graph (i.e., all vertices are connected among themselves by a binary connection) and the star model introduces an additional vertex connected to every other vertex by a binary connection.

Figure 2.2: A hyperedge (a) decomposed using the clique (b) and the star (c) models.

Source: from author.

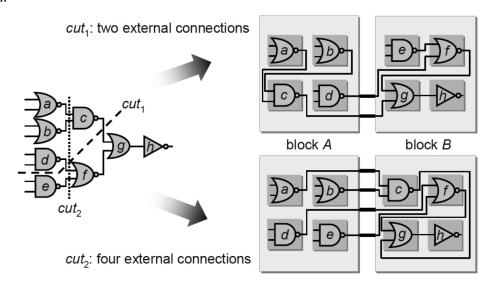

#### 2.3 Partitioning

In partitioning, the graph vertices are divided into groups, called *partitions*. The most common goal is to minimize the number of connections between partitions. Partitioning algorithms belong to a category called *min-cut partitioning*, where cut is the sum of the edge weights crossing between partitions. Figure 2.3 presents a netlist graph and two possible cuts. The solution of  $cut_1$  presents a better solution since it has only 2 connections between partitions while  $cut_2$  has 4 connections between partitions.

### 2.4 Clustering and Community Detection

Clustering, or cluster analysis, is a field that aims to divide a set of objects into homogeneous groups, called clusters (WIERZCHON; KLOPOTEK, 2018). Two objects belonging to the same cluster should have more *similarity* than objects belonging to different clusters (WIERZCHON; KLOPOTEK, 2018). Clustering has been applied to a wide range of applications in VLSI, like placement (ALPERT et al., 2005), CTS (HAN; KAHNG; LI, in press) and flop tray design (KAHNG; LI; WANG, 2016).

Community detection is a type of clustering in which the objects being clustered are vertices of a graph usually originated from social or biological networks (NEWMAN; GIRVAN, 2004). The similarity is given by the connections between vertices – the number of edges inside the clusters, which are referred to as *communities*, should be higher

Figure 2.3: Alternative 2-way partitioning solutions of a circuit netlist (left). The first solution, obtained with  $cut_1$  (upper), produces 2 partitions with 2 edges between them. The second solution, obtained with  $cut_2$  (lower), produces 2 solutions with 4 edges between them.

Source: Kahng et al. (2011).

than the number of edges spamming multiple clusters. Figure 2.4 depicts the outcome of the community detection algorithm of Newman and Girvan for a set of webpages (NEWMAN; GIRVAN, 2004). The color of each vertex denote the community the vertex has been assigned to and the edges represent hyperlinks between pages.

## 2.5 Half-Perimeter Wirelength

In the VLSI CAD tools, many optimization engines need to estimate wirelength efficiently. Many placement algorithms (and research) adopt the *half-perimeter wirelength* (HPWL) as an optimization goal and for solution quality measurement. HPWL is computed as follows. Consider the 4-pin net in Figure 2.5. The HPWL consists of the half-perimeter (summation of width and height) of the net pins' bounding-box. The half-perimeter can be computed in linear time, by just traversing all pins of the net once. Additionally, HPWL matches the minimum routed wirelength for nets with up to 3 pins.

Figure 2.4: Community structure for a set of webpages based on hyperlinks. Each color represents a community.

Source: Newman and Girvan (2004).

Figure 2.5: The bounding-box of 4-pin net. The half-perimeter wirelength is the summation of the width (W) and height (H) of the bounding-box.

Source: from author.

#### **3 LITERATURE REVIEW**

The scope of our present work spans three topics of interest: VLSI partitioning tools, community detection and placement. This Chapter presents a brief review of the literature and state-of-the-art on these topics.

## 3.1 VLSI Netlist Partitioning

Partitioning is extensively studied in VLSI research for many applications. For instance, one common strategy to cope with modern ICs complexity is to *decompose* the system into smaller logic and physical portions which can be implemented in parallel using partitioning. After implementation, these portions can be reassembled in a single die. Other applications include stacked voltage domain designs (BLUTMAN et al., 2017) and speed up of placement algorithms (ALPERT et al., 2005). In this Section, the literature on VLSI partitioning algorithms is studied following the taxonomy proposed by Alpert and Kahng (1995). Table 3.1 presents a summary of the partitioning algorithms studied in this work.

Table 3.1: Summary of the partitioning algorithms studied in this work and their category according to Alpert and Kahng (1995).

| Reference                       | Category                                  |  |

|---------------------------------|-------------------------------------------|--|

| Kernighan-Lin algorithm         |                                           |  |

| (KERNIGHAN; LIN, 1970)          |                                           |  |

| Fiduccia-Mattheyses algorithm   |                                           |  |

| (FIDUCCIA; MATTHEYSES, 1982)    | Move-based approaches                     |  |

| hMetis                          |                                           |  |

| (GEORGE; VIPIN, 1998)           |                                           |  |

| MLPart                          |                                           |  |

| (CALDWELL; KAHNG; MARKOV, 2000) |                                           |  |

| Barnes (1981)                   | Geometric representation-based approaches |  |

| Yang and Wong (1994)            |                                           |  |

| Blutman et al. (2017)           | Combinatorial formulations                |  |

| Rajaraman and Wong (1995)       | Clustering approaches                     |  |

| Alpert et al. (2005)            |                                           |  |

Source: from author.

## 3.1.1 Move-Based Approaches

Move-based approaches start from an initial arbitrary solution and try to improve it by iteratively swapping a single vertex from one partition to another or by swapping pairs of vertices belonging to different partitions. The core of these approaches is frequently inspired by the Kernighan-Lin (KERNIGHAN; LIN, 1970) and Fiduccia-Mattheyses algorithms (FIDUCCIA; MATTHEYSES, 1982).

The Kernighan-Lin algorithm has been introduced in 1970 to perform 2-way partitioning. The algorithm computes the cut improvement of swapping random pairs of vertices and stores the pair with best cut improvement. After being stored, the vertices of the pair are marked as *fixed*, i.e. cannot be selected again as candidates for swap. This process is repeated until all nodes become fixed. The algorithm then effectively swaps only the set of pairs that present the largest values of cut improvement. This is called a *pass*. After one pass, all vertices are unmarked as fixed. The algorithm stops when the gain seen after the pass is less than a threshold.

In 1982, Fiduccia and Mattheyses propose an extension to the Kernighan-Lin algorithm, called Fiduccia-Mattheyses, with multiple improvements: (i) the algorithm performs single-vertex swaps, allowing unbalanced unbalancing between partitions; (ii) support for hypergraphs; (iii) support for area constraints in partitions and (iv) faster selection of candidates to swap. While the overall flow is similar, the Fiduccia-Mattheyses cost function is modified. The gain of swapping a node from one partition to another is measured as:

$$\Delta G = FS(v) - TE(v) \tag{3.1}$$

where v is the vertex; FS(v) is the number of nets or (hyper) edges connected to v but not connected to any other vertex in the same partition, and TE(v) is the number of nets or (hyper) edges connected to v and not connected to any vertex from the other partition. Next, we discuss two Fiduccia-Mattheyses-based tools hMetis (KARYPIS; KUMAR, 1999) and MLPart (CALDWELL; KAHNG; MARKOV, 2000), widely used in academic and commercial flows.

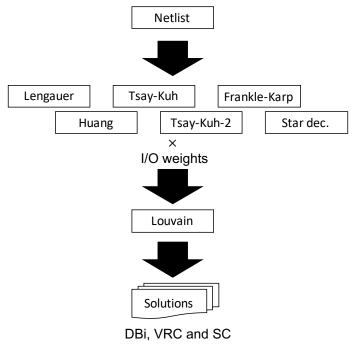

#### 3.1.1.1 hMetis

Karypis et al. propose a *multilevel* hypergraph partitioning algorithm called hMetis (GEORGE; VIPIN, 1998; KARYPIS; KUMAR, 1999). The flow of hMetis is composed of three phases: (i) coarsening phase, (ii) initial partitioning phase and (iii) refinement phase. In the *coarsening phase*, the size of the hypergraph is iteratively reduced by contracting vertices and edges. Karypis et al. study contracting schemes, called matching schemes and describe them in Karypis et al. (1997). Once the hypergraph is sufficiently coarse, the *initial partitioning* phase builds N random 2-way partitions and uses the Fiduccia-Mattheyses to refine each solution. In the end, the solution with the best mincut among all is chosen. In the *refinement phase*, the vertices and edges are iteratively uncontracted to obtain the original hypergraph. At each level, refinement algorithms are applied to improve the solution obtained in the initial partitioning phase. The hMetis flow is depicted in Figure 3.1.

Figure 3.1: The hMetis flow.

Source: George and Vipin (1998).

#### 3.1.1.2 MLPart

Caldwell et al. propose MLPart, a multilevel partitioning tool similar to hMetis but with improvements in the 2-way partitioning and in the coarsening scheme (CALD-WELL; KAHNG; MARKOV, 2000). The Fiduccia-Mattheyses implementation of ML-Part starts by putting all vertices in a single partition, a strategy called VILE ("very illegal") initial solution. The acceptance criterion for legal moves is relaxed, meaning that movements are accepted if they do not increase the balancing constraints. Their imple-

mentation and the gain of a movement is randomized in the first iterations. Caldwell et al. also implement a *LIFO Fiduccia-Mattheyses algorithm* (HAGEN; J.-H.; KAHNG, 1995) along with a "wiggling" strategy. For its multilevel partitioning, MLPart employs the strategy of edge coarsening from Alpert, Huang and Kahng (1997) and Karypis et al. (1997). Their edge coarsening scheme differs from previous works because it updates the graph continuously while clustering is performed. MLPart also adds balancing constraints when performing contraction of edges and vertices.

## 3.1.2 Geometric Representation-Based Approaches

This class is composed of partitioning algorithms that rely on the geometric embeddings of the netlist to achieve better partitioning results. Some algorithms represent the geometric embeddings with an adjacency matrix C, where each element  $C_{ij}$  is the sum of the edge weights connecting vertices i and j. Other methods use the Laplacian matrix L = C - M, where D is a  $N \times N$  diagonal matrix where N is the number of vertices in the netlist graph and each element  $D_{ii}$  is the degree of vertex i. Hall et al. show that the second eigenvector ( $\nu_2$ ) of the Laplacian matrix represents the 1D placement of the vertices with minimum squared wirelength (HALL, 1970). The graph can be divided into two partitions by sorting the vertices according to the entries of  $\nu_2$  and then assigning the first half of the vertices to one partition and the second half to the other. Later, Barnes (1981) and Alpert, Kahng and Yao (1999) extend this strategy to perform k-way partitioning.

#### 3.1.3 Combinatorial Formulations

Combinatorial formulations encompass partitioning methods based on formulations that can capture complex objective functions and constraints such as *network flow*. Yang and Wong (1994) apply network flow to perform 2-way min-cut partitioning. They propose a methodology to represent the netlist as a flow network and show how to perform balanced 2-way partitioning using a max-flow min-cut technique. More recently, Blutman et al. (2017) show how to extend this formulation to comprehend timing and layout information to perform partitioning on stacked voltage domain designs.

### 3.1.4 Clustering Approaches

Clustering approaches are often taxonomized as being either bottom-up or top-down. Bottom-up methods start with each module being an individual cluster, with clusters being iteratively merged until a given condition is satisfied. Top-down methods start with a single cluster and iteratively split clusters into two or more (smaller) clusters. For instance, Rajaraman and Wong (1995) propose a bottom-up polynomial time algorithm for clustering networks aiming to minimize delay and subject to capacity constraints. Alternatively, Alpert et al. (2005) propose a semi-persistent clustering technique to speed up placement. Li, Behjat and Kennings (2007) propose a bottom-up clustering algorithm based on a score function that aims to reduce the number of nets in the clustered netlist and penalize large clusters. Yan, Chu and Mak (2010) use clustering to reduce the netlist size and speed up placement. A "safe condition" is devised and guarantees that clustering will not degrade wirelength. Rakai et al. (2012) devise a bottom-up clustering algorithm that relies on wirelength prediction of nets.

### 3.2 Community Detection

This Section presents a study on *community detection* methods. These methods are closely related to graph partitioning, as the ones covered in Section 3.1 and hierarchical clustering studied in sociology (NEWMAN; GIRVAN, 2004). *Communities* are defined as the division of the vertices of the graph into groups within the connections are denser and between and between which the connections are sparser (NEWMAN; GIRVAN, 2004). Figure 3.2 depicts a graph divided into 3 communities, highlighted by dashed red lines. Community detection differs from graph partitioning as follows.

- Community detection methods do not impose a target number of communities, in contrast with partitioning methods for which users define the target number of partitions.

- The communities do not have to be balanced in terms of area, number of edges or vertices.

- Community detection methods do not minimize cut, since it is natural for larger communities to have higher numbers of edges connected to them.

Figure 3.2: Example of communities in a graph. Bold black lines are edges connecting vertices that belong to the same community; Gray lines are edges connecting vertices that belong to different communities and dashed red lines outline the communities.

Source: Newman and Girvan (2004).

Community detection methods may be divided into three categories: *divisive methods* find communities by iteratively removing edges from the graph (GIRVAN; NEW-MAN, 2002; NEWMAN; GIRVAN, 2004; RADICCHI et al., 2004); *agglomerative methods* iteratively merge vertices and communities (PONS; LATAPY, 2006; BLONDEL et al., 2008) and *optimization methods* maximize an objective function (CLAUSET; NEW-

MAN; MOORE, 2004; WU; HUBERMAN, 2004; NEWMAN, 2006) using heuristic methods (e.g. *simulated annealing (KIRKPATRICK; GELATT; VECCHI, 1983)*).

The remaining of this Section studies the evolution of the so-called *modularity-driven community detection* methods. Table 3.2 summarizes the method to be discussed from Sections 3.2.1 through 3.2.7. Section 3.2.1 starts showing how modularity has been first introduced by Newman and Girvan to evaluate the outcome of community detection methods. Then, Sections 3.2.2 through 3.2.4 show how modularity has become an objective function and how to effectively optimize it. Section 3.2.5 discusses the fast and effective Louvain algorithm, that will be used later in this work. Sections 3.2.6 and 3.2.7 discuss the limitations of modularity-driven techniques and present the alternative metrics *structural similarity* and *similarity-based modularity*. Section 3.2.8 concludes with a brief review of modularity-based community detection on hypergraphs.

Table 3.2: Summary of the community detection methods to be discussed in this Section.

| Reference                | Objective function               | Category      |

|--------------------------|----------------------------------|---------------|

| Newman and Girvan, 2004  | Edge betweenness                 | Divisive      |

| Newman, 2004             | Modularity                       | Agglomerative |

| Clauset et al., 2004     | Modularity                       | Agglomerative |

| Wakita and Tsusumi, 2007 | Modularity + consolidation ratio | Agglomerative |

| Blondel et al., 2008     | Modularity                       | Agglomerative |

| Xu et al., 2007          | Structural similarity            | Agglomerative |

| Feng et al., 2007        | Similarity-based modularity      | Agglomerative |

Source: from author.

# 3.2.1 Finding and Evaluating Community Structure in Networks (NEWMAN; GIR-VAN, 2004)

Newman and Girvan propose three *divisive methods* for community detection (NEWMAN; GIRVAN, 2004). In each iteration, the methods find the pair of connected vertices with least *similarity* to remove. The process is repeated iteratively until some stop condition is met. The end goal of this process is to divide the graph into smaller pieces. Each piece is an output community. Newman and Girvan propose three heuristics to quantify a pair of vertices similarity:

• Shortest-path betweenness. Compute the shortest path between any pair of nodes and find how many paths run along each edge.

- Random-walk betweenness. For each edge, compute the expected number of times a random walk between every two pairs of nodes will run along the current edge.

- Current-flow betweenness. Models every edge of the graph as one resistance with

a constant value. Each pair of nodes is considered a source and sink of current. The

heuristic computes the current in each edge for every pair of nodes. The values of

the current for each edge are summed up.

Newman and Girvan compare their heuristics using artificial and real-world graphs whose ground-truth communities are known. However, they highlight that in most real-world problems, the ground-truth communities are not known. To tackle this problem, the authors propose a metric, called *modularity*, aiming to evaluate the quality of the division of a graph into communities. Modularity is defined as:

$$Q = \frac{1}{2m} \sum_{i,j} \left[ A_{ij} - \frac{k_i k_j}{2m} \right] \delta(C(i), C(j))$$

(3.2)

where Q is the modularity value;  $A_{ij}$  is the sum of the edge weights between communities i and j;  $k_i$  is the sum of the edges weights connected to i; m is computed as  $m = \frac{1}{2} \sum_{ij} A_{ij}$ ; C(i) is the community of vertex i and  $\delta(C(i), C(j))$  assumes value 1 if C(i) is equal to C(j) and 0 otherwise.

The correlation between modularity and the ground-truth communities for a given graph has been assessed using artificial-generated test cases. Newman and Girvan have noticed peaks of modularity (E.g.: Q>0.7) for solutions whose communities have correlated well with the ground-truth.

# 3.2.2 Fast Algorithm for Detecting Community Structure in Networks (NEWMAN, 2004)

Girman and Newman show that modularity is a good metric to assess the outcome of a community detection algorithm (NEWMAN; GIRVAN, 2004). Following this assumption, Newman finds the answer to the question "If a high value of modularity represents a good community division, why not simply optimize modularity over all possible divisions to find the best one?" (NEWMAN, 2004). Of course, it is infeasible to explore all the solution space for graphs with thousands or millions of vertices, but approximation algorithms could be applied.

Newman proposes a greedy agglomerative algorithm that starts with every vertex as a sole member of a community. Then, the algorithm repeatedly merges communities together in pairs. At each step, the algorithm chooses the pair of communities that results in the best increase in modularity. Since it is impossible to increase the value of modularity by merging pairs that do not have an edge between them, the algorithm only considers pairs of neighboring communities. The modularity delta of joining two communities is computed as

$$\Delta Q = \frac{1}{2m} \sum_{i,j} \left[ A_{ij} + A_{ji} - 2 \frac{k_i k_j}{2m} \right]$$

(3.3)

where  $\Delta Q$  is the variation of modularity value;  $A_{ij}$  is the sum of the edge weights between communities i and j;  $k_i$  is the sum of the edges weights connected to to i and m is computed as  $m = \frac{1}{2} \sum_{ij} A_{ij}$ .

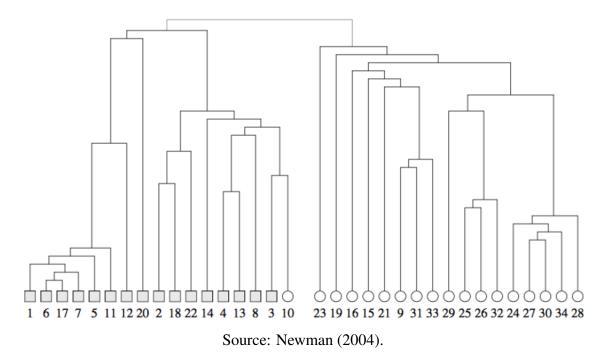

Each pass of this algorithm has a complexity of O(|E|+|V|), where |E| is the number of edges in the graph and |V| is the number of vertices. There is a total of |V|-1 passes to construct the dendrogram (EVERITT; SKRONDAL, 2002) of the graph. The entire algorithm runs in O((|E|+|V|)|V|) and  $O(|V|^2)$  in sparse graphs. Figure 3.3 represents the outcome of Newman's algorithm for the "Karate club" benchmark (ZACHARY, 1977) as a dendrogram. The dendrogram is a graphical representation of hierarchical clustering. In Figure 3.3, the shapes at the bottom level represent the known ground-truth. Girvan and Newman's only assigns vertex 10 to a "wrong" cluster.

# 3.2.3 Finding Community Structure in Very Large Networks (CLAUSET; NEW-MAN; MOORE, 2004)

Clauset et al. propose optimized data structures to speed up Newman's algorithm so it can be applied in larger and sparser graphs (CLAUSET; NEWMAN; MOORE, 2004). While Newman uses an adjacency matrix to represent the graph, Clauset et al. propose the use of a  $\Delta Q$  matrix that stores the change in modularity by joining every pair of vertices i and j. Since most real-life graphs are sparse, they propose to apply data structures optimized for sparse matrices. In addition, they propose to use fast data structures to keep track of the highest deltas of modularity.

In summary, the authors propose three data structures:

• A sparse matrix  $\Delta Q_{ij}$  containing the delta of modularity for every pair of vertices.

Figure 3.3: Dendrogram of the clustering found by Newman for the "Karate club" benchmark. Numbers are the vertices indices and the shapes represent the ground-truth communities.

The authors propose to implement each row of the matrix as a balanced binary tree, so elements can be efficiently inserted and found.

- A max heap containing the largest  $\Delta Q$  for every row of the matrix along with labels identifying the indices of the vertices to join.

- A vector containing the values of the normalized degree of the vertices.

The algorithm, called CNM, may be outlined in three steps:

- 1. Initialize the values of  $\Delta Q$ , the vector and the max heap.

- 2. Find the largest  $\Delta Q$ , merge communities and update the matrix, the max heap and the vector.

- 3. Repeat (2) until only one community remains.

# 3.2.4 Finding Community Structure in Mega-Scale Social Networks (WAKITA; TSU-RUMI, 2007)

According to Wakita and Tsurumi (WAKITA; TSURUMI, 2007), the CNM algorithm only scales well for graphs with up to 500K vertices. They diagnose the cause of the inefficiency being the unbalanced nature of the process of merging vertices and com-

munities. Their experiments show only a small number of communities growing very fast. Wakita and Tsurumi hence propose an extension to the CNM algorithm whose goal is to balance the size of communities during the merging process. In their extension, the candidate pairs of communities to be merged are ranked by the weighted delta in modularity, instead of delta of modularity solely. They propose weighting schemes called *consolidation ratio* that are expressed as:

$$consolidation\_ratio(c_i, c_j) = \min(h(c_i)/h(c_j), h(c_j)/h(c_i))$$

(3.4)

where  $c_i$  and  $c_j$  are the communities and h is a weighting scheme function. Wakita and Tsurumi propose three weighting schemes:

- **HE**. The value of h for a given community is equal to the number of edges connecting the community to its neighbors;

- **HE**'. First, a set of pairs that produce the best delta modularity for each community is computed. The best pairs are then ranked as in HE.

- **HN**. The value of h for a given community is equal to the number of vertices from the original graph that belongs to the given community.

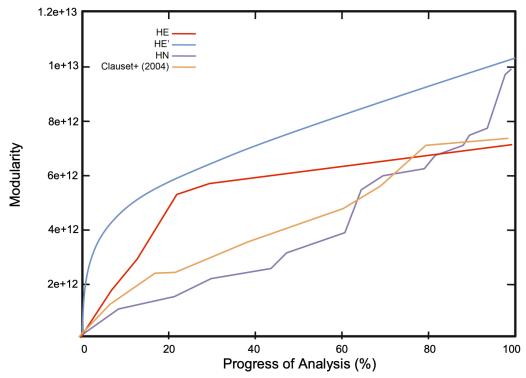

Figure 3.4 shows how the vanilla CNM algorithm and Wakita and Tsurumi extension scale for graphs with up to 1M vertices. Figure 3.5 shows the values of modularity vs. iterations ("progress of analysis") in a graph with 500K vertices.<sup>4</sup> The HE' heuristic is able to outperform CNM in terms of performance and modularity while HE and HN outperform CNM in performance but perform 21-28% worse than vanilla CNM.

#### 3.2.5 Fast Unfolding of Communities in Large Networks (BLONDEL et al., 2008)

Blondel et al. propose an agglomerative modularity-driven method, called *Louvain algorithm* (BLONDEL et al., 2008). In the beginning, each vertex of the graph is considered a community. The *first phase* of the Louvain algorithm iterates through all vertices of the graph. For each vertex, Louvain computes the cost of moving the given vertex from its current community to the neighboring communities. The vertex is moved to the neighboring community that presents the higher cost. The vertex remains in the original community if the maximum cost is not positive. The cost is given by the modu-

<sup>&</sup>lt;sup>4</sup>In Figure 3.5, Wakita and Tsurumi multiply the value of modularity by the squared number of edges in the graph.

25000 ΗE HE' HN Clauset+ (2004) 20000 Elapsed Time (sec) 15000 10000 5000 100000 200000 400000 500000 600000 700000 800000 900000 Size of Social Network

Figure 3.4: Runtime comparison between CNM and Wakita and Tsurumi.

Source: adapted from Newman (2004).

Figure 3.5: Values of modularity for CNM and Wakita and Tsurumi. For the latter, different weighting schemes are shown.

Source: adapted from Newman (2004).

larity delta, which is efficiently computed using equation 3.3 The first phase is repeated until modularity stops improving.<sup>5</sup>

The *second phase* builds a new graph in which the vertices are the communities found in the first phase. The edges among the vertices of the new graph are the sum of the edges between the vertices of the corresponding communities on the old graph. Edges between nodes belonging to the same community are summed up and create a self-loop in the new graph. After the second phase is completed, the first phase is performed again, upon the new graph, and so forth. Each iteration between the first and second phases is called *a pass*. The algorithm stops when there is no gain in modularity after a pass.

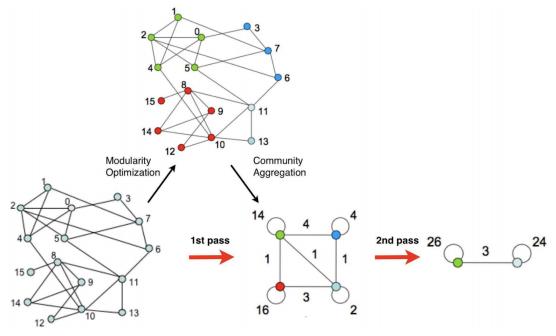

Figure 3.6 depicts the steps of the Louvain algorithm. The input of the example is a graph with 16 vertices and 53 edges (all edges have weight = 1). In the first phase, the Louvain algorithm finds 4 communities, depicted in red, green, blue and gray. The second phase builds a new graph with 4 nodes corresponding to the communities found in the first phase and, 9 edges. The output of the second pass is a graph with 2 vertices and 3 edges.

Unlike previous approaches, Louvain is fast and scalable. Experiments performed by Blondel et al. show linear runtime complexity with respect to the number of vertices in sparse graphs. For instance, Louvain is able to perform community detection in a graph with 118M vertices in 152 minutes. Since each pass reduces the size of the graph, most of the runtime is spent on the first iteration.

## 3.2.6 SCAN: A Structural Clustering Algorithm for Network (XU et al., 2007)

Modularity-driven methods do not detect and isolate two very common structures found in graphs: *hubs* and *outliers*. Consider the graph depicted in Figure 3.7. Vertices 0 through 5 and 7 through 12 clearly form two clusters. However, vertex 6 is equally connected with three other vertices from both clusters and, therefore, is considered a hub; Vertex 13 is connected only with vertex 9 and does not clearly make part of the any cluster, therefore it is called an outlier.

<sup>&</sup>lt;sup>5</sup>One might note that the order in which nodes are iterated changes the output of the algorithm. However, Blondel et al. have performed experiments showing that the variation in modularity is not significant.

Figure 3.6: Outline of Louvain algorithm. The algorithm has two phases: *modularity* optimization and community aggregation. Each iteration of the two phases is called a pass.

Source: Blondel et al. (2008).

Xu et al. devise a metric, called *structural similarity*, that measures how strongly connected two vertices are (XU et al., 2007). The structural similarity metric is a real number ranging from 0 to 1, defined as:

$$\chi(u,v) = \frac{|\Gamma(u) \cap \Gamma(v)|}{\sqrt{|\Gamma(u)||\Gamma(v)|}}$$

(3.5)

where  $\chi(u,v)$  is the value of structural similarity of vertices u and v, and  $\Gamma(u)$  is a set of vertices comprising u and its topological neighbors. The more similar is the neighborhood of two adjacent vertices, higher is the value of their structural similarity and may be used to find clusters, hubs and outliers.

Xu et al. also propose an algorithm called SCAN, based on the traditional clustering algorithm DBSCAN. SCAN uses a heuristic to find vertices to be used as seeds for clusters and then apply structural similarity to expand the seeds and form clusters. The vertices not assigned to any clusters after the execution of SCAN are classified as hubs or outliers. The algorithm requires  $O(|E|^2/|V|)$  runtime. Most of the runtime of the algorithm comes from the computation of structural similarity which takes O(|E|/|V|) runtime.

7 7 4 11 0