### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

MIGUEL CARDOSO NEVES

# Enforcing properties in programmable networks

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Marinho Pilla Barcellos

Porto Alegre May 2020 Neves, Miguel Cardoso

Enforcing properties in programmable networks / Miguel Cardoso Neves. – Porto Alegre: PPGC da UFRGS, 2020.

96 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2020. Advisor: Marinho Pilla Barcellos.

1. Programmable networks. 2. Network verification. 3. Network debugging. 4. SDN. 5. P4. 6. Monitoring. I. Barcellos, Marinho Pilla. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof. Carla Maria Dal Sasso Freitas Coordenadora do PPGC: Prof. Luciana Salete Buriol Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"If you always do what you always did, you will always get what you always got." — Albert Einstein

#### ACKNOWLEDGEMENTS

This thesis would not be possible without the support of many extraordinary people. First of all, I am very thankful to Marinho Barcellos for his patience and commitment to this work. More than an advisor, Marinho became a good friend that has taught me important lessons. I am also very grateful to Kirill Levchenko for co-advising this work. His creativity and pragmatism certainly made this research more interesting and useful. Also, visiting Kirill's research group at UC San Diego was one of the most enriching experiences in my life.

My family and friends also played a central role in this journey. In particular, I am hugely grateful to my parents, Paulo Neves and Rosane Cardoso, to give up from so much in their lives to make my dreams possible, and to my fiancée, Elisandra Pradella, for being by my side at all hours. I was also very fortunate to have good friends sharing the same workspace with me. In special, thanks to Lucas Muller, Fabrício Mazzola, Pedro Marcos, Rodrigo Oliveira and Sérgio Gutiérrez for transforming my work hours (and after hours) into something pleasant and comfortable.

I am thankful to my professors at UFRGS, who actively contributed to my development as a professional and human being. In particular, thanks to all the members of the Computer Networks Research Group, with whom I was fortunate to collaborate and engage in exciting discussions. Finally, thanks to Theophilus Benson, Christian Rothenberg, Luciano Gaspary and Richard Nelson, the committee of my thesis proposal and thesis defenses, for their constructive feedback that helped advance our research and improve this manuscript.

#### ABSTRACT

Avoiding software bugs and misconfigurations in programmable networks is challenging. Recent studies show that they are among the biggest causes of failures in network infrastructures. Moreover, their consequences can be disastrous. Previous efforts have proposed network debugging and verification techniques as a means to check that the network behaves as expected, but these techniques usually lead to incomplete solutions that can not catch all bugs or face severe scalability issues. In this thesis, we introduce the abstraction of data plane monitors, special modules that allow network programmers to enforce desired properties in a scalable and expressive way. Together with P4box, a system we propose for instrumenting data plane programs with monitors, our abstraction creates an enforcement kernel that cannot be hindered, tampered or circumvented by faulty code. To assess the benefits of our mechanism, we are exploring two use cases: dynamic and static property enforcement. The former is useful when verification does not meet time constraints while the latter enables the verification of previously unfeasible properties. Our experiments using P4box in programmable network hardware show that monitors represent a small overhead in terms of latency and resource consumption when dynamically enforcing a broad range of properties. Moreover, they enable P4box to verify (or statically enforce) reachability properties for large networks (> 190 routers) within a few minutes using off-the-shelf equipment.

**Keywords:** Programmable networks. network verification. network debugging. SDN. P4. monitoring.

#### Assegurando propriedades em redes programáveis

#### **RESUMO**

Evitar bugs e erros de configuração em redes programáveis é um desafio. Estudos recentes mostram que essas estão entre as maiores causas de falhas em infraestruturas de rede. Além disso, as consequências dessas falhas podem ser catastróficas. Trabalhos na literatura propõem técnicas de depuração e verificação de redes como forma de checar se a infraestrutura está funcionando da maneira esperada, mas tais técnicas comumente levam a soluções incapazes de identificar todos os bugs e enfrentam sérios problemas de escalabilidade. Nesta tese nós introduzimos o conceito de monitores de planos de dados, módulos especiais que permitem a programadores de rede assegurar propriedades de interesse de forma expressiva e escalável. Juntamente com o sistema que estamos propondo para instrumentar programas de rede com monitores de planos de dados, chamado P4box, nosso mecanismo cria um núcleo de proteção que não pode ser impedido, violado ou evitado por programas sujeitos a falhas. A fim de mostrar os benefícios do nosso mecanismo, exploramos dois casos de uso: assegurar propriedades dinamica e estaticamente. Enquanto o primeiro é útil em cenários onde verificação não consegue atingir restrições de tempo, o segundo permite a verificação de propriedades que não eram possíveis até então. Resultados mostram que monitores de planos de dados implicam numa baixa sobrecarga aos dispositivos de rede em termos de latência e consumo de recursos ao assegurar propriedades dinamicamente. Além disso, eles permitem que o sistema proposto (i.e., P4box) verifique propriedades de rede como atingibilidade entre hosts em grandes topologias (com mais de 190 roteadores) em poucos minutos.

**Palavras-chave:** Redes programáveis, verificação de redes, depuração de redes, SDN, P4, monitoramento.

#### LIST OF ABBREVIATIONS AND ACRONYMS

- ISP Internet Service Provider

- NAT Network Address Translator

- PISA Protocol Independent Switch Architecture

- SDN Software Defined Network

- SEFL Symbolic Execution Friendly Language

- SMT Satisfiability Modulo Theory

- SMV Symbolic Model Verifier

- TTL Time to Live

# LIST OF FIGURES

| Figure 2.1 Example of PISA-based switch. Dashed blocks can be programmed in P4. 16                                                                                      |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 2.2 Example P4 program                                                                                                                                           | ) |

| Figure 3.1 P4box programming model                                                                                                                                      | ł |

| Figure 3.2 P4box workflow                                                                                                                                               |   |

| Figure 3.3 Example of control block monitor to enforce header protection                                                                                                |   |

| Figure 3.4 Instrumentation of control blocks                                                                                                                            |   |

| Figure 3.5 Instrumentation of parsers                                                                                                                                   |   |

| Figure 3.6 Instrumentation of extern calls                                                                                                                              |   |

| Figure 3.7 Assertion language grammar                                                                                                                                   |   |

| Figure 3.8 Example of annotated monitor                                                                                                                                 |   |

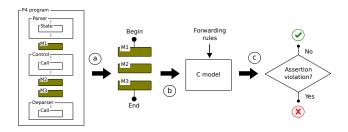

| Figure 3.9 Workflow for checking monitor correctness. M1, M2, M3 = annotated                                                                                            | - |

|                                                                                                                                                                         | , |

| monitors. $a = monitor$ assembling. $b = model$ extraction. $c = symbolic$ execution.32<br>Figure 3.10. Equivalent model in C to the monitor described in Section 3.2.1 |   |

| Figure 3.10 Equivalent model in C to the monitor described in Section 3.2.1                                                                                             | , |

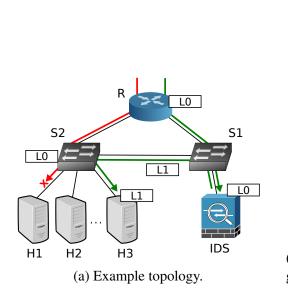

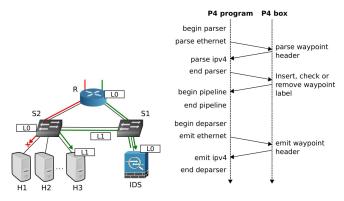

| Figure 4.1 Enforcing waypointing                                                                                                                                        | 5 |

| Figure 4.2 Monitors to enforce waypointing                                                                                                                              | ) |

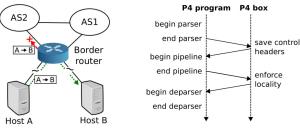

| Figure 4.3 Enforcing traffic locality                                                                                                                                   | 1 |

| Figure 4.4 Monitor to enforce traffic locality                                                                                                                          | 3 |

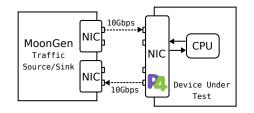

| Figure 4.5 Testbed topology. Dashed arrows represent the data flow. Solid arrows                                                                                        |   |

| indicate control traffic (e.g., for programming the NIC firmware using P4 and                                                                                           |   |

| collecting statistics)                                                                                                                                                  | ) |

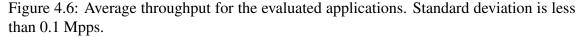

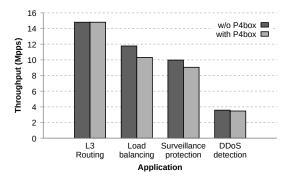

| Figure 4.6 Average throughput for the evaluated applications. Standard deviation                                                                                        |   |

| is less than 0.1 Mpps41                                                                                                                                                 |   |

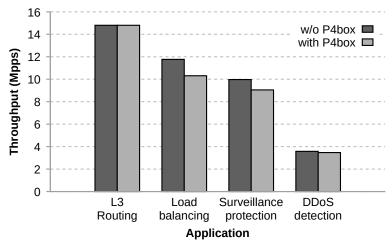

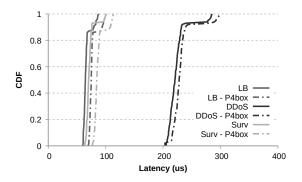

| Figure 4.7 CDF of the packet latency for the evaluated applications                                                                                                     | l |

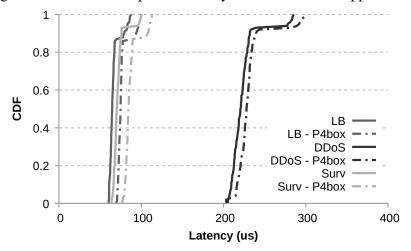

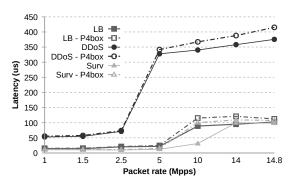

| Figure 4.8 95-percentile tail latencies at different packet rates                                                                                                       | ) |

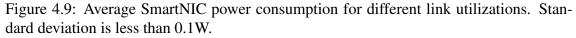

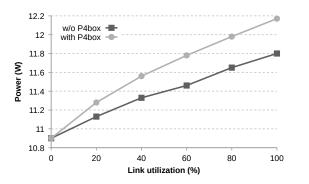

| Figure 4.9 Average SmartNIC power consumption for different link utilizations.                                                                                          |   |

| Standard deviation is less than 0.1W43                                                                                                                                  | 3 |

| Figure 5.1 Motivating example to show the benefits of P4box monitors to static                                                                                          |   |

| property enforcement                                                                                                                                                    | 5 |

| Figure 5.2 Example of network model adopted by P4box                                                                                                                    |   |

|                                                                                                                                                                         |   |

| Figure 5.3 Equivalent C model to the topology shown in Figure 5.2                                                                                                       | ' |

| Figure 5.4 Optimizing network models by grouping similar rules under the same                                                                                           | ) |

| branch                                                                                                                                                                  | ) |

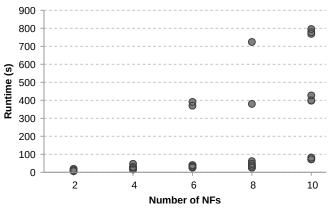

| -                                                                                                                                                                       | 1 |

| the network                                                                                                                                                             |   |

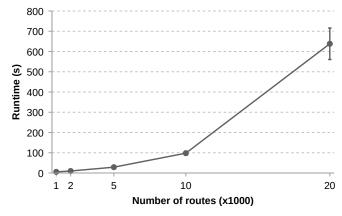

| Figure 5.6 Memory consumption for different numbers of network function in-                                                                                             | , |

| stances in the network                                                                                                                                                  |   |

|                                                                                                                                                                         |   |

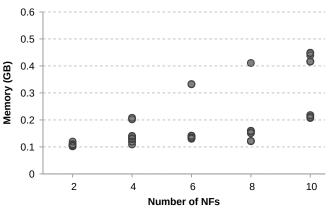

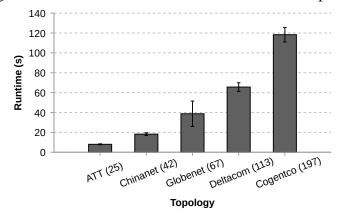

| Figure 5.8 Verification time for different network topologies                                                                                                           |   |

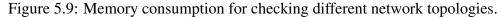

| Figure 5.9 Memory consumption for checking different network topologies                                                                                                 |   |

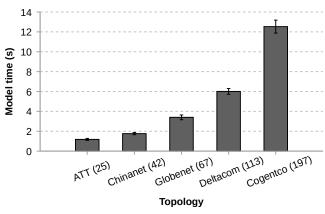

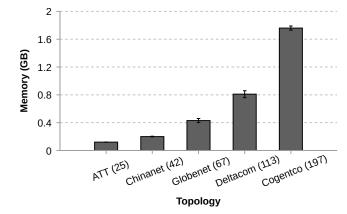

| Figure 5.10 Time to create a C model for different numbers of routes                                                                                                    |   |

| Figure 5.11 Verification time for different numbers of routes                                                                                                           |   |

| Figure 5.12 Memory consumption for different numbers of routes                                                                                                          | ) |

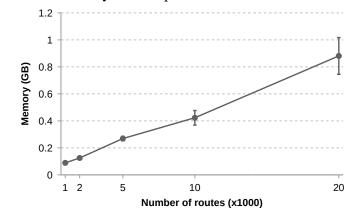

| Figure 5.13 Normalized verification time with respect to the least connected node                                                                                       | _ |

| (Node $ID = 0$ ) for all the remaining nodes in the ATT topology                                                                                                        | ) |

| Figure A.1 Arquitetura de um monitor de plano de dados71                                                                                                                |   |

Figure A.2 Sintaxe para especificação de monitores de planos de dados.....71

## LIST OF TABLES

| Table 2.1 Summary of control plane verifiers.                                       | 20 |

|-------------------------------------------------------------------------------------|----|

| Table 2.2 Summary of data plane verifiers                                           |    |

| Table 2.3 Summary of P4 verifiers. $\mathbf{O}$ = partial support                   | 21 |

| Table 2.4 Summary of network debugging tools.                                       | 22 |

| Table 2.5    Summary of network monitoring tools.                                   | 23 |

| Table 4.1 Average, 5th and 95th-percentile latency cost of the properties described |    |

| in Sections 4.1 and 4.2.                                                            | 40 |

| Table 4.2 Evaluated applications. LoC = Lines of Code.                              | 40 |

| Table 4.3 Average power consumption (in Watts) at line rate for different applica-  |    |

| tions. Standard deviation is less than 0.1W                                         | 43 |

| Table 5.1 Average time to generate a C model for different numbers of network       |    |

| function instances. Standard deviation is less than 20 ms.                          | 51 |

# CONTENTS

| 1 INTRODUCTION                               |     |

|----------------------------------------------|-----|

| 1.1 Context and motivation                   | .12 |

| 1.2 Contributions                            | .12 |

| 1.3 Outline                                  |     |

| 2 BACKGROUND AND RELATED WORK                |     |

| 2.1 Programmable networks                    |     |

| 2.2 Desired properties                       |     |

| 2.3 Current enforcement approaches           | .18 |

| 2.3.1 Network verification                   | .19 |

| 2.3.2 Network debugging                      | .21 |

| 3 P4BOX: CREATING AN ENFORCEMENT KERNEL      |     |

| 3.1 Overview                                 |     |

| 3.2 Data plane monitors                      |     |

| 3.2.1 Control block monitors                 |     |

| 3.2.2 Parser monitors                        |     |

| 3.2.3 Extern monitors                        |     |

| 3.3 Monitor correctness                      |     |

| 3.4 Implementation                           |     |

| 4 CASE STUDY: DYNAMIC ENFORCEMENT            | .34 |

| 4.1 Program Properties                       | .34 |

| 4.2 Network-Wide Properties                  | .35 |

| 4.3 Performance                              | .37 |

| 4.3.1 Evaluation Methodology                 |     |

| 4.3.2 Property overhead                      | .39 |

| 4.3.3 Application performance                |     |

| 4.3.4 Effect of packet rate                  | .41 |

| 4.3.5 Power consumption                      | .42 |

| 5 CASE STUDY: STATIC ENFORCEMENT             | .44 |

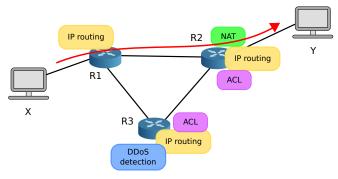

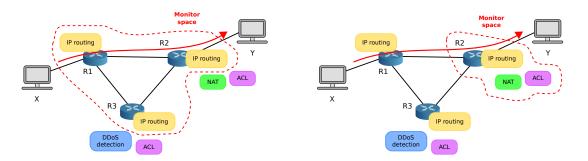

| 5.1 Motivating example                       | .44 |

| 5.2 Modeling networks                        | .45 |

| 5.3 Optimizations                            | .47 |

| 5.4 Enforcing properties                     | .49 |

| 5.5 Evaluation                               | .49 |

| 5.5.1 Setup                                  | .50 |

| 5.5.2 Effectiveness                          | .50 |

| 5.5.3 Scalability                            | .52 |

| 6 CONCLUSION                                 | .57 |

| 6.1 Summary                                  | .57 |

| 6.2 Achievements                             | .57 |

| 6.3 Future work                              | .59 |

| REFERENCES                                   |     |

| APPENDIX A — RESUMO EXPANDIDO                |     |

| APPENDIX B — PAPER AT IFIP NETWORKING 2019   |     |

| APPENDIX C — PAPER SUBMITTED TO IEEE/ACM TON | .85 |

#### **1 INTRODUCTION**

#### **1.1 Context and motivation**

Programmable networks allow operators to modify the behavior of network devices (by reprogramming either the control or the data plane) to quickly deploy new protocols, customize functions or implement advanced services. This flexibility has become mandatory to deal with the increasing scale and traffic demand of applications (YAP et al., 2017). The introduction of network programming languages has greatly lowered the barriers for configuring networks, offering important abstractions and facilitating the specification of complex policies. Today it is reasonable to think that an ecosystem of networking software is emerging, where devices (whether a switch or the network controller) run code written by teams of developers across multiple organizations, assembled by a network operator from libraries and modules to implement a particular set of features.

To reap the benefits of this software ecosystem, network programmers need to ensure that the software they produce behaves correctly. Recent studies show that software bugs and mosconfigurations are the biggest causes of failures in large network infrastructures (up to 60%) (MEZA et al., 2018; GOVINDAN et al., 2016), and the introduction of greater programmability only exacerbates the problem. Fortunately, decades of progress in software engineering and verification have produced mature tools and techniques - from testing to formal methods - for ensuring that software behaves correctly. In the networking domain, these tools are of great importance to reduce the number of incidents, and many of them have been proposed over the last years to enforce the most varied properties (LI et al., 2018). Nevertheless, the problem of network software reliability is far from solved. Despite the simplicity of the network programming model compared to general-purpose software development, e.g., network programming languages usually do not support dynamic memory allocation or even loops (BOSSHART et al., 2014), current state-of-the-art network debugging and verification tools still require considerable amounts of time, skill and effort when applied in production environments.

#### **1.2 Contributions**

Most of the complexity for identifying and removing bugs and misconfigurations from network infrastructures comes from three fundamental aspects. First, there is a complex chain of interactions between the control and the data plane and among network devices themselves. This makes difficult modeling or stressing all possible behaviors the network can present. Second, the scale of current networks result in tools that often hit the wall of theoretical limits (e.g., soundness *versus* completeness, state-space explosion). Even worse, simplifications in network models may lead to unreliable results. Finally, many tools are designed by experts in formal methods and software engineering, which causes these tools to struggle in terms of usability when manipulated by operators and networking practitioners that do not have the same background.

This thesis tackles the problem of preventing failures caused by software bugs and misconfigurations in programmable networks. To that purpose, we rely on two key insights: i) the creation of small, privileged, isolated and safe modules (called monitors) in the network data plane, which are suitable for verification and greatly reduce the scale of the problem; and ii) the usage of abstractions (rather than a new language or complex formalism) largely drawn from P4 – a widespread data plane programming language – to specify properties of interest, which minimizes the burden to network programmers and operators with the learning process. The development of **data plane monitors** is the *first contribution* of the thesis.

Based on these insights we propose P4box, a system for enforcing properties in programmable networks. Our system instruments P4 programs with data plane monitors at compile time. It does this in such a way that monitors can interpose and modify the behavior of the program without being hindered, tampered or circumvented. Moreover, P4box ensures monitors respect a set of desired properties by verifying their code (which is usually much smaller than the original program) through symbolic execution. The design and implementation of **P4box** is the *second contribution* of the thesis.

To show the value of our mechanism, we investigate two use cases. First, we study how to dynamically enforce properties in programmable networks using P4box and its monitors. **Dynamic property enforcement** is particularly useful when network programmers want to import code produced by (potentially untrusted) third parties or when verification does not meet time constraints. In this case, programmers can use monitors to specify additional program blocks devoted exclusively to enforce the desired property. This is the *third contribution* of the thesis.

Finally, we explore how to enable **static property enforcement**<sup>1</sup> in programmable networks using monitors and P4box. We are specially interested in properties that can

<sup>&</sup>lt;sup>1</sup>We use the terms *verification* and *static enforcement* interchangeably throughout the text.

not be verified (at least in practical times) even by state-of-the-art techniques such as reachability among end hosts. Rather than verifying the whole data plane, we show that it is possible to ensure these properties by verifying only monitors. This is the *fourth contribution* of the thesis.

#### 1.3 Outline

The remainder of this thesis is organized as follows. Chapter 2 examines programmable networks (including their architecture, main programming languages and desired properties), emphasizes the necessity of property enforcement mechanisms and summarizes existing solutions. Chapter 3 introduces program monitors, describes P4box and discusses its properties and limitations. Chapter 4 explores our first case study, dynamic enforcement, showing how to enforce program and network properties at runtime using P4box and quantifying its overhead to network devices. Chapter 5 then addresses our second case study, static enforcement, describing how to use P4box to scale network verification in the context of programmable data planes. Finally, Chapter 6 presents concluding remarks about our work and outlines research directions for future investigations.

#### **2 BACKGROUND AND RELATED WORK**

#### 2.1 Programmable networks

**Architecture.** A programmable network is one in which the behavior of network devices is handled by software independently from the network hardware (FEAMSTER; REXFORD; ZEGURA, 2014; MACEDO et al., 2015). This idea has evolved over the last thirty years and culminated in an architecture that is driven by two key principles: i) the separation between the control and the data plane; and ii) the programmability of both planes. The control plane is a logically centralized program that acts as an operating system for the network. It usually runs on a set of physically distributed commodity servers and interacts with network elements using an API, e.g., OpenFlow (MCKEOWN et al., 2008) or P4Runtime<sup>1</sup>. In this scenario, a single control software controls multiple data plane elements. The data plane, on the other hand, is implemented as a programmable packet processor present in each network device. This processor is silicon-independent (i.e., can run over an ASIC, FPGA, CPU or GPU) and offers a match + action abstraction that is specified using a high-level programming language, e.g., P4 (BOSSHART et al., 2014). Depending on the control-plane configuration, the data plane of an element can behave like a router, firewall, NAT, load balancer or something in between.

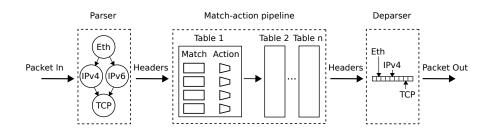

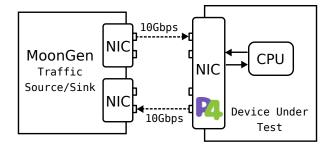

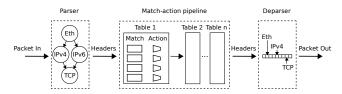

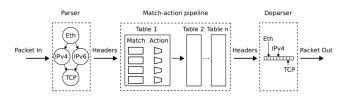

**Programmable network devices.** In programmable networks, forwarding devices (a.k.a. *targets*) implement variations of the Protocol Independent Switch Architecture - PISA<sup>2</sup>. In this architecture, a device contains multiple programmable blocks, which can be parsers, deparsers, match-action stages or queueing systems. Figure 2.1 presents an example of a PISA-based switch containing three programmable blocks (dashed boxes): a parser, a match-action pipeline and a deparser. Each programmable block is configured by developers using a data plane programming language, and the organization and capabilities of these blocks are abstracted to data plane programs as an interface or *architecture model*. Current examples of programmable network devices include hardware and software switches (SHARMA et al., 2017; SHAHBAZ et al., 2016), FPGA-based packet processing accelerators (WANG et al., 2017), packet filters (HØILAND-JØRGENSEN et al., 2018) and network interface cards - NICs (STEPHENS; AKELLA; SWIFT, 2018).

**P4 programming language.** Currently, the standard *de facto* language to describe the datapath of programmable network devices is P4. As a domain specific language, P4

<sup>&</sup>lt;sup>1</sup><https://p4.org/p4-runtime/>

<sup>&</sup>lt;sup>2</sup><https://p4.org/assets/p4-ws-2017-p4-architectures.pdf>

Figure 2.1: Example of PISA-based switch. Dashed blocks can be programmed in P4.

offers many constructs to facilitate the specification of packet processing tasks. Programmers can, for example, declare packet headers, parsers, tables, actions to modify packets, and control blocks to compose sequences of tables. These abstractions are used to configure one or more programmable blocks, and the configuration of all blocks in a device comprises a P4 program. Figure 2.2 shows an example of a program for configuring the PISA-based switch presented in Figure 2.1. We omitted some parts for the sake of simplicity. In this example, the match-action pipeline implements a single table that routes packets based on their IPv4 source and destination addresses (1.8-15). The pipeline block is then composed with the parser and deparser specifications according to the architecture model to form the datapath (1.22). It is worth mentioning that the P4 program is only part of the device configuration. It is still necessary to specify the rules (i.e., the control plane logic) that dictate its forwarding behavior.

Figure 2.2: Example P4 program.

```

parser ParserImpl( packet_in packet ){...}

1

2

control Pipeline( inout headers hdr ){

3

4

action route( bit<9> iface ){ ... }

5

6

/* Route IPv4 packets */

7

8

table route_packet {

9

actions = { route; }

10

key = {

hdr.ipv4.srcAddr : ternary;

11

hdr.ipv4.dstAddr : ternary;

12

13

14

size = 1024;

}

15

16

17

apply{ route_packet.apply(); }

18 }

19

20 control DeparserImpl( packet_out packet ){...}

21

22 Switch(ParserImpl(), Pipeline(), DeparserImpl())

```

#### **2.2 Desired properties**

Programmable networks are subject to many types of bugs, which can ultimately compromise their security, reliability and performance. On the control plane, bugs usually arise at the controller program and its applications, and are the consequence of a large (sometimes distributed) code base that must deal with many simultaneous events (CANINI et al., 2012; EL-HASSANY et al., 2016). The data plane, on its turn, has a much simpler programming model (e.g., P4 programs have no loops or dynamic memory allocation), but still has demonstrated to be prone to software errors. These errors vary in nature, but overall they can be the consequence of both generic bugs (i.e. wellknown from other software development contexts) such as information overwriting<sup>3</sup> and data use-before-initialization<sup>4</sup>, and also network specific bugs such as the creation of malformed packets (LOPES et al., 2016), incorrect implementation of protocol specifications (NEVES et al., 2018) or policy violations due to bad table configurations (LOPES et al., 2015; STOENESCU et al., 2016). In this work, we focus on enforcing properties at the data plane, as it implicitly captures all control plane functionality (expressed in the form of forwarding rules) and is comparatively simpler to analyze due to its limited operations (essentially dropping, modifying or forwarding packets).

At a high-level, one can classify the desired properties of a programmable network according to three criteria: i) if it concerns one or multiple devices; ii) if it is generic or associated to an specific program or protocol; and iii) if it involves context or not (ZA-OSTROVNYKH et al., 2017; FAYAZ et al., 2016). Below, we define each of these types of properties and give some examples. This is important to understand the capabilities of the state-of-the-art techniques that will be presented in the next section in terms of the classes of bugs and misconfigurations they can prevent.

• **Program** *versus* **network properties.** Program properties refer to the software running on individual elements in the network (e.g., a switch, router or middle-box) regardless of how they are configured or connected in a topology. Examples include absence of: buffer over/underflows, invalid pointer dereferences, out-of-bounds array indexing, variable use-after-free or use-before-initialization. Network properties, on the other hand, concern the resulting behavior of the network when its devices are combined (i.e., configured and connected) in a particular way. Prop-

<sup>&</sup>lt;sup>3</sup><https://github.com/p4lang/switch/issues/97>

<sup>&</sup>lt;sup>4</sup><https://github.com/p4lang/switch/pull/102>

erties such as reachability, waypointing and absence of forwarding loops are all in this group.

- Semantic *versus* general safety properties. When a property specifies the behavior of an specific program or protocol running in the network it is considered a semantic property. For example, the designer of a router may want to ensure that IPv4 packets have their TTL field decremented on every hop, while NAT programmers would like to check that their implementation conforms to the traditional NAT specification (i.e., RFC 3022). Otherwise, properties are considered general safety ones. Absence of buffer overflows and forwarding loops are also general safety properties.

- **Context-dependent** *versus* **context-independent properties.** Context-dependent properties consider the presence of stateful elements in a program or network. For instance, the forwarding decision in a stateful firewall typically depends on previous packets seen by the device, so it is necessary to take this state into account when verifying reachability or isolation (e.g., host A can communicate with host B only if host B has initiated a connection with host A). Properties that do not have this dependency are context-independent ones (e.g., TTL decrementation).

Note that we are focusing in this work on a restricted set of boolean related properties that does not take into account, for example, quantities and probabilities. Although being able to enforce non-boolean properties is highly desirable, as we will see in the next section state-of-the-art tools still face serious issues to enforce many boolean invariants on programmable networks, and this is the gap we are trying to fill with this thesis. We leave the investigation of techniques for enforcing quantitative and probabilistic properties in programmable networks as a future work.

#### 2.3 Current enforcement approaches

Tremendous progress has been made towards ensuring that a programmable network does not violate its desired properties. Most of the efforts fall under the scope of two broad techniques: *network verification* and *debugging*. In this section, we present an overview of these efforts to help putting our contributions in perspective. Notice that we do not aim to be exhaustive in our review, but rather offer to the reader an intuition of the main gaps we are trying to fill. We refer to the work of Li et al. (2019) for a more detailed study<sup>5</sup>.

#### 2.3.1 Network verification

Network verification uses formal analysis techniques (e.g., model checking, theorem proving, SAT/SMT solving) to prove that a property holds in the network for any possible state or configuration (i.e., sequence of packets, protocol stack, set of forwarding rules or network events). Network verification tools can be targeted to either the control or the data plane. Control plane tools usually verify the software running in the network controller (i.e., the network operating system and its applications), while data plane tools act directly over the datapath (i.e., code and forwarding rules) of network devices.

There are two main approaches for control plane verification: i) synthesizing verified controllers through programming frameworks; and ii) verifying control programs using automatic generated models. In the former, network programming languages (e.g., NetCore (MONSANTO et al., 2012) and NetKAT (ANDERSON et al., 2014)) have builtin constructs and proven derivations (i.e., theorems and axioms) that allow programmers to encode their properties using the language itself (i.e., there is no need to create a model of the system). The program is then compiled to generate a correct-by-construct network controller. The latter, on the other hand, converts control programs into equivalent models, and use these models to prove the desired properties. For example, Kinetic (KIM et al., 2015b) converts a control program into an SMV model and uses the NuSMV model checker for verifying properties. NICE (CANINI et al., 2012), on its turn, proposes a customized model-checker for OpenFlow-based controllers. Vericon (BALL et al., 2014) converts control programs into first-order logic formulas and checks them using the Z3 theorem prover. Finally, SDNRacer (EL-HASSANY et al., 2016) explores execution traces to build a happens-before model and identify sequences of events that lead to property violations. Table 2.1 summarizes these control plane verifiers.

Data plane verification encompasses checking the program running on a particular network device or in the whole set of devices forming the network topology. Intuitively, verifying a single network device should be much easier than verifying many of them, but it actually depends on the model and technique being adopted as well as the property of interest. For instance, (DOBRESCU; ARGYRAKI, 2014) uses symbolic execution to prove general safety properties (e.g., crash-freedom and bounded execution) on Click

<sup>&</sup>lt;sup>5</sup>As opposed to us the authors do not cover the P4 landscape.

| Verifier | Model        | Approach                                     |

|----------|--------------|----------------------------------------------|

| NetCore  |              | Formal semantics                             |

| NetKAT   |              | Formal semantics + Kleene algebra with tests |

| Kinetic  | $\checkmark$ | Model checking                               |

| NICE     | $\checkmark$ | Model checking + symbolic execution          |

| Vericon  | $\checkmark$ | SMT solving                                  |

| SDNRacer | $\checkmark$ | Happens-before graphs                        |

Table 2.1: Summary of control plane verifiers.

| Verifier              | Network<br>properties | Stateful     | Real time    | Approach                                 |

|-----------------------|-----------------------|--------------|--------------|------------------------------------------|

| DOBRESCU et al., 2014 |                       | $\checkmark$ |              | Symbolic execution                       |

| VigNAT                |                       | $\checkmark$ |              | Symbolic execution + theorem proving     |

| Hassel                | $\checkmark$          |              |              | Header space analysis                    |

| NoD                   | $\checkmark$          |              |              | Datalog                                  |

| SymNet                | $\checkmark$          | $\checkmark$ |              | Symbolic execution                       |

| VMN                   | $\checkmark$          | $\checkmark$ |              | SMT solving                              |

| Veriflow              | $\checkmark$          |              | $\checkmark$ | IP-based packet equivalence classes      |

| NetPlumber            | $\checkmark$          |              | $\checkmark$ | Header space analysis + graph algorithms |

| АРКеер                | $\checkmark$          |              | $\checkmark$ | Multi-field packet equivalence classes   |

Table 2.2: Summary of data plane verifiers.

elements. Their tool takes around twenty minutes to check the desired properties over an IP router implementation. VigNAT (ZAOSTROVNYKH et al., 2017) takes a step further and proves semantic properties over a NAT implementation (written in C) in less than forty minutes using a hybrid strategy based on symbolic execution and formal theorem proving. In contrast, Hassel (KAZEMIAN; VARGHESE; MCKEOWN, 2012) can verify the existence of forwarding loops in a network containing more than 25 switches and routers in less than 12 minutes through a dedicated algebra computed over header spaces (i.e., the notion of viewing packet headers as points in a geometric space).

Other data plane verifiers include: NoD (LOPES et al., 2015), which allows operators to model networks and properties using Datalog; SymNet (STOENESCU et al., 2016), which proposes a symbolic execution friendly language (SEFL) for modeling networks and symbolically executing these models; and VMN (PANDA et al., 2017), which takes middleboxes into account while checking reachability properties in ISPs and data center networks. Unlike all the previous approaches, Veriflow (KHURSHID et al., 2013), NetPlumber (KAZEMIAN et al., 2013) and APKeep (ZHANG et al., 2020) use customized techniques and data structures (e.g., equivalence classes) to enable real-time network verification (i.e., in the order of seconds or miliseconds). Table 2.2 summarizes these data plane verifiers.

| Verifier  | Network<br>properties | Approach           |

|-----------|-----------------------|--------------------|

| p4v       |                       | SMT solving        |

| assert-p4 |                       | Symbolic execution |

| Vera      | lacksquare            | Symbolic execution |

| P4k       | lacksquare            | K framework        |

| P4nod     | ${}^{\bullet}$        | Datalog            |

Table 2.3: Summary of P4 verifiers.  $\bigcirc$  = partial support.

Finally, many tools try to cope with the need for manually building a new model of the network whenever its data plane changes. For example, ASSERT-P4 (NEVES et al., 2018) automatically converts a P4 program into an equivalent model in C. p4v (LIU et al., 2018), on the other hand, uses SMT constraints to represent the data plane code. Both tools are able to check only program-specific properties though. Vera (STOENESCU et al., 2018) and P4NoD (LOPES et al., 2016) create models of data plane programs that can be used as input to SymNet and NoD, respectively. Although they can quickly verify small data plane programs (i.e., in the order of seconds), the verification time grows exponentially with both the program and the network size. Moreover, they either require programmers to manually compose program models to create a network-wide one or restrict the set of properties that programmers can check (e.g., enforce only reachability and well-formedness properties). P4K (KHERADMAND; ROSU, 2018), a tool that defines an executable semantics for P4 in K, has reported promising results in terms of performance, but it requires from programmers expertise in K for specifying the desired properties, network topology, forwarding rules and even input packets. Table 2.3 provides a summary of these P4-enabled verifiers.

#### 2.3.2 Network debugging

Network debugging involves generating test packets or network events (e.g., link failures) and monitoring the network response. Network debugging tools can perform some or all of these tasks (i.e., probing, monitoring, etc). For example, Pingmesh (GUO et al., 2015) generates probe packets among selected pairs of servers and monitors the network response to diagnose performance and connectivity problems. ATPG (ZENG et al., 2012), on the other hand, focuses on finding the minimum set of packets that exercise every link and forwarding rule in the network. Other tools that involve packet generation include: BUZZ (FAYAZ et al., 2016), which considers the presence of stateful elements

(e.g., middleboxes) in a topology and uses symbolic execution to generate sequences of packets that trigger relevant states; p4pktgen (NöTZLI et al., 2018), which takes into account the programmability of the data plane and generates test packets for P4 programs; and p4rl (SHUKLA et al., 2019), which uses reinforcement learning-guided fuzzing to augment coverage of a P4 program input space (i.e., cover more program paths with less test packets).

Some network debuggers can also systematically create relevant events (e.g., the partition of a distributed network controller, a packet loss or a switch failure) to exercise diverse operational conditions in a network. In this sense, STS (SCOTT et al., 2014) randomly generates sequences of events based on manually assigned probabilities and logs the activity of the network controller in response to those events. The log is then analyzed in order to find the minimal causal sequence that triggered a property violation. Armageddon (SHELLY et al., 2015), on its turn, tries to find the optimal sequence of link failures that enables operators to fail every link (and observe the respective behavior of the control plane) without violating any reachability property in the network. This is important when applying debuggers directly on production environments. Table 2.4 summarizes these network debugging tools.

| Table 2.4. Summary of network debugging tools. |                   |                    |              |              |

|------------------------------------------------|-------------------|--------------------|--------------|--------------|

| Debugger                                       | Packet<br>probing | Failure generation | Monitoring   | P4 support   |

| Pingmesh                                       | $\checkmark$      |                    | $\checkmark$ |              |

| ATPG                                           | $\checkmark$      |                    |              |              |

| BUZZ                                           | $\checkmark$      |                    |              |              |

| p4pktgen                                       | $\checkmark$      |                    |              | $\checkmark$ |

| p4rl                                           | $\checkmark$      |                    | $\checkmark$ | $\checkmark$ |

| STS                                            | $\checkmark$      | $\checkmark$       | $\checkmark$ |              |

| Armageddon                                     |                   | $\checkmark$       | $\checkmark$ |              |

Table 2.4: Summary of network debugging tools.

Finally, many tools involve exclusively monitoring the network infrastructure to catch property violations and their root cause. OpenSketch (YU; JOSE; MIAO, 2013), UnivMon (LIU et al., 2016), FlowRadar (LI et al., 2016), SketchVisor (HUANG et al., 2017) and \*Flow ("Star Flow") (SONCHACK et al., 2018) propose new data structures for efficiently storing and manipulating measurement information in network devices. Trumpet (MOSHREF et al., 2016) and PathDump (TAMMANA; AGARWAL; LEE, 2016), on the other hand, make use of end hosts for storing monitoring information rather than forwarding devices. SwitchPointer (TAMMANA; AGARWAL; LEE, 2018) proposes a hybrid approach that combines the visibility of network devices with the greater flexibil-

ity and amount of resources in end hosts.

In addition to the location where monitors run, state-of-the-art tools allow operators to set flexible monitoring campaigns using query languages and programmable frameworks. For example, INT (KIM et al., 2015a) provides a low-level programmable monitoring framework that exposes queue lengths and other performance metadata from switches by piggybacking them on packets. PathQuery (NARAYANA et al., 2016), Marple (NARAYANA et al., 2017) and Sonata (GUPTA et al., 2018) propose high-level languages based on predicates and functional constructs (e.g., map, filter, groupby) that facilitate the expression of complex monitoring tasks. NetQRE (YUAN et al., 2017) and Varanus (NELSON et al., 2016) extend this idea to capture quantitative and stateful network policies, respectively. Finally, Stroboscope (TILMANS et al., 2018) adds the notion of time and schedules measurement tasks according to resource constraints on forwarding devices. Table 2.5 provides a summary of the network monitoring tools we discussed.

| Tool          | Custom<br>data structure | Custom<br>query language | P4 support   |

|---------------|--------------------------|--------------------------|--------------|

| OpenSketch    | $\checkmark$             |                          |              |

| UnivMon       | $\checkmark$             |                          | $\checkmark$ |

| FlowRadar     | $\checkmark$             |                          | $\checkmark$ |

| SketchVisor   | $\checkmark$             |                          |              |

| *Flow         | $\checkmark$             |                          | $\checkmark$ |

| Trumpet       | $\checkmark$             | $\checkmark$             |              |

| PathDump      |                          | $\checkmark$             |              |

| SwitchPointer | $\checkmark$             |                          | $\checkmark$ |

| INT           |                          |                          | $\checkmark$ |

| PathQuery     |                          | $\checkmark$             |              |

| Marple        |                          | $\checkmark$             | $\checkmark$ |

| Sonata        |                          | $\checkmark$             | $\checkmark$ |

| NetQRE        |                          | $\checkmark$             |              |

| Varanus       |                          | $\checkmark$             |              |

| Stroboscope   |                          | $\checkmark$             |              |

Table 2.5: Summary of network monitoring tools.

#### **3 P4BOX: CREATING AN ENFORCEMENT KERNEL**

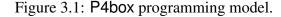

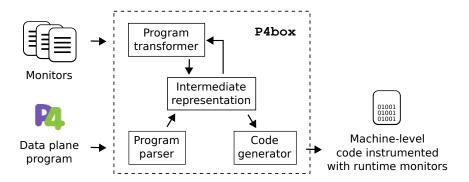

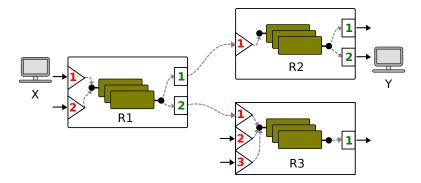

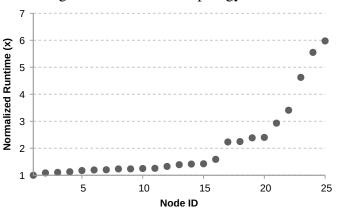

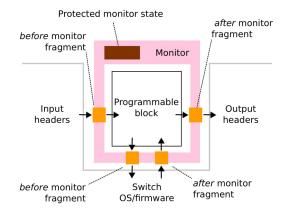

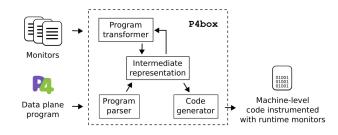

P4box is a system that allows network programmers to deploy data plane *monitors* in programmable networks. Monitors are privileged, isolated and safe modules that can be attached before and after control blocks, parser state transitions, and calls to external functions of a P4 program. Each monitor can modify the input and output of the code block or function it supervises. This enables the verification of pre- and post-conditions which can be used to enforce specific properties or modify the behavior of the monitored block. P4box instruments the P4 program with its monitors at the intermediate representation level (i.e., during the compilation phase). The resulting program (original code plus monitors) then continues the compilation as before, which allows P4box to be used with any backend compiler based on the P4<sub>16</sub> reference implementation. In the rest of this section, we provide an overview of P4box and runtime monitors (Section 3.1), describe the three kinds of monitors P4box can deploy in detail (Sections 3.2.1, 3.2.2 and 3.2.3), show how we verify monitors to ensure their correctness (Section 3.3), and present our prototype implementation (Section 3.4).

#### **3.1 Overview**

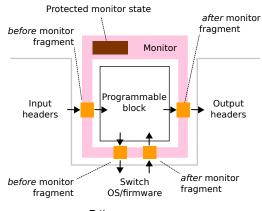

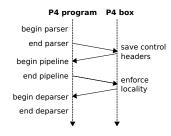

A runtime monitor interposes on the interaction of a P4 control block or parser with the rest of the execution environment (Figure 3.1), allowing the monitor programmer to modify the behavior of the enclosed P4 block. A P4 programmable block (either a control block or parser) interfaces with the rest of the P4 execution environment at entry into the block, return from the block, and at calls to architecture-supplied external functions. In the P4box programming model, when a programmable block is invoked, control first passes to a monitor, also written in P4, before passing to the intended programmable block. Similarly, when a programmable block completes processing, control first passes to the monitor before returning to the device. This allows a monitor to modify the behavior of programmable blocks in a well-defined way.

Monitors can also interpose on calls to external functions: when a programmable block invokes an external function, control first passes to the monitor, then the function, and then back to the monitor again, before returning to the programmable block. A monitor can thus modify the apparent behavior of a external function. Monitors are declared and defined at the top level of a P4 program, alongside control blocks, parser blocks, and other top-level declarations. The syntax for a monitor is:

```

monitor <name> ( [param-list] ) on <object> {

[local-declarations]

(before | after) { <p4-statements> }

}

```

Each monitor is identified by a unique  $\langle name \rangle$  and may receive additional parameters ( $\langle param-list \rangle$ ) containing headers and metadata in addition to the parameters of the monitored object. Every monitor must be associated with a data plane  $\langle object \rangle$ , which can be a parser, control block or extern function. The resource type defines the set of  $\langle p4-statements \rangle$  elements the monitor supports (e.g., match-action tables, counters, registers, parser states). Monitors can have two types of methods, namely: *before* and *after*, which specify code fragments that are executed before and after the monitored resource, respectively. Finally, they can also contain local declarations (e.g., actions, tables) visible inside the monitor but not the monitored block.

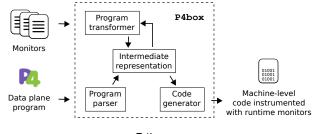

Figure 3.2 shows the P4box workflow. The original P4 program and P4 source files defining runtime monitors are provided to P4box which combines the original program with the monitors at the intermediate level to produce a new program suitable for further compilation. At the end, machine-level code containing all monitors is generated for a variety of targets. During the instrumentation process, P4box takes advantage of language features provided by P4 such as separate scopes and namespaces in addition to static analysis to provide the following guarantees for each monitor:

• Complete mediation: The flow of execution of the original data plane program

will always pass through a monitor (when one is defined by the programmer). This means it is not possible for the original program to circumvent a monitor.

Non-interference: The original program cannot interfere in the operation of a monitor (e.g., by modifying its local variables or headers), which means monitors are completely isolated from the data plane program.

Together, the complete mediation and non-interference properties allow monitors to restrict what the original P4 program is allowed to do even when the latter is *untrusted*. Hence, monitors are also a form of software sandbox that can be used to encapsulate untrusted or buggy P4 programs. Next, we show examples and describe each of the three kinds of monitors P4box supports in more detail.

Figure 3.3: Example of control block monitor to enforce header protection.

```

1

monitor hdrInvMonitor() on Pipeline {

2

ipv4_t protec_ipv4;

3

udp_t protec_udp;

4

5

before {

protec_ipv4 = hdr.inner_ipv4;

6

protec_udp = hdr.inner_udp;

7

}

8

9

10

after {

if( protec_ipv4 != hdr.inner_ipv4 ||

11

12

protec_udp != hdr.inner_udp ){

*Run enforcement action

13

14

(e.g., restore original header

value, notify the control plane,

15

16

write log) */

17

}}

15 }

```

#### 3.2 Data plane monitors

#### **3.2.1** Control block monitors

P4box can attach monitors to top-level control blocks. In this case, *before* and *after* contain statements that will be executed at the beginning and the end of block, respectively. Figure 3.3 shows an example of a control block monitor. This monitor is responsible for ensuring that a header is not erroneously modified by the data plane program. The monitor is attached to the processing pipeline and has two elements: i) before the programmable block, it collects state from the original packet as soon as it is parsed (1.5-8); and ii) after the block, it tests whether monitored headers were modified (1.10-17). Local variables (i.e., visible only to the monitor) are used to store protected headers (1.2-3). If the monitor detects a violation, different actions can be performed to enforce the desired property (e.g., restore the original header value, notify the network controler, log an event), being up to the programmer to decide what to do.

P4box performs the instrumentation of control blocks in three steps: first, monitor parameters containing headers and metadata are merged with parameters of the monitored block (e.g., joining the fields of two structs to create a super struct). If during this process P4box identifies there is no feasible mapping (e.g., because there is no parameter in the monitored block that supports the merge operation), a message is emitted and the instrumentation process is aborted; second, *before* and *after* blocks as well as local declarations are inserted in the monitored block; finally, a name resolution pass maps monitor names to their new namespaces. The left part of Figure 3.4 illustrates this transformation, where a generic control block is instrumented with its monitoring primitives. A corresponding example is shown on the right, representing the instrumentation performed to the monitor specified in Figure 3.3. As a result of this transformation, all packets crossing the control block also pass through the monitor since P4 assumes network devices execute statements in order.

#### **3.2.2 Parser monitors**

Parser monitors, on their turn, can be attached to top-level parsers. As such, *before* and *after* can contain finite state machines and both of them must have a start and accept state. It is possible to specialize a parser monitor to an specific parser state, in which

```

control <control_name>

control pipeline(inout newHeaders hdr,

( <combined-params> ){

inout metadata meta){

[local_elements]

ipv4_t protec_ipv4;

[monitor_local_elements]

apply {

apply{

protec_ipv4 = hdr.inner_ipv4;

[before_statement]

if(protec_ipv4 != hdr.inner_ipv4

[block_statement]

|| protec_udp != hdr.inner_udp){

[after_statement]

}

}

}

}

}

```

Figure 3.4: Instrumentation of control blocks.

case *before* and *after* are associated only to the latter. An example of a parser monitor is shown in the next chapter (Figure 4.2 – lines 6 to 17), where the monitor is attached to the parse\_ethernet state and used to extract an enforcement header. Parser monitors are also particularly useful for extracting packet bits that for some reason (e.g., confidentiality) should not be visible to the data plane program.

To instrument parsers, P4box takes into account if *before* and *after* are attached to states or not. If not, P4box assumes the start and end (i.e., accept) states of the monitored parser as its hooking points. Otherwise, it applies the transformations shown in the left part of Figure 3.5 to the monitored parser. Assuming state  $S_k$  is being monitored, P4box links the finite state machine specified inside *before* (before\_FSM) between states  $S_{k-1}$  and  $S_k$  by modifying state transitions. An analogous process is performed for the finite state machine specified inside *after* (after\_FSM), linking it between states  $S_k$  and  $S_{k+1}$ . The right part of Figure 3.5, on its turn, shows an example of these transformations, where P4box performs the instrumentation to the parser monitor specified in Figure 4.2. Instead of transitioning directly from state parse\_ethernet to parse\_ipv4, the execution flow goes through states \_M\_START\_ and parse\_wp\_header.

#### **3.2.3 Extern monitors**

Extern monitors are attached to extern calls. Their capabilities are restricted to what actions can do in P4 because of limitations the latter have on extern callers (e.g., it is not possible to make local declarations or invoke a table from inside an action). Similar to parser monitors, extern monitors can also be specialized to subgroups of a resource (e.g., a subset of the headers emitted to a packet). In this case, a type signature is used to apply

```

parser <parser_name>

parser pipeline(packet_in packet,

( <combined-params> ){

out newHeaders hdr){

[local_elements]

[monitor_local_elements]

state parse_ethernet {

transition _M_START_;

state <s_k-1> {

}

transition [before_FSM];

state _M_START_ {

transition select(...){

[state before_FSM {

16w0xFFFF : parse_wp_header;

transition <s_k> }]

state <s_k> {

}

transition [after_FSM];

}

state parse_wp_header {

[state after_FSM {

transition parse_ipv4;

transition <s_k+1> }]

}

state <s_k+1> {

state parse_ipv4 {

transition <s_k+2>

transition parse_tcp;

}

}

}

}

```

Figure 3.5: Instrumentation of parsers.

a monitor only to part of the extern calls. An example is presented in Figure 4.2 – lines 20 to 24, where the extern monitor is applied only to calls for emitting headers of type ethernet\_t. Extern monitors are useful to mediate how the data plane program interacts with the platform underlying it.

P4box instruments extern calls by adding *before* and *after* blocks right before and after every monitored call, respectively. The left part of Figure 3.6 illustrates this transformation, where the same extern call appears twice (inside an action and directly in the control block body). For the particular case in which a monitor has a type signature, only calls with that signature are instrumented. As an example, the right part of Figure 3.6 shows the instrumentation to the extern monitor specified in Figure 4.2.

Figure 3.6: Instrumentation of extern calls.

```

control <control_name>

control DeparserImpl(

( <combined-params> ){

packet out packet,

action <action_name>(){

in newHeaders hdr){

apply{

[before_statement]

. . .

[extern_A_call]

packet.emit(hdr.ethernet);

[after_statement]

packet.emit(hdr.wp_header);

packet.emit(hdr.ipv4);

}

. . .

}

apply{

}

[before_statement]

[extern A call]

[after_statement]

. . .

}

}

```

| b ::= v<br>  f<br>  m<br>  !b<br>  b    b<br>  b && b<br>  b == b<br>  b != b<br>  i >= i<br>  i <= i<br>  i < i<br>  i > i<br>  i == i<br>  i != i | <pre>m ::= forward()     traverse_path()     constant(f)     if(b, b, [b])     extract_header(h)     emit_header(h) i ::= v     f     i * i     i / i     i % i     i + i     i - i</pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 3.7: Assertion language grammar.

#### **3.3 Monitor correctness**

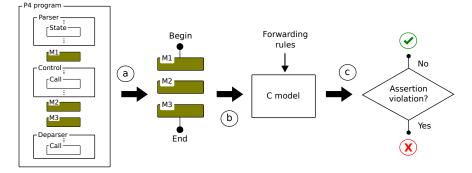

Monitors are less likely to contain bugs compared to P4 programs due to their smaller size and complexity. For example, a monitor to enforce header protection has no more than a dozen of lines of code while traditional P4 programs usually have hundreds to thousands of lines (two to three orders of magnitude larger) (STOENESCU et al., 2018; LIU et al., 2018). Despite their simplicity, monitors are still subject to bugs and misconfigurations. For this reason, we developed an automated framework for allowing programmers to check invariants in their specified monitors. In this section, we describe how developers can verify properties in monitors from the same P4 program. We refer to Section 5.2 for details about how we extend this idea for proving network-wide properties on sets of monitors distributed over a network topology.

Our framework is inspired in assert-p4 (NEVES et al., 2018), a state-of-the-art tool for checking invariants in P4 programs. Like assert-p4, our framework is based on assertions and symbolic execution (see Figure 3.9 for its workflow). First of all, programmers annotate monitors with assertions expressing properties of interest. We adopt the same assertion language as proposed in Neves et al. (2018), since monitors are essentially comprised of P4 constructs. Figure 3.7 shows the language grammar. As we can see, each assertion is composed of a boolean expression (b), which may include constant values (V), header fields (f), primitive methods (m) or logical, relational and arithmetic expressions involving these elements.

Note that our concept of assertion is more general than the C-style assertions found in traditional programming languages, and includes both *location-restricted* and *locationunrestricted* elements. A location-restricted element is one that tests the value of a monitor variable where the assertion is specified, as in traditional programming languages like C or Java. The location-unrestricted ones, in contrast, apply to the entire monitor space. They can be used for example to guarantee higher level properties that the monitors are expected to satisfy, such as data invariance – asserting certain headers are never modified throughout the code.

The methods work as follows. if( $b_1$ ,  $b_2$ ,  $[b_3]$ ) is similar to traditional conditional statements: if expression  $b_1$  is true, then expression  $b_2$  will be evaluated, otherwise the alternative  $b_3$  will be evaluated). This is the only location restricted method, with all other ones being unrestricted. traverse\_path() indicates if a given construct inside a monitor (e.g., an action) will be eventually traversed before the monitor execution ends. constant(f) is true if field f will not change from the assertion location onwards, i.e., until the execution of *all* monitors terminate. forward() returns true if the packet is not dropped after the execution of all monitors. extract\_header(h) is true if a header h has been, or will be, extracted from the packet. Finally, emit\_header(h) returns true if packet will be transmitted with header h.

Figure 3.8 shows an example assertion (in bold purple – line 6) to the monitor described in Section 3.2.1. The assertion contains a location-unrestricted method and tests whether the *protec\_ipv4* variable is not being erroneously modified by the monitor. Once annotated, monitors are assembled in a "virtual program" respecting the same order of execution as the monitored code. This means if monitors A and B are monitoring programmable blocks X and Y, respectively, and X runs before Y, then A will precede B. In addition, the assembled code also contains all header and metadata definitions from the original program, which are treated as symbolic inputs by the verification engine and enable programmers to check invariants on monitors that manipulate program state (e.g., change a header value). After the assembling phase, the new virtual program is translated into an equivalent model in C, and assertions are checked using a symbolic execution tool.

Translating monitors to C allows us to use an off-the-shelf symbolic execution engine, e.g., KLEE (CADAR; DUNBAR; ENGLER, 2008), to check the desired properties. Moreover, tools to ensure the correctness of the translation process are also available<sup>1</sup>. As an example, Figure 3.10 shows the resulting model for the annotated monitor presented in Figure 3.8 (we omit some parts for the sake of simplicity). The *main* code (lines 25-32) controls the call order for the monitors, which are on their turn modeled as additional functions (lines 14-23). We make all monitor inputs (i.e., packet headers, metadata and protected state) symbolic (lines 8-11), so that they can be comprehensively checked by

<sup>&</sup>lt;sup>1</sup><https://github.com/gnmartins/assert-p4>

Figure 3.8: Example of annotated monitor.

```

monitor hdrInvMonitor() on Pipeline {

1

ipv4_t protec_ipv4;

2

3

udp_t protec_udp;

4

5

before {

@assert("constant(protec_ipv4)");

6

7

protec_ipv4 = hdr.inner_ipv4;

protec_udp = hdr.inner_udp;

8

9

}

10

after {

11

if( protec_ipv4 != hdr.inner_ipv4 ||

12

protec_udp != hdr.inner_udp ){

13

/*Run enforcement action

14

(e.g., restore original header

15

value, notify the control plane,

16

17

write log) */

18

}}

19 }

```

Figure 3.9: Workflow for checking monitor correctness. M1, M2, M3 = annotated monitors. a = monitor assembling. b = model extraction. c = symbolic execution.

the symbolic execution engine. Local monitor definitions (e.g. variables and match-action tables) are modeled as unique global constructs (lines 4-5). In particular, each table and action definition is modeled as a separate function. Finally, each assertion is modeled independently, and usually involves variables that are set and tested at relevant points in the program. For example, the assertion modeled in lines 16 and 30 checks whether the monitor, which should ensure a packet header is not modified, is not itself erroneously modifying the header. We refer to Neves et al. (2018) for more details on the translation process. A control plane configuration, expressed in the form of forwarding rules during the model extraction phase, can be considered if a monitor contains one or more match-action tables. Finally, if the verification fails, a trace is generated containing the sequence of commands executed to reach the violated assertion to help programmers correcting the error.

Figure 3.10: Equivalent model in C to the monitor described in Section 3.2.1.

```

#include "klee.h"

1

2

3

//Model monitor locals

4

ipv4_t protec_ipv4;

5

udp_t protec_udp;

6

7

//Make monitor inputs symbolic

void symbolizeInputs(){

8

klee_make_symbolic(&hdr, sizeof(hdr), "hdr");

9

klee_make_symbolic(&meta, sizeof(meta), "meta");

10

11 }

12

13 //Model monitor logic

14 void hdrInvMonitor_before(){

15 protec_ipv4 = hdr.inner_ipv4;

16 constant_protec_var = protec_ipv4;

protec_udp = hdr.inner_udp;

17

18 }

19

20 void hdrInvMonitor_after(){

21 if( protec_ipv4 != hdr.inner_ipv4 ||

22

protec_udp != hdr.inner_udp ){ ... }

23 }

24

25 int main(){

symbolizeInputs();

26

hdrInvMonitor_before();

27

28 hdrInvMonitor_after();

29

//Model assertions

30 hasChanged( constant_protec_var, protec_ipv4 );

return 0;

31

32 }

```

#### **3.4 Implementation**

We implemented a prototype of P4box by extending the  $P4_{16}$  reference compiler<sup>2</sup>. Our system has around 3K lines of C++ code and is publicly available<sup>3</sup>. We modified the front-end compiler to: i) instrument programs by adding additional passes over their intermediate representation; and ii) generate our C models.

<sup>&</sup>lt;sup>2</sup><https://github.com/p4lang/p4c>

<sup>&</sup>lt;sup>3</sup><https://github.com/mcnevesinf/p4box>

#### **4 CASE STUDY: DYNAMIC ENFORCEMENT**

The value of a mechanism like P4box is best seen through examples. In this section, we show how P4box can be used to dynamically enforce several kinds of properties in programmable networks.

#### **4.1 Program Properties**

As defined in Section 2.2, program properties concern the behavior of a program running on an individual device. These properties must hold regardless of how the device is configured or connected in a topology. They are also referred to as *network function properties* in the literature (ZAOSTROVNYKH et al., 2017). In this work, we consider program properties that are either semantic or general safety properties. Below we show how we enforce two program properties of interest, well-formedness and header protection.

Well-formedness. The output of a data plane program is *well-formed* if it complies with relevant protocol standards. *Well-formedness* determines the interoperability between multiple implementations of a protocol stack. In terms of programmable data planes, this means that the packets produced by one data plane program can be processed by another, and vice-versa. Enforcing well-formedness invariants is particularly useful in hybrid networks (i.e., networks containing both P4-enabled and legacy devices), where the elements may not support the same set of protocols. P4box can enforce wellformedness properties (e.g., packets do not contain both an IPv4 and IPv6 header, ICMP packets always have an IPv4 header) with simple checks of header validity at the end of the processing pipeline.

Header protection. In some cases, it may be desirable to ensure that a header is not modified by a forwarding device or programmable block. For example, in an deployment where VLANs are used to isolate potentially untrusted domains, it may be necessary to provide strong assurance that a VLAN tag is not modified by a forwarding device. P4box can be used to ensure that headers are not modified by collecting the appropriate packet state at the beginning of the processing pipeline (e.g., the value of a VLAN tag), and comparing it against the emitted headers. Such properties can be easily extended to allow only transformations to a pre-defined domain (e.g., source MAC can be modified only to a set of output interface addresses).

#### **4.2 Network-Wide Properties**

We now describe how P4box can enforce common network-wide properties. As a reminder, these properties concern forwarding devices when configured and connected in a particular topology (see Section 2.2). Although we focus on general safety and context-independent properties in this work, P4box could also be used to enforce semantic and context-dependent (or stateful) ones. We leave exploring the latter as a future work.

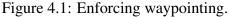

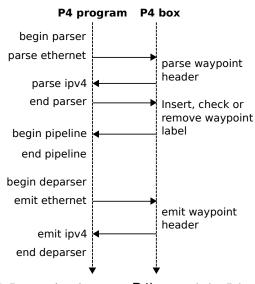

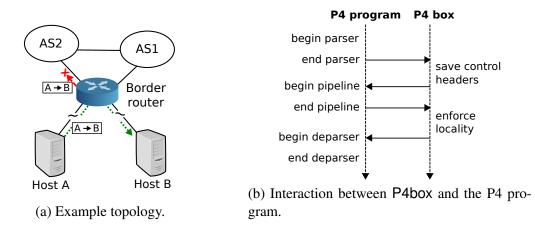

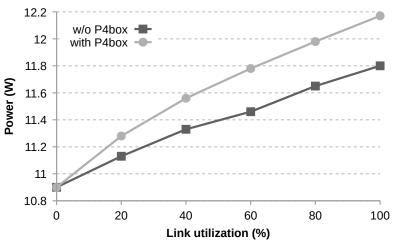

**Waypointing** Network operators may want to force packets to pass through a sequence of devices (waypoints) before the network delivers them to an end host. P4box can enforce waypoint properties by checking and updating labels whenever these packets cross a device in the chain. As an example, Figure 4.1a shows a scenario where packets coming from an external network (i.e., through router R) must first be inspected by an IDS system before arriving at a web server (hosts H1–H3). In this case, a P4box monitor in R introduces labels in each packet in order to enforce waypointing. These labels are then updated by another monitor at switch S1, and a third monitor checks them at switch S2 for dropping packets that are destined to the web servers and do not contain the updated tag (L1). Figure 4.1b shows how P4box interacts with the P4 program to enforce waypointing, where vertical arrows represent the flow of execution. Note that P4box traps the program at three points: first, between the parsing of the Ethernet and IPv4 headers, to check whether the packet contains a label and extract the latter; second, right before the beginning of the match-action pipeline, to operate on the label (e.g., check, updates or remove) depending on how the device is connected in the topology; finally, to emit the label during the deparsing phase.

Figure 4.2 shows a summary (with some parts omitted) of the code used to enforce waypoint properties. Each trap is programmed as a separate monitor. Parser (lines 6-17) and extern (lines 20-24) monitors are employed to extract and emit labels, which are declared in the *wp\_header* header (line 2). Moreover, a control block monitor uses match-action tables to insert, check/update and remove labels according to the incoming/outgoing ports of the packet. P4box monitors can be configured (proactive or reactively) to reroute packets on-the-fly and correct property violations. Moreover, we can extrapolate the labeling mechanism described above to enforce path conformance (i.e., to guarantee that the actual path taken by a packet conforms to the operator policy). In this case, P4box monitors check and update packet labels on every hop.

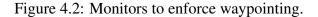

Traffic locality. Sometimes operators want to preserve traffic locality, e.g., pack-

(b) Interaction between P4box and the P4 program.

```

struct p4boxState {

1

2

waypoint_t wp_header;

3

}

4

5

//Parser monitor to extract enforcement header

6

monitor wpParser(inout p4boxState pstate) on ParserImpl {

7

after parse_ethernet {

8

state start {

transition select(packet.lookahead<bit<32>>()){

9

10

16w0xFFFF : parse_wp_header;

default : accept;

11

12

}

13

}

14

state parse_wp_header {

packet.extract(pstate.wp_header);

15

16

transition accept;

17 }}}

18

//Extern monitor to emit enforcement header

19

20 monitor wpExtern(inout p4boxState pstate)

21

on emit<ethernet_t>{

22

after {

23

packet.emit(pstate.wp_header);

24 }}

25

26 monitor wpControl(inout p4boxState pstate) on Pipeline {

27

28

table check_waypoint {...}

29

. . .

30

31

before {

//Enforce waypointing property

32

33

insert_label.apply();

34

check_waypoint.apply();

35

remove_label.apply();

36 }}

```

Figure 4.3: Enforcing traffic locality.