# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

#### Geração de Processador para Aplicação Específica

por

MÁRCIO EDUARDO KREUTZ

Dissertação submetida à avaliação como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

> Prof. Altamiro Amadeu Susin Orientador

Porto Alegre, agosto de 1997

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Kreutz, Márcio Eduardo

Geração de Processador para Aplicação Específica / por Márcio Eduardo Kreutz. - Porto Alegre: CPGCC da UFRGS, 1997.

111f.: il.

Dissertação (mestrado) - Universidade Federal do Rio Grande do Sul. Curso de Pós-Graduação em Ciência da Computação, Porto Alegre, BR - RS, 1997. Orientador: Suzim, Altamiro A.

1. Microcontrolador para aplicação específica. 2. Pipeline 3. Sistema Integrado para Aplicação Específica. 4. Otimização do conjunto de instruções do processador 5. Microcontrolador MCS8051. I. Suzim, Altamiro Amadeu. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitora: Profa. Wrana Panizzi

Pró-Reitor de Pós-Graduação: Prof. José Carlos Ferraz Hennemann Diretor do Instituto de Informática: Prof. Roberto Tom Price Coordenador do CPGCC: Prof. Flávio Rech Wagner Bibliotecária-Chefe do Instituto de Informática: Zita Prates de

Oliveira

### **Agradecimentos**

Gostaria de agradecer primeiramente a duas pessoas que tornaram possível a realização deste trabalho, seja pelo constante apoio e compreensão, seja pelas oportunidades oferecidas: Altamiro Suzim e Luigi Carro.

Em segundo lugar, gostaria de agradecer a todos os colegas de trabalho no grupo de microeletrônica, pela amizade e por proporcionarem um ambiente de trabalho agradável e construtivo; principalmente a Carlos Antonio Alba Pinto que gentilmente cedeu horas de trabalho em todos os momentos em que sua ajuda tornouse imprescindível.

Agradeço também os professores da graduação que me incentivaram a seguir o caminho do mestrado, inclusive ajudando com as recomendações: Raul Ceretta (UFSM) e André Lemos (Unijuí).

Finalmente, agradeço ao Brasil pelo Instituto de Informática da UFRGS, com todos os seus recursos humanos e materiais, indispensáveis para a realização deste trabalho.

À todos, VIELEN DANK!!!

# Sumário

| Lista de Abreviaturas                                      | 5   |

|------------------------------------------------------------|-----|

| Lista de Figuras                                           | 7   |

| Lista de Tabelas                                           | 9   |

| Resumo                                                     | 10  |

| Abstract                                                   | 12  |

|                                                            |     |

| 1                                                          | 14  |

| Introdução                                                 |     |

| 1.1 Contribuições                                          | 18  |

| 1.2 Organização da dissertação                             |     |

| 2 A abordagem ASIP para o MCS8051                          | 21  |

| 2.1 O Projeto de ASIPs                                     | 22  |

| 2.2 O Processo de criação do MCS8051 ASIP                  |     |

| 3 Arquitetura do MCS8051                                   | 29  |

| 3.1 Descrição VHDL do MCS8051                              | 30  |

| 4 A abordagem Pipeline para o MCS8051                      | 38  |

| 4.1 Motivações para o uso do Pipeline                      | 40  |

| 4.2 A escolha do modelo do Pipeline                        | 41  |

| 4.3 A implementação do Pipeline                            |     |

| 5 Síntese Lógica do MCS8051                                | 51  |

| 5.1 Síntese do MCS8051 no Alliance                         | 51  |

| 5.1.1 Resultados da Síntese Lógica no Alliance             |     |

| 5.2 Síntese do MCS8051 no Altera                           |     |

| 5.2.1 Resultados da Síntese Lógica no Altera               |     |

| 6 O Compilador C para o MCS8051 ASIP                       |     |

| 6.1 Alterações realizadas sobre o Compilador CCC51         |     |

| 6.2 A implementação do CCC51                               |     |

| 6.3 Resultados obtidos                                     |     |

| 7 Conclusões e trabalhos futuros                           |     |

| Anexo 1 Síntese Lógica no Alliance                         |     |

| Anexo 2 Simulação no Alliance                              | 80  |

| Anexo 3 Código em linguagem montadora da aplicação decoder |     |

| gerado pelos compiladores CCC51 e Keil C                   | 0.5 |

| Compiler                                                   | 85  |

| Bibliografia                                               | 108 |

.

#### Lista de Abreviaturas

ACC Acumulador.

AHDL Altera Hardware Description Language.

ASIC Application Specific Integrated Circuit.

ASIP Application Specific Instruction-Set Processor.

ASIS Application Specific Integrated System.

C Linguagem de programação C.

CCC51 C Cross Compiler to MCS8051.

CCC51 - I CCC51 primeira otimização.

CCC51 - II CCC51 segunda otimização.

CCC51 - III CCC51 terceira otimização.

CPGCC Curso de Pós-Graduação em Ciência da Computação.

FPGA Field-Programmable Gate Arrays.

HDL Hardware Description Language.

HW Hardware.

MUX Multiplexador.

PC Program Counter.

PO Parte Operativa.

PSW Processor Status Word.

SIAE Sistema Integrado para Aplicação Específica.

SP Stack Pointer.

SW Software.

RISC Reduced Instruction-Set Computer.

UFRGS Universidade Federal do Rio Grande do Sul.

ULA Unidade Lógico-Aritmética.

VHDL Very high speed integrated circuits Hardware Description Language.

# Lista de Figuras

| FIGURA 2.1 - O projeto de ASIPS                                                                                  | 25 |

|------------------------------------------------------------------------------------------------------------------|----|

| FIGURA 2.2 - Etapas na criação de um 8051 adaptado a uma aplicação                                               | 28 |

| FIGURA 3.1.1 - Fluxo dos sinais entre as entidades VHDL da descrição do 8051                                     | 33 |

| FIGURA 3.1.2 - MUX para o endereçamento da RAM                                                                   | 34 |

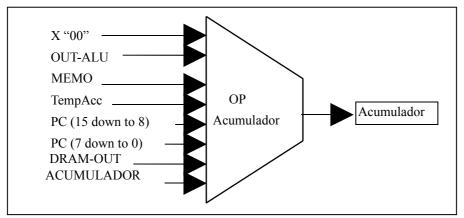

| FIGURA 3.1.3 - MUX para escrita no Acumulador                                                                    | 35 |

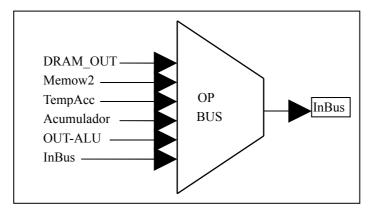

| FIGURA 3.1.4 - MUX para escrita no Registrador InBus                                                             | 36 |

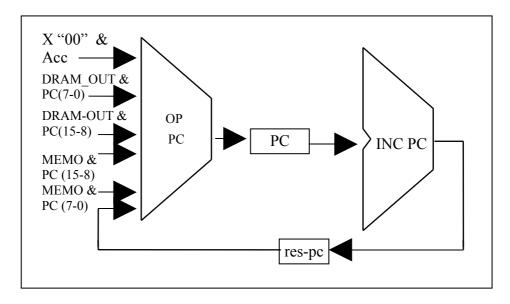

| FIGURA 3.1 5 - MUX para escrita no PC e Incrementador do PC                                                      | 36 |

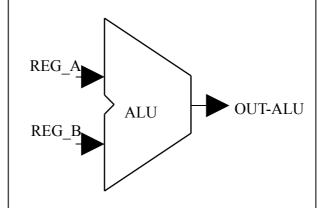

| FIGURA 3.1.6 - Registradores de entrada da Unidade Lógico-Aritmética                                             | 36 |

| FIGURA 3.1.7 - MUX para escrita no Registrador <i>Reg_a</i> da ULA                                               | 37 |

| FIGURA 3.1.8 - Parte Operativa do 8051 com pipeline                                                              | 37 |

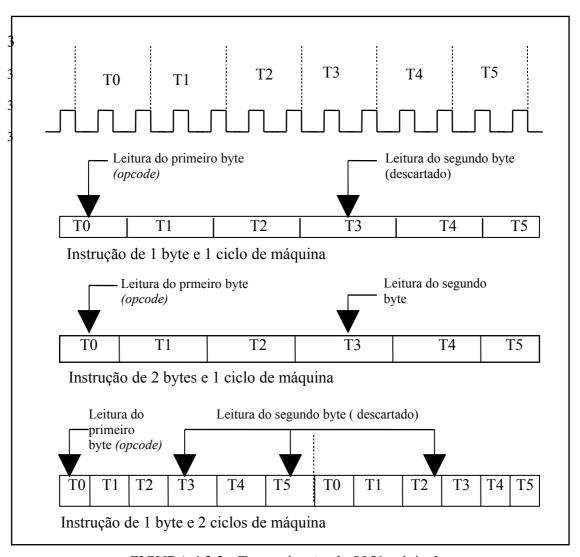

| FIGURA 4.2.1 - Pipeline de instruções com 1 instrução por ciclo de relógio                                       | 42 |

| FIGURA 4.2.2 - Pipeline implementado para o 8051                                                                 | 43 |

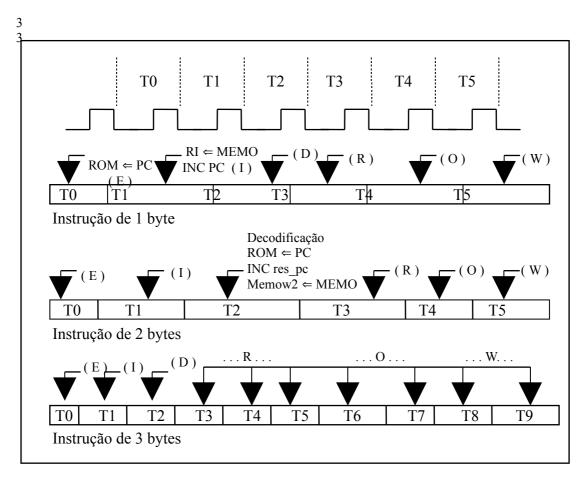

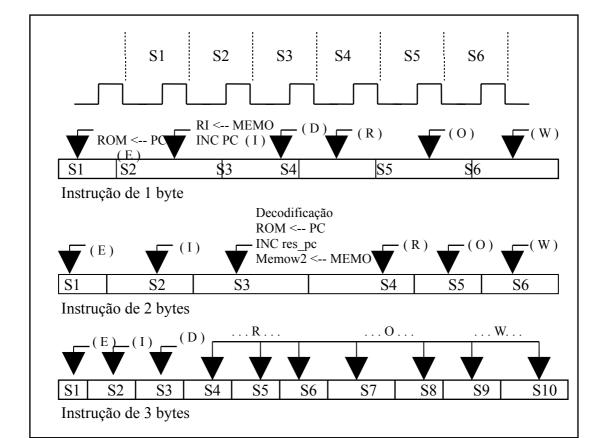

| FIGURA 4.3.1 - Fases E, I e D de execução do <i>pipeline</i>                                                     | 49 |

| FIGURA 4.3.2 - Temporização do 8051 original                                                                     | 47 |

| FIGURA 4.3.3 - Temporização do 8051 com pipeline                                                                 | 48 |

| FIGURA 4.3.4 - Microinstruções na Parte de Validação para instrução com temporização original                    | 50 |

| FIGURA 4.3.5 - Microinstruções na Parte de Validação para instrução com temporização adequado ao <i>pipeline</i> |    |

| FIGURA 5.1.1 - Código VHDL contendo os modos de endereçamento da RAM                                             | 54 |

| FIGURA 5.1.2 - Entradas para o Registrador InBus                                                                 | 58 |

| FIGURA 5.1.3 - Entradas para o Registrador Acumulador                                                            | 58 |

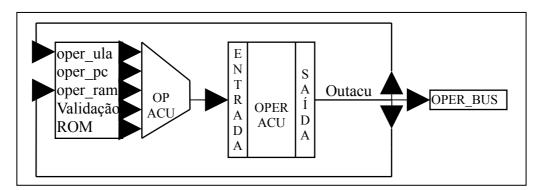

| FIGURA 5.1.4 - Entradas e Saídas da entidade oper_acu                                                            | 58 |

| FIGURA 5.1.5 - Multiplexador para o envio do microcódigo à Parte Operativa                                       | 61 |

| FIGURA 5.2.1 - Código VHDL de duas instruções na Parte de Validação                 | 62 |

|-------------------------------------------------------------------------------------|----|

| FIGURA 5.2.2 - Código VHDL da Parte de Validação adaptado ao Altera                 | 63 |

| FIGURA 5.2.3 - Multiplexador com a palavra de microcódigo enviada à Parte Operativa | 64 |

# Lista de Tabelas

| Com pipeline do 8051                                                                                             | 61 |

|------------------------------------------------------------------------------------------------------------------|----|

| TABELA 5.1.2 - Resultados da Síntese Lógica no Alliance para a descrição sem <i>pipeline</i> do 8051             | 62 |

| TABELA 5.2.1 - Resultados do processo de Síntese Lógica no Altera para a descrição do 8051 sem <i>pipeline</i> . | 64 |

| TABELA 5.2.2 - Resultados do processo de Síntese Lógica no Altera para a descrição do 8051 com <i>pipeline</i>   | 64 |

| TABELA 6.1.1-Rotinas C para a adaptar o CCC51 às aplicações específicas                                          |    |

| TABELA 6.2.1 - Instruções substituídas no CCC51 - I                                                              | 71 |

| TABELA 6.3.1 - Substituição das instruções MOV que quebram o <i>pipeline</i>                                     | 73 |

| TABELA 6.3.2 - Instruções de movimentação implementadas no CCC51 - III                                           | 74 |

| TABELA 6.3.3- Número de instruções em linguagem montadora necessárias para implementar as aplicações             | 75 |

| TABELA 6.3.4 - Número de instruçõs diferentes em cada aplicação                                                  | 75 |

#### Resumo

Este trabalho propõe a geração de uma arquitetura dedicada a aplicações específicas, baseadas no microcontrolador MCS8051. Por ser utilizado na solução de problemas em indústrias locais, este processador foi escolhido para servir como base em um sistema dedicado. O 8051 dedicado gerado deverá permitir a integração completa do sistema, proporcionando um aumento do valor agregado e, conseqüentemente, a diminuição do custo.

Busca-se com a otimização da arquitetura obter um conjunto de instruções reduzido, construído com as instruções mais utilizadas em cada aplicação. O objetivo principal da otimização do conjunto de instruções está relacionado ao fato de que os circuitos decodificadores e geradores de microcódigo da parte de controle ocupam uma área significativa do processador. Uma otimização no sentido de reduzir-se o conjunto de instruções, portanto, resulta numa economia de área, o que vem de encontro com a idéia da integração completa do sistema com o processador.

Um processador dedicado a aplicações específicas (ASIP) irá possuir um custo maior do que a sua versão original, devido as otimizações realizadas. Para compensar este custo, uma alternativa a seguir é a integração completa do sistema. Um Sistema Integrado para Aplicações Específicas (SIAE) torna-se desejável, pois aumentando o valor agregado do circuito possibilita-se a redução do custo pela eliminação de conexões da placa, do encapsulamento de outros circuitos, entre outros motivos. Todavia, para que um SIAE possa ser construído com um custo aceitável, é necessário que seja construído em uma área que não exceda muito a área original do processador. Tenta-se fazer isto neste trabalho, através da implementação de aplicações com poucas instruções diferentes.

Por ser uma arquitetura comercial, o 8051 possui um grande parque de *software* desenvolvido e resolvendo problemas. Isto pode ser considerado uma vantagem pois, *software* básicos como por exemplo, compiladores, já estão desenvolvidos. Outra vantagem é o grande número de engenheiros treinados na sua utilização. Desse modo, torna-se necessária a criação de uma compatibilidade de *software*, para preservar o que já está desenvolvido. Uma vez que a programação em nível de linguagem montadora tende a constituir-se em uma tarefa cansativa e sujeita a erros, é desejável que se tenha uma compatibilidade em alto nível, ou seja, através de um compilador.

Para criar a compatibilidade de SW necessária é realizada a otimização de um compilador C desenvolvido para o 8051. A escolha pela linguagem C deve-se ao fato de sua grande utilização. O compilador C otimizado procura utilizar um conjunto de instruções reduzido para obter a economia de área. Quando uma instrução necessita ser utilizada e não está presente no conjunto de instruções desejado, o compilador tenta substituí-la por outra(s). Um conjunto de instruções é utilizado para cada aplicação, sendo constituído pelas instruções mais utilizadas por esta. Para determinar as instruções mais utilizadas de cada aplicação é realizada uma análise estática sobre um código em linguagem montadora previamente compilado. As instruções implementadas serão sempre parte do conjunto de instruções original do 8051, de modo que novas instruções não serão criadas.

Um programa em linguagem montadora gerado com um conjunto de instruções reduzido (RISC) normalmente terá um número maior de instruções do que o seu

equivalente com o conjunto de instruções completo (CISC). Isto ocorre porque possivelmente algumas substituições de uma instrução por outras, terão que ser realizadas. Como as instruções que serão utilizadas nas substituições pertencem ao conjunto de instruções original, o programa gerado com o compilador otimizado poderá executar em um tempo maior do que se fosse compilado com o código CISC. Para compensar esse atraso foi implementado um *pipeline* de instruções para o 8051.

Este trabalho apresenta resultados da Síntese Lógica em *Standard Cell* e FPGA da arquitetura otimizada. Além disso, resultados de programas em linguagem montadora gerados com o compilador otimizado, são também apresentados.

**Palavras-chave**: Microcontrolador para aplicação específica, Otimização do conjunto de instruções do processador, Pipeline, Sistema Integrado para Aplicação Específica, Microcontrolador MCS8051.

#### Title: "Application Specific Processor Generation"

#### **Abstract**

This work discusses a processor for specific applications architecture, based on the MCS8051 microcontroller. This processor is used as a solution for many local industry applications, being the base of dedicated systems. The dedicated 8051 generated should allow complete integration of the system, and with the added value to the chip, reduced costs.

The architecture optimization will produce as result a reduced instruction set, made by the often used instructions for each application. The main instruction set optimization goal refers to the instructions decoders and microcode generators in the control part, because a large area in the processor is needed to implement them. Thus, a reduced instruction set will allow area savings, making possible the complete system integration in a chip.

An ASIP architecture will have a higher cost than the original one. An alternative to solve this problem is add value to the chip, creating an Application Specific Integrated System (ASIS). An ASIS can be made with a acceptable cost, if it's possible to integrate other circuits to the chip without area increase. This can be done in the area saved by using fewer implemented instructions.

Because the 8051 is a commercial architecture, there is a large amount of software developed for it. This can be considered an advantage because basic softwares like compilers are available, being not necessary to create them. Another advantage refers to the large number of engineers trained to use the 8051. To preserve the already developed applications it's necessary to mantain software compatibility. Assembler level programming is very boring an error prone task, being desirable to have software compatibility at higher levels through the use of high level languages.

To create the necessary SW compatibility, a C compiler developed for 8051 was optimized. The chose for C language refers to its large utilization. The optimized C compiler tries to use a reduced instruction set, formed with the most important instructions for each application, in order ro save area. When an instruction needs to be used in an application, and it's not present in the instruction set, the compiler tries to replace it with other instructions. The compiler will not use instructions not present in the original 8051 instruction set. So, new instructions will be not created. To create an instruction set formed with the most important instructions for each application, a static analysis is made on a precompiled assembler source.

An assembler source generated with a reduced instruction set (RISC) will probably have more instructions than the same assembler generated with a full instruction set (CISC). This can be explained because of the replacements instruction. If one instruction is replaced by other two, and these are from the original instruction set, probably the time needed to execute them would be higher. In order to deal with this problem, an instruction pipeline was implemented to the 8051.

This work presents Standard Cells and FPGA results of Logic Synthesis of the optimized architecture. Also, assembly programs generated by the optimized compiler are presented.

**Keywords**: Application specific microcontrollers, Core Processor Instruction set optimization, Pipeline, Application Specific Integrated System, MCS8051 Microcontroller.

#### 1 Introdução

Microcontroladores são Circuitos Integrados que implementam em uma pastílha de Silício um Sistema Computacional completo. Integram um microcontrolador: Unidade Central de Processamento, memórias RAM e ROM, portas de entrada e saída, temporizadores, etc. As características deste tipo de circuito, conferem-lhe funcionalidades largamente utilizadas na indústria para diversas aplicações, dentre as quais: impressora de cheques, controle de motores, controle de barramento de chão de fábrica, etc. Como um destaque na Indústria brasileira, pode-se citar o Microcontrolador Intel MCS-8051. O projeto deste chip data dos anos 80. Face o vertiginoso avanço tecnológico das áreas de informática e microeletrônica pode ser considerado um projeto desatualizado. Mesmo assim, este componente ainda continua sendo largamente utilizado na indústria nacional, pois atende muito bem a uma grande variedade de aplicações, além de possuir um custo muito baixo, devido ao projeto ter sido amortizado. Isto garante uma relação custo/benefício satisfatória.

O baixo custo do componente, aliado ao grande investimento em bases de desenvolvimento viabiliza pensar em transformações a serem feitas em sua arquitetura original, visando adaptá-lo melhor ainda às aplicações a que se destina. Deve-se ressaltar que mudanças feitas na arquitetura não devem implicar em um custo muito elevado, pois nesse caso estaría-se elevando a uma condição pior, a relação custo/benefício da arquitetura sendo utilizada no momento. Assim, um objetivo a ser conquistado pode ser a adaptação do 8051 para trazer mais vantagens na execução de certas aplicações, mantendo-se um baixo custo. Modificações que se podem fazer em uma arquitetura podem ser mudanças no conjunto de instruções, na Parte Operativa, na temporização, etc.

Para fazer uma modificação é necessitário antes verificar as características arquiteturais do Processador. Uma característica importante deste circuito, é que se constitue numa arquitetura CISC (Complex Instruction Set Computer), ou seja, possui um conjunto de instruções grande, constituído por instruções complexas. Quando forem feitas adaptações na arquitetura de um processador em relação ao seu conjunto de instruções, é bastante interessante que também se façam alterações nos compiladores desenvolvidos para esta arquitetura. Isto é importante para que se mantenha a compatibilidade com o software já desenvolvido. Para processadores CISC como o 8051, uma mudança no Compilador será muito onerosa, tendo em vista o grande número de instruções a serem gerenciadas por este compilador. Esta característica dificulta as modificações necessárias quanto a compatibilidade de software nas arquiteturas CISC.

Outra característica que deve ser levada em consideração é que em arquiteturas CISC, a Parte de Controle ocupa a maior parte da área do chip [CAR 96a]. Isto ocorre porque, com um conjunto muito grande de instruções complexas, tem-se também como consequência um grande número de decodificadores ou um decodificador de grande complexidade, além de um grande número de estados para o circuito de geração das microoperações e sequencialização destas. Para arquiteturas CISC dessa natureza pode-se utilizar uma memória ROM para o armazenamento do microcódigo. Esta técnica facilita a tarefa de sequencialização das operações, mas impõe como penalidade uma grande área e uma velocidade menor de operação.

Trabalhos realizados no IEE-UFRGS [CAR 96a] aplicaram programas de análise de execução de instruções para certos programas de aplicações específicas que executam sobre o 8051. Com base em uma análise estática e dinâmica da execução destes programas, verificou-se que um número pequeno de instruções era suficiente para executar quase que a totalidade daquelas aplicações, tendo por base o conjunto de instruções completo do 8051. Como resultado estatístico dessas análises, tem-se que 17 instruções eram suficientes para executar aproximadamente 82% do código das aplicações. Esses resultados vieram a afirmar a possibilidade de se adaptar o 8051 para uma arquitetura RISC. Dentro da filosofia RISC temos apenas um conjunto pequeno de instruções implementadas. Neste caso, a decodificação torna-se mais simples, podendo ser realizada diretamente em *hardware* através de uma Parte de Validação.

Entretando ressalta-se que, dentro do contexto aqui abordado, o processador a ser gerado não possui todas as características de uma arquitetura RISC pura, como por exemplo, instruções que executam em apenas um ciclo de relógio, orientação a registrador, acesso à memória através de instruções *load* e store, etc. Para esta abordagem estão incluídas instruções que acessam a memória (não sendo orientadas a registrador) e executam em mais de um ciclo. Portanto, dentro do contexto deste trabalho, a classificação RISC, refere-se a uma arquitetura composta de um conjunto de instruções reduzido e com *pipeline*. Além disto, pode-se citar que a maioria das instruções originais do 8051 são relativamente simples e portanto não demandam por circuitos decodificadores e geradores de microcódigo complexos, como por exemplo, os encontrados nas máquinas CISC atuais. Sendo assim, as instruções implementadas para a arquitetura a ser gerada podem ser decodificadas por *hardware* (*hardwired*), o que vem a constituir-se de uma importante característica das máquinas RISC.

A Parte de Validação de uma máquina RISC constitue-se em um pequeno decodificador para cada instrução que se deseja implementar na arquitetura, trabalhando em conjunto com a máquina de estados para gerar a sequência de microoperações necessárias à execução de cada instrução. Estas microoperações são enviadas diretamente para a Parte Operativa. A Parte de Validação implementada como descrito acima permite que a inserção/retirada de uma instrução seja feita de maneira muito simples. Uma descrição VHDL pode ser utilizada para gerar diferentes conjuntos de instruções.

Com as modificações explicadas nos parágrafos acima pode-se chegar a duas conclusões, verificadas em [CAR 96a]:

com a arquitetura RISC (um conjunto pequeno de instruções implementadas) tem-se uma grande diminuição na área e no consumo do chip, através da diminuição da Parte de Controle; e

existe a possibilidade de modificar o conjunto de instruções de uma aplicação para outra.

Tem-se assim, um processador adaptado para uma aplicação específica, ou seja, um ASIP (*Application Specific Instruction-Set Processor*). Estas características permitem uma grande flexibilidade em termos de adaptação do MCS8051 para aplicações específicas. Dessa forma modifica-se o conjunto de instruções do 8051, a

fim de que este seja o menor possível, para economizar área, e adaptado à uma aplicação específica.

Como se pode observar em processadores RISC, o tamanho do código em linguagem montadora tende a ser maior do que o mesmo código escrito com um conjunto complexo de instruções (CISC). Esta característica provem do fato de que cada uma das instruções complexas presentes no código CISC, deverá ser representada ou emulada por 2 ou mais instruções simples, características do código RISC. Com isso, um programa RISC normalmente ocupa mais espaço em memória. Porém, em uma máquina RISC típica, as instruções são simples o suficiente para serem decodificadas por hardware (hardwired) e o seu tempo de execução é pequeno, de forma que o tempo total de execução de um programa equivalente pode até ser menor. Para o caso de processadores para aplicações específicas em que implementam-se subconjuntos (específicos à cada aplicação) do conjunto de instruções total igualmente pode haver necessidade de uma emulação. Neste caso, as instruções implementadas e específicas da aplicação deverão emular as outras instruções. A emulação normalmente necessita de 2 ou mais instruções para substituir a instrução que se deseja emular. Neste caso, as instruções que emularão outras instruções, não serão necessariamente mais simples do que a instrução emulada. Desta maneira, o código não apenas ficará maior, como também terá um tempo de execução maior. Para o caso do 8051 CISC, o tempo de execução das instruções é semelhante, pois poucas instruções são muito complexas. Assim, por exemplo, no caso em que tem-se uma substituição de uma instrução por duas, o tempo de execução destas será em torno do dobro do tempo de execução da instrução que foi substituída.

Para compensar este atraso, pensou-se em implementar para o 8051 alguma técnica de paralelismo para acelerar o tempo de execução das instruções. Dentre as técnicas de paralelismo existente, como por exemplo sistemas multiprocessados ou matriciais, optou-se pelo *pipeline*, devido ao fato de este apresentar uma melhor adequação em relação a um dos objetivos, que é a manutenção do baixo custo.

Um dos objetivos a serem alcançados é que as modificações que serão efetuadas sobre o 8051 não aumentem o custo do processador de maneira significativa. Se isto ocorrer, vê-se que provavelmente a relação custo/benefício que tem-se hoje, não será mais tão favorável. Em outras palavras, o custo do processador poderá não justificar a sua substituição do original para o modelo modificado. Técnicas de paralelismo como por exemplo, multiprocessadores, não poderiam ser implementados sem um aumento significativo de custo, devido à replicação de hardware e dos barramentos. Além do mais, estas instruções deveriam executar em paralelo, para ocuparem o mesmo tempo que levariam para executar a instrução que estas estão substituindo (emulando). Em muitos casos não é possível por causa da dependência entre os seus operandos. É claro que dependendo da aplicação poderia-se ter partes de um programa executando em processadores replicados, o que pode resultar uma aceleração considerável. Em segundo lugar, é necessário que se respeite as características originais da arquitetura para manter-se uma compatibilidade com o processador original e manter o baixo custo. Isto significa que não podemos por exemplo, implementar mais de uma ULA no 8051. Embora o custo de um ASIP sempre seja maior do que o processador original, as características desse novo processador devem compensar esse custo adicional, aumentando o valor agregado chip pela integração do sistema em um único chip.

A técnica de *pipeline* foi a técnica de paralelismo que mais adequou-se aos objetivos propostos, proporcionando uma aceleração de execução das instruções sem a necessidade de adição de *hardware* significativo. A Parte Operativa permanece praticamente a mesma. As modificações que são necessárias para implementar o pipeline dizem respeito a inclusão de registradores e alterações da Parte de Controle, pois tem-se uma máquina de estados modificada e microoperações executando em paralelo. As modificações na Parte de Controle implicam em uma pequena adição de *hardware*. Assim, com o pipeline, tem-se uma aceleração na execução das instruções, a um custo aceitável. Com o pipeline implementado no 8051 será possível compensar o aumento do tempo de execução dos programas otimizados para aplicações específicas.

No momento em que se tem um microcontrolador MCS8051 RISC com *pipeline* adaptado a aplicações específicas, é necessário que se proporcione também uma compatibilidade de SW, principalmente para que se possa aproveitar todo o parque de SW já instalado. Uma compatibilidade de SW deve ser feita no Compilador do processador, já que foi modificado o seu conjunto de instruções. Se não for adaptado um Compilador para esse novo conjunto de instruções definido, seria necessário que se programasse o processador através de linguagem Montadora, ou *Assembly*. A própria linguagem montadora deveria ser modificada para não aceitar as instruções não implementadas. Assim, é conveniente que se mantenha a compatibilidade de *software* através da adaptação do Compilador para cada diferente conjunto de instruções do processador. Isto implicará em dois benefícios básicos:

facilidade para o desenvolvimento de novas aplicações; e

compatibilidade com os programas já desenvolvidos para o processador original.

Devido a sua grande popularidade, foi escolhido o Compilador da linguagem C para proporcionar uma compatibilidade de SW com o MCS8051 RISC pipeline. Primeiramente foi desenvolvido no CPGCC-UFRGS um Compilador C para o 8051 [MED 91]. Este compilador foi desenvolvido para gerar um código Assembly para o conjunto completo de instruções do 8051. Durante a compilação do código fonte em C, após as análises léxica, sintática e semântica é gerado um código intermediário. A partir desse código intermediário podem ser gerados diferentes códigos em linguagem Assembly, ou até em outras linguagens. Dentro do contexto deste trabalho está-se tratando o 8051 como um ASIP, com diferentes conjuntos de instruções, um para cada aplicação. O conjunto de instruções de cada aplicação deverá constituir-se de poucas instruções para salvar área na Parte de Validação. Tendo por base este fato, fica claro neste contexto a importância do Compilador. Este terá que, para cada aplicação em questão, gerar um código assembly do 8051 contendo apenas as instruções definidas para cada aplicação. Na verdade será papel do Compilador definir o conjunto de instruções que será implementado. As instruções em que não se conseguiu emular, também farão parte do conjunto de instruções desta aplicação. Poderão existir instruções que não executam em um ciclo normal do pipeline, quebrando-o. Estas instruções deverão ser evitadas ao máximo, principalmente se tiverem um percentual grande de utilização. Os objetivos do Compilador são:

gerar um código em linguagem montadora que utilize um conjunto de instruções reduzido;

emular as instruções pouco utilizadas. Se isto não for possível, incluí-las no conjunto de instruções; e

evitar o uso das instruções que quebram o pipeline.

É importante ressaltar que quanto menor for o conjunto de instruções implementado, menor será a Parte de Validação, e por conseguinte, menor a área e o consumo do chip.

Uma vez gerado o código em linguagem montadora e definido o conjunto de instruções da aplicação, este poderá ser implementado em HW, colocando-se estas instruções na Parte da Validação da descrição do 8051 em VHDL. Finalmente, através de ferramentas de síntese automática, pode-se sintetizar a descrição e prototipar o circuito em FPGA. As vantagens de se prototipar em FPGA dizem respeito ao baixo custo e velocidade. Desse modo, pode-se ter rapidamente um protótipo de um MCS8051 adaptado à uma aplicação específica.

O fato de ter-se poucas instruções implementadas resulta em um grande ganho de área em relação ao processador original. Esta área poderá ser utilizada para implementar outros circuitos, como por exemplo protocolos de comunicação, memória RAM, etc., aumentando o valor agregado do chip [CAR 96]. Desse modo, numa mesma área é possível ter-se um circuito que realize mais tarefas, trazendo um maior benefício ao usuário. Em última análise, estaria-se desenvolvendo o conceito de um ASIS (*Application Specific Integrated System* - Sistema Integrado para Aplicação Específica) ou seja, um sistema computacional completo *on chip*.

#### 1.1 Contribuições

O presente trabalho diferencia-se da literatura atual em termos de pesquisa sobre ASIPS, pela geração de um sistema microcontrolado adaptado a aplicações específicas baseado no 8051 e compatível com as aplicações existentes. O escopo deste trabalho situa-se na otimização do 8051 para operar com um conjunto de instruções reduzido e específico a cada aplicação, onde existe a compatibilidade com os programas já escritos em C, obtendo-se assim, a compatibilidade de *software* em alto nível. Esta compatibilidade é requerida por tratar-se o 8051 de uma arquitetura de uso comercial e portanto largamente utilizada na indústria local e nacional. Modificações já foram realizadas sobre o 8051 em relação à redução do seu conjunto de instruções e programas de análise estática das instruções executadas em cada aplicação. A novidade deste trabalho é a otimização da velocidade de execução das instruções através da técnica de *pipeline*, e a geração de um conjunto de instruções reduzido e compatível com o *pipeline*, através de um compilador C.

Desta forma, não é necessário que se desenvolvam novas aplicações, compiladores etc., pois todo o parque de *software* desenvolvido será compatível, bastanto recompilar o programa. Com isso será possível gerar-se um novo 8051 com um conjunto de instruções menor, adaptado a uma aplicação específica. Como consequência tem-se uma economia de área, por ter-se implementadas poucas instruções. Essa área pode ser utilizada para a integração do sistema. O 8051 otimizado pode ser prototipado em FPGA.

Implementando-se as aplicações com um conjunto de instruções reduzido (RISC), a tendência é que os programas em linguagem montadora venham a tornar-se maior. Mesmo tendo programas RISC um maior número de instruções, possivelmente, devido ao *pipeline*, o tempo de execução poderá ser menor.

Através de uma prototipação rápida e a um baixo custo (FPGA), as aplicações atuais poderão passar a executar sobre esse novo processador. Isto permite uma migração rápida das aplicações para essa nova abordagem do 8051. O Compilador C garante a compatibilidade de *software* com o que já foi desenvolvido permitindo uma migração rápida para circuitos integrados dedicados.

Após a prototipação tem-se um processador com área e consumo de potência menor. Além disso, com a área excedente em relação a arquitetura original, pode-se implementar outros circuitos (como funções implementadas em *hardware*) aumentando o valor agregado do microcontrolador. A arquitetura permanece praticamente a mesma, pois a inclusão do pipeline não implica em muitas modificações quanto ao *hardware*, além de não serem criadas novas instruções. As instruções utilizadas são as mesmas da arquitetura original, onde dentre estas são escolhidos subconjuntos do conjunto total de instruções. Cada subconjunto irá corresponder a uma aplicação. Isto mantém a compatibilidade com Montadores já desenvolvidos para o MCS8051. Finalmente, pode-se observar que, para aplicações desenvolvidas em C, o número de instruções utilizadas é pequeno pois os compiladores em geral não utilizam todo o repertório de instruções disponível no processador.

#### 1.2 Organização da Dissertação

A dissertação está organizada da seguinte forma:

O capítulo 2 refere-se a sistemas para a geração de ASIPs encontrados na literatura, realizando uma comparação com a abordagem para aplicações específicas proposta para o 8051.

O capítulo 3 apresenta alguns conceitos de arquitetura de computadores no que diz respeito a processadores para aplicações específicas. Ainda neste capítulo é mostrada e analisada a arquitetura do 8051, bem como a sua descrição em VHDL.

O capítulo 4 realiza uma discussão sobre alternativas de implementação do pipeline para esta arquitetura, explicitando e justificando a maneira como esta foi realizada. Segue-se a análise do desempenho e as implicações da implementação do pipeline para 8051.

No capítulo 5 é realizado processo de Síntese Lógica para a descrição VHDL do 8051 em duas versões: com e sem pipeline. Comparações são feitas entre estas duas descrições em termos dos resultados obtidos com a síntese. Esses resultados são úteis para a validação do pipeline.

O capítulo 6 trata do Compilador C desenvolvido para o 8051. Neste capítulo são mostradas as características do Compilador e as modificações necessárias para adaptá-lo à geração de instruções específicas a cada aplicação. Neste capítulo também

é tratada a geração e prototipação do circuito tendo como entrada o programa em C, e como saída a prototipação em FPGA. Alguns exemplos são analisados e testados.

O capítulo 7 apresenta conclusões e as propostas de trabalhos futuros.

## 2 A abordagem ASIP para o MCS8051

Os microprocessadores oferecem uma solução flexível e de baixo custo para sistemas que trabalham com algoritmos complexos, como no processamento digital de sinais (DSP) e em controle digital ou as que trabalham com tempo real. Sistemas baseados em microprocessadores são de natureza preponderantemente eletrônica e digital. Esses sistemas aplicam-se a uma larga gama de problemas desde que sejam programados para tal. Estruturalmente estes sistemas são organizados através de um ou mais processadores (capazes de executar instruções), memória e periféricos (ASICs, ...). Todos esses componentes atuam em conjunto para a execução de programas que implementam uma ampla variedade de aplicações.

Em relação a aplicações específicas os sistemas microprocessados apresentam algumas desvantagens que dizem respeito principalmente a área, consumo e desempenho se comparado aos sistemas de *hardware* específico. Isto porque os sistemas adaptados para aplicações específicas possuem apenas o HW e o conjunto de instruções necessários à execução daquela aplicação. Portanto, Sistemas Microprocessados para Aplicações Específicas são a solução quando os sistemas centrados em microprocessador de propósito geral não podem cumprir algum dos requisitos de desempenho, de portabilidade, de menor área ou de consumo [ALB 96].

Microcontroladores são sistemas microprocessados que integram, em apenas uma pastilha de silício, processador, memórias, portas de entrada/saída, temporizadores, etc, sendo utilizados para aplicações gerais. A adaptação de microcontroladores para aplicações específicas, com o objetivo de conseguir um melhor desempenho, consiste basicamente na adequção do processador às características da aplicação. Uma maneira de conseguir isto é através da modificação do conjunto de instruções, tornando-o um processador com conjunto de instruções adaptado a uma aplicação específica. Dessa maneira, o conjunto de instruções desse processador será formado pelas instruções mais importantes, ou aquelas mais utilizadas pela aplicação.

Como pode ser visto em [MIC 94], dependendo do estilo de projeto adotado, tem-se diferentes soluções para a execução das aplicações. Uma abordagem seria a concepção de um ASIC (Application Specific Integrated Circuit), como sendo uma solução orientada ao hardware. Para essa abordagem é construído um circuito que implementa um algoritmo. Este procedimento constitui-se na solução mais eficiente, devido à execução do algoritmo em *hardware*, porém demanda um longo tempo de projeto e um custo considerável, por tratarem-se normalmente de circuitos complexos.

Como um outro estilo de projeto, tem-se a abordagem ASIP (Application Specific Instruction-set Processor), onde se tem um processador capaz de ajustar-se à execução de aplicações específicas, através da modificação de seu conjunto de instruções e de sua arquitetura. Assim, para cada aplicação serão definidas as instruções que melhor se adaptam a sua realização, sendo estas implementadas no processador. A arquitetura da Parte Operativa será escolhida de modo a implementar da melhor maneira possível o conjunto de instruções, normalmente com base em certas restrições como por exemplo, a área ocupada pelo circuito, o consumo de potência, etc. Um ASIP possui um alto desempenho, pois a sua arquitetura é projetada e ajustada de acordo com as características da aplicação. O tempo de projeto de um

ASIP tende a ser maior do que tempo necessário para o projeto do mesmo sistema utilizando o processador padrão. Isto tende a diminuir, entretanto, com a crescente automatização. Um ASIP necessita de um CAD de suporte bem elaborado, para permitir a migração de um aplicação para outra. A compatibilidade de software, especialmente do Compilador do ASIP é importante pois permite a programação da nova arquitetura em alto nível sem a necessidade de alteração na plataforma de desenvolvimento.

Como uma terceira alternativa de projeto, tem-se um processador central com HW adicional, resultante do processo *Hardware/Software Codesign*. Essa abordagem resulta num desempenho relativamente inferior aos ASIPs, mas mantém uma programabilidade muito boa, bem como um custo de projeto médio. Pelo fato de o HW adicional constituir normalmente uma função da aplicação, no caso de esta ser uma função complexa, praticamente estar-se-á implementando um ASIC com um tempo de projeto proporcional.

Finalmente, tem-se a abordagem orientada ao SW. Nessa abordagem, a execução da aplicação se realizará através da execução de um programa num processador de propósito geral. Assim, obtem-se como vantagens principais a versatilidade e a programabilidade, pois esta máquina pode resolver um grande número de aplicações. O tempo de projeto para essa abordagem é menor em relação às outras, porém com um desempenho inferior e possivelmente maior consumo.

Dentro do contexto deste trabalho, está-se utilizando a abordagem ASIP, porém com uma arquitetura já existente. Desse modo, para manter um baixo custo, as alterações efetuadas para a migração entre as aplicações restringir-se-ão a alteração do conjunto de instruções, sem modificações na Parte Operativa. Assim, a vantagem de se optar por essa abordagem confirma fato constatado em [CAR 96b], onde a implementação de apenas algumas instruções do conjunto total das instruções especificadas originalmente resulta em uma grande economia de área, através da diminuição da Parte de Validação. Essa área excedente pode ser utilizada para aumentar o valor agregado do processador [CAR 96], possibilitando a realização do "Sistema Integrado para Aplicações Específicas" (SIAE) ou "Application Specific Integrated System" (ASIS).

#### 2.1 O Projeto de ASIPs

Para o projeto de um ASIP, existem duas abordagens possíveis:

a criação de uma arquitetura nova; e

adaptação de um processador já existente.

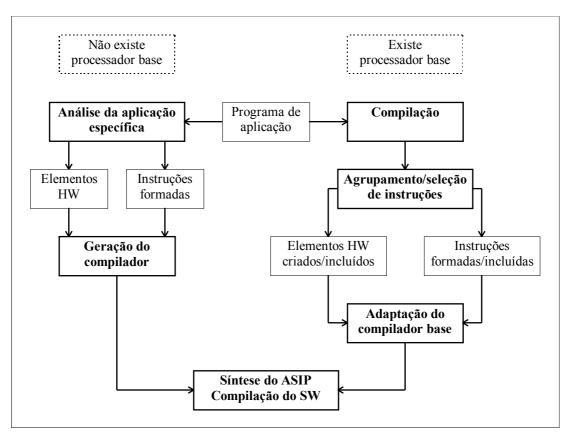

A figura 2.1 apresenta essas duas abordagens.

Na primeira abordagem, uma arquitetura para uma determinada aplicação é criada a partir da análise de processos escritos em linguagem de alto nível. Esses processos são traduzidos para estruturas do tipo grafos de fluxo de controle, para a verificação de como são realizadas as instruções em nível de microoperações. Em seguida são realizadas análises sobre essas estruturas para saber, por exemplo quais são as instruções mais utilizadas pela aplicação, o custo em termos de HW para sua

execução, as restrições (área, consumo) a serem obedecidas, etc. A partir dos resultados desta análise, é escolhido o conjunto de instruções que melhor atende a aplicação, composto pelas instruções mais utilizadas e uma arquitetura adequada, bem como a lógica de controle para a execução dessas instruções. A especificação da arquitetura consiste normalmente de uma seleção de elementos de HW pré-definidos. Para a programação com o conjunto de instruções definida, é criada uma linguagem montadora, e em alguns casos, um compilador, permitindo a programação em alto nível. A nova arquitetura ASIP é descrita através de uma HDL (*Hardware Description Language*), para posterior síntese.

Em relação ao que foi encontrado na literatura, verifica-se que a maioria desses trabalhos adotam este tipo de abordagem para a especificação da arquitetura do ASIP.

Isto pode ser verificado por exemplo, em [GOV 96], que permite o projeto simultâneo de um HW com pipeline e do SW para executar sobre este pipeline. Em [NGU 95], propõe-se um algoritmo para particionamento de HW/SW codesign para selecionar uma boa arquitetura para o pipeline. Procura-se achar uma série de operações implementadas em HW para obter um bom desempenho para o ASIP pipeline, levando-se em consideração o número de portas (gate count) e consumo de potência como limitações. Nota-se que se tratam de arquiteturas genéricas criadas automaticamente. Assim, são arquiteturas novas, tornando-se necessário que se desenvolvam novos compiladores e SW para torná-la compativel comercialmente. Isto pode ter um grande custo e também um grande tempo de chegada ao mercado. Em [VAN 94] é apresentada uma abordagem interativa para definição de microinstruções otimizadas dos ASIPs. Também apresenta um método para definição das instruções quando for gerado o código para o ASIP. Então é gerado o modelo da parte operativa com o seu conjunto de instruções onde a aplicação é mapeada. Neste caso, temos um data-path específico e otimizado e um modelo da nova arquitetura. Uma abordagem semelhante é encontrada em [IMA 92], onde a definição de microinstruções otimizadas de ASIPs é feita interativamente.

Em [HUA 94a] verifica-se que o projeto de um sistema de um ASIP inclui pelo menos três tarefas independentes:

- 1. projeto da microarquitetura;

- 1. projeto do conjunto de instruções; e

- 1. mapeamento do conjunto de instruções da aplicação.

Em [HUA 94a] é apresentado um método que unifica estes três problemas de projeto com uma única formulação: um problema de escalonamento/alocação agregado a um processo de formação de instruções integrado. As microoperações que representam a aplicação são escalonadas em passos de tempo. As instruções são formadas e os recursos de HW são alocados durante o processo de escalonamento. Ao fim do processo de escalonamento é obtido automaticamento o código em linguagem montadora da aplicação. Esta abordagem considera o paralelismo entre as microoperações, codificação das instruções, o atraso de *load/store/branch*, execução condicional das microoperações e vários modelos de arquiteturas. Nota-se que ao final do processo é gerado um código em linguagem montadora e não um compilador.

Ainda sob o enfoque da criação de arquiteturas novas dedicadas, em [ALO 93] verifica-se a implementação e experimentos com o PEAS - I, um sistema de HW/SW co-design para geração de ASIPs. Este sistema possue como entrada um conjunto de programas (aplicações) escritos em C associado um conjunto de dados e as limitações do projeto, como área e consumo. A partir dessas variáveis, o sistema gera um modelo de CPU descrito numa HDL, um compilador C, um assembler e um simulador. Umas das contribuições desse artigo é a criação de um novo modelo para o projeto do conjunto de instruções através de uma abordagem que utiliza programação inteira. Além disso, verifica-se a preocupação com a compatibilidade de SW, através da geração do compilador e do assembler para a arquitetura gerada. Esta pode ser considerada uma semelhança com a abordagem aqui proposta.

A segunda abordagem para o projeto de um ASIP diz respeito a adaptação de um processador já existente. Neste enfoque realiza-se uma modificação sobre um processador, de modo a que se obtenha um melhor desempenho para a execução de determinada aplicação. Assim como na abordagem explicitada no parágrafo anterior, nesta abordagem igualmente são realizados testes sobre a aplicação de modo a determinar quais as instruções mais utilizadas. O passo seguinte consiste em adaptarse o conjunto de instruções para as instruções que serão implementadas. Isto pode ser feito simplesmente pela retirada de algumas instruções, e/ou pela criação de outras. De qualquer maneira, as alterações no conjunto de instruções implicarão mudanças na Parte de Controle e na Parte de Validação. A otimização da Parte Operativa não se torna necessária para o caso e em que não haverá a criação de novas instruções, ou até mesmo, se as novas instruções são adaptadas ao data-path e aos elementos de HW da Parte Operativa. Porém, qualquer otimização que venha a ser feita, resultará numa melhor adequação do ASIP às restrições impostas quando da idéia de sua concepção. Ainda, uma modificação na Parte Operativa pode ser a inclusão de funções à serem executadas em HW. Caso o processador que será transformado em ASIP já possua um Compilador desenvolvido, para manter a compatibilidade de SW, torna-se necessário adaptar o Compilador para que este reconheça o novo conjunto de instruções, também para que se possa continuar utilizando o SW já desenvolvido para esta arquitetura.

Sistemas que trabalham sob essa abordagem são encontrados em [ATH 93] e [LIE 94]. Athanas [ATH 93] usa a informação extraída durante a compilação do programa de aplicação para a criação e seleção das instruções. Liem [LIE 94] usa uma representação de padrões de instrução que descrevem fluxos de dados, fluxos de controle e fluxos combinados de dados e controle do programa de aplicação e obtém as instruções pelo agrupamento desses padrões.

25

FIGURA 2.1 - O projeto de ASIPs

O projeto de transformação do 8051 em ASIP, pode ser enquadrado sob a segunda abordagem apresentada, pois está-se trabalhando com uma arquitetura existente. A maior diferença encontrada em relação a literatura, diz respeito ao fato de esta ser uma arquitetura de uso comercial. De certa forma isto constitui-se numa vantagem, pois para cada aplicação, basta apenas que se gere uma nova versão do processador, adaptada àquela aplicação. A vantagem verifica-se principalmente no número de engenheiros treinados, pois sempre que uma arquitetura nova é lançada torna-se necessário a construção (projeto e programação) de todo o software básico necessário ao suporte da nova arquitetura. A construção desses softwares básicos, como por exemplo compiladores, sistemas operacionais, por possuírem algoritmos não triviais, envolve uma tarefa relativamente complicada e principalmente demorada. Este problema não se verifica numa arquitetura já existente, pois para esse processador não apenas estão implementados todos esses *softwares*, como já foram largamente testados, sendo utilizados comercialmente [MED 91]. Além disso, existe um grande número de engenheiros e programadores treinados na sua utilização.

Outra característica importante diz respeito ao custo de produção da nova arquitetura. É interessante observar que, para uma arquitetura nova tornar-se barata, é necessário que se seja produzida em larga escala. O baixo custo é uma exigência, sendo que a escolha do 8051 para que este seja adaptado à aplicações específicas, deve-se também ao fato de esse processador ser produzido comercialmente há um longo tempo, e em larga escala. Como consequência, tem-se um baixo custo final para os consumidores. Dentro do contexto do mercado brasileiro, produzir uma arquitetura nova em larga escala pode ser uma tarefa complicada, principalmente pela carência de estrutura industrial em termos de *foundries*. Assim, uma maneira encontrada para trabalhar-se com uma arquitetura reconfigurável a um baixo custo, é a utilização de

um processador comercial, sob o ponto de vista de que esta arquitetura já possui um grande parque de SW instalado, além de engenheiros treinados na sua utilização. Em relação ao custo propriamente dito, ressalta-se que a arquitetura ASIP terá um custo mais elevado em relação ao seu equivalente comercial. Porém o que se busca para compensar este custo a mais é o aumento do valor agregado da arquitetura, pela inclusão de outras partes do sistema no mesmo chip do 8051 ASIP, ou seja, a integração do sistema para aplicação específica (ASIS).

Outras características deste trabalho dizem respeito a prototipação rápida e economia de área para aumentar o valor agregado do processador. A prototipação rápida verifica-se pelo fato de ser realizada em FPGA. A implementação utilizará a abordagem da Altera, como pode ser verificado no capítulo 5. Além disso, um FPGA permite a integração completa do sistema a um baixo custo.

As idéias que deram origem a este trabalho foram discutidas em trabalhos anteriores realizados no GME-UFRGS e podem ser encontradas em [CAR 96] e [ALB 96].

Em [CAR 96] encontram-se as idéias que deram origem a este trabalho, no sentido de se trabalhar com arquiteturas reconfiguráveis e dedicadas a aplicações específicas. Em [CAR 96] são mostradas diferentes formas de se adaptar uma arquitetura à melhor execução de determinados tipos de aplicações como por exemplo, aplicações que realizam diversas chamadas a sub-rotinas ou possuem um grande número de saltos. O presente trabalho constitui-se numa extensão destas propostas no sentido da realização de modificações na temporização e implementação de pipeline para arquiteturas comerciais, como é o caso do 8051, a fim de tornar estas arquiteturas dedicadas.

Em [ALB 96], trabalha-se com um gerador de microcontroladores para aplicações específcas MbSG (Microcontroller based System Generator). Este sistema está projetado para ser automático desde a análise de um programa na linguagem C, junto com requisitos do usuário, até a geração da descrição em VHDL da arquitetura do microcontrolador resultante. As análises realizadas no MbSG têm como objetivo otimizar a arquitetura de um processador chamado Risco [JUN 93] (que será a base do microcontrolador) adaptando-a à aplicação. Assim, são determinados os registradores usados pelo programa de entrada, as unidades funcionais e instruções necessárias para o programa de aplicação ser executado e serem considerados posteriormente na geração da arquitetura. O processo central do MbSG é a análise das rotinas do programa de aplicação. Essa análise consiste na execução simulada do programa, junto com os vetores de entrada fornecidos pelo usuário, para encontrar a rotina ou conjunto de rotinas críticas (com o maior número de ciclos de máquina necessários à sua execução) a serem otimizadas com uma arquitetura particular de acordo a sua característica básica (rotinas podem ser computacionalmente intensivas, intensivas em acessos à memória e intensivas em desvios do fluxo de controle do programa). A arquitetura gerada consiste em um processador Risco base, memórias de instruções (ROM e/ou WCS) memória de dados (RAM), interfaces com o exterior e hardware de suporte (rotinas críticas sintetizadas). Essa arquitetura é descrita em VHDL para logo ser sintetizada com as ferramentas do Sistema Alliance [BAZ 94].

Verifica-se que a intenção deste trabalho igualmente é a geração de uma arquitetura microcontroladora tendo como entrada um compilador C para o 8051,

adaptado a geração de instruções específicas de cada aplicação. A diferença está no fato de que aqui não se está tratando da criação de uma arquitetura nova baseada na variação de um modelo, mas apenas na modificação, através da análise realizada em tempo de compilação, do subconjunto de instruções implementadas. Outra diferença é a própria prototipação em FPGA. Assim, neste trabalho, o objetivo maior é a economia de área pela implementação de poucas instruções e a rápida prototipação para facilitar a integração de sistemas [KRE 97].

#### 2.2 O Processo de criação do MCS8051 ASIP

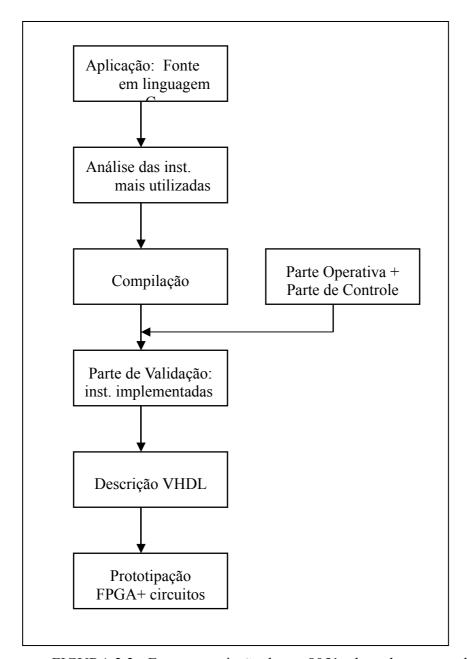

A figura 2.2 mostra as etapas necessárias para a adaptação do 8051 a uma determinada aplicação.

O processo inicia-se com a aplicação escrita em linguagem C. Num primeiro momento essa aplicação é compilada, utilizando-se qualquer compilador C definido para gerar instruções em linguagem montadora do 8051, inclusive o compilador C desenvolvido no GME-UFRGS para o 8051 [MED 91], sobre o qual este trabalho se baseia. O próprio compilador modificado terá uma opção para gerar todas as instruções. Em seguida, o programa em linguagem montadora gerado pelo compilador é submetido a uma ferramenta que realiza a análise de quais são as instruções mais utilizadas pela aplicação. Tanto o compilador C, quanto as ferramentas de análise são ferramentas comerciais. Neste sentido procura-se simular o ambiente encontrado pelos projetistas e engenheiros que dedicam-se a trabalhar com o 8051, como demonstrado em [CAR 96].

Seguindo o processo, tem-se então a atuação do compilador C modificado para gerar um conjunto de instruções reduzido e adaptado à aplicação. Uma possível abordagem a ser seguida, é a de que o compilador receba como entrada um arquivo contendo as instruções que são passíveis de implementação, ou seja, as mais utilizadas pela aplicação. Nota-se que esse arquivo contém somente instruções do 8051, sendo que nenhuma instrução nova será criada. O compilador, a partir do código intermediário, tenta implementar somente as instruções especificadas no arquivo de entrada. Uma regra a ser seguida pelo compilador diz respeito a que, quanto maior for a porcentagem de utilização da instrução, maior a necessidade de que esta não quebre o pipeline para sua execução. Se este for o caso, tenta-se substituí-la por outra(s) que possua(m) a mesma função sem quebrar o pipe. Por exemplo, a instrução INC A pode ser susbtituída por ADD A,#01. No caso de uma substituição não ser possível, a instrução será implementada.

Após a definição das instruções que serão implementadas, é gerada a Parte de Validação sob a forma de um arquivo VHDL comportamental. Às outras partes da descrição VHDL do 8051 (ver capítulo 3) é incorporada a Parte de Validação, tornando a descrição completa e pronta para ser sintetizada. Pode-se verificar aqui que não são realizadas modificações sobre a Parte Operativa, pois as mudanças que ocorrem dizem respeito somente ao conjunto de instruções, sendo que este será constituído de um subconjunto do conjunto de instruções completo do 8051. Nota-se ainda que esta descrição já está implementada com o pipeline. Detalhes sobre a implementação do pipeline para o 8051 são discutidos no capítulo 4.

FIGURA 2.2 - Etapas na criação de um 8051 adaptado a uma aplicação.

Finalmente, após a compilação da descrição VHDL, tem-se a prototipação em FPGA. De acordo com a economia de área obtida, através da implementação de poucas instruções, torna-se possível então a colocação de outros circuitos, como por exemplo *hardware functions*, para serem prototipados em conjunto com o 8051. Dessa forma, obtem-se a integração do sistema completo em apenas um chip (ASIS). Observa-se entretanto, que não constitui-se em tarefa do compilador a determinação de como a área excedente será utilizada.

#### 3 Arquitetura do MCS8051

Por ser um microcontrolador, o MCS8051 possui em sua pastilha não somente a Unidade Lógica e aritmética e Registradores, mas também temporizadores, memórias RAM e ROM internas e portas de Entrada e Saída. Para este trabalho, foi realizada uma descrição VHDL do 8051, com a finalidade de automatizar a síntese através de ferramentas para síntese automática de circuitos, como por exemplo, Alliance [BAZ 94] e Altera[ALT 92]. Uma discussão sobre a descrição do 8051 é realizada na seção 3.1, sendo que esta descrição contém todos os elementos microarquiteturais necessários à execução das instruções as quais desejam-se implementar. Estas instruções serão necessárias à execução das aplicações para as quais o 8051 será dedicado dentro do conceito de ASIP. Algumas elementos da Parte Operativa não foram descritos ainda, pois para a simulação da execução das instruções, esses elementos não são essenciais. descritos Portanto, foram somente os microarquiteturais necessários à execução das instruções as quais está-se simulando. Num momento de implementação de um protótipo ou da utilização efetiva do 8051 em uma aplicação específica, possivelmente algums elementos a mais deverão ser descritos, como por exemplo, as portas de comunicação e a memória RAM externa.

Tipicamente, uma instrução do 8051 é composta pelo código da operação (opcode) e pelo(s) operando(s). O código da operação é representado pelo respectivo mnemônico em assembler, como por exemplo, ADD para soma, DIV para divisão. Os operandos fonte são representados pelo modo de endereçamento que especifica como estes são acessados, e o operando destino, pelo endereço onde o resultado da instrução deve ser armazenado. Desse modo, o que diferencia uma instrução de outra é o seu tipo e o modo como acessa e armazena os operandos. Cabe relembrar aqui, que o conjunto de instruções a ser implementado constitui-se, na verdade, de um subconjunto do conjunto total de instruções original do 8051. Dessa maneira, a substituição ou emulação de uma instrução por outra(s), se fará através da modificação do tipo e modos de endereçamento dos operandos da instrução por um tipo e/ou modo de endereçamento já existente no conjutno de instruções original. Isto ocorre porque não serão criadas instruções novas. Conclui-se, então, que se houver uma substituição de um tipo de instrução por outro, a instrução substituta deve ser de um tipo contido no conjunto de instruções original do 8051.

O 8051 possui definido, no seu conjunto de instruções, 5 diferentes modos para endereçar os operandos de uma instrução:

- Registrador: o operando está em um registrador do banco de registradores. O registrador é endereçado através dos três bits menos significativos do primeiro byte da instrução;

- 1. Direto: o segundo byte da instrução especifica o endereço do operando na RAM interna, sendo um endereço de 8 bits;

- 1. Indireto: o bit menos significativo do primeiro byte da instrução especifica entre o registrador R0 ou R1 do banco de registradores, o qual possuirá como conteúdo, o endereço de 8 bits do operando. O endereço é de 8 bits pelo fato de os registradores possuírem o tamanho de 8 bits;

- 1. Constante: pode ser uma constante no segundo byte da instrução, um endereço de 11 ou 16 bits (instrução de três bytes), ou ainda um endereço para uma instrução de salto. Dependendo da instrução, este endereço pode estar no segundo byte da instrução (8 bits) ou no segundo e no terceiro byte da instrução (16 bits). Quando a constante constitui-se num endereço para uma instrução de salto é chamada de endereço relativo;

- 1. Bit: endereço direto de um bit na RAM interna. Este modo de endereçamento é utilizado nas instruções de manipulação de bit.

O banco de registradores do 8051 é mapeado nas posições inferiores da memória RAM interna, sendo composto por 4 bancos com 8 registradores cada. A memória RAM externa pode ser endereçada por 8 ou 16 bits.

As instruções do 8051 podem possuir um, dois ou três bytes. O código da operação sempre é especificado no primeiro byte, não importando o número de bytes da instrução. Em uma instrução de um byte, além do código de operação pode estar especificado o endereço de um registrador, implementando assim os modos de endereçamento direto e indireto. Nas instruções de dois bytes, o segundo byte será um endereço de memória (modo de endereçamento direto), uma constante ou um endereço de salto.

#### 3.1 Descrição VHDL do MCS8051

Para a descrição em VHDL do MCS-8051 procurou-se tornar prática a tarefa de retirar/colocar instruções, devido ao fato de este trabalho estar inserido dentro do contexto de ASIPs, ou seja, arquiteturas com conjunto de instruções reconfigurável para aplicações específicas, ou em outras palavras, um conjunto de instruções para cada aplicação. Torna-se importante destacar que, por estar-se trabalhando sobre uma arquitetura já implementada, inclusive de uso comercial, e também para manter um baixo custo, não serão realizadas grandes modificações sobre esta arquitetura. Desta maneira, uma modificação no conjunto de instruções não implicará em uma modificação em todos os elementos microarquiteturais, no sentido de retirar alguns e colocar outros para melhor implementar as instruções. A opção, para manter o baixo custo, se realizou no sentido de que qualquer modificação no conjunto de instruções implicará basicamente apenas na mudança da parte de decodificação e geração do microcódigo, que é parte integrante da Parte de Controle. Em outras palavras, o que se está dizendo é que quando houver modificações no conjunto de instruções, isto não implicará em mudanças arquiteturais na Parte Operativa. Este conceito se reforça quando se pensa que as instruções implementadas serão um subconjunto do conjunto total de instruções do 8051. Dessa maneira, para a decodificação e geração do microcódigo das instruções, foi reservada uma entidade VHDL separada. Esta entidade é chamada Parte de Validação.

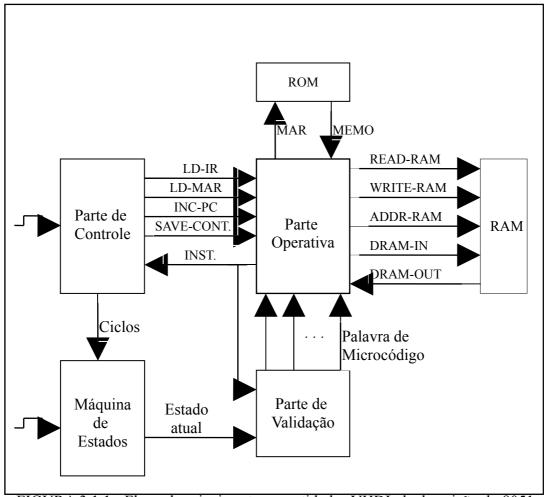

Para a descrição de todo o microcontrolador, foram utilizadas as seguintes entidades VHDL:

Parte de Controle; Parte Operativa; Parte de Validação; Máquina de Estados; Memória ROM interna; e Memória RAM interna.

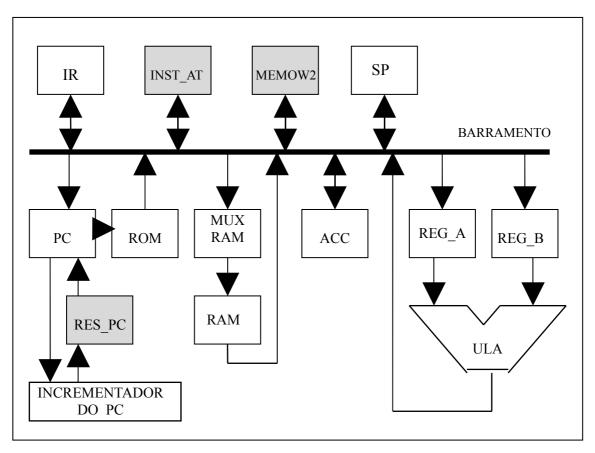

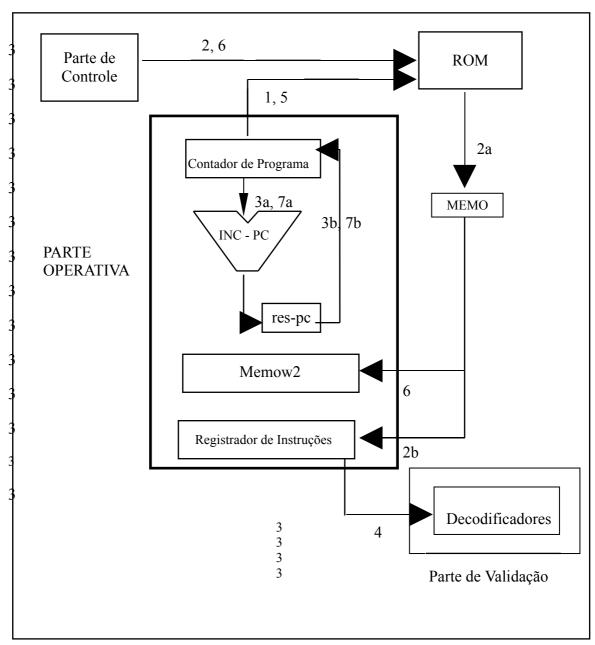

A figura 3.1.1 mostra a relação em termos do fluxo dos sinais entre as entidades.

Para esta descrição, a Parte de Controle é responsável pelo controle de alguns sinais durante a execução de cada instrução. Por exemplo, é esta entidade que gera o INC-PC no tempo apropriado, ordenando à Parte Operativa que realize um incremento no Contador de Programa (Program Counter). Também esta entidade é responsável pela geração dos sinais de leitura da próxima instrução (LD-IR), igualmente endereçado à Parte Operativa, bem como os sinais de leitura e habilitação da ROM interna (LD-MAR). Um endereço para a ROM é o conteúdo do PC, pois é nesta memória que estão armazenadas as instruções do programa a ser executado. Como o objetivo aqui é trabalhar-se com arquiteturas para aplicações específicas, é natural que o programa seja armazenado em uma ROM. A instrução lida da ROM passa pelo barramento MEMO e é escrita no Registrador de Instruções (Instruction Register - IR) na Parte Operativa. Para a descrição com pipeline, a entidade Parte de Controle também envia um sinal à Parte Operativa para que esta carregue em um registrador auxiliar a instrução que está sendo executada. Este sinal chama-se save context e é enviado um estado antes da próxima instrução ser carregada no IR. Este sinal torna-se necessário para que se mantenha a instrução sendo executada, uma vez que a próxima instrução será carregada no IR. Nota-se que apenas o primeiro byte da instrução é carregado no registrador auxiliar, pois para manter-se o contexto basta que o código da instrução (opcode) seja preservado.

Também a entidade Parte de Controle determina o número de ciclos e de bytes da instrução a ser executada. O número de ciclos é enviado à Máquina de Estados através do sinal *ciclos*, para que esta possa determinar o número de estados necessários à execução de cada instrução. O número de bytes é utilizado pela própria Parte de Controle para determinar o número de vezes que o Contador de Programas é incrementado em cada ciclo de execução de uma instrução. Se por exemplo, a instrução a ser executada possuir 3 bytes, o PC terá que ser incrementado 3 vezes durante a sua execução; uma vez para endereçar a busca do primeiro operando da instrução, outra vez para o segundo e finalmente a terceira vez que serve para endereçar a próxima instrução a ser executada. Ainda, a Parte de Controle é responsável pelo envio do código da instrução sendo executada para a Parte de Validação. Na descrição com *pipeline* é realizado um teste ao enviar-se o código da instrução para a Parte de Validação, para verificar se este código pertence a instrução sendo executada e não a instrução seguindo, já carregada no IR.

A entidade Parte Operativa contém todos os elementos microarquiteturais necessários à execução das instruções definidas para o 8051. Sendo assim, nesta entidade está definida a Unidade Lógico-Aritmética (ULA), o registrador PC, o incrementador do PC, os registradores Acumulador, o Apontador de Pilha, o Registrador de Instruções, além de alguns registradores auxiliares. A conexão entre os elementos microarquiteturais está realizada através de multiplexadores ao invés de

barramentos, como especifica a arquitetura original. A escolha por multiplexadores deu-se pelo fato de que o objetivo final será a prototipação em FPGA, que é constituído por multiplexadores.

A ULA realiza as operações de soma e subtração e deslocamentos para a direita e esquerda.

As figuras nos parágrafos abaixo ilustram os multiplexadores utilizados nas conexões entre os elementos microarquiteturais da Parte Operativa.

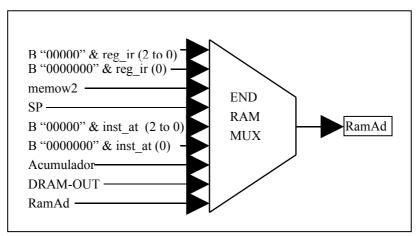

Na figura 3.1.2 estão expostas as entradas para o MUX que serve para o endereçamento da memória RAM interna. Este MUX permite que a RAM seja endereçada de diversas maneiras. Por exemplo, quando o operando de uma instrução é um registrador do banco de registradores (ver início do capítulo), o endereçamento da RAM é formado através dos 3 bits menos significativos do primeiro byte da palavra de instrução. Isto ocorre por que o banco de registradores está mapeado na RAM interna. Assim, uma entrada para o multiplexador constitui-se nos 3 bits de endereçamento da palavra de instrução.

O registrador *RamAd* constitui-se no barramento de endereços da RAM. Nota-se que tanto para *reg\_ir* quanto para *inst\_at* estão definidas entradas para o bit menos significativo e para os 3 bits menos significativos. Estas entradas correspondem respectivamente ao modo de endereçamento indireto e a registrador, como visto anteriormente.

O registrador *inst\_at* faz-se necessário para a descrição com pipeline. Mais detelhes sobre o *pipeline* para o 8051 são mostrados no capítulo 4. Ainda podem endereçar a RAM interna, o Acumulador, o Ponteiro de Pilha, SP, a saída da própria RAM e a saída da ROM. A saída da ROM está representada pelo registrador memow2 e serve para implementar o modo de endereçamento direto, pois o conteúdo de memow2 será o segundo byte de uma instrução. A saída da RAM, DRAM\_OUT, é realimentada para o seu barramento de endereços para a implementação do modo de endereçamento indireto, pois o byte (R0 ou R1) que o bit menos significativo irá endereçar possui como conteúdo, um endereço. A saída da RAM, DRAM\_OUT, pode ser realimentada para a entrada do MUX de endereçamento pois o barramento de endereços *Ram Ad*, está implementado com sendo um registrador.

A figura 3.1.3 mostra o MUX que conecta todos os elementos microarquiteturais que podem realizar a operação de escrita no Acumulador, como por exemplo, a saída da RAM, DRAM-OUT, da ULA, OUT\_ALU, da ROM, MEMO e o Contador de Programas, PC. A entrada X"00"corresponde ao *reset*.

O registrador InBus atua como um barramento da Parte Operativa, pois realiza a conexão entre algums de seus componentes. A figura 3.1.4 mostra os componentes que podem escrever no registrador InBus através do MUX apropriado.

A figura 3.1.5 mostra o MUX definido na Parte Operativa para a escrita de alguns componentes no Contador de Programas, PC, bem como o Incrementador do PC. Pode-se verificar na figura 3.1.5 que o resultado de um incremento no PC (saída do Incrementador INC-PC) é armazenado num registrador auxiliar chamado *res-pc*. O conteúdo desse registrador é posteriormente armazenado no PC. Dessa forma o

registrador res-pc constitui-se também numa das entradas para o MUX de entrada do Contador de Programa. O fato de existir o registrador res-pc permite ao contador de programas endereçar uma instrução ao mesmo tempo em que é incrementado. Esta característica é utilizada para instruções de dois bytes que executam sobre o *pipeline*. O capítulo 4, que discute o *pipeline*, exemplifica como o PC é incrementado através do registrador res\_pc.

FIGURA 3.1.1 - Fluxo dos sinais entre as entidades VHDL da descrição do 8051.

A saída da RAM, DRAM\_OUT, atualiza o PC quando é executada uma instrução de retorno de sub-rotina, RET. Neste caso, a saída da RAM é o conteúdo da pilha que contém o valor do PC armazenado antes da chamada da sub-rotina. Por outro lado, a saída da ROM, MEMO, escreve no PC quando da execução de uma instrução de chamada a sub-rotina, LCALL. Neste caso, MEMO, possui o endereço de chamada da sub-rotina. Tanto para MEMO quanto para DRAM\_OUT, são necessárias duas entradas no MUX de entrada do PC porque o PC possui 16 bits. Desse modo, para cada entrada é realizada a concatenação (sinal & na descrição) com os outros 8 bits do PC, sendo necessárias duas leituras para atualizar o Contador de Programa.

FIGURA 3.1.2 - MUX para endereçamento da RAM

A figura 3.1.6 mostra as entradas (registradores Reg-A e Reg-B) e a saída (Out-ALU) da Unidade Lógico-Aritmética.

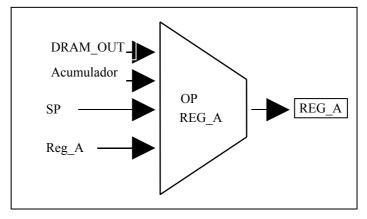

O registrador de entrada da ULA chamado Reg-A, pode ter o seu conteúdo alterado através de mais de um elemento microarquitetural. Dessa forma foi especificado um MUX para realizar a conexão entre todos os componentes da Parte Operativa que realizam a operação de escrita neste registrador. A figura 3.1.7 mostra esse MUX, onde pode-se verificar que o Acumulador, o Apontador de Pilha e a saída da ULA podem alterar o conteúdo de Reg-A.

A figura 3.1.8 ilustra um esboço da Parte Operativa. Por questões de praticidade do desenho, os elementos microarquiteturais estão conectados através de um barramento. Na figura 3.1.8 aparecem destacados os registradores que foram acrescentados à PO para a impementação do *pipeline*. O capítulo 4 exemplifica cada um desses registradores.

A entidade Parte de Validação serve para decodificação das instruções e geração do microcódigo. Para conseguir isso, esta entidade recebe como entradas, da Parte Operativa a instrução sendo executada, e da Máquina de Estados, o Estado atual do sistema. Desse modo, tendo por base a instrução decodificada e o estado, gera-se o microcódigo apropriado, pois cada palavra do microcódigo está em função dessas duas variáveis. Devido ao comportamento da Parte de Validação, para colocar-se e retirar-se instruções do conjunto de instruções do 8051, basta modificá-la em relação aos decodificadores de cada instrução.

Assim, a entidade Parte de Validação oferece a facilidade de modificação do conjunto de instruções, sendo indicada para arquiteturas reconfiguráveis. Cabe ressaltar que, como a PO não sofre alterações, o conceito de arquiteturas reconfiguráveis dentro dessa abordagem está significando uma alteração do conjunto de instruções, utilizando-se apenas as instruções definidas originalmente para o 8051. Isso significa que não irão ser incorporadas instruções novas no conjunto de instruções.

FIGURA 3.1.3 - MUX para escrita no Acumulador

A entidade ROM constitui-se na memória ROM interna, onde estão gravadas as instruções de qualquer programa específico que se queira realizar sobre o 8051. Do mesmo modo, a entidade RAM é a memória RAM interna onde se tem as variáveis ou os operandos.

Finalmente, a entidade Máquina de Estados é a geradora dos estados do microcontrolador para a execução do microcódigo. Tendo como entrada o número de bytes da instrução recebida da Parte de Controle, esta entidade gera o número de estados apropriados à execução da instrução. Como saída, envia o *estado atual* do microcontrolador para a Parte de Controle e Parte de Validação. A Parte de Controle utiliza-o para enviar os sinais de controle no tempo correto, como por exemplo, uma ordem para a Parte Operativa realizar uma leitura na ROM. A Parte de Validação utiliza o estado atual para gerar cada palavra do microcódigo. Para a descrição com Pipeline o número de estados gerados pela Máquina de Estados, alternam-se entre três (T0, T1 e T2) para as instruções que executam em um ciclo normal do *pipeline*, e doze (T0,...T11) para as instruções que causam uma "quebra" no *pipeline*.

A descrição do microcontrolador foi realizada dividindo o processador em módulos. Isso facilitou a simulação e depuração de cada módulo embora tenha criado uma tarefa suplementar: a definição dos sinais de *interface* entre os módulos.

A decisão de restringir as alterações unicamente ao módulo correspondente a *Parte de Validação*, ao ser gerado um novo processador, facilita a geração da descrição para a síntese em alto nível, porque o processo de decodificação e geração do microcódigo para todas instruções, é realizado neste módulo. Isto torna a Parte de Validação autônoma no sentido da realização de alterações no conjunto de instruções.

Como a Parte Operativa não sofrerá alterações, o que irá diferenciar um processador otimizado para uma determinada aplicação, de um processador otimizado para outra aplicação, será o conjunto de instruções. Assim, sempre que for necessária a definição de uma nova descrição, basta que sejam efetuadas alterações na Parte de Validação.

FIGURA 3.1.4 - MUX para ecrita no Registrador InBus

FIGURA 3.1.5 - MUX para escrita no PC e Incrementador do PC

FIGURA 3.1.6 - Registradores de entrada da Unidade Lógica-Aritmética

FIGURA 3.1.7 - MUX para escrita no Registrador *Reg\_a* da ULA.

FIGURA 3.1.8 - Parte Operativa do 8051 com pipeline

# 4 A abordagem Pipeline para o MCS8051

Microprocessadores e Microcontroladores cujo projeto datam da década de 70, como 8080, 8086, M6800, Z80, MCS8051, não exploram exaustivamente em sua arquitetura, a implementação de técnicas de paralelismo, como por exemplo, o *Pipeline*. Naquela época, praticamente ainda no princípio do desenvolvimento dos grandes microprocessadores, provavelmente não se imaginava que a demanda pelo aumento do poder de computação desses circuitos fosse crescer tanto e tão rapidamente, quanto verificou-se nos anos posteriores.