Resumo

Dezembro de 2004

Título: Implementação de um co-processador RSA

Orientador: André Inácio Reis

Co-orientador: Renato Perez Ribas

Aluno: Alcides Silveira Costa

Matrícula: 0069/99-1

### Nota

Este trabalho foi realizado no primeiro ano de existência do projeto BRAFITEC-PAGINER, coordenado pelo Prof. Dr. Cláudio F. R. Geyer e com o objetivo de promover o intercâmbio acadêmico entre alunos de engenharia de computação da UFRGS e estudantes de engenharia do INPG – Institut National Polytechnique de Grenoble (França).

Durante o período de agosto de 2003 a junho de 2004, cursei o último ano do curso de Engenharia de Telecomunicações em Grenoble, o qual é composto por duas etapas: um semestre de disciplinas e um semestre de estágio em uma empresa ou laboratório da universidade.

Na segunda etapa, realizei meu estágio no laboratório de pesquisas TIMA, onde desenvolvi, durante quatro meses, meu projeto de final de estudos. Regressando ao Brasil, propus continuar com meu trabalho, realizando, assim, uma obra um pouco diferenciada. Logo, este trabalho divide-se em duas partes: uma feita no Brasil e escrita em português (este resumo) e outra feita na França e escrita em inglês. Além disso, no final da versão inglesa encontram-se as transparências e o código em VHDL apresentado para a banca avaliadora do meu projeto no Brasil.

Porto Alegre, 05 de janeiro de 2005.

Alcides Silveira Costa.

# Introdução à versão brasileira

O presente trabalho tem por finalidade continuar com o projeto de final de estudos desenvolvido na França, INPG – *Départment Télécommunications* através do programa CAPES/BRAFITEC. Realizado no *TIMA Laboratory* sob orientação do Professor Régis Leveugle (PhD em microeletrônica – INP Grenoble) durante o período de fevereiro de 2004 até junho de 2004, foi avaliado por Jean-Louis Roch (PhD em Matemática Aplicada - Université Joseph Fourrier de Grenoble), obtendo nota final 14/20.

O tema proposto era o desenvolvimento em VHDL de um coprocessador criptográfico utilizando o algoritmo RSA [4]. Devido à complexidade do problema em manipular números de alta ordem, muito tempo foi despendido em busca de uma arquitetura capaz de executar o algoritmo em um tempo plausível. Várias arquiteturas foram estudadas e, após profunda análise, optamos por implementar uma arquitetura com seu núcleo baseado em pipeline [26]. Ao final do tempo de projeto, terminamos e validamos por meio de simulações a implementação de um módulo que realizava a multiplicação Montgomery [18].

De volta à UFRGS, venho propor a implementação do algoritmo de cifragem/decifragem RSA, sem o processo de geração de chaves. Isto foi definido pelo fato de sabermos que a geração de chaves pode ser feita via software. Além do mais, o processo de geração de chaves é realizado apenas uma vez, não havendo necessidade real de um hardware dedicado para isto. Logo, este documento relata o esforço no desenvolvimento final do hardware, sem preocupar-se com o processo de geração de chaves.

A estrutura desse trabalho está organizada da seguinte forma: este resumo apresenta, na primeira parte, uma síntese do trabalho realizado na França. Após, adicionou-se os resultados adquiridos na UFRGS. A versão detalhada com conceitos sobre o RSA, algoritmos de implementação estudados, diferentes arquiteturas e resultados anteriores está em inglês e anexada ao final deste documento. Maiores detalhes podem ser encontrados e serão referenciados no decorrer do texto.

### Resumo

### Síntese da versão inglesa

O surgimento da internet mudou radicalmente a maneira pela qual as pessoas trocam informações. Devido à sua crescente popularidade, aplicações como correio eletrônico, clientes de mensagens instantâneas, comércio eletrônico, transações bancárias e compras on-line estão se tornando parte de nossas vidas. Serviços como SMS e WAP estão crescendo em popularidade também. Entretanto, toda essa informação está sujeita a escuta. Uma pessoa pode interceptar sua informação se o sistema não prover mecanismos de segurança adequados para seus usuários. Tentando evitar problemas como estes, criptosistemas devem ser usados quando uma comunicação segura for necessária.

Criptografia é muito mais que apenas codificar e decodificar mensagens. Quando analisamos o mundo eletrônico, autenticação e identificação também são necessárias. Por exemplo, utilizamos autenticação a cada dia em nossas vidas, assinando documentos, cheques, etc. Entretanto, quando movemos para um mundo onde nossas decisões são tomadas eletronicamente, precisamos dispor de técnicas apropriadas.

Observando esse problema, Ronald Rivest, Adi Shamir, and Leonard Adleman desenvolveram em 1978 o criptosistema RSA (Rivest, Shamir, Adleman) [4]: um sistema de chave pública que permite tanto cifragem quanto assinaturas digitais (autenticação).

Em sistemas de chave pública, cada usuário possui um par de chaves. A chave pública é, obviamente, deixada pública enquanto a chave privada é mantida em segredo. A cifragem é realizada com a chave pública enquanto a decifragem é feita com a chave privada. A assinatura de um documento é realizada com a chave privada enquanto a autenticação é feita com a chave pública. Melhores detalhes sobre o funcionamento de sistemas de chave pública, como o RSA, podem ser encontrados na versão inglesa, seção 2, *Understanding Public-key Cryptosystems*.

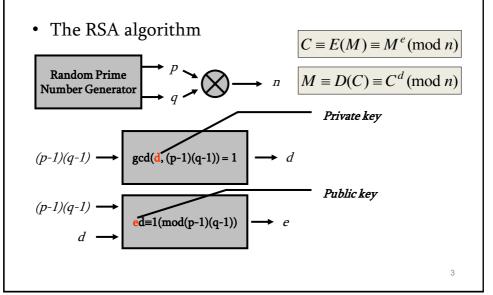

O algoritmo de cifragem RSA é simples e está descrito na seção 3, *The RSA Cryptosystem*. Sendo a chave pública definida pelo par de números positivos (e, n) e, similarmente, a chave privada definida pelo par (d, n), temos

$$C \equiv E(M) \equiv M^e \pmod{n}$$

para a cifragem de uma mensagem Me

$$M \equiv D(C) \equiv C^d \pmod{n}$$

para realizar a decifragem de uma mensagem cifrada C.

Apesar de simples, o algoritmo envolve números de altíssima ordem (atualmente, M, e, n e d devem ser de, pelo menos, 1024 bits de tamanho, conforme [8]). Essa ordem de grandeza surge do fato que a segurança do RSA está baseada na dificuldade de fatorar grandes números: as chaves são calculadas matematicamente combinando dois números primos de alta ordem. Mesmo conhecendo-se o produto desses números primos (que faz parte da chave pública divulgada, n), a segurança do algoritmo é garantida pela complexidade de fatorar esse produto e se obter os valores secretos.

Sendo assim, a implementação desse algoritmo em hardware torna-se desafiadora, pois o problema concentra-se em encontrar uma forma de realizar uma exponenciação modular rapidamente.

Para um melhor entendimento do algoritmo, robusteza, tamanho das chaves e um simples exemplo mostrando sua funcionalidade, refira-se à versão inglesa, seção 3, *The RSA Cryptosystem*.

Vários algoritmos foram estudados para resolver esse problema [7, 14-18, 20, 24]. Dentre eles, foi escolhido o método de exponenciação de Montgomery [7] (seção 4.1.2), utilizando o método de multiplicação de Montgomery [18]. Mesmo assim, três arquiteturas diferentes também foram analisadas, todas sugerindo maneiras diferentes de executar o RSA. Estas eram: arquiteturas em pipeline [16], arquiteturas baseadas em CRT [15] e arquiteturas baseadas em RNS [17]. Após análise, foram tiradas as seguintes conclusões.

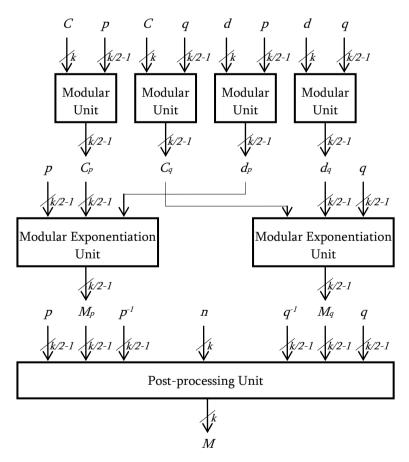

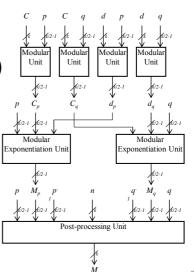

### Arquiteturas baseadas em CRT

Apresentam falha de segurança, deixando margem para o atacante. Como os fatores p e q, necessários para a geração das chaves não são destruídos (são mantido dentro do chip), o atacante pode decifrá-los através de um método de ataque por hardware [19]. Entretanto, essas arquiteturas são as que apresentam a solução mais rápida atualmente, pois dividem o cálculo da execução do RSA em duas unidades de processamento com tamanho de dados reduzidos pela metade.

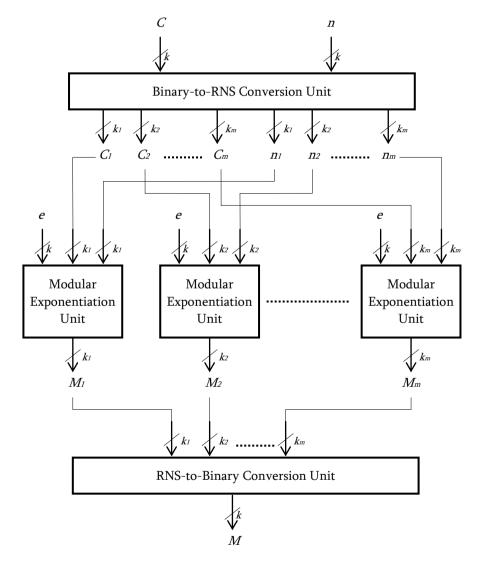

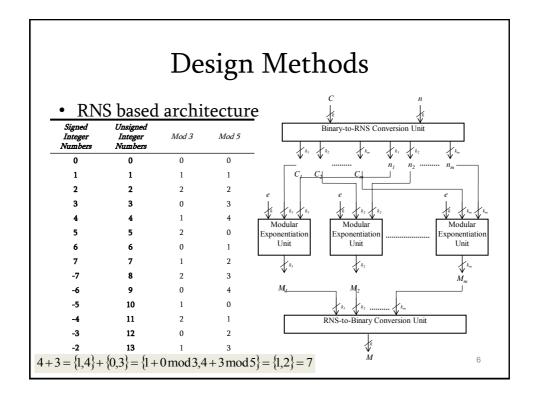

### Arquiteturas baseadas em RNS

Convertendo números binários para um sistema de números diferente (RNS), uma arquitetura altamente paralelizada pode ser implementada. Entretanto, estas não são adequadas para tamanhos de chave pequena, pois os passos de conversão de binário para RNS e vice-versa consomem muito tempo de processamento. Além do mais, sua complexidade de implementação é a maior dentre as três arquiteturas propostas. Apresenta resultados satisfatórios quando o tamanho de chave é maior que 2048 bits.

### Arquiteturas baseadas em Pipeline

Apesar de não apresentarem a mesma taxa de cifragem que as duas arquiteturas propostas anteriormente, não apresentam problemas de segurança em sua estrutura e não são tão complexas. Além do mais, sua taxa de cifragem de dados é mais que suficiente para muitas aplicações.

Optamos por implementar a arquitetura em pipeline, devido a sua simplicidade e eficiência. Maiores detalhes sobre os algoritmos e as arquiteturas estudadas podem ser encontrados na seção 4 da versão inglesa, *Design Methods*.

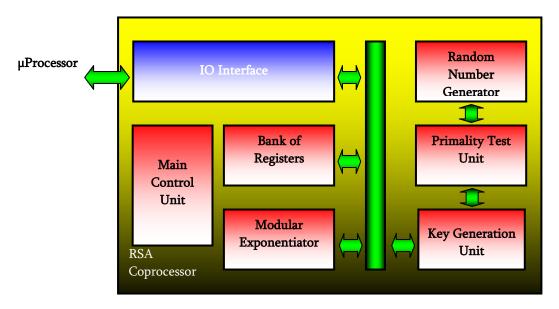

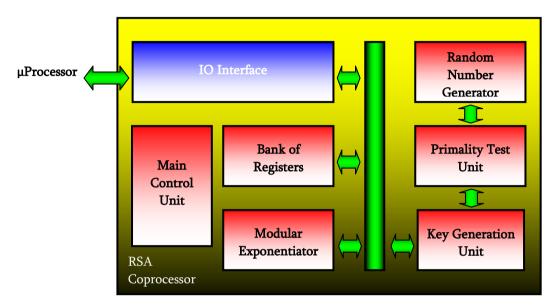

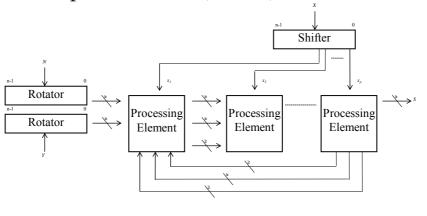

Depois de escolhida a arquitetura, partimos para a especificação do sistema, a qual pode ser vista na seção 5. Abaixo, temos a estrutura de blocos do sistema.

Figura 1 - Diagrama de Blocos

Cabe salientar que a idéia inicial era a de codificar todo o algoritmo RSA em VHDL. Entretanto, esse trabalho requer muito mais tempo de projeto. Perceba que vários blocos precisam ser implementados, cada um com características diferentes. Por exemplo, um bloco de geração de números aleatórios exige um tratamento totalmente diferente do bloco de testes de números primos. Logo, percebendo a inviabilidade de implementarmos todo o sistema em tempo hábil, decidimos concentrar nosso foco na unidade de exponenciação modular.

No final de quatro meses de trabalho, conseguimos terminar e validar por simulações um submódulo da unidade de exponenciação modular – a multiplicação de Montgomery – utilizando uma estrutura

em pipeline. Algoritmos, softwares utilizados e desenvolvidos para a validação do módulo podem ser analisados na seção 6 do documento em anexo.

Ao término do tempo de projeto, obtivemos um módulo totalmente parametrizável, podendo realizar a multiplicação de Montgomery com qualquer tamanho de operando, pois este seria quebrado em palavras definidas pelo usuário. Além disso, o trabalho foi escrito de maneira a conter ótimas referências, dando oportunidade para aqueles que querem conhecer a área de criptografia uma ótima introdução ao assunto.

# Continuação

### Trabalho realizado no Brasil

Chegando ao Brasil, foi proposta a continuação do trabalho com algumas restrições. Não seria implementada a parte de geração de chaves RSA no trabalho: apenas a continuação do algoritmo de exponenciação modular. Logo, tínhamos como meta implementar todos os blocos referentes a cifragem/decifragem.

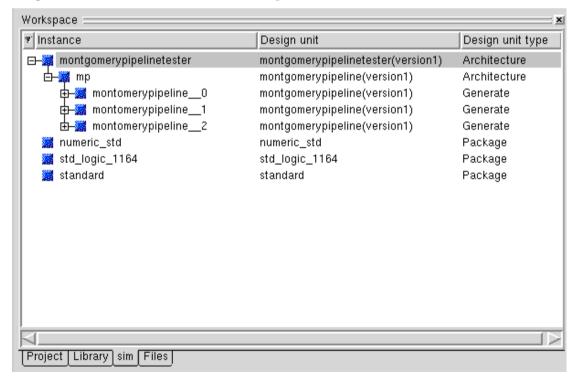

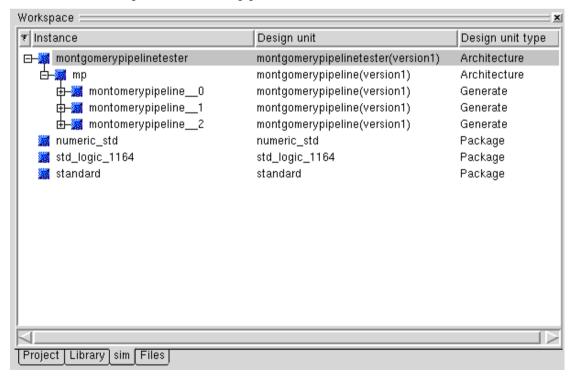

### Adaptação ao novo ambiente, reescrita de código e revalidação

A primeira dificuldade encontrada foi o novo ambiente de desenvolvimento utilizado. Todo o projeto tinha sido desenvolvido no Modelsim e sintetizado utilizando o Leonardo Spectrum da Mentor Graphics. Agora, estávamos utilizando o Quartus II Web edition da Altera. Houve necessidade de reescrita de código em alguns trechos devido a incompatibilidades encontradas no momento da síntese. Além do mais, *test benches* desenvolvidos em VHDL não eram mais necessários, desde que o ambiente da Altera utiliza *waveforms* para obter resultados de simulações. Logo, um certo tempo inicial foi despendido no aprendizado da nova ferramenta.

Passada esta etapa inicial, revalidamos o Módulo de multiplicação de Montgomery no Quartus II e extraímos os seus resultados. Conferimos com os resultados já adquiridos com o ModelSim (seção 6.1.1.1, *IP Implementation*) e todos fecharam. Entretanto, o trabalho original não descreve a arquitetura interna dos blocos PE (*processing element*), apenas mostra uma arquitetura básica do módulo de multiplicação modular (figura 4-3, versão inglês). Logo, detalharemos um pouco mais a arquitetura do coprocessador neste trabalho, começando pela a organização interna de um PE.

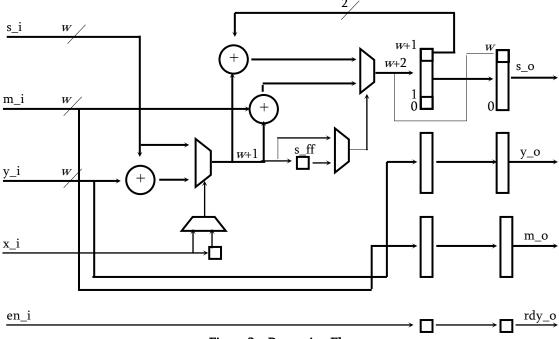

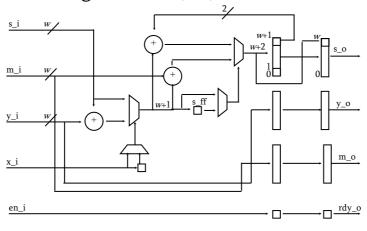

### Processing Element (PE)

A figura 2 representa a implementação das linhas 3 a 14 do algoritmo da seção 6.1.1. Note que s\_ff mantém o resultado da primeira soma (linha 3), o qual é usado para decidir se m\_i (módulo) será somado ao resultado nas outras iterações ou não.

Figura 2 – Processing Element

Além disso, há necessidade de um contador para controle do for loop nas linhas 6 e 11, pois este é controlado pelo sinal de habilitação (en\_i), que permanece ativo enquanto os dados de entrada forem válidos. As operações de deslocamento (linhas 8 a 13) são realizadas no registrador mais próximo da saída s o.

Entretanto, o algoritmo de multiplicação Montgomery ainda não está pronto, pois este deve utilizar vários PE para ser construído, conforme explicado a seguir.

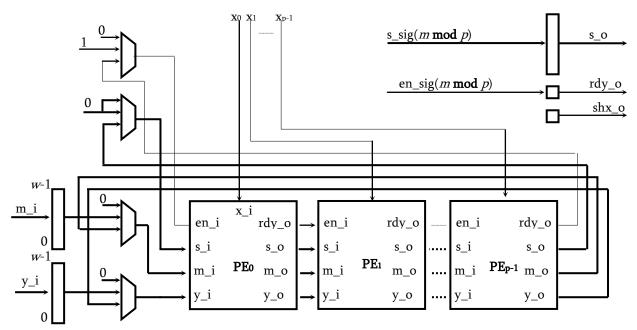

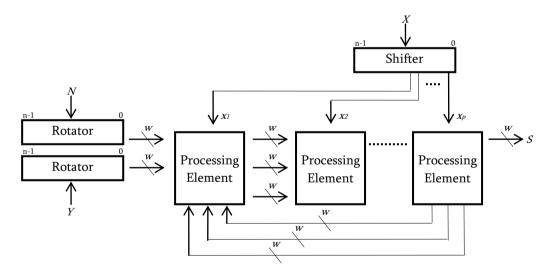

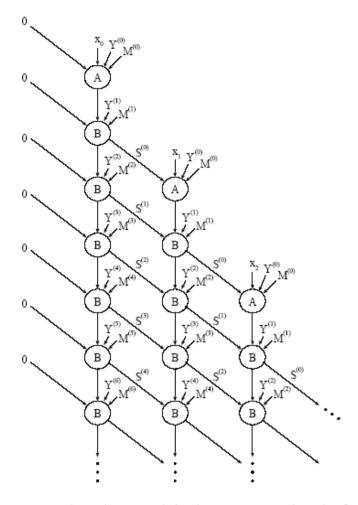

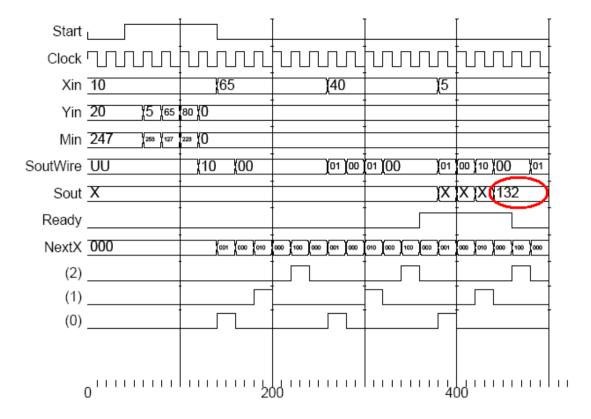

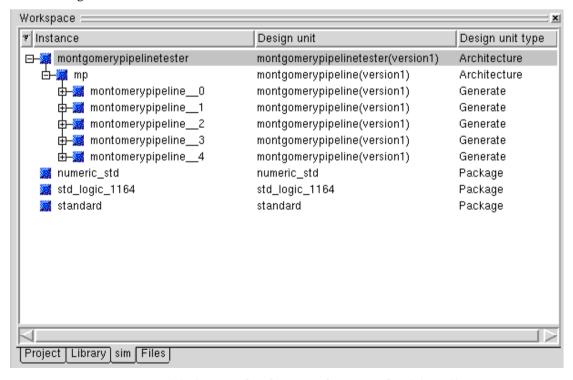

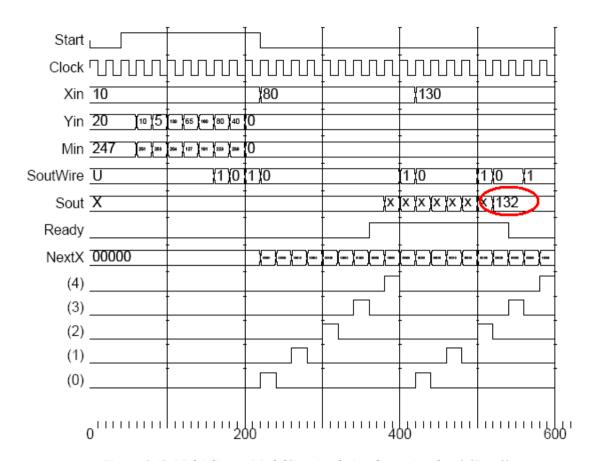

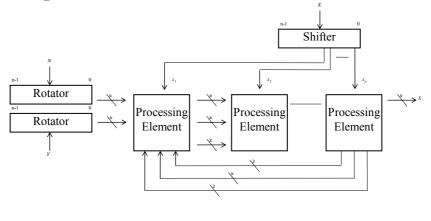

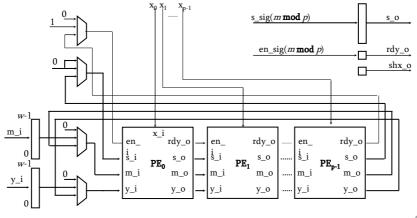

### Montgomery Multiplication Unit (MM)

Figura abaixo mostra a maneira como foi implementado o multiplicador de Montgomery.

Figura 3 – Montgomery Pipeline

Salientamos que o pipeline mostrado na figura acima é realimentado e que sua saída é totalmente dependentes dos parâmetros p (número de unidades paralelas) e m (tamanho do módulo em bits). Logo, existe um controle especial para determinar quando o resultado do pipeline deve ser copiado para os registradores de saída. Outro sinal importante é o  $shx_o$ . Este indica quando o registrador x (figura 4-3, versão inglês) deve ser deslocado.

### Escolha do algoritmo de exponenciação modular

Finalmente chegamos ao momento de implementar o RSA propriamente dito. Vários algoritmos foram estudados (seção 4, *Design Methods*). Entretanto, o que melhor se adaptou às nossas necessidades foi o algoritmo apresentado logo abaixo, estudado no Brasil e extraído de [16].

### Exponenciação de Montgomery

Entradas: M, e, n, k

*Saída: M<sup>e</sup> mod n*

1.  $\overline{M} := \operatorname{MonPro}(M, k)$

2. x := MonPro(1, k)

3 for i := k-1 down to 0 do

```

4 \overline{x} := \operatorname{MonPro}\left(\overline{x}, \overline{x}\right)

5. if e_i = 1 then \overline{x} := \operatorname{MonPro}\left(\overline{M}, \overline{x}\right)

6 x := \operatorname{MonPro}\left(\overline{x}, 1\right)

7. return x

```

O parâmetro k é uma constante e deve ser pré-calculado, assim como as chaves. Ele vale  $2^{2m} \mod n$ , onde m equivale ao tamanho do módulo n em bits. Perceba, também, que o algoritmo usa somente a unidade de multiplicação de Montgomery, não havendo necessidade de uma unidade especial para o cálculo do algoritmo de Euclides, como proposto no algoritmo da seção 4.1.2.

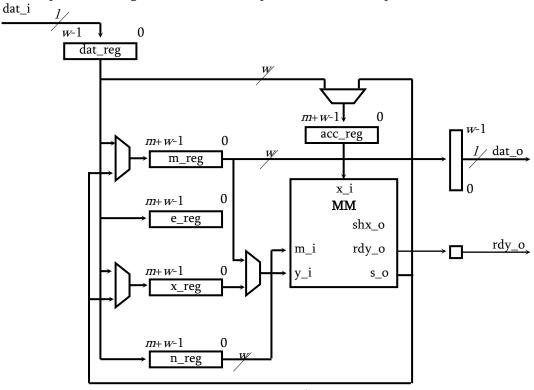

### O Coprocessador RSA

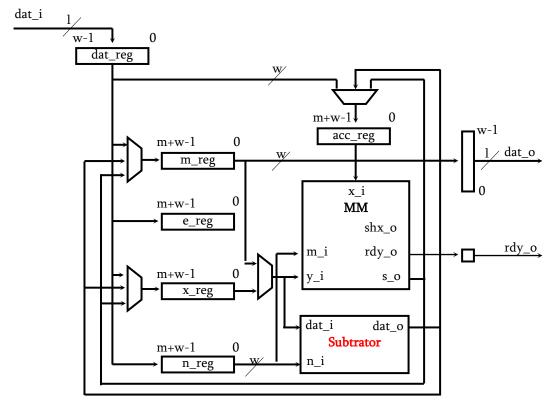

O coprocessador RSA desenvolvido também possui uma interface parametrizável onde os dados de entrada são quebrados em palavras. Dessa forma, podemos carregar os dados para dentro do coprocessador com uma palavra de tamanho *I.* Este tamanho independe do tamanho das palavras internas ao coprocessador (barramento interno), ou seja, os cálculos internos são realizados com um tamanho de palavra *w.* A figura abaixo ilustra a arquitetura interna do coprocessador RSA.

Figura 4 - Coprocessador RSA

Os registradores *dat\_reg*, *m\_reg*, *x\_reg* e *n\_reg* possuem *n*+w bits de tamanho. Este requisito é necessário para o funcionamento do algoritmo de multiplicação (capítulo 6). Os registradores *m\_reg* e *x\_reg* são rotacionadores de *w* bits e *acc\_reg* é um registrador de deslocamento de *p* bits controlado pelo sinal *shx\_o* (MM). Além disso, *acc\_reg* também serve de acumulador para resultados intermediários.

Note que essas características permitem, por exemplo, sintetizar um coprocessador com uma quantidade mínima de pinos. Este é o caso de muitos Smart Cards que são utilizados em transações bancárias, onde o número de pinos não passa de oito.

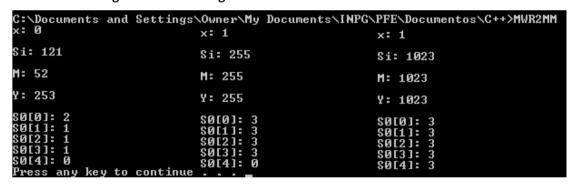

### Problemas com o algoritmo MWR2MM

O algoritmo proposto por [26] e apresentado no capítulo 6 apresenta algumas falhas. Na implementação do coprocessador RSA, foram descobertos alguns erros. Por exemplo, suponha o seguinte problema:

Sendo n=13, M=6 e=5, calcule  $C = M^e \mod n$ .

Substituindo os valores, temos C=2. Entretanto, se encontrarmos C=15, este resultado não está totalmente errado, já que  $C=15 \mod 13=2$ . Ou seja, a maneira como foi implementado o algoritmo MWR2MM, retorna, em alguns casos, um resultado fora do intervalo [0, n). Logo, um bloco de correção deve ser adicionado na figura 4. Sua arquitetura é mostrada na figura abaixo.

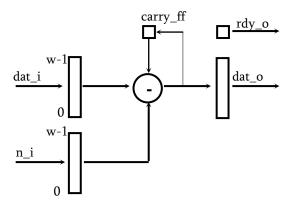

Figura 5 – Subtrator em pipeline

Note que a correção é uma subtração entre o resultado fora do intervalo [0, n) e n. Para isso, os dados de entrada são calculados, palavra a palavra, da mesma maneira que o cálculo da multiplicação Montgomery. A nova arquitetura da figura 4, então, é mostrada na figura 6.

Figura 6 - Coprocessador RSA com correções

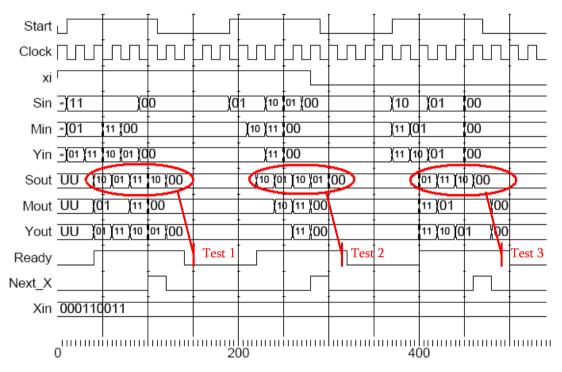

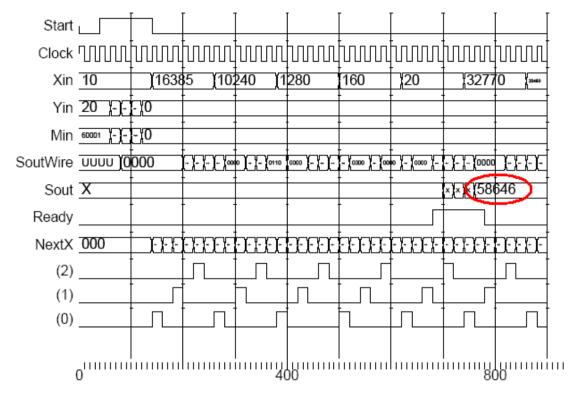

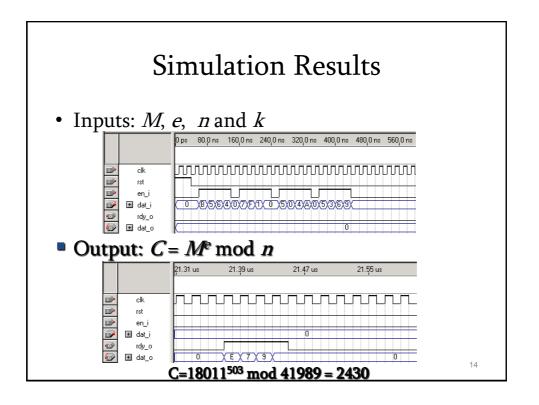

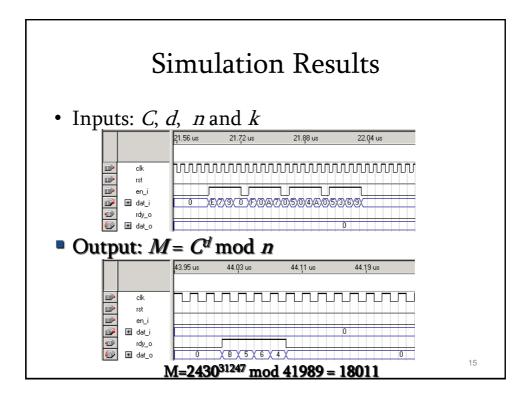

### Resultados da Simulação

Sendo m o número de bits dos operandos, w o tamanho de uma palavra interna e l o tamanho do barramento de dados de entrada, analisamos os seguintes casos:

**Caso I:**

$$m = 8$$

,  $w = 4$ ,  $l = 2 e r = 2^m = 256$

Para os dados de entrada, temos:

$$M = 200$$

,  $d = 199$ ,  $e = 55$ ,  $n = 221e k = r^2 \mod n = 256^2 \mod 221 = 120$

E, em binário:

$M = 11\ 00\ 10\ 00$

$e = 00 \ 11 \ 01 \ 11$   $d = 11 \ 00 \ 01 \ 11$

$n = 11\ 01\ 11\ 01$   $k = 01\ 11\ 10\ 00$

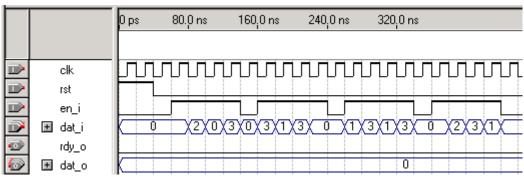

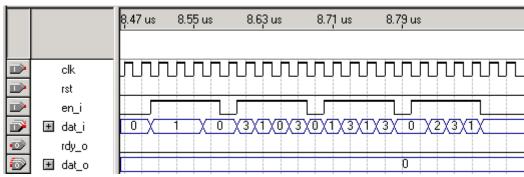

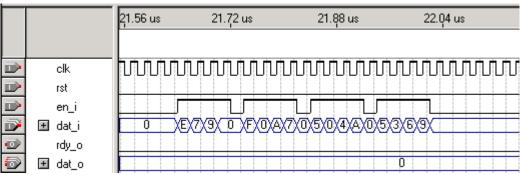

Os dados devem ser inseridos da palavra menos significativa à mais significativa, necessariamente. A ordem dos operandos deve ser: M/C, e/d, n e k. A figura abaixo mostra M, e, n, e k sendo carregados, respectivamente, no coprocessador (carregados aos pares de bits). Note que um sinal de reset foi inserido para inicializar o sistema.

Figura 7 – Simulação (entradas - M, e, n e k)

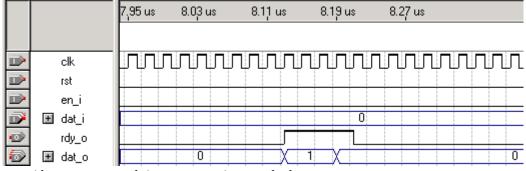

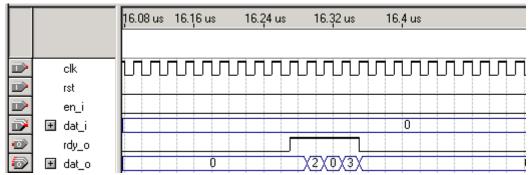

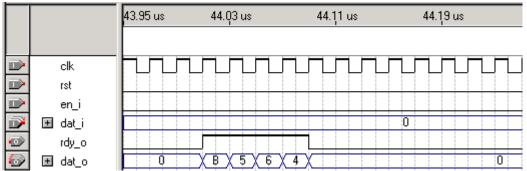

Transcorrido certo tempo, obtivemos o seguinte resultado:

Figura 8 – Simulação (resultado - C)

Ou seja,  $C = 200^{55} \mod 221 = 00010101_b = 21$ . Carregando C, d, n, e k novamente nas entradas do coprocessador, devemos obter M, a mensagem cifrada. As figuras a seguir ilustram esse processo.

Figura 9 – Simulação (entradas – C, d, n e k)

Figura 10 - Simulação (resultado - M)

$M = 21^{199} \, \mathrm{mod} \, 221 = 11001000_b = 200$  . Deciframos a mensagem.

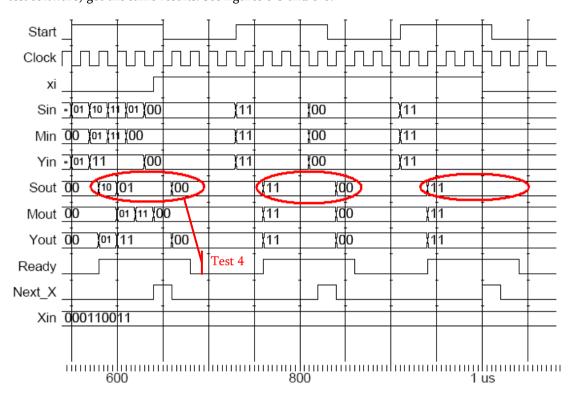

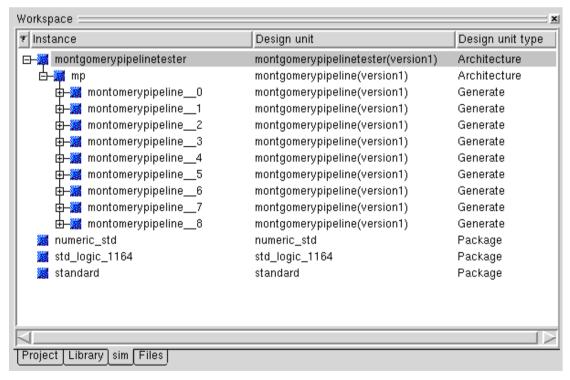

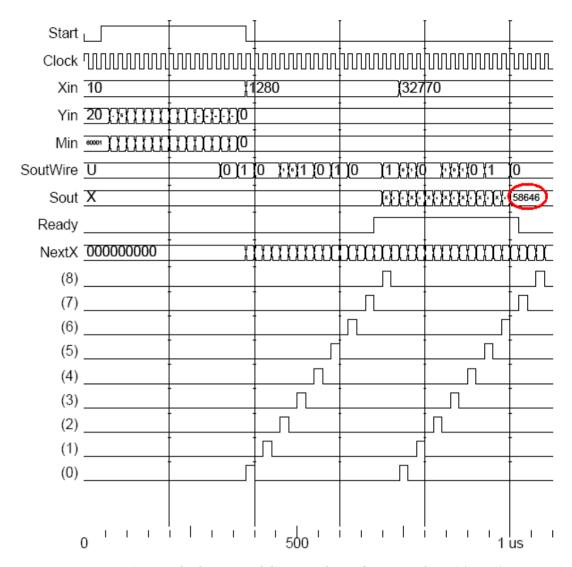

**Caso II:** m = 16, w = 4,  $l = 2 er = 2^m = 65536$

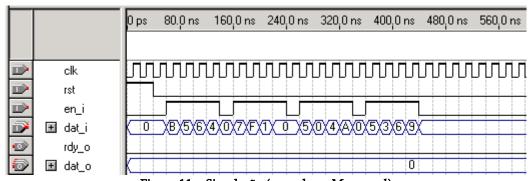

Entrada: M = 18001, d = 31247, e = 503, n = 41989 e  $k = r^2 \mod n = 65536^2 \mod 41989 = 38453$ Seguindo os mesmos passos da sistemática de testes do caso I, temos:

Figura 11 – Simulação (entradas - M, e, n e k)

Figura 12 – Simulação (resultado - C)

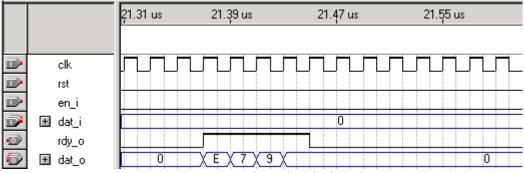

Figura 13 – Simulação (entradas – C, d, n e k)

Figura 14 – Simulação (resultado – M)

Novamente, os resultados confirmam a funcionalidade do coprocessador desenvolvido.

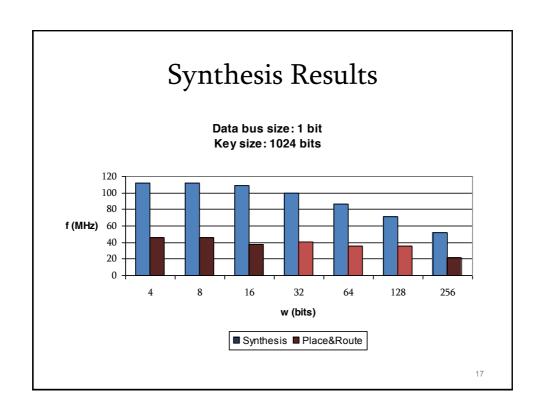

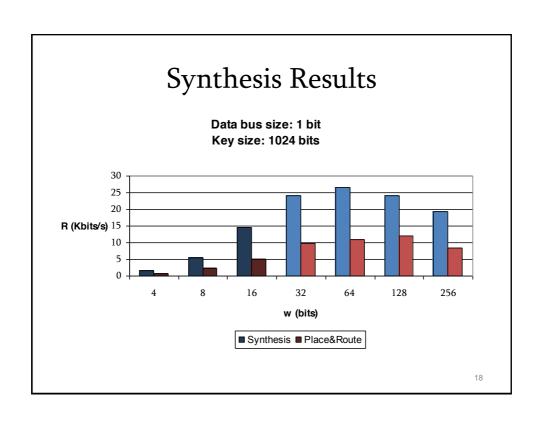

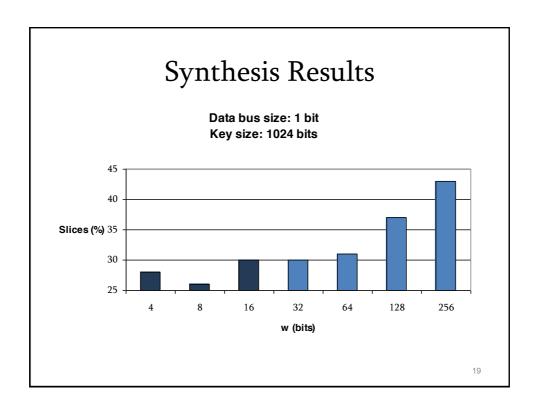

### Resultados da Síntese

Sendo m=1024, w=32 e l=8, obtemos os seguintes resultados utilizando o sintetizador XST da Xilinx e codificação one-hot:

### Total de Registradores: 373

- 91 Flip-flops

- 1 Registrador de 10 bits

- 256 Registradores de 32 bits

- 17 Registradores de 34 bits

- 2 Registradores de 6 bits

- 6 Registradores de 8 bits

## Total de Multiplexadores: 165

- 1 Multiplexador de 1 bit de 1056-para-1

- 164 Multiplexadores 2-para-1

### Total de Somadores/Subtratores: 57

- 1 subtrator de 10 bits

- 17 somadores de 32 bits

- 2 subtratores de 33 bits

- 34 somadores de 24 bits

- 2 somadores de 6 bits

- 1 somador de 8 bits

### Total de Comparadores: 2

2 Comparadores de 9 bits (menor igual)

### Total de pinos de IO: 20

O dispositivo selecionado foi um Virtex Pro II (2vp100ff1696-6). Abaixo segue um relatório sobre o total de recursos utilizados:

Number of Slices

: 12829 out of 44096 (29%)

Number of Slice Flip Flops

: 8977 out of 88192 (10%)

Number of 4 input LUTs

: 22562 out of 88192 (25%)

Number of bonded IOBs

: 19 out of 1164 (1%)

Number of GCLKs

: 1 out of 16 (6%)

Freqüência máxima de operação : 99.636MHz

### Caminho Crítico:

mp\_block/current\_state\_FFd4 (FF) -> mp\_block/MP0/cs\_reg1\_33 (FF) Tempo: 6.863ns lógica e 3.174ns roteamento (68.4% lógica e 31.6% roteamento)

Sabendo que a equação do número de ciclos para a cifragem de *m* bits é dada por:

$$N_{mc} = \frac{m}{l} + (m+2) \cdot e^{\frac{m}{p}}$$

(melhor caso)

$$N_{pc} = \frac{m}{l} + 2 \cdot (m+2) \cdot e \left(\frac{m}{p} + \frac{m}{w}\right),$$

(pior caso)

podemos estimar a taxa média de bits cifrados por segundo, o qual pode ser aproximada por:

$$T_{cifragem} = \frac{2 \cdot freq}{N_{pc} + N_{mc}} \cong 24 m \, bits / s .$$

Como m=1024 nos nossos testes, obtivemos uma taxa média de cifragem de 24Kbits/s.

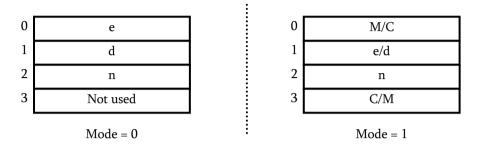

### Interface do Coprocessador RSA

Para o funcionamento do IP, as seguintes medidas devem ser tomadas':

### Durante processo de síntese

- A largura do barramento de dados de entrada deve ser menor ou igual à do barramento de dados internos  $w \ge l$ .

### Durante o funcionamento

- Mensagem a ser cifrada deve ser menor que o módulo n;

- Módulo *n* deve permanecer entre o intervalo  $(2^{m-1}, 2^m)$ ;

- Parâmetro k deve ser pré-calculado;

Abaixo segue uma tabela com os pinos de entrada e saída do coprocessador recém desenvolvido:

| Nome do Pino | Tamanho | Direção | Ativo           | Descrição                         |

|--------------|---------|---------|-----------------|-----------------------------------|

| clk          | 1       | entrada | borda de subida | Relógio do Sistema                |

| en_i         | 1       | entrada | 1 lógico        | Habilita dados de entrada         |

| dat_i        | L       | entrada | -               | Dados de entrada (mensagem)       |

| rdy_o        | 1       | saída   | 1 lógico        | Indica dados válidos na saída     |

| dat_o        | L       | saída   | =               | Dados de saída (mensagem cifrada) |

Tabela 1 – descrição dos pinos do coprocessador RSA

## Conclusão da versão brasileira

O presente trabalho mostrou diversos passos considerados no desenvolvimento de um coprocessador RSA. Do aprendizado de um novo assunto até o resultado final, muitas decisões foram tomadas.

Apesar de existirem soluções mais rápidas, esta implementação garante a segurança dos dados cifrados, pois não mantém internamente os fatores primos intermediários para acelerar o seu cálculo (CRT). Apresentando apenas uma unidade de cálculo, a arquitetura desenvolvida tem a grande vantagem de consumir menos recursos da arquitetura alvo, fato não verdadeiro em arquiteturas RNS.

Muitas dificuldades foram encontradas no decorrer do caminho: um assunto novo, uma arquitetura desafiadora, um algoritmo problemático e ferramentas de desenvolvimento não disponíveis para o desenvolvimento. Entretanto, chegamos ao final do tempo de projeto com um IP funcional e reutilizável para qualquer tamanho de chave, pelo menos enquanto o RSA existir e for considerado seguro.

Mesmo assim, ainda podemos realizar algumas melhorias no coprocessador. Por exemplo, atualmente o IP não suporta que a largura do barramento de dados externo seja maior ou igual do que a largura do barramento de dados interno (l >= w). Leituras após a validação do projeto [16], constataram que uma melhoria no algoritmo pode levar a taxas de 50 Kb/s, não importando se for o melhor ou o pior caso. Esta melhoria aconteceria com a duplicação dos recursos utilizados do dispositivo alvo. Além disso, o coprocessador não aceita mensagens maiores que n e menores que n, uma precaução ainda não tomada.

E, finalmente, apesar de existirem soluções mais rápidas, a velocidade de cifragem atingida neste trabalho é mais que suficiente para muitas aplicações. Por exemplo, alguém utilizando uma Smart Card para autorizar o débito em sua conta bancária, com certeza, não se importaria em esperar cinco centésimos de segundo para assinar uma mensagem digitalmente. Em outro exemplo, podemos citar o envio de informações telefônicas no início de uma chamada por celular (código do aparelho e número do telefone do assinante), onde este tempo gasto não faria a menor diferença para o usuário (e o protegeria da clonagem de seu aparelho).

# DÉPARTEMENT TÉLÉCOMMUNICATIONS

**ENSIMAG ENSERG**

incillut railand polytechnique de Grancbie établissement d'ensetgrement supérieur public

Projet de fin d'étude Rapport final Juin 2004

Sujet: Implémentation d'un co-processeur RSA

Nom et prénom du responsable: Leveugle, Régis

Nom et prénom du tuteur de l'INPG: Jean-Louis, Roch

Nom, prénom et option de l'étudiant: Costa, Alcides, Architecture des Equipements

## Résumé

Ce travail décrit la conception d'un co-processeur RSA. Les fondements des cryptosystèmes à clef publique sont présentés, en montrant leur importance et leurs applications. L'algorithme RSA est ensuite présenté et expliqué. Trois architectures différentes utilisées aujourd'hui pour l'implémentation matérielle de cet algorithme sont ensuite étudiées et analysées: CRT, RNS et l'architecture basée sur un pipeline. Des algorithmes arithmétiques existants sont également détaillés. Après l'analyse des avantages et des inconvénients de chaque solution, nous avons décidé d'implémenter une architecture pipeline qui calcule l'algorithme de multiplication de Montgomery.

Le circuit correspondant a été décrit en VHDL et simulé avec ModelSim. Les résultats obtenus ont montré que l'architecture développée est entièrement fonctionnelle. Elle peut manipuler des nombres de taille quelconque simplement en choisissant la taille des données du pipeline. Finalement, nous pouvons réaliser un taux d'encryptage/décryptage d'environ 25 Kbits/s avec une horloge de 80,9 Mhz et des entrées de 1024 bits.

## **Abstract**

This work describes the design of a scalable RSA coprocessor. By introducing the basics of public-key cryptosystems we provide a good background in cryptography, showing its importance and applications. The RSA algorithm is presented and explained. Three different architectures used today are studied and analyzed: CRT, RNS and Pipelined-based architectures. Existing arithmetic algorithms are also covered. After realizing advantages and disadvantages of each solution we decided to implement a pipelined-based architecture which computes the Montgomery Multiplication algorithm.

By doing this, we coded this architecture in VHDL and simulated it with ModelSim. The results obtained proved that the developed architecture is fully functional. It can manipulate any number of bits simply by selecting the pipeline word size. Finally, with an 80.9 MHz clock and 1024-bit inputs, we can achieve an encryption/decryption rate of about 25 Kb/s.

# **Contents**

| Introduction                                                  | 9  |

|---------------------------------------------------------------|----|

| 1. A Glance at Cryptography                                   | 11 |

| 1.1. Concepts                                                 | 11 |

| 1.2. Cryptography Applications                                | 12 |

| 1.2.1. Secure Communication.                                  | 12 |

| 1.2.2. Identification and Authentication                      |    |

| 1.2.3. Secret Sharing                                         |    |

| 1.2.4. Electronic Commerce                                    |    |

| 1.2.6. Key Recovery                                           |    |

| 1.2.7. Remote Access                                          |    |

| 1.2.8. Other Applications                                     |    |

| 1.3. Importance of Cryptography                               | 13 |

| 1.3.1. Cryptography on the Internet                           |    |

| 1.3.2. Authentication                                         |    |

|                                                               |    |

| 2. Understanding Public-key Cryptosystems                     | 17 |

| 2.1. Public-key Cryptosystems                                 |    |

| 2.1.1. Encryption                                             |    |

| 2.1.2. Digital Signatures                                     |    |

| 2.2. Systems related to Public-key Cryptosystems              |    |

| 2.2.1. Secret-key Cryptosystem                                |    |

| 2.2.2. Hash functions                                         |    |

| 2.3. Advantages and disadvantages of public-key cryptosystems |    |

| 2.4. Some applications liked to Public-key Cryptosystems      |    |

| 2.4.1. Authentication and Digital Signature                   |    |

| 2.4.2. Key agreement protocol                                 |    |

| 2.4.4. Identification                                         |    |

| 2 TH. DCA C 4 4                                               | 22 |

| 3. The RSA Cryptosystem                                       |    |

| 3.1. The RSA algorithm                                        |    |

| 3.1.2. Digital Signature                                      |    |

| 3.2. RSA Speed                                                |    |

| 3.3. RSA Robustness                                           |    |

|                                                               |    |

| 3.4. Key sizes                                                |    |

| 3.5. A Simple Example                                         | 26 |

| 4. Design Methods                                             |    |

| 4.1. Modular Exponentiation Algorithms                        |    |

| 4.1.1. Binary Exponentiation Method.                          |    |

| 4.1.1.1 Interleaving multiplication and reduction             |    |

| 4.1.1.2. Restoring Division Algorithm                         |    |

| 4.1.1.4. Montgomery's Multiplication Algorithm                |    |

| 4.1.2. Montgomery Exponentiation                              |    |

| 4.2. RSA Architectures                                        | 34 |

| 4.2.1 CRT Based Architecture                                  | 34 |

| 8. Bibliography                                                | 59 |

|----------------------------------------------------------------|----|

| 7. Conclusion                                                  | 57 |

| 6.3. Synthesis Results                                         | 56 |

| 6.2. Simulation Results                                        | 48 |

| 6.1. Multiple Word Raidx-2 Montgomery Multiplication Algorithm | 45 |

| 6. IP Implementation                                           | 45 |

| 5.7. Main Control Unit                                         | 44 |

| 5.6. Modular Exponentiator                                     | 44 |

| 5.5. Key Generation Unit                                       | 43 |

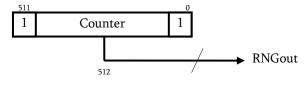

| 5.4. Primality Test Unit                                       | 43 |

| 5.3. Random Number Generator                                   | 42 |

| 5.2. Bank of Registers                                         | 42 |

| 5.1.10 Interface                                               | 41 |

| 5. Coprocessor IP Specification                                | 41 |

| 4.3. Conclusions                                               | 39 |

| 4.2.3. Pipelined Architecture                                  |    |

| 4.2.2. RNS Based Architecture                                  | 36 |

# Introduction

The advent of the Internet has radically changed the way people exchange information. Due to its growing popularity, applications like electronic mail, instant messengers, electronic commerce, electronic banking, and online shopping are becoming part of our lives. Cell phones services like SMS and WAP are growing in their popularity as well. However, all this information is vulnerable to eavesdropping. A third party group may tap your information if the system doesn't provide adequate security for users. To avoid this problem, cryptographic algorithms are used when secure communication is needed.

Since ancient times, cryptography has been used mainly for military purposes. Its first use dates back to 1900 BC, when a scribe in Egypt used a derivation of the standard hieroglyphic of the day to communicate [12]. However, the Roman emperor Julius Caesar is considered to be one of the first people to have employed encryption for securing messages [11]. Caesar decided his standard algorithm would shift each letter of the Roman alphabet a predetermined number of places. He informed all of his generals of his decision. By following this example and shifting the contemporary English alphabet over 3 places, a message like ZEBRA would be ciphered as CHEUD. Despite of being an unbreakable cryptography system at that time, this system can be currently broken in a few seconds.

Today's cryptography is concerned with more than just encrypting and decrypting messages. When we move to an electronic world, authentication and identification schemas are needed. Whenever we log on a remote computer to access our bank account, or we shop online using our credit card, we are subjected to eavesdropping and possibly forgery.

By observing this problem, Ronald Rivest, Adi Shamir, and Leonard Adleman developed in 1978 the RSA (Rivest, Shamir, Adleman) cryptosystem [4]: a public-key cryptosystem that offers both encryption and digital signatures (authentication).

Public key cryptosystems are not the only ones used in applications. Secret key cryptosystems and elliptic curve cryptosystems are largely exploited as well. However, a detailed explanation about these last cryptosystems is outside the scope of this work. Only cryptography tools associated to the RSA cryptosystem will be discussed.

It's not the purpose of this work to write lines of codes or draw pages of logic schematics. The purpose of this work is to present the design of a RSA coprocessor and give a theoretical base to the reader in the cryptography field. This allows interested parties to understand the project and proceed with the work, if necessary. For this reason, the first three sections are reserved to give a good background to the reader. The other sections will be reserved for the project itself, detailed below.

Section 1 provides a basic introduction to the field of cryptography. It gives a brief explanation about its main concepts, some applications where it can be found, and its importance to the electronic world.

In section 2 public-key cryptosystems are covered. Also, two systems related to public-key cryptosystems are introduced: secret-key cryptosystems and hash functions.

Section 3 approaches the RSA cryptosystem, explaining its algorithm in a very practical way.

Section 4 introduces some modular exponentiation algorithms used to compute RSA and how they can be applied in digital systems. It presents and compares the three most used architectures found in the literature today: CRT, RNS and Pipelined based architectures.

Section 5 specifies our proposed coprocessor organization in a block diagram form and its related pinout interface.

Finally, in section 6 we describe the techniques used to implement some blocks introduced in the section 5 and its results.

# 1. A Glance at Cryptography

This section provides the reader a basic introduction to the field of cryptography. It gives a brief explanation about its main concepts, some applications where it can be found, and its importance to the electronic world. This chapter was extracted from [1].

# 1.1. Concepts

Cryptography today might be summed up as the study of techniques and applications that depend on the existence of difficult problems. We should also say that it is the science of using mathematics to secure information and create a high degree of trust. Cryptanalysis is the study of how to compromise (defeat) cryptographic mechanisms, and cryptology (from the Greek kryptos logos, meaning "hidden word") is the discipline of cryptography and cryptanalysis combined. To most people, cryptography is concerned with keeping communications private. Indeed, the protection of sensitive communications has been the emphasis of cryptography throughout much of its history. However, this is only one part of today's cryptography.

*Encryption* is the transformation of data into a form that is as close as possible to an understandable form of reading without the appropriate knowledge (a key; see below). Its purpose is to ensure privacy by keeping information hidden from anyone who it is not allowed, even those who have access to the encrypted data. *Decryption* is the reverse of encryption; it is the transformation of encrypted data back into an intelligible form.

Encryption and decryption generally require the use of some secret information, referred to as a *key*. For some encryption mechanisms, the same key is used for both encryption and decryption; for other mechanisms, the key used for encryption and decryption is different. Data to be encrypted is called *Plaintext*. *Ciphertext* is the encrypted data.

Today's cryptography is more than encryption and decryption. *Authentication* is as fundamental as privacy. We use authentication throughout our everyday lives (when we sign our name to some document, for instance). As we move to a world where our decisions and agreements are communicated electronically, we need to have electronic techniques for providing authentication.

Cryptography provides mechanisms for such procedures. A *digital signature* binds a document to the possessor of a particular key, while a *digital timestamp* binds a document to its creation at a particular time. These cryptographic mechanisms can be used to control access to a shared disk drive, a high security installation, or a pay-per-view TV channel.

The field of cryptography encompasses other uses as well. With just a few basic cryptographic tools, it is possible to build elaborate schemes and protocols that allow us to pay using electronic money, to prove we know certain information without revealing the information itself, and to share a secret quantity in such a way that a subset of the shares can reconstruct the secret.

While modern cryptography is growing increasingly diverse, cryptography is fundamentally based on problems that are difficult to solve. A problem may be difficult because its solution requires some secret knowledge, such as decrypting an encrypted message or signing some digital document without the key. The problem may also be hard because it is intrinsically difficult to complete, such as finding a message that produces a given hash value (explained in section 3.2.2).

An encryption system together with a corresponding decryption system is a *cryptosystem* [2]. Two classes of cryptosystems are *secret-key* and *public-key cryptosystems*. In secret-key cryptosystems, also referred to as *symmetric cryptography*, the same key is used for both encryption and decryption. The most popular secret-key cryptosystem in use today is the *Data Encryption Standard*, also known as *DES*.

In public-key cryptosystems, each user has a *public key* and a *private key*. The public key is made public while the private key remains secret. Encryption is performed with the public key while decryption is done with the private key. The *RSA public-key cryptosystem* is the most popular form

of public-key cryptography. RSA stands for Rivest, Shamir, and Adleman, the inventors of the RSA cryptosystem.

The *Digital Signature Algorithm* (*DSA*) is also a popular public-key technique, though it can only be used only for signatures, not encryption. *Elliptic curve cryptosystems* (*ECCs*) are cryptosystems based on mathematical objects known as elliptic curves. Elliptic curve cryptography has been gaining in popularity recently. Lastly, the *Diffie-Hellman key agreement protocol* is a popular public-key technique for establishing secret keys over an insecure channel.

# 1.2. Cryptography Applications

Privacy is perhaps the most obvious application of cryptography. Cryptography can be used to implement privacy simply by encrypting the information intended to remain private. In order for someone to read this private data, one must first decrypt it.

There are a large number of applications in which it is being currently in use. For example, simple cryptography systems can be used for *secure communication*, *identification*, *authentication*, and *secret sharing*. However, more complicated applications include systems for *electronic commerce*, *certification*, *secure electronic mail*, *key recovery*, and *secure computer access*. A better explanation of these applications can be read in the next lines below.

### 1.2.1. Secure Communication

Secure communication is the most straightforward use of cryptography. Two people may communicate securely by encrypting the messages sent between them. This can be done in such a way that a third party eavesdropping may never be able to decipher the messages. While secure communication has existed for centuries, the *key management*<sup>1</sup> problem has prevented it from becoming commonplace. Thanks to the development of public-key cryptography, it is possible to create a large-scale network of people who can communicate securely with one another even if they had never communicated before.

### 1.2.2. Identification and Authentication

Identification and authentication are two widely used applications of cryptography. Identification is the process of verifying someone's or something's identity. For example, when you withdraw some money from a bank, a teller asks you to see your identification (a drive's license, for instance). By doing this, he or she verifies the identity of the owner's account (your identity). This same process can be done electronically by using cryptography. Every automatic teller machine (ATM) card is associated with a "secret" personal identification number (PIN), which binds the owner to the card and thus to the account. When the card is inserted into the ATM, the machine prompts the cardholder for the PIN. If the correct PIN is entered, the machine identifies that person as the rightful owner and it grants him access. Another important application of cryptography is authentication. Authentication is similar to identification, in that both allow an entity access to resources (such as an Internet account), but authentication is broader because it does not necessarily involve identifying a person or entity. Authentication merely determines whether that person or entity is authorized for whatever is in question.

### 1.2.3. Secret Sharing

Another application of cryptography, called secret sharing, allows the trust of a secret to be distributed among a group of people. For example, in a (k, n)-threshold scheme, information about a secret is distributed in such a way that k-out of n people  $(k \le n)$  have enough information to determine the secret, but any set of k-1 people do not. In any secret sharing scheme, there are designated sets of people whose cumulative information suffices to determine the secret. In some

<sup>&</sup>lt;sup>1</sup> The various processes that deals with the creation, distribution, authentication, and storage of keys.

implementations of secret sharing schemes, each participant receives the secret after it has been generated. In other implementations, the actual secret is never made visible to the participants, although the purpose for which they sought the secret (for example, access to a building or permission to execute a process) is allowed.

### 1.2.4. Electronic Commerce

Over the past few years there has been a growing amount of business conducted over the Internet. This form of business is called electronic commerce or *e*-commerce. *E*-commerce is comprised of online banking, online brokerage accounts, and Internet shopping, to name a few of the many applications. One can book plane tickets, make hotel reservations, rent a car, transfer money from one account to another, buy compact disks (CDs), clothes, books and so on all while sitting in front of a computer. However, simply entering a credit card number on the Internet leaves one open to fraud. One cryptographic solution to this problem is to encrypt the credit card number (or other private information) when it is entered online, another is to secure the entire session. When a computer encrypts this information and sends it out on the Internet, it is incomprehensible to a third party viewer. The web server ("Internet shopping center") receives the encrypted information, decrypts it, and proceeds with the sale without fear that the credit card number (or other personal information) slipped into wrong hands. As more and more business is conducted over the Internet, the need for protection against fraud, theft, and corruption of vital information increases.

### 1.2.5. Certification

Another application of cryptography is certification. Certification is a scheme by which trusted agents such as certifying authorities vouch for unknown agents, such as users. The trusted agents issue vouchers called certificates which each have some inherent meaning. Certification technology was developed to make identification and authentication possible on a large scale.

### 1.2.6. Key Recovery

Key recovery is a technology that allows a key to be revealed under certain circumstances without the owner of the key revealing it. This is useful for two main reasons: first of all, if a user loses or accidentally deletes his or her key, key recovery could prevent a disaster. Secondly, if a law enforcement agency wishes to eavesdrop on a suspected criminal without the suspect's knowledge (akin to a wiretapping) the agency must be able to recover the key. Key recovery techniques are in use in some instances. However, the use of key recovery as a law enforcement technique is somewhat controversial.

### 1.2.7. Remote Access

Secure remote access is another important application of cryptography. The basic system of passwords certainly gives a level of security for secure access, but it may not be enough in some cases. For instance, passwords can be eavesdropped, forgotten, stolen, or guessed. Many products supply cryptographic methods for remote access with a higher degree of security.

## 1.2.8. Other Applications

Cryptography is not confined to the world of computers. Cryptography is also used in cellular (mobile) phones as a means of authentication, that is, it can be used to verify that a particular phone has the right to bill to a particular phone number. This prevents people from stealing ("cloning") cellular phone numbers and access codes. Another application is to protect phone calls from eavesdropping using voice encryption.

### 1.3. Importance of Cryptography

Cryptography allows people to transfer to an account the confidence found in the physical world to the electronic world, thus allowing people to do business electronically without worries of deceit and

deception. Every day hundreds of thousands of people interact electronically, whether it is through *e*-mail, *e*-commerce, ATM machines, or cellular phones. The constant increase of information transmitted electronically has lead to an increased reliance on cryptography.

### 1.3.1. Cryptography on the Internet

The Internet, comprised of millions of interconnected computers, allows nearly instantaneous communication and transfer of information, around the world. People use *e*-mail to correspond with one another. The World Wide Web is used for online business, data distribution, marketing, research, learning, and a myriad of other activities.

Cryptography makes secure web sites and electronic safe transmissions possible. For a web site to be secure all of the data transmitted between the computers where the data is kept and where it is received must be encrypted. This allows people to do online banking, online trading, and make online purchases with their credit cards, without worrying that any of their account information is being compromised. Cryptography is very important to the continued growth of the Internet and electronic commerce.

*E*-commerce is increasing at a very rapid rate. By the turn of the century, commercial transactions on the Internet are expected to total hundreds of billions of dollars a year. This level of activity could not be supported without cryptographic security. It has been said that one is safer using a credit card over the Internet than within a store or restaurant. It requires much more work to capture credit card numbers over computer networks than it does to simply walk by a table in a restaurant and take a credit card receipt. These levels of security, though not yet widely used, give the means to strengthen the foundation with which *e*-commerce can grow.

People use *e*-mail to conduct personal and business matters on a daily basis. *E*-mail has no physical form and may exist electronically in more than one place at a time. This poses a potential problem as it increases the opportunity for an eavesdropper to catch the transmission. Encryption protects *e*-mail by rendering it very difficult to read by any unintended party. Digital signatures can also be used to authenticate the origin and the content of an *e*-mail message.

### 1.3.2. Authentication

In some cases cryptography allows you to have more confidence in your electronic transactions than you do in real life transactions. For example, signing documents in real life still leaves one vulnerable to the following scenario. After signing your will, agreeing to what is put forth in the document, someone can change that document and your signature is still attached. In the electronic world this type of falsification is much more difficult because digital signatures are built using the contents of the document being signed.

### 1.3.3. Access Control

Cryptography is also used to regulate access to satellite and cable TV. Cable TV is set up so people can watch only the channels they pay for. Since there is a direct line from the cable company to each individual subscriber's home, the Cable Company will only send those channels that are paid for. Many companies offer pay-per-view channels to their subscribers. Pay-per-view cable allows cable subscribers to "rent" a movie directly through the cable box. What the cable box does is decode the incoming movie, but not until the movie has been "rented." If a person wants to watch a pay-per-view movie, he/she calls the cable company and requests it. In return, the Cable Company sends out a signal to the subscriber's cable box, which unscrambles (decrypts) the requested movie.

Satellite TV works slightly differently since the satellite TV companies do not have a direct connection to each individual subscriber's home. This means that anyone with a satellite dish can pick up the signals. To alleviate the problem of people getting free TV, they use cryptography. The trick is to allow only those who have paid for their service to unscramble the transmission; this is done with receivers ("unscramblers"). Each subscriber is given a receiver; the satellite transmits

signals that can only be unscrambled by such a receiver. Pay-per-view works in essentially the same way as it does for regular cable TV.

As seen, cryptography is widely used. Not only is it used over the Internet, but also it is used in phones, televisions, and a variety of other common household items. Without cryptography, hackers could get into our *e*-mail, listen in on our phone conversations, tap into our cable companies and acquire free cable service, or break into our bank accounts.

# 2. Understanding Public-key Cryptosystems

This section gives more details about public-key cryptosystems, providing more information about the concepts involved in cryptography. Two systems related to public-key cryptosystems are introduced; secret-key cryptosystems and hash functions. These systems are introduced because they can be found in many applications using public-key cryptosystems (section 3.4). Also, a comparison between secret-key cryptosystems and public-key cryptosystem is written.

This chapter was extracted from [1].

### 2.1. Public-key Cryptosystems

In traditional cryptography, the sender and receiver of a message know and use the same secret key. The sender uses the secret key to encrypt the message, and the receiver uses the same secret key to decrypt the message. This method is known as secret key or symmetric cryptography. The main challenge is getting the sender and receiver to agree on the secret key without anyone else finding out. If they are in separate physical locations, they must trust a courier, a phone system, or some other transmission medium to prevent the disclosure of the secret key. Anyone who overhears or intercepts the key in transit can later read, modify, and forge all messages encrypted or authenticated using that key. The generation, transmission and storage of keys is called *key management*. All cryptosystems must deal with key management issues. Because all keys in a secret-key cryptosystem must remain secret, secret-key cryptography often has difficulty providing secure key management, especially in open systems with a large number of users.

In order to solve the key management problem, Whitfield Diffie and Martin Hellman introduced the concept of public-key cryptosystems in 1976 [3]. Public-key cryptosystems have two primary uses, encryption and digital signatures. In their system, each person gets a pair of keys, one called the public key and the other called the private key. The public key is published, while the private key is kept secret. The need for the sender and receiver to share secret information is eliminated: all communications involve only public keys, and no private key is ever transmitted or shared. In this system, it is no longer necessary to trust the security of some means of communications. The only requirement is that public keys be associated with their users in a trusted (authenticated) manner (for instance, in a trusted directory). Anyone can send a confidential message by just using public information, but the message can only be decrypted with a private key, which is in the sole possession of the intended recipient. Furthermore, public-key cryptography can be used not only for privacy (encryption), but also for authentication (digital signatures) and other various techniques.

In a public-key cryptosystem, the private key is always linked mathematically to the public key. Therefore, it is always possible to attack a public-key system by deriving the private key from the public key. Typically, the defense against this is to make the problem of deriving the private key from the public key as difficult as possible. For instance, some public-key cryptosystems are designed such that deriving the private key from the public key requires the attacker to factor a large number, in such a way that it is computationally infeasible to perform the derivation. This is the idea behind the RSA public-key cryptosystem.

### 2.1.1. Encryption

When Alice wishes to send a secret message to Bob, she looks up Bob's public key in a directory, uses it to encrypt the message and sends it off. Bob then uses his private key to decrypt the message and read it. No one listening in can decrypt the message. Anyone can send an encrypted message to Bob, but only Bob can read it (because only Bob knows Bob's private key).

### 2.1.2. Digital Signatures

To sign a message, Alice does a computation involving both her private key and the message itself. The output is called a digital signature and is attached to the message. To verify the signature, Bob

does a computation involving the message, the purported signature, and Alice's public key. If the result is correct according to a simple, prescribed mathematical relation, the signature is verified to be genuine; otherwise, the signature is fraudulent, or the message may have been altered.

# 2.2. Systems related to Public-key Cryptosystems

## 2.2.1. Secret-key Cryptosystem

Secret-key cryptosystems is sometimes referred to as symmetric cryptography. It is the more traditional form of cryptography, in which a single key can be used to encrypt and decrypt a message. Secret-key cryptography not only deals with encryption, but it also deals with authentication. One such technique is called *message authentication codes*.

The main problem with secret-key cryptosystems is getting the sender and receiver to agree on the secret key without anyone else finding out. This requires a method by which the two parties can communicate without fear of eavesdropping.

Public-key cryptography has come to overcome this deficiency of secret-key cryptosystems by establishing secure means for sending keys in a trusted way. Public-key cryptography is not meant to replace secret-key cryptography, but rather to supplement it, to make it more secure (see key agreement protocol, 3.4.2). Secret-key cryptography remains extremely important and is the subject of much ongoing study and research.

#### 2.2.2. Hash functions

A *hash function* H is a transformation that takes an input m and returns a fixed-size string, which is called the hash value h (that is, h = H(m)). Hash functions with just this property have a variety of general computational uses, but when employed in cryptography, the hash functions are usually chosen to have some additional properties.

The basic requirements for a cryptographic hash function are as follows.

- The input can be of any length.

- The output has a fixed length.

- H(x) is relatively easy to compute for any given x.

- H(x) is one-way.

- H(x) is collision-free.

A hash function H is said to be *one-way* if it is hard to invert, where "hard to invert" means that given a hash value h, it is computationally infeasible to find some input x such that H(x) = h. If, given a message x, it is computationally infeasible to find a message y not equal to x such that H(x) = H(y), then H is said to be a *weakly collision-free* hash function. A *strongly collision-free* hash function H is one for which it is computationally infeasible to find any two messages x and y such that H(x) = H(y).

The hash value represents concisely the longer message or document from which it was computed; this value is called the *message digest*. One can think of a message digest as a "digital fingerprint" of the larger document. Examples of well known hash functions are MD2 and MD5 and SHA.

Perhaps the main role of a cryptographic hash function is in the provision of message integrity checks and digital signatures. Since hash functions are generally faster than encryption or digital signature algorithms, it is typical to compute the digital signature or integrity check to some document by applying cryptographic processing to the document's hash value, which is small compared to the document itself. Additionally, a digest can be made public without revealing the contents of the document from which it is derived.

Note that sometimes information is not supposed to be accessed by anyone, and in these cases, the information may be stored in such a way that reversing the process is virtually impossible. For

instance, on a typical multi-user system, no one is supposed to know the list of passwords of everyone on the system. Often hash values of passwords are stored instead of the passwords themselves. This allows the users of the system to be confident their private information is actually kept private while still enabling an entered password to be verified (by computing its hash and comparing that result against a stored hash value). This scheme is applied in the widely used operating system UNIX [2]

# 2.3. Advantages and disadvantages of public-key cryptosystems

The primary advantage of public-key cryptography is increased security and convenience: private keys never need to be transmitted or revealed to anyone. In a secret-key system, by contrast, the secret keys must be transmitted (either manually or through a communication channel) since the same key is used for encryption and decryption. A serious concern is that there may be a chance that an enemy can discover the secret key during transmission.

Another major advantage of public-key systems is that they can provide digital signatures that cannot be repudiated. Authentication via secret-key systems requires the sharing of some secret and sometimes requires trust of a third party as well. As a result, a sender can repudiate a previously authenticated message by claiming the shared secret was somehow compromised by one of the parties sharing the secret. For example, there are secret-key authentication systems involving a central database that keeps copies of the secret keys of all users; an attack on the database would allow widespread forgery. Public-key authentication, on the other hand, prevents this type of repudiation; each user has sole responsibility for protecting his or her private key. This property of public-key authentication is often called non-repudiation.

A disadvantage of using public-key cryptography for encryption is speed. There are many secret-key encryption methods that are significantly faster than any currently available public-key encryption method. Nevertheless, public-key cryptography can be used with secret-key cryptography to get the best of both worlds. For encryption, the best solution is to combine public- and secret-key systems in order to get both the security advantages of public-key systems and the speed advantages of secret-key systems. Such a protocol is called a *digital envelope* (section 3.4.3).

Public-key cryptography may be vulnerable to impersonation, even if users' private keys are not available. A successful attack on a certification authority will allow an adversary to impersonate whomever he or she chooses by using a public-key certificate from the compromised authority to bind a key of the adversary's choice to the name of another user.

In some situations, public-key cryptography is not necessary and secret-key cryptography alone is sufficient. These include environments where secure secret key distribution can take place, for example, by users meeting in private. It also includes environments where a single authority knows and manages all the keys, for example, a closed banking system. Since the authority knows everyone's keys already, there is not much advantage for some to be "public" and others to be "private." Note, however, that such a system may become impractical if the number of users becomes large; there are not necessarily any such limitations in a public-key system.

Public-key cryptography is usually not necessary in a single-user environment. For example, if you want to keep your personal files encrypted, you can do so with any secret key encryption algorithm using, say, your personal password as the secret key. In general, public-key cryptography is best suited for an open multi-user environment.

# 2.4. Some applications liked to Public-key Cryptosystems

#### 2.4.1. Authentication and Digital Signature

Authentication is any process through which one proves and verifies certain information. Sometimes one may want to verify the origin of a document, the identity of the sender, the time and date a document was sent and/or signed, the identity of a computer or user, and so on. A *digital signature* is a cryptographic means through which many of these may be verified. The digital signature of a

document is a piece of information based on both the document and the signer's private key. It is typically created through the use of a hash function and a private signing function (encrypting with the signer's private key), but there are other methods.

Every day, people sign their names to letters, credit card receipts, and other documents, demonstrating they are in agreement with the contents. That is, they authenticate that they are in fact the sender or originator of the item. This allows others to verify that a particular message did indeed originate from the signer. However, this is not foolproof, since people can 'lift' signatures off one document and place them on another, thereby creating fraudulent documents. Written signatures are also vulnerable to forgery because it is possible to reproduce a signature on other documents as well as to alter documents after they have been signed.

Digital signatures and hand-written signatures both rely on the fact that it is very hard to find two people with the same signature. People use public-key cryptography to compute digital signatures by associating something unique with each person. When public-key cryptography is used to encrypt a message, the sender encrypts the message with the public key of the intended recipient. When public-key cryptography is used to calculate a digital signature, the sender encrypts the "digital fingerprint" of the document with his or her own private key. Anyone with access to the public key of the signer may verify the signature.

Suppose Alice wants to send a signed document or message to Bob. The first step is generally to apply a hash function to the message, creating what is called a message digest. The message digest is usually considerably shorter than the original message. In fact, the job of the hash function is to take a message of arbitrary length and shrink it down to a fixed length. To create a digital signature, one usually signs (encrypts) the message digest as opposed to the message itself. This saves a considerable amount of time, though it does create a slight insecurity (addressed below). Alice sends Bob the encrypted message digest and the message, which she may or may not encrypt. In order for Bob to authenticate the signature he must apply the same hash function as Alice to the message she sent him, decrypt the encrypted message digest using Alice's public key and compare the two. If the two are the same he has successfully authenticated the signature. If the two do not match there are a few possible explanations. Either someone is trying to impersonate Alice, the message itself has been altered since Alice signed it or an error occurred during transmission.

There is a potential problem with this type of digital signature. Alice not only signed the message she intended to but also signed all other messages that happen to hash to the same message digest. When two messages hash to the same message digest it is called a *collision*; the collision-free properties of hash functions are a necessary security requirement for most digital signature schemes. A hash function is secure if it is very time consuming to figure out the original message given its digest. However, there is an attack called the *birthday attack* that relies on the fact that it is easier to find two messages that hash to the same value than to find a message that hashes to a particular value. Its name arises from the fact that for a group of 23 or more people the probability that two or more people share the same birthday is better than 50%.

In addition, someone could pretend to be Alice and sign documents with a key pair he claims is Alice's. To avoid scenarios such as this, there are digital documents called certificates that associate a person with a specific public key.

Digital timestamps may be used in connection with digital signatures to bind a document to a particular time of origin. It is not sufficient to just note the date in the message, since dates on computers can be easily manipulated. It is better that timestamping is done by someone everyone trusts, such as a certifying authority. There have been proposals suggesting the inclusion of some unpredictable information in the message such as the exact closing share price of a number of stocks; this information should prove that the message was created *after* a certain point in time.

#### 2.4.2. Key agreement protocol

A *key agreement protocol*, also called a *key exchange protocol*, is a series of steps used when two or more parties need to agree upon a key to use for a secret-key cryptosystem. These protocols allow people to share keys freely and securely over any insecure medium, without the need for a previously-established shared secret.

Suppose Alice and Bob want to use a secret-key cryptosystem to communicate securely. They first must decide on a shared key. Instead of Bob calling Alice on the phone and discussing what the key will do, which would leave them vulnerable to an eavesdropper; they decide to use a key agreement protocol. By using a key agreement protocol, Alice and Bob may securely exchange a key in an insecure environment. One example of such a protocol is called the Diffie-Hellman key agreement. In many cases, public-key cryptography is used in a key agreement protocol. Another example is the use of digital envelopes for key agreement.

### 2.4.3. Digital Envelope

When we are using secret-key cryptosystems, users must first agree on a session key, that is, a secret key to be used for the duration of one message or communication session. In completing this task there is a risk the key will be intercepted during transmission. This is part of the key management problem. Public-key cryptosystems offers an attractive solution to this problem within a framework called a digital envelope.

The digital envelope consists of a message encrypted using secret-key cryptography and an encrypted secret key. While digital envelopes usually use public-key cryptography to encrypt the secret key, this is not necessary. If Alice and Bob have an established secret key, they could use this to encrypt the secret key in the digital envelope.

Suppose Alice wants to send a message to Bob using secret-key cryptography for message encryption and public-key cryptography to transfer the message encryption key. Alice chooses a secret key and encrypts the message with it, then encrypts the secret key using Bob's public key. She sends Bob both the encrypted secret key and the encrypted message. When Bob wants to read the message he decrypts the secret key, using his private key, and then decrypts the message, using the secret key. In a multi-addressed communications environment such as e-mail, this can be extended directly and usefully. If Alice's message is intended for both Bob and Carol, the message encryption key can be represented concisely in encrypted forms for Bob and for Carol, along with a single copy of the message's content encrypted under that message encryption key.

Alice and Bob may use this key to encrypt just one message or they may use it for an extended communication. One of the nice features about this technique is they may switch secret keys as frequently as they would like. Switching keys often is beneficial because it is more difficult for an adversary to find a key that is only used for a short period of time.

Not only do digital envelopes help solve the key management problem; they increase performance (relative to using a public-key system for direct encryption of message data) without sacrificing security. The increase in performance is obtained by using a secret-key cryptosystem to encrypt the large and variably sized amount of message data, reserving public-key cryptography for encryption of short-length keys. In general, secret-key cryptosystems are much faster than public-key cryptosystems.

The digital envelope technique is a method of key exchange, but not all key exchange protocols use digital envelopes.

## 2.4.4. Identification

*Identification* is a process through which one ascertains the identity of another person or entity. In our daily lives, we identify our family members, friends, and coworkers by their physical properties, such as voice, face or other characteristics. These characteristics, called biometrics, can only be used

on computer networks with special hardware. Entities on a network may also identify one another using cryptographic methods.

An identification scheme allows Alice to identify herself to Bob in such a way that someone listening in cannot pose as Alice later. One example of an identification scheme is a zero-knowledge proof. Zero knowledge proofs allow a person (or a server, web site, etc.) to demonstrate they have certain piece of information without giving it away to the person (or entity) they are convincing. Suppose Alice knows how to solve the Rubik's cube and wants to convince Bob she can without giving away the solution. They could proceed as follows. Alice gives Bob a Rubik's cube which he thoroughly messes up and then gives back to Alice. Alice turns away from Bob, solves the puzzle and hands it back to Bob. This works because Bob saw that Alice solved the puzzle, but he did not see the solution.

This idea may be adapted to an identification scheme if each person involved is given a "puzzle" and its answer. The security of the system relies on the difficulty of solving the puzzles. In the case above, if Alice were the only person who could solve a Rubik's cube, then that could be her puzzle. In this scenario Bob is the verifier and is identifying Alice, the prover.

The idea is to associate with each person something unique; something only that person can reproduce. This in effect takes the place of a face or a voice, which are unique factors allowing people to identify one another in the physical world.

Authentication and identification are different. Identification requires that the verifier check the information presented against all the entities it knows about, while authentication requires that the information be checked for a single, previously identified, entity. In addition, while identification must, by definition, uniquely identify a given entity, authentication does not necessarily require uniqueness. For instance, someone logging into a shared account is not uniquely identified, but by knowing the shared password, they are authenticated as one of the users of the account. Furthermore, identification does not necessarily authenticate the user for a particular purpose.

# 3. The RSA Cryptosystem

The present section approaches the RSA cryptosystem, explaining its algorithm in a very practical way. It also covers its main characteristics like its speed compared to other secret-key cryptosystems, its strength against attacks, and its security closely related to the key sizes. At the end of this section, we have solved a very simple example using the RSA algorithm. The contents of sections 3.1 to 3.4 were estracted from [1, 4-5, 8-10].

# 3.1. The RSA algorithm

The RSA cryptosystem is a public-key cryptosystem that offers both encryption and digital signatures (authentication). Ronald Rivest, Adi Shamir, and Leonard Adleman developed the RSA system in 1978; RSA stands for the first letter in each of its inventors' last names.

The RSA algorithm works as described below:

First, compute *n*, where

$$n = pq \tag{3.1.1}$$

and p and q should be two large prime numbers chosen randomly. The number n is called *modulus*.

Then, pick up an integer d to be a large, random integer which is *relatively prime* to (p-1)(q-1). That is, check that d satisfies:

$$\gcd(d, (p-1)\cdot (q-1)) = 1. \tag{3.1.2}$$

Here, gcd means "greatest common divisor". Finally, compute another number e from p, q, and d to be the *multiplicative inverse* of d modulo (p-1).(q-1). Thus we have

$$ed \equiv 1(\operatorname{mod}(p-1) \cdot (q-1)). \tag{3.1.3}$$

The *encryption key* is thus the pair of positive integers (e, n). Similarly, the *decryption key* is the pair of positive integers (d, n). Each user makes his encryption key public, and keeps the corresponding decryption key private (these integers should properly be subscripted as in  $n_A$ ,  $e_A$ , and  $e_A$ , since each user has his own set).

Now, to encrypt a message M using a public encryption key (e, n), proceed as follows:

Represent the message as an integer between 0 and n-1. If necessary, break a long message into a series of blocks, and represent each block as such an integer. The purpose here is not to encrypt the message but only to get it into the numeric form necessary for encryption.

Then, encrypt the message by raising it to the  $e^{th}$  power modulo n. That is, the result (the ciphertext C) is the remainder when  $M^e$  is divided by n.

To decrypt the ciphertext, raise it to another power d, again modulo n. The encryption and decryption algorithms E and D are thus:

$$C \equiv E(M) \equiv M^e \pmod{n},\tag{3.1.4}$$

for a message M.

$$M \equiv D(C) \equiv C^d \pmod{n},\tag{3.1.5}$$

for a ciphertext C.

Note that encryption does not increase the size of a message. Both the message M and the ciphertext C are integers in the range 0 to n-1.

## 3.1.1. Encryption

Suppose Alice wants to send a message M to Bob. Alice creates the ciphertext C by exponentiating C =  $M^e \mod n$ , where e and n are Bob's public key. She sends C to Bob. To decrypt, Bob also

exponentiates:  $M = C^d \mod n$ ; the relationship between e and d ensures that Bob correctly recovers M. Since only Bob knows d, only Bob can decrypt this message.

### 3.1.2. Digital Signature

Suppose Alice wants to send a message M to Bob in such a way that Bob is assured the message is both authentic, has not been tampered with, and from Alice. Alice creates a digital signature S by exponentiating:  $S = M^d \mod n$ , where d and n are Alice's private key. She sends M and S to Bob. To verify the signature, Bob exponentiates and checks that the message M is recovered:  $M = S^e \mod n$ , where e and n are Alice's public key.

Thus encryption and authentication take place without any sharing of private keys: each person uses only another's public key or their own private key. Anyone can send an encrypted message or verify a signed message, but only someone in possession of the correct private key can decrypt or sign a message.

For interested readers, a formal proof and explanation of the RSA algorithm can be found in [4].

# 3.2. RSA Speed

An "RSA operation", whether encrypting, decrypting, signing, or verifying is essentially a modular exponentiation. This computation is performed by a series of modular multiplications.