## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

LUIZ GUSTAVO CASAGRANDE

# Soft Error Analysis With and Without Operating System

Work presented in partial fulfillment of the requirements for the degree of Master in Microelectronics

Advisor: Prof. Dr. Fernanda G. de Lima Kastensmidt

Porto Alegre June 2016 Casagrande, Luiz Gustavo

Soft Error Analysis With and Without Operating System / Luiz Gustavo Casagrande. – 2016.

103 f.:il.

Orientador: Fernanda Gusmão de Lima Kastensmidt.

Dissertação (Mestrado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2016.

1. Efeitos da Radiação em Processadores. 2. Metodologias e ferramentas de injeção de falhas. 3. Emulação de processadores. I. Kastensmidt, Fernanda Gusmão de Lima. II. Soft Error Analysis With and Without Operating System.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb Coordenador do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGMENTS

The loneliness of the decision to the responsibility of the gesture. Not even the intention escapes the judgment. What would be nobler then? Deliver your best days and steady arms to the social claim or bear in mind the very free and tragic image? To decide something, whether or not conducted by Opinion, is performing a morbid act. It is an impulse, a spark who disguises herself as motivation and ideal. This is all anger and hopelessness, the insoluble existential doubt urging cease.

In this process, the head is an island, but I am thankful to have open the ports to many people that, even sometimes unknowingly, contributed with words, experiences, actions or provocations. Among them, I mention Caroline Araujo for her constancy, availability and beautiful smile. My mother, Maria, for unquestioned support and my Father, Ivo, for the silent and unconditional love, know that I am very proud of what you represent and that without you nothing would be possible. Thanks to my supervisor, Fernanda Kastensmidt, for the patience. To my current and past colleagues for the technical discussions and philosophical clashes. To my friends (including the previously mentioned), for the comic relief and delight of oblivion. My professors Delfim Luiz Torok, for the confidence and youthful spirit, Ewerton Cappelatti, for the fellowship, Paulo Piber, for the placidity and Ronaldo do Espírito Santo, for the character.

#### ABSTRACT

The complexity of integrated system on-chips as well as commercial processor's architecture has increased dramatically in recent years. Thus, the effort for assessing the susceptibility to faults due to the incidence of spatial charged particles in these devices has growth at the same rate. This work presents a comparative analysis of soft errors susceptibility in the commercial large-scale embedded microprocessor ARM Cortex-A9 single core, widely used in critical applications, performing a set of 11 applications developed for a bare metal environment and the Linux operating system. The soft errors analysis is performed by fault injection in OVPSim simulation platform along with the OVPSim-FIM fault injector, able to randomly select the time and place to inject the fault. The fault injection campaign reproduces thousands of bit-flips in the microprocessor register file during the execution of the benchmarks set, with a diverse code behavior ranging from control flow dependency to data intensive applications. The analysis method is based on comparing applications executions where faults were injected with a fault-free implementation. The results show the error rate classified by their effect as: masked (UNACE), crash or loss of control flow (HANG) and silent data corruption (SDC); and by register locations. By separating latent errors by its location in the results and exceptions detected by the operating system, one can provide new better observability for a large-scale processor. The proposed method and the results can guide software developers in choosing different code architectures in order to improve the fault tolerance of the embedded system as a whole.

**Keywords**: Open Virtual Platform (OVP). Soft error. ARM Cortex-A9. Bare metal. Linux operating system. Embedded processor.

#### **RESUMO**

A complexidade dos sistemas integrados em chips bem como a arquitetura de processadores comerciais vem crescendo dramaticamente nos últimos anos. Com isto, a dificuldade de avaliarmos a suscetibilidade às falhas em decorrência da incidência de partículas espaciais carregadas nestes dispositivos cresce com a mesma taxa. Este trabalho apresenta uma análise comparativa da susceptibilidade à erros de software em um microprocessador embarcado ARM Cortex-A9 single core de larga escala comercial, amplamente utilizado em aplicações críticas, executando um conjunto de 11 aplicações desenvolvidas para um ambiente bare metal e para o sistema operacional Linux. A análise de soft errors é executada por injeção de falhas na plataforma de simulação OVPSim juntamente com o injetor OVPSim-FIM, capaz de sortear o momento e local de injeção de uma falha. A campanha de injeção de falhas reproduz milhares de bit-flips no banco de registradores do microprocessador durante a execução do conjunto de benchmarks que possuem um comportamento de código diverso, desde dependência de fluxo de controle até aplicações intensivas em dados. O método de análise consiste em comparar execuções da aplicação onde falhas foram injetadas com uma execução livre de falhas. Os resultados apresentam a taxa de falhas que são classificadas em: mascaradas (UNACE), travamento ou perda de controle de fluxo (HANG) e erro nos resultados (SDC). Adicionalmente, os erros são classificados por registradores, separando erros latentes por sua localização nos resultados e por exceções detectadas pelo sistema operacional, provendo novas possibilidades de análise para um processador desta escala. O método proposto e os resultados obtidos podem ajudar a orientar desenvolvedores de software na escolha de diferentes arquiteturas de código, a fim de aprimorar a tolerância à falhas do sistema embarcado como um todo.

**Palavras-chave**: Plataforma virtual (OVP). *Soft error*; ARM Cortex-A9. *Bare metal*. Sistema operacional Linux. Processador embarcado.

## LIST OF FIGURES

| Figure 2.1 – Embedded system with CPU, memory and peripherals                              | 15  |

|--------------------------------------------------------------------------------------------|-----|

| Figure 2.2 – Johnson's Fault Tolerant System Flow                                          | 18  |

| Figure 2.3 - Induced Charge by Radiation in the Gate Oxide of a N channel MOSFET: (a) norm | nal |

| operation, (b) after irradiation                                                           | 19  |

| Figure 2.4 – Particle Crossing the Substrate of a Transistor                               | 20  |

| Figure 2.5 – OVP Interfaces                                                                |     |

| Figure 3.1 – ARM Cortex-A9 Block Diagram                                                   | 35  |

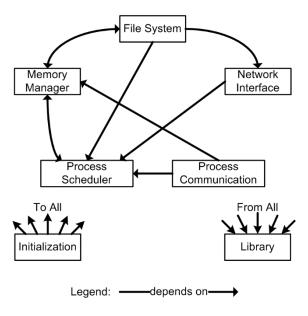

| Figure 3.2 – Linux System Major Subsystems                                                 |     |

| Figure 3.3 – Linux Kernel Architecture                                                     |     |

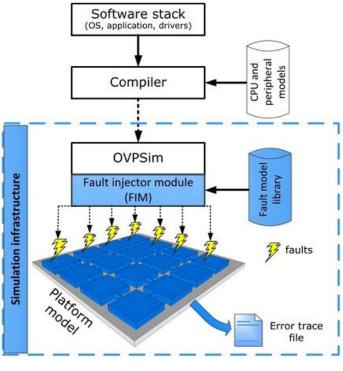

| Figure 3.4 – Proposed fault injection framework organization                               | 43  |

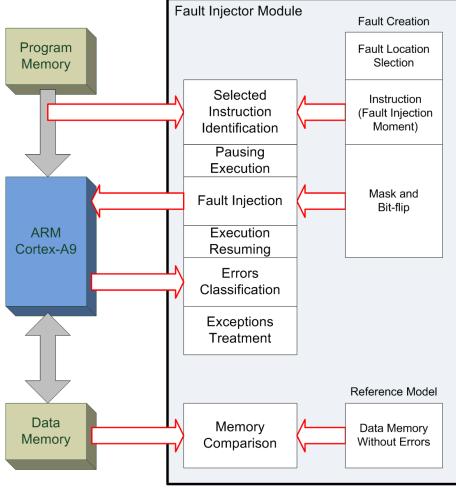

| Figure 3.5 – Fault injector module architecture                                            | 46  |

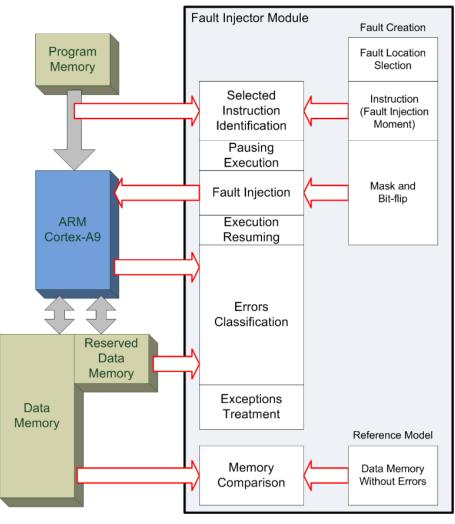

| Figure 3.6 - Fault injector module architecture for embedded system with Linux             | 47  |

| Figure 3.7 – Fault Injector Operation Flow                                                 | 48  |

| Figure 4.1 – Test Environments Structure                                                   | 52  |

| Figure 4.2 – Emulated CPU Information                                                      | 53  |

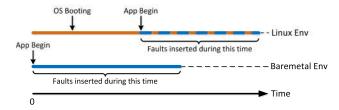

| Figure 4.3 – Bare Metal Fault Distribution over Time                                       | 57  |

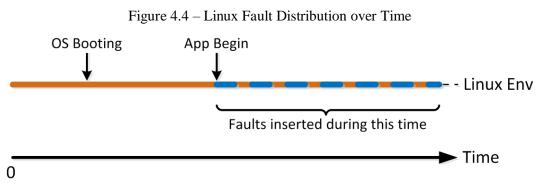

| Figure 4.4 – Linux Fault Distribution over Time                                            | 58  |

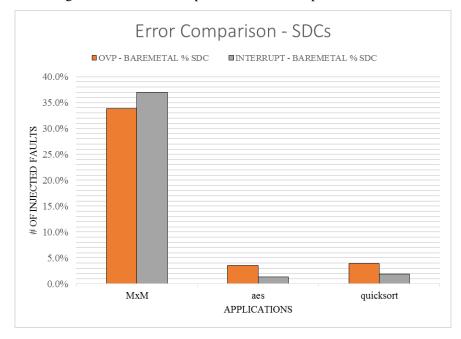

| Figure 5.1 - SDCs Comparison with Interruption-based Platform                              | 63  |

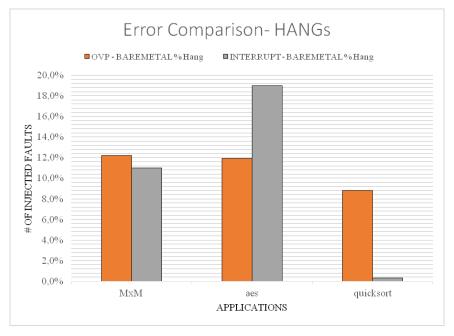

| Figure 5.2 – HANGs Comparison with Interruption-based Platform                             | 64  |

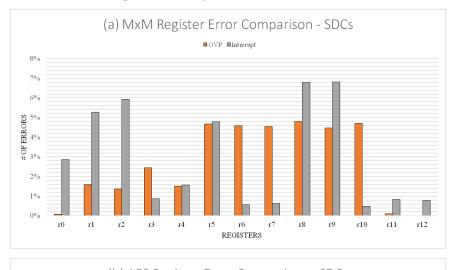

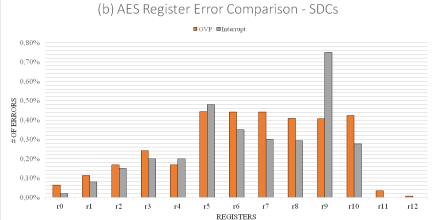

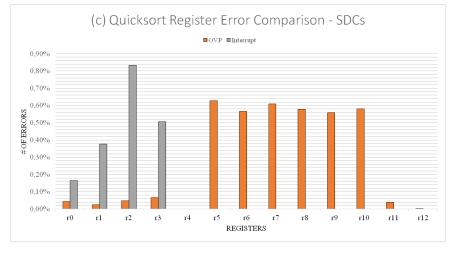

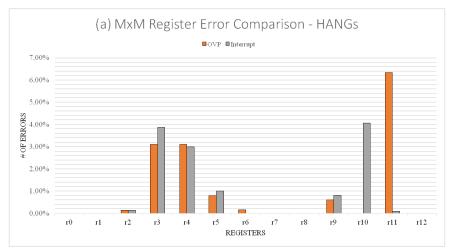

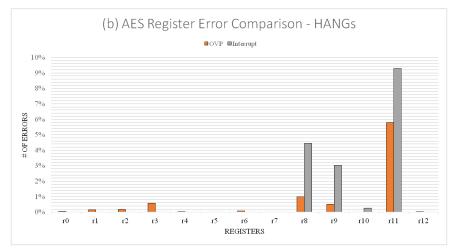

| Figure 5.3 - SDCs Comparison at Register Level: (a) MxM, (b) AES and (c) Quicksort         | 65  |

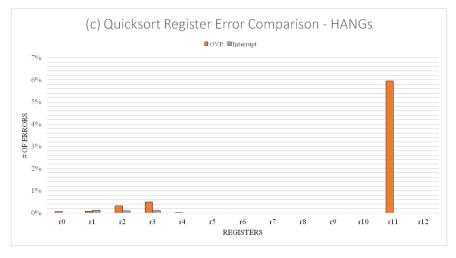

| Figure 5.4 - HANGs Comparison at Register Level: (a) MxM, (b) AES and (c) Quicksort        | 66  |

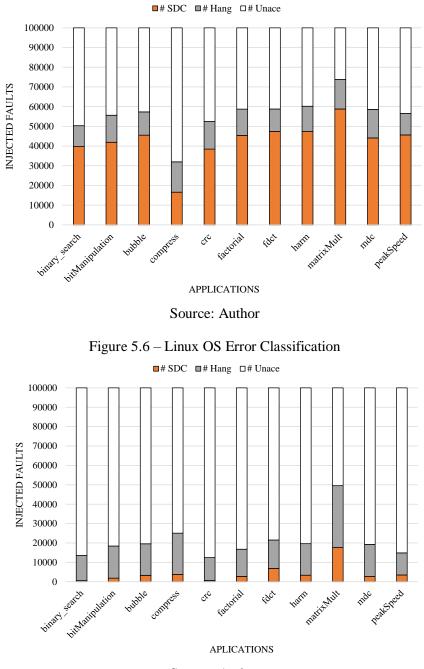

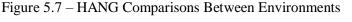

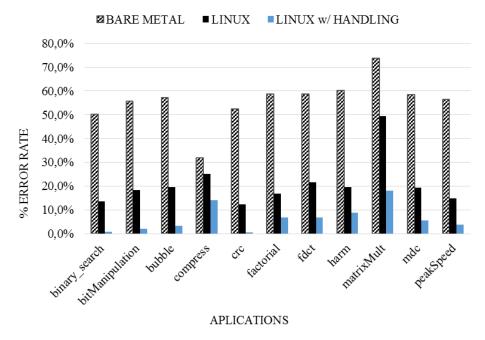

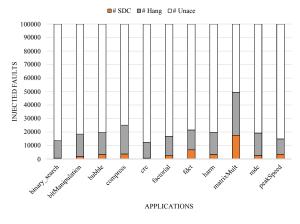

| Figure 5.5 – Bare Metal Error Classification                                               |     |

| Figure 5.6 – Linux OS Error Classification                                                 | 69  |

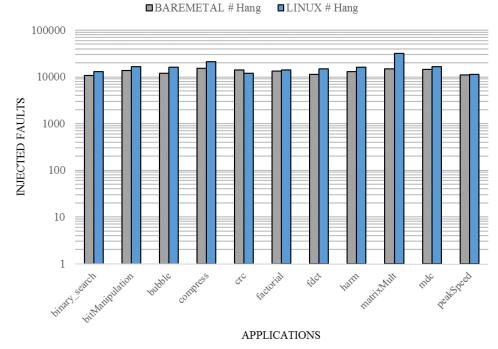

| Figure 5.7 – HANG Comparisons Between Environments                                         | 70  |

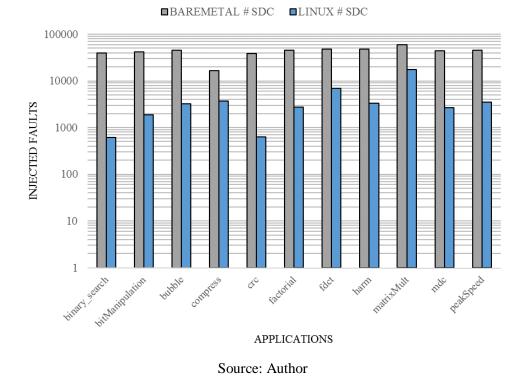

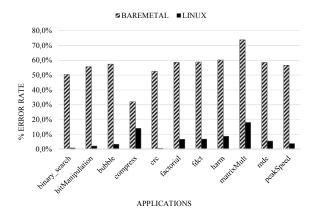

| Figure 5.8 - SDC Comparisons Between Environments                                          | 71  |

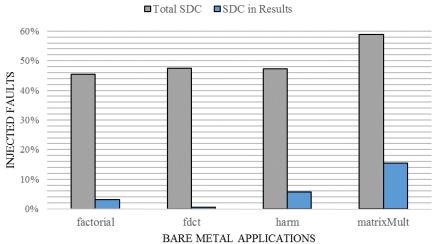

| Figure 5.9 - Bare Metal Total SDC vs SDC Only in Results                                   | 76  |

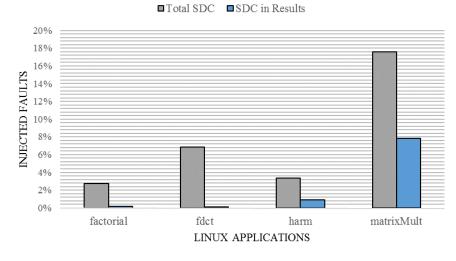

| Figure 5.10 – Linux Total SDC vs. SDC Only in Results                                      | 77  |

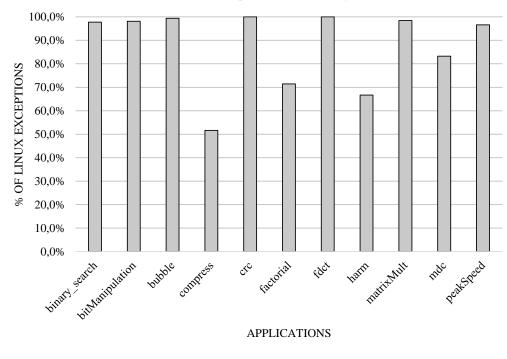

| Figure 5.11 - Linux Exception Signal Rate Over Total Detected HANGs                        | 78  |

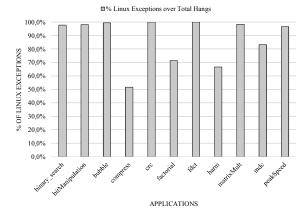

| Figure 5.12 - Linux Exception Signal Rate Over Total Detected HANGs                        | 79  |

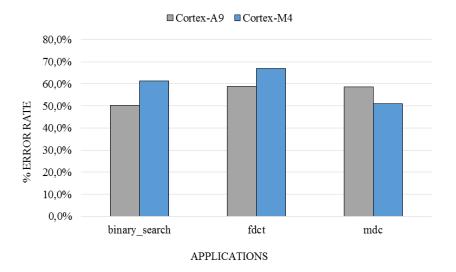

| Figure 5.13 - Error Rate of Three Applications Running on ARM Cortex-A9 and Cortex-M4      | 80  |

|                                                                                            |     |

### LIST OF TABLES

| Table 3.1 – ARM Cortex-A9 Register File                                                 |    |

|-----------------------------------------------------------------------------------------|----|

| Table 3.2 – Failure Group Classification                                                | 51 |

| Table 4.1 – Number of Instructions Executed in Bare metal and in Linux for the set of A |    |

| Table 4.2 – Result Example with Faults Details                                          |    |

| Table 5.1 – Manifested Failures by Register                                             | 73 |

| Table Appendix A.1 – Bare Metal Benchmark Results with Full Classification (a)          | 91 |

| Table Appendix A.2 – Bare Metal Benchmark Results with Full Classification (b)          | 92 |

| Table Appendix A.3 – Linux OS Benchmark Results with Full Classification (a)            | 93 |

| Table Appendix A.4 - Linux OS Benchmark Results with Full Classification (b)            |    |

## LIST OF ABBREVIATIONS AND ACRONYMS

| ACP   | Accelerator Coherence Port                |

|-------|-------------------------------------------|

| API   | Application Programming Interface         |

| ASIC  | Application Specific Integrated Circuit   |

| AVF   | Architectural Vulnerability Factor        |

| CAN   | Controller Area Network                   |

| CISC  | Complex Instruction Set Computer          |

| COTS  | Commercial of the Shelf                   |

| CPU   | Central Processor Unit                    |

| CRC   | Cyclic Redundancy Check                   |

| DMA   | Direct Memory Access                      |

| DSP   | Digital Signal Processor                  |

| DUT   | Design Under Test                         |

| ESA   | European Space Agency                     |

| FI    | Functional Interrupts                     |

| FIM   | Fault Injector Module                     |

| FIT   | Failure In Time                           |

| FPGA  | Field Programmable Gate Array             |

| FPU   | Floating Point Unit                       |

| GCC   | GNU Compiler Collection                   |

| GP    | General Purpose                           |

| GPP   | General Purpose Processor                 |

| IC    | Integrated Circuit                        |

| ICM   | Innovative CPU Manager                    |

| IDE   | Integrated Development Environment        |

| ΙΟ    | Input/output                              |

| ISA   | Instruction Set Architecture              |

| ISS   | Instruction Set Simulator                 |

| JEDEC | Joint Electron Device Engineering Council |

| JIT   | Just in Time Compiler                     |

| JTAG  | Joint Test Action Group                   |

| MBU   | Multi Bit Upset                           |

| MIPS  | Million Instructions per Second           |

|       |                                           |

| MOS  | Metal-Oxide Semiconductor                   |

|------|---------------------------------------------|

|      |                                             |

| MPE  | Media Processing Engine                     |

| OCD  | On-Chip Debug                               |

| OS   | Operating System                            |

| OVP  | Open Virtual Platform                       |

| PC   | Personal Computer                           |

| PTM  | Production Test Mode                        |

| PVF  | Program Vulnerability Factor                |

| RAM  | Random Access Memory                        |

| RHBP | Radiation Hardening By Design               |

| RISC | Reduced Instruction Set Computer            |

| RTL  | Register Transfer Level                     |

| SBU  | Single Bit Upset                            |

| SDC  | Silent Data Corruption                      |

| SEE  | Single Event Effect                         |

| SEGR | Single Event Gate Rupture                   |

| SEL  | Single Event Latch Up                       |

| SER  | Soft Error Rate                             |

| SET  | Single Transient Effect                     |

| SEU  | Single Event Upset                          |

| SIMD | Single Instruction, Multiple Data           |

| SMP  | Symmetric Multiprocessor                    |

| SP   | Stack Pointer                               |

| SPI  | Serial Peripheral Interface                 |

| SWI  | Software Implemented                        |

| TAP  | Test Access Port                            |

| TID  | Total Ionizing Dose                         |

| TLB  | Translation Lookaside Buffer                |

| TLM  | Transaction Level Modeling                  |

| UART | Universal Asynchronous Receiver/Transmitter |

| VFP  | Vector Floating Point Unit                  |

| VHDL | VHSIC Hardware Description Language         |

| VMI  | Virtual Machine Interface                   |

| WCET | Worst-Case Execution Time                   |

|      |                                             |

## SUMMARY

| 1   | INTRODUCTION                                                                   |    |

|-----|--------------------------------------------------------------------------------|----|

| 2   | FAULT EVALUATION IN EMBEDDED SYSTEMS                                           |    |

|     | 2.1 DEFINING AN EMBEDDED SYSTEM                                                |    |

|     | 2.2 FAULT INJECTION IN EMBEDDED PROCESSORS                                     | 16 |

|     | 2.2.1 Faults, Errors and Failures                                              | 17 |

|     | 2.2.2 Faults in Embedded Systems                                               | 17 |

|     | 2.2.3 Radiation Effects in Embedded Processors                                 | 19 |

|     | 2.2.3.1 Single Event Upset                                                     |    |

|     | 2.2.4 Failure Classification, Metrics and Operating System Impact              |    |

|     | 2.2.5 Fault Tolerance Evaluation Techniques                                    |    |

|     | 2.2.5.1 Physical Fault Injection                                               |    |

|     | 2.2.5.2 Logical Fault Injection.                                               |    |

|     | 2.3 OPEN VIRTUAL PLATFORM (OVP)                                                |    |

|     | 2.3.1 APIs                                                                     |    |

|     | 2.3.2 Hardware Behavioral Models                                               |    |

| 3   | · · · · · · · · · · · · · · · · · · ·                                          | )R |

| ARC | CHITECTURE                                                                     |    |

|     | 3.1 ARM CORTEX-A9 ARCHITECTURE                                                 |    |

|     | 3.1.1 Main Functionalities and Relevant Features                               |    |

|     | 3.2 OVP MODEL OF THE ARM CORTEX-A9 ARCHITECTURE                                |    |

|     | 3.2.1 Modeled Functionalities                                                  |    |

|     | 3.2.1.1 Pipeline e Cache L1                                                    |    |

|     | 3.2.1.2 Performance and Timing                                                 |    |

|     | 3.2.1.3 Special Functions                                                      |    |

|     | <ul><li>3.2.1.4 Modeled Registers</li><li>3.3 LINUX OPERATING SYSTEM</li></ul> |    |

|     | 3.3.1 Conceptual Architecture                                                  |    |

|     | 3.3.2 Exception Management                                                     |    |

|     | 3.4 FAULT INJECTION ENVIRONMENT                                                |    |

|     | 3.4.1 Fault Model Definition                                                   |    |

|     | 3.4.2 Fault Injector Module                                                    |    |

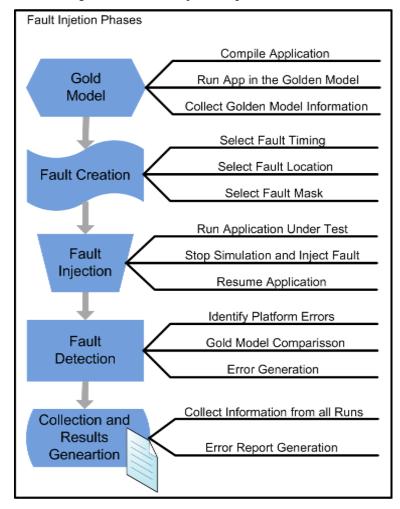

|     | 3.4.2.1 Fault Injection Phases                                                 |    |

|     | 3.4.3 Falure Classification                                                    |    |

| 4   | APPLICATIONS ENVIRONMENT                                                       |    |

| -   | 4.1 TESTING PLATFORM                                                           |    |

|     | 4.1 TESTING PLATFORM                                                           |    |

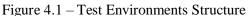

|     | 4.3 FAULT DISTRIBUTION                                                         |    |

|     | 4.3.1 System Observability                                                     |    |

| _   |                                                                                |    |

| 5   |                                                                                |    |

|     | 5.1 INTERRUPTION-BASED PHYSICAL ENVIRONMENT COMPARISON                         |    |

|     | 5.2 ENVIRONMENT COMPARISON                                                     |    |

|     | 5.2.1 Register Fault Susceptibility Analysis                                   |    |

|     | 5.3 SILENT DATA CORRUPTION CLASSIFICATION                                      |    |

|     | 5.4 LINUX OS AND ERROR MITIGATION                                              |    |

|   | 5.5     | OVERALL ERROR RATE                                                                                | 79 |

|---|---------|---------------------------------------------------------------------------------------------------|----|

| 6 | COI     | NCLUSIONS                                                                                         | 82 |

| R | EFER    | ENCES                                                                                             | 85 |

|   |         | DIX A – COMPLETE BENCHMARK RESULTS                                                                |    |

|   |         | DIX B – LATS 2016 PAPER                                                                           |    |

| A | I I LIN | $\mathbf{DIA} \mathbf{D} = \mathbf{LA} \mathbf{IS} 2010 \mathbf{I} \mathbf{AI} \mathbf{EK} \dots$ | 93 |

#### **1 INTRODUCTION**

Failures in integrated circuits (ICs) such as complex embedded systems can be responsible for endangering human life. Because of this, the demand for secure systems has grown considerably in recent years, a phenomenon that can be observed by the continuous research activity in the area. A secure system is characterized by several attributes, including reliability, availability and debugging capabilities [1], [2]. Among these systems, microprocessors are present in most digital systems due to its reprogramming flexibility, performance and especially cost, which is still not comparable with other devices such as FPGAs. These reasons led microprocessors to various application areas such as medical, automotive and aerospace, where the safety factor should be considered the most important.

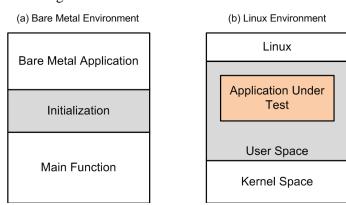

Safe-critical applications seek high reliability. They are usually composed of single or multi-core processors that may run embedded software developed with or without operating systems. Bare metal software is a term used in embedded systems when the program code is directly hosted on the target microprocessor and is self-managed. They allow high controllability of hardware and software flow. Additionally, maintenance, debugging and troubleshooting of code is easier and less time consuming. Operating systems can provide the availability of hardware resources for applications with a high level of complexity. The increasing need of this complex operations and resource sharing demands better using of the available capabilities as well as better programmability.

However, erroneous behaviors in this type of systems have been observed since the early 70s. Phenomena such as soft errors can result in serious failures, and their incidence is worsened due to the significant decrease in the ICs' transistor size [3]. Soft errors occurs due to transient faults and are mainly observed as bit-flips in memory elements operating under a radiation environment [4], also called single event upsets (SEU). The radiation environment can be space or on Earth, where neutrons interact with the material provoking secondary particles such as alpha to provoke transient faults [5]. Soft errors becomes as a representative issue while projecting a microprocessor, since the effects of SEUs can be noticed by failures in data results or deviations in the application flow. Not only the physical architecture, but the code architecture itself influences directly its performance in front of soft errors, which are the main aspects to be considered in a reliable efficient design.

In this way, it is mandatory a preliminary analysis of the embedded systems microprocessor behavior in critical applications without and with operating system [6][7], and

fault injection experiments have shown to be one of the most effective techniques for reliability evaluation of an IC [7][8]. However, a fault injection environment is costly and complex, as it requires compliance of numerous parameters, such as injection model, list of failures, workload, data acquisition mechanism and data analysis methodology, which directly influence coherence and results interpretation [9].

Therefore, in this work we adopt the use of a virtual platform capable of simulating embedded systems running real application code with performance comparable to a traditional system, in the order of hundreds of MIPS. Originally developed to accelerate the development of software, such simulators typically offer a range of CPU models and memory systems for exploitation of resources during development stage [10], allowing the analysis and implementation of different applications or operating systems for several architectures, including multiprocessor systems. Currently UFRGS conducts research using the Open Virtual Platform (OVP) OVPsim, which has shown great applicability for environments development for fault simulation. Compared to the others, which reach rates of around 200 KIPS [11], the OVPsim can achieve simulation speeds up to 100 MIPS. This factor was decisive in choosing this platform to model the embedded system used in this work.

In view of these considerations and along with OVPSim virtual platform, this work aims to compare soft error susceptibility in embedded software that was developed for a bare metal environment and under an operating system. It also analyses the architectural vulnerability factor (AVF) of the register file in the well-known embedded microprocessor ARM Cortex-A9, widely used commercially in low power or thermally constrained applications. The soft error analysis is performed by fault injection with the OVPSim-FIM module that was proposed by [12], capable of simulating SEU type faults on the processor registers bank, producing bit-flips with controlled locality and temporality, allowing investigation of the failures detected and treated by both the platforms. Another contribution of this work, besides the comparative analysis of application environments, is the improvement of the mentioned fault injector, allowing Operating System analysis from processor architectural perspective to software masking level.

A set of 11 applications was used as benchmarks that diversify control and data flow behavior. Those applications were compiled for the target architecture and run directly on the processor for the bare metal tests. The chosen operating system for the comparative tests was Linux, mainly because it has open code, which significantly facilitates the controllability and observability required by the experiments. Beyond that, it is worth mentioning that Linux is already considered as an option of a commercial purpose operating system, which is being included in a wide range of applications, including those with reliability requirements [13].

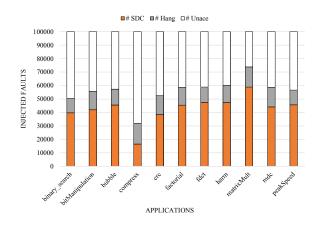

During the fault injection campaign, it was injected 100,000 faults in the register file to evaluate each benchmarks. Results were classified into masked faults (UNACE), silent data corruption (SDC) and hang. Results show that applications running in Linux environment are usually less prone to failures due to bit-flips in the register file, while bare metal applications have shown to be more susceptible to this faults, specially silent data corruption (SDC) failures.

This work is divided as follows: Chapter 2 evaluates faults in embedded systems, going through fault injection techniques commonly used in these environments, failure classification and presenting the OVPSim platform, discussing its operation and organization. Chapter 3 describes the proposed embedded system architecture, including the ARM Cortex-A9 CPU and its modeled functionalities, the Linux operating system and the fault injector structure, with failure classification and special features. Chapter 4 introduces the test platform and used benchmarks, explaining the fault distribution methodology and system observability. Chapter 5 exposes the results in many forms, such as environment comparisons, detailed classification, Linux error mechanism observation and overall error rate analysis. Finally, Chapter 6 presents the conclusions.

#### **2 FAULT EVALUATION IN EMBEDDED SYSTEMS**

The radiation effects in embedded systems have become a concern for safe critical software developing, which includes land level applications like medical, military and aerospace applications. Soft errors arise because of these radiation interactions, causing undesirable changes in memory elements that may lead to catastrophic failures. In most cases radiation tolerant COTS processors are not financially viable, so even devices used in such applications are the same we can find in regular cellphones or computers. It is therefore essential that embedded systems can be evaluated with respect to their susceptibility to faults in order to determine its limitations and, based on this, develop outline methods such as tolerant software techniques.

#### 2.1 Defining an Embedded System

An embedded system comprises a broad field of study and therefore there are many definitions of what it is. Depending on what's the study aims to emphasize the definition can vary, but in Noergaard [14] we found a short and objective designation that is aligned with the work proposes, defining an embedded system as an applied computer system.

An embedded system can be seen as a resource manager, which provides an orderly allocation of processors, memory, input devices and output data. It is found in a wide range of devices and combines software and hardware. However, different than an operating system, it is a physically limited computer system, usually with size, power and memory constraints, which has limited and specific, functions [16]. A notable example of embedded systems was the Apollo Guidance Computer, a redundant hardware used in the spacecraft control, with error recovery routines, meaning that that it one of the first embedded systems was fault tolerant [17].

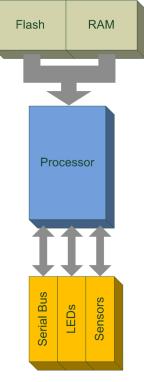

An embedded system is depicted in Figure 2.1 with its main divisions: CPU, memory and peripherals. Additionally, a communication layer and the embedded code can be listed, since the system must interact with external elements and its tasks shall be defined [18].

Figure 2.1 – Embedded system with CPU, memory and peripherals

Source: Author

An embedded system has one or more CPUs, which are responsible for fetching and executing instructions from memory. It can be considered the main system component, and has a well defined execution cycle, that includes searching instructions from memory, decode them to determine the operation and operands, execution, external memory accesses and writing back to updated values. Each CPU has a specific set of instructions and all application code shall be translated to this specific set before loaded into the embedded system. Furthermore, as the access time to memory to fetch instructions or operands is bigger than the time to perform them, the CPUs have internal registers to store key variables and temporary results [16]. Embedded systems CPUs, as commented, are intended to specific tasks, thus it is common to found several devices models, which should be considered depending on the application, such an Application Specific Instruction-set Processor (ASIP), a RISC or CISC architecture, a Digital Signal Processing (DSP) [19] or intended for low power applications [17].

Another major component in an embedded system is the memory. Ideally, the memory should be non-volatile, inexpensive and faster than the processor, so that the CPU was not delayed, but today technology does not meets these requirements. Therefore, the system memory is organized in layers, where the faster, smaller, and proportionally more expensive

memory, are closer of the CPU in terms of access, while memories with greater storage capacity are more distant. The memories order, from the slower to the faster, and technologies typically are internal registers, cache memory, external RAM and Flash memories or hard drives [14] [16]. From the application execution point of view, memory can be organized as instruction and data memories, which represents only a logical separation to determine how the CPU will organize the instructions under execution (internal registers, cache and RAM), the application code (Flash or hard drive) and the operations results (all layers).

Peripherals or I/O devices may consist of two parts: a controller and the device itself. The controller tend to have standard interfaces with the CPU, which helps to share communication resources between them, but as each peripheral has its own purpose, typically a driver should be used. The devices are commonly used as auxiliary communication, I/O driving, sensing, status or additional storage, adding more functionality to the embedded system [17].

Finally, the non-physical part of an embedded system is the embedded application, which uses all the described parts of the system. The code developed by the programmer must be compiled to the intended architecture, being converted into machine code, which will reside in the physical platform. The CPU has a initial state and starts to fetch instructions from a known place that depends on the processor model. Thereafter, the sequence of instructions performed by the CPU coordinate the operation of the embedded system, including communication with peripherals[17].

#### 2.2 Fault Injection in Embedded Processors

To understand the implications and assumptions around fault injection in embedded processors, definitions regarding terminology must be defined, as well as the nature of a fault, like what provoke them and how faults react in a system and become an error. As well, concepts concerning how it interacts with operating systems and measurement metrics are discussed in this section. The literature define the terms that surround this work in different ways, trying to explain a common phenomena. To avoid misunderstandings, we use as reference the article developed by [71].

As the author suggests, a failure is defined as an unexpected behavior or unwanted operation of the target system that is perceived by the user. The error concept is understand as an state of the system that may lead to a failure, i.e., the error create a condition in which the subsequent computing operations may fail. Finally, the error state is achieved by the effect of a fault, that is defined as the error physical reason.

#### 2.2.2 Faults in Embedded Systems

A system is said to be fault-tolerant when it has the ability to perform properly their duties regardless of the occurrence of faults [21]. Even a system that has apparently been developed properly is subject to failures due to wear of the devices or design errors that result in a logic failure. Two types of failures may occur in a system: the first is the natural failures caused by wear, internal or external sources or a component; second, the failures resulting from an accidental or intentional human action [22]. A situation in which these two types of failure can occur is, for example, an operator setting the parameters of an installation to perform an overloaded task. This systematic operation will cause the installation, inevitably, to malfunction due to wear of its parts. In this particular example, an error caused by human action generated a natural lack. The occurrence of these faults does not imply that other type of failure may not happen.

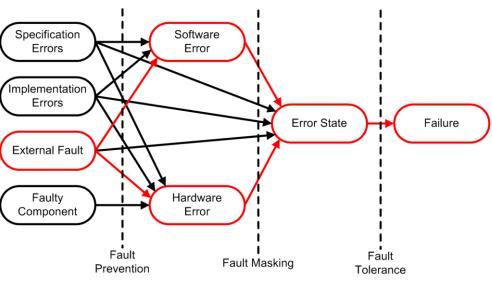

However, fault-tolerant systems should be able to drive the system to a safe state when the error is detected, or allowing the system to operate in degraded form, but meeting the minimum requirements of the same. Given this context, there are some techniques to give proper treatment to this events: (a) redundant structures to mask components that suffered an error; (b) error control codes and double or triple voting mechanism to discover or correct erroneous information; (c) diagnostic techniques to locate defective components; (d) and techniques for automatic conversions to replace a subsystem that has crashed [22]. In 1984, Johnson defined the three main techniques to try to improve or maintain the normal operation of a system: fault avoidance, fault masking and fault tolerance [21]. Fault avoidance aims to block the fault occurrence or even its effect that is the error. It can be achieved through good project management practices and system testing for design mistakes not observed in the detailing phase. The idea is to prevent the system to be released to the market with a "bug", which in safe critical applications can be catastrophic. In this regard, extensive testing of the application is used. However, the time spent in the testing phase will increase the "time to market" (amount of time from conception to launch the product on the market).

The fault masking is applied in real-time system and aims to prevent the error from spreading to other system components or leading to an error state causing a failure. One way to implement this technique is through the implementation of voters.

The fault tolerance, unlike the others, is not intended to eliminate the presence of the fault or its propagation, but drive the system to a state that is acceptable in terms of execution and security. There are four principles on which is based the use of the fault tolerance: detection, location, containment and recovery.

Figure 2.2 shows a flowchart where the techniques described by Johnson can be used to increase the guarantee proper functioning of the system [21].

Figure 2.2 – Johnson's Fault Tolerant System Flow

Source: Adapted from [21]

In this work, our attention is around the path marked in red, except that we are not proposing any mitigation technique, but in fact, exposing an embedded system weakness to soft errors by injecting external disturbances, analyzing if it manifests in hardware or software and classifying the arising failures.

#### 2.2.3 Radiation Effects in Embedded Processors

One of the main concerns around failures in embedded processors relies on external sources, especially the radiation effects that may cause soft errors. They can be divided in effects due to Total Ionizing Dose (TID) and SEEs (Single Event Effects). As discussed by [36], this phenomena occurs due to the impact of atmospheric particles, like neutrons, that collides with silicon atoms of the device, causing nuclear reactions that generates an internal ionization. These phenomena and its impact in embedded systems is the central theme of this work, but it is necessary to understand the type of fault in which the device is exposed.

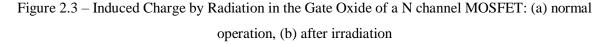

The TID effect is cumulative, resulting in degradation of characteristics of the electrical parameters of the electronic device over time due to the deposit of charges. They are long-term effects that depends on the intensity of radiation and the time that the circuit is exposed to this radiation. In a transistor gate, for example, the TID may cause an increase of the skew and leakage current due to changes in the voltage thresholds. A big exposition to this particles can result in error of the electronic device [20], as shown in Figure 2.3 below.

Source: [24]

The total ionizing dose is measured in rad (radiation absorbed dose). The rad represents 100 ergs of energy deposited per gram of material, which can be correlated with

Joule, such that  $1 = \text{erg } 0,1\mu$ J [25]. Since the energy depends on the material, the units need to be expressed in this terms, such as the silicon: 100 rad (Si) [20].

The TID is specified in units of rads in silicon (rad(Si)), where one rad is defined as the absorbed radiation dose. A rad is a measure of the amount of energy deposited into the material and is equal to 100 ergs (6.24E4 10 eV or NJ) of energy deposited per gram of material [25]. The energy deposited in a device must be specified for the material of interest. Thus, for a transistor of a metal oxide semiconductor (MOS), the total dose is measured in units of rad (Si) or rad (SiO2). The ability to resist to TID in reinforced components against radiation is also defined in rads or krads [28].

The effect can be reduced by shielding or by changing the default device fabrication process. When using shielding the idea is to include a layer of a material, like aluminum, to absorb a range of charged particles, specially low energy ones. Depending on the environment profile, this technique may not be effective, since high energy particles can still cross the shield layer. Another solution, as mentioned, is to modify the fabrication process by including, for example, an epitaxial layer in the high-doping regions of the transistors or an oxide layer in the substrate [20].

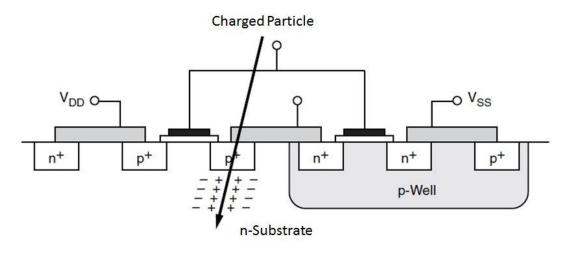

The category that is analysed in this work and that may result in undesirable effects in the system functionality are the Single Event Effects (SEE), described by [20] also as electrical disturbances due to colliding particles, but now the high energetic particle does not need to accumulate to generate an observable effect, it has such energy that it can change the state of a given device. Figure 2.4 depicts the effect of a single charged particle passing through the structure of a PMOS transistor.

Figure 2.4 – Particle Crossing the Substrate of a Transistor

#### Source: [20]

As mentioned, the particle must have enough energy to transfer the charge necessary in the transistor gate to make state changes in its outputs. This charge is represented in the following equation by Qcrit.

$$Qcrit = Cnode \times Vnode \tag{2.1}$$

According to [20], in equation (2.1), Cnode denotes the capacitance between the nodes of transistors and Vnode is the transistor operating voltage. Today, reducing the size of transistors and the significant increase in transistor density on a single chip increases sensitive to SEE, in part since the chances of collision are bigger, in the other side the capacitance and stored charges of the devices decreases, which results in a lower Qcrit [27] and for consequence the range of potential charged particles necessary for generating an upset increases.

The SEE can occur in different ways such as a transient effect (SET), upset (SEU), latch up (SEL), door break (SEGR), among others. A typical case is in a circuit with memory elements, for example, where a single event may provoke that an incorrect value is stored and may produce an error that will persist until the value is overwritten. Also, the SEE may flip a signal in a combinational logic, generating incorrect values in arithmetic operations or even producing a wrong output, such an interruption [20]. In this work, we will analyze the Single Event Upset effects, since it is one of the most common persistent and latent errors.

#### 2.2.3.1 Single Event Upset

The term Single Event Upset and the correlation with charged particles appeared in [26] for the first time as it is known today. The acronym has been used to describe disorders in digital circuits of memory devices, caused by radiation or cosmic rays and they are the focus of this work

They differ from the SETs, since they are not transient, associated with the inversion bit memory elements. They are also referred to in the literature as soft errors and can have an indefinite duration or may be fixed after one or more clock cycles. The SEU is called single bit upset (SBU) if only one memory element inverts its state and multi-bit upset (MBU) if more than one element changes [20].

A characteristic of SEUs is that they are random events and, therefore, they may occur at unpredictable times. For example, they can damage the contents of a processor register during the execution of an instruction, which in case of a pipelined processor may result in an instruction being correctly executed in the first pipeline stages and then corrupted in the middle of operation, avoiding any pre decoding correction mechanism and causing unpredictable effects in the data flow.

### 2.2.4 Failure Classification, Metrics and Operating System Impact

As mentioned, radiation effects can lead to soft errors in electronic devices according to ionization characteristics. In the firsts occurrences it is not permanent since only repeated events in the same point can damage the silicon structure, and so the error is called "soft".

Not all soft error occurrences generate a manifested failure. They are the originating factor that results in the appearance of an error. When a soft error occurs, the system can or cannot be driven to an inconsistent/incoherent state, which characterizes the existence of an failure. In a given system, [30] defines the probability that the soft error has to generate a failure, as shown in equation (2.2).

$$\sigma = \sum_{i} \sigma_{raw} \times V_i \tag{2.2}$$

The author introduces new terminologies to define the probability. The cross-section is represented by  $\sigma$  [cm<sup>2</sup>]. It defines the radiation susceptible area in which an error happens if a particle collides. Depending on the technology, the radiation sensitivity varies and it is expressed by the constant  $\sigma_{raw}$ . Finally, the probability to generate an error is represented by V, which means de vulnerability factor.

The vulnerability factor is often estimated using radiation test campaigns with accelerated particles as a reason of the number of errors observed and the particles flux, which is the amount of particles per unit area. In some cases, it is possible to estimate the vulnerability using simulation if a detailed description of the design is available to the tester.

During the test campaigns, either radiation tests or simulation, the most usual metric is the soft error rate (SER), which indicates the number of errors manifested in the functionality of the system during a defined time, commonly represented by the terminology Failure in Time (FIT) and expressed by [31] in the following equation.

Soft Error Rate =

$$\frac{\eta}{N} \times \varphi \times 10^9$$

(2.3)

The equation shows that under a fluency of particles, expressed by N, the number of errors observed, indicated by  $\eta$ , and the total particle flux, the  $\phi$  in the equation, is possible to determine the soft error rate in terms of FIT. Since the Failure in Time express one failure per  $10^9$  hours, the scale is also included in the equation.

The SER is the main parameter to evaluate in a device as it indicates how tolerant it is to radiation. A well-controlled environment is required to determine this metric, since the flux shall be constant and the error properly detected. That is why simulation techniques has had so much visibility, allowing practical and precise measures as long the device model is correctly represented.

To guaranty a good evaluation, in an embedded system context the failures can be divided in two types: functional interrupts (FI) and silent data corruption (SDC). The functional interrupts means that the system or application running in the processor hanged or crashed and may lead the system to an unresponsive state, eventually requiring the reboot or a power cycle to recover. Silent data corruption means that application has finished but its result differs from the expected one. Note that not only the produced results of an algorithm, for example, is important but the entire memory space, since latent errors may occur due to data corrupted that not necessarily was used after soft error event, remaining undetected for a long period.

According to [32] the vulnerability factor can take into account the SDC and FI classification, as they represent different criticality depending on the system. In this manner, it is possible to classify the vulnerability into FI factor and SDC factor that indicates the probability of a soft error in a defined element to generate a functional interrupt or a silent data corruption, respectively.

This classification became even more important when an Operating System (OS) is involved. The work presented in [33] has shown that errors in the presence of an OS tend to cause FIs, and SDC rate is not significantly influenced as its occurrences has the application as the major contributor.

#### 2.2.5 Fault Tolerance Evaluation Techniques

Fault injection is the most common and widely accepted approach for analysis of safe critical systems in the presence of faults [34]. The fault injection techniques try to provide

information about the reliability of the design under test (DUT). This information can be about: a) compliance validation with reliability requirements; b) detection of weaknesses in the adopted fault tolerance techniques and; c) DUT behavior forecast in the presence of faults.

Fault injection is related to all techniques that simulate or emulate the device behavior in the presence of a fault. Among these techniques are those applied mainly to processor systems in which software changes are made to simulate the occurrence of a fault in the hardware device. Thus, it is important to have a distinction between fault injection in hardware and software, the latter is outside the scope of this work.

The fault injection techniques are not limited on the injection approaches. The techniques involve the complete process that comprises the entire environment required for startup of the DUT, selecting the appropriate workload, the capture of relevant data, comparison with the fault-free DUT data, classification of the effects and monitoring of the whole process. As will be discussed later, the approach of this works involves these steps, where the analysis is made according to a comparison between a fault-free run of the system and a faulty run, which is a run under the effects of the fault injections.

The fault injection method depends on the type of DUT being tested. In the case of memories, for example, the effect being examined by injecting faults will be predominantly SEUs. Another factor to consider is the possibility to cause real faults on the device, i.e., physical faults in the real device or if only fault models (logical) will be applied. The abstraction level of the fault type is directly related to the DUT that can be a COTS, a prototype or a design model. Observability is another important parameter, since it interferes directly on the quality of the extracted results. Finally, the results will be direct influenced by the chosen injection technique, since more realistic techniques like tests under radiation has less observability than simulation methods that, on the other hand, are less precise in terms of device behavior.

The fault injection campaign according to [35] can be divided in four basic elements that are applicable to all techniques:

- Fault Model: Injected faults are used to model the SEEs at different abstraction levels. At least the level of the system behavioral model shall be used. When a COTS is being evaluated, different fault models can be applied, depending on the test needs and device observability.

- Workload: Used to emulate the typical operation of the system under test.

- Observation Elements: Those are applied in the system to classify the effects of the injected faults. Once a failure is identified, it may be classified as any of the many types of failures definable. It is also common to classify the fault itself.

- Measurements: States the degree of dependability of the evaluated system and can be connected with the metric employed (commonly the SER).

This section provides an overview of all existing fault injection techniques. Techniques are presented in two groups, namely those working with physical fault injection and injection techniques that address at the logical level.

#### 2.2.5.1 Physical Fault Injection

Physical fault injection methods use external sources to allow tests with radiation, electromagnetic noise and aging of ICs. The purpose of these tests was to analyze the strength of a COTS or qualify a prototype as hardened against the effects caused by radiation.

The cosmic radiation is the main source of SEE in ICs. Therefore, performing tests with the device at high altitude or even in space is the most realistic way to assess the sensitivity of the ICs to SEE. However, considering the low probability of error, it would require hundreds of thousands of samples of the DUT to obtain a valid measurement, making the time and cost of this approach unfeasible. The particle accelerators are used to classify these products, performing tests that last for hours or days [34]. In these tests, various types of particles are used with different energy values in order to cause different effects. The types of particles and typical energy values used to generate a SEE are detailed in [36]. These parameters are standardized according to the final application of the device. Spatial intended devices are exposed to a different radiation environment than medical equipment, for example, and are defined by space agencies or committees as the JEDEC who created the standard JESD89 [37], which defines the requirements and procedures for testing of SERs for ICs.

Fault injection using laser rays is similar to the method that uses heavy ions in the sense of the beam is applied directly on the silicon surface. However, the laser beam is much more accurate, and thus it is possible to inject faults in specific places in a more controlled way. The incidence of the laser beam in silicon can cause effects similar to those caused by particles of cosmic rays and this method is usually associated with the state change of circuit elements and is used to test the effect of SEU events. With the help of a special microscope,

the use of laser to fault injection provides high accessibility as you can select the region to execute the campaign in the circuit. Thus, the fault injection is cheaper than systems who employ radiation tests. Furthermore, the laser needs a simpler fault injection environment since it is not necessary to isolate the DUT or the components in the periphery of the DUT that are not being tested and they didn't suffer disturbances caused by radiation, which would compromise the results of the analysis.

Unlike other physical techniques of fault injection presented, the method by induction values at the DUT pins requires physical contact between the test platform and the DUT. The method seeks to replicate the effect of a natural fault by forcing changes of the logical value of an IC pins. Considering the complexity of modern systems, fault injection in the pins is very limited due to accessibility limitation of the method. This technique is often employed for testing tools in combination with other techniques in order to extend the results. Solutions as Messaline, MARS, FIST, RIFLE described in [38] employ features of fault injection method in circuit pins.

#### 2.2.5.2 Logical Fault Injection

The results of physical injection methods provide realistic values of SER. It is widely used for hardening qualification of critical applications in harsh environments, like space. However, installations with neutron accelerators, for example, charge in the range of hundred to a thousand dollars per hour of exposure [39], i.e., physical fault injection is extremely expensive and thus it is necessary analysis solutions that can be applied earlier in the circuit design. The fault injection methods in logical level exploit resources available in order to insert the effect that a fault in hardware may provoke.

Between logic fault injection, software implemented (SWI) method is directly linked to the execution of specific pieces of software that modify internal elements (accessible by the user) causing the effect of a fault occurred in the hardware. The SWI method is related mainly to embedded processors systems where the normal application software is stopped for the execution of a fault injection code that changes an element such a register, a memory data, or even an application instruction. SWI also appears in the DUT behavior analysis to evaluate communication problems or interaction with other systems, for example, repeated/missing messages or inaccurate information, failure to read from memory, among others. This type of fault injection can be applied in different moments, which can be at compile time or at runtime. At compile time, changes in the software image are made and, when executed, it enables the simulation of an error in hardware. This type of fault does not need additional code to be executed and is generally used to emulate permanent errors. In the case of runtime fault injection, trigger mechanisms are used to notify the time of the fault injection. Timers or specific instructions in the code are used for stopping the implementation and starting the fault injection task. In [40] two processors PowerPC 750 running LynxOS were used along with Xception tool to emulate the effect of SEUs in the system. The Xception tool exploits the advanced features for monitoring performance and errors present in the processors and uses the exception mechanisms of the processor itself to identify the failures. Another tools in [38] like FERRARI, use timers to trigger a fault injection routine. The FIAT tool may delay tasks, corrupt messages or complete them abruptly. Finally, FTAPE tool can add fault injection drivers in the operating system.

The injection of simulation-based faults uses a model of the system being analyzed. Simulation models can use hardware description languages like VHDL and Verilog or a higher abstraction level like SystemC. In the simulation method, faults can be injected by the simulation tool or by changing the description of the hardware model. In the latter case, dedicated modules can be added in the model with the unique purpose of injecting faults or the use of components with the presence of a known error. In the higher abstraction level, is possible to adapt the simulation tools in order to use commands to control internal signals of the system model. This method is dependent on the simulator functionalities and available commands. However, there is no need to change the hardware model. In [41], a model of LEON3 Gaisler processor used by the European Space Agency (ESA) described in SystemC is used for fault simulation. This model described in SystemC is implemented at transaction level (TLM) and employ dedicated modules that are used to simulate the effect of faults in the memory sections (buffers, instructions and data memory, etc.) of the processor. The MEFISTO tool presented in [42] uses saboteurs and simulation commands to execute a more detailed analysis of the error behavior in the VHDL model. Tools like VERIFY propose an extension of VHDL description to add features for fault injection in [38].

Current processors have specific resources to support testing and debugging. These features, known as on-chip debug (OCD), also enable the fault injection and observation of the effects externally to processor. The FIMBUL tool developed in [43] uses the test access port (TAP) of the Thor processor for fault injection. The TAP allows access to internal scan chains and the periphery of Thor processor, thus transient faults are injected throughout where

the chain have access. As a comparison, the MEFISTO tool that uses the simulation technique has a slightly higher error coverage than FIMBUL tool that uses the TAP technique, but in the other hand, it proved to be a hundred times faster. The work presented in [44] proposes changes in the debug infrastructure (OCD) in order to enable fault injection to support the verification of fault tolerant mechanisms. The OCD oriented to fault injection is based on the NEXUS standard and it is an additional hardware that automatically triggers in the occurrence of predefined conditions. The instruction address that will trigger the fault injection is generated at random from one of the values present in the address space of instruction memory. The same applies to the address of the data memory that will have its value changed when the mechanism has been triggered. After the faults have been injected, the results are recovered after the completion of all experiments.

The last logical fault injection method is the emulation FPGAs based hardware. It became popular in ASIC verification, and more recently has been exploited for rapid injection campaigns. The term emulation in this context is related to prototyping the circuit to be analyzed in FPGAs. Many techniques that employ these devices use it only as a mean to perform fault injection and quickly identify if the method can be implemented in other technologies. The controllability in most cases is achieved accessing the configuration memory, causing virtual bit-flips. Another approach consists in adding hardware blocks to support the fault injection. An early work using FPGA for fault emulation is shown in [45], which implements permanent errors (stuck-at) connecting signals at constant values. For each injected fault, the circuit was synthesized again and thus the bit-stream had to be reloaded in the FPGA to a new emulation. Among the newer methods that use FPGAs for fault emulation two types of approaches can be perceived. The first method is called instrumentation; it inserts logic in some way in the circuit in order to increase the control and observability of the DUT during its execution [46]. The second uses existing partial reconfiguration capabilities available in newer devices to identify and recover part of the internal circuit [47].

This work uses the simulation-based method and employs OVPSim tool, as shown in the following section.

#### **2.3 Open Virtual Platform (OVP)**

A virtual platform is a complete simulation of a computer system. All hardware is abstracted into a model, in which a regular software is able to run, i.e., the platform should be modeled in a way that compiled application is no different from the actual physical hardware.

The virtual platform can be seen as an Instruction Set Simulator (ISS), which simulates not only the CPU, but also the complete system, including memory, cache and buses. The modeling of virtual platforms is defined as modeling in electric system level [48]. This environment can be placed between a RTL level and the functional level description, and is mostly used when the cycle accurate RTL is considered to be too detailed, but still requires a truthful simulation of at least instruction level.

Thus, a virtual platform is designed to: a) enable the development of software more effectively and with better prediction; b) minimize dependence on hardware and; c) increase the test efficiency.

Open Virtual Platform (OVP) is the tool that is used for the implementation of the virtual platform in this work. The Imperas<sup>™</sup> Software Limited announced the formation of the alliance OVP to service the needs of the market. This alliance has created models of CPUs, scan tools, debugging and analysis, in addition to simulation platforms. According to the company, the platform allows the development of virtual prototypes with instruction accuracy of up to 100 MIPS in conventional computers [49].

The OVP has three main components:

- APIs that allow C models Additional modules are developed;

- A collection of models of processors and peripherals on open source;

- The OVPsim simulator, responsible for the implementation of these models.

#### 2.3.1APIs

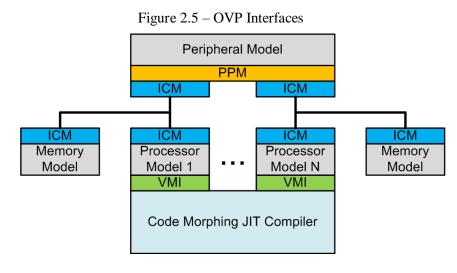

Modeling an environment requires development of the main parts of a real embedded system, such processors, memory and peripherals, but also the platforms and the integration environment. The platform is responsible to promote the integration of the behavioral components. Processors execute the compiled code and the peripherals enable a way to represent the environment in which the application will interact. Thus, the OVP is constructed of four interfaces:

- CPU Manager or Innovative CPU Manager (ICM);

- Virtual Machine Interface;

- Interface with behavioral model of the hardware;

- Interface for programming the peripheral model.

The interaction between these interfaces is shown in Figure 2.5.

Source: Adapted from [50]

The ICM is an API codded in C used to create the platform interconnection environment and netlist with the modeled system to use along with the OVPsim simulator. Through, it is possible to instantiate multiple processors, buses, memories and peripherals. The ICM interface is also responsible for linking these modules and it allows applications to be loaded and executed on instantiated memories [50]. Figure 2.5 locates the ICM in the platform environment as described above in which it interfaces between various modules in the platform.

The Virtual Machine Interface (VMI) is interfaced with the C based processor model, allowing communication with the simulation kernel and other system components. The VMI is the centerpiece for the high performance provided by the OVP, since the processors use a morphing code approach that is coupled to a just-in-time (JIT) compiler that maps the model instructions to native local machine instructions. Between the processor model and compiler there is a set of optimized commands where the processor operations are mapped, being responsible for the OVPsim to provide fast and efficient interpretation of the native machine capabilities. Some of the VMI abilities are [51]:

- Provide virtualization features, such as file I / O, allowing direct execution on the host using the standard libraries that are provided with the environment;

- Instruction set templates encapsulation with OVPsim, if they export some basic characteristics such as availability of Instruction Set model as a shared object;

- The VMI can be used for both RISC processors and CISC processors, supporting any instruction format;

- Finally, it allows the modeling of L2 caches and other extensions around the processor.

#### 2.3.2 Hardware Behavioral Models

The Open Virtual Platform has many processor models like the Altera NIOS, ARC, ARM Cortex A, ARM Cortex M and ARM Cortex R, Xilinx MicroBlaze, several MIPS models, Power PC, Renesas and NEC, most of them provided by the processor manufacturer. In addition, a large number of available devices allow the assembly of a complete platform, including various types of memories, bridges, DMAs and UART modules.

As mentioned, the processor models are instruction level accurate. Behavioral models based on instruction set simulators aim to implement the instructions considering the real number of cycles to execute and perform the IO operations along with each step of each instruction. However, OVP processor models execute each instruction in a functional approach, disregarding timing. The precision level of OVP allows internal registers to store properly the values at the end of each instruction, generating all expected effect. The platform executes an instruction at a time, but abstracts everything regarding the pipeline, for example. The main disadvantages of the platform rely on the high abstraction level of the architecture, that doesn't permit an clock cycle analysis of the tests, as well deeply architecture examination.

The OVPsim also supports description of multicore platforms. It can simulate multiple processors including configurations with shared memory, and heterogeneous multiprocessor systems. The model performance depends on variants of the chosen processor and the nature of the application, but it is possible to achieve speeds of hundreds of millions of instructions per second. As OVP models can be compiled as common objects, they can also be encapsulated in any simulation environment capable of using shared objects. This includes C, C ++ and SystemC environments.

# 3 CASE-STUDY, PROCESSOR-BASED SYSTEM AND FAULT INJECTOR ARCHITECTURE

An embedded processor can be defined as a processor that is responsible for computation and control of devices that are not regular computers. Embedded processors are used in several product fields, including automotive, networking, mobile, medical and aerospace, and according to [52], they has the following design criterias: (a) performance, represented by the maximum of data that they can process per unit of time and can be achieved by parallel architectures, multi-level caches, function specific internal modules, clock frequency, etc.; (b) power, that depends on the technology process, die area, number of transistors, clock frequency, gate sizing and core voltage; and (c) cost, in which the manufacturability is the key point, being related with the circuit complexity and area. In this way, modern processors needs to balance the use of special architectures, such as multipliers, additional caches, memory controllers and branch predictors, depending mainly on the market share they want to reach.

In this chapter, the ARM Cortex-A9 series processors is evaluated, a mobile processor constrained for the embedded market. This processor has its own OVPSim model provided by ARM itself, making this analysis more reliable in terms of functional equivalence to the physical device. This processor was chosen because it is present in many commercial platforms such as Zynq<sup>TM</sup>-7000 All Programmable SoC from Xilinx [67] and Cyclone V from Altera [66]. These FPGA based platforms allows failure analysis methodologies on the real target, and can be used further on to correlate and validate our results. The Linux operating system is discussed in terms of how its architecture can contribute to processor dependability. Finally, the fault injector organization, embedded system integration characteristics and the main injection phases are explained.

#### 3.1 ARM Cortex-A9 Architecture

The ARM Cortex-A9 has a specific set of features and functionality beyond the traditional ARMv7 architecture in which it was based, in order to provide a high performance and low power consumption. The main features of the architecture are described in this section.

#### 3.1.1Main Functionalities and Relevant Features

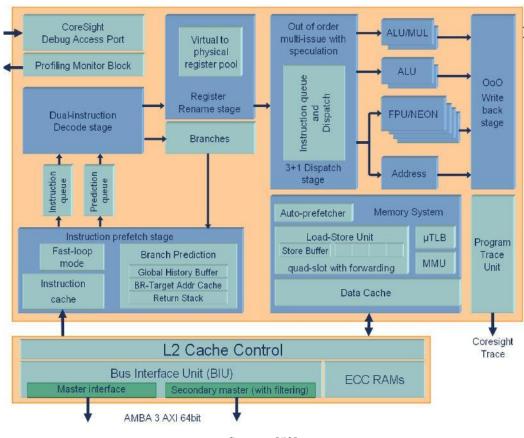

The processor ARM is based on a RISC architecture, being the most popular embedded processor for mobile applications. It happens due to its architecture that can provide high performance and operates within the mobile power acceptable range, which is under 5W of constant power consumption. With its high performance ARM macro equipped with an L1 cache subsystem, it enables the use of a full virtual memory system, reaching around of 98% of mobile devices and 75% of all 32-bit embedded processors [53] [52].

All processors of the Cortex-A family are designed for mobile purposes, but is also intended for televisions and TV receivers. The Cortex-A9 uses an advanced version of the instruction set of the Cortex-A8, based on the ARMv7 ISA, with extended FPU and ability to perform data level parallelism, since it has multiple internal processing elements. The parallelism allows the core to perform several optimizations. The ones that are considered relevant for this work is:

- Out of order and speculative execution, that may result in a more allocated register file;

- Dynamical renaming of physical registers, promoting autonomy from the code and leading to a non obvious register allocation.

- Hardware based unrolling of loops, that spreads control information among available registers .

Figure 3.1 present the top level diagram of the Cortex-A9. The described functions can be located after the decoding stage.

Figure 3.1 – ARM Cortex-A9 Block Diagram

The Cortex-A9 MPCore processor is the one modeled for the OVP environment and includes an enhanced version of the ARM MPCore technology, which provides the flexibility for vendors to implement between one and four CPUs in a cache coherent system architecture design, as in the Zynq<sup>TM</sup>-7000 SoC that implements 2 cores.

The ARM Cortex-A9 embedded in Zynq and Cyclone FPGAs are a dual-core ARM that can be configured to work as single or dual core and to access an embedded SRAM memory, caches level 1 and level 2 and a flash-based memory located outside the chip. In this work, we use the model of the single core Cortex A9.

## 3.2 OVP Model of the ARM Cortex-A9 Architecture

As described by Imperas<sup>©</sup> [55], the processor models used along with the OVP simulator are shared object files, represented by the .dll files in Windows and by the .so files in Linux. The models may include support for SystemC integration.

The exclusive purpose of an OVP processor models is code conversion. It has the ability to translate the original application code previously compiled for the target architecture into the simulator own abstraction layer and for the just-in-time code mechanism, available in its VMI API. This API is used for disassembling and generation of the simulator interface, breaking the correlation with the original application, through a specific decoder that knows the real processor instruction set. The simulator is responsible for all the other tasks, leaving the execution complexity for the part of the environment that do not depends on the models being used. It implements the mentioned just-in-time mechanism that converts dynamically the original instructions into the simulator ones, memory allocation and other simulation dependencies [55].

### 3.2.1 Modeled Functionalities

The used OVP model is a single core processor modeled by ARM Ltd to be used along with OVP simulator, called "Cortex-A9MPx1". Its instruction model is accurate, and the simulation results of a single thread program will correctly match the actual hardware that it models. However, not all actual architectures characteristics are modeled, these being dependent on the processor used, since the existence of a given function is a developer's decision and not necessarily a limitation of the platform. Therefore, it is possible to find processors with and without cache implemented, for example, but as mentioned the Cortex-A9 model is provided by ARM with the purpose to provide means of simulated debugging software so that it can later be used in a real processor, a factor that indicates the equivalence between the model and the device is reliable.

### 3.2.1.1 Pipeline e Cache L1

The Cortex-A9 instruction pipeline is not modeled, so that the bus may not be accessed in the proper sequence, but it is assumed that all instructions conclude immediately when read from memory and in the same reading order, disregarding all of the steps of load, fetch and store, for example. This means that the instructions of the type Instruction Barrier and Data Barrier, such as ISB and DSB, are treated as NOPs, except for instructions with defined behavior at runtime only. The model also does not implement the functionality of a speculative fetch.

For this reason, typically caches are not modeled, although the platform has the resources to create both L1 as the shared L2, L3, etc. The ARM used in this work does not have caches or modeled buffers, nor the branch cache shown in real processor architecture. Cache handling instructions are implemented as NOPs, but again except for instructions with defined behavior at runtime, which are modeled. However, the cache control registers are present, allowing applications that normally make use of this resource, to run normally [56].

# 3.2.1.2 Performance and Timing

The OVP model approximate the processor performance, but does not model accurately the execution time of the real processor, since it would need to be cycle accurate. It is given an estimative of MIPS that represents the same parameters of real processors, but in the processor model perspective, each instruction is executed in one unit of time, meaning that a fair comparison can be done between application running in the same environment, but a real hardware can produce very different performance results. The idea of time used in the OVP simulator is based on simulation time, that is incremented at the end of each iteration, which is global across the simulator and is called simulation quantum [55].

# 3.2.1.3 Special Functions

According to the description of the real architecture [56], the special functions that were modeled in the ARM Cortex-A9 are:

- Specific instructions for memory reduction;

- Java byte code execution for JIT operations;

- Single Instruction, Multiple Data (SIMD) are supported;

- Functions for NEON media processing;

- Vector Floating Point Coprocessor (VFP) is modeled;

- Extensions for data security modules (TrustZone);

- Address translation for secured and unsecured virtual memory.

### 3.2.1.4 Modeled Registers

To support the implementation of a real processor application, whole register file and support registers are implemented, enabling a better reproduction of the real behavior.

| Name | me # of Bits Initial Valu |   | <b>Operation Type</b> | Function        |  |

|------|---------------------------|---|-----------------------|-----------------|--|

| R0   | 32                        | 0 | R/W                   | General Purpose |  |

| R1   | 32                        | 0 | R/W                   | General Purpose |  |

| R2   | 32                        | 0 | R/W                   | General Purpose |  |

| R3   | 32                        | 0 | R/W                   | General Purpose |  |

| R4   | 32                        | 0 | R/W                   | General Purpose |  |

| R5   | 32                        | 0 | R/W                   | General Purpose |  |

| R6   | 32                        | 0 | R/W                   | General Purpose |  |

| R7   | 32                        | 0 | R/W                   | General Purpose |  |

| R8   | 32                        | 0 | R/W                   | General Purpose |  |

| R9   | 32                        | 0 | R/W                   | General Purpose |  |

| R10  | 32                        | 0 | R/W                   | General Purpose |  |

| R11  | 32                        | 0 | R/W                   | Frame Pointer   |  |

| R12  | 32                        | 0 | R/W                   | General Purpose |  |

| SP   | 32                        | 0 | R/W                   | Stack Pointer   |  |

| PC   | 32                        | 0 | R/W                   | Program Counter |  |

Table 3.1 lists the modeled registers of the ARM Cortex-A9 architecture.

Table 3.1 – ARM Cortex-A9 Register File

Source: [56]

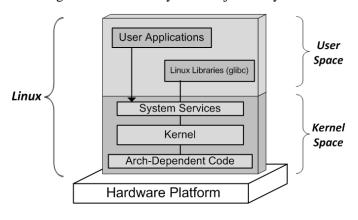

## **3.3 Linux Operating System**

The Linux kernel was selected as a target for our experiments as it provides a representative Operating System. The mainly reason for choosing this OS is that it is an open source environment, which significantly facilitates the controllability and observability required by the internal experiments. Beyond that, it is worth mentioning that Linux is already considered as an option of a commercial purpose operating system, which is being included in a wide range of applications, including those with reliability requirements [13].